複合電子部品及び複合電子部品の実装構造

【課題】複数の電子部品を含む複合電子部品の信頼性を向上させること。

【解決手段】複合電子部品1は、電子部品2と、導体層3と、支持体4とを含む。電子部品2は、素体10の対向する表面のそれぞれに、第1端子電極11と第2端子電極12とを有する。導体層3は、複数の電子部品2が有する第1端子電極11を電気的に接続する。支持体4は、導体層3が設けられる。複数の電子部品2が有する第2端子電極12は、回路基板の端子に接続されるための実装端子電極となる。

【解決手段】複合電子部品1は、電子部品2と、導体層3と、支持体4とを含む。電子部品2は、素体10の対向する表面のそれぞれに、第1端子電極11と第2端子電極12とを有する。導体層3は、複数の電子部品2が有する第1端子電極11を電気的に接続する。支持体4は、導体層3が設けられる。複数の電子部品2が有する第2端子電極12は、回路基板の端子に接続されるための実装端子電極となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の電子部品を有する複合電子部品及び複合電子部品の実装構造に関する。

【背景技術】

【0002】

複数の電子部品を一体化して1つの電子部品とする複合電子部品が知られている。例えば、特許文献1には、複数のディスクリート受動コンポーネント同士を分離し、複数のディスクリート受動コンポーネントに対する保護構造を有するメカニカルな受け構造を備えたことを特徴とする電子アセンブリが記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2004−40083号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1に記載されている電子アセンブリ(複合電子部品に相当する)は、複数のディスクリート受動コンポーネント(電子部品に相当する)がそれぞれ独立して組み合わされているので、それぞれの電子部品は、いずれも独立して回路基板に実装されることになる。特許文献1の技術は、1個の電子部品に不具合が発生すると、他の電子部品によって不具合が発生した電子部品の機能を補うことができないため、信頼性が低下するという問題がある。本発明は、複数の電子部品を含む複合電子部品の信頼性を向上させることを目的とする。

【課題を解決するための手段】

【0005】

本発明は、素体の対向する表面のそれぞれに、第1端子電極と第2端子電極とを有する複数の電子部品と、複数の前記電子部品が有する前記第1端子電極を電気的に接続する導体層と、前記導体層が設けられる支持体と、を含み、複数の前記電子部品が有する前記第2端子電極が、回路基板の端子に接続されるための実装端子電極となることを特徴とする複合電子部品である。

【0006】

この複合電子部品は、導体層によって複数の電子部品の第1端子電極同士が電気的に接続されている。このため、電子部品に不具合が発生したとしても、他の電子部品が正常であれば、正常な電子部品によって複合電子部品としての機能を維持することができる。その結果、複数の電子部品を含む複合電子部品の信頼性が向上する。

【0007】

本発明において、複数の前記電子部品は、第1の方向と、前記第1の方向に直交する第2の方向とに向かってそれぞれ配置されることが好ましい。このようにすれば、複合電子部品内に配置される電子部品の密度を大きくすることができるので、例えば、電子部品にコンデンサを用いた場合には、複合電子部品の静電容量を大きくすることができる。また、この場合、同じ静電容量であれば、複合電子部品を小型化することができる。

【0008】

本発明において、前記導体層の表面に設けられて、前記導体層とは反対側から複数の前記第2端子電極の少なくとも一部を露出させる絶縁部材を含むことが好ましい。このようにすれば、支持体による複数の電子部品の支持に加え、絶縁部材も複数の電子部品を支持することができるので、複数の電子部品がより強固に支持される。

【0009】

本発明において、前記絶縁部材は、前記第2端子電極が露出する側から前記導体層まで前記絶縁部材を貫通する貫通孔を含み、前記電子部品は前記貫通孔の内部に配置されることが好ましい。このようにすれば、貫通孔が電子部品の位置決めをするので、電子部品の位置精度が向上する。

【0010】

本発明において、隣接する前記電子部品は、それぞれの前記第2端子電極同士が異極性となるように前記回路基板の端子に接続されることが好ましい。このようにすれば、隣接する電子部品を流れる電流の向きは、それぞれ反対方向になる。その結果、この複合電子部品は、ESL(Equivalent Series Inductance:等価直列インダクタンス)を低減することができる。

【0011】

本発明において、複数の前記電子部品は、コンデンサ素子であることが好ましい。このようにすることで、複合電子部品をコンデンサとして機能させることができる。

【0012】

本発明において、複数の前記電子部品は、コンデンサ素子及び抵抗素子であり、前記コンデンサ素子と前記抵抗素子とは隣接して配置されることが好ましい。このようにすることで、隣接するコンデンサ素子と抵抗素子とを直列に接続することができるので、複合電子部品のESR(Equivalent Series Resistance:等価直列抵抗)を高くすることができる。

【0013】

隣接する前記コンデンサ素子と前記抵抗素子とは、それぞれの前記第2端子電極が異極性となるように前記回路基板の端子に接続されることが好ましい。このようにすることで、複合電子部品は、ESLを低減することができる。

【0014】

本発明において、前記電子部品は、複数の素子部を有するアレイ型電子部品であることが好ましい。このようにすることで、複合電子部品が有する電子部品の数を低減できるので、電子部品を支持体に実装する際の作業効率が向上する。

【0015】

本発明において、前記支持体は、複数の前記電子部品が配置される側とは反対側に、放熱部材を有することが好ましい。このようにすることで、放熱部材は複合電子部品の昇温を効果的に抑制することができる。

【0016】

本発明において、前記素体は、直方体形状であり、前記第1端子電極と前記第2端子電極とは、前記素体の対向する2個の短側面同士を接続する4個の長側面のうち、内部電極が露出し、かつ対向する前記長側面のそれぞれに設けられることが好ましい。このようにすることで、それぞれの電子部品のESLが低下するので、複合電子部品全体のESLも低下する。

【0017】

本発明において、前記支持体は導電体であることが好ましい。一般に、導電体は、熱の良導体でもあるので、支持体を導電体とすることにより、複合電子部品が有する複数の電子部品の熱をより効率よく伝えることができる。

【0018】

本発明において、前記支持体は絶縁体であることが好ましい。このようにすると、支持体は第1端子電極を電気的に絶縁することができるので、支持体を介して、電子部品と回路基板が格納される筐体又は回路基板に実装されている他の電子部品等とが短絡するおそれを低減できる。

【0019】

本発明において、前記導体層は、隣接する複数の前記電子部品の周囲を囲み、かつ前記支持体まで達する溝を有することが好ましい。このようにすることで、複合電子部品は、溝で区画された導体層のそれぞれの領域によって、複数の電子部品の第1端子電極同士を電気的に接続された、複数の電子部品群を有する。そして、複合電子部品は、複数の前記電子部品群に所定の機能を発揮させることができるとともに、それぞれの電子部品群の信頼性を向上させることができる。

【0020】

本発明において、前記溝で囲まれる複数の前記電子部品は、コンデンサ素子及びインダクタ素子又は抵抗素子であり、フィルタとしての機能を有することが好ましい。このようにすることで、複数のフィルタを有する複合電子部品を得ることができる。

【0021】

本発明において、前記溝で囲まれる複数の前記電子部品は、バリスタ素子及び抵抗であり、バリスタとしての機能を有することが好ましい。このようにすることで、複数のバリスタを有する複合電子部品を得ることができる。

【0022】

本発明は、素体の対向するそれぞれの端面に、第1端子電極と第2端子電極とを有する電子部品と、複数の前記電子部品が有する前記第1端子電極を電気的に接続する導体層と、前記導体層が設けられる支持体と、を含み、複数の前記電子部品が有するそれぞれの前記第2端子電極同士が異極性となるように、回路基板の端子に接続されることを特徴とする複合電子部品の実装構造である。

【0023】

この複合電子部品の実装構造で回路基板に実装される電子部品は、導体層によって複数の電子部品の第1端子電極同士が電気的に接続されている。このため、電子部品に不具合が発生したとしても、他の電子部品が正常であれば、正常な電子部品によって複合電子部品としての機能を維持することができる。その結果、複数の電子部品を含む複合電子部品の信頼性が向上する。また、複数の電子部品が有するそれぞれの第2端子電極同士が異極性となるように、回路基板の端子に接続されることにより、隣接する電子部品を流れる電流の向きは、それぞれ反対方向になる。その結果、この複合電子部品の実装構造は、ESLを低減することができる。

【0024】

本発明において、複数の前記電子部品は、コンデンサ素子及び抵抗素子であり、前記コンデンサ素子と前記抵抗素子とは隣接して配置され、かつ隣接する前記コンデンサ素子と前記抵抗素子とは、それぞれの前記第2端子電極が異極性となるように前記回路基板の端子に接続されることが好ましい。このようにすることで、隣接するコンデンサ素子と抵抗素子とを直列に接続することができるので、複合電子部品のESR(Equivalent Series Resistance:等価直列抵抗)を高くすることができる。

【発明の効果】

【0025】

本発明は、複数の電子部品を含む複合電子部品の信頼性を向上させることができる。

【図面の簡単な説明】

【0026】

【図1】図1は、実施形態1に係る複合電子部品の平面図である。

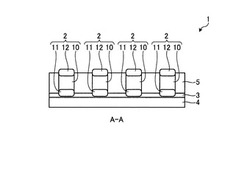

【図2】図2は、図1のA−A矢視図である。

【図3】図3は、実施形態1に係る複合電子部品が備える電子部品の斜視図である。

【図4】図4は、実施形態1に係る複合電子部品の等価回路を示す図である。

【図5】図5は、実施形態1に係る複合電子部品の実装構造を示す図である。

【図6】図6は、実施形態1の第1変形例に係る実装構造において、複合電子部品の実装端子電極の極性を説明するための図である。

【図7】図7は、実施形態1の第1変形例に係る実装構造において、複合電子部品の実装端子電極の極性を説明するための図である。

【図8】図8は、実施形態1の第1変形例に係る実装構造を示す図である。

【図9】図9は、実施形態1の第1変形例に係る実装構造の等価回路を示す図である。

【図10】図10は、本実施形態の第2変形例に係る複合電子部品を示す平面図である。

【図11】図11は、図10のB−B矢視図である。

【図12】図12は、本実施形態の第2変形例に係る複合電子部品が有する電子部品の斜視図である。

【図13】図13は、実施形態1の第3変形例に係る複合電子部品を示す平面図である。

【図14】図14は、図13のC−C矢視図である。

【図15】図15は、実施形態1の第3変形例に係る複合電子部品が有する電子部品の一例を示す断面図である。

【図16】図16は、本実施形態の第3変形例に係る複合電子部品に、他の電子部品を適用した例を示す一部断面図である。

【図17】図17は、図16に示す電子部品を示す断面図である。

【図18】図18は、実施形態1の第4変形例に係る複合電子部品を示す平面図である。

【図19】図19は、図18のD−D矢視図である。

【図20】図20は、実施形態1の第4変形例に係る複合電子部品の等価回路を示す図である。

【図21】図21は、実施形態1の第4変形例に係る実装構造を示す図である。

【図22】図22は、実施形態2に係る複合電子部品の平面図である。

【図23】図23は、図22のE−E矢視図である。

【図24】図24は、実施形態3に係る複合電子部品及びその実装構造を示す図である。

【図25】図25は、実施形態4に係る複合電子部品の平面図である。

【図26】図26は、図24のF−F矢視図である。

【図27】図27は、実施形態4に係る複合電子部品の等価回路を示す図である。

【図28】図28は、実施形態4の変形例に係る複合電子部品の平面図である。

【図29】図29は、実施形態4の変形例に係る複合電子部品の等価回路を示す図である。

【図30】図30は、実施形態4の第2変形例に係る複合電子部品の平面図である。

【図31】図31は、実施形態4の第2変形例に係る複合電子部品が有する導体層の形態を示す平面図である。

【図32】図32は、図30のG−G矢視図である。

【図33】図33は、実施形態5の第2変形例に係る複合電子部品の等価回路を示す図である。

【図34】図34は、他のフィルタの等価回路を示す図である。

【図35】図35は、実施形態4の第3変形例に係る複合電子部品を示す平面図である。

【図36】図36は、実施形態4の第3変形例に係る複合電子部品が有する電子部品を示す図である。

【図37】図37は、実施形態4の第3変形例に係る複合電子部品が有する電子部品を示す図である。

【図38】図38は、実施形態4の複合電子部品が有する電子部品群の変形例に係る等価回路を示す図である。

【発明を実施するための形態】

【0027】

本発明を実施するための形態(以下、実施形態という)につき、図面を参照しつつ詳細に説明する。以下の実施形態に記載した内容により本発明が限定されるものではない。また、以下に記載した構成には、当業者が容易に想定できるもの、実質的に同一のものが含まれる。さらに、以下に開示した構成は適宜組み合わせることが可能である。さらに、下記実施形態で開示した構成は適宜組み合わせることが可能である。また、本発明の要旨を逸脱しない範囲で構成の種々の省略、置換又は変更を行うことができる。

【0028】

(実施形態1)

図1は、実施形態1に係る複合電子部品の平面図である。図2は、図1のA−A矢視図である。図3は、実施形態1に係る複合電子部品が備える電子部品の斜視図である。図4は、実施形態1に係る複合電子部品の等価回路を示す図である。図5は、実施形態1に係る複合電子部品の実装構造を示す図である。複合電子部品1は、複数の電子部品2と、導体層3と、支持体4と、を含む。本実施形態において、複合電子部品1は、さらに絶縁部材5を含むが、絶縁部材5は必ずしも必要ではない。

【0029】

複合電子部品1は、16個の電子部品2を含むが、電子部品2の数は限定されず、奇数であってもよい。図2、図3に示すように、電子部品2は、素体10と、第1端子電極11と、第2端子電極12とを含む。素体10は、内部に電極又は導電体と誘電体とを有するセラミックの素体である。素体10は、例えば、内部電極層と誘電体層とからなるセラミックの素体である。

【0030】

素体10は、略直方体形状を呈しており、その外表面として、対向する第1及び第2の主面10M、10Mと、対向する第1及び第2の端面10E、10Eと、対向する第1及び第2の側面10U、10Uとを有する。第1及び第2の端面10E、10Eは、略長方形状である第1及び第2の主面10M、10M間を連結するように、第1及び第2の主面10M、10Mの短辺方向に延在する。第1及び第2の側面10U、10Uは、略長方形状である第1及び第2の主面10M、10M間を連結するように第1及び第2の主面10S、10Sの長辺方向に延在する。

【0031】

本実施形態において、第1及び第2の端面10E、10Eは、平面視が略正方形形状である。第1及び第2の端面10E、10Eは、2個の短側面10Tに相当する。第1及び第2の主面10M、10Mと第1及び第2の側面10U、10Uとは平面視が略長方形形状であり、これらは4個の長側面10Sに相当する。なお、素体10の形状はこれに限定されるものではない。素体10が内部電極層と誘電体層からなる場合には、第1及び第2の端面10E、10E及び第1及び第2の側面10U、10Uと略平行で、かつ主面10Mと直交するように、内部電極層と誘電体層とが積層される。

【0032】

電子部品2は、素体10の対向する表面(本実施形態では、短側面10T、10T)のそれぞれに、第1端子電極11と第2端子電極12とを有する。第1端子電極11及び第2端子電極12は、短側面10T、10Tの全体と4個の長側面10Sの一部とを覆う。一般に、このような電子部品2は、チップ型電子部品と呼ばれる種類の電子部品であり、回路基板の表面に実装できる表面実装型の電子部品である。本実施形態では、複数の電子部品2が有する第2端子電極12が、図5に示す回路基板20の第1基板端子23、第2基板端子24と電気的に接続されるための実装端子電極となり、複数の電子部品2が有する第1端子電極11が導体層3と電気的に接続される。

【0033】

本実施形態において、電子部品2は、すべてコンデンサ素子(例えば、チップ型コンデンサ)である。このコンデンサ素子は、上述した素体10の内部に設けられた2個以上の電極(内部電極)と誘電体とが積層されるとともに、前記誘電体を挟んで一方の前記内部電極が第1端子電極11と電気的に接続され、他方の前記内部電極が第2端子電極12と電気的に接続される、積層型の素子である。複合電子部品1は、複数の電子部品として複数のコンデンサ素子を備えることになるので、コンデンサとして機能する。複合電子部品1が有する電子部品2の種類はコンデンサ素子に限定されるものではなく、抵抗素子、インダクタ素子又はバリスタ素子等であってもよい。また、複合電子部品1が有する電子部品2は、すべて同じ種類であってもよいし、異なる種類であってもよい。

【0034】

導体層3は、例えば、導電性接着材又は導電性樹脂であり、本実施形態では前者である。図2に示すように、導体層3は、複数の電子部品2が有する第1端子電極11を電気的に接続する。支持体4は、本実施形態において、平面視が長方形(正方形を含む)形状の板状の部材である。本実施形態において、支持体4は、導電体であってもよいし絶縁体であってもよい。一般に、導電体は熱の良導体であるので、支持体4に導電体を用いると、複合電子部品1が有する複数の電子部品2の熱をより効率よく大気中へ伝えることができる。

【0035】

支持体4に絶縁体を用いると、第1端子電極11と支持体4とを電気的に絶縁することができるので、支持体4を介して、電子部品2と回路基板20が格納される筐体又は回路基板20に実装されている他の電子部品等とが短絡するおそれを低減できる。また、複合電子部品1の回路基板20と対向する部分を除き、複合電子部品1の表面を導電体で被覆して電磁シールド層を形成する場合がある。支持体4に絶縁体を用いると、支持体4及び前記電磁シールド層を介して、電子部品2と回路基板20が格納される筐体又は回路基板20に実装されている他の電子部品等とが短絡するおそれを低減できる。

【0036】

支持体4は、導体層3が設けられる。より具体的には、支持体4が有する面のうち、最も面積の大きい2つの面(導体層配置面)の一方に、導体層3が設けられる。このような構造により、導体層3によって第1端子電極11が電気的に接続された複数の電子部品2は、支持体4に支持される。

【0037】

本実施形態において、絶縁部材5は、絶縁性を有する樹脂であるが、これに限定されるものではない。絶縁部材5は、導体層3と接しており、導体層3を介して支持体4に固定されて支持される。絶縁部材5は、複合電子部品1が有するそれぞれの電子部品2の周囲に配置される。このような構造により、絶縁部材5は、隣接する電子部品2の間に配置される。複数の電子部品2の第2端子電極12は、絶縁部材5の表面から突出する。複数の第2端子電極12は、素体10の短側面10Tの全体を覆う部分がそれぞれ略同一平面に配置されている。このようにすると、図5に示す回路基板20に複合電子部品1を実装した際に、回路基板20の端子としての第1基板端子23及び第2基板端子24と複数の第2端子電極12との距離を略一定にすることができる。そして、回路基板20に複合電子部品1を実装した際は、すべての第2端子電極12と回路基板20の端子との接続条件を揃えることができるので、接続のばらつきを抑制することができる。その結果、複合電子部品1を回路基板20へ確実に実装するとともに、信頼性の低下を抑制することができる。

【0038】

本実施形態において、絶縁部材5は、電子部品2と接触している。このように、絶縁部材5は、電子部品2同士を絶縁するとともに、複数の電子部品2を支持する。また、絶縁部材5は、導体層3を介して支持体4に固定されている。このため、複数の電子部品2は、導体層3のみならず絶縁部材5によっても支持体4に取り付けられることになるので、より強固に支持体4に支持される。その結果、複合電子部品1は、耐振性能が高くなる。絶縁部材5は、例えば、導体層3によって支持体4に複数の電子部品2を取り付けた後、絶縁性を有する樹脂を電子部品2の周囲に充填して硬化させることによって、支持体4に設けられる。

【0039】

このような構造により、複合電子部品1は、支持体4とは反対側に配置された絶縁部材5の表面から、複数の第2端子電極12が露出する。それぞれの第2端子電極12は、互いに電気的に絶縁されている。複合電子部品1を回路基板に実装する際に、第2端子電極12の露出した部分が、回路基板20の端子と接続される実装端子電極となる。複数の第2端子電極12は、素体10の短側面10Tを覆う部分が、回路基板20の端子としての第1基板端子23、第2基板端子24と電気的に接続される。複合電子部品1の導体層3は、回路基板20の端子と直接は電気的に接続されず、電子部品2の第1端子電極11及び第2端子電極12を介して、間接的に回路基板20の端子と接続される。本実施形態において、複合電子部品1は、自身が有する電子部品2の数の同じ数の実装端子電極、すなわち、第2端子電極12を有する。

【0040】

複合電子部品1は、複数の電子部品2が、第1の方向(図1のX方向)と、第1の方向に直交する第2の方向(図2のY方向)とに向かってそれぞれ配置される。このように、複数の電子部品2は、マトリックス状に配置される。本実施形態において、隣接する電子部品2同士は等間隔で配置されるが、隣接する電子部品2同士の間隔は不等間隔であってもよい。第2端子電極12は平面視が略正方形形状なので、複数の電子部品2をマトリックス状に配置することにより、同じ支持体4の表面の面積であれば、電子部品2が配置される密度を最も高くすることができる。このため、複数の電子部品2をマトリックス状に配置することにより、複合電子部品1の静電容量を大きくすることができる。また、複数の電子部品2をマトリックス状に配置することにより、電子部品2が配置される密度を高くすることができるので、複合電子部品1を小型化することもできる。

【0041】

図5に示す複合電子部品の実装構造(以下、必要に応じて実装構造という)100において、複合電子部品1は、第2端子電極12が、回路基板20の端子としての第1基板端子23及び第2基板端子24と、はんだ25で電気的に接続される。回路基板20は、第1配線21と第2配線22とを有しており、第1配線21に第1基板端子23が電気的に接続され、第2配線21に第2基板端子24が電気的に接続される。本実施形態において、複合電子部品1は、コンデンサとして機能する。この場合、複合電子部品1は、瞬間停電等による電圧変動を抑制するため、CPU(Central Processing Unit)の近傍に実装される電流供給用のデカップリングコンデンサ等に用いられる。

【0042】

導体層3で第1端子電極11が電気的に接続された複数の電子部品2のうち、2個の電子部品2の第2端子電極12は、それぞれ第1基板端子23と第2基板端子24とに接続される。このように、2個の電子部品2が1個の電子部品対2Pとして、第1基板端子23と第2基板端子24とを介して第1配線21と第2配線22との間に接続される。複合電子部品1は、複数組の電子部品対2Pが、第1配線21と第2配線22との間に接続されて、例えば、上述したデカップリングコンデンサとして機能する。

【0043】

一組の電子部品対2Pは、2個の電子部品2が直列に接続されている。また、実装構造100は、複数の電子部品対2Pが第1配線21と第2配線22とに対して並列に接続されている。このため、複合電子部品1がn(偶数)個の電子部品2を有し、かつ電子部品2の静電容量がCiである場合、実装構造100において、コンデンサとして機能する複合電子部品1の静電容量Caは、(n/2)×(Ci/2)となる。本実施形態では、複合電子部品1は16個の電子部品2を有しているので、複合電子部品1の静電容量Caは、4×Ciになる。

【0044】

複合電子部品1は、実装構造100のように、2個の電子部品2を直列に接続して得られた複数の電子部品対2Pを並列に接続して使用することができる。このため、複合電子部品1は、電子部品2に不具合が発生したとしても、不具合が発生した電子部品2を有する電子部品対2P以外の電子部品対2Pの電子部品2が正常であれば、静電容量は低下するが、複合電子部品1の機能、すなわち、コンデンサとしての機能を維持することができる。例えば、図5に示す例では、第1配線21に接続されている2個の電子部品2のうち1個に不具合が発生しても、残りの電子部品2と、第2配線21に接続されている2個の電子部品2とは導体層3で電気的に接続されている。したがって、複合電子部品1は、静電容量が、不具合が発生する前のCiから2×Ci/3に低下するものの、コンデンサとしての機能は維持できる。

【0045】

また、複合電子部品1は、複数の電子部品2の第1端子電極11が導体層3により電気的に接続されている。このため、複合電子部品1は、第1配線21に接続される複数の電子部品2と、第2配線22に接続される複数の電子部品2とで、それぞれ少なくとも1つの電子部品2が正常であれば、静電容量は低下するが、コンデンサとしての機能を維持することができる。例えば、図5に示す例では、第1配線21に接続されている2個の電子部品2のうち1個及び第2配線22に接続されている2個の電子部品2のうち1個に不具合が発生しても、第1配線21及び第2配線21にそれぞれ接続されている残りの1個の電子部品2同士は導体層3で電気的に接続されている。したがって、複合電子部品1は、静電容量が、不具合が発生する前のCiからCi/2に低下するものの、コンデンサとしての機能は維持できる。

【0046】

さらに、奇数、例えば、3個の電子部品2の第1端子電極11を導体3で電気的に接続し、1個の電子部品2の第2端子電極12を第1配線21に接続するとともに、残りの2個の電子部品2の第2端子電極12を第2配線22に接続する。このようにすると、第1配線21と第2配線22との間に、並列に接続された2個の電子部品2と、1個の電子部品2とが直列に接続される。この場合、並列に接続された2個の電子部品2のうち1つに不具合が発生しても、第1配線21と第2配線22との間には、2個の電子部品2が直列に接続されることになる。したがって、複合電子部品1は、静電容量が、不具合が発生する前の2×Ci/3からCi/2に低下するものの、コンデンサとしての機能は維持できる。

【0047】

このように、複合電子部品1は、信頼性が向上するので、これが搭載された電子機器の信頼性を向上させることができる。また、複合電子部品1は、複数の電子部品2を1つにまとめて一体化してあるので、電子部品2がコンデンサ素子である場合には、大きい静電容量をコンパクトな寸法で実現することができる。さらに、複合電子部品1が有する複数の第2端子電極12の中からいくつかを選択して、回路基板20の第1基板端子23及び第2基板端子24に接続すれば、複合電子部品1の静電容量を所望の大きさとなるように調整することもできる。

【0048】

複合電子部品1の電子部品2が誘電体を有する場合、電子部品2を回路基板20に実装すると、誘電体に発生する電歪現象に起因した音鳴きが発生したり、素体10にクラックが発生したりすることがある。複合電子部品1が有する複数の電子部品2は、第1端子電極11が支持体4に取り付けられているが、第2端子電極12は支持体4に対して解放されている。このため、回路基板20に実装された複合電子部品1は、電子部品2から回路基板20へ伝達される力が解放されるとともに、電子部品から回路基板20に伝達される振動が緩和される。その結果、この複合電子部品1は、誘電体を有する電子部品2の電歪現象に起因して発生する音鳴きを抑制できるとともに、素体10へのクラックの発生を抑制できる。また、複合電子部品1を回路基板20に実装した場合、電子部品2は、第2端子電極12のみが回路基板20に拘束される。このため、複合電子部品1が有する電子部品2は、電子部品2の第1端子電極11及び第2端子電極12が回路基板20に接続されて拘束される場合と比較して、回路基板20の変形の影響を受けにくい。その結果、複合電子部品1は、複合電子部品1又は電子部品2の熱膨張率と回路基板20の熱膨張率との違いに起因して電子部品2が回路基板20から受ける力を低減できるので、電子部品2へのクラックの発生を抑制できる。

【0049】

(第1変形例)

図6、図7は、実施形態1の第1変形例に係る実装構造において、複合電子部品の実装端子電極の極性を説明するための図である。図8は、実施形態1の第1変形例に係る実装構造を示す図である。図9は、実施形態1の第1変形例に係る実装構造の等価回路を示す図である。図6、図7及び図9中の+、−は、複合電子部品1が有する電子部品2の実装端子電極である第2端子電極12の極性を示す。+が正極であり、−が負極である。本変形例に係る実装構造100’において、複合電子部品1の隣接する電子部品2は、それぞれの第2端子電極12同士が異極性となるように、回路基板20の端子としての第1基板端子23及び第2基板端子24に接続される。本変形例において、電子部品2はコンデンサ素子である。

【0050】

このため、図6、図7に示すように、格子状に配列された複数の第2端子電極12は、正極と負極とがそれぞれ千鳥状になる。すなわち、マトリックス状に配置された複数の電子部品2の第2端子電極12は、行方向と列方向とに向かって、正極と負極とが交互に配置される。図8に示す実装構造100’において、回路基板の第1配線21は回路基板20の信号線又は電力供給線であり、第2配線22は回路基板20のGND線である。符号2sで示す電子部品2は、第2端子電極12がはんだ25及び第1基板端子23を介して正極としての第1配線21に接続される。また、符号2gで示す電子部品2は、第2端子電極12がはんだ25及び第2基板端子24を介して負極としての第2配線22に接続される。

【0051】

図8に示すように、隣接する電子部品2s、2gの第1端子電極11は、導体層3によって接続されている。電子部品2sの第2端子電極12は、回路基板20の第1配線21に接続され、電子部品2gの第2端子電極12は、回路基板20の第2配線22に接続される。第1配線21から第2配線22へ向かって電流が流れる場合、電子部品2sを流れる電流をIa、電子部品2gを流れる電流をIbとする。電流Iaは、電子部品2sの第2端子電極12から第1端子電極11へ向かって流れる。また、電流Ibは、電子部品2gの第1端子電極11から第2端子電極12へ向かって流れる。このように、実装構造100’において、複合電子部品1が有する、隣接する電子部品2s、2gを流れる電流Ia、Ibの向きは、それぞれ反対方向になる。その結果、複合電子部品1及びその実装構造100’は、ESLを低減することができる。

【0052】

隣接する電子部品2s、2g同士の距離を小さくすると、ESLを低減させる効果が高くなる。隣接する電子部品2s、2g同士の距離を小さくするためには、電子部品2s、2gの寸法を小さくすることが好ましい。また、ESLを低下させるためには、本変形のように、複数の第2端子電極12の正極と負極とがそれぞれ千鳥状になるようにすることが好ましい。しかし、マトリックス状に配置された複数の電子部品2の第2端子電極12は、行又は列毎に異極性となるようにしてもよい。このようにしても、ある電子部品2と、この電子部品に対して行方向又は列方向に隣接する電子部品2とは、互いに異極性となるので、ESLを低減することができる。すなわち、本変形例の実装構造100’において、複合電子部品1は、ある電子部品2と、この電子部品2に隣接する少なくとも1つの電子部品2とが互いに異極性となるように、回路基板20へ実装されていればよい。このようにすれば、複合電子部品1のESLを低減させることができる。

【0053】

(第2変形例)

図10は、本実施形態の第2変形例に係る複合電子部品を示す平面図である。図11は、図10のB−B矢視図である。図12は、本実施形態の第2変形例に係る複合電子部品が有する電子部品の斜視図である。複合電子部品1aは、電子部品2aを複数(本変形例では4個)有している。複数の電子部品2aの第1端子電極11aは、導体層3によって電気的に接続されている。第2端子電極12aは、少なくとも一部が絶縁部材5の表面から露出して、実装端子電極となる。

【0054】

本変形例において、複合電子部品1aが有する電子部品2aは、直方体形状である素体10aの対向する2個の短側面10T、10T(第1及び第2の端面10E、10E)同士を接続する4個の長側面10Sのうち、内部電極が露出し、かつ対向する長側面10Sのそれぞれに、第1端子電極11aと第2端子電極12aとが設けられる。この長側面10S、10Sは、第1及び第2の主面10M、10Mではなく第1及び第2の側面10U、10Uに相当する。第1端子電極11aと第2端子電極12aとは、これらが設けられる長側面10Sの全体を覆っている。第1端子電極11aと第2端子電極12aとは、これらが全体を覆っていない2つの長側面10Sの一部及び短側面10Tの一部に延出している。

【0055】

本変形例において、電子部品2aは、コンデンサ素子である。このコンデンサ素子は、少なくとも2個の内部電極と誘電体とが積層されるとともに、前記誘電体を挟んで一方の前記内部電極が第1端子電極11aと電気的に接続され、他方の前記内部電極が第2端子電極12aと電気的に接続される積層型の素子である。電子部品2aが有する素体10aの長側面10Sは、平面視が略長方形形状である。短側面10Tは、素体10aは平面視が略長方形形状又は正方形形状であり、略長方形形状である場合、長辺は長側面10Sの長辺よりも短い。本実施形態において、第1端子電極11aと第2端子電極12aとがそれぞれ全体を覆う長側面10Sは、第1端子電極11aと第2端子電極12aとが一部に延出する長側面10Sよりも短辺の長さが短い。

【0056】

このような構造の電子部品2aは、素体10aの内部に設けられた内部電極の幅が大きく、長さが小さくなるので、電流の経路を短くすることができる。その結果、電子部品2aは、ESLを低減することができる。この例において、内部電極の幅は、第1端子電極11aと第2端子電極12aとがそれぞれ全体を覆う長側面10Sの長手方向における寸法であり、第1側面及び第2側面に引き出される内部電極の幅である。また、内部電極の長さは、第1端子電極11aから第2端子電極12aに向かう方向の寸法である。

【0057】

このような電子部品2aを複数有する複合電子部品1aは、信頼性の確保及び音鳴きの低減等といった効果に加え、ESLをより効果的に低減できるという効果が得られる。複合電子部品1aを回路基板へ実装する際には、隣接する第2端子電極12a同士がそれぞれ異極性となるようにすることで、ESLを効果的に低減できる点は上述した通りである。

【0058】

(第3変形例)

図13は、実施形態1の第3変形例に係る複合電子部品を示す平面図である。図14は、図13のC−C矢視図である。図15は、実施形態1の第3変形例に係る複合電子部品が有する電子部品の一例を示す断面図である。本変形例は、複合電子部品1bが有する電子部品2bとして、複数の素子部を有するアレイ型電子部品を用いる。図13に示すように、複合電子部品1bは、複数(本変形例では8個)の電子部品2bを有する。図14に示すように、複数の電子部品2bの第1端子電極11は導体層3によって電気的に接続される。第2端子電極12は、絶縁部材5から少なくとも一部が露出して実装端子電極となる。

【0059】

電子部品2bは、複数(本変形例では2個)の素子部EPを有する。本変形例において、素子部EPはコンデンサである。すなわち、電子部品2bは、コンデンサアレイである。図15に示すように、電子部品2bが有するそれぞれの素子部EPは、複数の内部電極13、14と誘電体15とが積層される素体10bを有するとともに、誘電体15を挟んで一方の内部電極13が第1端子電極11と電気的に接続され、他方の内部電極14が第2端子電極12と電気的に接続される。電子部品2bは、それぞれの素子部EPに対応して、2個の第1端子電極11及び2個の第2端子電極12を有している。2個の第1端子電極11は、電子部品2bの1つの長側面に配置され、2個の第2端子電極は、第1端子電極11が配置されている長側面と対向する長側面に配置される。

【0060】

図13に示すように、複合電子部品1bは、電子部品2bの素子部EPが配列されている方向に向かって2個の電子部品2bが配置され、素子部EPが配列されている方向と直交する方向に向かって4個の電子部品2bが配列されている。このような構造により、複合電子部品1bは、第1の方向(図13のX方向)及び第2の方向(図13のY方向)に向かって、それぞれ4個ずつの素子部EPが配列される。すなわち、複数の素子部EPがマトリックス状に配置される。

【0061】

図14に示すように、複合電子部品1bは、1個の電子部品2bが含む隣接する2個の素子部EPが、互いに異極性となるように回路基板へ実装することができる。この例では、+の第2端子電極12を正極として、回路基板の信号線又は電力供給線に接続し、−の第2端子電極12を負極として、回路基板のGND線に接続する。+の第2端子電極12を有する素子部EPは、第2端子電極12から第1端子電極11へ電流Iaが流れ、−の第2端子電極12を有する素子部EPは、第1端子電極11から第2端子電極12へ電流Ibが流れる。このように複合電子部品1bが回路基板へ実装されることにより、電子部品2bが有する隣接する素子部EP、EPを流れる電流Ia、Ibの向きは、それぞれ反対方向になる。その結果、複合電子部品1bは、ESLを低減することができる。

【0062】

図16は、本実施形態の第3変形例に係る複合電子部品に、他の電子部品を適用した例を示す一部断面図である。図17は、図16に示す電子部品を示す断面図である。複合電子部品1b’は、4個の素子部EPを有する電子部品2b’を複数有する。図16は、複合電子部品1b’が有する1個の電子部品2b’を示すが、この例において、複合電子部品1b’は4個の電子部品2b’を有する。

【0063】

図17に示すように、電子部品2b’は、素子部EPを4個有する。この例において、素子部EPはコンデンサであるので、電子部品2b’は、コンデンサアレイである。電子部品2b’が有するそれぞれの素子部EPの構造は、電子部品2bが有する素子部EPと同様である。図16に示すように、複合電子部品1b’も、上述した複合電子部品1bと同様に、1個の電子部品2b’が含む隣接する2個の素子部EPが、互いに異極性となるように回路基板へ実装することができる。その結果、複合電子部品1bと同様に、複合電子部品1b’も、隣接する素子部EP、EPを流れる電流Ia、Ibの向きをそれぞれ反対方向にして、ESLを低減することができる。

【0064】

複合電子部品1b、1b’は、電子部品2b、2b’としてアレイ型電子部品を有する。このため、上述した、1つの素子部のみを有する電子部品2、2aを用いる複合電子部品1、1aと比較して、電子部品2b、2b’の数を低減することができる。その結果、複合電子部品1b、1b’は、マウンタ等の実装装置が電子部品2bを支持体4に実装する回数を低減できるので、電子部品2b、2b’が支持体4に実装される時間を短縮することができる。また、複合電子部品1b、1b’は、アレイ型電子部品を用いるため、1つの素子部のみを有する電子部品2、2aよりも電子部品2b、2b’の取扱いが容易になる。その結果、複合電子部品1b、1b’は、マウンタ等の実装装置が電子部品2bを支持体4に実装する際の作業効率を向上させることができる。このように、複合電子部品1b、1b’は、電子部品2b、2b’が支持体4に実装される際の作業効率を向上させて、生産性を向上させることができる。この効果は、アレイ型電子部品が有する素子部EPの数が増加するほど顕著になる。このため、4個の素子部EPを有する電子部品2b’が用いられる複合電子部品1b’の方が、2個の素子部EPを有する電子部品2bが用いられる複合電子部品1bよりも、作業効率及び生産性向上の効果をより実現できる。

【0065】

(第4変形例)

図18は、実施形態1の第4変形例に係る複合電子部品を示す平面図である。図19は、図18のD−D矢視図である。図20は、実施形態1の第4変形例に係る複合電子部品の等価回路を示す図である。図21は、実施形態1の第4変形例に係る実装構造を示す図である。本変形例の複合電子部品1cは、異なる機能を持つ2種類の電子部品2C、2Rを有する。本変形例において、電子部品2Cはコンデンサ素子であり、電子部品2Rは抵抗素子(例えば、チップ型抵抗)であるが、これに限定されるものではない。

【0066】

電子部品2Cと電子部品2Rとは、互いに隣接して支持体4の表面に配置される。このため、電子部品2C及び電子部品2Rは、それぞれ千鳥状に配置されることになる。すなわち、複合電子部品1cは、第1の方向(図18のX方向)及び第2の方向(図18のY方向)に向かって電子部品2Cと電子部品2Rとが交互に配列される。このように、複合電子部品1cは、電子部品2C、2Rが交互に、かつマトリックス状に配置されている。

【0067】

コンデンサ素子である電子部品2Cは、図19に示すように、複数の内部電極13、14と誘電体15とが積層される素体10Cを有するとともに、誘電体15を挟んで一方の内部電極13が第1端子電極11と電気的に接続され、他方の内部電極14が第2端子電極12と電気的に接続される。抵抗素子である電子部品2Rは、抵抗体16と誘電体17とが積層される素体10Rを有するとともに、抵抗体16は、第1端子電極11及び第2端子電極12と電気的に接続される。抵抗体16は、例えば、フェライトビーズを用いることができる。

【0068】

図21に示すように、実装構造100cにおいて、複合電子部品1cは、隣接する電子部品2Cと電子部品2Rとを直列に接続して一組の電子部品対2Pcとするとともに、回路基板20の第1配線21と第2配線22との間にそれぞれの電子部品対2Pcを並列に接続する。このように、隣接する電子部品2Cと電子部品2Rとを直列に接続することにより、複合電子部品1cは、ESRを高くすることができる。複合電子部品1cは、ESRが低すぎると共振してノイズが増加する場合もある。このため、本変形例では、コンデンサ素子(電子部品2C)と直列に抵抗素子(電子部品2R)を接続して、複合電子部品1cの共振を抑制する。また、抵抗素子としての電子部品2Rが有する抵抗体16に適用できるフェライトビーズは、高周波になると電気抵抗が上昇する特性を有している。このため、電子部品2Rの抵抗体16にフェライトビーズを用いると、高周波の信号に対して複合電子部品1cのESRを上昇させることができる。

【0069】

また、本変形例では、電子部品対2Pcが有する隣接する電子部品2C、2Rを直列に接続する。そして、抵抗素子としての電子部品2Rの第2端子電極12は、正極として、回路基板20の第1基板端子23を介して第1配線21に接続され、コンデンサ素子としての電子部品2Cの第2端子電極12は、負極として、回路基板20の第2基板端子24を介して第2配線22に接続される。第1配線21は、例えば、回路基板20の信号線又は電力供給線であり、第2配線22は、例えば、回路基板20のGND線である。

【0070】

正極としての第2端子電極12を有する電子部品2Rは、第2端子電極12から第1端子電極11へ電流Iaが流れ、負極としての第2端子電極12を有する電子部品2Cは、第1端子電極11から第2端子電極12へ電流Ibが流れる。実装構造100cにおいて、このような形態で複合電子部品1cが回路基板20へ実装されることにより、電子部品2R、2Cを流れる電流Ia、Ibの向きはそれぞれ反対方向になる。その結果、複合電子部品1cは、ESLを低減することができる。

【0071】

以上、本実施形態及びその変形例は、複数の電子部品の第1端子電極を導体層で電気的に接続するとともに、第2端子電極を、回路基板の端子と接続するための実装端子電極とする。このようにすることで、本実施形態及びその変形例は、複合電子部品が有する電子部品に不具合が発生したとしても、不具合が発生した電子部品が属する電子部品対以外の電子部品対に属する電子部品が正常であれば、コンデンサとしての機能を維持することができる。その結果、本実施形態及びその変形例は、複数の電子部品を含む複合電子部品の信頼性を向上させることができるとともに、複合電子部品が搭載された電子機器の信頼性を向上させることができる。本実施形態及びその変形例の構成は、以下の実施形態においても適宜適用することができる。また、本実施形態及びその変形例の構成を備えるものは、本実施形態及びその変形例と同様の作用、効果を奏する。

【0072】

(実施形態2)

図22は、実施形態2に係る複合電子部品の平面図である。図23は、図22のE−E矢視図である。本実施形態の複合電子部品1dは、電子部品2の第2端子電極12が露出する側から前記4まで絶縁部材5dを貫通する貫通孔6を含み、電子部品2は貫通孔6の内部に配置される。他の構成は、実施形態1の複合電子部品1と同様である。

【0073】

絶縁部材5dは、最も大きい2個を貫通する複数の貫通孔6を有している。貫通孔6の数は、複合電子部品1dが有する電子部品2の数と同数である。この貫通孔6の内部に、複数の電子部品2が配置される。そして、電子部品2は、第1端子電極11が導体層3と電気的に接続され、第2端子電極12の少なくとも一部が貫通孔6の開口部6Hから露出する。本実施形態では、貫通孔6の開口部6Hを超えて、第2端子電極12が貫通孔6の開口部6Hから露出する。

【0074】

複合電子部品1dを製造するにあたって、支持体4に導体層3となる導電性接着材を塗布した後、複数の貫通孔6を有する絶縁部材5dを前記導電性接着材の表面に載置する。その後、貫通孔6の内部に、第1端子電極11から先に電子部品2を挿入して、第1端子電極11と前記導電性接着材とを接触させることにより、電子部品2を支持体4に搭載する。そして、前記導電性接着材を硬化させて、それぞれの第1端子電極11を電気的に接続するとともに、支持体4と絶縁部材5dとを接着する。このようにして、複合電子部品1dが完成する。複合電子部品1dは、電子部品2を支持体4に搭載する際には、貫通孔6が電子部品2のガイドとして機能するので、電子部品2を支持体4に搭載する作業が容易になる。また、貫通孔6は、それぞれの電子部品2の位置決めをするガイドとしても機能するので、複合電子部品1dが有する電子部品2の位置精度を向上させることもできる。さらに、複合電子部品1dは、板状の絶縁部材5dを支持体4に取り付けるので、絶縁樹脂を充填して絶縁部材5とする実施形態1の複合電子部品1と比較して、絶縁部材5dの厚み(最も大きい2個の面と直交する方向の寸法)の寸法精度及び第2端子電極12側の面の平面度を向上させることができる。その結果、第2端子電極12が絶縁部材5dに埋もれてしまうような事態を回避できる。

【0075】

以上、本実施形態は、実施形態1と同様の作用、効果に加え、電子部品を支持体に搭載する作業の効率が向上するとともに、複数の電子部品の位置精度が向上するという効果が得られる。本実施形態及びその変形例の構成は、以下の実施形態においても適宜適用することができる。また、本実施形態及びその変形例の構成を備えるものは、本実施形態及びその変形例と同様の作用、効果を奏する。

【0076】

(実施形態3)

図24は、実施形態3に係る複合電子部品及びその実装構造を示す図である。本実施形態の複合電子部品1eは、支持体4が、複数の電子部品2が配置される側とは反対側に、放熱部材7を有する。他の構成は、実施形態1の複合電子部品1又は実施形態2の複合電子部品1dと同様である。放熱部材7は、複合電子部品1eが有する複数の電子部品2が発生する熱を大気中へ放熱して、複合電子部品1eの昇温を抑制する。実装構造100eは、放熱部材7を有する複合電子部品1eの第2端子電極12を、回路基板20の第1基板端子23及び第2基板端子24にはんだ25で接合することにより、複合電子部品1eを回路基板20へ実装したものである。複合電子部品1eは、放熱性能が高いため、回路基板20に昇温しやすい電子部品が搭載されている場合及び昇温しやすい環境で使用される場合に好ましい。

【0077】

図24に示すように、複合電子部品1eは、実施形態1の複合電子部品1又は実施形態2の複合電子部品1dの支持体4に、放熱部材7を取り付けた構造である。より具体的には、複合電子部品1eは、複合電子部品1又は1dが有する支持体4の最も大きい2つの面4H、4Dのうち、導体層3が設けられる面4Dとは反対の面4H、すなわち、複数の電子部品2が配置される側とは反対側に、放熱部材7が取り付けられている。放熱部材7は、熱伝導性の高い材料が用いられる。本実施形態では、例えば、アルミニウム、アルミニウム合金、銅又は銅合金等の金属材料が放熱部材7に用いられるが、これらに限定されるものではない。放熱部材7は、支持体4とは反対側に、複数のフィン7Fを有する。複数のフィン7Fは、放熱部材7の表面積を大きくして、放熱性能を向上させる。

【0078】

本実施形態において、導体層3を介して複数の電子部品2及び絶縁部材5、5eが取り付けられる支持体4は、導電体であってもよいし、絶縁体であってもよい。一般に、導電体は熱の良導体であるので、支持体4に導電体を用いると、複合電子部品1eが有する複数の電子部品2の熱をより効率よく放熱部材7へ伝えることができる。また、支持体4に絶縁体を用いると、第1端子電極11と放熱部材7とを電気的に絶縁することができるので、放熱部材7を介して、電子部品2と回路基板20が格納される筐体又は回路基板20に実装されている他の電子部品等とが短絡するおそれを低減できる。

【0079】

以上、本実施形態は、実施形態1と同様の作用、効果に加え、複合電子部品の放熱性能が向上するという効果が得られる。本実施形態及びその変形例の構成は、以下の実施形態においても適宜適用することができる。また、本実施形態及びその変形例の構成を備えるものは、本実施形態及びその変形例と同様の作用、効果を奏する。

【0080】

(実施形態4)

図25は、実施形態4に係る複合電子部品の平面図である。図26は、図24のF−F矢視図である。図27は、実施形態4に係る複合電子部品の等価回路を示す図である。本実施形態の複合電子部品1fは、支持体4が絶縁体であり、導体層3fは、隣接する複数の電子部品2の周囲を囲み、かつ支持体4まで達する溝8を有している。他の構成は、実施形態1の複合電子部品1と同様である。本実施形態において、電子部品2はコンデンサであるが、これに限定されるものではない。

【0081】

図25、図26に示すように、複合電子部品1fは、16個の電子部品2が、第1の方向としてのX方向に4個配列され、第1の方向に直交する第2の方向としてのY方向に4個配列されている。このように、複合電子部品1fは、16個の電子部品2が4×4のマトリックス状に配置されている。複合電子部品1fが有する複数の電子部品2を、マトリックスの要素(成分)として見た場合、要素(2、2)、(2、3)、(3、2)、(3、3)に対応する電子部品2の周囲は、溝8で囲まれている。図25、図26に示すように、溝8は、導体層3fに設けられるとともに、支持体4まで達している。より具体的には、溝8は、導体層3fの第2端子電極12側から支持体4の第1端子電極11側における表面まで貫通している。このような構造により、溝8は、導体層3fを2つの領域、すなわち、内側領域3fiと外側領域3foとに区画するとともに、両者を電気的に絶縁する。

【0082】

外側領域3foの導体層3fは、外側領域3foに配置される12個の電子部品2の第1端子電極11を電気的に接続する。内側領域3fiの導体層3fは、内側領域3fiに配置される4個の電子部品2の第1端子電極11を電気的に接続する。このような構造により、複合電子部品1fは、図27の等価回路に示すように、4個の電子部品2の第1端子電極11が電気的に接続された内側電子部品群2Giと、12個の電子部品2の第1端子電極11が電気的に接続された外側電子部品群2Goと、を有する。本実施形態において、電子部品2はコンデンサであるので、複合電子部品1fは、内側電子部品群2Giと外側電子部品群2Goとがそれぞれ1つのコンデンサとして機能する。すなわち、内側電子部品群2Giが有する複数の電子部品2と外側電子部品群2Goが有する複数の電子部品2とは、所定の機能を有する回路となる。

【0083】

このように、複合電子部品1fは、所定の機能(本実施形態ではコンデンサとしての機能)を発揮する電子部品群を複数有する。それぞれの電子部品群は、複数の電子部品2を有し、かつ第1端子電極11同士が電気的に接続されている。このため、それぞれの電子部品群は、信頼性が向上する。したがって、複合電子部品1fは、信頼性の高い複数の電子部品群を有することができる。複合電子部品1fは、実施形態1の複合電子部品1と同様の絶縁部材5を有するものとしたが、複合電子部品1fの絶縁部材5はこれに限定されるものではない。例えば、実施形態2の複合電子部品1dが有する絶縁部材5dのように、内部に電子部品2が配置される貫通孔6を有していてもよい。

【0084】

(変形例)

図28は、実施形態4の変形例に係る複合電子部品の平面図である。図29は、実施形態4の変形例に係る複合電子部品の等価回路を示す図である。本変形例の複合電子部品1f’は、実施形態4の複合電子部品1fと同様であるが、導体層3f’が区画される形態が異なる。複合電子部品1f’は、3本の溝8が導体層3f’を4個の領域、すなわち、第1領域3fa、第2領域3fb、第3領域3fc及び第4領域3fdに区画する。第1領域3faと第2領域3fbと第3領域3fcと第4領域3fdとは、それぞれ電気的に絶縁される。第1領域3fa、第2領域3fb、第3領域3fc及び第4領域3fdは、4個の電子部品2の第1端子電極11を電気的に接続する。このように、3本の溝8は、4×4のマトリックス状に配置された16個の電子部品2を列毎に区画して、4個の電子部品群2Ga、2Gb、2Gc、2Gdとする。

【0085】

複合電子部品1f’は、4個の電子部品群2Ga、2Gb、2Gc、2Gdが、それぞれ1つのコンデンサとして機能する。複合電子部品1f’が有する複数の電子部品群2Ga、2Gb、2Gc、2Gdは、複数の電子部品2を有し、かつ第1端子電極11同士が電気的に接続されている。このため、それぞれの電子部品群2Ga、2Gb、2Gc、2Gdは信頼性が向上するので、複合電子部品1f’は信頼性の高い複数の電子部品群2Ga、2Gb、2Gc、2Gdを有することができる。実施形態4及び本変形例で示したように、溝8が導体層3f、3f’を区画した領域によって複数の電子部品2の第1端子電極11同士が電気的に接続されていれば、区画の形態は限定されるものではない。

【0086】

(第2変形例)

図30は、実施形態4の第2変形例に係る複合電子部品の平面図である。図31は、実施形態4の第2変形例に係る複合電子部品が有する導体層の形態を示す平面図である。図32は、図30のG−G矢視図である。図33は、実施形態5の第2変形例に係る複合電子部品の等価回路を示す図である。本変形例の複合電子部品1gは、実施形態4及びその変形例の複合電子部品1f、1f’と同様であるが、溝で区画された領域に配置された複数の電子部品2は、所定の機能としてフィルタの機能を有する点が異なる。

【0087】

複合電子部品1gは、複数(本実施形態では8個)のフィルタ9を有する。複合電子部品1gが有するフィルタ9の数は限定されるものではない。フィルタ9は、3個の電子部品2を有する。電子部品2Cはコンデンサ素子であり、電子部品2Lはインダクタ素子(例えば、チップ型インダクタ等)である。以下においては、必要に応じて電子部品2Cをコンデンサ素子2C、電子部品2Lをインダクタ素子2Lという。

【0088】

図31に示すように、複合電子部品1gは、溝8が導体層3gを区画した複数の領域3gpを有している。本実施形態では、3本の溝8と、この3本の溝8に直交する1本の溝8によって、導体層3gは8個の領域3gpに区画されている。それぞれの領域3gpは、互いに電気的に絶縁されている。図32に示すように、それぞれの領域3gpは、1つのコンデンサ素子2C及び2つのインダクタ素子2Lの第1端子電極11を電気的に接続する。このような構造により、1個のコンデンサ素子2Cと2個のインダクタ素子2Lとを有するフィルタ9が作られる。1個のコンデンサ素子2C及び2個のインダクタ素子2Lの第2端子電極12は、絶縁部材5の表面から少なくとも一部が露出して、複合電子部品1gの実装端子電極となる。絶縁部材5は、実施形態2の複合電子部品1dが有する絶縁部材5dのように、内部に電子部品2が配置される貫通孔6を有していてもよい。

【0089】

図33に示すように、フィルタ9は、一方のインダクタ素子2Lの第2端子電極12が信号の入力端子INと電気的に接続され、他方のインダクタ素子2Lの第2端子電極12が信号の出力端子OUTと電気的に接続される。コンデンサ素子2Cの第2端子電極12は、グランド端子GNDと電気的に接続される。その結果、フィルタ9はローパスフィルタとして機能する。この場合、2個のインダクタ素子2Lのうち少なくとも一方を抵抗素子に変更してもよい。抵抗素子としては、フェライトビーズを用いてもよい。また、2個のインダクタ素子2Lの代わりにフェライトビーズを用いてもよい。

【0090】

図34は、他のフィルタの等価回路を示す図である。フィルタ9’は、電子部品として、2個のコンデンサ素子2Cと、1個のインダクタ素子2Lとを有する。フィルタ9’は、一方のコンデンサ素子2Cの第2端子電極12が信号の入力端子INに接続され、他方のコンデンサ素子2Cの第2端子電極12が信号の出力端子OUTに接続される。インダクタ素子2Lの第2端子電極12は、グランド端子GNDに接続される。コンデンサ素子2C、インダクタ素子2L及び抵抗素子2Rの第1端子電極11は、それぞれ導体3gの領域3gpによって電気的に接続される。その結果、フィルタ9’はハイパスフィルタとして機能する。この場合、2個のコンデンサ素子2Cのうち一方を抵抗素子に変更してもよい。抵抗素子としては、フェライトビーズを用いてもよい。上記説明では、コンデンサ素子とインダクタ素子と抵抗素子とのうち少なくとも2種類を用いたローパスフィルタ又はハイパスフィルタを例としたが、フィルタに用いられる素子の種類及びフィルタの種類は上述した例に限定されるものではない。

【0091】

(第3変形例)

図35は、実施形態4の第3変形例に係る複合電子部品を示す平面図である。図36、図37は、実施形態4の第3変形例に係る複合電子部品が有する電子部品を示す図である。本変形例の複合電子部品1g’は、電子部品として、複数のコンデンサアレイ2CA及びインダクタアレイ2LAを有し、これらを用いてフィルタ9を形成する点が異なる。

【0092】

図35に示すように、複合電子部品1g’は、2個のコンデンサアレイ2CAと4個のインダクタアレイ2LAとを有する。図36に示すように、コンデンサアレイ2CAは、4個のコンデンサ素子部CPを有している。4個のコンデンサ素子部CPは、一列に配置される。それぞれのコンデンサ素子部CPは、第1端子電極11及び第2端子電極12を有している。図37に示すように、インダクタアレイ2LAは、4個のインダクタ素子部LPを有している。4個のインダクタ素子部LPは、一列に配置される。それぞれのインダクタ素子部LPは、第1端子電極11及び第2端子電極12を有している。

【0093】

複合電子部品1g’は、第2変形例の複合電子部品1gが有する導体層3gを有している。すなわち、複合電子部品1g’は複数の溝8で電気的に絶縁された複数の領域3gpを有している。図35に示すように、複合電子部品1g’は、インダクタアレイ2LA、コンデンサアレイ2CA、インダクタアレイ2LAの順に配列されている。2個のインダクタアレイ2LAが有する2個のインダクタ素子部LPの第1端子電極11と、1個のコンデンサアレイ2CAが有する1個のコンデンサ素子部CPの第1端子電極11は、導体層3gの1つの領域3gpで電気的に接続される。領域3gpで第1端子電極11が電気的に接続された2個のインダクタ素子部LPと、1個のコンデンサ素子部CPとで、フィルタ9が形成される。このように、フィルタ9は、コンデンサアレイ2CA及びインダクタアレイ2LAのようなアレイ型電子部品を組み合わせて形成してもよい。

【0094】

図38は、実施形態4の複合電子部品が有する電子部品群の変形例に係る等価回路を示す図である。この例において、上述した溝8で囲まれる電子部品群9aが有する電子部品2は、バリスタ素子(例えば、チップ型バリスタ)2V及び抵抗素子2Rである。前記電子部品群は、1個のバリスタ素子2Vの第1端子電極11と2個の抵抗素子2Rの第1端子電極11とが導体層の領域3gpで電気的に接続されて、所定の機能として、バリスタとしての機能を有する。電子部品群9aは、一方の抵抗素子2Rの第2端子電極12が信号の入力端子INと電気的に接続され、他方の抵抗素子2Rの第2端子電極12が信号の出力端子OUTと電気的に接続される。また、バリスタ素子2Vの第2端子電極12はグランド端子GNDと電気的に接続される。本実施形態の複合電子部品は、このような電子部品群9aを複数有していてもよい。

【0095】

以上、本実施形態及びその変形例は、実施形態1と同様の作用、効果に加え、導体層に設けられた溝によって複数の電子部品が組み合わされて所定の機能を発揮する複数の電子部品群を1つの複合電子部品に組み込むとともに、それぞれの電子部品群の信頼性を向上させることができるという効果が得られる。本実施形態及びその変形例の構成は、以下の実施形態においても適宜適用することができる。

【符号の説明】

【0096】

1、1a、1b、1b’、1c、1d、1e、1f、1f’、1g、1g’ 複合電子部品

2、2C、2L、2R、2a、2b、2s、2g 電子部品

2Ga、2Gb、2Gc、2Gd、9a 電子部品群

2Gi 内側電子部品群

2Go 外側電子部品群

2LA インダクタアレイ

2CA コンデンサアレイ

2P、2Pc 電子部品対

3、3f、3g 導体層

3fo 外側領域

3fi 内側領域

3fa、3fb、3fc、3fd、3gp 領域

4 支持体

5、5d 絶縁部材

6 貫通孔

6H 開口部

7 放熱部材

8 溝

9、9’ フィルタ

10、10C、10R、10a、10b 素体

10S 長側面

10T 短側面

11、11a 第1端子電極

12、12a 第2端子電極

13、14 内部電極

15、17 誘電体

16 抵抗体

20 回路基板

21 第1配線

22 第2配線

23 第1基板端子

24 第2基板端子

100、100c、100e 実装構造

CP コンデンサ素子部

EP 素子部

GND グランド端子

IN 入力端子

Ia、Ib 電流

LP インダクタ素子部

OUT 出力端子

【技術分野】

【0001】

本発明は、複数の電子部品を有する複合電子部品及び複合電子部品の実装構造に関する。

【背景技術】

【0002】

複数の電子部品を一体化して1つの電子部品とする複合電子部品が知られている。例えば、特許文献1には、複数のディスクリート受動コンポーネント同士を分離し、複数のディスクリート受動コンポーネントに対する保護構造を有するメカニカルな受け構造を備えたことを特徴とする電子アセンブリが記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2004−40083号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1に記載されている電子アセンブリ(複合電子部品に相当する)は、複数のディスクリート受動コンポーネント(電子部品に相当する)がそれぞれ独立して組み合わされているので、それぞれの電子部品は、いずれも独立して回路基板に実装されることになる。特許文献1の技術は、1個の電子部品に不具合が発生すると、他の電子部品によって不具合が発生した電子部品の機能を補うことができないため、信頼性が低下するという問題がある。本発明は、複数の電子部品を含む複合電子部品の信頼性を向上させることを目的とする。

【課題を解決するための手段】

【0005】

本発明は、素体の対向する表面のそれぞれに、第1端子電極と第2端子電極とを有する複数の電子部品と、複数の前記電子部品が有する前記第1端子電極を電気的に接続する導体層と、前記導体層が設けられる支持体と、を含み、複数の前記電子部品が有する前記第2端子電極が、回路基板の端子に接続されるための実装端子電極となることを特徴とする複合電子部品である。

【0006】

この複合電子部品は、導体層によって複数の電子部品の第1端子電極同士が電気的に接続されている。このため、電子部品に不具合が発生したとしても、他の電子部品が正常であれば、正常な電子部品によって複合電子部品としての機能を維持することができる。その結果、複数の電子部品を含む複合電子部品の信頼性が向上する。

【0007】

本発明において、複数の前記電子部品は、第1の方向と、前記第1の方向に直交する第2の方向とに向かってそれぞれ配置されることが好ましい。このようにすれば、複合電子部品内に配置される電子部品の密度を大きくすることができるので、例えば、電子部品にコンデンサを用いた場合には、複合電子部品の静電容量を大きくすることができる。また、この場合、同じ静電容量であれば、複合電子部品を小型化することができる。

【0008】

本発明において、前記導体層の表面に設けられて、前記導体層とは反対側から複数の前記第2端子電極の少なくとも一部を露出させる絶縁部材を含むことが好ましい。このようにすれば、支持体による複数の電子部品の支持に加え、絶縁部材も複数の電子部品を支持することができるので、複数の電子部品がより強固に支持される。

【0009】

本発明において、前記絶縁部材は、前記第2端子電極が露出する側から前記導体層まで前記絶縁部材を貫通する貫通孔を含み、前記電子部品は前記貫通孔の内部に配置されることが好ましい。このようにすれば、貫通孔が電子部品の位置決めをするので、電子部品の位置精度が向上する。

【0010】

本発明において、隣接する前記電子部品は、それぞれの前記第2端子電極同士が異極性となるように前記回路基板の端子に接続されることが好ましい。このようにすれば、隣接する電子部品を流れる電流の向きは、それぞれ反対方向になる。その結果、この複合電子部品は、ESL(Equivalent Series Inductance:等価直列インダクタンス)を低減することができる。

【0011】

本発明において、複数の前記電子部品は、コンデンサ素子であることが好ましい。このようにすることで、複合電子部品をコンデンサとして機能させることができる。

【0012】

本発明において、複数の前記電子部品は、コンデンサ素子及び抵抗素子であり、前記コンデンサ素子と前記抵抗素子とは隣接して配置されることが好ましい。このようにすることで、隣接するコンデンサ素子と抵抗素子とを直列に接続することができるので、複合電子部品のESR(Equivalent Series Resistance:等価直列抵抗)を高くすることができる。

【0013】

隣接する前記コンデンサ素子と前記抵抗素子とは、それぞれの前記第2端子電極が異極性となるように前記回路基板の端子に接続されることが好ましい。このようにすることで、複合電子部品は、ESLを低減することができる。

【0014】

本発明において、前記電子部品は、複数の素子部を有するアレイ型電子部品であることが好ましい。このようにすることで、複合電子部品が有する電子部品の数を低減できるので、電子部品を支持体に実装する際の作業効率が向上する。

【0015】

本発明において、前記支持体は、複数の前記電子部品が配置される側とは反対側に、放熱部材を有することが好ましい。このようにすることで、放熱部材は複合電子部品の昇温を効果的に抑制することができる。

【0016】

本発明において、前記素体は、直方体形状であり、前記第1端子電極と前記第2端子電極とは、前記素体の対向する2個の短側面同士を接続する4個の長側面のうち、内部電極が露出し、かつ対向する前記長側面のそれぞれに設けられることが好ましい。このようにすることで、それぞれの電子部品のESLが低下するので、複合電子部品全体のESLも低下する。

【0017】

本発明において、前記支持体は導電体であることが好ましい。一般に、導電体は、熱の良導体でもあるので、支持体を導電体とすることにより、複合電子部品が有する複数の電子部品の熱をより効率よく伝えることができる。

【0018】

本発明において、前記支持体は絶縁体であることが好ましい。このようにすると、支持体は第1端子電極を電気的に絶縁することができるので、支持体を介して、電子部品と回路基板が格納される筐体又は回路基板に実装されている他の電子部品等とが短絡するおそれを低減できる。

【0019】

本発明において、前記導体層は、隣接する複数の前記電子部品の周囲を囲み、かつ前記支持体まで達する溝を有することが好ましい。このようにすることで、複合電子部品は、溝で区画された導体層のそれぞれの領域によって、複数の電子部品の第1端子電極同士を電気的に接続された、複数の電子部品群を有する。そして、複合電子部品は、複数の前記電子部品群に所定の機能を発揮させることができるとともに、それぞれの電子部品群の信頼性を向上させることができる。

【0020】

本発明において、前記溝で囲まれる複数の前記電子部品は、コンデンサ素子及びインダクタ素子又は抵抗素子であり、フィルタとしての機能を有することが好ましい。このようにすることで、複数のフィルタを有する複合電子部品を得ることができる。

【0021】

本発明において、前記溝で囲まれる複数の前記電子部品は、バリスタ素子及び抵抗であり、バリスタとしての機能を有することが好ましい。このようにすることで、複数のバリスタを有する複合電子部品を得ることができる。

【0022】

本発明は、素体の対向するそれぞれの端面に、第1端子電極と第2端子電極とを有する電子部品と、複数の前記電子部品が有する前記第1端子電極を電気的に接続する導体層と、前記導体層が設けられる支持体と、を含み、複数の前記電子部品が有するそれぞれの前記第2端子電極同士が異極性となるように、回路基板の端子に接続されることを特徴とする複合電子部品の実装構造である。

【0023】

この複合電子部品の実装構造で回路基板に実装される電子部品は、導体層によって複数の電子部品の第1端子電極同士が電気的に接続されている。このため、電子部品に不具合が発生したとしても、他の電子部品が正常であれば、正常な電子部品によって複合電子部品としての機能を維持することができる。その結果、複数の電子部品を含む複合電子部品の信頼性が向上する。また、複数の電子部品が有するそれぞれの第2端子電極同士が異極性となるように、回路基板の端子に接続されることにより、隣接する電子部品を流れる電流の向きは、それぞれ反対方向になる。その結果、この複合電子部品の実装構造は、ESLを低減することができる。

【0024】

本発明において、複数の前記電子部品は、コンデンサ素子及び抵抗素子であり、前記コンデンサ素子と前記抵抗素子とは隣接して配置され、かつ隣接する前記コンデンサ素子と前記抵抗素子とは、それぞれの前記第2端子電極が異極性となるように前記回路基板の端子に接続されることが好ましい。このようにすることで、隣接するコンデンサ素子と抵抗素子とを直列に接続することができるので、複合電子部品のESR(Equivalent Series Resistance:等価直列抵抗)を高くすることができる。

【発明の効果】

【0025】

本発明は、複数の電子部品を含む複合電子部品の信頼性を向上させることができる。

【図面の簡単な説明】

【0026】

【図1】図1は、実施形態1に係る複合電子部品の平面図である。

【図2】図2は、図1のA−A矢視図である。

【図3】図3は、実施形態1に係る複合電子部品が備える電子部品の斜視図である。

【図4】図4は、実施形態1に係る複合電子部品の等価回路を示す図である。

【図5】図5は、実施形態1に係る複合電子部品の実装構造を示す図である。

【図6】図6は、実施形態1の第1変形例に係る実装構造において、複合電子部品の実装端子電極の極性を説明するための図である。

【図7】図7は、実施形態1の第1変形例に係る実装構造において、複合電子部品の実装端子電極の極性を説明するための図である。

【図8】図8は、実施形態1の第1変形例に係る実装構造を示す図である。

【図9】図9は、実施形態1の第1変形例に係る実装構造の等価回路を示す図である。

【図10】図10は、本実施形態の第2変形例に係る複合電子部品を示す平面図である。

【図11】図11は、図10のB−B矢視図である。

【図12】図12は、本実施形態の第2変形例に係る複合電子部品が有する電子部品の斜視図である。

【図13】図13は、実施形態1の第3変形例に係る複合電子部品を示す平面図である。

【図14】図14は、図13のC−C矢視図である。

【図15】図15は、実施形態1の第3変形例に係る複合電子部品が有する電子部品の一例を示す断面図である。

【図16】図16は、本実施形態の第3変形例に係る複合電子部品に、他の電子部品を適用した例を示す一部断面図である。

【図17】図17は、図16に示す電子部品を示す断面図である。

【図18】図18は、実施形態1の第4変形例に係る複合電子部品を示す平面図である。

【図19】図19は、図18のD−D矢視図である。

【図20】図20は、実施形態1の第4変形例に係る複合電子部品の等価回路を示す図である。

【図21】図21は、実施形態1の第4変形例に係る実装構造を示す図である。

【図22】図22は、実施形態2に係る複合電子部品の平面図である。

【図23】図23は、図22のE−E矢視図である。

【図24】図24は、実施形態3に係る複合電子部品及びその実装構造を示す図である。

【図25】図25は、実施形態4に係る複合電子部品の平面図である。

【図26】図26は、図24のF−F矢視図である。

【図27】図27は、実施形態4に係る複合電子部品の等価回路を示す図である。

【図28】図28は、実施形態4の変形例に係る複合電子部品の平面図である。

【図29】図29は、実施形態4の変形例に係る複合電子部品の等価回路を示す図である。

【図30】図30は、実施形態4の第2変形例に係る複合電子部品の平面図である。

【図31】図31は、実施形態4の第2変形例に係る複合電子部品が有する導体層の形態を示す平面図である。

【図32】図32は、図30のG−G矢視図である。

【図33】図33は、実施形態5の第2変形例に係る複合電子部品の等価回路を示す図である。

【図34】図34は、他のフィルタの等価回路を示す図である。

【図35】図35は、実施形態4の第3変形例に係る複合電子部品を示す平面図である。

【図36】図36は、実施形態4の第3変形例に係る複合電子部品が有する電子部品を示す図である。

【図37】図37は、実施形態4の第3変形例に係る複合電子部品が有する電子部品を示す図である。

【図38】図38は、実施形態4の複合電子部品が有する電子部品群の変形例に係る等価回路を示す図である。

【発明を実施するための形態】

【0027】

本発明を実施するための形態(以下、実施形態という)につき、図面を参照しつつ詳細に説明する。以下の実施形態に記載した内容により本発明が限定されるものではない。また、以下に記載した構成には、当業者が容易に想定できるもの、実質的に同一のものが含まれる。さらに、以下に開示した構成は適宜組み合わせることが可能である。さらに、下記実施形態で開示した構成は適宜組み合わせることが可能である。また、本発明の要旨を逸脱しない範囲で構成の種々の省略、置換又は変更を行うことができる。

【0028】

(実施形態1)

図1は、実施形態1に係る複合電子部品の平面図である。図2は、図1のA−A矢視図である。図3は、実施形態1に係る複合電子部品が備える電子部品の斜視図である。図4は、実施形態1に係る複合電子部品の等価回路を示す図である。図5は、実施形態1に係る複合電子部品の実装構造を示す図である。複合電子部品1は、複数の電子部品2と、導体層3と、支持体4と、を含む。本実施形態において、複合電子部品1は、さらに絶縁部材5を含むが、絶縁部材5は必ずしも必要ではない。

【0029】

複合電子部品1は、16個の電子部品2を含むが、電子部品2の数は限定されず、奇数であってもよい。図2、図3に示すように、電子部品2は、素体10と、第1端子電極11と、第2端子電極12とを含む。素体10は、内部に電極又は導電体と誘電体とを有するセラミックの素体である。素体10は、例えば、内部電極層と誘電体層とからなるセラミックの素体である。

【0030】

素体10は、略直方体形状を呈しており、その外表面として、対向する第1及び第2の主面10M、10Mと、対向する第1及び第2の端面10E、10Eと、対向する第1及び第2の側面10U、10Uとを有する。第1及び第2の端面10E、10Eは、略長方形状である第1及び第2の主面10M、10M間を連結するように、第1及び第2の主面10M、10Mの短辺方向に延在する。第1及び第2の側面10U、10Uは、略長方形状である第1及び第2の主面10M、10M間を連結するように第1及び第2の主面10S、10Sの長辺方向に延在する。

【0031】

本実施形態において、第1及び第2の端面10E、10Eは、平面視が略正方形形状である。第1及び第2の端面10E、10Eは、2個の短側面10Tに相当する。第1及び第2の主面10M、10Mと第1及び第2の側面10U、10Uとは平面視が略長方形形状であり、これらは4個の長側面10Sに相当する。なお、素体10の形状はこれに限定されるものではない。素体10が内部電極層と誘電体層からなる場合には、第1及び第2の端面10E、10E及び第1及び第2の側面10U、10Uと略平行で、かつ主面10Mと直交するように、内部電極層と誘電体層とが積層される。

【0032】

電子部品2は、素体10の対向する表面(本実施形態では、短側面10T、10T)のそれぞれに、第1端子電極11と第2端子電極12とを有する。第1端子電極11及び第2端子電極12は、短側面10T、10Tの全体と4個の長側面10Sの一部とを覆う。一般に、このような電子部品2は、チップ型電子部品と呼ばれる種類の電子部品であり、回路基板の表面に実装できる表面実装型の電子部品である。本実施形態では、複数の電子部品2が有する第2端子電極12が、図5に示す回路基板20の第1基板端子23、第2基板端子24と電気的に接続されるための実装端子電極となり、複数の電子部品2が有する第1端子電極11が導体層3と電気的に接続される。

【0033】

本実施形態において、電子部品2は、すべてコンデンサ素子(例えば、チップ型コンデンサ)である。このコンデンサ素子は、上述した素体10の内部に設けられた2個以上の電極(内部電極)と誘電体とが積層されるとともに、前記誘電体を挟んで一方の前記内部電極が第1端子電極11と電気的に接続され、他方の前記内部電極が第2端子電極12と電気的に接続される、積層型の素子である。複合電子部品1は、複数の電子部品として複数のコンデンサ素子を備えることになるので、コンデンサとして機能する。複合電子部品1が有する電子部品2の種類はコンデンサ素子に限定されるものではなく、抵抗素子、インダクタ素子又はバリスタ素子等であってもよい。また、複合電子部品1が有する電子部品2は、すべて同じ種類であってもよいし、異なる種類であってもよい。

【0034】

導体層3は、例えば、導電性接着材又は導電性樹脂であり、本実施形態では前者である。図2に示すように、導体層3は、複数の電子部品2が有する第1端子電極11を電気的に接続する。支持体4は、本実施形態において、平面視が長方形(正方形を含む)形状の板状の部材である。本実施形態において、支持体4は、導電体であってもよいし絶縁体であってもよい。一般に、導電体は熱の良導体であるので、支持体4に導電体を用いると、複合電子部品1が有する複数の電子部品2の熱をより効率よく大気中へ伝えることができる。

【0035】

支持体4に絶縁体を用いると、第1端子電極11と支持体4とを電気的に絶縁することができるので、支持体4を介して、電子部品2と回路基板20が格納される筐体又は回路基板20に実装されている他の電子部品等とが短絡するおそれを低減できる。また、複合電子部品1の回路基板20と対向する部分を除き、複合電子部品1の表面を導電体で被覆して電磁シールド層を形成する場合がある。支持体4に絶縁体を用いると、支持体4及び前記電磁シールド層を介して、電子部品2と回路基板20が格納される筐体又は回路基板20に実装されている他の電子部品等とが短絡するおそれを低減できる。

【0036】

支持体4は、導体層3が設けられる。より具体的には、支持体4が有する面のうち、最も面積の大きい2つの面(導体層配置面)の一方に、導体層3が設けられる。このような構造により、導体層3によって第1端子電極11が電気的に接続された複数の電子部品2は、支持体4に支持される。

【0037】

本実施形態において、絶縁部材5は、絶縁性を有する樹脂であるが、これに限定されるものではない。絶縁部材5は、導体層3と接しており、導体層3を介して支持体4に固定されて支持される。絶縁部材5は、複合電子部品1が有するそれぞれの電子部品2の周囲に配置される。このような構造により、絶縁部材5は、隣接する電子部品2の間に配置される。複数の電子部品2の第2端子電極12は、絶縁部材5の表面から突出する。複数の第2端子電極12は、素体10の短側面10Tの全体を覆う部分がそれぞれ略同一平面に配置されている。このようにすると、図5に示す回路基板20に複合電子部品1を実装した際に、回路基板20の端子としての第1基板端子23及び第2基板端子24と複数の第2端子電極12との距離を略一定にすることができる。そして、回路基板20に複合電子部品1を実装した際は、すべての第2端子電極12と回路基板20の端子との接続条件を揃えることができるので、接続のばらつきを抑制することができる。その結果、複合電子部品1を回路基板20へ確実に実装するとともに、信頼性の低下を抑制することができる。

【0038】

本実施形態において、絶縁部材5は、電子部品2と接触している。このように、絶縁部材5は、電子部品2同士を絶縁するとともに、複数の電子部品2を支持する。また、絶縁部材5は、導体層3を介して支持体4に固定されている。このため、複数の電子部品2は、導体層3のみならず絶縁部材5によっても支持体4に取り付けられることになるので、より強固に支持体4に支持される。その結果、複合電子部品1は、耐振性能が高くなる。絶縁部材5は、例えば、導体層3によって支持体4に複数の電子部品2を取り付けた後、絶縁性を有する樹脂を電子部品2の周囲に充填して硬化させることによって、支持体4に設けられる。

【0039】

このような構造により、複合電子部品1は、支持体4とは反対側に配置された絶縁部材5の表面から、複数の第2端子電極12が露出する。それぞれの第2端子電極12は、互いに電気的に絶縁されている。複合電子部品1を回路基板に実装する際に、第2端子電極12の露出した部分が、回路基板20の端子と接続される実装端子電極となる。複数の第2端子電極12は、素体10の短側面10Tを覆う部分が、回路基板20の端子としての第1基板端子23、第2基板端子24と電気的に接続される。複合電子部品1の導体層3は、回路基板20の端子と直接は電気的に接続されず、電子部品2の第1端子電極11及び第2端子電極12を介して、間接的に回路基板20の端子と接続される。本実施形態において、複合電子部品1は、自身が有する電子部品2の数の同じ数の実装端子電極、すなわち、第2端子電極12を有する。

【0040】

複合電子部品1は、複数の電子部品2が、第1の方向(図1のX方向)と、第1の方向に直交する第2の方向(図2のY方向)とに向かってそれぞれ配置される。このように、複数の電子部品2は、マトリックス状に配置される。本実施形態において、隣接する電子部品2同士は等間隔で配置されるが、隣接する電子部品2同士の間隔は不等間隔であってもよい。第2端子電極12は平面視が略正方形形状なので、複数の電子部品2をマトリックス状に配置することにより、同じ支持体4の表面の面積であれば、電子部品2が配置される密度を最も高くすることができる。このため、複数の電子部品2をマトリックス状に配置することにより、複合電子部品1の静電容量を大きくすることができる。また、複数の電子部品2をマトリックス状に配置することにより、電子部品2が配置される密度を高くすることができるので、複合電子部品1を小型化することもできる。

【0041】

図5に示す複合電子部品の実装構造(以下、必要に応じて実装構造という)100において、複合電子部品1は、第2端子電極12が、回路基板20の端子としての第1基板端子23及び第2基板端子24と、はんだ25で電気的に接続される。回路基板20は、第1配線21と第2配線22とを有しており、第1配線21に第1基板端子23が電気的に接続され、第2配線21に第2基板端子24が電気的に接続される。本実施形態において、複合電子部品1は、コンデンサとして機能する。この場合、複合電子部品1は、瞬間停電等による電圧変動を抑制するため、CPU(Central Processing Unit)の近傍に実装される電流供給用のデカップリングコンデンサ等に用いられる。

【0042】

導体層3で第1端子電極11が電気的に接続された複数の電子部品2のうち、2個の電子部品2の第2端子電極12は、それぞれ第1基板端子23と第2基板端子24とに接続される。このように、2個の電子部品2が1個の電子部品対2Pとして、第1基板端子23と第2基板端子24とを介して第1配線21と第2配線22との間に接続される。複合電子部品1は、複数組の電子部品対2Pが、第1配線21と第2配線22との間に接続されて、例えば、上述したデカップリングコンデンサとして機能する。

【0043】

一組の電子部品対2Pは、2個の電子部品2が直列に接続されている。また、実装構造100は、複数の電子部品対2Pが第1配線21と第2配線22とに対して並列に接続されている。このため、複合電子部品1がn(偶数)個の電子部品2を有し、かつ電子部品2の静電容量がCiである場合、実装構造100において、コンデンサとして機能する複合電子部品1の静電容量Caは、(n/2)×(Ci/2)となる。本実施形態では、複合電子部品1は16個の電子部品2を有しているので、複合電子部品1の静電容量Caは、4×Ciになる。

【0044】

複合電子部品1は、実装構造100のように、2個の電子部品2を直列に接続して得られた複数の電子部品対2Pを並列に接続して使用することができる。このため、複合電子部品1は、電子部品2に不具合が発生したとしても、不具合が発生した電子部品2を有する電子部品対2P以外の電子部品対2Pの電子部品2が正常であれば、静電容量は低下するが、複合電子部品1の機能、すなわち、コンデンサとしての機能を維持することができる。例えば、図5に示す例では、第1配線21に接続されている2個の電子部品2のうち1個に不具合が発生しても、残りの電子部品2と、第2配線21に接続されている2個の電子部品2とは導体層3で電気的に接続されている。したがって、複合電子部品1は、静電容量が、不具合が発生する前のCiから2×Ci/3に低下するものの、コンデンサとしての機能は維持できる。

【0045】

また、複合電子部品1は、複数の電子部品2の第1端子電極11が導体層3により電気的に接続されている。このため、複合電子部品1は、第1配線21に接続される複数の電子部品2と、第2配線22に接続される複数の電子部品2とで、それぞれ少なくとも1つの電子部品2が正常であれば、静電容量は低下するが、コンデンサとしての機能を維持することができる。例えば、図5に示す例では、第1配線21に接続されている2個の電子部品2のうち1個及び第2配線22に接続されている2個の電子部品2のうち1個に不具合が発生しても、第1配線21及び第2配線21にそれぞれ接続されている残りの1個の電子部品2同士は導体層3で電気的に接続されている。したがって、複合電子部品1は、静電容量が、不具合が発生する前のCiからCi/2に低下するものの、コンデンサとしての機能は維持できる。

【0046】

さらに、奇数、例えば、3個の電子部品2の第1端子電極11を導体3で電気的に接続し、1個の電子部品2の第2端子電極12を第1配線21に接続するとともに、残りの2個の電子部品2の第2端子電極12を第2配線22に接続する。このようにすると、第1配線21と第2配線22との間に、並列に接続された2個の電子部品2と、1個の電子部品2とが直列に接続される。この場合、並列に接続された2個の電子部品2のうち1つに不具合が発生しても、第1配線21と第2配線22との間には、2個の電子部品2が直列に接続されることになる。したがって、複合電子部品1は、静電容量が、不具合が発生する前の2×Ci/3からCi/2に低下するものの、コンデンサとしての機能は維持できる。

【0047】

このように、複合電子部品1は、信頼性が向上するので、これが搭載された電子機器の信頼性を向上させることができる。また、複合電子部品1は、複数の電子部品2を1つにまとめて一体化してあるので、電子部品2がコンデンサ素子である場合には、大きい静電容量をコンパクトな寸法で実現することができる。さらに、複合電子部品1が有する複数の第2端子電極12の中からいくつかを選択して、回路基板20の第1基板端子23及び第2基板端子24に接続すれば、複合電子部品1の静電容量を所望の大きさとなるように調整することもできる。

【0048】

複合電子部品1の電子部品2が誘電体を有する場合、電子部品2を回路基板20に実装すると、誘電体に発生する電歪現象に起因した音鳴きが発生したり、素体10にクラックが発生したりすることがある。複合電子部品1が有する複数の電子部品2は、第1端子電極11が支持体4に取り付けられているが、第2端子電極12は支持体4に対して解放されている。このため、回路基板20に実装された複合電子部品1は、電子部品2から回路基板20へ伝達される力が解放されるとともに、電子部品から回路基板20に伝達される振動が緩和される。その結果、この複合電子部品1は、誘電体を有する電子部品2の電歪現象に起因して発生する音鳴きを抑制できるとともに、素体10へのクラックの発生を抑制できる。また、複合電子部品1を回路基板20に実装した場合、電子部品2は、第2端子電極12のみが回路基板20に拘束される。このため、複合電子部品1が有する電子部品2は、電子部品2の第1端子電極11及び第2端子電極12が回路基板20に接続されて拘束される場合と比較して、回路基板20の変形の影響を受けにくい。その結果、複合電子部品1は、複合電子部品1又は電子部品2の熱膨張率と回路基板20の熱膨張率との違いに起因して電子部品2が回路基板20から受ける力を低減できるので、電子部品2へのクラックの発生を抑制できる。

【0049】

(第1変形例)

図6、図7は、実施形態1の第1変形例に係る実装構造において、複合電子部品の実装端子電極の極性を説明するための図である。図8は、実施形態1の第1変形例に係る実装構造を示す図である。図9は、実施形態1の第1変形例に係る実装構造の等価回路を示す図である。図6、図7及び図9中の+、−は、複合電子部品1が有する電子部品2の実装端子電極である第2端子電極12の極性を示す。+が正極であり、−が負極である。本変形例に係る実装構造100’において、複合電子部品1の隣接する電子部品2は、それぞれの第2端子電極12同士が異極性となるように、回路基板20の端子としての第1基板端子23及び第2基板端子24に接続される。本変形例において、電子部品2はコンデンサ素子である。

【0050】

このため、図6、図7に示すように、格子状に配列された複数の第2端子電極12は、正極と負極とがそれぞれ千鳥状になる。すなわち、マトリックス状に配置された複数の電子部品2の第2端子電極12は、行方向と列方向とに向かって、正極と負極とが交互に配置される。図8に示す実装構造100’において、回路基板の第1配線21は回路基板20の信号線又は電力供給線であり、第2配線22は回路基板20のGND線である。符号2sで示す電子部品2は、第2端子電極12がはんだ25及び第1基板端子23を介して正極としての第1配線21に接続される。また、符号2gで示す電子部品2は、第2端子電極12がはんだ25及び第2基板端子24を介して負極としての第2配線22に接続される。

【0051】

図8に示すように、隣接する電子部品2s、2gの第1端子電極11は、導体層3によって接続されている。電子部品2sの第2端子電極12は、回路基板20の第1配線21に接続され、電子部品2gの第2端子電極12は、回路基板20の第2配線22に接続される。第1配線21から第2配線22へ向かって電流が流れる場合、電子部品2sを流れる電流をIa、電子部品2gを流れる電流をIbとする。電流Iaは、電子部品2sの第2端子電極12から第1端子電極11へ向かって流れる。また、電流Ibは、電子部品2gの第1端子電極11から第2端子電極12へ向かって流れる。このように、実装構造100’において、複合電子部品1が有する、隣接する電子部品2s、2gを流れる電流Ia、Ibの向きは、それぞれ反対方向になる。その結果、複合電子部品1及びその実装構造100’は、ESLを低減することができる。

【0052】

隣接する電子部品2s、2g同士の距離を小さくすると、ESLを低減させる効果が高くなる。隣接する電子部品2s、2g同士の距離を小さくするためには、電子部品2s、2gの寸法を小さくすることが好ましい。また、ESLを低下させるためには、本変形のように、複数の第2端子電極12の正極と負極とがそれぞれ千鳥状になるようにすることが好ましい。しかし、マトリックス状に配置された複数の電子部品2の第2端子電極12は、行又は列毎に異極性となるようにしてもよい。このようにしても、ある電子部品2と、この電子部品に対して行方向又は列方向に隣接する電子部品2とは、互いに異極性となるので、ESLを低減することができる。すなわち、本変形例の実装構造100’において、複合電子部品1は、ある電子部品2と、この電子部品2に隣接する少なくとも1つの電子部品2とが互いに異極性となるように、回路基板20へ実装されていればよい。このようにすれば、複合電子部品1のESLを低減させることができる。

【0053】

(第2変形例)

図10は、本実施形態の第2変形例に係る複合電子部品を示す平面図である。図11は、図10のB−B矢視図である。図12は、本実施形態の第2変形例に係る複合電子部品が有する電子部品の斜視図である。複合電子部品1aは、電子部品2aを複数(本変形例では4個)有している。複数の電子部品2aの第1端子電極11aは、導体層3によって電気的に接続されている。第2端子電極12aは、少なくとも一部が絶縁部材5の表面から露出して、実装端子電極となる。

【0054】

本変形例において、複合電子部品1aが有する電子部品2aは、直方体形状である素体10aの対向する2個の短側面10T、10T(第1及び第2の端面10E、10E)同士を接続する4個の長側面10Sのうち、内部電極が露出し、かつ対向する長側面10Sのそれぞれに、第1端子電極11aと第2端子電極12aとが設けられる。この長側面10S、10Sは、第1及び第2の主面10M、10Mではなく第1及び第2の側面10U、10Uに相当する。第1端子電極11aと第2端子電極12aとは、これらが設けられる長側面10Sの全体を覆っている。第1端子電極11aと第2端子電極12aとは、これらが全体を覆っていない2つの長側面10Sの一部及び短側面10Tの一部に延出している。

【0055】

本変形例において、電子部品2aは、コンデンサ素子である。このコンデンサ素子は、少なくとも2個の内部電極と誘電体とが積層されるとともに、前記誘電体を挟んで一方の前記内部電極が第1端子電極11aと電気的に接続され、他方の前記内部電極が第2端子電極12aと電気的に接続される積層型の素子である。電子部品2aが有する素体10aの長側面10Sは、平面視が略長方形形状である。短側面10Tは、素体10aは平面視が略長方形形状又は正方形形状であり、略長方形形状である場合、長辺は長側面10Sの長辺よりも短い。本実施形態において、第1端子電極11aと第2端子電極12aとがそれぞれ全体を覆う長側面10Sは、第1端子電極11aと第2端子電極12aとが一部に延出する長側面10Sよりも短辺の長さが短い。

【0056】

このような構造の電子部品2aは、素体10aの内部に設けられた内部電極の幅が大きく、長さが小さくなるので、電流の経路を短くすることができる。その結果、電子部品2aは、ESLを低減することができる。この例において、内部電極の幅は、第1端子電極11aと第2端子電極12aとがそれぞれ全体を覆う長側面10Sの長手方向における寸法であり、第1側面及び第2側面に引き出される内部電極の幅である。また、内部電極の長さは、第1端子電極11aから第2端子電極12aに向かう方向の寸法である。

【0057】

このような電子部品2aを複数有する複合電子部品1aは、信頼性の確保及び音鳴きの低減等といった効果に加え、ESLをより効果的に低減できるという効果が得られる。複合電子部品1aを回路基板へ実装する際には、隣接する第2端子電極12a同士がそれぞれ異極性となるようにすることで、ESLを効果的に低減できる点は上述した通りである。

【0058】

(第3変形例)

図13は、実施形態1の第3変形例に係る複合電子部品を示す平面図である。図14は、図13のC−C矢視図である。図15は、実施形態1の第3変形例に係る複合電子部品が有する電子部品の一例を示す断面図である。本変形例は、複合電子部品1bが有する電子部品2bとして、複数の素子部を有するアレイ型電子部品を用いる。図13に示すように、複合電子部品1bは、複数(本変形例では8個)の電子部品2bを有する。図14に示すように、複数の電子部品2bの第1端子電極11は導体層3によって電気的に接続される。第2端子電極12は、絶縁部材5から少なくとも一部が露出して実装端子電極となる。

【0059】

電子部品2bは、複数(本変形例では2個)の素子部EPを有する。本変形例において、素子部EPはコンデンサである。すなわち、電子部品2bは、コンデンサアレイである。図15に示すように、電子部品2bが有するそれぞれの素子部EPは、複数の内部電極13、14と誘電体15とが積層される素体10bを有するとともに、誘電体15を挟んで一方の内部電極13が第1端子電極11と電気的に接続され、他方の内部電極14が第2端子電極12と電気的に接続される。電子部品2bは、それぞれの素子部EPに対応して、2個の第1端子電極11及び2個の第2端子電極12を有している。2個の第1端子電極11は、電子部品2bの1つの長側面に配置され、2個の第2端子電極は、第1端子電極11が配置されている長側面と対向する長側面に配置される。

【0060】

図13に示すように、複合電子部品1bは、電子部品2bの素子部EPが配列されている方向に向かって2個の電子部品2bが配置され、素子部EPが配列されている方向と直交する方向に向かって4個の電子部品2bが配列されている。このような構造により、複合電子部品1bは、第1の方向(図13のX方向)及び第2の方向(図13のY方向)に向かって、それぞれ4個ずつの素子部EPが配列される。すなわち、複数の素子部EPがマトリックス状に配置される。

【0061】

図14に示すように、複合電子部品1bは、1個の電子部品2bが含む隣接する2個の素子部EPが、互いに異極性となるように回路基板へ実装することができる。この例では、+の第2端子電極12を正極として、回路基板の信号線又は電力供給線に接続し、−の第2端子電極12を負極として、回路基板のGND線に接続する。+の第2端子電極12を有する素子部EPは、第2端子電極12から第1端子電極11へ電流Iaが流れ、−の第2端子電極12を有する素子部EPは、第1端子電極11から第2端子電極12へ電流Ibが流れる。このように複合電子部品1bが回路基板へ実装されることにより、電子部品2bが有する隣接する素子部EP、EPを流れる電流Ia、Ibの向きは、それぞれ反対方向になる。その結果、複合電子部品1bは、ESLを低減することができる。

【0062】

図16は、本実施形態の第3変形例に係る複合電子部品に、他の電子部品を適用した例を示す一部断面図である。図17は、図16に示す電子部品を示す断面図である。複合電子部品1b’は、4個の素子部EPを有する電子部品2b’を複数有する。図16は、複合電子部品1b’が有する1個の電子部品2b’を示すが、この例において、複合電子部品1b’は4個の電子部品2b’を有する。

【0063】

図17に示すように、電子部品2b’は、素子部EPを4個有する。この例において、素子部EPはコンデンサであるので、電子部品2b’は、コンデンサアレイである。電子部品2b’が有するそれぞれの素子部EPの構造は、電子部品2bが有する素子部EPと同様である。図16に示すように、複合電子部品1b’も、上述した複合電子部品1bと同様に、1個の電子部品2b’が含む隣接する2個の素子部EPが、互いに異極性となるように回路基板へ実装することができる。その結果、複合電子部品1bと同様に、複合電子部品1b’も、隣接する素子部EP、EPを流れる電流Ia、Ibの向きをそれぞれ反対方向にして、ESLを低減することができる。

【0064】

複合電子部品1b、1b’は、電子部品2b、2b’としてアレイ型電子部品を有する。このため、上述した、1つの素子部のみを有する電子部品2、2aを用いる複合電子部品1、1aと比較して、電子部品2b、2b’の数を低減することができる。その結果、複合電子部品1b、1b’は、マウンタ等の実装装置が電子部品2bを支持体4に実装する回数を低減できるので、電子部品2b、2b’が支持体4に実装される時間を短縮することができる。また、複合電子部品1b、1b’は、アレイ型電子部品を用いるため、1つの素子部のみを有する電子部品2、2aよりも電子部品2b、2b’の取扱いが容易になる。その結果、複合電子部品1b、1b’は、マウンタ等の実装装置が電子部品2bを支持体4に実装する際の作業効率を向上させることができる。このように、複合電子部品1b、1b’は、電子部品2b、2b’が支持体4に実装される際の作業効率を向上させて、生産性を向上させることができる。この効果は、アレイ型電子部品が有する素子部EPの数が増加するほど顕著になる。このため、4個の素子部EPを有する電子部品2b’が用いられる複合電子部品1b’の方が、2個の素子部EPを有する電子部品2bが用いられる複合電子部品1bよりも、作業効率及び生産性向上の効果をより実現できる。

【0065】

(第4変形例)

図18は、実施形態1の第4変形例に係る複合電子部品を示す平面図である。図19は、図18のD−D矢視図である。図20は、実施形態1の第4変形例に係る複合電子部品の等価回路を示す図である。図21は、実施形態1の第4変形例に係る実装構造を示す図である。本変形例の複合電子部品1cは、異なる機能を持つ2種類の電子部品2C、2Rを有する。本変形例において、電子部品2Cはコンデンサ素子であり、電子部品2Rは抵抗素子(例えば、チップ型抵抗)であるが、これに限定されるものではない。

【0066】

電子部品2Cと電子部品2Rとは、互いに隣接して支持体4の表面に配置される。このため、電子部品2C及び電子部品2Rは、それぞれ千鳥状に配置されることになる。すなわち、複合電子部品1cは、第1の方向(図18のX方向)及び第2の方向(図18のY方向)に向かって電子部品2Cと電子部品2Rとが交互に配列される。このように、複合電子部品1cは、電子部品2C、2Rが交互に、かつマトリックス状に配置されている。

【0067】

コンデンサ素子である電子部品2Cは、図19に示すように、複数の内部電極13、14と誘電体15とが積層される素体10Cを有するとともに、誘電体15を挟んで一方の内部電極13が第1端子電極11と電気的に接続され、他方の内部電極14が第2端子電極12と電気的に接続される。抵抗素子である電子部品2Rは、抵抗体16と誘電体17とが積層される素体10Rを有するとともに、抵抗体16は、第1端子電極11及び第2端子電極12と電気的に接続される。抵抗体16は、例えば、フェライトビーズを用いることができる。

【0068】

図21に示すように、実装構造100cにおいて、複合電子部品1cは、隣接する電子部品2Cと電子部品2Rとを直列に接続して一組の電子部品対2Pcとするとともに、回路基板20の第1配線21と第2配線22との間にそれぞれの電子部品対2Pcを並列に接続する。このように、隣接する電子部品2Cと電子部品2Rとを直列に接続することにより、複合電子部品1cは、ESRを高くすることができる。複合電子部品1cは、ESRが低すぎると共振してノイズが増加する場合もある。このため、本変形例では、コンデンサ素子(電子部品2C)と直列に抵抗素子(電子部品2R)を接続して、複合電子部品1cの共振を抑制する。また、抵抗素子としての電子部品2Rが有する抵抗体16に適用できるフェライトビーズは、高周波になると電気抵抗が上昇する特性を有している。このため、電子部品2Rの抵抗体16にフェライトビーズを用いると、高周波の信号に対して複合電子部品1cのESRを上昇させることができる。

【0069】

また、本変形例では、電子部品対2Pcが有する隣接する電子部品2C、2Rを直列に接続する。そして、抵抗素子としての電子部品2Rの第2端子電極12は、正極として、回路基板20の第1基板端子23を介して第1配線21に接続され、コンデンサ素子としての電子部品2Cの第2端子電極12は、負極として、回路基板20の第2基板端子24を介して第2配線22に接続される。第1配線21は、例えば、回路基板20の信号線又は電力供給線であり、第2配線22は、例えば、回路基板20のGND線である。

【0070】

正極としての第2端子電極12を有する電子部品2Rは、第2端子電極12から第1端子電極11へ電流Iaが流れ、負極としての第2端子電極12を有する電子部品2Cは、第1端子電極11から第2端子電極12へ電流Ibが流れる。実装構造100cにおいて、このような形態で複合電子部品1cが回路基板20へ実装されることにより、電子部品2R、2Cを流れる電流Ia、Ibの向きはそれぞれ反対方向になる。その結果、複合電子部品1cは、ESLを低減することができる。

【0071】

以上、本実施形態及びその変形例は、複数の電子部品の第1端子電極を導体層で電気的に接続するとともに、第2端子電極を、回路基板の端子と接続するための実装端子電極とする。このようにすることで、本実施形態及びその変形例は、複合電子部品が有する電子部品に不具合が発生したとしても、不具合が発生した電子部品が属する電子部品対以外の電子部品対に属する電子部品が正常であれば、コンデンサとしての機能を維持することができる。その結果、本実施形態及びその変形例は、複数の電子部品を含む複合電子部品の信頼性を向上させることができるとともに、複合電子部品が搭載された電子機器の信頼性を向上させることができる。本実施形態及びその変形例の構成は、以下の実施形態においても適宜適用することができる。また、本実施形態及びその変形例の構成を備えるものは、本実施形態及びその変形例と同様の作用、効果を奏する。

【0072】

(実施形態2)

図22は、実施形態2に係る複合電子部品の平面図である。図23は、図22のE−E矢視図である。本実施形態の複合電子部品1dは、電子部品2の第2端子電極12が露出する側から前記4まで絶縁部材5dを貫通する貫通孔6を含み、電子部品2は貫通孔6の内部に配置される。他の構成は、実施形態1の複合電子部品1と同様である。

【0073】

絶縁部材5dは、最も大きい2個を貫通する複数の貫通孔6を有している。貫通孔6の数は、複合電子部品1dが有する電子部品2の数と同数である。この貫通孔6の内部に、複数の電子部品2が配置される。そして、電子部品2は、第1端子電極11が導体層3と電気的に接続され、第2端子電極12の少なくとも一部が貫通孔6の開口部6Hから露出する。本実施形態では、貫通孔6の開口部6Hを超えて、第2端子電極12が貫通孔6の開口部6Hから露出する。

【0074】

複合電子部品1dを製造するにあたって、支持体4に導体層3となる導電性接着材を塗布した後、複数の貫通孔6を有する絶縁部材5dを前記導電性接着材の表面に載置する。その後、貫通孔6の内部に、第1端子電極11から先に電子部品2を挿入して、第1端子電極11と前記導電性接着材とを接触させることにより、電子部品2を支持体4に搭載する。そして、前記導電性接着材を硬化させて、それぞれの第1端子電極11を電気的に接続するとともに、支持体4と絶縁部材5dとを接着する。このようにして、複合電子部品1dが完成する。複合電子部品1dは、電子部品2を支持体4に搭載する際には、貫通孔6が電子部品2のガイドとして機能するので、電子部品2を支持体4に搭載する作業が容易になる。また、貫通孔6は、それぞれの電子部品2の位置決めをするガイドとしても機能するので、複合電子部品1dが有する電子部品2の位置精度を向上させることもできる。さらに、複合電子部品1dは、板状の絶縁部材5dを支持体4に取り付けるので、絶縁樹脂を充填して絶縁部材5とする実施形態1の複合電子部品1と比較して、絶縁部材5dの厚み(最も大きい2個の面と直交する方向の寸法)の寸法精度及び第2端子電極12側の面の平面度を向上させることができる。その結果、第2端子電極12が絶縁部材5dに埋もれてしまうような事態を回避できる。

【0075】

以上、本実施形態は、実施形態1と同様の作用、効果に加え、電子部品を支持体に搭載する作業の効率が向上するとともに、複数の電子部品の位置精度が向上するという効果が得られる。本実施形態及びその変形例の構成は、以下の実施形態においても適宜適用することができる。また、本実施形態及びその変形例の構成を備えるものは、本実施形態及びその変形例と同様の作用、効果を奏する。

【0076】

(実施形態3)

図24は、実施形態3に係る複合電子部品及びその実装構造を示す図である。本実施形態の複合電子部品1eは、支持体4が、複数の電子部品2が配置される側とは反対側に、放熱部材7を有する。他の構成は、実施形態1の複合電子部品1又は実施形態2の複合電子部品1dと同様である。放熱部材7は、複合電子部品1eが有する複数の電子部品2が発生する熱を大気中へ放熱して、複合電子部品1eの昇温を抑制する。実装構造100eは、放熱部材7を有する複合電子部品1eの第2端子電極12を、回路基板20の第1基板端子23及び第2基板端子24にはんだ25で接合することにより、複合電子部品1eを回路基板20へ実装したものである。複合電子部品1eは、放熱性能が高いため、回路基板20に昇温しやすい電子部品が搭載されている場合及び昇温しやすい環境で使用される場合に好ましい。

【0077】

図24に示すように、複合電子部品1eは、実施形態1の複合電子部品1又は実施形態2の複合電子部品1dの支持体4に、放熱部材7を取り付けた構造である。より具体的には、複合電子部品1eは、複合電子部品1又は1dが有する支持体4の最も大きい2つの面4H、4Dのうち、導体層3が設けられる面4Dとは反対の面4H、すなわち、複数の電子部品2が配置される側とは反対側に、放熱部材7が取り付けられている。放熱部材7は、熱伝導性の高い材料が用いられる。本実施形態では、例えば、アルミニウム、アルミニウム合金、銅又は銅合金等の金属材料が放熱部材7に用いられるが、これらに限定されるものではない。放熱部材7は、支持体4とは反対側に、複数のフィン7Fを有する。複数のフィン7Fは、放熱部材7の表面積を大きくして、放熱性能を向上させる。

【0078】

本実施形態において、導体層3を介して複数の電子部品2及び絶縁部材5、5eが取り付けられる支持体4は、導電体であってもよいし、絶縁体であってもよい。一般に、導電体は熱の良導体であるので、支持体4に導電体を用いると、複合電子部品1eが有する複数の電子部品2の熱をより効率よく放熱部材7へ伝えることができる。また、支持体4に絶縁体を用いると、第1端子電極11と放熱部材7とを電気的に絶縁することができるので、放熱部材7を介して、電子部品2と回路基板20が格納される筐体又は回路基板20に実装されている他の電子部品等とが短絡するおそれを低減できる。

【0079】

以上、本実施形態は、実施形態1と同様の作用、効果に加え、複合電子部品の放熱性能が向上するという効果が得られる。本実施形態及びその変形例の構成は、以下の実施形態においても適宜適用することができる。また、本実施形態及びその変形例の構成を備えるものは、本実施形態及びその変形例と同様の作用、効果を奏する。

【0080】

(実施形態4)

図25は、実施形態4に係る複合電子部品の平面図である。図26は、図24のF−F矢視図である。図27は、実施形態4に係る複合電子部品の等価回路を示す図である。本実施形態の複合電子部品1fは、支持体4が絶縁体であり、導体層3fは、隣接する複数の電子部品2の周囲を囲み、かつ支持体4まで達する溝8を有している。他の構成は、実施形態1の複合電子部品1と同様である。本実施形態において、電子部品2はコンデンサであるが、これに限定されるものではない。

【0081】

図25、図26に示すように、複合電子部品1fは、16個の電子部品2が、第1の方向としてのX方向に4個配列され、第1の方向に直交する第2の方向としてのY方向に4個配列されている。このように、複合電子部品1fは、16個の電子部品2が4×4のマトリックス状に配置されている。複合電子部品1fが有する複数の電子部品2を、マトリックスの要素(成分)として見た場合、要素(2、2)、(2、3)、(3、2)、(3、3)に対応する電子部品2の周囲は、溝8で囲まれている。図25、図26に示すように、溝8は、導体層3fに設けられるとともに、支持体4まで達している。より具体的には、溝8は、導体層3fの第2端子電極12側から支持体4の第1端子電極11側における表面まで貫通している。このような構造により、溝8は、導体層3fを2つの領域、すなわち、内側領域3fiと外側領域3foとに区画するとともに、両者を電気的に絶縁する。

【0082】

外側領域3foの導体層3fは、外側領域3foに配置される12個の電子部品2の第1端子電極11を電気的に接続する。内側領域3fiの導体層3fは、内側領域3fiに配置される4個の電子部品2の第1端子電極11を電気的に接続する。このような構造により、複合電子部品1fは、図27の等価回路に示すように、4個の電子部品2の第1端子電極11が電気的に接続された内側電子部品群2Giと、12個の電子部品2の第1端子電極11が電気的に接続された外側電子部品群2Goと、を有する。本実施形態において、電子部品2はコンデンサであるので、複合電子部品1fは、内側電子部品群2Giと外側電子部品群2Goとがそれぞれ1つのコンデンサとして機能する。すなわち、内側電子部品群2Giが有する複数の電子部品2と外側電子部品群2Goが有する複数の電子部品2とは、所定の機能を有する回路となる。

【0083】

このように、複合電子部品1fは、所定の機能(本実施形態ではコンデンサとしての機能)を発揮する電子部品群を複数有する。それぞれの電子部品群は、複数の電子部品2を有し、かつ第1端子電極11同士が電気的に接続されている。このため、それぞれの電子部品群は、信頼性が向上する。したがって、複合電子部品1fは、信頼性の高い複数の電子部品群を有することができる。複合電子部品1fは、実施形態1の複合電子部品1と同様の絶縁部材5を有するものとしたが、複合電子部品1fの絶縁部材5はこれに限定されるものではない。例えば、実施形態2の複合電子部品1dが有する絶縁部材5dのように、内部に電子部品2が配置される貫通孔6を有していてもよい。

【0084】

(変形例)

図28は、実施形態4の変形例に係る複合電子部品の平面図である。図29は、実施形態4の変形例に係る複合電子部品の等価回路を示す図である。本変形例の複合電子部品1f’は、実施形態4の複合電子部品1fと同様であるが、導体層3f’が区画される形態が異なる。複合電子部品1f’は、3本の溝8が導体層3f’を4個の領域、すなわち、第1領域3fa、第2領域3fb、第3領域3fc及び第4領域3fdに区画する。第1領域3faと第2領域3fbと第3領域3fcと第4領域3fdとは、それぞれ電気的に絶縁される。第1領域3fa、第2領域3fb、第3領域3fc及び第4領域3fdは、4個の電子部品2の第1端子電極11を電気的に接続する。このように、3本の溝8は、4×4のマトリックス状に配置された16個の電子部品2を列毎に区画して、4個の電子部品群2Ga、2Gb、2Gc、2Gdとする。

【0085】

複合電子部品1f’は、4個の電子部品群2Ga、2Gb、2Gc、2Gdが、それぞれ1つのコンデンサとして機能する。複合電子部品1f’が有する複数の電子部品群2Ga、2Gb、2Gc、2Gdは、複数の電子部品2を有し、かつ第1端子電極11同士が電気的に接続されている。このため、それぞれの電子部品群2Ga、2Gb、2Gc、2Gdは信頼性が向上するので、複合電子部品1f’は信頼性の高い複数の電子部品群2Ga、2Gb、2Gc、2Gdを有することができる。実施形態4及び本変形例で示したように、溝8が導体層3f、3f’を区画した領域によって複数の電子部品2の第1端子電極11同士が電気的に接続されていれば、区画の形態は限定されるものではない。

【0086】

(第2変形例)

図30は、実施形態4の第2変形例に係る複合電子部品の平面図である。図31は、実施形態4の第2変形例に係る複合電子部品が有する導体層の形態を示す平面図である。図32は、図30のG−G矢視図である。図33は、実施形態5の第2変形例に係る複合電子部品の等価回路を示す図である。本変形例の複合電子部品1gは、実施形態4及びその変形例の複合電子部品1f、1f’と同様であるが、溝で区画された領域に配置された複数の電子部品2は、所定の機能としてフィルタの機能を有する点が異なる。

【0087】

複合電子部品1gは、複数(本実施形態では8個)のフィルタ9を有する。複合電子部品1gが有するフィルタ9の数は限定されるものではない。フィルタ9は、3個の電子部品2を有する。電子部品2Cはコンデンサ素子であり、電子部品2Lはインダクタ素子(例えば、チップ型インダクタ等)である。以下においては、必要に応じて電子部品2Cをコンデンサ素子2C、電子部品2Lをインダクタ素子2Lという。

【0088】

図31に示すように、複合電子部品1gは、溝8が導体層3gを区画した複数の領域3gpを有している。本実施形態では、3本の溝8と、この3本の溝8に直交する1本の溝8によって、導体層3gは8個の領域3gpに区画されている。それぞれの領域3gpは、互いに電気的に絶縁されている。図32に示すように、それぞれの領域3gpは、1つのコンデンサ素子2C及び2つのインダクタ素子2Lの第1端子電極11を電気的に接続する。このような構造により、1個のコンデンサ素子2Cと2個のインダクタ素子2Lとを有するフィルタ9が作られる。1個のコンデンサ素子2C及び2個のインダクタ素子2Lの第2端子電極12は、絶縁部材5の表面から少なくとも一部が露出して、複合電子部品1gの実装端子電極となる。絶縁部材5は、実施形態2の複合電子部品1dが有する絶縁部材5dのように、内部に電子部品2が配置される貫通孔6を有していてもよい。

【0089】

図33に示すように、フィルタ9は、一方のインダクタ素子2Lの第2端子電極12が信号の入力端子INと電気的に接続され、他方のインダクタ素子2Lの第2端子電極12が信号の出力端子OUTと電気的に接続される。コンデンサ素子2Cの第2端子電極12は、グランド端子GNDと電気的に接続される。その結果、フィルタ9はローパスフィルタとして機能する。この場合、2個のインダクタ素子2Lのうち少なくとも一方を抵抗素子に変更してもよい。抵抗素子としては、フェライトビーズを用いてもよい。また、2個のインダクタ素子2Lの代わりにフェライトビーズを用いてもよい。

【0090】

図34は、他のフィルタの等価回路を示す図である。フィルタ9’は、電子部品として、2個のコンデンサ素子2Cと、1個のインダクタ素子2Lとを有する。フィルタ9’は、一方のコンデンサ素子2Cの第2端子電極12が信号の入力端子INに接続され、他方のコンデンサ素子2Cの第2端子電極12が信号の出力端子OUTに接続される。インダクタ素子2Lの第2端子電極12は、グランド端子GNDに接続される。コンデンサ素子2C、インダクタ素子2L及び抵抗素子2Rの第1端子電極11は、それぞれ導体3gの領域3gpによって電気的に接続される。その結果、フィルタ9’はハイパスフィルタとして機能する。この場合、2個のコンデンサ素子2Cのうち一方を抵抗素子に変更してもよい。抵抗素子としては、フェライトビーズを用いてもよい。上記説明では、コンデンサ素子とインダクタ素子と抵抗素子とのうち少なくとも2種類を用いたローパスフィルタ又はハイパスフィルタを例としたが、フィルタに用いられる素子の種類及びフィルタの種類は上述した例に限定されるものではない。

【0091】

(第3変形例)

図35は、実施形態4の第3変形例に係る複合電子部品を示す平面図である。図36、図37は、実施形態4の第3変形例に係る複合電子部品が有する電子部品を示す図である。本変形例の複合電子部品1g’は、電子部品として、複数のコンデンサアレイ2CA及びインダクタアレイ2LAを有し、これらを用いてフィルタ9を形成する点が異なる。

【0092】

図35に示すように、複合電子部品1g’は、2個のコンデンサアレイ2CAと4個のインダクタアレイ2LAとを有する。図36に示すように、コンデンサアレイ2CAは、4個のコンデンサ素子部CPを有している。4個のコンデンサ素子部CPは、一列に配置される。それぞれのコンデンサ素子部CPは、第1端子電極11及び第2端子電極12を有している。図37に示すように、インダクタアレイ2LAは、4個のインダクタ素子部LPを有している。4個のインダクタ素子部LPは、一列に配置される。それぞれのインダクタ素子部LPは、第1端子電極11及び第2端子電極12を有している。

【0093】

複合電子部品1g’は、第2変形例の複合電子部品1gが有する導体層3gを有している。すなわち、複合電子部品1g’は複数の溝8で電気的に絶縁された複数の領域3gpを有している。図35に示すように、複合電子部品1g’は、インダクタアレイ2LA、コンデンサアレイ2CA、インダクタアレイ2LAの順に配列されている。2個のインダクタアレイ2LAが有する2個のインダクタ素子部LPの第1端子電極11と、1個のコンデンサアレイ2CAが有する1個のコンデンサ素子部CPの第1端子電極11は、導体層3gの1つの領域3gpで電気的に接続される。領域3gpで第1端子電極11が電気的に接続された2個のインダクタ素子部LPと、1個のコンデンサ素子部CPとで、フィルタ9が形成される。このように、フィルタ9は、コンデンサアレイ2CA及びインダクタアレイ2LAのようなアレイ型電子部品を組み合わせて形成してもよい。

【0094】

図38は、実施形態4の複合電子部品が有する電子部品群の変形例に係る等価回路を示す図である。この例において、上述した溝8で囲まれる電子部品群9aが有する電子部品2は、バリスタ素子(例えば、チップ型バリスタ)2V及び抵抗素子2Rである。前記電子部品群は、1個のバリスタ素子2Vの第1端子電極11と2個の抵抗素子2Rの第1端子電極11とが導体層の領域3gpで電気的に接続されて、所定の機能として、バリスタとしての機能を有する。電子部品群9aは、一方の抵抗素子2Rの第2端子電極12が信号の入力端子INと電気的に接続され、他方の抵抗素子2Rの第2端子電極12が信号の出力端子OUTと電気的に接続される。また、バリスタ素子2Vの第2端子電極12はグランド端子GNDと電気的に接続される。本実施形態の複合電子部品は、このような電子部品群9aを複数有していてもよい。

【0095】

以上、本実施形態及びその変形例は、実施形態1と同様の作用、効果に加え、導体層に設けられた溝によって複数の電子部品が組み合わされて所定の機能を発揮する複数の電子部品群を1つの複合電子部品に組み込むとともに、それぞれの電子部品群の信頼性を向上させることができるという効果が得られる。本実施形態及びその変形例の構成は、以下の実施形態においても適宜適用することができる。

【符号の説明】

【0096】

1、1a、1b、1b’、1c、1d、1e、1f、1f’、1g、1g’ 複合電子部品

2、2C、2L、2R、2a、2b、2s、2g 電子部品

2Ga、2Gb、2Gc、2Gd、9a 電子部品群

2Gi 内側電子部品群

2Go 外側電子部品群

2LA インダクタアレイ

2CA コンデンサアレイ

2P、2Pc 電子部品対

3、3f、3g 導体層

3fo 外側領域

3fi 内側領域

3fa、3fb、3fc、3fd、3gp 領域

4 支持体

5、5d 絶縁部材

6 貫通孔

6H 開口部

7 放熱部材

8 溝

9、9’ フィルタ

10、10C、10R、10a、10b 素体

10S 長側面

10T 短側面

11、11a 第1端子電極

12、12a 第2端子電極

13、14 内部電極

15、17 誘電体

16 抵抗体

20 回路基板

21 第1配線

22 第2配線

23 第1基板端子

24 第2基板端子

100、100c、100e 実装構造

CP コンデンサ素子部

EP 素子部

GND グランド端子

IN 入力端子

Ia、Ib 電流

LP インダクタ素子部

OUT 出力端子

【特許請求の範囲】

【請求項1】

素体の対向する表面のそれぞれに、第1端子電極と第2端子電極とを有する複数の電子部品と、

複数の前記電子部品が有する前記第1端子電極を電気的に接続する導体層と、

前記導体層が設けられる支持体と、を含み、

複数の前記電子部品が有する前記第2端子電極が、回路基板の端子に接続されるための実装端子電極となることを特徴とする複合電子部品。

【請求項2】

複数の前記電子部品は、第1の方向と、前記第1の方向に直交する第2の方向とに向かってそれぞれ配置される請求項1に記載の複合電子部品。

【請求項3】

前記導体層の表面に設けられて、前記導体層とは反対側から複数の前記第2端子電極の少なくとも一部を露出させる絶縁部材を含む請求項1又は2に記載の複合電子部品。

【請求項4】

前記絶縁部材は、

前記第2端子電極が露出する側から前記導体層まで前記絶縁部材を貫通する貫通孔を含み、前記電子部品は前記貫通孔の内部に配置される請求項3に記載の複合電子部品。

【請求項5】

隣接する前記電子部品は、それぞれの前記第2端子電極同士が異極性となるように前記回路基板の端子に接続される請求項1から4のいずれか1項に記載の複合電子部品。

【請求項6】

複数の前記電子部品は、コンデンサ素子である請求項1から5のいずれか1項に記載の複合電子部品。

【請求項7】

複数の前記電子部品は、コンデンサ素子及び抵抗素子であり、前記コンデンサ素子と前記抵抗素子とは隣接して配置される請求項1から5のいずれか1項に記載の複合電子部品。

【請求項8】

隣接する前記コンデンサ素子と前記抵抗素子とは、それぞれの前記第2端子電極が異極性となるように前記回路基板の端子に接続される請求項7に記載の複合電子部品。

【請求項9】

前記電子部品は、複数の素子部を有するアレイ型電子部品である請求項1から8のいずれか1項に記載の複合電子部品。

【請求項10】

前記支持体は、複数の前記電子部品が配置される側とは反対側に、放熱部材を有する請求項1から9のいずれか1項に記載の複合電子部品。

【請求項11】

前記素体は、直方体形状であり、前記第1端子電極と前記第2端子電極とは、前記素体の対向する2個の短側面同士を接続する4個の長側面のうち、内部電極が露出し、かつ対向する前記長側面のそれぞれに設けられる請求項1から10のいずれか1項に記載の複合電子部品。

【請求項12】

前記支持体は導電体である請求項1から11のいずれか1項に記載の複合電子部品。

【請求項13】

前記支持体は絶縁体である請求項1から11のいずれか1項に記載の複合電子部品。

【請求項14】

前記導体層は、隣接する複数の前記電子部品の周囲を囲み、かつ前記支持体まで達する溝を有する請求項13に記載の複合電子部品。

【請求項15】

前記溝で囲まれる複数の前記電子部品は、コンデンサ素子及びインダクタ素子又は抵抗素子であり、フィルタとしての機能を有する請求項14に記載の複合電子部品。

【請求項16】

前記溝で囲まれる複数の前記電子部品は、バリスタ素子及び抵抗素子であり、バリスタとしての機能を有する請求項14に記載の複合電子部品。

【請求項17】

素体の対向するそれぞれの端面に、第1端子電極と第2端子電極とを有する電子部品と、

複数の前記電子部品が有する前記第1端子電極を電気的に接続する導体層と、

前記導体層が設けられる支持体と、を含み、

複数の前記電子部品が有するそれぞれの前記第2端子電極同士が異極性となるように、回路基板の端子に接続されることを特徴とする複合電子部品の実装構造。

【請求項18】

複数の前記電子部品は、コンデンサ素子及び抵抗素子であり、前記コンデンサ素子と前記抵抗素子とは隣接して配置され、かつ隣接する前記コンデンサ素子と前記抵抗素子とは、それぞれの前記第2端子電極が異極性となるように前記回路基板の端子に接続される請求項17に記載の複合電子部品の実装構造。

【請求項1】

素体の対向する表面のそれぞれに、第1端子電極と第2端子電極とを有する複数の電子部品と、

複数の前記電子部品が有する前記第1端子電極を電気的に接続する導体層と、

前記導体層が設けられる支持体と、を含み、

複数の前記電子部品が有する前記第2端子電極が、回路基板の端子に接続されるための実装端子電極となることを特徴とする複合電子部品。

【請求項2】

複数の前記電子部品は、第1の方向と、前記第1の方向に直交する第2の方向とに向かってそれぞれ配置される請求項1に記載の複合電子部品。

【請求項3】

前記導体層の表面に設けられて、前記導体層とは反対側から複数の前記第2端子電極の少なくとも一部を露出させる絶縁部材を含む請求項1又は2に記載の複合電子部品。

【請求項4】

前記絶縁部材は、

前記第2端子電極が露出する側から前記導体層まで前記絶縁部材を貫通する貫通孔を含み、前記電子部品は前記貫通孔の内部に配置される請求項3に記載の複合電子部品。

【請求項5】

隣接する前記電子部品は、それぞれの前記第2端子電極同士が異極性となるように前記回路基板の端子に接続される請求項1から4のいずれか1項に記載の複合電子部品。

【請求項6】

複数の前記電子部品は、コンデンサ素子である請求項1から5のいずれか1項に記載の複合電子部品。

【請求項7】

複数の前記電子部品は、コンデンサ素子及び抵抗素子であり、前記コンデンサ素子と前記抵抗素子とは隣接して配置される請求項1から5のいずれか1項に記載の複合電子部品。

【請求項8】

隣接する前記コンデンサ素子と前記抵抗素子とは、それぞれの前記第2端子電極が異極性となるように前記回路基板の端子に接続される請求項7に記載の複合電子部品。

【請求項9】

前記電子部品は、複数の素子部を有するアレイ型電子部品である請求項1から8のいずれか1項に記載の複合電子部品。

【請求項10】

前記支持体は、複数の前記電子部品が配置される側とは反対側に、放熱部材を有する請求項1から9のいずれか1項に記載の複合電子部品。

【請求項11】

前記素体は、直方体形状であり、前記第1端子電極と前記第2端子電極とは、前記素体の対向する2個の短側面同士を接続する4個の長側面のうち、内部電極が露出し、かつ対向する前記長側面のそれぞれに設けられる請求項1から10のいずれか1項に記載の複合電子部品。

【請求項12】

前記支持体は導電体である請求項1から11のいずれか1項に記載の複合電子部品。

【請求項13】

前記支持体は絶縁体である請求項1から11のいずれか1項に記載の複合電子部品。

【請求項14】

前記導体層は、隣接する複数の前記電子部品の周囲を囲み、かつ前記支持体まで達する溝を有する請求項13に記載の複合電子部品。

【請求項15】

前記溝で囲まれる複数の前記電子部品は、コンデンサ素子及びインダクタ素子又は抵抗素子であり、フィルタとしての機能を有する請求項14に記載の複合電子部品。

【請求項16】

前記溝で囲まれる複数の前記電子部品は、バリスタ素子及び抵抗素子であり、バリスタとしての機能を有する請求項14に記載の複合電子部品。

【請求項17】

素体の対向するそれぞれの端面に、第1端子電極と第2端子電極とを有する電子部品と、

複数の前記電子部品が有する前記第1端子電極を電気的に接続する導体層と、

前記導体層が設けられる支持体と、を含み、

複数の前記電子部品が有するそれぞれの前記第2端子電極同士が異極性となるように、回路基板の端子に接続されることを特徴とする複合電子部品の実装構造。

【請求項18】

複数の前記電子部品は、コンデンサ素子及び抵抗素子であり、前記コンデンサ素子と前記抵抗素子とは隣接して配置され、かつ隣接する前記コンデンサ素子と前記抵抗素子とは、それぞれの前記第2端子電極が異極性となるように前記回路基板の端子に接続される請求項17に記載の複合電子部品の実装構造。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【公開番号】特開2013−80773(P2013−80773A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2011−219137(P2011−219137)

【出願日】平成23年10月3日(2011.10.3)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成23年10月3日(2011.10.3)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

[ Back to top ]