複数のはんだバンプから成るアレイにおいて、部分的に異なるはんだバンプを用いるアレイ配置上の工夫

【課題】 シリコンチップの層間絶縁膜に機械的強度の低い(脆い)low−k材料が用いられる構造においても、シリコンチップ上にかかる応力を軽減するような低応力のはんだバンプ接続を実現すること。

【解決手段】 正方形シリコンチップ(厚さ725μm)とラミネート層(厚さ1000μm)とが、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を介して、正方形シリコンチップとラミネート層との間に2次元アレイ状に配置された複数のはんだバンプの溶融後の硬化により接続されている、積層体として、

正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された部分的な複数のはんだバンプについては、他の部分の複数のはんだバンプよりも弾性率が相対的に低くなるようにフィラーを入れて調整されている、ことを特徴とするものである。

【解決手段】 正方形シリコンチップ(厚さ725μm)とラミネート層(厚さ1000μm)とが、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を介して、正方形シリコンチップとラミネート層との間に2次元アレイ状に配置された複数のはんだバンプの溶融後の硬化により接続されている、積層体として、

正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された部分的な複数のはんだバンプについては、他の部分の複数のはんだバンプよりも弾性率が相対的に低くなるようにフィラーを入れて調整されている、ことを特徴とするものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のはんだバンプによって接合を形成する積層体および製造方法に関する。より詳しくは、シリコンチップ上にかかる応力を軽減することを目的として、複数のはんだバンプから成るアレイにおいて、部分的に異なるはんだバンプを用いるアレイ配置上の工夫に関する。

【背景技術】

【0002】

3次元集積化技術では、入出力(I/O))数の増加に伴って、はんだバンプ(はんだボール)の微細化(例えば、5μm〜40μm径)が進んでいる。

【0003】

寄生容量を減らす目的で、LSIの層間の絶縁膜にはlow−k(低い誘電率)材料が使われる。この絶縁膜によって、半導体チップの配線層(BEOL)を絶縁する。

【0004】

最先端のLSIでは、層間絶縁膜に機械的強度の低い(脆い)low−k材料(さらに低誘電率のULKを含む。)が用いられることが多くなっており、低応力のはんだバンプ接続(接合)が求められている。

【0005】

特許文献1は、フィラー入りのはんだを使用して、接合部分近傍のクラックの発生を防止することについて説明している。

【0006】

しかし、特許文献1がはんだバンプ単体における工夫である点で、本発明とは大きく異なる。

【0007】

また、特許文献1においては、はんだバンプ単体の中においても、接合箇所だけにフィラーであるシリカが集中しすぎている点で、溶融と硬化のプロセスを通じての安定性に疑問が残る。

【0008】

本発明が対象としているはんだバンプに比較すると、特許文献1が対象としているはんだバンプは、サイズ、スケールともに大きいものである。

【0009】

特許文献1の方法に従って、本発明が対象としているような微細化の進んだ小さいスケールのはんだバンプの溶融後の硬化の処理を行おうとすると、金属間化合物(IMC)が形成され易く、より弾性率の高い材料へと変化してしまうこともある。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2010−219507号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明の目的は、シリコンチップの層間絶縁膜に機械的強度の低い(脆い)low−k材料が用いられる構造においても、シリコンチップ上にかかる応力を軽減するような低応力のはんだバンプ接続を実現することにある。

【課題を解決するための手段】

【0012】

正方形シリコンチップ(厚さ725μm)とラミネート層(厚さ1000μm)とが、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を介して、正方形シリコンチップとラミネート層との間に2次元アレイ状に配置された複数のはんだバンプの溶融後の硬化により接続されている、積層体として、

正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された部分的な複数のはんだバンプについては、他の部分の複数のはんだバンプよりも弾性率が相対的に低くなるようにフィラーを入れて調整されている、ことを特徴とするものである。

【発明の効果】

【0013】

最大応力を20%まで下げることが可能である。

【図面の簡単な説明】

【0014】

【図1】図1は、はんだバンプによる積層体の構造と、その製造プロセスを示す模式図である。

【図2】図2は、混合材料の弾性率(ヤング率)について説明する図である。

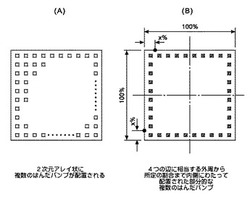

【図3】図3は、正方形シリコンチップ上に2次元アレイ状に配置された複数のはんだバンプを示す図である。

【図4】図4は、本発明の効果を検証するために、有限要素法(FEM)によるシミュレーションをするモデルを説明する図である。

【図5】図5は、有限要素法(FEM)によるシミュレーションの結果を示す図である。

【図6】図6は、本発明を適用した、有限要素法(FEM)によるシミュレーションの結果を示す図である。

【発明を実施するための形態】

【0015】

図1は、はんだバンプによる積層体の構造と、その製造プロセスを示す模式図である。

図1(A)は、積層体の側面図である。サイズ、スケールともに誇張して描かれている部分があることに留意されたい。

【0016】

ラミネート層(厚さt=1000μm)の上に、シリコンチップ(厚さt=725μm)が3次元的に積層されているが、これらの間には複数のはんだバンプが配置されている。実際には、シリコンチップは、ほとんどの場合、(上から見ると)正方形であるが、ここでは側面図であるので、正方形であることまでは分からない。

【0017】

図1(B)は、ひとつのはんだバンプ付近の構造を拡大した模式図である。

【0018】

ラミネート層の上には金属パッドが設けられている。はんだバンプが溶融後に硬化することによって、はんだバンプと金属パッドとの間が機械的かつ電気的に接合される。

【0019】

シリコンチップ上の配置は特徴的であり、low-k層という絶縁層が設けられている。これは配線層(BEOL)の絶縁層であり、このlow-k層を介して金属パッドが設けられている。

【0020】

この図では、はんだバンプはシリコンチップ側の金属パッド上に(予め)配置されているが、はんだバンプがラミネート層側の金属パッド上に(予め)配置されるような態様であってもよい。

【0021】

はんだバンプは、はんだボール等として別体として提供される場合もある。

【0022】

積層させていくプロセスは、積層体の製造方法として具現化することもできる。積層体を製造する前準備として、はんだバンプを配置する方法としても特徴がある。

【0023】

図1(C)は、はんだバンプの弾性率(ヤング率)をフィラーを入れて調整すること、および、はんだバンプの溶融後の硬化によって生じうる現象を説明する模式図である。

【0024】

母体(m:matrix)のはんだバンプの弾性率をEmとすると、フィラー(f:filler)を入れて調整された弾性率Efは、Ef<Emの関係となる。

【0025】

混合材料(c:composite)としての、はんだバンプ+フィラーは、Ec<Emであるが、線膨張係数(CTE)も母体のはんだバンプよりも小さい。

【0026】

はんだバンプを溶融させて硬化させるプロセスを経ると、はんだバンプと金属パッドとの間で金属間化合物(IMC)が形成されてしまうこともある。

【0027】

金属間化合物(IMC)に状態が遷移すると、融点が高くなり、弾性率が高くなることも知られている。しかし、脆いlow−k層へかかってしまう応力の負担を考えると、弾性率が高くなることは必ずしも好ましいことではない。

【0028】

図2は、混合材料の弾性率(ヤング率)について説明する図である。

【0029】

図2(A)のように、母体がすず(Sn)から成るはんだバンプを考え、銅(Cu)から成る金属パッドを考える。すると、これらの混合材料(C)または金属間化合物(IMC)は、Cu−Sn系金属間化合物(Cu3Sn、Cu6Sn5)ということになる。また、フィラー(f)については、シリカ(SiO2)を考える。

【0030】

図2(B)は、混合材料の弾性率を計算する計算式である。

【0031】

図2(C)は、混合材料の各材料の機械的特性を表にしたものである。

【0032】

図2(D)は、フィラーの含有率による弾性率(ヤング率)の変化を示すグラフである。図2(B)の計算式に従って導出することができる。

【0033】

図3は、正方形シリコンチップ上に2次元アレイ状に配置された複数のはんだバンプを示す図である。図1(A)に示す積層体の平面図に相当する。

【0034】

図3(A)では、はんだバンプの数を誇張してかなり少なめに模式的に描いているが、実際には、非常に多数にわたる微細なはんだバンプが、2次元平面にわたってアレイ状に並んでいる。

【0035】

本発明では、図3(B)のように、複数のはんだを2次元アレイ状に配置するにあたって、正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された複数のはんだバンプについては、弾性率が相対的に低くなるようにフィラーを入れて調整されたはんだバンプにする、

【0036】

「所定の割合」は、シリコンチップの幅(サイズ)すなわち辺と辺とを結ぶ距離を100%(パーセント)とした場合の、x(エックス)%(パーセント)を示す(部分的な)領域として表現することができる。

【0037】

図4は、本発明の効果を検証するために、有限要素法(FEM)によるシミュレーションをするモデルを説明する図である。

【0038】

図4に説明している通りの、寸法(サイズ、スケール)、条件をもってモデリングして、シミュレーション(数値実験)を行っている。

【0039】

図5は、有限要素法(FEM)によるシミュレーションの結果を示す図である。

【0040】

シリコンチップ上にかかる応力を軽減する目的に沿って、通常のはんだバンプを用いてシリコンチップ上にかかる最大応力を100と正規化した場合に対し、フィラー入りのはんだバンプを用いていくと、相対的な最大応力が減っていくことが読み取れる。

【0041】

図6は、本発明を適用した、有限要素法(FEM)によるシミュレーションの結果を示す図である。

【0042】

3種類のチップサイズについて、図3(B)のようにフィラー入りバンプを、部分的に異なるはんだバンプとして配置した結果、辺から35%の領域まで(より好ましくは、辺から25%の領域まで)フィラー入りバンプを使用すれば、最大応力を20%まで下げることが可能であることがわかった。

【0043】

したがって、3.0mm〜20mm程度の範囲内(検証できている最大の範囲としては12.6mmであるが、それ以上の範囲については十分適用可能と類推できる)のチップサイズに有効であることが検証できている。

【技術分野】

【0001】

本発明は、複数のはんだバンプによって接合を形成する積層体および製造方法に関する。より詳しくは、シリコンチップ上にかかる応力を軽減することを目的として、複数のはんだバンプから成るアレイにおいて、部分的に異なるはんだバンプを用いるアレイ配置上の工夫に関する。

【背景技術】

【0002】

3次元集積化技術では、入出力(I/O))数の増加に伴って、はんだバンプ(はんだボール)の微細化(例えば、5μm〜40μm径)が進んでいる。

【0003】

寄生容量を減らす目的で、LSIの層間の絶縁膜にはlow−k(低い誘電率)材料が使われる。この絶縁膜によって、半導体チップの配線層(BEOL)を絶縁する。

【0004】

最先端のLSIでは、層間絶縁膜に機械的強度の低い(脆い)low−k材料(さらに低誘電率のULKを含む。)が用いられることが多くなっており、低応力のはんだバンプ接続(接合)が求められている。

【0005】

特許文献1は、フィラー入りのはんだを使用して、接合部分近傍のクラックの発生を防止することについて説明している。

【0006】

しかし、特許文献1がはんだバンプ単体における工夫である点で、本発明とは大きく異なる。

【0007】

また、特許文献1においては、はんだバンプ単体の中においても、接合箇所だけにフィラーであるシリカが集中しすぎている点で、溶融と硬化のプロセスを通じての安定性に疑問が残る。

【0008】

本発明が対象としているはんだバンプに比較すると、特許文献1が対象としているはんだバンプは、サイズ、スケールともに大きいものである。

【0009】

特許文献1の方法に従って、本発明が対象としているような微細化の進んだ小さいスケールのはんだバンプの溶融後の硬化の処理を行おうとすると、金属間化合物(IMC)が形成され易く、より弾性率の高い材料へと変化してしまうこともある。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2010−219507号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明の目的は、シリコンチップの層間絶縁膜に機械的強度の低い(脆い)low−k材料が用いられる構造においても、シリコンチップ上にかかる応力を軽減するような低応力のはんだバンプ接続を実現することにある。

【課題を解決するための手段】

【0012】

正方形シリコンチップ(厚さ725μm)とラミネート層(厚さ1000μm)とが、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を介して、正方形シリコンチップとラミネート層との間に2次元アレイ状に配置された複数のはんだバンプの溶融後の硬化により接続されている、積層体として、

正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された部分的な複数のはんだバンプについては、他の部分の複数のはんだバンプよりも弾性率が相対的に低くなるようにフィラーを入れて調整されている、ことを特徴とするものである。

【発明の効果】

【0013】

最大応力を20%まで下げることが可能である。

【図面の簡単な説明】

【0014】

【図1】図1は、はんだバンプによる積層体の構造と、その製造プロセスを示す模式図である。

【図2】図2は、混合材料の弾性率(ヤング率)について説明する図である。

【図3】図3は、正方形シリコンチップ上に2次元アレイ状に配置された複数のはんだバンプを示す図である。

【図4】図4は、本発明の効果を検証するために、有限要素法(FEM)によるシミュレーションをするモデルを説明する図である。

【図5】図5は、有限要素法(FEM)によるシミュレーションの結果を示す図である。

【図6】図6は、本発明を適用した、有限要素法(FEM)によるシミュレーションの結果を示す図である。

【発明を実施するための形態】

【0015】

図1は、はんだバンプによる積層体の構造と、その製造プロセスを示す模式図である。

図1(A)は、積層体の側面図である。サイズ、スケールともに誇張して描かれている部分があることに留意されたい。

【0016】

ラミネート層(厚さt=1000μm)の上に、シリコンチップ(厚さt=725μm)が3次元的に積層されているが、これらの間には複数のはんだバンプが配置されている。実際には、シリコンチップは、ほとんどの場合、(上から見ると)正方形であるが、ここでは側面図であるので、正方形であることまでは分からない。

【0017】

図1(B)は、ひとつのはんだバンプ付近の構造を拡大した模式図である。

【0018】

ラミネート層の上には金属パッドが設けられている。はんだバンプが溶融後に硬化することによって、はんだバンプと金属パッドとの間が機械的かつ電気的に接合される。

【0019】

シリコンチップ上の配置は特徴的であり、low-k層という絶縁層が設けられている。これは配線層(BEOL)の絶縁層であり、このlow-k層を介して金属パッドが設けられている。

【0020】

この図では、はんだバンプはシリコンチップ側の金属パッド上に(予め)配置されているが、はんだバンプがラミネート層側の金属パッド上に(予め)配置されるような態様であってもよい。

【0021】

はんだバンプは、はんだボール等として別体として提供される場合もある。

【0022】

積層させていくプロセスは、積層体の製造方法として具現化することもできる。積層体を製造する前準備として、はんだバンプを配置する方法としても特徴がある。

【0023】

図1(C)は、はんだバンプの弾性率(ヤング率)をフィラーを入れて調整すること、および、はんだバンプの溶融後の硬化によって生じうる現象を説明する模式図である。

【0024】

母体(m:matrix)のはんだバンプの弾性率をEmとすると、フィラー(f:filler)を入れて調整された弾性率Efは、Ef<Emの関係となる。

【0025】

混合材料(c:composite)としての、はんだバンプ+フィラーは、Ec<Emであるが、線膨張係数(CTE)も母体のはんだバンプよりも小さい。

【0026】

はんだバンプを溶融させて硬化させるプロセスを経ると、はんだバンプと金属パッドとの間で金属間化合物(IMC)が形成されてしまうこともある。

【0027】

金属間化合物(IMC)に状態が遷移すると、融点が高くなり、弾性率が高くなることも知られている。しかし、脆いlow−k層へかかってしまう応力の負担を考えると、弾性率が高くなることは必ずしも好ましいことではない。

【0028】

図2は、混合材料の弾性率(ヤング率)について説明する図である。

【0029】

図2(A)のように、母体がすず(Sn)から成るはんだバンプを考え、銅(Cu)から成る金属パッドを考える。すると、これらの混合材料(C)または金属間化合物(IMC)は、Cu−Sn系金属間化合物(Cu3Sn、Cu6Sn5)ということになる。また、フィラー(f)については、シリカ(SiO2)を考える。

【0030】

図2(B)は、混合材料の弾性率を計算する計算式である。

【0031】

図2(C)は、混合材料の各材料の機械的特性を表にしたものである。

【0032】

図2(D)は、フィラーの含有率による弾性率(ヤング率)の変化を示すグラフである。図2(B)の計算式に従って導出することができる。

【0033】

図3は、正方形シリコンチップ上に2次元アレイ状に配置された複数のはんだバンプを示す図である。図1(A)に示す積層体の平面図に相当する。

【0034】

図3(A)では、はんだバンプの数を誇張してかなり少なめに模式的に描いているが、実際には、非常に多数にわたる微細なはんだバンプが、2次元平面にわたってアレイ状に並んでいる。

【0035】

本発明では、図3(B)のように、複数のはんだを2次元アレイ状に配置するにあたって、正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された複数のはんだバンプについては、弾性率が相対的に低くなるようにフィラーを入れて調整されたはんだバンプにする、

【0036】

「所定の割合」は、シリコンチップの幅(サイズ)すなわち辺と辺とを結ぶ距離を100%(パーセント)とした場合の、x(エックス)%(パーセント)を示す(部分的な)領域として表現することができる。

【0037】

図4は、本発明の効果を検証するために、有限要素法(FEM)によるシミュレーションをするモデルを説明する図である。

【0038】

図4に説明している通りの、寸法(サイズ、スケール)、条件をもってモデリングして、シミュレーション(数値実験)を行っている。

【0039】

図5は、有限要素法(FEM)によるシミュレーションの結果を示す図である。

【0040】

シリコンチップ上にかかる応力を軽減する目的に沿って、通常のはんだバンプを用いてシリコンチップ上にかかる最大応力を100と正規化した場合に対し、フィラー入りのはんだバンプを用いていくと、相対的な最大応力が減っていくことが読み取れる。

【0041】

図6は、本発明を適用した、有限要素法(FEM)によるシミュレーションの結果を示す図である。

【0042】

3種類のチップサイズについて、図3(B)のようにフィラー入りバンプを、部分的に異なるはんだバンプとして配置した結果、辺から35%の領域まで(より好ましくは、辺から25%の領域まで)フィラー入りバンプを使用すれば、最大応力を20%まで下げることが可能であることがわかった。

【0043】

したがって、3.0mm〜20mm程度の範囲内(検証できている最大の範囲としては12.6mmであるが、それ以上の範囲については十分適用可能と類推できる)のチップサイズに有効であることが検証できている。

【特許請求の範囲】

【請求項1】

正方形シリコンチップ(厚さ725μm)とラミネート層(厚さ1000μm)とが、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を介して、正方形シリコンチップとラミネート層との間に2次元アレイ状に配置された複数のはんだバンプの溶融後の硬化により接続されている、積層体であって、

正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された部分的な複数のはんだバンプについては、他の部分の複数のはんだバンプよりも弾性率が相対的に低くなるようにフィラーを入れて調整されていることを特徴とする、

積層体。

【請求項2】

正方形シリコンチップの辺の長さ(チップサイズ)が、3.0mm〜20mm程度の範囲内であることを特徴とする、

請求項1に記載の積層体。

【請求項3】

所定の割合が、辺の外周から、辺の長さを100パーセントとした場合の、辺の長さの35パーセントを示す領域であることを特徴とする、

請求項1に記載の積層体。

【請求項4】

所定の割合が、辺の外周から、辺の長さを100パーセントとした場合の、辺の長さの25パーセントを示す領域であることを特徴とする、

請求項1に記載の積層体。

【請求項5】

積層体の製造方法であって、

ラミネート層(厚さ1000μm)を用意するステップと、

ラミネート層上に、複数のはんだを2次元アレイ状に配置するステップであって、正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された複数のはんだバンプについては、弾性率が相対的に低くなるようにフィラーを入れて調整されたはんだバンプにする、配置するステップと、

正方形シリコンチップ(厚さ725μm)を、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を複数のはんだバンプに向けて、複数のはんだバンプを覆うステップと、

複数のはんだバンプを溶融させるステップと、

複数のはんだバンプを硬化させるステップとを有する、

方法。

【請求項6】

請求項5に記載の製造方法で製造された、積層体。

【請求項7】

はんだバンプを配置する方法であって、

ラミネート層(厚さ1000μm)または正方形シリコンチップ(厚さ725μm)を用意するステップと、

ラミネート層上に、または、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を複数のはんだバンプに向けて、複数のはんだを2次元アレイ状に配置するステップであって、正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された複数のはんだバンプについては、弾性率が相対的に低くなるようにフィラーを入れて調整されたはんだバンプにする、配置するステップとを有する、

方法。

【請求項1】

正方形シリコンチップ(厚さ725μm)とラミネート層(厚さ1000μm)とが、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を介して、正方形シリコンチップとラミネート層との間に2次元アレイ状に配置された複数のはんだバンプの溶融後の硬化により接続されている、積層体であって、

正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された部分的な複数のはんだバンプについては、他の部分の複数のはんだバンプよりも弾性率が相対的に低くなるようにフィラーを入れて調整されていることを特徴とする、

積層体。

【請求項2】

正方形シリコンチップの辺の長さ(チップサイズ)が、3.0mm〜20mm程度の範囲内であることを特徴とする、

請求項1に記載の積層体。

【請求項3】

所定の割合が、辺の外周から、辺の長さを100パーセントとした場合の、辺の長さの35パーセントを示す領域であることを特徴とする、

請求項1に記載の積層体。

【請求項4】

所定の割合が、辺の外周から、辺の長さを100パーセントとした場合の、辺の長さの25パーセントを示す領域であることを特徴とする、

請求項1に記載の積層体。

【請求項5】

積層体の製造方法であって、

ラミネート層(厚さ1000μm)を用意するステップと、

ラミネート層上に、複数のはんだを2次元アレイ状に配置するステップであって、正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された複数のはんだバンプについては、弾性率が相対的に低くなるようにフィラーを入れて調整されたはんだバンプにする、配置するステップと、

正方形シリコンチップ(厚さ725μm)を、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を複数のはんだバンプに向けて、複数のはんだバンプを覆うステップと、

複数のはんだバンプを溶融させるステップと、

複数のはんだバンプを硬化させるステップとを有する、

方法。

【請求項6】

請求項5に記載の製造方法で製造された、積層体。

【請求項7】

はんだバンプを配置する方法であって、

ラミネート層(厚さ1000μm)または正方形シリコンチップ(厚さ725μm)を用意するステップと、

ラミネート層上に、または、正方形シリコンチップ上に配置されているところのlow-k層(配線層(BEOL)の絶縁層)を複数のはんだバンプに向けて、複数のはんだを2次元アレイ状に配置するステップであって、正方形シリコンチップ(の4つの辺に相当する)外周から所定の割合まで内側にわたって配置された複数のはんだバンプについては、弾性率が相対的に低くなるようにフィラーを入れて調整されたはんだバンプにする、配置するステップとを有する、

方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−105951(P2013−105951A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−249848(P2011−249848)

【出願日】平成23年11月15日(2011.11.15)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構、立体構造新機能集積回路(ドリームチップ)技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月15日(2011.11.15)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構、立体構造新機能集積回路(ドリームチップ)技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【Fターム(参考)】

[ Back to top ]