複数のチップ間の高精度アライメントに利用するスタッドの組合せの作成

【課題】 複数のチップ間または基板とチップとの間に期待される高精度アライメントを実現すること。

【解決手段】 複数のチップ間においてはんだバンプが溶融した場合に、複数のチップ同士の横方向の相対的な動きを規制する複数のスタッドの組合せが作成される。複数のチップ同士が複数のはんだバンプの溶融によって相対的に移動した場合であっても、相対的な動きが規制されて、複数のチップのそれぞれに設定された複数のはんだバンプ同士が所定の範囲内に整列するように、複数のチップ間に配置される複数のはんだバンプのピッチに従って配置されているところの任意のはんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せが、複数のチップのそれぞれに作成される。

【解決手段】 複数のチップ間においてはんだバンプが溶融した場合に、複数のチップ同士の横方向の相対的な動きを規制する複数のスタッドの組合せが作成される。複数のチップ同士が複数のはんだバンプの溶融によって相対的に移動した場合であっても、相対的な動きが規制されて、複数のチップのそれぞれに設定された複数のはんだバンプ同士が所定の範囲内に整列するように、複数のチップ間に配置される複数のはんだバンプのピッチに従って配置されているところの任意のはんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せが、複数のチップのそれぞれに作成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、層間の電気的機械的接合に関する。より具体的には、複数のチップを2次元実装または3次元実装するにあたってのチップ間または基板とチップとの間に期待される高精度アライメントに関する。

【背景技術】

【0002】

フリップチップボンディングは、チップ上にはんだバンプなどの接合用の溶融金属を介在させて、その面をパッケージ基板に合わせて接続するという、面実装タイプのボンディング方法である。

【0003】

チップの全面を接合に使えるというメリットがあるため、端子数が多くかつチップ面積が小さい集積回路において、よく利用されている。

【0004】

しかし、リワークが困難であるために、高い実装品質が求められる。

【0005】

フリップチップでは、チップ上に多数のはんだバンプが配置されるために、はんだバンプ間のピッチが非常に狭くなるファインピッチ化が進んでおり、高い実装品質を確保することが難しくなってきている。

【0006】

図1は、フリップチップボンディングのプロセスフローにおいて、実装品質に影響してしまう外的要因を、2次元実装を例にして説明する図である。

【0007】

図1の(A)で示すように、チップ(基板)の上にフラックスが適用され、その上に(ここでは2つの)はんだバンプが配置され、それらのはんだバンプの上にチップ、チップの上には部品、というように搭載した状態(未だ接合は完了していない状態)を示している。

【0008】

フラックスは、はんだバンプを基板上の金属パッド等とはんだ付けするために、酸化膜などを除去するためのものである。

【0009】

この例のようなフラックス上のはんだバンプ(等の部品)は、フリップチップボンディングの場合、はんだ付けが完了するまでの間、フラックスの接着剤的な働きに期待して、フラックスの粘性(粘着力)のみで保持される。

【0010】

しかし、はんだを溶融させるべく加温するに伴い、フラックスの粘度は(通常)低くなり、はんだバンプ(等の部品)を保持する力が弱まってしまう。

【0011】

図1の(B)で示すように、フリップチップボンディングのために、フリップチップを基板上に搭載(マウント)する。

【0012】

しかし、図1の(C2)で示すように、目標とする成功例には至らずに、図1の(C1)で示すような搭載ズレのある失敗例に至ってしまうことがある。

【0013】

そもそもフリップチップボンディングにおいては、図1の(D1)で説明するように、チップを多段に搭載した状態を維持する必要性から、通常は、一定の圧力を加えておく必要がある。

【0014】

さらには、一定の圧力が加えられていることだけでなく、図1の(D2)で説明するように、振動や循環風(例えば、溶融したはんだチップの冷却等のため)など様々な外的要因によって、搭載ズレの失敗に至ることもある。

【0015】

図1の(E)に示すように、最終的な搭載ズレは、はんだバンプと基板上の金属パッドとの機械的接合および電気的接合について、接続不良を生じる。

【0016】

図2は、フリップチップボンディングのプロセスフローにおいて、実装品質に影響してしまう外的要因を、3次元実装を例にして説明する図である。

【0017】

図1の2次元実装に比較して、図2の3次元実装では、3枚のチップが積層されているため、3枚のうちの中間のチップが搭載ズレを起こしてしまうと、接続不良が、上側のチップと、下側のチップとの両方に及んでしまうことになり、より一層、高い実装品質を確保することが難しくなる。

【0018】

図3は、ピックアンドプレースのプロセスフローにおいて、実装品質に影響してしまう外的要因を、3次元実装における2段階の積層を例にして説明する図である。

【0019】

1段階目の積層において搭載ズレを起こさないことにに成功したとしても、後のプロセスである2段階目の積層において、成功している1段階目の積層の搭載ズレを起こしてしまうことがあることを、説明している。

【0020】

特許文献1は、優先溶融はんだの表面張力を利用した復元力の作用により、接合のセルフアライメント(位置決め)を利用する技術を開示している。しかし、表面張力に期待できるセルフアライメントの精度には限界がある。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】特開2006−12833号公報

【発明の概要】

【発明が解決しようとする課題】

【0022】

本発明の目的は、複数のチップ間または基板とチップとの間に期待される高精度アライメントを実現することにある。

【課題を解決するための手段】

【0023】

複数のチップ間においてはんだバンプが溶融した場合に、複数のチップ同士の横方向の相対的な動きを規制する複数のスタッドの組合せを作成する。

【0024】

複数のチップを用意して、複数のチップに配置される複数のはんだバンプについて、それらを配置させるピッチを設定する。

【0025】

複数のチップ同士が複数のはんだバンプの溶融によって相対的に移動した場合であっても、相対的な動きが規制されて、複数のチップのそれぞれに設定された複数のはんだバンプ同士が所定の範囲内に整列するように、それらを配置させるピッチに従って配置されているところの特定のはんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せを、複数のチップのそれぞれに作成する。

【発明の効果】

【0026】

複数のチップ間または基板とチップとの間に期待される高精度アライメントが実現する。

【図面の簡単な説明】

【0027】

【図1】図1は、フリップチップボンディングのプロセスフローにおいて、実装品質に影響してしまう外的要因を、2次元実装を例にして説明する図である。

【図2】図2は、フリップチップボンディングのプロセスフローにおいて、実装品質に影響してしまう外的要因を、3次元実装を例にして説明する図である。

【図3】図3は、ピックアンドプレースのプロセスフローにおいて、実装品質に影響してしまう外的要因を、3次元実装における2段階の積層を例にして説明する図である。

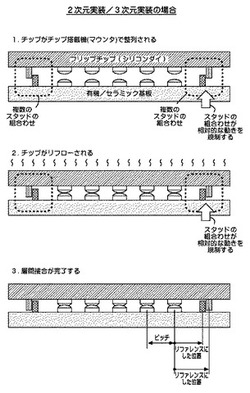

【図4】図4は、高精度アライメントに利用するスタッドの組合せを利用した、本発明のフリップチップボンディングのプロセスフロー(2次元実装/3次元実装の場合)を説明する図である。

【図5】図5は、高精度アライメントに利用するスタッドの組合せを利用した、本発明のフリップチップボンディングのプロセスフロー(3次元実装の場合)を説明する図である。

【図6】図6は、複数のスタッドの組合せの応用例(平面を利用した発展態様)を示す平面図である。

【図7】図7は、複数のスタッドの組合せについてのバリエーションを示す図である。

【発明を実施するための形態】

【0028】

図4は、高精度アライメントに利用するスタッドの組合せを利用した、本発明のフリップチップボンディングのプロセスフロー(2次元実装/3次元実装の場合)を説明する図である。

【0029】

本発明は、複数のチップ間、あるいはチップと基板間において、はんだバンプが溶融した場合に、複数のチップ同士、あるいはチップと基板の(紙面から見た)横方向の相対的な動きを規制する複数のスタッドの組合せを作成しておくことに特徴がある。

【0030】

複数のチップ(この図4では、チップと有機/セラミック基板)の上にフリップチップ(シリコンダイ)を用意する。プロセスフローとして、1.チップがチップ搭載機(マウンタ)で整列される。

【0031】

このような整列(アライメント)は、複数のスタッドの組合せに与えられているクリアランスを利用して高精度に行う必要がある。ただし、一旦、搭載が完了すると、複数のスタッドの組合せには、相対的な動きを規制する作用がある。

【0032】

次に、2.チップがリフローされる。複数のはんだバンプを溶融させるためである。複数のはんだバンプを溶融させると、チップと基板同士が表面張力の作用に従って横方向に相対的に移動する。

【0033】

しかし、このような相対的な移動が生じたところで、複数のスタッドの組合せによって、相対的な動きが規制される作用がある。

【0034】

溶融していたはんだバンプが(冷却によって)固化すると、3.層間結合が完了する。すなわち、層間の電気的機械的結合が完了する。

【0035】

しかし、複数のスタッドの組合せで期待できるところの、複数のチップのそれぞれに設定された複数のはんだバンプ同士の整列は、複数のスタッドの組合せに(設計上)与えられているクリアランスに依存することにはなるが、所定の範囲内に整列できる。

【0036】

設計において、複数のはんだバンプを配置するピッチを設定して、配置されているところの特定の(もちろん、ピッチに従っているのであれば、任意のものでもよい)はんだバンプをリファレンスにして、複数のスタッドの組合せの位置を決めればよい。

【0037】

「リファレンスにして」位置を決めれば、設計上または作成上において同一の基準位置を利用することができ、設計誤差、作成公差等の累積を抑えることができる。

【0038】

通常は、複数のスタッドの組合せの一方についての中心位置を定め、その中心位置において所定の幅(W)を設定することになろう。もっとも、複数のスタッドは、組合せとしてこそ相対的な動きを規制する作用を発揮できるものであるため、図7において「W(幅)」と記載されている箇所が、複数のスタッド同士の接触によって、ほぼ互いの相対的な動きを作用する箇所となることであろう。

【0039】

図5は、高精度アライメントに利用するスタッドの組合せを利用した、本発明のフリップチップボンディングのプロセスフロー(3次元実装の場合)を説明する図である。

【0040】

図4で説明した内容で、1段階目の積層が完了すれば、2段階目の積層も同様に進めることができ、図2で説明したような接続不良を生じにくくすることができる。

【0041】

図6は、複数のスタッドの組合せの応用例(平面を利用した発展態様)を示す平面図である。

【0042】

ここでは、1枚のチップ側のみの平面内において、複数のはんだバンプがアレイ状に配置されていることを模式的に示している。

【0043】

複数のスタッドの組合せは、下側のチップと上側のチップとにそれぞれ分かれて作成されるものであるが、ここでは、下側のチップと、下側のチップに作成される複数のスタッドの組合せの一方と、上側のチップに作成される複数のスタッドの組合せの他方のみ、を示している。

【0044】

この平面図のように複数のはんだバンプが平面に分布していても、はんだバンプを配置させるピッチに従って、配置されているところの特定の(または任意の)はんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せを、複数のチップのそれぞれに作成すればよい。

【0045】

図7は、複数のスタッドの組合せについてのバリエーションを示す図である。

【0046】

図7の(A)のように、複数のスタッドの組合せが、金(Au)から成るスタッドバンプまたは銅(Cu)から成るスタッドバンプであってもよい。

【0047】

その場合、複数のスタッドの組合せが、はんだバンプの溶融後に作成されればよい。

【0048】

図7の(B)のように、複数のスタッドの組合せは、はんだバンプであってもよい。

【0049】

その場合、複数のスタッドの組合せが、はんだバンプの溶融後において、溶融されたはんだがインジェクションで塗布されるものであってもよい。

【0050】

図7の(C)のように、複数のスタッドの組合せが、金(Au)または銅(Cu)から成る、ポールまたはウォールであってもよい。

【0051】

その場合、複数のスタッドの組合せが、インクジェットプリンタによるナノペーストの塗布によって形成されればよい。

【0052】

かかるナノジェットプリンティングの技術を応用すれば、±1μm以下の精度でもって、高さ(h)方向に均一な幅が続くスタッドを、実現できる。複数のスタッドの組合せ同士が接触する横方向位置が、高さ(h)方向のどの箇所においても一定になるという点では、図7の(A)や図7の(B)よりは有利である。

【0053】

この他にも、この発明の属する技術の分野における通常の知識を有する者であるならば、図7の(A)(B)(C)に記載されている各スタッドを、任意に組合せて利用することもできるであろう。

【技術分野】

【0001】

本発明は、層間の電気的機械的接合に関する。より具体的には、複数のチップを2次元実装または3次元実装するにあたってのチップ間または基板とチップとの間に期待される高精度アライメントに関する。

【背景技術】

【0002】

フリップチップボンディングは、チップ上にはんだバンプなどの接合用の溶融金属を介在させて、その面をパッケージ基板に合わせて接続するという、面実装タイプのボンディング方法である。

【0003】

チップの全面を接合に使えるというメリットがあるため、端子数が多くかつチップ面積が小さい集積回路において、よく利用されている。

【0004】

しかし、リワークが困難であるために、高い実装品質が求められる。

【0005】

フリップチップでは、チップ上に多数のはんだバンプが配置されるために、はんだバンプ間のピッチが非常に狭くなるファインピッチ化が進んでおり、高い実装品質を確保することが難しくなってきている。

【0006】

図1は、フリップチップボンディングのプロセスフローにおいて、実装品質に影響してしまう外的要因を、2次元実装を例にして説明する図である。

【0007】

図1の(A)で示すように、チップ(基板)の上にフラックスが適用され、その上に(ここでは2つの)はんだバンプが配置され、それらのはんだバンプの上にチップ、チップの上には部品、というように搭載した状態(未だ接合は完了していない状態)を示している。

【0008】

フラックスは、はんだバンプを基板上の金属パッド等とはんだ付けするために、酸化膜などを除去するためのものである。

【0009】

この例のようなフラックス上のはんだバンプ(等の部品)は、フリップチップボンディングの場合、はんだ付けが完了するまでの間、フラックスの接着剤的な働きに期待して、フラックスの粘性(粘着力)のみで保持される。

【0010】

しかし、はんだを溶融させるべく加温するに伴い、フラックスの粘度は(通常)低くなり、はんだバンプ(等の部品)を保持する力が弱まってしまう。

【0011】

図1の(B)で示すように、フリップチップボンディングのために、フリップチップを基板上に搭載(マウント)する。

【0012】

しかし、図1の(C2)で示すように、目標とする成功例には至らずに、図1の(C1)で示すような搭載ズレのある失敗例に至ってしまうことがある。

【0013】

そもそもフリップチップボンディングにおいては、図1の(D1)で説明するように、チップを多段に搭載した状態を維持する必要性から、通常は、一定の圧力を加えておく必要がある。

【0014】

さらには、一定の圧力が加えられていることだけでなく、図1の(D2)で説明するように、振動や循環風(例えば、溶融したはんだチップの冷却等のため)など様々な外的要因によって、搭載ズレの失敗に至ることもある。

【0015】

図1の(E)に示すように、最終的な搭載ズレは、はんだバンプと基板上の金属パッドとの機械的接合および電気的接合について、接続不良を生じる。

【0016】

図2は、フリップチップボンディングのプロセスフローにおいて、実装品質に影響してしまう外的要因を、3次元実装を例にして説明する図である。

【0017】

図1の2次元実装に比較して、図2の3次元実装では、3枚のチップが積層されているため、3枚のうちの中間のチップが搭載ズレを起こしてしまうと、接続不良が、上側のチップと、下側のチップとの両方に及んでしまうことになり、より一層、高い実装品質を確保することが難しくなる。

【0018】

図3は、ピックアンドプレースのプロセスフローにおいて、実装品質に影響してしまう外的要因を、3次元実装における2段階の積層を例にして説明する図である。

【0019】

1段階目の積層において搭載ズレを起こさないことにに成功したとしても、後のプロセスである2段階目の積層において、成功している1段階目の積層の搭載ズレを起こしてしまうことがあることを、説明している。

【0020】

特許文献1は、優先溶融はんだの表面張力を利用した復元力の作用により、接合のセルフアライメント(位置決め)を利用する技術を開示している。しかし、表面張力に期待できるセルフアライメントの精度には限界がある。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】特開2006−12833号公報

【発明の概要】

【発明が解決しようとする課題】

【0022】

本発明の目的は、複数のチップ間または基板とチップとの間に期待される高精度アライメントを実現することにある。

【課題を解決するための手段】

【0023】

複数のチップ間においてはんだバンプが溶融した場合に、複数のチップ同士の横方向の相対的な動きを規制する複数のスタッドの組合せを作成する。

【0024】

複数のチップを用意して、複数のチップに配置される複数のはんだバンプについて、それらを配置させるピッチを設定する。

【0025】

複数のチップ同士が複数のはんだバンプの溶融によって相対的に移動した場合であっても、相対的な動きが規制されて、複数のチップのそれぞれに設定された複数のはんだバンプ同士が所定の範囲内に整列するように、それらを配置させるピッチに従って配置されているところの特定のはんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せを、複数のチップのそれぞれに作成する。

【発明の効果】

【0026】

複数のチップ間または基板とチップとの間に期待される高精度アライメントが実現する。

【図面の簡単な説明】

【0027】

【図1】図1は、フリップチップボンディングのプロセスフローにおいて、実装品質に影響してしまう外的要因を、2次元実装を例にして説明する図である。

【図2】図2は、フリップチップボンディングのプロセスフローにおいて、実装品質に影響してしまう外的要因を、3次元実装を例にして説明する図である。

【図3】図3は、ピックアンドプレースのプロセスフローにおいて、実装品質に影響してしまう外的要因を、3次元実装における2段階の積層を例にして説明する図である。

【図4】図4は、高精度アライメントに利用するスタッドの組合せを利用した、本発明のフリップチップボンディングのプロセスフロー(2次元実装/3次元実装の場合)を説明する図である。

【図5】図5は、高精度アライメントに利用するスタッドの組合せを利用した、本発明のフリップチップボンディングのプロセスフロー(3次元実装の場合)を説明する図である。

【図6】図6は、複数のスタッドの組合せの応用例(平面を利用した発展態様)を示す平面図である。

【図7】図7は、複数のスタッドの組合せについてのバリエーションを示す図である。

【発明を実施するための形態】

【0028】

図4は、高精度アライメントに利用するスタッドの組合せを利用した、本発明のフリップチップボンディングのプロセスフロー(2次元実装/3次元実装の場合)を説明する図である。

【0029】

本発明は、複数のチップ間、あるいはチップと基板間において、はんだバンプが溶融した場合に、複数のチップ同士、あるいはチップと基板の(紙面から見た)横方向の相対的な動きを規制する複数のスタッドの組合せを作成しておくことに特徴がある。

【0030】

複数のチップ(この図4では、チップと有機/セラミック基板)の上にフリップチップ(シリコンダイ)を用意する。プロセスフローとして、1.チップがチップ搭載機(マウンタ)で整列される。

【0031】

このような整列(アライメント)は、複数のスタッドの組合せに与えられているクリアランスを利用して高精度に行う必要がある。ただし、一旦、搭載が完了すると、複数のスタッドの組合せには、相対的な動きを規制する作用がある。

【0032】

次に、2.チップがリフローされる。複数のはんだバンプを溶融させるためである。複数のはんだバンプを溶融させると、チップと基板同士が表面張力の作用に従って横方向に相対的に移動する。

【0033】

しかし、このような相対的な移動が生じたところで、複数のスタッドの組合せによって、相対的な動きが規制される作用がある。

【0034】

溶融していたはんだバンプが(冷却によって)固化すると、3.層間結合が完了する。すなわち、層間の電気的機械的結合が完了する。

【0035】

しかし、複数のスタッドの組合せで期待できるところの、複数のチップのそれぞれに設定された複数のはんだバンプ同士の整列は、複数のスタッドの組合せに(設計上)与えられているクリアランスに依存することにはなるが、所定の範囲内に整列できる。

【0036】

設計において、複数のはんだバンプを配置するピッチを設定して、配置されているところの特定の(もちろん、ピッチに従っているのであれば、任意のものでもよい)はんだバンプをリファレンスにして、複数のスタッドの組合せの位置を決めればよい。

【0037】

「リファレンスにして」位置を決めれば、設計上または作成上において同一の基準位置を利用することができ、設計誤差、作成公差等の累積を抑えることができる。

【0038】

通常は、複数のスタッドの組合せの一方についての中心位置を定め、その中心位置において所定の幅(W)を設定することになろう。もっとも、複数のスタッドは、組合せとしてこそ相対的な動きを規制する作用を発揮できるものであるため、図7において「W(幅)」と記載されている箇所が、複数のスタッド同士の接触によって、ほぼ互いの相対的な動きを作用する箇所となることであろう。

【0039】

図5は、高精度アライメントに利用するスタッドの組合せを利用した、本発明のフリップチップボンディングのプロセスフロー(3次元実装の場合)を説明する図である。

【0040】

図4で説明した内容で、1段階目の積層が完了すれば、2段階目の積層も同様に進めることができ、図2で説明したような接続不良を生じにくくすることができる。

【0041】

図6は、複数のスタッドの組合せの応用例(平面を利用した発展態様)を示す平面図である。

【0042】

ここでは、1枚のチップ側のみの平面内において、複数のはんだバンプがアレイ状に配置されていることを模式的に示している。

【0043】

複数のスタッドの組合せは、下側のチップと上側のチップとにそれぞれ分かれて作成されるものであるが、ここでは、下側のチップと、下側のチップに作成される複数のスタッドの組合せの一方と、上側のチップに作成される複数のスタッドの組合せの他方のみ、を示している。

【0044】

この平面図のように複数のはんだバンプが平面に分布していても、はんだバンプを配置させるピッチに従って、配置されているところの特定の(または任意の)はんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せを、複数のチップのそれぞれに作成すればよい。

【0045】

図7は、複数のスタッドの組合せについてのバリエーションを示す図である。

【0046】

図7の(A)のように、複数のスタッドの組合せが、金(Au)から成るスタッドバンプまたは銅(Cu)から成るスタッドバンプであってもよい。

【0047】

その場合、複数のスタッドの組合せが、はんだバンプの溶融後に作成されればよい。

【0048】

図7の(B)のように、複数のスタッドの組合せは、はんだバンプであってもよい。

【0049】

その場合、複数のスタッドの組合せが、はんだバンプの溶融後において、溶融されたはんだがインジェクションで塗布されるものであってもよい。

【0050】

図7の(C)のように、複数のスタッドの組合せが、金(Au)または銅(Cu)から成る、ポールまたはウォールであってもよい。

【0051】

その場合、複数のスタッドの組合せが、インクジェットプリンタによるナノペーストの塗布によって形成されればよい。

【0052】

かかるナノジェットプリンティングの技術を応用すれば、±1μm以下の精度でもって、高さ(h)方向に均一な幅が続くスタッドを、実現できる。複数のスタッドの組合せ同士が接触する横方向位置が、高さ(h)方向のどの箇所においても一定になるという点では、図7の(A)や図7の(B)よりは有利である。

【0053】

この他にも、この発明の属する技術の分野における通常の知識を有する者であるならば、図7の(A)(B)(C)に記載されている各スタッドを、任意に組合せて利用することもできるであろう。

【特許請求の範囲】

【請求項1】

複数のチップ間あるいはチップと基板との間においてはんだバンプが溶融した場合に、複数のチップ同士、あるいはチップと基板の横方向の相対的な動きを規制する複数のスタッドの組合せを作成する方法であって、

複数のチップを用意するステップと、

複数のチップに配置される複数のはんだバンプについて、それらを配置させるピッチを設定して、複数のチップ同士が複数のはんだバンプの溶融によって相対的に移動した場合であっても、相対的な動きが規制されて、複数のチップのそれぞれに設定された複数のはんだバンプ同士が所定の範囲内に整列するように、それらを配置させるピッチに従って配置されているところの特定のはんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せを、複数のチップのそれぞれに作成するステップとを有する、

方法。

【請求項2】

複数のスタッドの組合せが、金(Au)から成るスタッドバンプまたは銅(Cu)から成るスタッドバンプである、請求項1に記載の方法。

【請求項3】

複数のスタッドの組合せが、はんだバンプの溶融後に作成される、請求項2に記載の方法。

【請求項4】

複数のスタッドの組合せが、はんだバンプである、請求項1に記載の方法。

【請求項5】

複数のスタッドの組合せが、はんだバンプの溶融後において、溶融されたはんだがインジェクションで塗布される、請求項4に記載の方法。

【請求項6】

複数のスタッドの組合せが、金(Au)または銅(Cu)から成る、ポールまたはウォールである、請求項1に記載の方法。

【請求項7】

複数のスタッドの組合せが、インクジェットプリンタによるナノペーストの塗布によって形成される、請求項6に記載の方法。

【請求項8】

複数のチップ間あるいはチップと基板との間においてはんだバンプが溶融した場合に、複数のチップ同士、あるいはチップと基板の横方向の相対的な動きを規制する、複数のスタッドの組合せであって、

複数のチップ同士が複数のはんだバンプの溶融によって相対的に移動した場合であっても、相対的な動きが規制されて、複数のチップのそれぞれに設定された複数のはんだバンプ同士が所定の範囲内に整列するように、複数のチップ間に配置される複数のはんだバンプのピッチに従って配置されているところの任意のはんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せが、複数のチップのそれぞれに作成されている、

複数のスタッドの組合せ。

【請求項9】

請求項8に記載の複数のスタッドの組合せが作成されているところの、複数のチップについて、1段階目の積層として、これら複数のチップ同士を整列させる方法であって、

チップまたは基板の上に、複数のはんだバンプを配置するステップと、

複数のはんだバンプの上に、チップを搭載するステップと、

チップをリフローして、はんだバンプを溶融させるステップと、

はんだバンプを冷却させて固化させるステップとを有する、

方法。

【請求項10】

請求項9に記載の方法について、さらに、

チップを(2段階目の積層として)整列させる方法であって、

1段階目で積層されたチップの上に、さらに、

複数のはんだバンプを配置するステップと、

複数のはんだバンプの上に、チップを搭載するステップと、

チップをリフローして、はんだバンプを溶融させるステップと、

はんだバンプを冷却させて固化させるステップとを有する、

方法。

【請求項1】

複数のチップ間あるいはチップと基板との間においてはんだバンプが溶融した場合に、複数のチップ同士、あるいはチップと基板の横方向の相対的な動きを規制する複数のスタッドの組合せを作成する方法であって、

複数のチップを用意するステップと、

複数のチップに配置される複数のはんだバンプについて、それらを配置させるピッチを設定して、複数のチップ同士が複数のはんだバンプの溶融によって相対的に移動した場合であっても、相対的な動きが規制されて、複数のチップのそれぞれに設定された複数のはんだバンプ同士が所定の範囲内に整列するように、それらを配置させるピッチに従って配置されているところの特定のはんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せを、複数のチップのそれぞれに作成するステップとを有する、

方法。

【請求項2】

複数のスタッドの組合せが、金(Au)から成るスタッドバンプまたは銅(Cu)から成るスタッドバンプである、請求項1に記載の方法。

【請求項3】

複数のスタッドの組合せが、はんだバンプの溶融後に作成される、請求項2に記載の方法。

【請求項4】

複数のスタッドの組合せが、はんだバンプである、請求項1に記載の方法。

【請求項5】

複数のスタッドの組合せが、はんだバンプの溶融後において、溶融されたはんだがインジェクションで塗布される、請求項4に記載の方法。

【請求項6】

複数のスタッドの組合せが、金(Au)または銅(Cu)から成る、ポールまたはウォールである、請求項1に記載の方法。

【請求項7】

複数のスタッドの組合せが、インクジェットプリンタによるナノペーストの塗布によって形成される、請求項6に記載の方法。

【請求項8】

複数のチップ間あるいはチップと基板との間においてはんだバンプが溶融した場合に、複数のチップ同士、あるいはチップと基板の横方向の相対的な動きを規制する、複数のスタッドの組合せであって、

複数のチップ同士が複数のはんだバンプの溶融によって相対的に移動した場合であっても、相対的な動きが規制されて、複数のチップのそれぞれに設定された複数のはんだバンプ同士が所定の範囲内に整列するように、複数のチップ間に配置される複数のはんだバンプのピッチに従って配置されているところの任意のはんだバンプをリファレンスにした位置において、所定の幅を有する複数のスタッドの組合せが、複数のチップのそれぞれに作成されている、

複数のスタッドの組合せ。

【請求項9】

請求項8に記載の複数のスタッドの組合せが作成されているところの、複数のチップについて、1段階目の積層として、これら複数のチップ同士を整列させる方法であって、

チップまたは基板の上に、複数のはんだバンプを配置するステップと、

複数のはんだバンプの上に、チップを搭載するステップと、

チップをリフローして、はんだバンプを溶融させるステップと、

はんだバンプを冷却させて固化させるステップとを有する、

方法。

【請求項10】

請求項9に記載の方法について、さらに、

チップを(2段階目の積層として)整列させる方法であって、

1段階目で積層されたチップの上に、さらに、

複数のはんだバンプを配置するステップと、

複数のはんだバンプの上に、チップを搭載するステップと、

チップをリフローして、はんだバンプを溶融させるステップと、

はんだバンプを冷却させて固化させるステップとを有する、

方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−115135(P2013−115135A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−258013(P2011−258013)

【出願日】平成23年11月25日(2011.11.25)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構、立体構造新機能集積回路(ドリームチップ)技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構、立体構造新機能集積回路(ドリームチップ)技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【Fターム(参考)】

[ Back to top ]