解像度変換装置及び解像度変換方法

【課題】メモリ容量を削減しながら画質の劣化を抑える。

【解決手段】解像度変換回路200は、入力された画像データを格納するラインバッファ202,203と、ラインバッファ202,203に格納された画素データを含む計3画素を参照して垂直方向の補間画素Poを生成する際、補間画素Poの上2画素Pi1,Pi2と下1画素Pi3を参照する補間と補間画素Poの上1画素Pi2と下2画素Pi3,Pi4を参照する補間とをフレーム毎に切り替える3画素畳み込み演算回路208とを備える。

【解決手段】解像度変換回路200は、入力された画像データを格納するラインバッファ202,203と、ラインバッファ202,203に格納された画素データを含む計3画素を参照して垂直方向の補間画素Poを生成する際、補間画素Poの上2画素Pi1,Pi2と下1画素Pi3を参照する補間と補間画素Poの上1画素Pi2と下2画素Pi3,Pi4を参照する補間とをフレーム毎に切り替える3画素畳み込み演算回路208とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、解像度を変換する解像度変換装置及び解像度変換方法に関し、特に、液晶ディスプレイ装置などの解像度が一定の表示装置に搭載される解像度変換回路に関する。

【背景技術】

【0002】

表示装置には、解像度を向上させるための解像度変換回路が搭載されている。従来、この解像度変換回路としては、一般的に、良好な画質を得ることができるバイキュービック補間を用いた解像度変換回路が用いられている。

【0003】

バイキュービック補間では、出力画素位置に対応する入力画素位置の周辺の垂直方向4 画素、水平方向4画素を出力画素ごとに参照して画素を生成する。ここで、垂直方向におけるバイキュービック補間では、生成したい画素位置から上下2画素ずつ計4画素を参照する。すなわち、図8に示すように、生成したい画素を補間画素Poとすると、参照画素は2ライン上の入力画素Pi1、1ライン上の入力画素Pi2、1ライン下の入力画素Pi3、2ライン下の入力画素Pi4の4点となる。この4点を下記に示す式(1)に代入することで、Pi2とPi3 の間に補間画素Poを生成することができる。

【数1】

【数2】

【0004】

ここで、yはPi2からPoの距離を示し、aには経験値としてa=−1前後の値が用いられる。バイキュービック補間を用いることで、図9に示すように、各入力画素間が滑らかな曲線で補間することができる。しかし、この補間方法を用いると、以下に説明するように、入力画像を3ライン格納するメモリが必要であった。

【0005】

図10は、バイキュービック補間を用いた場合の解像度変換回路100の構成図である。入力された画像データ101はラインバッファ102に供給される。ラインバッファ102に溜められた画像データはラインバッファ103に供給され、同様にラインバッファ103からラインバッファ104に供給される。対象となる4ライン分のうち3ライン分の画像データがラインバッファに溜まったら、読み出し制御回路105は、入力画像101とラインバッファ102,103,104から同時に4画素分の画素データ(Pi1,Pi2,Pi3,Pi4)を4画素畳み込み演算回路107に供給する。それと同時に、重み係数生成回路106は、式(2)を用いて重み係数f(y+1)、f(y)、f(y−1)、f(y−2)を求め、これらの値を4画素畳み込み演算回路107に供給する。4画素畳み込み演算回路107は、式(1)を用いてPi2とPi3の間の補間画素Poを算出して水平方向拡大/縮小回路108に供給する。水平方向拡大/縮小回路108は、水平方向の補間処理を行うことで解像度変換を行って画像データ109を出力する。

【0006】

ところで、年々入力画像の画素数は増加傾向にある。画素数の増加は1ラインを格納するためのメモリ容量の増加に直接影響してしまい、前記の方法では、容量の大きなメモリを搭載する必要がある。そこで、1画素毎のデータ量を削減してメモリに格納する方法が知られている。例えば、特許文献1では、入力画像の画素データRGBを輝度信号と色差信号(YCbCr)に変換し、2つの色差信号を交互に間引きしてメモリに格納する。これにより、1画素毎のデータ量が減り、メモリ容量を2/3にすることができる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2002−218490公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

特許文献1では、入力画像のデータをRGBから例えばYCbCrに変換し、間引きすることで、メモリに格納するデータを削減していた。その変換式を以下の式(3)に示す。Yは輝度信号を表し、Cb、Crは色差信号を表す。輝度信号Yと1画素毎にB−Y信号かR−Y信号をラインメモリに格納することで、メモリに格納する色差信号を半分としている。

【数3】

【0009】

しかしながら、この方法によると、色差信号が2画素に1度間引きされるため、間引かれた分の情報が欠落してしまう。そのため、画素間を滑らかな曲線で補間できたとしても、画質の劣化を引き起こしてしまう可能性がある。また、RGBからYCbCrに変換する回路だけではなく、出力時にYCbCrからRGBに変換する回路が必要となり、回路量が増えてしまう。

【0010】

本発明は前記課題を解決するためになされたものであり、その目的は、メモリ容量を削減しながら画質の劣化を抑えることのできる解像度変換装置及び解像度変換方法を提供することである。

【課題を解決するための手段】

【0011】

前記課題を解決するために、本発明の実施形態に係る解像度変換装置は、入力された画像データを格納するラインバッファと、前記ラインバッファに格納された画素データを含む計3画素を参照して垂直方向の補間画素を生成する際、前記補間画素の上2画素と下1画素を参照する補間(上側の補間)と前記補間画素の上1画素と下2画素を参照する補間(下側の補間)とをフレーム毎に切り替える演算部とを備えることを特徴とする。

【0012】

前記解像度変換装置において、前記演算部は、Lagrange補間を用いてPi2とPi3との間の補間画素Poを生成する際、Pi1,Pi2,Pi3を参照するLagrange補間(上側のLagrange補間)を式(4)に基づいて行い、Pi2,Pi3,Pi4を参照するLagrange補間(下側のLagrange補間)を式(5)に基づいて行ってもよい。

【数4】

【数5】

【0013】

前記解像度変換装置において、更に、前記演算部により生成された補間画素を用いて水平方向の補間処理を行う水平方向拡大/縮小部を備えてもよい。

【0014】

前記課題を解決するために、本発明の実施形態に係る解像度変換方法は、入力された画像データをラインバッファに格納するステップと、前記ラインバッファに格納された画素データを含む計3画素を参照して垂直方向の補間画素を生成する際、前記補間画素の上2画素と下1画素を参照する補間と前記補間画素の上1画素と下2画素を参照する補間とをフレーム毎に切り替えるステップとを備えることを特徴とする。

【発明の効果】

【0015】

本発明では、補間画素の上2画素と下1画素を参照する補間と補間画素の上1画素と下2画素を参照する補間とをフレーム毎に切り替えるようにしている。そのため、メモリ容量を削減しながら画質の劣化を抑えることのできる解像度変換装置及び解像度変換方法を提供することが可能である。

【図面の簡単な説明】

【0016】

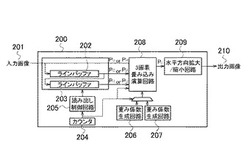

【図1】図1は、本発明の実施形態における解像度変換回路の構成図である。

【図2】図2は、本発明の実施形態におけるLagrange補間の説明図である。

【図3】図3は、本発明の実施形態における上側のLagrange補間の結果を示すグラフである。

【図4】図4は、本発明の実施形態における下側のLagrange補間の結果を示すグラフである。

【図5】図5は、本発明の実施形態における最終的な補間の結果を示すグラフである。

【図6】図6は、本発明の実施形態における解像度変換回路の動作を示すフローチャートである。

【図7】図7は、本発明の実施形態における別の解像度変換回路の構成図である。

【図8】図8は、従来のバイキュービック補間の説明図である。

【図9】図9は、従来のバイキュービック補間の結果を示すグラフである。

【図10】図10は、従来の解像度変換回路の構成図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施形態について図面を参照して詳細に説明する。

【0018】

図1は、本発明の実施形態における解像度変換回路200の構成図である。この解像度変換回路200は、解像度を変換する解像度変換装置の一例であって、図1に示すように、ラインバッファ202,203と、カウンタ204と、読み出し制御回路205と、重み係数生成回路206,207と、3画素畳み込み演算回路208と、水平方向拡大/縮小回路209とを備えている。以下、解像度変換回路200に入力される画像データを「入力画像201」、解像度変換回路200から出力される画像データを「出力画像210」という場合がある。

【0019】

ラインバッファ202,203は、入力画像201を格納するメモリである。カウンタ204は、入力画像201のフレームの数をカウントする。読み出し制御回路205は、カウンタ204のカウント結果に基づいて、ラインバッファ202,203から画素データを読み出すタイミング(すなわち、3画素畳み込み演算回路208に画素データを供給するタイミング)を制御する。重み係数生成回路206,207は、3画素畳み込み演算回路208で用いる重み係数を生成する。3画素畳み込み演算回路208は、重み係数生成回路206,207により生成された重み係数を用いて3画素畳み込み演算を行い、垂直方向の補間画素を生成する。水平方向拡大/縮小回路209は、3画素畳み込み演算回路208により生成された補間画素を用いて水平方向の補間処理を行う。

【0020】

本発明に至るまでの考え方について説明する。

【0021】

従来技術に記述した通り、滑らかな曲線で補間したい場合、画素の上下2画素ずつ参照する必要がある。この参照画素を3画素に削減した場合、図2に示すように、Pi2とPi3との間の補間画素Poを求めるには、参照画素としてPi1,Pi2,Pi3を使用する場合とPi2,Pi3,Pi4を使用する場合の2通りある。この2通りの補間についてLagrange補間を用いて説明する。Lagrange補間は、3画素を参照して補間する方法の1つである。以下、参照画素としてPi1,Pi2,Pi3を使用する場合のLagrange補間を「上側のLagrange補間」と呼ぶ。また、参照画素としてPi2,Pi3,Pi4を使用する場合のLagrange補間を「下側のLagrange補間」と呼ぶ。上側のLagrange補間と下側のLagrange補間の式を式(4),式(5)に示す。

【数6】

【数7】

【0022】

式(4)、式(5)を用いた場合のグラフを図3〜図5に示す。縦軸は画素値を示し、横軸は垂直方向の座標を示している。まず、上側のLagrange補間によると、図3に示すように、垂直方向座標2〜5の間は滑らかな曲線になるが、垂直方向座標0〜1の間は直線になっている。また、垂直方向座標1〜2の間は滑らかな曲線になるが、垂直方向座標0〜1と1〜2の接続が滑らかではなく、1〜2と2〜3の接続が滑らかではない。次に、下側のLagrange補間によると、図4に示すように、垂直方向座標0〜3の間は滑らかな曲線になるが、垂直方向座標4〜5の間は直線になっている。また、垂直方向座標3〜4の間は滑らかな曲線になるが、垂直方向座標2〜3と3〜4の接続が滑らかではなく、3〜4と4〜5の接続が滑らかでない。このように、3画素を参照して補間する場合は、どちらかに偏りが生じてしまうことがある。

【0023】

ところで、人間の目の時間分解能は50ms〜100msと言われ、一般的に、モニタ上でチラつき(フリッカー)を感じる垂直同期周波数は60Hz以下であるとされ、70Hz〜80Hz以上であるとほとんど気にならないとされている(フリッカーフリー)。つまり、フリッカーフリーのスピードで表示した場合、フレーム間の違いを目で追従できない。そこで、本実施形態では、入力画像201の各フレームの時間間隔が目で追従できないほど短い場合は、上側のLagrange補間と下側のLagrange補間をフレーム毎に切り替えるようにしている。これにより、図5に示すように、両者が混じり合い、滑らかにかつ両端のエッジの補間曲線が左右対称となる。

【0024】

以下、図6を用いて、解像度変換回路200の構成をその動作とともに説明する。

【0025】

まず、解像度変換回路200に入力された画像データ201はラインバッファ202に供給され、ラインバッファ202に溜められた画像データはラインバッファ203に供給される(ステップS1)。この時、カウンタ204はフレームの数をカウントし(ステップS2)、そのカウント結果(現フレームが奇数であるか偶数であるかを示す信号)を読み出し制御回路205、重み係数生成回路206,207、3画素畳み込み演算回路208に供給する。読み出し制御回路205は、対象となる3ライン分のうち2ライン分の画素データがラインバッファに溜まったら、入力画像201とラインバッファ202,203から同時に3画素分の画素データを3画素畳み込み演算回路208に供給する。具体的には、現フレームが奇数の場合は上側の3画素(Pi1,Pi2,Pi3)を、現フレームが偶数の場合は下側の3画素(Pi2,Pi3,Pi4)を3画素畳み込み演算回路208に供給するようになっている。それと同時に、現フレームが奇数の場合は重み係数生成回路206が重み係数(wodd1,wodd2,wodd3)を生成して3画素畳み込み演算回路208に供給する。一方、現フレームが偶数の場合は重み係数生成回路207が重み係数(weven1,weven2,weven3)を生成して3画素畳み込み演算回路208に供給する。3画素畳み込み演算回路208は、上側の3画素(Pi1,Pi2,Pi3)が供給された場合、すなわち現フレームが奇数の場合は、式(4)を用いて補間画素Poを生成し、生成した補間画素Poを水平方向拡大/縮小回路209に供給する(ステップS3→S4)。一方、下側の3画素(Pi2,Pi3,Pi4)が供給された場合、すなわち現フレームが偶数の場合は、式(5)を用いて補間画素Poを生成し、生成した補間画素Poを水平方向拡大/縮小回路209に供給する(ステップS3→S5)。水平方向拡大/縮小回路209は、水平方向の補間処理を行うことで解像度変換を行って画像データ210を出力する(ステップS6)。以降も、上側のLagrange補間と下側のLagrange補間とをフレーム毎に切り替える処理を繰り返す。

【0026】

以上のように、本発明の実施形態における解像度変換回路200によれば、メモリ容量を削減しながら画質の劣化を抑えることができる。すなわち、参照画素を4画素から3画素に削減しているため、メモリ容量を削減することが可能である。また、このように参照画素を削減しても、上側のLagrange補間と下側のLagrange補間とをフレーム毎に切り替えるようにしているため、画質の劣化を抑えることが可能である。しかも、特許文献1のように入力データの変換を行わないので、回路量が増加するという問題も生じない。その結果、コストダウンを図ることが可能である。

【0027】

なお、解像度変換では、入力時と出力時のクロック周波数が異なる場合、周波数差を吸収するためにラインバッファが1ライン以上必要となる。そのため、例えばバイキュービック補間では、図10のラインバッファが4ラインとなってしまう。このような場合でも、本発明によれば、図7に示すように、3ラインのラインバッファ302,303,304で対応することが可能である。

【0028】

また、本発明は、解像度変換回路(装置)200として実現することができるだけでなく、このような解像度変換回路200が備える特徴的な処理部をステップとする解像度変換方法として実現したり、それらのステップをコンピュータに実行させるプログラムとして実現したりすることもできる。このようなプログラムは、CD−ROM等の記録媒体やインターネット等の伝送媒体を介して配信することができるのはいうまでもない。

【符号の説明】

【0029】

200…解像度変換回路(解像度変換装置)

202,203…ラインバッファ

208…3画素畳み込み演算回路(演算部)

209…水平方向拡大/縮小回路(水平方向拡大/縮小部)

【技術分野】

【0001】

本発明は、解像度を変換する解像度変換装置及び解像度変換方法に関し、特に、液晶ディスプレイ装置などの解像度が一定の表示装置に搭載される解像度変換回路に関する。

【背景技術】

【0002】

表示装置には、解像度を向上させるための解像度変換回路が搭載されている。従来、この解像度変換回路としては、一般的に、良好な画質を得ることができるバイキュービック補間を用いた解像度変換回路が用いられている。

【0003】

バイキュービック補間では、出力画素位置に対応する入力画素位置の周辺の垂直方向4 画素、水平方向4画素を出力画素ごとに参照して画素を生成する。ここで、垂直方向におけるバイキュービック補間では、生成したい画素位置から上下2画素ずつ計4画素を参照する。すなわち、図8に示すように、生成したい画素を補間画素Poとすると、参照画素は2ライン上の入力画素Pi1、1ライン上の入力画素Pi2、1ライン下の入力画素Pi3、2ライン下の入力画素Pi4の4点となる。この4点を下記に示す式(1)に代入することで、Pi2とPi3 の間に補間画素Poを生成することができる。

【数1】

【数2】

【0004】

ここで、yはPi2からPoの距離を示し、aには経験値としてa=−1前後の値が用いられる。バイキュービック補間を用いることで、図9に示すように、各入力画素間が滑らかな曲線で補間することができる。しかし、この補間方法を用いると、以下に説明するように、入力画像を3ライン格納するメモリが必要であった。

【0005】

図10は、バイキュービック補間を用いた場合の解像度変換回路100の構成図である。入力された画像データ101はラインバッファ102に供給される。ラインバッファ102に溜められた画像データはラインバッファ103に供給され、同様にラインバッファ103からラインバッファ104に供給される。対象となる4ライン分のうち3ライン分の画像データがラインバッファに溜まったら、読み出し制御回路105は、入力画像101とラインバッファ102,103,104から同時に4画素分の画素データ(Pi1,Pi2,Pi3,Pi4)を4画素畳み込み演算回路107に供給する。それと同時に、重み係数生成回路106は、式(2)を用いて重み係数f(y+1)、f(y)、f(y−1)、f(y−2)を求め、これらの値を4画素畳み込み演算回路107に供給する。4画素畳み込み演算回路107は、式(1)を用いてPi2とPi3の間の補間画素Poを算出して水平方向拡大/縮小回路108に供給する。水平方向拡大/縮小回路108は、水平方向の補間処理を行うことで解像度変換を行って画像データ109を出力する。

【0006】

ところで、年々入力画像の画素数は増加傾向にある。画素数の増加は1ラインを格納するためのメモリ容量の増加に直接影響してしまい、前記の方法では、容量の大きなメモリを搭載する必要がある。そこで、1画素毎のデータ量を削減してメモリに格納する方法が知られている。例えば、特許文献1では、入力画像の画素データRGBを輝度信号と色差信号(YCbCr)に変換し、2つの色差信号を交互に間引きしてメモリに格納する。これにより、1画素毎のデータ量が減り、メモリ容量を2/3にすることができる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2002−218490公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

特許文献1では、入力画像のデータをRGBから例えばYCbCrに変換し、間引きすることで、メモリに格納するデータを削減していた。その変換式を以下の式(3)に示す。Yは輝度信号を表し、Cb、Crは色差信号を表す。輝度信号Yと1画素毎にB−Y信号かR−Y信号をラインメモリに格納することで、メモリに格納する色差信号を半分としている。

【数3】

【0009】

しかしながら、この方法によると、色差信号が2画素に1度間引きされるため、間引かれた分の情報が欠落してしまう。そのため、画素間を滑らかな曲線で補間できたとしても、画質の劣化を引き起こしてしまう可能性がある。また、RGBからYCbCrに変換する回路だけではなく、出力時にYCbCrからRGBに変換する回路が必要となり、回路量が増えてしまう。

【0010】

本発明は前記課題を解決するためになされたものであり、その目的は、メモリ容量を削減しながら画質の劣化を抑えることのできる解像度変換装置及び解像度変換方法を提供することである。

【課題を解決するための手段】

【0011】

前記課題を解決するために、本発明の実施形態に係る解像度変換装置は、入力された画像データを格納するラインバッファと、前記ラインバッファに格納された画素データを含む計3画素を参照して垂直方向の補間画素を生成する際、前記補間画素の上2画素と下1画素を参照する補間(上側の補間)と前記補間画素の上1画素と下2画素を参照する補間(下側の補間)とをフレーム毎に切り替える演算部とを備えることを特徴とする。

【0012】

前記解像度変換装置において、前記演算部は、Lagrange補間を用いてPi2とPi3との間の補間画素Poを生成する際、Pi1,Pi2,Pi3を参照するLagrange補間(上側のLagrange補間)を式(4)に基づいて行い、Pi2,Pi3,Pi4を参照するLagrange補間(下側のLagrange補間)を式(5)に基づいて行ってもよい。

【数4】

【数5】

【0013】

前記解像度変換装置において、更に、前記演算部により生成された補間画素を用いて水平方向の補間処理を行う水平方向拡大/縮小部を備えてもよい。

【0014】

前記課題を解決するために、本発明の実施形態に係る解像度変換方法は、入力された画像データをラインバッファに格納するステップと、前記ラインバッファに格納された画素データを含む計3画素を参照して垂直方向の補間画素を生成する際、前記補間画素の上2画素と下1画素を参照する補間と前記補間画素の上1画素と下2画素を参照する補間とをフレーム毎に切り替えるステップとを備えることを特徴とする。

【発明の効果】

【0015】

本発明では、補間画素の上2画素と下1画素を参照する補間と補間画素の上1画素と下2画素を参照する補間とをフレーム毎に切り替えるようにしている。そのため、メモリ容量を削減しながら画質の劣化を抑えることのできる解像度変換装置及び解像度変換方法を提供することが可能である。

【図面の簡単な説明】

【0016】

【図1】図1は、本発明の実施形態における解像度変換回路の構成図である。

【図2】図2は、本発明の実施形態におけるLagrange補間の説明図である。

【図3】図3は、本発明の実施形態における上側のLagrange補間の結果を示すグラフである。

【図4】図4は、本発明の実施形態における下側のLagrange補間の結果を示すグラフである。

【図5】図5は、本発明の実施形態における最終的な補間の結果を示すグラフである。

【図6】図6は、本発明の実施形態における解像度変換回路の動作を示すフローチャートである。

【図7】図7は、本発明の実施形態における別の解像度変換回路の構成図である。

【図8】図8は、従来のバイキュービック補間の説明図である。

【図9】図9は、従来のバイキュービック補間の結果を示すグラフである。

【図10】図10は、従来の解像度変換回路の構成図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施形態について図面を参照して詳細に説明する。

【0018】

図1は、本発明の実施形態における解像度変換回路200の構成図である。この解像度変換回路200は、解像度を変換する解像度変換装置の一例であって、図1に示すように、ラインバッファ202,203と、カウンタ204と、読み出し制御回路205と、重み係数生成回路206,207と、3画素畳み込み演算回路208と、水平方向拡大/縮小回路209とを備えている。以下、解像度変換回路200に入力される画像データを「入力画像201」、解像度変換回路200から出力される画像データを「出力画像210」という場合がある。

【0019】

ラインバッファ202,203は、入力画像201を格納するメモリである。カウンタ204は、入力画像201のフレームの数をカウントする。読み出し制御回路205は、カウンタ204のカウント結果に基づいて、ラインバッファ202,203から画素データを読み出すタイミング(すなわち、3画素畳み込み演算回路208に画素データを供給するタイミング)を制御する。重み係数生成回路206,207は、3画素畳み込み演算回路208で用いる重み係数を生成する。3画素畳み込み演算回路208は、重み係数生成回路206,207により生成された重み係数を用いて3画素畳み込み演算を行い、垂直方向の補間画素を生成する。水平方向拡大/縮小回路209は、3画素畳み込み演算回路208により生成された補間画素を用いて水平方向の補間処理を行う。

【0020】

本発明に至るまでの考え方について説明する。

【0021】

従来技術に記述した通り、滑らかな曲線で補間したい場合、画素の上下2画素ずつ参照する必要がある。この参照画素を3画素に削減した場合、図2に示すように、Pi2とPi3との間の補間画素Poを求めるには、参照画素としてPi1,Pi2,Pi3を使用する場合とPi2,Pi3,Pi4を使用する場合の2通りある。この2通りの補間についてLagrange補間を用いて説明する。Lagrange補間は、3画素を参照して補間する方法の1つである。以下、参照画素としてPi1,Pi2,Pi3を使用する場合のLagrange補間を「上側のLagrange補間」と呼ぶ。また、参照画素としてPi2,Pi3,Pi4を使用する場合のLagrange補間を「下側のLagrange補間」と呼ぶ。上側のLagrange補間と下側のLagrange補間の式を式(4),式(5)に示す。

【数6】

【数7】

【0022】

式(4)、式(5)を用いた場合のグラフを図3〜図5に示す。縦軸は画素値を示し、横軸は垂直方向の座標を示している。まず、上側のLagrange補間によると、図3に示すように、垂直方向座標2〜5の間は滑らかな曲線になるが、垂直方向座標0〜1の間は直線になっている。また、垂直方向座標1〜2の間は滑らかな曲線になるが、垂直方向座標0〜1と1〜2の接続が滑らかではなく、1〜2と2〜3の接続が滑らかではない。次に、下側のLagrange補間によると、図4に示すように、垂直方向座標0〜3の間は滑らかな曲線になるが、垂直方向座標4〜5の間は直線になっている。また、垂直方向座標3〜4の間は滑らかな曲線になるが、垂直方向座標2〜3と3〜4の接続が滑らかではなく、3〜4と4〜5の接続が滑らかでない。このように、3画素を参照して補間する場合は、どちらかに偏りが生じてしまうことがある。

【0023】

ところで、人間の目の時間分解能は50ms〜100msと言われ、一般的に、モニタ上でチラつき(フリッカー)を感じる垂直同期周波数は60Hz以下であるとされ、70Hz〜80Hz以上であるとほとんど気にならないとされている(フリッカーフリー)。つまり、フリッカーフリーのスピードで表示した場合、フレーム間の違いを目で追従できない。そこで、本実施形態では、入力画像201の各フレームの時間間隔が目で追従できないほど短い場合は、上側のLagrange補間と下側のLagrange補間をフレーム毎に切り替えるようにしている。これにより、図5に示すように、両者が混じり合い、滑らかにかつ両端のエッジの補間曲線が左右対称となる。

【0024】

以下、図6を用いて、解像度変換回路200の構成をその動作とともに説明する。

【0025】

まず、解像度変換回路200に入力された画像データ201はラインバッファ202に供給され、ラインバッファ202に溜められた画像データはラインバッファ203に供給される(ステップS1)。この時、カウンタ204はフレームの数をカウントし(ステップS2)、そのカウント結果(現フレームが奇数であるか偶数であるかを示す信号)を読み出し制御回路205、重み係数生成回路206,207、3画素畳み込み演算回路208に供給する。読み出し制御回路205は、対象となる3ライン分のうち2ライン分の画素データがラインバッファに溜まったら、入力画像201とラインバッファ202,203から同時に3画素分の画素データを3画素畳み込み演算回路208に供給する。具体的には、現フレームが奇数の場合は上側の3画素(Pi1,Pi2,Pi3)を、現フレームが偶数の場合は下側の3画素(Pi2,Pi3,Pi4)を3画素畳み込み演算回路208に供給するようになっている。それと同時に、現フレームが奇数の場合は重み係数生成回路206が重み係数(wodd1,wodd2,wodd3)を生成して3画素畳み込み演算回路208に供給する。一方、現フレームが偶数の場合は重み係数生成回路207が重み係数(weven1,weven2,weven3)を生成して3画素畳み込み演算回路208に供給する。3画素畳み込み演算回路208は、上側の3画素(Pi1,Pi2,Pi3)が供給された場合、すなわち現フレームが奇数の場合は、式(4)を用いて補間画素Poを生成し、生成した補間画素Poを水平方向拡大/縮小回路209に供給する(ステップS3→S4)。一方、下側の3画素(Pi2,Pi3,Pi4)が供給された場合、すなわち現フレームが偶数の場合は、式(5)を用いて補間画素Poを生成し、生成した補間画素Poを水平方向拡大/縮小回路209に供給する(ステップS3→S5)。水平方向拡大/縮小回路209は、水平方向の補間処理を行うことで解像度変換を行って画像データ210を出力する(ステップS6)。以降も、上側のLagrange補間と下側のLagrange補間とをフレーム毎に切り替える処理を繰り返す。

【0026】

以上のように、本発明の実施形態における解像度変換回路200によれば、メモリ容量を削減しながら画質の劣化を抑えることができる。すなわち、参照画素を4画素から3画素に削減しているため、メモリ容量を削減することが可能である。また、このように参照画素を削減しても、上側のLagrange補間と下側のLagrange補間とをフレーム毎に切り替えるようにしているため、画質の劣化を抑えることが可能である。しかも、特許文献1のように入力データの変換を行わないので、回路量が増加するという問題も生じない。その結果、コストダウンを図ることが可能である。

【0027】

なお、解像度変換では、入力時と出力時のクロック周波数が異なる場合、周波数差を吸収するためにラインバッファが1ライン以上必要となる。そのため、例えばバイキュービック補間では、図10のラインバッファが4ラインとなってしまう。このような場合でも、本発明によれば、図7に示すように、3ラインのラインバッファ302,303,304で対応することが可能である。

【0028】

また、本発明は、解像度変換回路(装置)200として実現することができるだけでなく、このような解像度変換回路200が備える特徴的な処理部をステップとする解像度変換方法として実現したり、それらのステップをコンピュータに実行させるプログラムとして実現したりすることもできる。このようなプログラムは、CD−ROM等の記録媒体やインターネット等の伝送媒体を介して配信することができるのはいうまでもない。

【符号の説明】

【0029】

200…解像度変換回路(解像度変換装置)

202,203…ラインバッファ

208…3画素畳み込み演算回路(演算部)

209…水平方向拡大/縮小回路(水平方向拡大/縮小部)

【特許請求の範囲】

【請求項1】

解像度を変換する解像度変換装置であって、

入力された画像データを格納するラインバッファと、

前記ラインバッファに格納された画素データを含む計3画素を参照して垂直方向の補間画素を生成する際、前記補間画素の上2画素と下1画素を参照する補間と前記補間画素の上1画素と下2画素を参照する補間とをフレーム毎に切り替える演算部と、

を備えることを特徴とする解像度変換装置。

【請求項2】

前記演算部は、Lagrange補間を用いてPi2とPi3との間の補間画素Poを生成する際、Pi1,Pi2,Pi3を参照するLagrange補間を式(4)に基づいて行い、Pi2,Pi3,Pi4を参照するLagrange補間を式(5)に基づいて行うことを特徴とする請求項1記載の解像度変換装置。

【数8】

【数9】

【請求項3】

更に、前記演算部により生成された補間画素を用いて水平方向の補間処理を行う水平方向拡大/縮小部を備えることを特徴とする請求項1又は2記載の解像度変換装置。

【請求項4】

解像度を変換する解像度変換方法であって、

入力された画像データをラインバッファに格納するステップと、

前記ラインバッファに格納された画素データを含む計3画素を参照して垂直方向の補間画素を生成する際、前記補間画素の上2画素と下1画素を参照する補間と前記補間画素の上1画素と下2画素を参照する補間とをフレーム毎に切り替えるステップと、

を備えることを特徴とする解像度変換方法。

【請求項1】

解像度を変換する解像度変換装置であって、

入力された画像データを格納するラインバッファと、

前記ラインバッファに格納された画素データを含む計3画素を参照して垂直方向の補間画素を生成する際、前記補間画素の上2画素と下1画素を参照する補間と前記補間画素の上1画素と下2画素を参照する補間とをフレーム毎に切り替える演算部と、

を備えることを特徴とする解像度変換装置。

【請求項2】

前記演算部は、Lagrange補間を用いてPi2とPi3との間の補間画素Poを生成する際、Pi1,Pi2,Pi3を参照するLagrange補間を式(4)に基づいて行い、Pi2,Pi3,Pi4を参照するLagrange補間を式(5)に基づいて行うことを特徴とする請求項1記載の解像度変換装置。

【数8】

【数9】

【請求項3】

更に、前記演算部により生成された補間画素を用いて水平方向の補間処理を行う水平方向拡大/縮小部を備えることを特徴とする請求項1又は2記載の解像度変換装置。

【請求項4】

解像度を変換する解像度変換方法であって、

入力された画像データをラインバッファに格納するステップと、

前記ラインバッファに格納された画素データを含む計3画素を参照して垂直方向の補間画素を生成する際、前記補間画素の上2画素と下1画素を参照する補間と前記補間画素の上1画素と下2画素を参照する補間とをフレーム毎に切り替えるステップと、

を備えることを特徴とする解像度変換方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−65926(P2013−65926A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2011−201874(P2011−201874)

【出願日】平成23年9月15日(2011.9.15)

【出願人】(000002897)大日本印刷株式会社 (14,506)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成23年9月15日(2011.9.15)

【出願人】(000002897)大日本印刷株式会社 (14,506)

【Fターム(参考)】

[ Back to top ]