計数回路を備えたバッテリ管理システム

【課題】従来のバッテリ管理チップはそのアドレス指示に特別のピンを必要とし、特別のピンはバッテリ管理チップの無効サイズおよびプリント回路ボードエリアを増大させ、バッテリ管理チップコストが増加する。

【解決手段】システムは複数のチップおよびホストプロセッサを含みうる。ホストプロセッサは複数のチップに接続し、計数コマンドを送信できる。複数のチップは計数コマンドを含む計数パケットをチップからチップへ伝達でき、各チップは計数パケットの情報を使用してそれ自体の固有アドレスを判断できる。

【解決手段】システムは複数のチップおよびホストプロセッサを含みうる。ホストプロセッサは複数のチップに接続し、計数コマンドを送信できる。複数のチップは計数コマンドを含む計数パケットをチップからチップへ伝達でき、各チップは計数パケットの情報を使用してそれ自体の固有アドレスを判断できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、計数回路(enumerating circuit)を備えたバッテリ管理システムに関する。

[関連出願の相互参照]

本願は本願と同時出願のA.フリッピン(A. Flippin)他による「垂直バス(vertical bus circuit)回路を伴うバッテリ管理システム」と題する書類番号O2−0717−1による出願に関係する。

【背景技術】

【0002】

従来のバッテリ管理システムは複数のバッテリ管理チップおよびバッテリ管理チップに接続するホストプロセッサを含む。複数のバッテリ管理チップは複数のバッテリモジュールに接続でき、バッテリモジュールの状態を監視する。ホストプロセッサはバッテリ管理チップとの通信に使用できる。ホストプロセッサはバッテリ管理チップのアドレスを取得し、その後バッテリ管理チップにアクセスする。従来のバッテリ管理チップはそのアドレスの指示に特別のピン、例えば3本のピンを必要とする。である。

【発明の概要】

【発明が解決しようとする課題】

【0003】

しかし、特別のピンはバッテリ管理チップの無効サイズおよびプリント回路ボード(PCB、printed circuit board)エリアを増大させ、それ故バッテリ管理チップコストが従って増加する。

その上幾つかのアプリケーションでは、ホストプロセッサはブロードキャストコマンドを送信し、全てのバッテリ管理チップにコマンドの同時実行を指令する。しかし通信遅延により、全てのバッテリ管理チップにとりブロードキャストコマンドの同時実行は不可能

【課題を解決するための手段】

【0004】

一実施形態で、システムは複数のチップおよびホストプロセッサを含む。ホストプロセッサは複数のチップに接続し、計数コマンドを送信する。複数のチップは計数コマンドを含む計数パケットをチップからチップへ伝達し、各チップは計数パケットにおける情報を使用してそれ自体の固有アドレスを判断する。

【0005】

別の実施形態で、バッテリ管理チップはバッテリ管理ユニットおよび計数回路を含む。バッテリ管理ユニットはバッテリ管理チップに接続するバッテリモジュールの電池状態を監視し、サンプリングする。計数回路はバッテリ管理ユニットに接続し、計数パケットを受信する。計数パケットは計数コマンドおよび第1の番号を含む。計数回路は計数コマンドに応じ、第1の番号に基づき第2の番号を発生する。 特許請求主題の実施形態が持つ特徴および利点は以下の詳細な説明の進展に従い、同じ番号が同じ部分を表す図面の参照に応じて明らかになろう。

【図面の簡単な説明】

【0006】

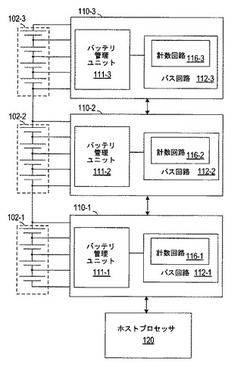

【図1】は本発明の一実施形態に従う計数回路を伴うバッテリ管理システム例のブロック図を示す。

【図2】は本発明の一実施形態に従う計数回路例のブロック図を示す。

【図3】は本発明の一実施形態に従う計数回路に関連する信号タイミング図を示す。

【図4】は本発明の一実施形態に従う計数回路を伴うバッテリ管理システム例のブロック図を示す。

【図5A】は本発明の一実施形態に従うバッテリ管理チップにおける垂直バス回路例のブロック図を示す。

【図5B】は本発明の一実施形態に従う垂直バス回路の受信機と関連する信号例を示す。

【図5C】は本発明の一実施形態に従う垂直バス回路の受信機と関連する信号例を示す。

【図6】本発明の一実施形態に従うバッテリ管理システムの動作タイミング図を示す。

【図7】本発明の一実施形態に従うバッテリ管理システムにより実行する動作フローチャートを示す。

【発明を実施するための形態】

【0007】

次に、本発明の実施形態を詳細に参照することにする。本発明をこれらの実施形態と共に説明することにするが、これらの実施形態はそれら自体に本発明を制限すると考えないことが理解されよう。逆に添付する特許請求の範囲により規定するように、本発明は本発明の精神および範囲内に含みうる代替、修正および等価物を包含すると考える。

【0008】

ここで説明する実施形態はプログラムモジュールのようなある形態のコンピュータ使用可能媒体に所在し、1台以上のコンピュータまたはその他のデバイスにより実行する汎用コンテキストコンピュータ実行可能命令において考察できる。一般にプログラムモジュールは、特定のタスクを実行するか、または特定の抽象データタイプを実装するルーティン、プログラム、オブジェクト、構成要素、データ構造などを含む。プログラムモジュールの機能は種々の実施形態において所望の如く結合または分散できる。

【0009】

以下の詳細な説明のある部分をコンピュータメモリ内のデータビット演算に関する手順、論理ブロック、処理およびその他のシンボリック表現により提示する。これらの説明および表現は当業者の作業内容を他の当業者に最も効率的に伝達するのにデータ処理技術の当業者により使用する手段である。本出願で、手順、論理ブロック、処理または同類は所望の結果に導くステップ若しくは命令の自己完結シーケンスであると考える。ステップは物理量の物理的操作を必要とするものである。必然的ではないが通常、これらの量はコンピュータシステムにおいて蓄積、伝送、結合、比較およびその他の操作を行いうる電気的または磁気的信号の形態を取る。

【0010】

とはいえ、全てのこれらおよび類似の用語は適する物理量に関連すべきであり、これらの量に適用する単に便利なラベルであることを留意すべきである。以下の考察から明らかなように別途特に記述しない限り、本出願を通じて「送信」、「検出」、「変換」、「比較」、「判断」または同類のような用語を利用する考察は、コンピュータシステムレジスタおよびメモリ内において物理(電子)量として表すデータを操作し、コンピュータシステムメモリまたはレジスタ若しくは他のそのような情報蓄積、伝送または表示デバイス内の物理量として同様に表す他のデータに変換する、コンピュータシステムまたは類似の電子計算デバイスの動作および処理に関連すると認識する。

【0011】

制限するのではなく例として、コンピュータ使用可能媒体はコンピュータ蓄積媒体および通信媒体を含みうる。コンピュータ蓄積媒体はコンピュータ可読命令、データ構造、プログラムモジュールまたはその他のデータのような任意の情報蓄積方法若しくは技術において実装する揮発性並びに不揮発性、取り外し可能および取り外し不可能媒体を含む。コンピュータ蓄積媒体は以下に限らないが、所望の情報の蓄積に使用できるランダムアクセスメモリ(RAM、random access memory)、読み出し専用メモリ(ROM、read only memory)、電気的消去可能プログラマブルROM(EEPROM、electrically erasa-ble programmable ROM)、フラッシュメモリまたはその他のメモリ技術、コンパクトディスクROM(CD−ROM、compact disk ROM)、ディジタル多用途ディスク(DVD、digital versatile disks)若しくはその他の光学的蓄積装置、磁気カセット、磁気テープ、磁気ディスク蓄積装置またはその他の磁気蓄積デバイス、若しくは任意の他の媒体を含む。

【0012】

通信媒体はコンピュータ可読命令、データ構造、プログラムモジュールまたは搬送波若しくは他の伝送機構のような変調データ信号における他のデータを表すことができ、任意の情報配信媒体を含む。用語「変調データ信号」は1つ以上のその特徴セットを有するか、若しくは情報を信号に符号化するように変化した信号を意味する。制限するのではなく例として、通信媒体は有線ネットワーク若しくは直接有線接続のような有線媒体および音響、無線周波数(RF、radio frequency)、赤外線並びにその他の無線媒体のような無線媒体を含む。任意の上記の組み合わせもコンピュータ可読媒体の範囲内に含むべきである。

【0013】

その上さらに本発明の以下の詳細な説明で、本発明の完全な理解をもたらすため、多くの特定の詳細を示す。しかし、本発明をこれらの特定の詳細以外において実行しうることは当業者により認識されよう。その他の場合、本発明の態様を不要に不明確にしないため、周知の方法、手順、構成要素および回路は詳細に説明していない。

【0014】

図1は本発明の一実施形態に従う計数回路を伴うバッテリ管理システム例100のブロック図を示す。一実施形態で、バッテリ管理システム100は直列に接続する複数のバッテリモジュール102−i、例えば102−1、102−2および102−3、バッテリモジュール102−1、102−2および102−3にそれぞれ接続するバッテリ管理チップ110−i、例えば110−1、110−2および110−3並びにバッテリ管理チップ110−1に接続するホストプロセッサ120を含む。図1に示す実施形態は例証を目的とするのみであるので、バッテリ管理チップ数はバッテリ管理チップを使用する特定アプリケーションの要求に応じて任意の数でありうる。

【0015】

バッテリモジュール102−iは1個以上のバッテリ電池、例えば図1の例に示すように4個のバッテリ電池をさらに含む。バッテリ管理チップ110−1、110−2および110−3はバスを介して互いに直列に接続する。各バッテリ管理チップ110−iは対応バッテリ管理ユニット111−iおよび対応バス回路112−iを含む。バッテリ管理ユニット111−iはホストプロセッサ120から受信する命令に従い対応バッテリモジュール102−iにおける各バッテリ電池の状態(例えば、電池電圧)を監視し、サンプリングできる。バス回路112−iは計数回路116−iを含み、バッテリ管理ユニット111−iとホストプロセッサ120間の信号を伝送する。

【0016】

一実施形態で、ホストプロセッサ120は計数コマンドをバッテリ管理チップに送信し、各バッテリ管理チップにそれ自体のアドレスの判断を可能にする。一実施形態で、固有チップ番号を各バッテリ管理チップ110−iに割り当て、バッテリ管理チップ110−iのアドレスを表す。このような一実施形態で、ホストプロセッサ120は計数コマンドおよび初期チップ番号を含む計数パケットを送信する。計数パケットを受信すると、バス回路112−iにおける計数回路116−iは受信計数パケットにおけるチップ番号に基づき、例えば新規チップ番号を発生するため1だけ受信チップ番号を増進させることにより新規チップ番号を発生できる。一実施形態で、バッテリ管理チップ110−iのアドレスを表すのに発生する新規チップ番号を使用できる。別の実施形態で、バッテリ管理チップ110−iのアドレスを表すのに受信チップ番号を使用でき、上方バッテリ管理チップ110−(i+1)のアドレスを表すのに発生する新規チップ番号を使用できる。このような一実施形態では図1の例に示すように、バッテリ管理チップ110−3は最上位チップである。それ故、最上位バッテリ管理チップ110−3における計数回路116−3は新規チップ番号を発生しない。

【0017】

一実施形態で、計数パケットはチェックデータをさらに含み、計数回路116−iはチェックデータに従い、例えばチェックデータの受信チップ番号との比較により、受信チップ番号をチェックする。受信チップ番号に誤りがあれば、バッテリ管理チップ110−iは受信計数パケットを廃棄でき、ホストプロセッサ120はこの場合新規計数パケットを再送し、そのバッテリ管理チップ110−iのアドレスを判断できる。

【0018】

有利には各バッテリ管理チップ110−iのアドレスを表す固有チップ番号の使用により、バッテリ管理チップ110−iのアドレスの指示に従来使用するピンを除去する。従って、バッテリ管理チップ110−iのピン数は減少する。それ故、無効サイズおよびバッテリ管理チップのプリント回路ボード(PCB)エリアは減少し、バッテリ管理チップコストは従って減少する。

【0019】

図2は、本発明の一実施形態に従う図1の計数回路例116−iのブロック図を示す。計数回路116−iはチェック回路210、チップ番号発生器220およびマルチプレクサ(MUX、multiplexer)230を含む。チップ番号発生器220は計数パケットを受信する第1の端子DATA_IN(データ_イン)並びに信号FIRST_CHIP_BIT(第1の_チップ_ビット)を受信する第2の端子を含む。一実施形態で、計数パケットにおけるチップ番号の第1のビットを端子DATA_INで受信する場合、信号FIRST_CHIP_BITはハイである。チップ番号発生器220は計数パケットのチップ番号を受信し、例えば1だけ受信チップ番号を増進させることにより新規チップ番号をマルチプレクサ230に出力する。図2の例で、チップ番号発生器220はXORゲート221、ORゲート222、ANDゲート223およびフリップフロップ224を含む。

【0020】

チェック回路210は計数パケットのチップ番号を受信する端子CHIP_IN「n」およびチップ番号発生器220により発生する新規チップ番号を受信する端子CHIP_OUT「n」を含む。一実施形態で、チェック回路210はチェック処理において端子DATA_INを介して計数パケットにおけるチェックデータをさらに受信する。チップ番号発生器220が新規チップ番号を発生後、チェック回路210により受信する信号START_CHECKはハイである。次いで、チェック回路210は端子DATA_INで受信するチェックデータを端子CHIP_IN「n」で受信するチップ番号と比較し、誤りが受信チップ番号に生じたかを示す信号CHECK_OKを発生する。その上、チェック回路210はMUX230に対する新規チェックデータを発生でき、新規チェックデータを使用してチップ番号発生器220により発生する新規チップ番号における誤りをチェックする。一実施形態で、チェックデータは計数回路116−iにより受信するチップ番号の反転である。図2の例で、チェック回路210はXORゲート211および216、インバータ212、ANDゲート213、ORゲート214およびフリップフロップ215を含む。

【0021】

MUX230はチップ番号発生器220により発生する新規チップ番号およびチェック回路210により発生する新規チェックデータを受信する。より明確には、MUX230の第1の入力端子Aはチップ番号発生器220に接続し、MUX230の第2の入力端子Bはチェック回路210に接続する。MUX230の選択端子Sは発生処理とチェック処理間の選択信号CHECKING_WINDOW(チェック中_ウインドウ)を受信する。発生処理過程で、MUX230はチップ番号発生器220により発生する新規チップ番号を提供する。チェック処理過程で、MUX230はチェック回路210により発生する新規チェックデータを提供する。

【0022】

図3は本発明の一実施形態に従う図2の計数回路116−iに関連する信号タイミング図を示す。図3を図2と組み合わせて説明する。計数パケットを端子DATA_INで受信する。図3の例で、計数パケットは幾つかのアイドルビット、プレアンブルP、計数コマンド、チップ番号(例えば、CHIP_NUM(チップ_番号)[0:5]、ここでCHIP_NUM[0]は最下位ビットであり、CHIP_NUM[5]は最上位ビットである)およびチェックデータ(例えば、CHECK(チェック)[0:5]、ここでCHECK[0]は最下位ビットであり、CHECK[5]は最上位ビットである)を含む。一実施形態で、計数コマンドをホストプロセッサ120により送信し、ホストプロセッサ120に接続するバッテリ管理チップ総数を判断し、各バッテリ管理チップにそれ自体のアドレスの判断を可能にする。一実施形態で、チェックデータCHECK[0:5]はチップ番号CHIP_NUM[0:5]の反転である。

【0023】

一実施形態で、チップ番号、例えばCHIP_NUM[0:5]を計数コマンドの後で受信する。チップ番号CHIP_NUM[0]の第1のビットを端子DATA_INで受信すると、信号FIRST_CHIP_BITはハイになり、これは発生処理を開始したことを示す。従って、ORゲート222の出力信号CARRY(キャリー)はサイクル(時間ピリオド)T0中にハイになる。サイクルTn+1(例えば、n=0、1、2、3および4)中の信号CARRYは対応入力ビットCHIP_NUM[n]に依存する。例えば入力ビットCHIP_NUM[n]がディジタルの1であれば、信号CARRYはクロックBIT_CLK(ビット_クロック)の次サイクルTn+1の間ハイである。しかし入力ビットCHIP_NUM[n]がディジタルの0であれば、入力ビットCHIP_NUM[n+1:5]がディジタルの0または1であるかにかわらず、信号CARRYは次サイクルTn+1からT5迄の間ローに留まる。それ故XORゲート221の使用により、チップ番号発生器220は、例えば受信チップ番号CHIP_NUM[0:5]を1だけ増進させたに等しい新規チップ番号を発生する。例えばチップ番号CHIP_NUM[0:5]がT0乃至T5の間110010であれば、信号CARRYはT0乃至T5の間111000であり、チップ番号発生器220は新規チップ番号CHIP_NUM‘[0:5]001010(CHIP_NUM’[0]は最下位ビットであり、CHIP_NUM‘[5]は最上位ビットである)を発生する。(垂直バスで、最下位ビットを最初に伝送し、CHIP_NUM[0]は最下位ビットであり、CHIP_NUM[5]は最上位ビットである。CHIP_NUM[0:5]が110010であれば、新規発生番号CHIP_NUM’[0:5]は001010であり、これは実際にチップ番号が010011であることを意味し、新規発生チップ番号は010100であり、これは010011を1だけ増進させたものである。)発生処理過程で、MUX230の選択端子Sで受信する信号CHECK_WINDOW(チェック_ウインドウ)はローになる。結果として、MUX230の出力DATA_OUT(データ_出口)はチップ番号発生器220の出力である。

【0024】

信号START_CHECK(開始_チェック)がハイになると、チェック処理が始まる。結果として、ORゲート214の出力信号CHECK_OK(チェック_OK)がハイになる。クロックBIT_CLKの次サイクルT0‘の間に信号START_CHECKはローになる。従って、信号CHECK_OKはANDゲート213の出力により決定する。チェックデータCHECK[0:5]をT0‘からT5‘の間に入力端子DATA_INで受信する。チェック処理が完了するまで、信号END_CHECK(終了_チェック)はローに留まる。結果として、インバータ212の出力はハイに留まる。チェックデータCHECK[0:5]は一実施形態ではチップ番号CHIP_NUM[0:5]の反転である。結果として、信号CHECK_OKはT0‘乃至T5‘の間ハイに留まり、これはチップ番号CHIP_NUM[0:5]において誤りが生じなかったことを示す。その間に、入力端子CHIP_OUT(チップ_出口)「n」はチップ番号発生器220により発生する新規チップ番号CHIP_NUM’[0:5]を受信する。チップ番号CHIP_NUM[n]に誤りがなければ、信号CHECK_OKはTn‘の間ハイに留まり、XORゲート216は端子CHIP_OUT「n」で受信するデータビットの反転である新規チェックデータビットを発生する。従って新規チェックデータを発生し、これはチップ番号発生器220により発生する新規チップ番号の反転である。T0‘からT5‘のチェック処理の間、MUX230の選択端子Sで受信する信号CHECK_WINDOWはハイに留まる。結果として、MUX230の出力DATA_OUTはチェック回路210の出力である。サイクルT5‘の後、信号CHECK_WINDOWは再びローになり、これはチェック処理が完了したことを示す。

【0025】

一実施形態で、バス回路112−iは計数コマンド、新規チップ番号および新規対応チェックデータを含む新規計数パケットを対応バッテリ管理チップ110−(i+1)の上方バス回路112−(i+1)に次いで送信する。一実施形態で、バッテリ管理チップ110−iが最上位バッテリ管理チップであれば、バッテリ管理チップ110−iはホストプロセッサ120にも送信しうる応答をバッテリ管理チップ110−(i−1)に送信する。応答は計数コマンドおよびバッテリ管理チップ110−iのチップ番号を含みえ、ホストプロセッサ120は応答のチップ番号に従いバッテリ管理システムのバッテリ管理チップ総数を判断できる。しかし信号CHECK_OKがT0‘乃至T5‘の間何時もローであることをバス回路112−iが検出すれば、チェック回路210はチップ番号発生器220により発生する新規チップ番号の反転でないチェックデータを発生する。この場合、上位バッテリ管理110−(i+1)はチップ番号またはチェックデータに誤りが発生したことを検出でき、計数パケットを廃棄でき、ホストプロセッサ120は新規計数コマンドを再送でき、ホストプロセッサ120に接続するバッテリ管理チップ総数を判断し、各バッテリ管理チップにそれ自体のアドレスの判断を可能にするようにする。

【0026】

図4は本発明の一実施形態に従う図2の計数回路を伴うバッテリ管理システム例400のブロック図を示す。一実施形態で、バッテリ管理システム400は直列に接続するバッテリモジュール402−i、例えば402−1、402−2および402−3、バッテリモジュール402−1、402−2および402−3にそれぞれ接続するバッテリ管理チップ410−i、例えば410−1、410−2および410−3およびバッテリ管理チップ410−1に接続するホストプロセッサ440を含む。図4に示す実施形態は例証を目的とするのみであるので、バッテリ管理チップ数は特定アプリケーションの要求に応じて任意の数でありうる。

【0027】

バッテリモジュール402−iは1個以上のバッテリ電池、例えば図4の例に示すように6個のバッテリ電池をさらに含む。バッテリ管理チップ410−1、410−2および410−3は1個以上の直流絶縁器を介して互いに接続する。一実施形態で、直流絶縁器はパッシブ絶縁器であり、従って直流絶縁器に電力を供給する追加電力供給を必要としない。例えば、複数個のキャパシタC1乃至C10はバッテリ管理システム400においてバッテリ管理チップ410−1乃至410−3の直流絶縁に使用できる。図4の例に示すように、バッテリ管理チップ410−3はキャパシタC6乃至C10を介してバッテリ管理チップ410−2に接続し、バッテリ管理チップ410−2はキャパシタC1乃至C5を介してバッテリ管理チップ410−1に接続する。別の実施形態では、複数の変圧器即ちインダクタもバッテリ管理システム400においてバッテリ管理チップ410−1乃至410−3の直流絶縁に使用できる。隣接バッテリ管理チップ間における直流絶縁器の使用により、バッテリ管理チップを直流絶縁し、隣接バッテリモジュール間に接続断が生じれば損傷から保護しうる。その上パッシブ直流絶縁器の使用により、バッテリ管理システムコストを削減する。

【0028】

一実施形態で、各バッテリ管理チップ410−iは対応バッテリ管理ユニット411−iおよび対応垂直バス回路412−iを含む。バッテリ管理ユニット411−iはホストプロセッサ440から受信する命令により対応バッテリモジュール402−iにおける各バッテリ電池の状態(例えば、電池電圧)を監視し、サンプリングできる。垂直バス回路412−iはバッテリ管理ユニット411−iとホストプロセッサ440間の信号を伝送する。一実施形態で、垂直バス回路412−iは計数回路416−iをさらに含む。図4に示すように、計数回路416−iの構成及び動作は図2の計数回路116−iに類似し、従って繰り返す説明は簡潔さおよび明快さのためここでは省略する。

【0029】

一実施形態で、垂直バス回路412−iはピンIN(入口)(i−1)’+およびIN(i−1)’を介して下位バッテリ管理チップ410−(i−1)から第1の差分入力データ信号対(例えば、正差分信号INPUT(入力)+および負差分信号INPUT−)を受信し、それぞれピンOUT(出口)i+およびOUTi−を介して上位バッテリ管理チップ410−(i+1)に第1の差分出力データ信号対(例えば、正差分信号OUTPUT(出力)+および負差分信号OUTPUT−)を出力する。垂直バス回路412−iはピンINi+およびINi−を介して上位バッテリ管理チップ410−(i+1)から第2の差分入力データ信号対をさらに受信し、ピンOUT(i−1)’+およびOUT(i−1)’を介して下位バッテリ管理チップ410−(i−1)に第2の差分出力データ信号対を出力する。一実施形態で、バッテリ管理チップ410−3のピンIN3+、IN3−,OUT3+、およびOUT3−を接地する、これはバッテリ管理チップ410−3が最上位チップであることを示す。それ故、バッテリ管理チップ410−3はピンIN3+およびIN3−を介して第2の差分入力データ信号対を受信しないが、バッテリ管理チップ410−3はピンOUT2‘+およびOUT2’−を介して下位バッテリ管理チップ410−2に第2の差分出力データ信号対を出力できる。一実施形態で、最下位バッテリ管理回路410−1の垂直バス回路412−1はピンIN0‘+およびIN0’−を介してコンバータ413から第1の差分入力データ信号対を受信し、ピンOUT1+およびOUT1−を介して上位バッテリ管理チップ410−2に第1の差分出力データ信号対を出力する。垂直バス回路412−1はピンIN1+およびIN1−を介してバッテリ管理チップ410−2から第2の差分入力データ信号対をさらに受信し、ピンOUT0‘+およびOUT0’−を介してコンバータ413に第2の差分出力データ信号対を出力する。垂直バス回路412−iはホストプロセッサ440に対応バッテリ管理チップ410−iの状態(例えば、バッテリ管理チップ410−iの自己テストが完了しているか)を通報し、ホストプロセッサ440からサービスを要求する警報信号をピンALT(警報)(i−1)‘を介してさらに提供できる。警報信号を下位バッテリ管理チップ410−(i−1)に送信し、ホストプロセッサ440にさらに伝送する。

【0030】

有利には差分入力/出力データ信号の使用により、垂直バスにおける雑音を削減または除去する。その上一実施形態で差分データ信号を伝送中の任意のバスにおける異常状態(例えば、回路開放または回路短絡)の場合、他の差分信号対の単一線路の使用により通信を継続できる。別の実施形態で丁度説明するような異常状態が生じれば、差分入力/出力データ信号の送信に他の線路対を使用することにより通信を継続できる。このように、差分入力/出力データ信号の伝送線路は両方向モードで動作できる。

【0031】

一実施形態で図4の例に示すように、コンバータ413はホストプロセッサ440および垂直バス回路412−1に接続する。コンバータ413は第1のタイプのプロトコル、例えば直列周辺インタフェース(SPI、Serial Peripheral Interface)バスプロトコルを使用してホストプロセッサ440と通信する。コンバータ413とホストプロセッサ440間で伝送する信号はピンSDOを介してコンバータ413からホストプロセッサ440に伝送する出力データ信号、ピンIRQを介してコンバータ413からホストプロセッサ440に伝送する要求信号、ピンSDIを介してホストプロセッサ440からコンバータ413に伝送する入力データ信号並びにピンSCKおよびピン/CSをそれぞれ介してホストプロセッサ440からコンバータ413に伝送するクロック信号並びに稼働信号を含む。一実施形態で、コンバータ413は第2のタイプのプロトコル、例えば垂直バスプロトコルを使用して垂直バス回路412−1と通信し、バッテリ管理チップ410−iは第2のタイプのプロトコル、例えば垂直バスプロトコルを使用して隣接バッテリ管理チップ410−(i+1)および410−(i−1)と通信する。コンバータ413は第1のタイプのプロトコルを使用して通信し、ピンSDIを介してホストプロセッサ440から受信するデータを第2のタイプのプロトコルを使用して通信でき、ピンIN0‘−およびIN0’+を介して垂直バス回路412−1に伝送できる差分データ信号対に変換できる。同様に、コンバータ413は第2のタイプのプロトコルにより通信し、ピンOUT0‘−およびOUT0’+を介して垂直バス回路412−1から受信する差分データ信号対を第1のタイプのプロトコルにより通信でき、ピンSDOを介してホストプロセッサ440に伝送できるデータへの変換もできる。図4の例で、コンバータ413はバッテリ管理チップ410−1に統合する。とはいえ、コンバータ413はバッテリ管理チップ410−1の外部に位置することもできる。

【0032】

動作では、ホストプロセッサ440はピンSDIを介してバッテリ管理チップ410−1に計数コマンドを送信し、ホストプロセッサ440に接続するバッテリ管理チップ総数を判断し、各バッテリ管理チップ410−iにそれ自体のアドレスの判断を可能にする。一実施形態で、各バッテリ管理チップ410−iに対応バッテリ管理チップのアドレスを表す固有チップ番号を割り当てる。例えばホストプロセッサ440から計数コマンドを受信すると、コンバータ413は初期化チップ番号、例えば000000を発生する。コンバータ413は計数誤りチェックのためチェックデータも発生でき、例えばチェックデータは初期化チップ番号の反転、例えば111111である。一実施形態で、コンバータ413は計数コマンド、初期化チップ番号およびチェックデータを含む計数パケットをバッテリ管理チップ410−1の垂直バス回路412−1に送信する。コンバータ413により送信する計数パケットは垂直バスプロトコルに準拠する。

【0033】

コンバータ413から計数パケットを受信すると、垂直バス回路412−1は計数パケットの初期化チップ番号を垂直バス回路412−1のレジスタに蓄積できる。垂直バス回路412−1の計数回路416−1は例えば受信計数パケットにおける初期化チップ番号の増進により新規チップ番号(例えば、000001)をさらに発生し、対応チェックデータ(例えば、111110)、例えば新規チップ番号の反転を発生し、計数コマンド、新規チップ番号および対応チェックデータを含む計数パケットを一実施形態ではバッテリ管理チップ410−2の垂直バス回路412−2に送信する。垂直バス回路412−2および412−3の動作は垂直バス回路412−1の動作と同じであり、従って繰り返す説明は簡潔さおよび明快さのためここでは省略する。

【0034】

一実施形態で、対応バッテリ管理チップ410−iの垂直バス回路412−iにより受信するチップ番号を使用してバッテリ管理チップ410−iのアドレスを表す。このような一実施形態では図4の例に示すように、バッテリ管理チップ410−3における垂直バス回路412−3のピンIN3+、IN3−,OUT3+、OUT3−およびALT3を接地する、これはバッテリ管理チップ410−3が最上位チップであることを示す。それ故、最上位バッテリ管理チップ410−3の垂直バス回路412−3は新規チップ番号を発生しない。とはいえ別の実施形態では、垂直バス回路412−iにより発生するチップ番号を使用してバッテリ管理チップ410−iのアドレスを表し、従って最上位バッテリ管理チップ410−3の垂直バス回路412−3はバッテリ管理チップ410−3のアドレスを表す新規チップ番号を発生する。

【0035】

一実施形態で最上位バッテリ管理チップ410−3が計数パケットを受信(そして新規チップ番号を使用してバッテリ管理チップ410−iのアドレスを表すのであれば、新規チップ番号を発生)後、最上位バッテリ管理チップ410−3は他のバッテリ管理チップ410−1および410−2並びにホストプロセッサ440にも応答を送信する。一実施形態では、応答は計数コマンドおよび最上位バッテリ管理チップのチップ番号(例えば、図4の例に示すようにバッテリ管理チップ410−3)を含む。ホストプロセッサ440が応答を受信後、例えば最上位バッテリ管理チップのチップ番号により、ホストプロセッサ440はホストプロセッサ440に接続するバッテリ管理チップ総数を判断できる。

【0036】

図5Aは本発明の一実施形態に従う図4のバッテリ管理チップ410−iにおける垂直バス回路例412−iのブロック図を示す。図5Aを図4と組み合わせて説明する。

【0037】

一実施形態で、垂直バス回路412−iは下方データ経路、上方データ経路および警報データ経路を含む。上方データ経路は受信機532−i、ディジタル位相ロックループ(PLL、phase-locked loop)517−i、コマンドプロセッサ510−i並びに送信機533−iを含む。コマンドプロセッサ510−iは計数回路516−iをさらに含みうる。下方データ経路は受信機531−i、ディジタル位相ロックループ(PLL)505−i、応答発生器507−iおよび送信機534−iを含む。警報データ経路は受信機521−i、警報論理522−i並びに変調器523−iを含む。

【0038】

受信機532−iはピンIN(i−1)‘+およびIN(i−1)‘−を介して第1の差分入力データ信号対INPUT+並びにINPUT−を受信する比較器対512−iおよび514−iを含む。例えば、ピンIN(i−1)‘+は差分信号の正差分信号INPUT+を受信し、ピンIN(i−1)‘−は差分信号の負差分信号INPUT−を受信する。共通モード電圧VCM1をノード562で電圧ソース566−iにより供給し、それぞれキャパシタC4およびC3を介して受信機532−iにより受信する(図5Aの例には図示しない)信号IN+並びにIN−に定常状態電圧を供給する。

【0039】

一実施形態で、オフセット電圧Voffsetを提供し、受信機532−iの出力信号DOUTおよびさらに雑音排除並びに高周波信号排除ヒステリシスエリアを規定する。図5Aの例に示すように、比較器512−iの非反転端子は埋め込みオフセット電圧発生器、例えば電圧ソース543−iを通じて比較器514−iの反転端子に接続する。比較器514−iの非反転端子は埋め込みオフセット電圧発生器、例えば電圧ソース544−iを通じて、図5Aの例に示すように比較器512−iの反転端子に接続する。電圧ソース543−iおよび電圧ソース544−iそれぞれを跨ぐ電圧はVoffsetに等しい。図5Aの例に示すように、電圧ソース544−iの負端子は比較器512−iの反転端子に接続し、電圧ソース543−iの負端子は比較器514−iの反転端子に接続する。別の実施形態で、電圧ソース544−iの正端子は比較器512−iの非反転端子に接続することもできる。電圧ソースの正端子は比較器514−iの非反転端子に接続できる。

【0040】

一実施形態で図5Aの例に示すように、埋め込みオフセット電圧発生器は電圧ソースにより実装できる。別の実施形態で、埋め込みオフセット電圧発生器は抵抗を通じて流れる電流を有する抵抗により代わって実装できる。

【0041】

図5Aの例に示すように、比較器512−iおよび514−iのそれぞれはNANDゲートに接続する。例えば、比較器512−iの出力はNANDゲート542−iに接続し、比較器514−iの出力はNANDゲート541−iに接続する。NANDゲート541−iの出力はディジタルPLL517−iに接続し、ピンIN(i−1)‘+で受信する正差分データ信号INPUT+を示すデータ信号DOUT(D出口)を同期のためディジタルPLL517−iに提供する。別の実施形態で、NAND542−iの出力はディジタルPLL517−iに接続でき、ピンIN(i−1)‘−で受信する負差分データ信号INPUT−を示す出力データ信号をディジタルPLL517−iに提供する。一実施形態で、比較器512−iおよび514−iは差分入力比較器に統合できる。

【0042】

一実施形態で図5Aの例に示すように、比較器512−iおよび514−i、オフセット電圧発生器544−i並びに543−iおよびNANDゲート541−i並びに542−iは受信機532−iの出力信号DOUTのヒステリシスユニットとして実装できる。信号IN+とIN−間の差分がオフセット電圧Voffsetより大きければ、出力信号DOUTは論理的ローまたは論理的ハイでありうる。より明確には、出力信号DOUTは式(1)により与えるように論理的ハイでありうる:

VIN+−VIN−>Voffset (1)

出力信号DOUTは式(2)により与えるように論理的ローでありうる:

VIN+−VIN−<−Voffset (2)

式(3)で示すように信号IN+とIN−間の差分がオフセット電圧Voffsetより小さければ、出力信号DOUTはその前の状態を維持し、変化しない。

|VIN+−VIN−|<Voffset (3)

【0043】

図5Aに示すように、図5Bは垂直バス回路412−iの受信機532−iに関連する信号例を示す。信号INPUT+およびINPUT−は下位バッテリ管理チップ410−(i−1)からそれぞれキャパシタC4並びにC3に送信する差分入力データ信号を表す。別の実施形態で、バッテリ管理チップが最下位バッテリ管理チップ410−1であれば、信号INPUT+およびINPUT−はコンバータ413からの差分入力データ信号を表す。信号IN+並びにIN−はそれぞれキャパシタC4およびC3を介して受信機532−iにより受信する信号である。信号DOUTはNANDゲート541−iにより出力し、受信機532−iの出力を表す。一実施形態で、DOUTはキャパシタC4により受信する正差分データ信号INPUT+を示す。図5Bの例に示すように、時間TnにおいてピンIN(i−1)‘+およびIN(i−1)‘−に雑音があり、差分信号IN+とIN−の差がオフセット電圧Voffsetにより規定するヒステリシスエリア内にあれば、その場合その雑音は信号DOUTにおいて削除できる。

【0044】

戻って図5Aを参照すると、ディジタルPLL517−iはバッテリ管理チップ410−iのクロックと受信データ信号を同期させ、同期データをコマンドプロセッサ510−iに送信する。コマンドプロセッサ510−iは同期データを処理できる。一実施形態で同期データがホストプロセッサ440からの命令、例えば対応バッテリモジュール402−iの電池電圧をサンプリングするバッテリ管理チップ410−iへの命令である場合、コマンドプロセッサ510−iは同期データのアドレスを対応バッテリ管理チップ410−iのアドレスと比較できる。一実施形態で、アドレスは計数過程で各バッテリ管理チップに割り当てる固有チップ番号でありうる。アドレスが整合すれば、コマンドプロセッサ510−iは応答発生器507−iにデータを送信する。このような一実施形態で、応答発生器507−iはバッテリ管理チップ410−iに命令の実行を指令する、例えばバッテリ管理ユニット411−iに対応バッテリモジュール402−iの電池電圧のサンプリングを指令し、ホストプロセッサ440への応答を発生する。アドレスが整合しなければ、コマンドプロセッサ510−iは同期データを送信機533−iに送信する。図5Aの例に示すように、送信機533−iは複数のインバータ511−i、513−iおよび515−iを含む。インバータ511−iおよび515−iは正差分信号を駆動し、出力でき、513−iは負差分信号を駆動し、出力できる。このように、送信機533−iはピンOUTi+およびOUTi−を介して同期データを示す差分出力データ信号対をバッテリ管理チップ410−(i+1)の垂直バス回路412−(i+1)に出力する。

【0045】

下方データ経路における受信機531−iの要素および構成は受信機532−iにおいて示すのと同じである。それ故、受信機532−iにおけるのと類似の機能を有する受信機531−iの要素は簡潔さおよび明快さのためここでは繰り返して説明しないことにする。

【0046】

図5Aに示すように、図5Cは、垂直バス回路412−iの受信機531−iと関連する信号例を示す。信号INPUT‘+およびINPUT’−は上位バッテリ管理チップ410−(i+1)からそれぞれキャパシタC6およびC7に送信する差分入力データ信号を表す。信号IN ‘+およびIN’−はそれぞれキャパシタC6およびC7を介して受信機531−iにより受信する信号である。信号DOUT‘はNANDゲート552−iにより出力し、受信機531−iの出力を表す。一実施形態で、信号DOUT’はキャパシタC6により受信する正差分データ信号INPUT‘+を示す。図5Cの例に示すように、時間Tn’においてピンINi+およびINi−に存在する雑音があり、差分信号IN’+とIN‘−の差がオフセット電圧Voffsetにより規定するヒステリシスエリア内にあれば、その場合その雑音は信号DOUT’において削除できる。

【0047】

戻って図5Aを参照すると、受信機531−iの出力データ信号をディジタルPLL505−iに送信する。ディジタルPLL505−iはバッテリ管理チップ410−iのクロックと受信データ信号を同期させ、同期データを応答発生器507−iに送信する。一実施形態で、応答発生器507−iは同期データを受信し、同期データを送信機534−iに伝送する。別の実施形態で、応答発生器507−iはホストプロセッサ440からの命令に応じて応答を発生し、送信機534−iを介してホストプロセッサ440に応答を送信する。図5Aの例に示すように、送信機534−iは複数のインバータ504−i、506−iおよび508−iを含む。インバータ504−i並びに506−iは正差分信号を駆動し、出力でき、インバータ508−iは負差分信号を駆動し、出力できる。このように、送信機534−iはピンOUT(i−1)‘+およびOUT(i−1)’−を介してバッテリ管理チップ410−(i−1)の垂直バス回路412−(i−1)に応答発生器507−iから受信するデータを示す差分出力データ信号対を出力する。しかしバッテリ管理チップ410−iが最下位バッテリ管理チップ410−1であれば、送信機534−1はピンOUT0‘+およびOUT0’−を介してコンバータ413に差分出力データ信号対を出力する。コンバータ413は受信差分データ信号対を第1のタイプのプロトコル、例えばSPIバスプロトコルに準拠するデータに変換でき、変換データをホストプロセッサ440に送信できる。

【0048】

有利には図5Aの例に示すように、受信機531−iおよび532−iは比較的低電力消費および簡単な回路を有する。その上、受信機532−i/531−iの差分入力信号の差がオフセット電圧Voffsetにより規定するヒステリシスエリア内にあれば、ピン(例えば、ピンIN(i−1)’+、IN(i−1)‘−、IN+およびIN−)に存在する雑音を削除できる。

【0049】

一実施形態で、垂直バス回路412−iの警報論理522−iは対応バッテリ管理チップ410−iの状態、例えばバッテリ管理チップ410−iの自己テストが完了しているかをホストプロセッサ440に通報し、ホストプロセッサ440からサービスを要求する警報信号を提供できる。警報信号は符号化のため変調器523−iに伝送する。符号化警報信号はピンALT(i−1)‘を介してバッテリ管理チップ410−(i−1)の垂直バス回路412−(i−1)に送信する。一実施形態で符号化警報信号を垂直バス回路412−(i−1)の受信機521−(i−1)により受信する場合、受信機521−(i−1)は受信符号化警報信号を警報論理522−(i−1)に伝送する。警報論理522−(i−1)は受信符号化警報信号を符号化解除し、符号化解除警報信号を符号化のため変調器523−(i−1)に送信する。符号化後、新規符号化警報信号をピンALT(i−2)‘を介して垂直バス回路412−(i−2)に送信し、ホストプロセッサ440にさらに伝送する。別の実施形態で変調器523−1が最下位バッテリ管理チップ410−1にあれば、変調器523−1はピンALT0‘を介して符号化警報信号をコンバータ413に送信できる。コンバータ413は第2のタイプのプロトコルにより通信する受信符号化警報信号を第1のタイプのプロトコルにより通信でき、ピンIRQを介してホストプロセッサ440に伝送できるデータに変換する。

【0050】

図6は本発明の一実施形態に従う図4のバッテリ管理システム400の動作タイミング図600を示す。図6を図4と組み合わせて説明する。t0で、コマンド、例えば計数コマンドをホストプロセッサ440により送信する。計数コマンドを使用してホストプロセッサ120に接続するバッテリ管理チップ総数を判断し、各バッテリ管理チップにそれ自体のアドレスの判断を可能にする。t1で、計数コマンド、初期チップ番号およびチェックデータを含む計数パケットを、コンバータ413を介して最下位バッテリ管理チップ410−1の垂直バス回路412−1により受信する。時間t2で、バッテリ管理チップ410−1の垂直バス回路412−1は計数コマンド、計数回路416−1により発生する新規チップ番号および対応チェックデータを含む計数パケットを発生し、計数パケットをバッテリ管理チップ410−2に送信する。時間t3で、バッテリ管理チップ410−2はバッテリ管理チップ410−1により送信する計数パケットを受信する。時間t4で、バッテリ管理チップ410−2は計数コマンド、計数回路416−2により発生する新規チップ番号および対応チェックデータを含む計数パケットを発生し、その計数パケットをバッテリ管理チップ410−3に送信する。バッテリ管理チップ410−3は時間t5でバッテリ管理チップ410−2により送信する計数パケットを受信する。

【0051】

図4の例に示すように、バッテリ管理チップ410−3は最上位チップである。最上位バッテリ管理チップ410−3がバッテリ管理チップ410−2から計数パケットを受信後時間t6で、最上位バッテリ管理チップ410−3はバッテリ管理チップ410−1、410−2およびホストプロセッサ440に応答を送信する。一実施形態で、応答は計数コマンド並びにバッテリ管理チップ410−3のチップ番号を含みうる。時間t7で、バッテリ管理チップ410−2は応答を受信し、バッテリ管理チップ410−1に応答をさらに送信する。時間t8で、バッテリ管理チップ410−1は応答を受信する。時間t9で、ホストプロセッサ440は応答を受信する。応答を受信すると、最上位バッテリ管理チップのチップ番号に基づき、ホストプロセッサ440はホストプロセッサ440に接続するバッテリ管理チップ総数を判断できる。

【0052】

その上一実施形態で、時間t2でバッテリ管理チップ410−1がバッテリ管理チップ410−2に計数パケットを送信すると、時間t8でバッテリ管理チップ410−1が最上位バッテリ管理チップ410−3から応答を受信するまでに、例えばバッテリ管理チップ410−1のタイマTIMER1は走行を開始する。このようにして、時間ピリオドT1(T1=t8−t2)を計算する。時間t4でバッテリ管理チップ410−2がバッテリ管理チップ410−3に計数パケットを送信すると、時間t7でバッテリ管理チップ410−2がバッテリ管理チップ410−3から応答を受信するまでに、例えばバッテリ管理チップ410−2のタイマTIMER2は走行を開始する。このようにして、時間ピリオドT2を計算する(T2=t7−t4)。

【0053】

時間ピリオドT1およびT2を使用して以下のようにバッテリ管理チップ間の通信遅延を補償する。一実施形態で、ホストプロセッサ440はバッテリ管理チップにブロードキャストコマンドを送信でき、バッテリ管理チップにバッテリモジュールの各電池状態のサンプリングを指令する。例えば時間t10で、ブロードキャストコマンド、例えば電池電圧をサンプリングするサンプリングコマンドをホストプロセッサ440により送信し、各バッテリ管理チップ410−iに対応バッテリモジュール402−iの各電池の電池電圧のサンプリングを指令する。時間t11で、バッテリ管理チップ410−1はサンプリングコマンドを受信する。例えばバッテリ管理チップ410−1の補償タイマは時間ピリオドTD1の間に走行を開始する。一実施形態で、TD1=T1/2である。従って、時間t13で、即ち時間t11の後遅延時間TD1で、バッテリ管理チップ410−1はバッテリモジュール402−1の電池の電池電圧をサンプリングする。同様に時間t12で、バッテリ管理チップ410−2はサンプリングコマンドを受信する。例えばバッテリ管理チップ410−2の補償タイマは時間ピリオドTD2の間に走行を開始する。一実施形態で、TD2=T2/2である。従って、時間t13で、即ち時間t12の後遅延時間TD2で、バッテリ管理チップ410−2もバッテリモジュール402−2の電池電圧をサンプリングする。時間t13で、最上位バッテリ管理チップ410−3はサンプリングコマンドを受信し、バッテリモジュール402−3の電池電圧をまたサンプリングする。有利には、全てのバッテリ管理チップ410−1乃至410−3は同時(t13)に電池状態をサンプリングする。

【0054】

従って、バッテリ管理チップが計数パケットを送信し、計数処理過程で応答を受信する時間の間の遅延(例えば、図6の例でT1およびT2)の計算により、対応時間補償パラメータ(例えば、図6の例でTD1およびTD2)を入手できる。それ故ホストプロセッサ440により送信するブロードキャストコマンドを受信すると、バッテリ管理チップ410−iは遅延の補償後にコマンド、例えば電池電圧のサンプリングを実行できる。有利には、各バッテリ管理チップ410−iはそれ故同時にブロードキャストコマンドを実行できる。

【0055】

図7は本発明の一実施形態に従うバッテリ管理システムにより実行する動作フローチャート700を示す。図7を図4と組み合わせて説明する。特定ステップを図7で開示するが、このようなステップは例示的である。即ち、本発明は種々の他のステップまたは図7で列挙するステップの変形の実行によく適す。

【0056】

図4の例に示すようにブロック702で、ホストプロセッサ、例えばホストプロセッサ440は計数コマンドを発生し、複数のチップ、例えばバッテリ管理チップ410−1乃至410−3に送信し、バッテリ管理チップ総数を判断し、各バッテリ管理チップ410−iにそれ自体のアドレスの判断を可能にする。

【0057】

ブロック704で、バッテリ管理チップは計数コマンドを含む対応計数パケットをチップからチップへ伝達する。より明確には、第1の計数パケットはコンバータ413により発生できる。一実施形態で、第1の計数パケットは計数コマンド、第1のチップ番号および第1のチェックデータを含みうる。第1のチェックデータを使用して前記第1のチップ番号の誤りをチェックできる。第1のバッテリ管理チップ410−1は第1の計数コマンドを受信し、第2のチップ番号および第2のチェックデータを含む第2の計数コマンドパケットを発生し、上方バッテリ管理チップ410−2に第2の計数コマンドパケットを送信する。バッテリ管理チップ410−2は第2の計数パケットを受信し、計数コマンド、第3のチップ番号および第3のチェックデータを含む第3の計数パケットを発生し、上方バッテリ管理チップ410−3に第3の計数パケットを送信する。図4の例に示すように、バッテリ管理チップ410−3は最上位チップである。従って、バッテリ管理チップ410−3は第3の計数パケットを受信するが、一実施形態では対応計数パケットを送信しない。

【0058】

ブロック706で受信計数パケットの情報を使用して、各チップはそれ自体の固有アドレスを判断する。より明確には一実施形態で、対応バッテリ管理チップ410−iにより受信するチップ番号を使用してバッテリ管理チップ410−iのアドレスを表す。そのような一実施形態で図4の例に示すように、バッテリ管理チップ410−3は最上位チップである。それ故、最上位バッテリ管理チップ410−3は新規チップ番号を発生しない。しかし別の実施形態では、バッテリ管理チップ410−iにより発生するチップ番号を使用してその固有アドレスを表すことができ、従って最上位バッテリ管理チップ410−3はバッテリ管理チップ410−3のアドレスを表す新規チップ番号を発生する。

【0059】

一実施形態で、最上位バッテリ管理チップ410−3は他のバッテリ管理チップ410−1および410−2並びにホストプロセッサ440にも応答を送信できる。一実施形態で、応答は計数コマンドおよびバッテリ管理チップ410−3のチップ番号を含む。本チップ番号はバッテリ管理チップ410−3のアドレスを表す。ホストプロセッサ440が応答を受信後、ホストプロセッサ440は、例えばバッテリ管理チップ410−3のチップ番号によりホストプロセッサ440に接続するバッテリ管理チップ総数を判断できる。

【0060】

以上の説明および図面は本発明の実施形態を表すが、添付する特許請求の範囲で規定するように本発明の原理の精神並びに範囲を逸脱することなく、種々の追加、修正並びに置換を本発明において為し得ることが理解されよう。本発明の実施において使用する形態、構成、配置、規模、材料、部品および構成要素他の多くの修正により、本発明を使用することができ、これらは本発明の原理を逸脱することなく、特定の環境並びに動作要求条件に特に適合することを当業者は認識するであろう。ここに開示する実施形態はそれ故あらゆる点で例証的であり、限定的でないと考えるべきであり、本発明の範囲は添付する特許請求の範囲およびその法的等価物により示し、以上の説明に制限されない。

【符号の説明】

【0061】

102−1,102−2,102−3、401−1、401−2、401−3 バッテリモジュール

110−1,110−2,110−3、410−1、410−2、410−3 バッテリ管理チップ

111−1、111−2、111−3、411−1、 411−2、411−3

バッテリ管理ユニット

112−1、112−2、112−3、412−1、412−2、412−3

(垂直)バス回路

116−1、116−2、116−3、116−i、416−1、416−2、

416−3 計数回路(EM)

120、440 ホストプロセッサ

210 チェック回路

211、216、221 XORゲート

212、504−i、506−i、508−i、511−i、513−i、

515−i インバータ

213、223 ANDゲート

214、222 ORゲート

215、224 フリップフロップ

220 チップ番号発生器

230 マルチプレクサ

400 バッテリ管理システム

500、412−1、412−2、412−3 垂直バス回路

512−i、514−i(501−i、503−i) 比較器対

531−i、532−i 受信機

533−i、534−i 送信機

541−i、542−i(551−i)、552−i NANDゲート

543−i、544−i、(553−i、554−i)、566−i、

(568−i) 電圧ソース

562(564) ノード

600 バッテリ管理システムの動作タイミング図

700 バッテリ管理システムにより実行する動作フローチャート

702 ホストプロセッサで計数コマンドを発生

704 計数コマンドを含む対応計数パケットをホストプロセッサに接続する複数の

チップの中のチップからチップへ伝達

706 計数コマンドパケットの情報を使用して各チップはそれ自体の固有アドレス

を判断

【技術分野】

【0001】

本発明は、計数回路(enumerating circuit)を備えたバッテリ管理システムに関する。

[関連出願の相互参照]

本願は本願と同時出願のA.フリッピン(A. Flippin)他による「垂直バス(vertical bus circuit)回路を伴うバッテリ管理システム」と題する書類番号O2−0717−1による出願に関係する。

【背景技術】

【0002】

従来のバッテリ管理システムは複数のバッテリ管理チップおよびバッテリ管理チップに接続するホストプロセッサを含む。複数のバッテリ管理チップは複数のバッテリモジュールに接続でき、バッテリモジュールの状態を監視する。ホストプロセッサはバッテリ管理チップとの通信に使用できる。ホストプロセッサはバッテリ管理チップのアドレスを取得し、その後バッテリ管理チップにアクセスする。従来のバッテリ管理チップはそのアドレスの指示に特別のピン、例えば3本のピンを必要とする。である。

【発明の概要】

【発明が解決しようとする課題】

【0003】

しかし、特別のピンはバッテリ管理チップの無効サイズおよびプリント回路ボード(PCB、printed circuit board)エリアを増大させ、それ故バッテリ管理チップコストが従って増加する。

その上幾つかのアプリケーションでは、ホストプロセッサはブロードキャストコマンドを送信し、全てのバッテリ管理チップにコマンドの同時実行を指令する。しかし通信遅延により、全てのバッテリ管理チップにとりブロードキャストコマンドの同時実行は不可能

【課題を解決するための手段】

【0004】

一実施形態で、システムは複数のチップおよびホストプロセッサを含む。ホストプロセッサは複数のチップに接続し、計数コマンドを送信する。複数のチップは計数コマンドを含む計数パケットをチップからチップへ伝達し、各チップは計数パケットにおける情報を使用してそれ自体の固有アドレスを判断する。

【0005】

別の実施形態で、バッテリ管理チップはバッテリ管理ユニットおよび計数回路を含む。バッテリ管理ユニットはバッテリ管理チップに接続するバッテリモジュールの電池状態を監視し、サンプリングする。計数回路はバッテリ管理ユニットに接続し、計数パケットを受信する。計数パケットは計数コマンドおよび第1の番号を含む。計数回路は計数コマンドに応じ、第1の番号に基づき第2の番号を発生する。 特許請求主題の実施形態が持つ特徴および利点は以下の詳細な説明の進展に従い、同じ番号が同じ部分を表す図面の参照に応じて明らかになろう。

【図面の簡単な説明】

【0006】

【図1】は本発明の一実施形態に従う計数回路を伴うバッテリ管理システム例のブロック図を示す。

【図2】は本発明の一実施形態に従う計数回路例のブロック図を示す。

【図3】は本発明の一実施形態に従う計数回路に関連する信号タイミング図を示す。

【図4】は本発明の一実施形態に従う計数回路を伴うバッテリ管理システム例のブロック図を示す。

【図5A】は本発明の一実施形態に従うバッテリ管理チップにおける垂直バス回路例のブロック図を示す。

【図5B】は本発明の一実施形態に従う垂直バス回路の受信機と関連する信号例を示す。

【図5C】は本発明の一実施形態に従う垂直バス回路の受信機と関連する信号例を示す。

【図6】本発明の一実施形態に従うバッテリ管理システムの動作タイミング図を示す。

【図7】本発明の一実施形態に従うバッテリ管理システムにより実行する動作フローチャートを示す。

【発明を実施するための形態】

【0007】

次に、本発明の実施形態を詳細に参照することにする。本発明をこれらの実施形態と共に説明することにするが、これらの実施形態はそれら自体に本発明を制限すると考えないことが理解されよう。逆に添付する特許請求の範囲により規定するように、本発明は本発明の精神および範囲内に含みうる代替、修正および等価物を包含すると考える。

【0008】

ここで説明する実施形態はプログラムモジュールのようなある形態のコンピュータ使用可能媒体に所在し、1台以上のコンピュータまたはその他のデバイスにより実行する汎用コンテキストコンピュータ実行可能命令において考察できる。一般にプログラムモジュールは、特定のタスクを実行するか、または特定の抽象データタイプを実装するルーティン、プログラム、オブジェクト、構成要素、データ構造などを含む。プログラムモジュールの機能は種々の実施形態において所望の如く結合または分散できる。

【0009】

以下の詳細な説明のある部分をコンピュータメモリ内のデータビット演算に関する手順、論理ブロック、処理およびその他のシンボリック表現により提示する。これらの説明および表現は当業者の作業内容を他の当業者に最も効率的に伝達するのにデータ処理技術の当業者により使用する手段である。本出願で、手順、論理ブロック、処理または同類は所望の結果に導くステップ若しくは命令の自己完結シーケンスであると考える。ステップは物理量の物理的操作を必要とするものである。必然的ではないが通常、これらの量はコンピュータシステムにおいて蓄積、伝送、結合、比較およびその他の操作を行いうる電気的または磁気的信号の形態を取る。

【0010】

とはいえ、全てのこれらおよび類似の用語は適する物理量に関連すべきであり、これらの量に適用する単に便利なラベルであることを留意すべきである。以下の考察から明らかなように別途特に記述しない限り、本出願を通じて「送信」、「検出」、「変換」、「比較」、「判断」または同類のような用語を利用する考察は、コンピュータシステムレジスタおよびメモリ内において物理(電子)量として表すデータを操作し、コンピュータシステムメモリまたはレジスタ若しくは他のそのような情報蓄積、伝送または表示デバイス内の物理量として同様に表す他のデータに変換する、コンピュータシステムまたは類似の電子計算デバイスの動作および処理に関連すると認識する。

【0011】

制限するのではなく例として、コンピュータ使用可能媒体はコンピュータ蓄積媒体および通信媒体を含みうる。コンピュータ蓄積媒体はコンピュータ可読命令、データ構造、プログラムモジュールまたはその他のデータのような任意の情報蓄積方法若しくは技術において実装する揮発性並びに不揮発性、取り外し可能および取り外し不可能媒体を含む。コンピュータ蓄積媒体は以下に限らないが、所望の情報の蓄積に使用できるランダムアクセスメモリ(RAM、random access memory)、読み出し専用メモリ(ROM、read only memory)、電気的消去可能プログラマブルROM(EEPROM、electrically erasa-ble programmable ROM)、フラッシュメモリまたはその他のメモリ技術、コンパクトディスクROM(CD−ROM、compact disk ROM)、ディジタル多用途ディスク(DVD、digital versatile disks)若しくはその他の光学的蓄積装置、磁気カセット、磁気テープ、磁気ディスク蓄積装置またはその他の磁気蓄積デバイス、若しくは任意の他の媒体を含む。

【0012】

通信媒体はコンピュータ可読命令、データ構造、プログラムモジュールまたは搬送波若しくは他の伝送機構のような変調データ信号における他のデータを表すことができ、任意の情報配信媒体を含む。用語「変調データ信号」は1つ以上のその特徴セットを有するか、若しくは情報を信号に符号化するように変化した信号を意味する。制限するのではなく例として、通信媒体は有線ネットワーク若しくは直接有線接続のような有線媒体および音響、無線周波数(RF、radio frequency)、赤外線並びにその他の無線媒体のような無線媒体を含む。任意の上記の組み合わせもコンピュータ可読媒体の範囲内に含むべきである。

【0013】

その上さらに本発明の以下の詳細な説明で、本発明の完全な理解をもたらすため、多くの特定の詳細を示す。しかし、本発明をこれらの特定の詳細以外において実行しうることは当業者により認識されよう。その他の場合、本発明の態様を不要に不明確にしないため、周知の方法、手順、構成要素および回路は詳細に説明していない。

【0014】

図1は本発明の一実施形態に従う計数回路を伴うバッテリ管理システム例100のブロック図を示す。一実施形態で、バッテリ管理システム100は直列に接続する複数のバッテリモジュール102−i、例えば102−1、102−2および102−3、バッテリモジュール102−1、102−2および102−3にそれぞれ接続するバッテリ管理チップ110−i、例えば110−1、110−2および110−3並びにバッテリ管理チップ110−1に接続するホストプロセッサ120を含む。図1に示す実施形態は例証を目的とするのみであるので、バッテリ管理チップ数はバッテリ管理チップを使用する特定アプリケーションの要求に応じて任意の数でありうる。

【0015】

バッテリモジュール102−iは1個以上のバッテリ電池、例えば図1の例に示すように4個のバッテリ電池をさらに含む。バッテリ管理チップ110−1、110−2および110−3はバスを介して互いに直列に接続する。各バッテリ管理チップ110−iは対応バッテリ管理ユニット111−iおよび対応バス回路112−iを含む。バッテリ管理ユニット111−iはホストプロセッサ120から受信する命令に従い対応バッテリモジュール102−iにおける各バッテリ電池の状態(例えば、電池電圧)を監視し、サンプリングできる。バス回路112−iは計数回路116−iを含み、バッテリ管理ユニット111−iとホストプロセッサ120間の信号を伝送する。

【0016】

一実施形態で、ホストプロセッサ120は計数コマンドをバッテリ管理チップに送信し、各バッテリ管理チップにそれ自体のアドレスの判断を可能にする。一実施形態で、固有チップ番号を各バッテリ管理チップ110−iに割り当て、バッテリ管理チップ110−iのアドレスを表す。このような一実施形態で、ホストプロセッサ120は計数コマンドおよび初期チップ番号を含む計数パケットを送信する。計数パケットを受信すると、バス回路112−iにおける計数回路116−iは受信計数パケットにおけるチップ番号に基づき、例えば新規チップ番号を発生するため1だけ受信チップ番号を増進させることにより新規チップ番号を発生できる。一実施形態で、バッテリ管理チップ110−iのアドレスを表すのに発生する新規チップ番号を使用できる。別の実施形態で、バッテリ管理チップ110−iのアドレスを表すのに受信チップ番号を使用でき、上方バッテリ管理チップ110−(i+1)のアドレスを表すのに発生する新規チップ番号を使用できる。このような一実施形態では図1の例に示すように、バッテリ管理チップ110−3は最上位チップである。それ故、最上位バッテリ管理チップ110−3における計数回路116−3は新規チップ番号を発生しない。

【0017】

一実施形態で、計数パケットはチェックデータをさらに含み、計数回路116−iはチェックデータに従い、例えばチェックデータの受信チップ番号との比較により、受信チップ番号をチェックする。受信チップ番号に誤りがあれば、バッテリ管理チップ110−iは受信計数パケットを廃棄でき、ホストプロセッサ120はこの場合新規計数パケットを再送し、そのバッテリ管理チップ110−iのアドレスを判断できる。

【0018】

有利には各バッテリ管理チップ110−iのアドレスを表す固有チップ番号の使用により、バッテリ管理チップ110−iのアドレスの指示に従来使用するピンを除去する。従って、バッテリ管理チップ110−iのピン数は減少する。それ故、無効サイズおよびバッテリ管理チップのプリント回路ボード(PCB)エリアは減少し、バッテリ管理チップコストは従って減少する。

【0019】

図2は、本発明の一実施形態に従う図1の計数回路例116−iのブロック図を示す。計数回路116−iはチェック回路210、チップ番号発生器220およびマルチプレクサ(MUX、multiplexer)230を含む。チップ番号発生器220は計数パケットを受信する第1の端子DATA_IN(データ_イン)並びに信号FIRST_CHIP_BIT(第1の_チップ_ビット)を受信する第2の端子を含む。一実施形態で、計数パケットにおけるチップ番号の第1のビットを端子DATA_INで受信する場合、信号FIRST_CHIP_BITはハイである。チップ番号発生器220は計数パケットのチップ番号を受信し、例えば1だけ受信チップ番号を増進させることにより新規チップ番号をマルチプレクサ230に出力する。図2の例で、チップ番号発生器220はXORゲート221、ORゲート222、ANDゲート223およびフリップフロップ224を含む。

【0020】

チェック回路210は計数パケットのチップ番号を受信する端子CHIP_IN「n」およびチップ番号発生器220により発生する新規チップ番号を受信する端子CHIP_OUT「n」を含む。一実施形態で、チェック回路210はチェック処理において端子DATA_INを介して計数パケットにおけるチェックデータをさらに受信する。チップ番号発生器220が新規チップ番号を発生後、チェック回路210により受信する信号START_CHECKはハイである。次いで、チェック回路210は端子DATA_INで受信するチェックデータを端子CHIP_IN「n」で受信するチップ番号と比較し、誤りが受信チップ番号に生じたかを示す信号CHECK_OKを発生する。その上、チェック回路210はMUX230に対する新規チェックデータを発生でき、新規チェックデータを使用してチップ番号発生器220により発生する新規チップ番号における誤りをチェックする。一実施形態で、チェックデータは計数回路116−iにより受信するチップ番号の反転である。図2の例で、チェック回路210はXORゲート211および216、インバータ212、ANDゲート213、ORゲート214およびフリップフロップ215を含む。

【0021】

MUX230はチップ番号発生器220により発生する新規チップ番号およびチェック回路210により発生する新規チェックデータを受信する。より明確には、MUX230の第1の入力端子Aはチップ番号発生器220に接続し、MUX230の第2の入力端子Bはチェック回路210に接続する。MUX230の選択端子Sは発生処理とチェック処理間の選択信号CHECKING_WINDOW(チェック中_ウインドウ)を受信する。発生処理過程で、MUX230はチップ番号発生器220により発生する新規チップ番号を提供する。チェック処理過程で、MUX230はチェック回路210により発生する新規チェックデータを提供する。

【0022】

図3は本発明の一実施形態に従う図2の計数回路116−iに関連する信号タイミング図を示す。図3を図2と組み合わせて説明する。計数パケットを端子DATA_INで受信する。図3の例で、計数パケットは幾つかのアイドルビット、プレアンブルP、計数コマンド、チップ番号(例えば、CHIP_NUM(チップ_番号)[0:5]、ここでCHIP_NUM[0]は最下位ビットであり、CHIP_NUM[5]は最上位ビットである)およびチェックデータ(例えば、CHECK(チェック)[0:5]、ここでCHECK[0]は最下位ビットであり、CHECK[5]は最上位ビットである)を含む。一実施形態で、計数コマンドをホストプロセッサ120により送信し、ホストプロセッサ120に接続するバッテリ管理チップ総数を判断し、各バッテリ管理チップにそれ自体のアドレスの判断を可能にする。一実施形態で、チェックデータCHECK[0:5]はチップ番号CHIP_NUM[0:5]の反転である。

【0023】

一実施形態で、チップ番号、例えばCHIP_NUM[0:5]を計数コマンドの後で受信する。チップ番号CHIP_NUM[0]の第1のビットを端子DATA_INで受信すると、信号FIRST_CHIP_BITはハイになり、これは発生処理を開始したことを示す。従って、ORゲート222の出力信号CARRY(キャリー)はサイクル(時間ピリオド)T0中にハイになる。サイクルTn+1(例えば、n=0、1、2、3および4)中の信号CARRYは対応入力ビットCHIP_NUM[n]に依存する。例えば入力ビットCHIP_NUM[n]がディジタルの1であれば、信号CARRYはクロックBIT_CLK(ビット_クロック)の次サイクルTn+1の間ハイである。しかし入力ビットCHIP_NUM[n]がディジタルの0であれば、入力ビットCHIP_NUM[n+1:5]がディジタルの0または1であるかにかわらず、信号CARRYは次サイクルTn+1からT5迄の間ローに留まる。それ故XORゲート221の使用により、チップ番号発生器220は、例えば受信チップ番号CHIP_NUM[0:5]を1だけ増進させたに等しい新規チップ番号を発生する。例えばチップ番号CHIP_NUM[0:5]がT0乃至T5の間110010であれば、信号CARRYはT0乃至T5の間111000であり、チップ番号発生器220は新規チップ番号CHIP_NUM‘[0:5]001010(CHIP_NUM’[0]は最下位ビットであり、CHIP_NUM‘[5]は最上位ビットである)を発生する。(垂直バスで、最下位ビットを最初に伝送し、CHIP_NUM[0]は最下位ビットであり、CHIP_NUM[5]は最上位ビットである。CHIP_NUM[0:5]が110010であれば、新規発生番号CHIP_NUM’[0:5]は001010であり、これは実際にチップ番号が010011であることを意味し、新規発生チップ番号は010100であり、これは010011を1だけ増進させたものである。)発生処理過程で、MUX230の選択端子Sで受信する信号CHECK_WINDOW(チェック_ウインドウ)はローになる。結果として、MUX230の出力DATA_OUT(データ_出口)はチップ番号発生器220の出力である。

【0024】

信号START_CHECK(開始_チェック)がハイになると、チェック処理が始まる。結果として、ORゲート214の出力信号CHECK_OK(チェック_OK)がハイになる。クロックBIT_CLKの次サイクルT0‘の間に信号START_CHECKはローになる。従って、信号CHECK_OKはANDゲート213の出力により決定する。チェックデータCHECK[0:5]をT0‘からT5‘の間に入力端子DATA_INで受信する。チェック処理が完了するまで、信号END_CHECK(終了_チェック)はローに留まる。結果として、インバータ212の出力はハイに留まる。チェックデータCHECK[0:5]は一実施形態ではチップ番号CHIP_NUM[0:5]の反転である。結果として、信号CHECK_OKはT0‘乃至T5‘の間ハイに留まり、これはチップ番号CHIP_NUM[0:5]において誤りが生じなかったことを示す。その間に、入力端子CHIP_OUT(チップ_出口)「n」はチップ番号発生器220により発生する新規チップ番号CHIP_NUM’[0:5]を受信する。チップ番号CHIP_NUM[n]に誤りがなければ、信号CHECK_OKはTn‘の間ハイに留まり、XORゲート216は端子CHIP_OUT「n」で受信するデータビットの反転である新規チェックデータビットを発生する。従って新規チェックデータを発生し、これはチップ番号発生器220により発生する新規チップ番号の反転である。T0‘からT5‘のチェック処理の間、MUX230の選択端子Sで受信する信号CHECK_WINDOWはハイに留まる。結果として、MUX230の出力DATA_OUTはチェック回路210の出力である。サイクルT5‘の後、信号CHECK_WINDOWは再びローになり、これはチェック処理が完了したことを示す。

【0025】

一実施形態で、バス回路112−iは計数コマンド、新規チップ番号および新規対応チェックデータを含む新規計数パケットを対応バッテリ管理チップ110−(i+1)の上方バス回路112−(i+1)に次いで送信する。一実施形態で、バッテリ管理チップ110−iが最上位バッテリ管理チップであれば、バッテリ管理チップ110−iはホストプロセッサ120にも送信しうる応答をバッテリ管理チップ110−(i−1)に送信する。応答は計数コマンドおよびバッテリ管理チップ110−iのチップ番号を含みえ、ホストプロセッサ120は応答のチップ番号に従いバッテリ管理システムのバッテリ管理チップ総数を判断できる。しかし信号CHECK_OKがT0‘乃至T5‘の間何時もローであることをバス回路112−iが検出すれば、チェック回路210はチップ番号発生器220により発生する新規チップ番号の反転でないチェックデータを発生する。この場合、上位バッテリ管理110−(i+1)はチップ番号またはチェックデータに誤りが発生したことを検出でき、計数パケットを廃棄でき、ホストプロセッサ120は新規計数コマンドを再送でき、ホストプロセッサ120に接続するバッテリ管理チップ総数を判断し、各バッテリ管理チップにそれ自体のアドレスの判断を可能にするようにする。

【0026】

図4は本発明の一実施形態に従う図2の計数回路を伴うバッテリ管理システム例400のブロック図を示す。一実施形態で、バッテリ管理システム400は直列に接続するバッテリモジュール402−i、例えば402−1、402−2および402−3、バッテリモジュール402−1、402−2および402−3にそれぞれ接続するバッテリ管理チップ410−i、例えば410−1、410−2および410−3およびバッテリ管理チップ410−1に接続するホストプロセッサ440を含む。図4に示す実施形態は例証を目的とするのみであるので、バッテリ管理チップ数は特定アプリケーションの要求に応じて任意の数でありうる。

【0027】

バッテリモジュール402−iは1個以上のバッテリ電池、例えば図4の例に示すように6個のバッテリ電池をさらに含む。バッテリ管理チップ410−1、410−2および410−3は1個以上の直流絶縁器を介して互いに接続する。一実施形態で、直流絶縁器はパッシブ絶縁器であり、従って直流絶縁器に電力を供給する追加電力供給を必要としない。例えば、複数個のキャパシタC1乃至C10はバッテリ管理システム400においてバッテリ管理チップ410−1乃至410−3の直流絶縁に使用できる。図4の例に示すように、バッテリ管理チップ410−3はキャパシタC6乃至C10を介してバッテリ管理チップ410−2に接続し、バッテリ管理チップ410−2はキャパシタC1乃至C5を介してバッテリ管理チップ410−1に接続する。別の実施形態では、複数の変圧器即ちインダクタもバッテリ管理システム400においてバッテリ管理チップ410−1乃至410−3の直流絶縁に使用できる。隣接バッテリ管理チップ間における直流絶縁器の使用により、バッテリ管理チップを直流絶縁し、隣接バッテリモジュール間に接続断が生じれば損傷から保護しうる。その上パッシブ直流絶縁器の使用により、バッテリ管理システムコストを削減する。

【0028】

一実施形態で、各バッテリ管理チップ410−iは対応バッテリ管理ユニット411−iおよび対応垂直バス回路412−iを含む。バッテリ管理ユニット411−iはホストプロセッサ440から受信する命令により対応バッテリモジュール402−iにおける各バッテリ電池の状態(例えば、電池電圧)を監視し、サンプリングできる。垂直バス回路412−iはバッテリ管理ユニット411−iとホストプロセッサ440間の信号を伝送する。一実施形態で、垂直バス回路412−iは計数回路416−iをさらに含む。図4に示すように、計数回路416−iの構成及び動作は図2の計数回路116−iに類似し、従って繰り返す説明は簡潔さおよび明快さのためここでは省略する。

【0029】

一実施形態で、垂直バス回路412−iはピンIN(入口)(i−1)’+およびIN(i−1)’を介して下位バッテリ管理チップ410−(i−1)から第1の差分入力データ信号対(例えば、正差分信号INPUT(入力)+および負差分信号INPUT−)を受信し、それぞれピンOUT(出口)i+およびOUTi−を介して上位バッテリ管理チップ410−(i+1)に第1の差分出力データ信号対(例えば、正差分信号OUTPUT(出力)+および負差分信号OUTPUT−)を出力する。垂直バス回路412−iはピンINi+およびINi−を介して上位バッテリ管理チップ410−(i+1)から第2の差分入力データ信号対をさらに受信し、ピンOUT(i−1)’+およびOUT(i−1)’を介して下位バッテリ管理チップ410−(i−1)に第2の差分出力データ信号対を出力する。一実施形態で、バッテリ管理チップ410−3のピンIN3+、IN3−,OUT3+、およびOUT3−を接地する、これはバッテリ管理チップ410−3が最上位チップであることを示す。それ故、バッテリ管理チップ410−3はピンIN3+およびIN3−を介して第2の差分入力データ信号対を受信しないが、バッテリ管理チップ410−3はピンOUT2‘+およびOUT2’−を介して下位バッテリ管理チップ410−2に第2の差分出力データ信号対を出力できる。一実施形態で、最下位バッテリ管理回路410−1の垂直バス回路412−1はピンIN0‘+およびIN0’−を介してコンバータ413から第1の差分入力データ信号対を受信し、ピンOUT1+およびOUT1−を介して上位バッテリ管理チップ410−2に第1の差分出力データ信号対を出力する。垂直バス回路412−1はピンIN1+およびIN1−を介してバッテリ管理チップ410−2から第2の差分入力データ信号対をさらに受信し、ピンOUT0‘+およびOUT0’−を介してコンバータ413に第2の差分出力データ信号対を出力する。垂直バス回路412−iはホストプロセッサ440に対応バッテリ管理チップ410−iの状態(例えば、バッテリ管理チップ410−iの自己テストが完了しているか)を通報し、ホストプロセッサ440からサービスを要求する警報信号をピンALT(警報)(i−1)‘を介してさらに提供できる。警報信号を下位バッテリ管理チップ410−(i−1)に送信し、ホストプロセッサ440にさらに伝送する。

【0030】

有利には差分入力/出力データ信号の使用により、垂直バスにおける雑音を削減または除去する。その上一実施形態で差分データ信号を伝送中の任意のバスにおける異常状態(例えば、回路開放または回路短絡)の場合、他の差分信号対の単一線路の使用により通信を継続できる。別の実施形態で丁度説明するような異常状態が生じれば、差分入力/出力データ信号の送信に他の線路対を使用することにより通信を継続できる。このように、差分入力/出力データ信号の伝送線路は両方向モードで動作できる。

【0031】

一実施形態で図4の例に示すように、コンバータ413はホストプロセッサ440および垂直バス回路412−1に接続する。コンバータ413は第1のタイプのプロトコル、例えば直列周辺インタフェース(SPI、Serial Peripheral Interface)バスプロトコルを使用してホストプロセッサ440と通信する。コンバータ413とホストプロセッサ440間で伝送する信号はピンSDOを介してコンバータ413からホストプロセッサ440に伝送する出力データ信号、ピンIRQを介してコンバータ413からホストプロセッサ440に伝送する要求信号、ピンSDIを介してホストプロセッサ440からコンバータ413に伝送する入力データ信号並びにピンSCKおよびピン/CSをそれぞれ介してホストプロセッサ440からコンバータ413に伝送するクロック信号並びに稼働信号を含む。一実施形態で、コンバータ413は第2のタイプのプロトコル、例えば垂直バスプロトコルを使用して垂直バス回路412−1と通信し、バッテリ管理チップ410−iは第2のタイプのプロトコル、例えば垂直バスプロトコルを使用して隣接バッテリ管理チップ410−(i+1)および410−(i−1)と通信する。コンバータ413は第1のタイプのプロトコルを使用して通信し、ピンSDIを介してホストプロセッサ440から受信するデータを第2のタイプのプロトコルを使用して通信でき、ピンIN0‘−およびIN0’+を介して垂直バス回路412−1に伝送できる差分データ信号対に変換できる。同様に、コンバータ413は第2のタイプのプロトコルにより通信し、ピンOUT0‘−およびOUT0’+を介して垂直バス回路412−1から受信する差分データ信号対を第1のタイプのプロトコルにより通信でき、ピンSDOを介してホストプロセッサ440に伝送できるデータへの変換もできる。図4の例で、コンバータ413はバッテリ管理チップ410−1に統合する。とはいえ、コンバータ413はバッテリ管理チップ410−1の外部に位置することもできる。

【0032】

動作では、ホストプロセッサ440はピンSDIを介してバッテリ管理チップ410−1に計数コマンドを送信し、ホストプロセッサ440に接続するバッテリ管理チップ総数を判断し、各バッテリ管理チップ410−iにそれ自体のアドレスの判断を可能にする。一実施形態で、各バッテリ管理チップ410−iに対応バッテリ管理チップのアドレスを表す固有チップ番号を割り当てる。例えばホストプロセッサ440から計数コマンドを受信すると、コンバータ413は初期化チップ番号、例えば000000を発生する。コンバータ413は計数誤りチェックのためチェックデータも発生でき、例えばチェックデータは初期化チップ番号の反転、例えば111111である。一実施形態で、コンバータ413は計数コマンド、初期化チップ番号およびチェックデータを含む計数パケットをバッテリ管理チップ410−1の垂直バス回路412−1に送信する。コンバータ413により送信する計数パケットは垂直バスプロトコルに準拠する。

【0033】

コンバータ413から計数パケットを受信すると、垂直バス回路412−1は計数パケットの初期化チップ番号を垂直バス回路412−1のレジスタに蓄積できる。垂直バス回路412−1の計数回路416−1は例えば受信計数パケットにおける初期化チップ番号の増進により新規チップ番号(例えば、000001)をさらに発生し、対応チェックデータ(例えば、111110)、例えば新規チップ番号の反転を発生し、計数コマンド、新規チップ番号および対応チェックデータを含む計数パケットを一実施形態ではバッテリ管理チップ410−2の垂直バス回路412−2に送信する。垂直バス回路412−2および412−3の動作は垂直バス回路412−1の動作と同じであり、従って繰り返す説明は簡潔さおよび明快さのためここでは省略する。

【0034】

一実施形態で、対応バッテリ管理チップ410−iの垂直バス回路412−iにより受信するチップ番号を使用してバッテリ管理チップ410−iのアドレスを表す。このような一実施形態では図4の例に示すように、バッテリ管理チップ410−3における垂直バス回路412−3のピンIN3+、IN3−,OUT3+、OUT3−およびALT3を接地する、これはバッテリ管理チップ410−3が最上位チップであることを示す。それ故、最上位バッテリ管理チップ410−3の垂直バス回路412−3は新規チップ番号を発生しない。とはいえ別の実施形態では、垂直バス回路412−iにより発生するチップ番号を使用してバッテリ管理チップ410−iのアドレスを表し、従って最上位バッテリ管理チップ410−3の垂直バス回路412−3はバッテリ管理チップ410−3のアドレスを表す新規チップ番号を発生する。

【0035】

一実施形態で最上位バッテリ管理チップ410−3が計数パケットを受信(そして新規チップ番号を使用してバッテリ管理チップ410−iのアドレスを表すのであれば、新規チップ番号を発生)後、最上位バッテリ管理チップ410−3は他のバッテリ管理チップ410−1および410−2並びにホストプロセッサ440にも応答を送信する。一実施形態では、応答は計数コマンドおよび最上位バッテリ管理チップのチップ番号(例えば、図4の例に示すようにバッテリ管理チップ410−3)を含む。ホストプロセッサ440が応答を受信後、例えば最上位バッテリ管理チップのチップ番号により、ホストプロセッサ440はホストプロセッサ440に接続するバッテリ管理チップ総数を判断できる。

【0036】

図5Aは本発明の一実施形態に従う図4のバッテリ管理チップ410−iにおける垂直バス回路例412−iのブロック図を示す。図5Aを図4と組み合わせて説明する。

【0037】

一実施形態で、垂直バス回路412−iは下方データ経路、上方データ経路および警報データ経路を含む。上方データ経路は受信機532−i、ディジタル位相ロックループ(PLL、phase-locked loop)517−i、コマンドプロセッサ510−i並びに送信機533−iを含む。コマンドプロセッサ510−iは計数回路516−iをさらに含みうる。下方データ経路は受信機531−i、ディジタル位相ロックループ(PLL)505−i、応答発生器507−iおよび送信機534−iを含む。警報データ経路は受信機521−i、警報論理522−i並びに変調器523−iを含む。

【0038】

受信機532−iはピンIN(i−1)‘+およびIN(i−1)‘−を介して第1の差分入力データ信号対INPUT+並びにINPUT−を受信する比較器対512−iおよび514−iを含む。例えば、ピンIN(i−1)‘+は差分信号の正差分信号INPUT+を受信し、ピンIN(i−1)‘−は差分信号の負差分信号INPUT−を受信する。共通モード電圧VCM1をノード562で電圧ソース566−iにより供給し、それぞれキャパシタC4およびC3を介して受信機532−iにより受信する(図5Aの例には図示しない)信号IN+並びにIN−に定常状態電圧を供給する。

【0039】

一実施形態で、オフセット電圧Voffsetを提供し、受信機532−iの出力信号DOUTおよびさらに雑音排除並びに高周波信号排除ヒステリシスエリアを規定する。図5Aの例に示すように、比較器512−iの非反転端子は埋め込みオフセット電圧発生器、例えば電圧ソース543−iを通じて比較器514−iの反転端子に接続する。比較器514−iの非反転端子は埋め込みオフセット電圧発生器、例えば電圧ソース544−iを通じて、図5Aの例に示すように比較器512−iの反転端子に接続する。電圧ソース543−iおよび電圧ソース544−iそれぞれを跨ぐ電圧はVoffsetに等しい。図5Aの例に示すように、電圧ソース544−iの負端子は比較器512−iの反転端子に接続し、電圧ソース543−iの負端子は比較器514−iの反転端子に接続する。別の実施形態で、電圧ソース544−iの正端子は比較器512−iの非反転端子に接続することもできる。電圧ソースの正端子は比較器514−iの非反転端子に接続できる。

【0040】

一実施形態で図5Aの例に示すように、埋め込みオフセット電圧発生器は電圧ソースにより実装できる。別の実施形態で、埋め込みオフセット電圧発生器は抵抗を通じて流れる電流を有する抵抗により代わって実装できる。

【0041】

図5Aの例に示すように、比較器512−iおよび514−iのそれぞれはNANDゲートに接続する。例えば、比較器512−iの出力はNANDゲート542−iに接続し、比較器514−iの出力はNANDゲート541−iに接続する。NANDゲート541−iの出力はディジタルPLL517−iに接続し、ピンIN(i−1)‘+で受信する正差分データ信号INPUT+を示すデータ信号DOUT(D出口)を同期のためディジタルPLL517−iに提供する。別の実施形態で、NAND542−iの出力はディジタルPLL517−iに接続でき、ピンIN(i−1)‘−で受信する負差分データ信号INPUT−を示す出力データ信号をディジタルPLL517−iに提供する。一実施形態で、比較器512−iおよび514−iは差分入力比較器に統合できる。

【0042】

一実施形態で図5Aの例に示すように、比較器512−iおよび514−i、オフセット電圧発生器544−i並びに543−iおよびNANDゲート541−i並びに542−iは受信機532−iの出力信号DOUTのヒステリシスユニットとして実装できる。信号IN+とIN−間の差分がオフセット電圧Voffsetより大きければ、出力信号DOUTは論理的ローまたは論理的ハイでありうる。より明確には、出力信号DOUTは式(1)により与えるように論理的ハイでありうる:

VIN+−VIN−>Voffset (1)

出力信号DOUTは式(2)により与えるように論理的ローでありうる:

VIN+−VIN−<−Voffset (2)

式(3)で示すように信号IN+とIN−間の差分がオフセット電圧Voffsetより小さければ、出力信号DOUTはその前の状態を維持し、変化しない。

|VIN+−VIN−|<Voffset (3)

【0043】

図5Aに示すように、図5Bは垂直バス回路412−iの受信機532−iに関連する信号例を示す。信号INPUT+およびINPUT−は下位バッテリ管理チップ410−(i−1)からそれぞれキャパシタC4並びにC3に送信する差分入力データ信号を表す。別の実施形態で、バッテリ管理チップが最下位バッテリ管理チップ410−1であれば、信号INPUT+およびINPUT−はコンバータ413からの差分入力データ信号を表す。信号IN+並びにIN−はそれぞれキャパシタC4およびC3を介して受信機532−iにより受信する信号である。信号DOUTはNANDゲート541−iにより出力し、受信機532−iの出力を表す。一実施形態で、DOUTはキャパシタC4により受信する正差分データ信号INPUT+を示す。図5Bの例に示すように、時間TnにおいてピンIN(i−1)‘+およびIN(i−1)‘−に雑音があり、差分信号IN+とIN−の差がオフセット電圧Voffsetにより規定するヒステリシスエリア内にあれば、その場合その雑音は信号DOUTにおいて削除できる。

【0044】

戻って図5Aを参照すると、ディジタルPLL517−iはバッテリ管理チップ410−iのクロックと受信データ信号を同期させ、同期データをコマンドプロセッサ510−iに送信する。コマンドプロセッサ510−iは同期データを処理できる。一実施形態で同期データがホストプロセッサ440からの命令、例えば対応バッテリモジュール402−iの電池電圧をサンプリングするバッテリ管理チップ410−iへの命令である場合、コマンドプロセッサ510−iは同期データのアドレスを対応バッテリ管理チップ410−iのアドレスと比較できる。一実施形態で、アドレスは計数過程で各バッテリ管理チップに割り当てる固有チップ番号でありうる。アドレスが整合すれば、コマンドプロセッサ510−iは応答発生器507−iにデータを送信する。このような一実施形態で、応答発生器507−iはバッテリ管理チップ410−iに命令の実行を指令する、例えばバッテリ管理ユニット411−iに対応バッテリモジュール402−iの電池電圧のサンプリングを指令し、ホストプロセッサ440への応答を発生する。アドレスが整合しなければ、コマンドプロセッサ510−iは同期データを送信機533−iに送信する。図5Aの例に示すように、送信機533−iは複数のインバータ511−i、513−iおよび515−iを含む。インバータ511−iおよび515−iは正差分信号を駆動し、出力でき、513−iは負差分信号を駆動し、出力できる。このように、送信機533−iはピンOUTi+およびOUTi−を介して同期データを示す差分出力データ信号対をバッテリ管理チップ410−(i+1)の垂直バス回路412−(i+1)に出力する。

【0045】

下方データ経路における受信機531−iの要素および構成は受信機532−iにおいて示すのと同じである。それ故、受信機532−iにおけるのと類似の機能を有する受信機531−iの要素は簡潔さおよび明快さのためここでは繰り返して説明しないことにする。

【0046】

図5Aに示すように、図5Cは、垂直バス回路412−iの受信機531−iと関連する信号例を示す。信号INPUT‘+およびINPUT’−は上位バッテリ管理チップ410−(i+1)からそれぞれキャパシタC6およびC7に送信する差分入力データ信号を表す。信号IN ‘+およびIN’−はそれぞれキャパシタC6およびC7を介して受信機531−iにより受信する信号である。信号DOUT‘はNANDゲート552−iにより出力し、受信機531−iの出力を表す。一実施形態で、信号DOUT’はキャパシタC6により受信する正差分データ信号INPUT‘+を示す。図5Cの例に示すように、時間Tn’においてピンINi+およびINi−に存在する雑音があり、差分信号IN’+とIN‘−の差がオフセット電圧Voffsetにより規定するヒステリシスエリア内にあれば、その場合その雑音は信号DOUT’において削除できる。

【0047】

戻って図5Aを参照すると、受信機531−iの出力データ信号をディジタルPLL505−iに送信する。ディジタルPLL505−iはバッテリ管理チップ410−iのクロックと受信データ信号を同期させ、同期データを応答発生器507−iに送信する。一実施形態で、応答発生器507−iは同期データを受信し、同期データを送信機534−iに伝送する。別の実施形態で、応答発生器507−iはホストプロセッサ440からの命令に応じて応答を発生し、送信機534−iを介してホストプロセッサ440に応答を送信する。図5Aの例に示すように、送信機534−iは複数のインバータ504−i、506−iおよび508−iを含む。インバータ504−i並びに506−iは正差分信号を駆動し、出力でき、インバータ508−iは負差分信号を駆動し、出力できる。このように、送信機534−iはピンOUT(i−1)‘+およびOUT(i−1)’−を介してバッテリ管理チップ410−(i−1)の垂直バス回路412−(i−1)に応答発生器507−iから受信するデータを示す差分出力データ信号対を出力する。しかしバッテリ管理チップ410−iが最下位バッテリ管理チップ410−1であれば、送信機534−1はピンOUT0‘+およびOUT0’−を介してコンバータ413に差分出力データ信号対を出力する。コンバータ413は受信差分データ信号対を第1のタイプのプロトコル、例えばSPIバスプロトコルに準拠するデータに変換でき、変換データをホストプロセッサ440に送信できる。

【0048】

有利には図5Aの例に示すように、受信機531−iおよび532−iは比較的低電力消費および簡単な回路を有する。その上、受信機532−i/531−iの差分入力信号の差がオフセット電圧Voffsetにより規定するヒステリシスエリア内にあれば、ピン(例えば、ピンIN(i−1)’+、IN(i−1)‘−、IN+およびIN−)に存在する雑音を削除できる。

【0049】

一実施形態で、垂直バス回路412−iの警報論理522−iは対応バッテリ管理チップ410−iの状態、例えばバッテリ管理チップ410−iの自己テストが完了しているかをホストプロセッサ440に通報し、ホストプロセッサ440からサービスを要求する警報信号を提供できる。警報信号は符号化のため変調器523−iに伝送する。符号化警報信号はピンALT(i−1)‘を介してバッテリ管理チップ410−(i−1)の垂直バス回路412−(i−1)に送信する。一実施形態で符号化警報信号を垂直バス回路412−(i−1)の受信機521−(i−1)により受信する場合、受信機521−(i−1)は受信符号化警報信号を警報論理522−(i−1)に伝送する。警報論理522−(i−1)は受信符号化警報信号を符号化解除し、符号化解除警報信号を符号化のため変調器523−(i−1)に送信する。符号化後、新規符号化警報信号をピンALT(i−2)‘を介して垂直バス回路412−(i−2)に送信し、ホストプロセッサ440にさらに伝送する。別の実施形態で変調器523−1が最下位バッテリ管理チップ410−1にあれば、変調器523−1はピンALT0‘を介して符号化警報信号をコンバータ413に送信できる。コンバータ413は第2のタイプのプロトコルにより通信する受信符号化警報信号を第1のタイプのプロトコルにより通信でき、ピンIRQを介してホストプロセッサ440に伝送できるデータに変換する。

【0050】

図6は本発明の一実施形態に従う図4のバッテリ管理システム400の動作タイミング図600を示す。図6を図4と組み合わせて説明する。t0で、コマンド、例えば計数コマンドをホストプロセッサ440により送信する。計数コマンドを使用してホストプロセッサ120に接続するバッテリ管理チップ総数を判断し、各バッテリ管理チップにそれ自体のアドレスの判断を可能にする。t1で、計数コマンド、初期チップ番号およびチェックデータを含む計数パケットを、コンバータ413を介して最下位バッテリ管理チップ410−1の垂直バス回路412−1により受信する。時間t2で、バッテリ管理チップ410−1の垂直バス回路412−1は計数コマンド、計数回路416−1により発生する新規チップ番号および対応チェックデータを含む計数パケットを発生し、計数パケットをバッテリ管理チップ410−2に送信する。時間t3で、バッテリ管理チップ410−2はバッテリ管理チップ410−1により送信する計数パケットを受信する。時間t4で、バッテリ管理チップ410−2は計数コマンド、計数回路416−2により発生する新規チップ番号および対応チェックデータを含む計数パケットを発生し、その計数パケットをバッテリ管理チップ410−3に送信する。バッテリ管理チップ410−3は時間t5でバッテリ管理チップ410−2により送信する計数パケットを受信する。

【0051】

図4の例に示すように、バッテリ管理チップ410−3は最上位チップである。最上位バッテリ管理チップ410−3がバッテリ管理チップ410−2から計数パケットを受信後時間t6で、最上位バッテリ管理チップ410−3はバッテリ管理チップ410−1、410−2およびホストプロセッサ440に応答を送信する。一実施形態で、応答は計数コマンド並びにバッテリ管理チップ410−3のチップ番号を含みうる。時間t7で、バッテリ管理チップ410−2は応答を受信し、バッテリ管理チップ410−1に応答をさらに送信する。時間t8で、バッテリ管理チップ410−1は応答を受信する。時間t9で、ホストプロセッサ440は応答を受信する。応答を受信すると、最上位バッテリ管理チップのチップ番号に基づき、ホストプロセッサ440はホストプロセッサ440に接続するバッテリ管理チップ総数を判断できる。

【0052】

その上一実施形態で、時間t2でバッテリ管理チップ410−1がバッテリ管理チップ410−2に計数パケットを送信すると、時間t8でバッテリ管理チップ410−1が最上位バッテリ管理チップ410−3から応答を受信するまでに、例えばバッテリ管理チップ410−1のタイマTIMER1は走行を開始する。このようにして、時間ピリオドT1(T1=t8−t2)を計算する。時間t4でバッテリ管理チップ410−2がバッテリ管理チップ410−3に計数パケットを送信すると、時間t7でバッテリ管理チップ410−2がバッテリ管理チップ410−3から応答を受信するまでに、例えばバッテリ管理チップ410−2のタイマTIMER2は走行を開始する。このようにして、時間ピリオドT2を計算する(T2=t7−t4)。

【0053】

時間ピリオドT1およびT2を使用して以下のようにバッテリ管理チップ間の通信遅延を補償する。一実施形態で、ホストプロセッサ440はバッテリ管理チップにブロードキャストコマンドを送信でき、バッテリ管理チップにバッテリモジュールの各電池状態のサンプリングを指令する。例えば時間t10で、ブロードキャストコマンド、例えば電池電圧をサンプリングするサンプリングコマンドをホストプロセッサ440により送信し、各バッテリ管理チップ410−iに対応バッテリモジュール402−iの各電池の電池電圧のサンプリングを指令する。時間t11で、バッテリ管理チップ410−1はサンプリングコマンドを受信する。例えばバッテリ管理チップ410−1の補償タイマは時間ピリオドTD1の間に走行を開始する。一実施形態で、TD1=T1/2である。従って、時間t13で、即ち時間t11の後遅延時間TD1で、バッテリ管理チップ410−1はバッテリモジュール402−1の電池の電池電圧をサンプリングする。同様に時間t12で、バッテリ管理チップ410−2はサンプリングコマンドを受信する。例えばバッテリ管理チップ410−2の補償タイマは時間ピリオドTD2の間に走行を開始する。一実施形態で、TD2=T2/2である。従って、時間t13で、即ち時間t12の後遅延時間TD2で、バッテリ管理チップ410−2もバッテリモジュール402−2の電池電圧をサンプリングする。時間t13で、最上位バッテリ管理チップ410−3はサンプリングコマンドを受信し、バッテリモジュール402−3の電池電圧をまたサンプリングする。有利には、全てのバッテリ管理チップ410−1乃至410−3は同時(t13)に電池状態をサンプリングする。

【0054】

従って、バッテリ管理チップが計数パケットを送信し、計数処理過程で応答を受信する時間の間の遅延(例えば、図6の例でT1およびT2)の計算により、対応時間補償パラメータ(例えば、図6の例でTD1およびTD2)を入手できる。それ故ホストプロセッサ440により送信するブロードキャストコマンドを受信すると、バッテリ管理チップ410−iは遅延の補償後にコマンド、例えば電池電圧のサンプリングを実行できる。有利には、各バッテリ管理チップ410−iはそれ故同時にブロードキャストコマンドを実行できる。

【0055】

図7は本発明の一実施形態に従うバッテリ管理システムにより実行する動作フローチャート700を示す。図7を図4と組み合わせて説明する。特定ステップを図7で開示するが、このようなステップは例示的である。即ち、本発明は種々の他のステップまたは図7で列挙するステップの変形の実行によく適す。

【0056】

図4の例に示すようにブロック702で、ホストプロセッサ、例えばホストプロセッサ440は計数コマンドを発生し、複数のチップ、例えばバッテリ管理チップ410−1乃至410−3に送信し、バッテリ管理チップ総数を判断し、各バッテリ管理チップ410−iにそれ自体のアドレスの判断を可能にする。

【0057】

ブロック704で、バッテリ管理チップは計数コマンドを含む対応計数パケットをチップからチップへ伝達する。より明確には、第1の計数パケットはコンバータ413により発生できる。一実施形態で、第1の計数パケットは計数コマンド、第1のチップ番号および第1のチェックデータを含みうる。第1のチェックデータを使用して前記第1のチップ番号の誤りをチェックできる。第1のバッテリ管理チップ410−1は第1の計数コマンドを受信し、第2のチップ番号および第2のチェックデータを含む第2の計数コマンドパケットを発生し、上方バッテリ管理チップ410−2に第2の計数コマンドパケットを送信する。バッテリ管理チップ410−2は第2の計数パケットを受信し、計数コマンド、第3のチップ番号および第3のチェックデータを含む第3の計数パケットを発生し、上方バッテリ管理チップ410−3に第3の計数パケットを送信する。図4の例に示すように、バッテリ管理チップ410−3は最上位チップである。従って、バッテリ管理チップ410−3は第3の計数パケットを受信するが、一実施形態では対応計数パケットを送信しない。

【0058】

ブロック706で受信計数パケットの情報を使用して、各チップはそれ自体の固有アドレスを判断する。より明確には一実施形態で、対応バッテリ管理チップ410−iにより受信するチップ番号を使用してバッテリ管理チップ410−iのアドレスを表す。そのような一実施形態で図4の例に示すように、バッテリ管理チップ410−3は最上位チップである。それ故、最上位バッテリ管理チップ410−3は新規チップ番号を発生しない。しかし別の実施形態では、バッテリ管理チップ410−iにより発生するチップ番号を使用してその固有アドレスを表すことができ、従って最上位バッテリ管理チップ410−3はバッテリ管理チップ410−3のアドレスを表す新規チップ番号を発生する。

【0059】

一実施形態で、最上位バッテリ管理チップ410−3は他のバッテリ管理チップ410−1および410−2並びにホストプロセッサ440にも応答を送信できる。一実施形態で、応答は計数コマンドおよびバッテリ管理チップ410−3のチップ番号を含む。本チップ番号はバッテリ管理チップ410−3のアドレスを表す。ホストプロセッサ440が応答を受信後、ホストプロセッサ440は、例えばバッテリ管理チップ410−3のチップ番号によりホストプロセッサ440に接続するバッテリ管理チップ総数を判断できる。

【0060】

以上の説明および図面は本発明の実施形態を表すが、添付する特許請求の範囲で規定するように本発明の原理の精神並びに範囲を逸脱することなく、種々の追加、修正並びに置換を本発明において為し得ることが理解されよう。本発明の実施において使用する形態、構成、配置、規模、材料、部品および構成要素他の多くの修正により、本発明を使用することができ、これらは本発明の原理を逸脱することなく、特定の環境並びに動作要求条件に特に適合することを当業者は認識するであろう。ここに開示する実施形態はそれ故あらゆる点で例証的であり、限定的でないと考えるべきであり、本発明の範囲は添付する特許請求の範囲およびその法的等価物により示し、以上の説明に制限されない。

【符号の説明】

【0061】

102−1,102−2,102−3、401−1、401−2、401−3 バッテリモジュール

110−1,110−2,110−3、410−1、410−2、410−3 バッテリ管理チップ

111−1、111−2、111−3、411−1、 411−2、411−3

バッテリ管理ユニット

112−1、112−2、112−3、412−1、412−2、412−3

(垂直)バス回路

116−1、116−2、116−3、116−i、416−1、416−2、

416−3 計数回路(EM)

120、440 ホストプロセッサ

210 チェック回路

211、216、221 XORゲート

212、504−i、506−i、508−i、511−i、513−i、

515−i インバータ

213、223 ANDゲート

214、222 ORゲート

215、224 フリップフロップ

220 チップ番号発生器

230 マルチプレクサ

400 バッテリ管理システム

500、412−1、412−2、412−3 垂直バス回路

512−i、514−i(501−i、503−i) 比較器対

531−i、532−i 受信機

533−i、534−i 送信機

541−i、542−i(551−i)、552−i NANDゲート

543−i、544−i、(553−i、554−i)、566−i、

(568−i) 電圧ソース

562(564) ノード

600 バッテリ管理システムの動作タイミング図

700 バッテリ管理システムにより実行する動作フローチャート

702 ホストプロセッサで計数コマンドを発生

704 計数コマンドを含む対応計数パケットをホストプロセッサに接続する複数の

チップの中のチップからチップへ伝達

706 計数コマンドパケットの情報を使用して各チップはそれ自体の固有アドレス

を判断

【特許請求の範囲】

【請求項1】

複数のチップおよび

ホストプロセッサ

を含み、前記ホストプロセッサは前記複数のチップに接続し、計数コマンドを送信するように動作可能であり、前記チップは前記計数コマンドを含む計数パケットをチップからチップへ伝達し、各チップは前記計数パケットにおける情報を使用してそれ自体の固有アドレスを判断するシステム。

【請求項2】

請求項1に記載のシステムであって、前記複数のチップの第1のチップは、前記計数コマンドと、第1のチップ番号と、前記第1のチップ番号における誤りをチェックする第1のチェックデータとを含む第1の計数パケットを受信し、前記計数コマンドと、第2のチップ番号と、前記第2のチップ番号における誤りをチェックする第2のチェックデータとを含む第2の計数パケットを前記複数のチップの第2のチップに送信するシステム。

【請求項3】

請求項2に記載のシステムであって、前記第2のチップは前記第2のパケットを受信し、前記第1のチップに応答を送信し、前記ホストプロセッサも前記応答を受信し、前記応答に従い前記システムにおけるチップ総数を判断するシステム。

【請求項4】

請求項3に記載のシステムであって、前記第1のチップは前記第1のチップが前記第2のパケットを前記第2のチップに送信する時間と前記第1のチップが前記応答を受信する時間の間の第1の時間遅延を計算するように動作可能であるシステム。

【請求項5】

請求項4に記載のシステムであって、前記ホストプロセッサは前記複数のチップにブロードキャストコマンドを送信し、前記第1のチップは第2の時間遅延後に前記ブロードキャストコマンドを受信すると前記ブロードキャストコマンドを実行し、前記第2の時間遅延を前記第1の時間遅延に基づいて判断するシステム。

【請求項6】

請求項5に記載のシステムであって、前記第2の時間遅延は前記第1の時間遅延の半分であるシステム。

【請求項7】

請求項2に記載のシステムであって、前記第1のチップは前記第1のチップ番号に従い前記第2のチップ番号を発生するように動作可能であるシステム。

【請求項8】

請求項2に記載のシステムであって、前記第1のチップは前記第2のチェックデータを発生するように動作可能であり、前記第2のチェックデータは前記第2のチップ番号の反転であるシステム。

【請求項9】

請求項2に記載のシステムであって、前記第1のチェックデータは前記第1のチップ番号の反転であるシステム。

【請求項10】

請求項2に記載のシステムであって、前記第1のチップ番号は前記第1のチップのアドレスを示し、前記第2のチップ番号は前記第2のチップのアドレスを示すシステム。

【請求項11】

請求項2に記載のシステムであって、前記第2のチップ番号は前記第1のチップのアドレスを示すシステム。

【請求項12】

バッテリ管理チップであって、

前記バッテリ管理チップに接続するバッテリモジュールの複数の電池状態を監視、サンプリングするように動作可能なバッテリ管理ユニットおよび

前記バッテリ管理ユニットに接続し、計数パケットを受信するように動作可能な計数回路

を含み、

前記計数パケットは計数コマンドおよび第1の番号を含み、

前記計数回路は前記計数コマンドに応じて前記第1の番号に基づき第2の番号を発生する、

バッテリ管理チップ。

【請求項13】

請求項12に記載のバッテリ管理チップであって、前記計数パケットは前記第1の番号における誤りをチェックする第1のチェックデータをさらに含む、バッテリ管理チップ。

【請求項14】

請求項13に記載のバッテリ管理チップであって、前記計数回路は、

前記第2の番号を発生するように動作可能なチップ番号発生器、および

前記第1のチェックデータに従い前記第1の番号における前記誤りをチェックするように動作可能であり、また前記第2の番号における誤りをチェックする第2のチェックデータを発生するように動作可能なチェック回路

を含み、

前記チェック回路は前記第2の番号に基づき前記第2のチェックデータを発生する、

バッテリ管理チップ。

【請求項15】

請求項14に記載のバッテリ管理チップであって、前記第1のチェックデータは前記第1の番号の反転であり、前記第2のチェックデータは前記第2の番号の反転である、バッテリ管理チップ。

【請求項16】

請求項14に記載のバッテリ管理チップであって、前記計数回路は前記チップ番号発生器および前記チェック回路に接続するマルチプレクサをさらに含み、前記マルチプレクサは発生処理過程において前記第2の番号を提供し、チェック処理過程において前記第2のチェックデータを提供する、バッテリ管理チップ。

【請求項17】

請求項14に記載のバッテリ管理チップであって、前記チップ番号発生器は前記第1の番号を受信する第1の端子を含み、前記チップ番号発生器は前記第1の番号を1だけ増進させ、前記第2の番号を発生する、バッテリ管理チップ。

【請求項18】

請求項14に記載のバッテリ管理チップであって、前記チェック回路は前記第2の番号を受信する第1の端子を含み、前記第2の番号に基づき前記第2のチェックデータを発生する、バッテリ管理チップ。

【請求項19】

請求項12に記載のバッテリ管理チップであって、前記第1の番号は前記バッテリ管理チップのアドレスを示す、バッテリ管理チップ。

【請求項20】

請求項12に記載のバッテリ管理チップであって、前記第2の番号は前記バッテリ管理チップのアドレスを示す、バッテリ管理チップ。

【請求項21】

請求項12に記載のバッテリ管理チップであって、前記バッテリ管理ユニットはホストプロセッサから命令を受信し、前記命令におけるアドレスが前記バッテリ管理チップのアドレスと整合すれば前記命令を実行する、バッテリ管理チップ。

【請求項22】

ホストプロセッサにおいて計数コマンドを発生するステップ、

前記ホストプロセッサに接続する複数のチップの中のチップからチップへ前記計数コマンドを含む対応計数パケットを伝達するステップ、および

前記計数コマンドパケットにおける情報を使用して前記チップのそれぞれがそれ自体の固有アドレスを判断するステップ

を含む方法。

【請求項23】

請求項22に記載の方法であって、

前記チップの第1のチップにおいて、前記計数コマンドと、第1のチップ番号と、前記第1のチップ番号における誤りをチェックする第1のチェックデータとを含む第1の計数パケットを受信するステップおよび

前記第1のチップから前記チップの第2のチップに前記計数コマンドと、前記第2のチップ番号と、前記第2のチップ番号における誤りをチェックする第2のチェックデータとを含む第2の計数パケットを送信するステップ

をさらに含む、方法。

【請求項24】

請求項23に記載の方法であって、

前記第2のチップにおいて前記第2の計数パケットを受信するステップ、

前記第2のチップが前記チップおよび前記ホストプロセッサに応答を送信するステップおよび

前記ホストプロセッサが前記応答に従い前記チップ総数を判断するステップ

をさらに含む、方法。

【請求項25】

請求項23に記載の方法であって、前記第1のチップ番号は前記第1のチップのアドレスを示し、前記第2のチップ番号は前記第2のチップのアドレスを示す、方法。

【請求項26】

請求項23に記載の方法であって、前記第2のチップ番号は前記第1のチップのアドレスを示す、方法。

【請求項1】

複数のチップおよび

ホストプロセッサ

を含み、前記ホストプロセッサは前記複数のチップに接続し、計数コマンドを送信するように動作可能であり、前記チップは前記計数コマンドを含む計数パケットをチップからチップへ伝達し、各チップは前記計数パケットにおける情報を使用してそれ自体の固有アドレスを判断するシステム。

【請求項2】

請求項1に記載のシステムであって、前記複数のチップの第1のチップは、前記計数コマンドと、第1のチップ番号と、前記第1のチップ番号における誤りをチェックする第1のチェックデータとを含む第1の計数パケットを受信し、前記計数コマンドと、第2のチップ番号と、前記第2のチップ番号における誤りをチェックする第2のチェックデータとを含む第2の計数パケットを前記複数のチップの第2のチップに送信するシステム。

【請求項3】

請求項2に記載のシステムであって、前記第2のチップは前記第2のパケットを受信し、前記第1のチップに応答を送信し、前記ホストプロセッサも前記応答を受信し、前記応答に従い前記システムにおけるチップ総数を判断するシステム。

【請求項4】

請求項3に記載のシステムであって、前記第1のチップは前記第1のチップが前記第2のパケットを前記第2のチップに送信する時間と前記第1のチップが前記応答を受信する時間の間の第1の時間遅延を計算するように動作可能であるシステム。

【請求項5】

請求項4に記載のシステムであって、前記ホストプロセッサは前記複数のチップにブロードキャストコマンドを送信し、前記第1のチップは第2の時間遅延後に前記ブロードキャストコマンドを受信すると前記ブロードキャストコマンドを実行し、前記第2の時間遅延を前記第1の時間遅延に基づいて判断するシステム。

【請求項6】

請求項5に記載のシステムであって、前記第2の時間遅延は前記第1の時間遅延の半分であるシステム。

【請求項7】

請求項2に記載のシステムであって、前記第1のチップは前記第1のチップ番号に従い前記第2のチップ番号を発生するように動作可能であるシステム。

【請求項8】

請求項2に記載のシステムであって、前記第1のチップは前記第2のチェックデータを発生するように動作可能であり、前記第2のチェックデータは前記第2のチップ番号の反転であるシステム。

【請求項9】

請求項2に記載のシステムであって、前記第1のチェックデータは前記第1のチップ番号の反転であるシステム。

【請求項10】

請求項2に記載のシステムであって、前記第1のチップ番号は前記第1のチップのアドレスを示し、前記第2のチップ番号は前記第2のチップのアドレスを示すシステム。

【請求項11】

請求項2に記載のシステムであって、前記第2のチップ番号は前記第1のチップのアドレスを示すシステム。

【請求項12】

バッテリ管理チップであって、

前記バッテリ管理チップに接続するバッテリモジュールの複数の電池状態を監視、サンプリングするように動作可能なバッテリ管理ユニットおよび

前記バッテリ管理ユニットに接続し、計数パケットを受信するように動作可能な計数回路

を含み、

前記計数パケットは計数コマンドおよび第1の番号を含み、

前記計数回路は前記計数コマンドに応じて前記第1の番号に基づき第2の番号を発生する、

バッテリ管理チップ。

【請求項13】

請求項12に記載のバッテリ管理チップであって、前記計数パケットは前記第1の番号における誤りをチェックする第1のチェックデータをさらに含む、バッテリ管理チップ。

【請求項14】

請求項13に記載のバッテリ管理チップであって、前記計数回路は、

前記第2の番号を発生するように動作可能なチップ番号発生器、および

前記第1のチェックデータに従い前記第1の番号における前記誤りをチェックするように動作可能であり、また前記第2の番号における誤りをチェックする第2のチェックデータを発生するように動作可能なチェック回路

を含み、

前記チェック回路は前記第2の番号に基づき前記第2のチェックデータを発生する、

バッテリ管理チップ。

【請求項15】

請求項14に記載のバッテリ管理チップであって、前記第1のチェックデータは前記第1の番号の反転であり、前記第2のチェックデータは前記第2の番号の反転である、バッテリ管理チップ。

【請求項16】

請求項14に記載のバッテリ管理チップであって、前記計数回路は前記チップ番号発生器および前記チェック回路に接続するマルチプレクサをさらに含み、前記マルチプレクサは発生処理過程において前記第2の番号を提供し、チェック処理過程において前記第2のチェックデータを提供する、バッテリ管理チップ。

【請求項17】

請求項14に記載のバッテリ管理チップであって、前記チップ番号発生器は前記第1の番号を受信する第1の端子を含み、前記チップ番号発生器は前記第1の番号を1だけ増進させ、前記第2の番号を発生する、バッテリ管理チップ。

【請求項18】

請求項14に記載のバッテリ管理チップであって、前記チェック回路は前記第2の番号を受信する第1の端子を含み、前記第2の番号に基づき前記第2のチェックデータを発生する、バッテリ管理チップ。

【請求項19】

請求項12に記載のバッテリ管理チップであって、前記第1の番号は前記バッテリ管理チップのアドレスを示す、バッテリ管理チップ。

【請求項20】

請求項12に記載のバッテリ管理チップであって、前記第2の番号は前記バッテリ管理チップのアドレスを示す、バッテリ管理チップ。

【請求項21】

請求項12に記載のバッテリ管理チップであって、前記バッテリ管理ユニットはホストプロセッサから命令を受信し、前記命令におけるアドレスが前記バッテリ管理チップのアドレスと整合すれば前記命令を実行する、バッテリ管理チップ。

【請求項22】

ホストプロセッサにおいて計数コマンドを発生するステップ、

前記ホストプロセッサに接続する複数のチップの中のチップからチップへ前記計数コマンドを含む対応計数パケットを伝達するステップ、および

前記計数コマンドパケットにおける情報を使用して前記チップのそれぞれがそれ自体の固有アドレスを判断するステップ

を含む方法。

【請求項23】

請求項22に記載の方法であって、

前記チップの第1のチップにおいて、前記計数コマンドと、第1のチップ番号と、前記第1のチップ番号における誤りをチェックする第1のチェックデータとを含む第1の計数パケットを受信するステップおよび

前記第1のチップから前記チップの第2のチップに前記計数コマンドと、前記第2のチップ番号と、前記第2のチップ番号における誤りをチェックする第2のチェックデータとを含む第2の計数パケットを送信するステップ

をさらに含む、方法。

【請求項24】

請求項23に記載の方法であって、

前記第2のチップにおいて前記第2の計数パケットを受信するステップ、

前記第2のチップが前記チップおよび前記ホストプロセッサに応答を送信するステップおよび

前記ホストプロセッサが前記応答に従い前記チップ総数を判断するステップ

をさらに含む、方法。

【請求項25】

請求項23に記載の方法であって、前記第1のチップ番号は前記第1のチップのアドレスを示し、前記第2のチップ番号は前記第2のチップのアドレスを示す、方法。

【請求項26】

請求項23に記載の方法であって、前記第2のチップ番号は前記第1のチップのアドレスを示す、方法。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図6】

【図7】

【公開番号】特開2013−27299(P2013−27299A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2012−79422(P2012−79422)

【出願日】平成24年3月30日(2012.3.30)

【出願人】(500521843)オーツー マイクロ, インコーポレーテッド (138)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成24年3月30日(2012.3.30)

【出願人】(500521843)オーツー マイクロ, インコーポレーテッド (138)

【Fターム(参考)】

[ Back to top ]