記憶装置および書き込み装置

【課題】記憶するデータのセキュリティを向上させる。

【解決手段】記憶装置は、データ記憶部と鍵記憶部と乱数発生部と乱数送信部とデータ受信部と計算部と判定部と記憶制御部とを備える。データ記憶部はデータを記憶する。鍵記憶部は外部装置と共有する共有鍵を記憶する。乱数発生部は乱数を発生する。乱数送信部は乱数を外部装置に送信する。データ受信部は、書き込みデータと、乱数および書き込みデータに基づいて計算された第1認証情報とを外部装置から受信する。計算部は、書き込みデータと乱数とから生成されるデータについて共有鍵を用いて第2認証情報を計算する。判定部は第1認証情報と第2認証情報とが一致するか否かを判定する。記憶制御部は、第1認証情報と第2認証情報とが一致すると判定された場合に、書き込みデータをデータ記憶部に記憶する。

【解決手段】記憶装置は、データ記憶部と鍵記憶部と乱数発生部と乱数送信部とデータ受信部と計算部と判定部と記憶制御部とを備える。データ記憶部はデータを記憶する。鍵記憶部は外部装置と共有する共有鍵を記憶する。乱数発生部は乱数を発生する。乱数送信部は乱数を外部装置に送信する。データ受信部は、書き込みデータと、乱数および書き込みデータに基づいて計算された第1認証情報とを外部装置から受信する。計算部は、書き込みデータと乱数とから生成されるデータについて共有鍵を用いて第2認証情報を計算する。判定部は第1認証情報と第2認証情報とが一致するか否かを判定する。記憶制御部は、第1認証情報と第2認証情報とが一致すると判定された場合に、書き込みデータをデータ記憶部に記憶する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、記憶装置および書き込み装置に関する。

【背景技術】

【0002】

PC、タブレットPCおよびスマートフォンなどのデバイスにおいて、DRM(Digital Rights Management:著作権保護管理機能)などを実装する場合、セキュリティの確保が重要となる。OS(オペレーティングシステム)やBIOS(Basic Input/Output System)などのシステムプログラムが改ざんされていた場合、DRM機能は意味を持たない。そのようなシステムプログラムの下でDRM機能を実現するプログラムが動作している場合、DRMが定義するデータの保護を無効化して、自由に出力したり読み書きしたりすることができるからである。

【0003】

システムプログラムの改ざんを防ぐためには、ディスクや不揮発性メモリの書き込みを防止することが重要である。システムプログラムを改ざんする攻撃者は、一般に、システムプログラムのデータやパラメータに永続的な書き変えを行うことを試みる。システムプログラムのセキュリティを解除するには、システムプログラムのデータやパラメータを書き変えた後に、システムを再立ち上げする必要があるからである。

【0004】

ディスクや不揮発性メモリの書き変えを防止する技術の1つとして、eMMC(Embedded MultiMediaCard)メモリにおけるRPMB(Reply Protected Memory Block)の技術が存在する。この技術では、ホスト(書き込み装置)とeMMCとが予め鍵(共有鍵)を共有しておく。ホストがeMMCにデータを書き込む際に、書きこむデータのMAC(Message Authentication Code:メッセージ認証コード)を、共有鍵を用いて計算し、書き込みデータにMACを付加してeMMCに送信する。eMMCの側では、受信したデータの中の書き込みデータのMACを、eMMCが保持する共有鍵を用いて計算する。次に、eMMCは、受信データ中のMACと、eMMC自身が計算したMAC値とを比較する。両者が一致している場合に限り、eMMCは受信データ中の書き込みデータを指定されたeMMC内のアドレスに記録する。

【0005】

書き込みデータに関するMACの値は、当該eMMCと鍵を共有するホストだけが計算することができる。従って、eMMCは、MACをチェックすることによって、受信データが正しいホストから送信されたデータであることを確認した上で書き込みを行うことができる。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】JEDEC STANDARD:EMBEDDED MULTI-MEDIA CARD (eMMC), ELECTRICAL STANDARD (4.5 Device),JESD84-B45,June 2011

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、RPMB技術をシステムプログラムの改ざん防止に利用する際には問題点がある。それは、RPMB技術では、システムプログラムのアップデートが保障されないことである。書き込みデータに付与されたMAC値さえ正しければeMMCは書き込み要求を受理する。従って、当該eMMCに記録されたシステムプログラムのイメージを保存しておけば、後にシステムプログラムがアップデートされた後に、古いシステムプログラムのイメージを再度eMMCに書き込んで、アップデートを無効にすることが可能である。

【課題を解決するための手段】

【0008】

実施形態の記憶装置は、データ記憶部と鍵記憶部と乱数発生部と乱数送信部とデータ受信部と計算部と判定部と記憶制御部とを備える。データ記憶部はデータを記憶する。鍵記憶部は外部装置と共有する共有鍵を記憶する。乱数発生部は乱数を発生する。乱数送信部は乱数を外部装置に送信する。データ受信部は、書き込みデータと、乱数および書き込みデータに基づいて計算された第1認証情報とを外部装置から受信する。計算部は、書き込みデータと乱数とから生成されるデータについて共有鍵を用いて第2認証情報を計算する。判定部は第1認証情報と第2認証情報とが一致するか否かを判定する。記憶制御部は、第1認証情報と第2認証情報とが一致すると判定された場合に、書き込みデータをデータ記憶部に記憶する。

【図面の簡単な説明】

【0009】

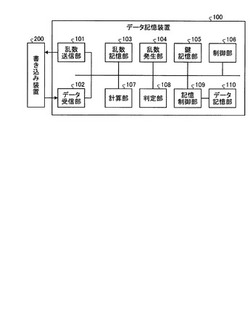

【図1】第1の実施形態の記憶装置のブロック図。

【図2】第1の実施形態の記憶装置の動作のフローチャート。

【図3】第1の実施形態の書き込み装置のブロック図。

【図4】第1の実施形態の書き込み装置の動作のフローチャート。

【図5】第2の実施形態の記憶装置のブロック図。

【図6】第2の実施形態の記憶装置の動作のフローチャート。

【図7】第2の実施形態の書き込み装置のブロック図。

【図8】第2の実施形態の書き込み装置の動作のフローチャート。

【図9】第1および第2の実施形態の装置のハードウェア構成図。

【発明を実施するための形態】

【0010】

以下に添付図面を参照して、この発明にかかる記憶装置および書き込み装置の好適な実施形態を詳細に説明する。

【0011】

(第1の実施形態)

第1の実施形態にかかる情報処理システムは、データを格納する記憶装置と、記憶装置にデータを書き込む書き込み装置(ホスト)とを含む。RPMB技術と同様、書き込み装置と記憶装置とは予め共有鍵を共有している。第1の実施形態にかかる情報処理システムでは、記憶装置が生成する乱数を用いてシステムプログラムを安全にアップデートする。

【0012】

本実施形態の情報処理システムによるデータの書き込み処理の概要を以下に説明する。以下では書き込み装置から記憶装置に書き込むデータを書き込みデータという。書き込みデータとして上記のようなシステムプログラムなどを適用できるが、これに限られるものではない。

【0013】

まず、記憶装置は生成した乱数を内部に保持する。書き込み装置は記憶装置から乱数を読み取り、当該乱数と書き込みデータとを結合したデータに関する認証情報であるMAC値を計算する。書き込み装置は、共有鍵を用いてMAC値を計算する。書き込み装置は、書き込みデータにMAC値を添えて、記憶装置に送る。記憶装置は、内部に保持する乱数と受信した書き込みデータを結合し、MAC値を計算する。当該MAC値が、書き込み装置から受信したMAC値と一致した場合に、指定されたアドレスに書き込みデータを記録する。MAC値が一致しない場合、記憶装置は書き込み装置からの当該書き込み要求を受理しない。この方法によれば、書き込みデータのMAC値が有効であるのは一度限りとなる。従って、記憶装置への書き込みに成功したデータを保持していて、当該データを再度書き込もうとしても、書き込みは不可能である。

【0014】

図1は、第1の実施形態の記憶装置100の構成の一例を示すブロック図である。記憶装置100は、データ記憶部110と、鍵記憶部105と、乱数発生部104と、乱数記憶部103と、乱数送信部101と、データ受信部102と、計算部107と、判定部108と、記憶制御部109と、制御部106と、を備えている。

【0015】

データ記憶部110は、書き込み装置200により書き込まれるデータ(書き込みデータ)を記憶する。データ記憶部110は、例えば不揮発メモリで構成される。

【0016】

鍵記憶部105は、MAC計算用の共有鍵を記憶する。この共有鍵は、記憶装置100と書き込み装置200との間で共有される鍵である。

【0017】

乱数発生部104は、乱数を発生する。乱数記憶部103は、乱数発生部104により発生された乱数を記憶する。乱数送信部101は、乱数記憶部103が格納する乱数を記憶装置100の外部に出力する。

【0018】

データ受信部102は、記憶装置100の外部から書き込みデータとMAC値とを受け取り、受け取った書き込みデータおよびMAC値を保持する。

【0019】

計算部107は、書き込みデータと乱数記憶部103が格納する乱数とから生成されるデータについて、鍵記憶部105が格納する共有鍵を用いてMAC値を計算する。MAC値の計算に用いるMACアルゴリズムとしては、ハッシュ関数を用いる方法(HMAC)などの従来から用いられているあらゆるアルゴリズムを適用できる。

【0020】

判定部108は、計算部107が計算したMAC値と、データ受信部102が受信したMAC値と、を比較し、両者が一致するか否かを判定する。判定部108は、両者が一致した場合に限り書き込みデータを受理する。

【0021】

記憶制御部109は、判定部108が受理した書き込みデータをデータ記憶部110に記録する。

【0022】

制御部106は、記憶装置100全体を制御する。

【0023】

次に、このように構成された第1の実施形態にかかる記憶装置100による記憶処理について図2を用いて説明する。図2は、第1の実施形態の記憶装置100の動作の一例を示すフローチャートである。

【0024】

データ受信部102は、書き込み装置200から書き込み要求を受信する(ステップS11)。乱数発生部104は、乱数を発生し、発生した乱数を乱数記憶部103に記憶する(ステップS12)。乱数送信部101は、乱数記憶部103に記憶された乱数を読み取り、読み取った乱数を書き込み装置200に送信する(ステップS13)。データ受信部102は、書き込み装置200から、書き込みデータとMAC値とを受信し(ステップS14)、それらを保持する。

【0025】

その後、計算部107は、データ受信部102から書き込みデータを読み出す。また、計算部107は、乱数記憶部103から乱数を読み出し、鍵記憶部105からMAC計算用の共有鍵を読み出す。計算部107は、それらを用いて、次の(1)式のようにMACの値Mを計算する(ステップS15)。

M=MAC(K,D||R) ・・・(1)

【0026】

ここに、KはMAC計算用の共有鍵、Dは書き込みデータ、Rは乱数値である。D||RはDとRとを結合したデータを示す。また、MAC(K,D||R)はKを用いてD||RのMAC値を計算する関数である。この関数により得られたMAC値をMとしている。

【0027】

なお、D||Rが、書き込みデータDと乱数Rとから生成されるデータに相当する。書き込みデータDと乱数Rとから生成されるデータは、DとRとを結合したデータに限られるものではない。

【0028】

次に判定部108は、計算部107からMAC値Mを読み出し、また、データ受信部102からMAC値(以下、MAC値M’とする)を読み出す。そして、判定部108は、読み出したMとM’とを比較し、両者が一致するか否かを判定する(ステップS16)。

【0029】

MとM’とが一致しなければ(ステップS16:No)、判定部108は、書き込みデータを受理しない。その場合、記憶装置100は動作を終了する。一方、MとM’とが一致する場合(ステップS16:Yes)、判定部108は、書き込みデータを受理する。その場合、記憶制御部109は、データ受信部102から書き込みデータを読み取り、当該書き込みデータをデータ記憶部110に記憶する(ステップS17)。

【0030】

図3は、第1の実施形態の書き込み装置200の構成の一例を示すブロック図である。書き込み装置200は、鍵記憶部203と、乱数受信部201と、計算部205と、データ送信部202と、書き込みデータ記憶部204と、制御部206と、を備えている。

【0031】

鍵記憶部203は、MAC計算用の共有鍵を記憶する。この共有鍵は、記憶装置100と書き込み装置200との間で共有される鍵である。

【0032】

乱数受信部201は、記憶装置100の外部から乱数を受信する。計算部205は、乱数受信部201が受信したデータと書き込みデータとから生成されるデータについて、鍵記憶部203が格納する共有鍵を用いてMAC値を計算する。

【0033】

データ送信部202は、書き込みデータと計算部205が計算したMAC値とを書き込み装置200の外部に送信する。

【0034】

書き込みデータ記憶部204は、書き込みデータを保持する。制御部206は、書き込み装置200全体を制御する。

【0035】

次に、このように構成された第1の実施形態にかかる書き込み装置200による書き込み処理について図4を用いて説明する。図4は、第1の実施形態の書き込み装置200の動作の一例を示すフローチャートである。

【0036】

書き込みデータを書き込む際、書き込み装置200のデータ送信部202は、記憶装置100に対して書き込み要求を発行する(ステップS21)。書き込み要求に応じて記憶装置100から乱数が送信されるので、乱数受信部201が当該乱数を受信して保持する(ステップS22)。計算部205は、書き込みデータ記憶部204から書き込みデータを受け取り、乱数受信部201から乱数を受け取る。計算部205は、鍵記憶部203の共有鍵を用いて、書き込みデータと乱数とを結合したデータのMAC値Mを、上記(1)式を用いて計算する(ステップS23)。

【0037】

その後、データ送信部202は、書き込みデータ記憶部204から書き込みデータDを受け取り、計算部205からMAC値Mを受け取る(ステップS24)。データ送信部202は、書き込みデータDとMAC値Mとを、記憶装置100に送信する(ステップS25)。

【0038】

このように、第1の実施形態にかかる情報処理システムでは、記憶装置が生成する乱数を用いて計算したMAC値により正当であると認証された場合にのみ書き込みデータを記憶装置に記憶する。乱数を用いるため、書き込みデータのMAC値が有効であるのは一度限りとなる。従って、記憶装置への書き込みに成功したデータを保持していて、当該データを再度書き込もうとしても、書き込みは不可能である。すなわち、システムプログラムなどのデータを安全にアップデート可能となる。

【0039】

(第2の実施形態)

第2の実施形態にかかる情報処理システムは、バージョン番号を用いてシステムプログラムを安全にアップデートする。本実施形態の情報処理システムによるデータの書き込み処理の概要を以下に説明する。

【0040】

書き込み装置は、システムプログラムなどの書き込みデータのバージョンを表すバージョン情報(バージョン番号)を、書き込みデータと共に記憶装置に送信する。その際、書き込み装置は書き込みデータとバージョン番号とを結合したデータに関するMAC値を計算し、当該MAC値も書き込みデータとバージョン番号に付随させて送信する。MAC値の計算には、記憶装置と共有している共有鍵を用いる。記憶装置は現在のバージョン番号を保持している。記憶装置は、書き込みデータとバージョン番号のMACを確認した後、バージョン番号が、記憶装置が保持する現在のバージョン番号より真に大きい場合に限り、指定アドレスにデータを書き込む。書き込みデータのバージョン番号が現在のバージョン番号より大きくない場合、記憶装置は書き込み装置からの当該書き込み要求を受理しない。この方法では、書き込み装置は乱数を受け取る必要がない。

【0041】

なお、上記説明では、バージョン番号は真に単調増加することを前提とした。しかし、「古くないデータ」を受け入れても良い場合は、記憶装置は、書き込みデータに付随するバージョン番号が、書き込み先アドレスのバージョン番号と同一である場合にも、書き込み先アドレスへの書き込みを行う。さらに、バージョン番号は単調減少であっても良い。また、書き込み装置と記憶装置との間で予め決められているルールによって、次のバージョン番号が計算できるように構成しても良い。例えば、関数fを、書き込み装置と記憶装置との間で共有する。記憶装置が現在保持しているバージョン番号をVcとする。この時、次のバージョン番号VnをVn=f(Vc)と定める。記憶装置は、バージョン番号Vnが付随する書き込みデータだけを受理する。

【0042】

図5は、第2の実施形態の記憶装置100−2の構成の一例を示すブロック図である。図5に示すように、記憶装置100−2は、データ記憶部110と、鍵記憶部105と、乱数送信部101と、データ受信部102−2と、計算部107−2と、バージョン記憶部111−2と、第1判定部112−2と、第2判定部113−2と、記憶制御部109−2と、制御部106と、を備えている。第1の実施形態の記憶装置100と同様の構成については、図1と同一符号を付し、ここでの説明は省略する。

【0043】

バージョン記憶部111−2は、書き込みデータのバージョン番号を格納する。なお、記憶装置100−2を初期化した直後などのように、まだデータが何も書き込まれていない時点では、バージョン記憶部111−2は、最も小さいバージョン番号、例えば0を格納する。

【0044】

データ受信部102−2は、記憶装置100−2の外部から書き込みデータとバージョン番号とMAC値とを受け取り、それらのデータを保持する。

【0045】

計算部107−2は、書き込みデータとバージョン番号とから生成されるデータについて、鍵記憶部105が格納する共有鍵を用いてMAC値を計算する。

【0046】

第1判定部112−2は、計算部107−2が計算したMAC値とデータ受信部102−2が受信したMAC値とを比較し、両者が一致するか否かを判定する。第1判定部112−2は、両者が一致した場合に限り書き込みデータを受理する。

【0047】

第2判定部113−2は、データ受信部102−2が受信したバージョン番号とバージョン記憶部111−2が格納するバージョン番号とを比較し、前者が後者より後のバージョンであるか否かを判定する。バージョン番号が真に単調増加する場合は、第2判定部113−2は、データ受信部102−2が受信したバージョン番号とバージョン記憶部111−2が格納するバージョン番号とを比較し、前者が後者より大であるか否かを判定する。第2判定部113−2は、前者が後者より大である場合に限り書き込みデータを受理する。

【0048】

記憶制御部109−2は、第1判定部112−2と第2判定部113−2が共に書き込みデータを受理した場合に限り書き込みデータをデータ記憶部110に記録する。

【0049】

次に、このように構成された第2の実施形態にかかる記憶装置100−2による記憶処理について図6を用いて説明する。図6は、第2の実施形態の記憶装置100−2の動作の一例を示すフローチャートである。

【0050】

まず、データ受信部102−2が、書き込み装置200−2から書き込みデータ、バージョン番号、およびMAC値を受信する(ステップS31)。計算部107−2は、データ受信部102−2から書き込みデータとバージョン番号とを受け取る。さらに計算部107−2は、鍵記憶部105からMAC計算用の共有鍵を読み出す。計算部107−2は、共有鍵を用いて、書き込みデータとバージョン番号とを結合したデータのMAC値を計算する(ステップS32)。すなわち、計算部107−2は以下の(2)式のようにMAC値Mを計算する(ステップS32)。

M=MAC(K,D||Vn) ・・・(2)

【0051】

ここに、Kは鍵記憶部105が格納している共有鍵、Dは書き込みデータ、Vnは書き込み装置200−2が送信しデータ受信部102−2が保持しているバージョン番号である。

【0052】

次に、第1判定部112−2は、書き込み装置200−2が送信しデータ受信部102−2が保持しているMAC値M’を読み出す。第1判定部112−2は、MとM’とを比較し、両者が一致するか否かを判定する(ステップS33)。両者が一致した場合(ステップS33:Yes)、第1判定部112−2は、書き込みデータを受理する。両者が一致しない場合(ステップS33:No)、記憶装置100−2は、書き込みデータを破棄して動作を停止する。

【0053】

第1判定部112−2が書き込みデータを受理した場合、第2判定部113−2は、バージョン記憶部111−2からバージョン番号Vcを読み出す。また、第2判定部113−2は、データ受信部102−2が保持しているバージョン番号Vnを読み出す。第2判定部113−2は、VnとVcとを比較し、VnがVcより大きいか否かを判定する(ステップS34)。

【0054】

VnがVcより大きくない場合(ステップS34:No)、第2判定部113−2は、書き込みデータを受理しない。この場合、データ受信部102−2の書き込みデータは破棄され、記憶装置100−2は動作を停止する。

【0055】

VnがVcより大きい(Vn>Vc)場合(ステップS34:Yes)、第2判定部113−2は、書き込みデータを受理する。第1判定部112−2と第2判定部113−2とが共にデータを受理した場合、記憶制御部109−2は、データ受信部102−2から書き込みデータを読み出し、当該書き込みデータをデータ記憶部110に記録する(ステップS35)。

【0056】

記憶制御部109−2は、データ受信部102−2が保持しているバージョン番号を読み出し、当該バージョン番号によってバージョン記憶部111−2が格納するバージョン番号を上書き更新する。例えば、システムプログラムのアップデートの際など、システムプログラムのバージョン番号をバージョン記憶部111−2に格納しておく。これにより、システムプログラムのロールバック(後戻り)を効果的に防止することができる。

【0057】

図7は、第2の実施形態の書き込み装置200−2の構成の一例を示すブロック図である。書き込み装置200−2は、鍵記憶部203と、バージョン受付部201−2と、計算部205−2と、データ送信部202−2と、書き込みデータ記憶部204と、制御部206と、を備えている。第1の実施形態の書き込み装置200と同様の構成については、図3と同一符号を付し、ここでの説明は省略する。

【0058】

バージョン受付部201−2は、書き込みデータのバージョン番号の入力を受付け、当該バージョン番号を保持する。計算部205−2は、書き込みデータと入力されたバージョン番号とから生成されるデータについて、鍵記憶部203が格納する共有鍵を用いてMAC値を計算する。

【0059】

データ送信部202−2は、書き込みデータとバージョン番号と計算部205−2が計算したMAC値とを、書き込み装置200−2の外部に送信する。

【0060】

次に、このように構成された第2の実施形態にかかる書き込み装置200−2による書き込み処理について図8を用いて説明する。図8は、第2の実施形態の書き込み装置200−2の動作の一例を示すフローチャートである。

【0061】

まず、バージョン受付部201−2が、バージョン番号の入力を受付ける(ステップS41)。入力されるバージョン番号として、書き込み対象である記憶装置100−2に対して最後に書き込んだバージョン番号より大きいバージョン番号が選択される。

【0062】

計算部205−2は、書き込みデータ記憶部204から書き込みデータDを受け取り、バージョン受付部201−2からバージョン番号Vnを受け取る。計算部205−2は、鍵記憶部105の共有鍵Kを用いて、書き込みデータとバージョン番号とを結合したデータのMAC値Mを、上記(2)式のように計算する(ステップS42)。

【0063】

その後、データ送信部202−2は、書き込みデータ記憶部204から書き込みデータDを受け取り、バージョン受付部201−2からバージョン番号Vnを受け取り、計算部205−2からMAC値Mを受け取る(ステップS43)。データ送信部202−2は、書き込みデータD、バージョン番号Vn、および、MAC値Mを記憶装置に送信する(ステップS44)。

【0064】

このように、第2の実施形態にかかる情報処理システムでは、書き込みデータのバージョン番号が、既に書き込まれているデータのバージョン番号より大きい場合にのみ書き込みデータを記憶装置に記憶する。記憶装置への書き込みに成功したデータを保持していて、当該データを再度書き込もうとしても、バージョン番号が現在のバージョン番号より大きくないため、書き込みは不可能である。すなわち、システムプログラムなどのデータを安全にアップデート可能となる。

【0065】

なお、ここではバージョン番号は数値であり、2つのバージョンの間には自明な大小関係が存在する。あるバージョン番号V1が別のバージョン番号V2より小さい時、バージョン番号V2はバージョン番号V1より「後の」バージョンであるということがある。バージョン番号は一般には全順序集合の要素である。全順序集合の定義は、例えば、日本数学会編集「岩波数学辞典第三版」に記載されている。バージョン番号の全順序集合における順序関係を≦で表す。バージョンV2がバージョンV1より大である(V1<V2)とは、V1≦V2であってV1≠V2であることをいう。

【0066】

以上説明したとおり、第1から第2の実施形態によれば、記憶装置にデータを書き込む場合のセキュリティを向上させることができる。例えば、記憶装置に記憶するシステムプログラムなどのデータのアップデートを保障することができる。

【0067】

次に、第1および第2の実施形態にかかる装置(記憶装置および書き込み装置)のハードウェア構成について図9を用いて説明する。図9は、第1および第2の実施形態にかかる装置のハードウェア構成を示す説明図である。

【0068】

第1および第2の実施形態にかかる装置は、CPU(Central Processing Unit)51などの制御装置と、ROM(Read Only Memory)52やRAM(RandoMACcess Memory)53などの記憶部と、ネットワークに接続して通信を行う通信I/F54と、各部を接続するバス61を備えている。

【0069】

第1および第2の実施形態にかかる装置で実行されるプログラムは、ROM52等に予め組み込まれて提供される。

【0070】

第1および第2の実施形態にかかる装置で実行されるプログラムは、インストール可能な形式又は実行可能な形式のファイルでCD−ROM(Compact Disk Read Only Memory)、フレキシブルディスク(FD)、CD−R(Compact Disk Recordable)、DVD(Digital Versatile Disk)等のコンピュータで読み取り可能な記録媒体に記録してコンピュータプログラムプロダクトとして提供されるように構成しても良い。

【0071】

さらに、第1および第2の実施形態にかかる装置で実行されるプログラムを、インターネット等のネットワークに接続されたコンピュータ上に格納し、ネットワーク経由でダウンロードさせることにより提供するように構成しても良い。また、第1および第2の実施形態にかかる装置で実行されるプログラムをインターネット等のネットワーク経由で提供または配布するように構成しても良い。

【0072】

第1および第2の実施形態にかかる装置で実行されるプログラムは、コンピュータを上述した装置の各部として機能させうる。このコンピュータは、CPU51がコンピュータ読取可能な記憶媒体からプログラムを主記憶装置上に読み出して実行することができる。

【0073】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0074】

100、100−2 記憶装置

101 乱数送信部

102 データ受信部

103 乱数記憶部

104 乱数発生部

105 鍵記憶部

106 制御部

107 計算部

108 判定部

109 記憶制御部

110 データ記憶部

111 バージョン記憶部

112−2 第1判定部

113−2 第2判定部

200、200−2 書き込み装置

201 乱数受信部

201−1 バージョン受付部

202 データ送信部

203 鍵記憶部

204 データ記憶部

205 計算部

206 制御部

【技術分野】

【0001】

本発明の実施形態は、記憶装置および書き込み装置に関する。

【背景技術】

【0002】

PC、タブレットPCおよびスマートフォンなどのデバイスにおいて、DRM(Digital Rights Management:著作権保護管理機能)などを実装する場合、セキュリティの確保が重要となる。OS(オペレーティングシステム)やBIOS(Basic Input/Output System)などのシステムプログラムが改ざんされていた場合、DRM機能は意味を持たない。そのようなシステムプログラムの下でDRM機能を実現するプログラムが動作している場合、DRMが定義するデータの保護を無効化して、自由に出力したり読み書きしたりすることができるからである。

【0003】

システムプログラムの改ざんを防ぐためには、ディスクや不揮発性メモリの書き込みを防止することが重要である。システムプログラムを改ざんする攻撃者は、一般に、システムプログラムのデータやパラメータに永続的な書き変えを行うことを試みる。システムプログラムのセキュリティを解除するには、システムプログラムのデータやパラメータを書き変えた後に、システムを再立ち上げする必要があるからである。

【0004】

ディスクや不揮発性メモリの書き変えを防止する技術の1つとして、eMMC(Embedded MultiMediaCard)メモリにおけるRPMB(Reply Protected Memory Block)の技術が存在する。この技術では、ホスト(書き込み装置)とeMMCとが予め鍵(共有鍵)を共有しておく。ホストがeMMCにデータを書き込む際に、書きこむデータのMAC(Message Authentication Code:メッセージ認証コード)を、共有鍵を用いて計算し、書き込みデータにMACを付加してeMMCに送信する。eMMCの側では、受信したデータの中の書き込みデータのMACを、eMMCが保持する共有鍵を用いて計算する。次に、eMMCは、受信データ中のMACと、eMMC自身が計算したMAC値とを比較する。両者が一致している場合に限り、eMMCは受信データ中の書き込みデータを指定されたeMMC内のアドレスに記録する。

【0005】

書き込みデータに関するMACの値は、当該eMMCと鍵を共有するホストだけが計算することができる。従って、eMMCは、MACをチェックすることによって、受信データが正しいホストから送信されたデータであることを確認した上で書き込みを行うことができる。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】JEDEC STANDARD:EMBEDDED MULTI-MEDIA CARD (eMMC), ELECTRICAL STANDARD (4.5 Device),JESD84-B45,June 2011

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、RPMB技術をシステムプログラムの改ざん防止に利用する際には問題点がある。それは、RPMB技術では、システムプログラムのアップデートが保障されないことである。書き込みデータに付与されたMAC値さえ正しければeMMCは書き込み要求を受理する。従って、当該eMMCに記録されたシステムプログラムのイメージを保存しておけば、後にシステムプログラムがアップデートされた後に、古いシステムプログラムのイメージを再度eMMCに書き込んで、アップデートを無効にすることが可能である。

【課題を解決するための手段】

【0008】

実施形態の記憶装置は、データ記憶部と鍵記憶部と乱数発生部と乱数送信部とデータ受信部と計算部と判定部と記憶制御部とを備える。データ記憶部はデータを記憶する。鍵記憶部は外部装置と共有する共有鍵を記憶する。乱数発生部は乱数を発生する。乱数送信部は乱数を外部装置に送信する。データ受信部は、書き込みデータと、乱数および書き込みデータに基づいて計算された第1認証情報とを外部装置から受信する。計算部は、書き込みデータと乱数とから生成されるデータについて共有鍵を用いて第2認証情報を計算する。判定部は第1認証情報と第2認証情報とが一致するか否かを判定する。記憶制御部は、第1認証情報と第2認証情報とが一致すると判定された場合に、書き込みデータをデータ記憶部に記憶する。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態の記憶装置のブロック図。

【図2】第1の実施形態の記憶装置の動作のフローチャート。

【図3】第1の実施形態の書き込み装置のブロック図。

【図4】第1の実施形態の書き込み装置の動作のフローチャート。

【図5】第2の実施形態の記憶装置のブロック図。

【図6】第2の実施形態の記憶装置の動作のフローチャート。

【図7】第2の実施形態の書き込み装置のブロック図。

【図8】第2の実施形態の書き込み装置の動作のフローチャート。

【図9】第1および第2の実施形態の装置のハードウェア構成図。

【発明を実施するための形態】

【0010】

以下に添付図面を参照して、この発明にかかる記憶装置および書き込み装置の好適な実施形態を詳細に説明する。

【0011】

(第1の実施形態)

第1の実施形態にかかる情報処理システムは、データを格納する記憶装置と、記憶装置にデータを書き込む書き込み装置(ホスト)とを含む。RPMB技術と同様、書き込み装置と記憶装置とは予め共有鍵を共有している。第1の実施形態にかかる情報処理システムでは、記憶装置が生成する乱数を用いてシステムプログラムを安全にアップデートする。

【0012】

本実施形態の情報処理システムによるデータの書き込み処理の概要を以下に説明する。以下では書き込み装置から記憶装置に書き込むデータを書き込みデータという。書き込みデータとして上記のようなシステムプログラムなどを適用できるが、これに限られるものではない。

【0013】

まず、記憶装置は生成した乱数を内部に保持する。書き込み装置は記憶装置から乱数を読み取り、当該乱数と書き込みデータとを結合したデータに関する認証情報であるMAC値を計算する。書き込み装置は、共有鍵を用いてMAC値を計算する。書き込み装置は、書き込みデータにMAC値を添えて、記憶装置に送る。記憶装置は、内部に保持する乱数と受信した書き込みデータを結合し、MAC値を計算する。当該MAC値が、書き込み装置から受信したMAC値と一致した場合に、指定されたアドレスに書き込みデータを記録する。MAC値が一致しない場合、記憶装置は書き込み装置からの当該書き込み要求を受理しない。この方法によれば、書き込みデータのMAC値が有効であるのは一度限りとなる。従って、記憶装置への書き込みに成功したデータを保持していて、当該データを再度書き込もうとしても、書き込みは不可能である。

【0014】

図1は、第1の実施形態の記憶装置100の構成の一例を示すブロック図である。記憶装置100は、データ記憶部110と、鍵記憶部105と、乱数発生部104と、乱数記憶部103と、乱数送信部101と、データ受信部102と、計算部107と、判定部108と、記憶制御部109と、制御部106と、を備えている。

【0015】

データ記憶部110は、書き込み装置200により書き込まれるデータ(書き込みデータ)を記憶する。データ記憶部110は、例えば不揮発メモリで構成される。

【0016】

鍵記憶部105は、MAC計算用の共有鍵を記憶する。この共有鍵は、記憶装置100と書き込み装置200との間で共有される鍵である。

【0017】

乱数発生部104は、乱数を発生する。乱数記憶部103は、乱数発生部104により発生された乱数を記憶する。乱数送信部101は、乱数記憶部103が格納する乱数を記憶装置100の外部に出力する。

【0018】

データ受信部102は、記憶装置100の外部から書き込みデータとMAC値とを受け取り、受け取った書き込みデータおよびMAC値を保持する。

【0019】

計算部107は、書き込みデータと乱数記憶部103が格納する乱数とから生成されるデータについて、鍵記憶部105が格納する共有鍵を用いてMAC値を計算する。MAC値の計算に用いるMACアルゴリズムとしては、ハッシュ関数を用いる方法(HMAC)などの従来から用いられているあらゆるアルゴリズムを適用できる。

【0020】

判定部108は、計算部107が計算したMAC値と、データ受信部102が受信したMAC値と、を比較し、両者が一致するか否かを判定する。判定部108は、両者が一致した場合に限り書き込みデータを受理する。

【0021】

記憶制御部109は、判定部108が受理した書き込みデータをデータ記憶部110に記録する。

【0022】

制御部106は、記憶装置100全体を制御する。

【0023】

次に、このように構成された第1の実施形態にかかる記憶装置100による記憶処理について図2を用いて説明する。図2は、第1の実施形態の記憶装置100の動作の一例を示すフローチャートである。

【0024】

データ受信部102は、書き込み装置200から書き込み要求を受信する(ステップS11)。乱数発生部104は、乱数を発生し、発生した乱数を乱数記憶部103に記憶する(ステップS12)。乱数送信部101は、乱数記憶部103に記憶された乱数を読み取り、読み取った乱数を書き込み装置200に送信する(ステップS13)。データ受信部102は、書き込み装置200から、書き込みデータとMAC値とを受信し(ステップS14)、それらを保持する。

【0025】

その後、計算部107は、データ受信部102から書き込みデータを読み出す。また、計算部107は、乱数記憶部103から乱数を読み出し、鍵記憶部105からMAC計算用の共有鍵を読み出す。計算部107は、それらを用いて、次の(1)式のようにMACの値Mを計算する(ステップS15)。

M=MAC(K,D||R) ・・・(1)

【0026】

ここに、KはMAC計算用の共有鍵、Dは書き込みデータ、Rは乱数値である。D||RはDとRとを結合したデータを示す。また、MAC(K,D||R)はKを用いてD||RのMAC値を計算する関数である。この関数により得られたMAC値をMとしている。

【0027】

なお、D||Rが、書き込みデータDと乱数Rとから生成されるデータに相当する。書き込みデータDと乱数Rとから生成されるデータは、DとRとを結合したデータに限られるものではない。

【0028】

次に判定部108は、計算部107からMAC値Mを読み出し、また、データ受信部102からMAC値(以下、MAC値M’とする)を読み出す。そして、判定部108は、読み出したMとM’とを比較し、両者が一致するか否かを判定する(ステップS16)。

【0029】

MとM’とが一致しなければ(ステップS16:No)、判定部108は、書き込みデータを受理しない。その場合、記憶装置100は動作を終了する。一方、MとM’とが一致する場合(ステップS16:Yes)、判定部108は、書き込みデータを受理する。その場合、記憶制御部109は、データ受信部102から書き込みデータを読み取り、当該書き込みデータをデータ記憶部110に記憶する(ステップS17)。

【0030】

図3は、第1の実施形態の書き込み装置200の構成の一例を示すブロック図である。書き込み装置200は、鍵記憶部203と、乱数受信部201と、計算部205と、データ送信部202と、書き込みデータ記憶部204と、制御部206と、を備えている。

【0031】

鍵記憶部203は、MAC計算用の共有鍵を記憶する。この共有鍵は、記憶装置100と書き込み装置200との間で共有される鍵である。

【0032】

乱数受信部201は、記憶装置100の外部から乱数を受信する。計算部205は、乱数受信部201が受信したデータと書き込みデータとから生成されるデータについて、鍵記憶部203が格納する共有鍵を用いてMAC値を計算する。

【0033】

データ送信部202は、書き込みデータと計算部205が計算したMAC値とを書き込み装置200の外部に送信する。

【0034】

書き込みデータ記憶部204は、書き込みデータを保持する。制御部206は、書き込み装置200全体を制御する。

【0035】

次に、このように構成された第1の実施形態にかかる書き込み装置200による書き込み処理について図4を用いて説明する。図4は、第1の実施形態の書き込み装置200の動作の一例を示すフローチャートである。

【0036】

書き込みデータを書き込む際、書き込み装置200のデータ送信部202は、記憶装置100に対して書き込み要求を発行する(ステップS21)。書き込み要求に応じて記憶装置100から乱数が送信されるので、乱数受信部201が当該乱数を受信して保持する(ステップS22)。計算部205は、書き込みデータ記憶部204から書き込みデータを受け取り、乱数受信部201から乱数を受け取る。計算部205は、鍵記憶部203の共有鍵を用いて、書き込みデータと乱数とを結合したデータのMAC値Mを、上記(1)式を用いて計算する(ステップS23)。

【0037】

その後、データ送信部202は、書き込みデータ記憶部204から書き込みデータDを受け取り、計算部205からMAC値Mを受け取る(ステップS24)。データ送信部202は、書き込みデータDとMAC値Mとを、記憶装置100に送信する(ステップS25)。

【0038】

このように、第1の実施形態にかかる情報処理システムでは、記憶装置が生成する乱数を用いて計算したMAC値により正当であると認証された場合にのみ書き込みデータを記憶装置に記憶する。乱数を用いるため、書き込みデータのMAC値が有効であるのは一度限りとなる。従って、記憶装置への書き込みに成功したデータを保持していて、当該データを再度書き込もうとしても、書き込みは不可能である。すなわち、システムプログラムなどのデータを安全にアップデート可能となる。

【0039】

(第2の実施形態)

第2の実施形態にかかる情報処理システムは、バージョン番号を用いてシステムプログラムを安全にアップデートする。本実施形態の情報処理システムによるデータの書き込み処理の概要を以下に説明する。

【0040】

書き込み装置は、システムプログラムなどの書き込みデータのバージョンを表すバージョン情報(バージョン番号)を、書き込みデータと共に記憶装置に送信する。その際、書き込み装置は書き込みデータとバージョン番号とを結合したデータに関するMAC値を計算し、当該MAC値も書き込みデータとバージョン番号に付随させて送信する。MAC値の計算には、記憶装置と共有している共有鍵を用いる。記憶装置は現在のバージョン番号を保持している。記憶装置は、書き込みデータとバージョン番号のMACを確認した後、バージョン番号が、記憶装置が保持する現在のバージョン番号より真に大きい場合に限り、指定アドレスにデータを書き込む。書き込みデータのバージョン番号が現在のバージョン番号より大きくない場合、記憶装置は書き込み装置からの当該書き込み要求を受理しない。この方法では、書き込み装置は乱数を受け取る必要がない。

【0041】

なお、上記説明では、バージョン番号は真に単調増加することを前提とした。しかし、「古くないデータ」を受け入れても良い場合は、記憶装置は、書き込みデータに付随するバージョン番号が、書き込み先アドレスのバージョン番号と同一である場合にも、書き込み先アドレスへの書き込みを行う。さらに、バージョン番号は単調減少であっても良い。また、書き込み装置と記憶装置との間で予め決められているルールによって、次のバージョン番号が計算できるように構成しても良い。例えば、関数fを、書き込み装置と記憶装置との間で共有する。記憶装置が現在保持しているバージョン番号をVcとする。この時、次のバージョン番号VnをVn=f(Vc)と定める。記憶装置は、バージョン番号Vnが付随する書き込みデータだけを受理する。

【0042】

図5は、第2の実施形態の記憶装置100−2の構成の一例を示すブロック図である。図5に示すように、記憶装置100−2は、データ記憶部110と、鍵記憶部105と、乱数送信部101と、データ受信部102−2と、計算部107−2と、バージョン記憶部111−2と、第1判定部112−2と、第2判定部113−2と、記憶制御部109−2と、制御部106と、を備えている。第1の実施形態の記憶装置100と同様の構成については、図1と同一符号を付し、ここでの説明は省略する。

【0043】

バージョン記憶部111−2は、書き込みデータのバージョン番号を格納する。なお、記憶装置100−2を初期化した直後などのように、まだデータが何も書き込まれていない時点では、バージョン記憶部111−2は、最も小さいバージョン番号、例えば0を格納する。

【0044】

データ受信部102−2は、記憶装置100−2の外部から書き込みデータとバージョン番号とMAC値とを受け取り、それらのデータを保持する。

【0045】

計算部107−2は、書き込みデータとバージョン番号とから生成されるデータについて、鍵記憶部105が格納する共有鍵を用いてMAC値を計算する。

【0046】

第1判定部112−2は、計算部107−2が計算したMAC値とデータ受信部102−2が受信したMAC値とを比較し、両者が一致するか否かを判定する。第1判定部112−2は、両者が一致した場合に限り書き込みデータを受理する。

【0047】

第2判定部113−2は、データ受信部102−2が受信したバージョン番号とバージョン記憶部111−2が格納するバージョン番号とを比較し、前者が後者より後のバージョンであるか否かを判定する。バージョン番号が真に単調増加する場合は、第2判定部113−2は、データ受信部102−2が受信したバージョン番号とバージョン記憶部111−2が格納するバージョン番号とを比較し、前者が後者より大であるか否かを判定する。第2判定部113−2は、前者が後者より大である場合に限り書き込みデータを受理する。

【0048】

記憶制御部109−2は、第1判定部112−2と第2判定部113−2が共に書き込みデータを受理した場合に限り書き込みデータをデータ記憶部110に記録する。

【0049】

次に、このように構成された第2の実施形態にかかる記憶装置100−2による記憶処理について図6を用いて説明する。図6は、第2の実施形態の記憶装置100−2の動作の一例を示すフローチャートである。

【0050】

まず、データ受信部102−2が、書き込み装置200−2から書き込みデータ、バージョン番号、およびMAC値を受信する(ステップS31)。計算部107−2は、データ受信部102−2から書き込みデータとバージョン番号とを受け取る。さらに計算部107−2は、鍵記憶部105からMAC計算用の共有鍵を読み出す。計算部107−2は、共有鍵を用いて、書き込みデータとバージョン番号とを結合したデータのMAC値を計算する(ステップS32)。すなわち、計算部107−2は以下の(2)式のようにMAC値Mを計算する(ステップS32)。

M=MAC(K,D||Vn) ・・・(2)

【0051】

ここに、Kは鍵記憶部105が格納している共有鍵、Dは書き込みデータ、Vnは書き込み装置200−2が送信しデータ受信部102−2が保持しているバージョン番号である。

【0052】

次に、第1判定部112−2は、書き込み装置200−2が送信しデータ受信部102−2が保持しているMAC値M’を読み出す。第1判定部112−2は、MとM’とを比較し、両者が一致するか否かを判定する(ステップS33)。両者が一致した場合(ステップS33:Yes)、第1判定部112−2は、書き込みデータを受理する。両者が一致しない場合(ステップS33:No)、記憶装置100−2は、書き込みデータを破棄して動作を停止する。

【0053】

第1判定部112−2が書き込みデータを受理した場合、第2判定部113−2は、バージョン記憶部111−2からバージョン番号Vcを読み出す。また、第2判定部113−2は、データ受信部102−2が保持しているバージョン番号Vnを読み出す。第2判定部113−2は、VnとVcとを比較し、VnがVcより大きいか否かを判定する(ステップS34)。

【0054】

VnがVcより大きくない場合(ステップS34:No)、第2判定部113−2は、書き込みデータを受理しない。この場合、データ受信部102−2の書き込みデータは破棄され、記憶装置100−2は動作を停止する。

【0055】

VnがVcより大きい(Vn>Vc)場合(ステップS34:Yes)、第2判定部113−2は、書き込みデータを受理する。第1判定部112−2と第2判定部113−2とが共にデータを受理した場合、記憶制御部109−2は、データ受信部102−2から書き込みデータを読み出し、当該書き込みデータをデータ記憶部110に記録する(ステップS35)。

【0056】

記憶制御部109−2は、データ受信部102−2が保持しているバージョン番号を読み出し、当該バージョン番号によってバージョン記憶部111−2が格納するバージョン番号を上書き更新する。例えば、システムプログラムのアップデートの際など、システムプログラムのバージョン番号をバージョン記憶部111−2に格納しておく。これにより、システムプログラムのロールバック(後戻り)を効果的に防止することができる。

【0057】

図7は、第2の実施形態の書き込み装置200−2の構成の一例を示すブロック図である。書き込み装置200−2は、鍵記憶部203と、バージョン受付部201−2と、計算部205−2と、データ送信部202−2と、書き込みデータ記憶部204と、制御部206と、を備えている。第1の実施形態の書き込み装置200と同様の構成については、図3と同一符号を付し、ここでの説明は省略する。

【0058】

バージョン受付部201−2は、書き込みデータのバージョン番号の入力を受付け、当該バージョン番号を保持する。計算部205−2は、書き込みデータと入力されたバージョン番号とから生成されるデータについて、鍵記憶部203が格納する共有鍵を用いてMAC値を計算する。

【0059】

データ送信部202−2は、書き込みデータとバージョン番号と計算部205−2が計算したMAC値とを、書き込み装置200−2の外部に送信する。

【0060】

次に、このように構成された第2の実施形態にかかる書き込み装置200−2による書き込み処理について図8を用いて説明する。図8は、第2の実施形態の書き込み装置200−2の動作の一例を示すフローチャートである。

【0061】

まず、バージョン受付部201−2が、バージョン番号の入力を受付ける(ステップS41)。入力されるバージョン番号として、書き込み対象である記憶装置100−2に対して最後に書き込んだバージョン番号より大きいバージョン番号が選択される。

【0062】

計算部205−2は、書き込みデータ記憶部204から書き込みデータDを受け取り、バージョン受付部201−2からバージョン番号Vnを受け取る。計算部205−2は、鍵記憶部105の共有鍵Kを用いて、書き込みデータとバージョン番号とを結合したデータのMAC値Mを、上記(2)式のように計算する(ステップS42)。

【0063】

その後、データ送信部202−2は、書き込みデータ記憶部204から書き込みデータDを受け取り、バージョン受付部201−2からバージョン番号Vnを受け取り、計算部205−2からMAC値Mを受け取る(ステップS43)。データ送信部202−2は、書き込みデータD、バージョン番号Vn、および、MAC値Mを記憶装置に送信する(ステップS44)。

【0064】

このように、第2の実施形態にかかる情報処理システムでは、書き込みデータのバージョン番号が、既に書き込まれているデータのバージョン番号より大きい場合にのみ書き込みデータを記憶装置に記憶する。記憶装置への書き込みに成功したデータを保持していて、当該データを再度書き込もうとしても、バージョン番号が現在のバージョン番号より大きくないため、書き込みは不可能である。すなわち、システムプログラムなどのデータを安全にアップデート可能となる。

【0065】

なお、ここではバージョン番号は数値であり、2つのバージョンの間には自明な大小関係が存在する。あるバージョン番号V1が別のバージョン番号V2より小さい時、バージョン番号V2はバージョン番号V1より「後の」バージョンであるということがある。バージョン番号は一般には全順序集合の要素である。全順序集合の定義は、例えば、日本数学会編集「岩波数学辞典第三版」に記載されている。バージョン番号の全順序集合における順序関係を≦で表す。バージョンV2がバージョンV1より大である(V1<V2)とは、V1≦V2であってV1≠V2であることをいう。

【0066】

以上説明したとおり、第1から第2の実施形態によれば、記憶装置にデータを書き込む場合のセキュリティを向上させることができる。例えば、記憶装置に記憶するシステムプログラムなどのデータのアップデートを保障することができる。

【0067】

次に、第1および第2の実施形態にかかる装置(記憶装置および書き込み装置)のハードウェア構成について図9を用いて説明する。図9は、第1および第2の実施形態にかかる装置のハードウェア構成を示す説明図である。

【0068】

第1および第2の実施形態にかかる装置は、CPU(Central Processing Unit)51などの制御装置と、ROM(Read Only Memory)52やRAM(RandoMACcess Memory)53などの記憶部と、ネットワークに接続して通信を行う通信I/F54と、各部を接続するバス61を備えている。

【0069】

第1および第2の実施形態にかかる装置で実行されるプログラムは、ROM52等に予め組み込まれて提供される。

【0070】

第1および第2の実施形態にかかる装置で実行されるプログラムは、インストール可能な形式又は実行可能な形式のファイルでCD−ROM(Compact Disk Read Only Memory)、フレキシブルディスク(FD)、CD−R(Compact Disk Recordable)、DVD(Digital Versatile Disk)等のコンピュータで読み取り可能な記録媒体に記録してコンピュータプログラムプロダクトとして提供されるように構成しても良い。

【0071】

さらに、第1および第2の実施形態にかかる装置で実行されるプログラムを、インターネット等のネットワークに接続されたコンピュータ上に格納し、ネットワーク経由でダウンロードさせることにより提供するように構成しても良い。また、第1および第2の実施形態にかかる装置で実行されるプログラムをインターネット等のネットワーク経由で提供または配布するように構成しても良い。

【0072】

第1および第2の実施形態にかかる装置で実行されるプログラムは、コンピュータを上述した装置の各部として機能させうる。このコンピュータは、CPU51がコンピュータ読取可能な記憶媒体からプログラムを主記憶装置上に読み出して実行することができる。

【0073】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0074】

100、100−2 記憶装置

101 乱数送信部

102 データ受信部

103 乱数記憶部

104 乱数発生部

105 鍵記憶部

106 制御部

107 計算部

108 判定部

109 記憶制御部

110 データ記憶部

111 バージョン記憶部

112−2 第1判定部

113−2 第2判定部

200、200−2 書き込み装置

201 乱数受信部

201−1 バージョン受付部

202 データ送信部

203 鍵記憶部

204 データ記憶部

205 計算部

206 制御部

【特許請求の範囲】

【請求項1】

外部装置と接続される記憶装置であって、

データを記憶するデータ記憶部と、

鍵を記憶する鍵記憶部と、

乱数を発生する乱数発生部と、

前記乱数発生部が発生した乱数を記憶する乱数記憶部と、

前記乱数を前記外部装置に送信する乱数送信部と、

前記データ記憶部に書き込む書き込みデータと、第1認証情報と、を前記外部装置から受信するデータ受信部と、

前記書き込みデータと前記乱数記憶部が記憶している乱数とから生成されるデータについて、前記鍵記憶部が記憶している鍵を用いて第2認証情報を計算する計算部と、

前記第1認証情報と前記第2認証情報とが一致するか否かを判定する判定部と、

前記第1認証情報と前記第2認証情報とが一致すると判定された場合に、前記書き込みデータをデータ記憶部に記憶する記憶制御部と、

を備えることを特徴とする記憶装置。

【請求項2】

記憶装置と接続される書き込み装置であって、

鍵を記憶する鍵記憶部と、

前記記憶装置から乱数を受信する乱数受信部と、

前記乱数と、前記記憶装置に書き込む書き込みデータとから生成されるデータについて、前記鍵記憶部が記憶している鍵を用いて認証情報を計算する計算部と、

前記書き込みデータと前記認証情報とを前記記憶装置に送信するデータ送信部と、

を備えることを特徴とする書き込み装置。

【請求項3】

外部装置と接続される記憶装置であって、

データを記憶するデータ記憶部と、

鍵を記憶する鍵記憶部と、

前記データのバージョンを表す第1バージョン情報を記憶するバージョン記憶部と、

前記データ記憶部に書き込む書き込みデータと、前記書き込みデータのバージョンを表す第2バージョン情報と、前記第2バージョン情報および前記書き込みデータに基づいて計算された第1認証情報と、を前記外部装置から受信するデータ受信部と、

前記書き込みデータと前記第1バージョン情報とから生成されるデータについて、前記鍵記憶部が記憶している鍵を用いて第2認証情報を計算する計算部と、

前記第1認証情報と前記第2認証情報とが一致するか否かを判定する第1判定部と、

前記第2バージョン情報により表されるバージョンが、前記第1バージョン情報により表されるバージョンより後のバージョンであるか否かを判定する第2判定部と、

前記第1認証情報と前記第2認証情報とが一致すると判定され、かつ、前記第2バージョン情報により表されるバージョンが前記第1バージョン情報により表されるバージョンより後のバージョンであると判定された場合に、前記書き込みデータをデータ記憶部に記憶する記憶制御部と、

を備えることを特徴とする記憶装置。

【請求項4】

前記記憶制御部は、前記データ記憶部に前記書き込みデータを記憶した後、前記第2バージョン情報によって、前記バージョン記憶部に記憶された前記第1バージョン情報を更新すること、

を特徴とする請求項3に記載の記憶装置。

【請求項5】

記憶装置と接続される書き込み装置であって、

鍵を記憶する鍵記憶部と、

前記記憶装置に書き込む書き込みデータのバージョンを表すバージョン情報の入力を受付ける受付部と、

前記バージョン情報と、前記書き込みデータとから生成されるデータについて、前記鍵記憶部が記憶している鍵を用いて認証情報を計算する計算部と、

前記書き込みデータと前記バージョン情報と前記認証情報とを前記記憶装置に送信するデータ送信部と、

を備えることを特徴とする書き込み装置。

【請求項1】

外部装置と接続される記憶装置であって、

データを記憶するデータ記憶部と、

鍵を記憶する鍵記憶部と、

乱数を発生する乱数発生部と、

前記乱数発生部が発生した乱数を記憶する乱数記憶部と、

前記乱数を前記外部装置に送信する乱数送信部と、

前記データ記憶部に書き込む書き込みデータと、第1認証情報と、を前記外部装置から受信するデータ受信部と、

前記書き込みデータと前記乱数記憶部が記憶している乱数とから生成されるデータについて、前記鍵記憶部が記憶している鍵を用いて第2認証情報を計算する計算部と、

前記第1認証情報と前記第2認証情報とが一致するか否かを判定する判定部と、

前記第1認証情報と前記第2認証情報とが一致すると判定された場合に、前記書き込みデータをデータ記憶部に記憶する記憶制御部と、

を備えることを特徴とする記憶装置。

【請求項2】

記憶装置と接続される書き込み装置であって、

鍵を記憶する鍵記憶部と、

前記記憶装置から乱数を受信する乱数受信部と、

前記乱数と、前記記憶装置に書き込む書き込みデータとから生成されるデータについて、前記鍵記憶部が記憶している鍵を用いて認証情報を計算する計算部と、

前記書き込みデータと前記認証情報とを前記記憶装置に送信するデータ送信部と、

を備えることを特徴とする書き込み装置。

【請求項3】

外部装置と接続される記憶装置であって、

データを記憶するデータ記憶部と、

鍵を記憶する鍵記憶部と、

前記データのバージョンを表す第1バージョン情報を記憶するバージョン記憶部と、

前記データ記憶部に書き込む書き込みデータと、前記書き込みデータのバージョンを表す第2バージョン情報と、前記第2バージョン情報および前記書き込みデータに基づいて計算された第1認証情報と、を前記外部装置から受信するデータ受信部と、

前記書き込みデータと前記第1バージョン情報とから生成されるデータについて、前記鍵記憶部が記憶している鍵を用いて第2認証情報を計算する計算部と、

前記第1認証情報と前記第2認証情報とが一致するか否かを判定する第1判定部と、

前記第2バージョン情報により表されるバージョンが、前記第1バージョン情報により表されるバージョンより後のバージョンであるか否かを判定する第2判定部と、

前記第1認証情報と前記第2認証情報とが一致すると判定され、かつ、前記第2バージョン情報により表されるバージョンが前記第1バージョン情報により表されるバージョンより後のバージョンであると判定された場合に、前記書き込みデータをデータ記憶部に記憶する記憶制御部と、

を備えることを特徴とする記憶装置。

【請求項4】

前記記憶制御部は、前記データ記憶部に前記書き込みデータを記憶した後、前記第2バージョン情報によって、前記バージョン記憶部に記憶された前記第1バージョン情報を更新すること、

を特徴とする請求項3に記載の記憶装置。

【請求項5】

記憶装置と接続される書き込み装置であって、

鍵を記憶する鍵記憶部と、

前記記憶装置に書き込む書き込みデータのバージョンを表すバージョン情報の入力を受付ける受付部と、

前記バージョン情報と、前記書き込みデータとから生成されるデータについて、前記鍵記憶部が記憶している鍵を用いて認証情報を計算する計算部と、

前記書き込みデータと前記バージョン情報と前記認証情報とを前記記憶装置に送信するデータ送信部と、

を備えることを特徴とする書き込み装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−69250(P2013−69250A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−209291(P2011−209291)

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]