記憶装置及び半導体装置

【課題】記憶機能の信頼性の高い有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導体装置を提供する。

【解決手段】第1の電極層及103び第2の電極層106からなる一対の電極間に有機化合物を含む層105を有する記憶素子と、当該記憶素子を有する素子層と、素子層上に形成される封止層111を有し、封止層111には吸湿材108が含まれている記憶装置及び半導体装置である。吸湿材108としては、溶融シリカ、結晶シリカ、アルミナ、窒化珪素、窒化アルミニウム、窒化ホウ素、ゼオライト、アルカリ土類金属の酸化物、硫酸塩、または高吸水性ポリマーの粒子で形成される。

【解決手段】第1の電極層及103び第2の電極層106からなる一対の電極間に有機化合物を含む層105を有する記憶素子と、当該記憶素子を有する素子層と、素子層上に形成される封止層111を有し、封止層111には吸湿材108が含まれている記憶装置及び半導体装置である。吸湿材108としては、溶融シリカ、結晶シリカ、アルミナ、窒化珪素、窒化アルミニウム、窒化ホウ素、ゼオライト、アルカリ土類金属の酸化物、硫酸塩、または高吸水性ポリマーの粒子で形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機化合物を含む層を有する記憶素子を備えた記憶装置及び半導体装置に関する。

【背景技術】

【0002】

近年、制御回路や記憶回路等に有機化合物を用いた有機薄膜トランジスタや記憶素子等の開発が盛んに行われている(例えば特許文献1)。

【0003】

また、絶縁表面上に複数の回路が集積され、様々な機能を有する半導体装置の開発が進められている。また、アンテナを設けることにより、無線によるデータの送受信が可能な半導体装置の開発が進められている。このような半導体装置は、無線チップ(IDタグ、ICタグ、ICチップ、RF(Radio Frequency)タグ、無線タグ、電子タグ、RFID(Radio Frequency Identification)タグともよばれる)とよばれ、既に一部の市場で導入されている。

【0004】

現在実用化されているこれらの半導体装置の多くは、Si等の半導体を用いた回路(IC(Integrated Circuit)チップとも呼ばれる)とアンテナとを有し、当該ICチップは記憶回路(メモリとも呼ぶ)や制御回路等から構成されている。

【特許文献1】特開2006−148080号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1で示すような有機化合物を含む層を有する記憶素子は、使用される環境によりダメージを受ける恐れがあり、その結果、記憶装置及び半導体装置の記憶機能、具体的には書込み特性、読み出し特性、記憶保持特性等の信頼性の低下を招く恐れがある。

【0006】

上記問題を鑑み、本発明は、有機化合物を含む層を有する素子が設けられた記憶装置及び半導体装置において、フレキシブルで記憶機能の信頼性の高い記憶装置及び半導体装置を提供する。

【課題を解決するための手段】

【0007】

第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子と、当該記憶素子を有する素子層と、素子層上に形成される封止層を有し、封止層には吸湿材が含まれていることを特徴とする記憶装置である。

【0008】

また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子と、当該記憶素子及び半導体素子を有する素子層と、素子層上に形成される封止層とを有し、封止層には吸湿材が含まれていることを特徴とする半導体装置である。

【0009】

吸湿材としては、溶融シリカ、結晶シリカ、アルミナ、窒化珪素、窒化アルミニウム、窒化ホウ素、ゼオライト、アルカリ土類金属の酸化物、金属の硫酸塩、または高吸水性ポリマーの粒子で形成される。吸湿材の粒径は、粒径1μm以上100μm以下、好ましくは5μm以上30μm以下、更に好ましくは5μm以上10μm以下である。

【0010】

封止層としては、フッ素含有ポリマー―、ポリオレフィン、ポリアクリロニトリル、ポリアミド、ポリエステル、エポキシ樹脂の高分子材料で形成される。

【0011】

また、半導体素子としては、MOSトランジスタ、薄膜トランジスタ、有機半導体トランジスタ等のトランジスタ、容量素子、抵抗素子等がある。また、素子層には、アンテナを含んでもよい。

【0012】

また、本発明の記憶装置及び半導体装置は情報を記憶する機能を有する。また、本発明の記憶装置及び半導体装置は、無線信号により命令やデータの送受信を行うと共に、当該無線信号で送受信した情報や、命令による処理結果を記憶する機能を有する。

【発明の効果】

【0013】

本発明の記憶装置及び半導体装置は、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子と、記憶素子を有する素子層と、素子層上に形成される封止層を有し、当該封止層には吸湿材が含まれている。封止層に吸湿材が含まれていることにより、記憶装置または半導体装置に曝される雰囲気中の水分が封止層に侵入しても、封止層に含まれる吸湿材で当該水分を吸収することができる。このため、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子が、水分に接触することを低減することが可能である。

【0014】

この結果、第1の電極、第2の電極、有機化合物を含む層等が水分や蒸気により劣化することを低減することが可能である。また、記憶素子の記憶保持特性の経年変化を抑制することが可能であり、記憶機能の信頼性の高い記憶装置及び半導体装置を作製することができる。また、素子層及び封止層を可撓性基板上に設けることにより、極めて薄く、フレキシブルで、且つ記憶保持能力の信頼性の高い記憶装置及び半導体装置を作製することができる。

【発明を実施するための最良の形態】

【0015】

本発明の実施の形態について図面を参照して説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

【0016】

(実施の形態1)

本実施の形態では、本発明の記憶装置の主要な構成について示す。代表的形態として、記憶素子が設けられたメモリセルを有する記憶装置を図1、2、及び4を用いて説明する。なお、各メモリ素子は、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有しており、メモリセルは記憶装置内でマトリクス状に配列されている。また、記憶素子の構造については、図3を用いて説明する。

【0017】

図4(A)に示すように、記憶装置127はメモリセルアレイ132及びメモリセルアレイを駆動する駆動回路を有する。メモリセルアレイ132には、メモリセル21がマトリクス状に設けられている。メモリセル21は、記憶素子107を有する(図1参照。)。記憶素子107は、基板101上に、第1の方向に延びた第1の電極層103と、第1の電極層103を覆う有機化合物を含む層105と、第1の方向と交差する第2の方向に延びた第2の電極層106とを有する。また、第2の電極層106を覆うように、保護膜として機能する絶縁層を設けてもよい。

【0018】

図4(A)に示すメモリセルアレイ132の断面構造について、図1及び2を用いて説明する。

【0019】

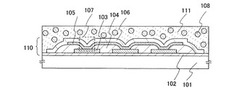

図1に示すように、基板101上に下地膜として機能する絶縁層102が形成される。絶縁層102上に第1の電極層103が形成され、第1の電極層103及び下地膜として機能する絶縁層102上に、絶縁層(または隔壁)104が形成される。なお、絶縁層(または隔壁)104は第1の電極層103を露出するように開口部が形成される。絶縁層(または隔壁)104及び第1の電極層上に有機化合物を含む層105が形成される。有機化合物を含む層105、絶縁層(または隔壁)104、及び下地膜として機能する絶縁層102上に第2の電極層106が形成される。

【0020】

第1の電極層103、有機化合物を含む層105、及び第2の電極層106により、記憶素子107を構成する。ここでは、下地膜として機能する絶縁層102から第2の電極層106までの積層物を素子層110という。

【0021】

また、素子層110上に吸湿材108を含む封止層111が形成される。

【0022】

封止層111は、塗布法を用いて組成物を塗布し、加熱または光照射による硬化により形成することが好ましい。封止層111は、後の剥離工程での保護層として設けるため、表面の凹凸の少ない絶縁層であることが好ましい。このような絶縁層は、塗布法により形成することができる。

【0023】

塗布法を用いて形成された封止層111は、フッ素含有ポリマー、ポリオレフィン、ポリアクリロニトリル、ポリアミド、ポリエステル、エポキシ樹脂、あるいはシロキサンポリマーを出発材料として形成された、シリカガラスに代表される無機シロキサンポリマー、又はアルキルシロキサンポリマー、アルキルシルセスキオキサンポリマー、水素化シルセスキオキサンポリマー、水素化アルキルシルセスキオキサンポリマーに代表される、珪素上の水素がメチル基やフェニル基のような有機基によって置換された有機シロキサンポリマーで形成される。

【0024】

フッ素含有ポリマーの代表例としては、ポリテトラフルオロエチレン、ポリクロロトリフルオロエチレン、ポリビニデンフルオライド、エチレン−テトラフルオロエチレン共重合体等がある。

【0025】

ポリオレフィンの代表例としては、ポリエチレン、ポリプロピレン、ポリブタジエン、ポリイソプレン、ポリスチレン等の重合体およびこれらの共重合体がある。

【0026】

エポキシ樹脂の代表例としては、クレゾールノボラック型エポキシ樹脂、ジシクロペンタジエン型エポキシ樹脂、トリフェニルメタン型エポキシ樹脂、ブロム含有エポキシ樹脂、ナフタレン環を有するエポキシ樹脂等がある。

【0027】

吸湿材108としては、粒径1μm以上100μm以下、好ましくは5μm以上30μm以下、更に好ましくは5μm以上10μm以下の吸湿性の高い粒子を用いることができる。吸湿性の高い粒子の代表例としては、溶融シリカ、結晶シリカ、アルミナ、窒化珪素、窒化アルミニウム、窒化ホウ素、ゼオライト、アルカリ土類金属の酸化物、金属の硫酸塩、高吸水性ポリマー等の粒子がある。

【0028】

アルカリ土類金属の酸化物の代表例としては、酸化カルシウム、酸化バリウム、酸化マグネシウム、酸化ストロンチウム等がある。

【0029】

金属の硫酸塩の代表例としては、硫酸リチウム、硫酸ナトリウム、硫酸カルシウム、硫酸マグネシウム、硫酸コバルト、硫酸ガリウム、硫酸チタン、硫酸ニッケル等がある。

【0030】

高吸水性ポリマーの代表例としては、ポリビニルアルコールやポリビニルピロリドン等のビニルポリマー、或いはポリエーテル、ポリエステル、ポリアミドなどの縮合系ポリマー等がある。なお、高吸水性ポリマーとは、水に溶けることなく、自重の1〜数100倍もの水を吸収し、且つ保持する能力を有するポリマーである。

【0031】

また、吸湿材108の形状は、球状、柱状、または多面体等である。また、水分を吸着する面積を増大させるため、表面が凹凸状であってもよい。また、吸湿材の表面に細孔が形成されていてもよい。

【0032】

また、封止層111における吸湿材108の割合は限定的ではないが、封止層111を形成する高分子材料、無機シロキサンポリマー、有機シロキサンポリマーに対して1〜20wt%、さらには5〜15wt%含まれることが好ましい。

【0033】

封止層111に吸湿材108が含まれることによって、封止層111が吸収した水分を吸湿材108で吸着、吸収することが可能である。このため、記憶装置の外気に含まれる水分が第1の電極層、第2の電極層、有機化合物を含む層等が形成されている素子層110に侵入することを抑制することが可能であり、これらの劣化を防ぐことができる。

【0034】

ここでは、封止層111は、吸湿材108として酸化カルシウム粒子が含まれたエポキシ樹脂を塗布法により塗布し、乾燥し焼成して形成する。

【0035】

基板101としては、ガラス基板、石英基板、金属基板やステンレス基板の一表面に絶縁層を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いる。上記に挙げた基板101には、大きさや形状に制約がないため、例えば、基板101として、1辺が1メートル以上であって、矩形状のものを用いれば、生産性を格段に向上させることができる。この利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。

【0036】

下地膜として機能する絶縁層102は、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、無機化合物を用いて単層又は多層で形成する。無機化合物の代表例としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素等がある。なお、下地膜として機能する絶縁層102に、窒化珪素、窒化酸化珪素、酸化窒化珪素等を用いることにより、後に形成される素子層へ水分や、酸素、二酸化炭素等の気体が外部から侵入することを防止することができる。

【0037】

さらには、下地膜として機能する絶縁層102を積層構造としても良い。例えば、無機化合物を用いて積層してもよく、代表的には、酸化珪素、窒化酸化珪素、及び酸化窒化珪素を積層して形成しても良い。

【0038】

第1の電極層103は、スパッタリング法やプラズマCVD法、塗布法、印刷法、電解メッキ法、無電解メッキ法等を用い、導電性の高い金属、合金、化合物等からなる単層または多層構造を用いて形成することができる。

【0039】

第1の電極層103としては、インジウム錫酸化物(以下、ITOと示す)、または酸化珪素を含有したインジウム錫酸化物、2〜20atomic%の酸化亜鉛(ZnO)を含む酸化インジウム等が挙げられる。また、チタン(Ti)、金(Au)、白金(Pt)、ニッケル(Ni)、タングステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、または金属材料の窒化物(例えば、窒化チタン、窒化タングステン、窒化モリブデン)等を用いることも可能である。

【0040】

また、第1の電極層103としては、リチウム(Li)やセシウム(Cs)等のアルカリ金属、およびマグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)等のアルカリ土類金属、アルミニウム(Al)およびこれらのいずれかを含む合金、ユーロピウム(Eu)、イッテルビウム(Yb)等の希土類金属およびこれらのいずれかを含む合金等が挙げられる。

【0041】

また、第1の電極層103として、スズ合金で形成することができる。スズ合金の代表例としては、スズ及び銀の合金、スズ及びビスマスの合金、スズ及びアンチモンの合金、スズ及び銅の合金、スズ及び金の合金、スズ及び亜鉛の合金、スズ及びインジウムの合金等がある。

【0042】

有機化合物を含む層105は、蒸着法、電子ビーム蒸着法、塗布法等を用いて形成することができる。

【0043】

ここでは、50〜200nmのチタン層をスパッタリング法により成膜した後、フォトリソグラフィ法により所望の形状にエッチングして第1の電極層103を形成する。次に、蒸着法によりNPBで形成される有機化合物を含む層を形成する。

【0044】

第2の電極層106は、蒸着法、スパッタリング法、CVD法、印刷法、塗布法等を用いて形成することができる。第2の電極層106は、第1の電極層103と同様の材料を適宜用いて形成することができる。また、第2の電極層106は、スズ合金で形成することができる。スズ合金の代表例としては、スズ及び銀の合金、スズ及びビスマスの合金、スズ及びアンチモンの合金、スズ及び銅の合金、スズ及び金の合金、スズ及び亜鉛の合金、スズ及びインジウムの合金等がある。さらには、銀、ビスマス、アンチモン、銅、金、亜鉛、及びインジウムから選ばれる複種類の元素及びスズとの合金を用いて第2の電極層106を形成してもよい。

【0045】

また、第2の電極層106を積層構造とすることもできる。代表的には、第1の層としてスズ合金層を形成した後、第2の層としてチタン(Ti)、金(Au)、白金(Pt)、ニッケル(Ni)、タングステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、アルミニウム(Al)、マグネシウム(Mg)、または金属材料の窒化物(例えば、窒化チタン、窒化タングステン、窒化モリブデン)等の金属層を形成してもよい。第2の層を形成することで、記憶素子にデータを書き込むときに高電流の通電が生じた場合、第1の層であるスズ合金層が剥れることを防止することができる。

【0046】

ここでは、蒸着法によりスズ及び銀を同時に蒸着して、スズ及び銀合金で第2の電極層106を形成する。

【0047】

ここで、記憶素子107のより具体的な構造について図3を用いて以下に示す。

【0048】

図3(A)に示すように、第1の電極層103及び第2の電極層106に印加された電圧により、結晶状態や導電性、形状が変化するような有機化合物を含む層105を形成することで、記憶素子107が形成される。第1の電極層103及び第2の電極層106に印加された電圧により、有機化合物を含む層105の結晶状態や導電性、形状が変化することで、記憶素子の電気抵抗が変化する。当該変化を用いて、0または1のデータを記録することができる。

【0049】

ここでは、有機化合物を含む層105は有機化合物層300で形成される。なお、有機化合物層300は、単層の有機化合物層または複数の有機化合物層で形成することができる。

【0050】

有機化合物を含む層105の厚さは、第1の電極層103及び第2の電極層106への電圧印加により記憶素子の電気抵抗が変化する厚さが好ましい。有機化合物を含む層105の代表的な膜厚は、1nmから100nm、好ましくは10nmから60nm、更に好ましくは5〜30nmである。

【0051】

有機化合物層300は、正孔輸送性を有する有機化合物又は電子輸送性を有する有機化合物を用いて形成することができる。

【0052】

正孔輸送性の有機化合物としては、例えば、フタロシアニン(略称:H2Pc)、銅フタロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VOPc)の他、4,4’,4’’−トリス(N,N−ジフェニルアミノ)トリフェニルアミン(略称:TDATA)、4,4’,4’’−トリス[N−(3−メチルフェニル)−N−フェニルアミノ]トリフェニルアミン(略称:MTDATA)、1,3,5−トリス[N,N−ジ(m−トリル)アミノ]ベンゼン(略称:m−MTDAB)、N,N’−ジフェニル−N,N’−ビス(3−メチルフェニル)−1,1’−ビフェニル−4,4’−ジアミン(略称:TPD)、4,4’−ビス[N−(1−ナフチル)−N−フェニルアミノ]ビフェニル(略称:NPB)、4,4’−ビス{N−[4−ジ(m−トリル)アミノ]フェニル−N−フェニルアミノ}ビフェニル(略称:DNTPD)、4,4’−ビス[N−(4−ビフェニリル)−N−フェニルアミノ]ビフェニル(略称:BBPB)、4,4’,4’’−トリ(N−カルバゾリル)トリフェニルアミン(略称:TCTA)などが挙げられるが、これらに限定されることはない。ここに述べた物質は、主に10−6cm2/Vs以上の正孔移動度を有する物質である。

【0053】

電子輸送性を有する有機化合物としては、トリス(8−キノリノラト)アルミニウム(略称:Alq3)、トリス(4−メチル−8−キノリノラト)アルミニウム(略称:Almq3)、ビス(10−ヒドロキシベンゾ[h]−キノリナト)ベリリウム(略称:BeBq2)、ビス(2−メチル−8−キノリノラト)−4−フェニルフェノラト−アルミニウム(略称:BAlq)等キノリン骨格またはベンゾキノリン骨格を有する金属錯体を用いることができる。また、この他、ビス[2−(2−ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称:Zn(BOX)2)、ビス[2−(2−ヒドロキシフェニル)ベンゾチアゾラト]亜鉛(略称:Zn(BTZ)2)などのオキサゾール、チアゾール配位子を有する金属錯体などの材料も用いることができる。さらに、金属錯体以外にも、2−(4−ビフェニリル)−5−(4−tert−ブチルフェニル)−1,3,4−オキサジアゾール(略称:PBD)、1,3−ビス[5−(p−tert−ブチルフェニル)−1,3,4−オキサジアゾール−2−イル]ベンゼン(略称:OXD−7)、3−(4−tert−ブチルフェニル)−4−フェニル−5−(4−ビフェニリル)−1,2,4−トリアゾール(略称:TAZ)、3−(4−tert−ブチルフェニル)−4−(4−エチルフェニル)−5−(4−ビフェニリル)−1,2,4−トリアゾール(略称:p−EtTAZ)、バソフェナントロリン(略称:BPhen)、バソキュプロイン(略称:BCP)等を用いることができる。ここに述べた物質は、主に10−6cm2/Vs以上の電子移動度を有する物質である。

【0054】

なお、上記範囲外の移動度を有する物質であっても良く、例えば2,3−ビス(4−ジフェニルアミノフェニル)キノキサリン(略称:TPAQn)、9−[4−(N−カルバゾリル)]フェニル−10−フェニルアントラセン(以下、CzPAと記す。)等を用いて形成してもよい。

【0055】

また、有機化合物層300は上記に示す有機化合物を複数混合して形成してもよい。また、上記に示す有機化合物を積層して形成してもよい。

【0056】

また、有機化合物層300は、正孔輸送性もしくは電子輸送性を有する有機化合物に絶縁物が混合されていても良い。なお、絶縁物は、均一に分散されている必要はない。絶縁物を混合することにより、有機化合物層300のモルフォロジーを向上することができる。よって、部分的な膜の結晶化を抑制することができるため、さらに記憶素子毎の挙動のばらつきを抑制することができる。

【0057】

また、図3(B)に示すように、有機化合物を含む層105として、有機化合物層300及びバッファ層301で形成してもよい。バッファ層301は、熱的及び化学的に安定な無機化合物または有機化合物で形成する。代表的には、無機絶縁物、無機半導体、または有機絶縁物で形成する。

【0058】

バッファ層301が無機絶縁物または有機絶縁物の場合は、トンネル効果により第1の電極層または第2の電極層から有機化合物層へ、正孔又は電子の電荷を注入する層である。バッファ層301は、所定の電圧において、トンネル効果により有機化合物層300へ電荷を注入することが可能な厚さで形成する。バッファ層301の代表的な厚さは、0.1nm以上4nm以下、好ましくは0.1nm以上2nm以下の絶縁層である。バッファ層301の膜厚は、0.1nm以上4nm以下と極めて薄いため、バッファ層301においてトンネル効果が生じ、有機化合物層300への電荷注入性が高まる。このため、バッファ層301は、厚さが4nmより厚くなると、バッファ層301におけるトンネル効果が生じず、有機化合物層300への電荷注入が困難となり、記憶素子の書き込み時の印加電圧が上昇する。

【0059】

バッファ層301を形成する無機絶縁物の代表例としては、酸化リチウム、酸化ナトリウム、酸化カリウム、酸化ルビジウム、酸化ベリリウム、酸化マグネシウム、酸化カルシウム、酸化ストロンチウム、酸化バリウム、酸化セシウム、酸化ジルコニウム、酸化ハフニウム、酸化フランシウム、酸化タンタル、酸化テクネチウム、酸化マンガン、酸化鉄、酸化コバルト、酸化パラジウム、酸化銀、アルミナ、酸化ガリウム、酸化ビスマス等に代表される絶縁性を有する酸化物が挙げられる。

【0060】

また、バッファ層301を形成する無機絶縁物の代表例としては、フッ化リチウム、フッ化ナトリウム、フッ化カリウム、フッ化セシウム、フッ化ベリリウム、フッ化マグネシウム、フッ化カルシウム、フッ化ストロンチウム、フッ化バリウム、フッ化アルミニウム、フッ化銀、フッ化マンガン等に代表される絶縁性を有するフッ化物、塩化リチウム、塩化ナトリウム、塩化カリウム、塩化セシウム、塩化ベリリウム、塩化カルシウム、塩化バリウム、塩化アルミニウム、塩化スズ、塩化銀、塩化亜鉛、塩化チタン、塩化ストロンチウム、塩化鉄、塩化パラジウム、塩化アンチモン、塩化ストロンチウム、塩化タリウム、塩化銅、塩化マンガン、塩化ルテニウム等に代表される絶縁性を有する塩化物、臭化カルシウム、臭化セシウム、臭化銀、臭化バリウム、臭化リチウム等に代表される絶縁性を有する臭化物、ヨウ化ナトリウム、ヨウ化カリウム、ヨウ化バリウム、ヨウ化タリウム、ヨウ化銀、ヨウ化チタン、ヨウ化カルシウム、ヨウ化珪素、ヨウ化セシウム等に代表される絶縁性を有するヨウ化物が挙げられる。

【0061】

また、バッファ層301を形成する無機絶縁物の代表例としては、炭酸リチウム、炭酸カルシウム、炭酸ナトリウム、炭酸マンガン、炭酸ストロンチウム、炭酸バリウム、炭酸鉄、炭酸コバルト、炭酸ニッケル、炭酸銅、炭酸銀、炭酸亜鉛等に代表される絶縁性を有する炭酸塩、硫化リチウム、硫化カルシウム、硫化ナトリウム、硫化マグネシウム、硫化ストロンチウム、硫化バリウム、硫化チタン、硫化ジルコニウム、硫化マンガン、硫化鉄、硫化コバルト、硫化ニッケル、硫化銅、硫化銀、硫化亜鉛、硫化アルミニウム、硫化インジウム、硫化スズ、硫化アンチモン、硫化ビスマス等に代表される絶縁性を有する硫酸塩、硝酸リチウム、硝酸カリウム、硝酸ナトリウム、硝酸マグネシウム、硝酸カルシウム、硝酸ストロンチウム、硝酸バリウム、硝酸チタン、硝酸ジルコニウム、硝酸マンガン、硝酸鉄、硝酸コバルト、硝酸ニッケル、硝酸銅、硝酸銀、硝酸亜鉛、硝酸アルミニウム、硝酸インジウム、硝酸スズ等に代表される絶縁性を有する硝酸塩、窒化アルミニウム、窒化珪素等に代表される絶縁性を有する窒化物が挙げられる。

【0062】

なお、バッファ層301を無機絶縁物で形成する場合、バッファ層301の膜厚は、0.1nm以上4nm以下が好ましい。絶縁層の膜厚が4nm以上になると、書き込み時の印加電圧が上昇する。

【0063】

バッファ層301を形成する有機絶縁物の代表例としては、ポリイミド、アクリル樹脂、ポリアミド、ベンゾシクロブテン樹脂、ポリエステル、ノボラック樹脂、メラミン樹脂、フェノール樹脂、エポキシ樹脂、シリコーン樹脂、フラン樹脂、ジアリルフタレート樹脂等に代表される有機化合物が挙げられる。

【0064】

バッファ層301を形成する無機半導体の代表例としては、シリコン、ゲルマニウム、酸化モリブデン、酸化スズ、酸化ビスマス、酸化バナジウム、酸化チタン、酸化鉄、酸化クロム、酸化銅、酸化マンガンシリコン、酸化ニッケル、酸化亜鉛、シリコンゲルマニウム、ヒ化ガリウム、窒化ガリウム、酸化インジウム、リン化インジウム、窒化インジウム、硫化カドミウム、テルル化カドミウム、チタン酸ストロンチウムなどの半導体を用いることができる。なお、バッファ層301は必ずしも一種の半導体から構成される必要はなく、複数の半導体材料が混合されていても良い。

【0065】

なお、バッファ層301を無機半導体で形成する場合、バッファ層301の膜厚は、0.1nm以上であれば特に限定されず、例えば10nm以下の薄い膜厚でも良いし、それ以上であっても良い。

【0066】

また、バッファ層301は異なる無機絶縁物、有機絶縁物、半導体で形成された層を単層で設けてもよいし、異なる無機絶縁物、有機絶縁物、半導体で形成された層を積層させて複数層としても良い。例えば、無機絶縁物層及び半導体層の積層、無機絶縁物層及び有機絶縁物層の積層、有機絶縁物層及び半導体層の積層等を適宜用いることができる。

【0067】

バッファ層301の形成方法としては、蒸着法、電子ビーム蒸着法、スパッタリング法、CVD法等を用いることができる。また、スピンコート法、ゾル−ゲル法、印刷法または液滴吐出法等を用いることができる。

【0068】

また、図3(C)に示すように、有機化合物を含む層105として、有機化合物層300及び凹凸を有する連続的なバッファ層302を用いて形成してもよい。但し、バッファ層の凸部における厚さは0.1nm以上10nm以下、好ましくは2nm以上8nm以下、凹部における厚さは、0.1nm以上4nm未満、好ましくは0.1nm以上2nm未満であることが好ましい。

【0069】

また、図3(D)に示すように、有機化合物を含む層105として、有機化合物層300及び分散された非連続な絶縁層303を用いて形成してもよい。非連続な絶縁層303は、島状、縞状、網目状等の形状を有してもよい。

【0070】

更には、バッファ層301〜303の代わりに、絶縁性粒子を設けてもよい。このときの絶縁性粒子は、粒径は0.1nm以上4nm以下であることが好ましい。

【0071】

なお、図3(B)〜(D)では、第1の電極層103及び有機化合物層300の間にバッファ層301〜303を設けたが、第2の電極層106及び有機化合物層300の間にバッファ層301〜303を設けてもよい。

【0072】

さらには、図3(E)に示すように、第1の電極層103及び有機化合物層300の間と、有機化合物層300及び第2の電極層106の間に、上記バッファ層301〜303または絶縁性粒子を設けてもよい。

【0073】

第1の電極層103及び有機化合物層300の間、または有機化合物層300及び第2の電極層106の間に、厚さが4nm以下、好ましくは2nm以下の無機絶縁物または有機絶縁物で形成されるバッファ層を設けることにより、当該絶縁層にトンネル電流が流れるため、記憶素子の書き込み時の印加電圧及び電流値のばらつきを低減することが可能である。また、第1の電極層103及び有機化合物層300の間、または有機化合物層300及び第2の電極層106の間に、厚さが4nm以下、好ましくは2nm以下の無機絶縁物または有機絶縁物で形成されるバッファ層を設けることにより、トンネル効果による電荷注入性が上昇し、有機化合物層300の膜厚を厚くすることが可能であり、初期状態でのショートを防止することが可能である。この結果、記憶装置及び半導体装置の信頼性を向上させることが可能である。

【0074】

また、上記構成とは異なる構成として、第1の電極層103及び有機化合物を含む層105の間、もしくは第2の電極層106と有機化合物を含む層105の間に、整流作用を有する素子を設けてもよい(図3(F))。整流作用を有する素子とは、代表的には、ショットキーダイオード、PN接合を有するダイオード、PIN接合を有するダイオード、あるいはゲート電極とドレイン電極を接続したトランジスタ等がある。もちろん、他の構成のダイオードでも構わない。ここでは、第1の電極層103と有機化合物を含む層105の間に、半導体層304、305を含むPN接合ダイオード306を設けた場合を示す。半導体層304、305のうち、一方はN型半導体であり、他方はP型半導体である。このように整流作用を有する素子を設けることにより、読み出し特性や書き込み特性を向上させることができる。

【0075】

また、基板上に形成した素子層及び封止層を剥して、図2(A)に示すような、可撓性を有する記憶装置113としてもよい。この場合、下地膜として機能する絶縁層102を、パッシベーション効果の有する層で形成することが好ましい。代表的な絶縁層102としては、窒化珪素層、窒化酸化珪素層を用いて形成することが好ましい。

【0076】

基板上に形成した素子層及び封止層を剥すために、基板及び下地膜として機能する絶縁層102の間に剥離層を形成することが好ましい。換言すると、基板から素子層及び封止層を容易に剥すために剥離層を用いることが好ましい。

【0077】

剥離層としては、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、タングステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、及び珪素(Si)の中から選択された元素、又は元素を主成分とする合金、又は元素を主成分とする化合物(代表的には、酸化物または窒化物)からなる層を、単層は複数の層を積層させて形成する。珪素を剥離層として用いる場合には、珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。

【0078】

剥離方法の一例としては、剥離層として上記金属のいずれかで形成される金属層及び当該金属酸化物層を形成し、剥離層を有する基板101及び素子層110を物理的手段により剥離する方法がある。物理的手段とは、力学的手段または機械的手段を指し、何らかの力学的エネルギー(機械的エネルギー)を半導体装置へ与える手段を指している。物理的手段は、代表的には機械的な力を加えること(例えば人間の手や把持具による剥離や、ローラを回転させる分離処理)である。

【0079】

また、他の剥離方法の一例としては、基板と素子層との間に、剥離層として水素を含む非晶質珪素層を設け、レーザ光の照射により非晶質珪素層に含まれる水素ガスを放出させて基板を剥離する方法がある。

【0080】

また、他の剥離方法の一例としては、基板と素子層との間に金属層及び金属酸化物層を有する剥離層を形成し、当該金属酸化物層を結晶化により脆弱化し、剥離層を液体のエッチャントやNF3、あるいはBrF3、ClF3等のフッ化ハロゲンガスによりエッチングで除去する方法がある。

【0081】

また、他の剥離方法の一例としては、素子層110及び封止層111が形成された基板101のみを機械的に削除する、又は基板101をエッチングで除去する方法がある。

【0082】

また、他の剥離方法の一例としては、基板101と素子層110との間に剥離層として金属層及び金属酸化物層を設け、当該金属酸化物層を結晶化により脆弱化し、金属層の一部を液体のエッチャントやNF3、あるいはBrF3、ClF3等のフッ化ハロゲンガスによりエッチングで除去した後、上記物理的方法を用いて脆弱化された金属酸化物層において物理的に剥離する方法がある。

【0083】

さらには、図2(B)に示すように、下地膜として機能する絶縁層102に可撓性基板120を接着材122を用いて貼りあわせて記憶装置128を形成してもよい。これにより、可撓性基板120上に素子層110及び封止層111が設けられる。このような記憶装置128は、薄型であり、且つ機械的強度の高い記憶装置である。

【0084】

可撓性基板120としては、可撓性を有する基板を用いることが好ましく、薄くて軽いものが好ましい。代表的には、PET(ポリエチレンテレフタレート)、PEN(ポリエチレンナフタレート)、PES(ポリエーテルスルホン)、ポリプロピレン、ポリプロピレンサルファイド、ポリカーボネート、ポリエーテルイミド、ポリフェニレンサルファイド、ポリフェニレンオキサイド、ポリサルフォン、ポリフタールアミド等のプラスチック基板、繊維質な材料からなる紙、セラミックシート等を用いることができる。当該基板を用いる場合、封止層111と可撓性基板120との間に接着材122を設けて、封止層111及び可撓性基板120を貼りあわせる。

【0085】

また、可撓性基板120として、繊維質な材料からなる紙または基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム等)と、接着性有機樹脂フィルム(アクリル樹脂、エポキシ樹脂等)との積層フィルムなどを用いることもできる。当該基板を用いる場合、可撓性基板120及び絶縁層102を熱圧着し、接着性有機樹脂フィルムを可塑化させた後、硬化させることで、積層フィルムに絶縁層102を固着させることができる。この場合は、絶縁層102及び可撓性基板120の間に接着材122を別途設ける必要は無い。

【0086】

素子層110または封止層111の一方の面に可撓性基板を有することで、このような記憶装置128の機械的強度を高めることが可能である。

【0087】

また、図2(C)に示すように、封止層111に接着材123を用いて可撓性基板125を貼り付けて、記憶装置126を形成することができる。即ち、可撓性基板120、125によって素子層110及び封止層111が封止されている。

【0088】

このような記憶装置126は素子層及び封止層111の周囲が可撓性基板で封止されているため、機械的強度及び外部環境に対する耐性を高めることが可能である。

【0089】

次に、上記で示す記憶装置のデータの書き込み動作及び読み出し動作について図4を用いて示す。

【0090】

図4(A)に示すように、メモリセル21は、ワード線Wy(1≦y≦n)に接続される第1の電極層と、ビット線Bx(1≦x≦m)に接続される第2の電極層と、有機化合物を含む層とを有する。有機化合物を含む層は、第1の電極層と第2の電極層の間に設けられる。

【0091】

メモリセルにデータの書き込みを行う際の動作について説明する。データの書き込みは、電気的作用によりデータの書き込みを行う場合について説明する。なお、書き込みはメモリセルの電気特性を変化させることで行うが、メモリセルの初期状態(電気的作用を加えていない状態)をデータ「0」、電気特性を変化させた状態を「1」とする。

【0092】

メモリセル21にデータ「1」を書き込む場合、まず、デコーダ133、134およびセレクタ135によってメモリセル21を選択する。例えば、デコーダ134によって、メモリセル131に接続されるワード線W3に所定の電圧V2が印加される。また、デコーダ133とセレクタ135によって、メモリセル21に接続されるビット線B3を読み出し/書き込み回路136に接続する。そして、読み出し/書き込み回路136からビット線B3へ書き込み電圧V1を出力する。こうして、当該メモリセル21を構成する第1の電極層と第2の電極層の間には電圧Vw=V1−V2を印加する。電位Vwを適切に選ぶことで、当該導電層間に設けられた有機化合物を含む層の特性を物理的もしくは電気的に変化させ、データ「1」の書き込みを行う。具体的には、読み出し動作電圧において、データ「1」の状態の第1の電極層と第2の電極層の間の電気抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化させるとよく、電圧Vwは5〜15V、あるいは−5〜−15Vとすればよい。例えば、(V1、V2)=(0V、5〜15V)、あるいは(3〜5V、−12〜−2V)などとすることができる。

【0093】

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「1」が書き込まれないよう制御する。例えば、非選択のワード線および非選択のビット線を浮遊状態とすればよい。メモリセル中のメモリ素子には、ダイオード特性など、選択性を確保できる特性を与える必要がある。

【0094】

一方、メモリセル21にデータ「0」を書き込む場合は、メモリセル21には電気的作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコーダ133、134およびセレクタ135によってメモリセル21を選択するが、読み出し/書き込み回路136からビット線B3への出力電位を、選択されたワード線W3の電位あるいは非選択ワード線の電位と同程度とする。すなわち、メモリセル131を構成する第1の電極層と第2の電極層の間に、メモリセル21の電気特性を変化させない程度の電圧(例えば−5〜5V)を印加すればよい。

【0095】

次に、メモリセルからデータの読み出しを行う際の動作について説明する(図4(B)、(C)参照)。データの読み出しは、メモリセルの電気特性が、データ「0」を有するメモリセルとデータ「1」を有するメモリセルとで異なることを利用して行う。例えば、データ「0」を有するメモリセルを構成する第1の電極層と第2の電極層の間の実効的な電気抵抗(以下、単にメモリセルの電気抵抗と呼ぶ)が、読み出し電圧においてR0、データ「1」を有するメモリセルの電気抵抗を、読み出し電圧においてR1とし、電気抵抗の差を利用して読み出す方法を説明する。なお、R1<<R0とする。読み出し/書き込み回路は、読み出し部分の構成として、例えば、図4(B)に示す抵抗素子146と差動増幅器147を用いた回路136を考えることができる。抵抗素子146は抵抗値Rrを有し、R1<Rr<R0であるとする。抵抗素子146の代わりにトランジスタ148を用いても良いし、差動増幅器の代わりにクロックドインバータ149を用いることも可能である(図4(C))。クロックドインバータ149には、読み出しを行うときにHi、行わないときにLowとなる信号又は反転信号が入力される。勿論、回路構成は図4(B)及び(C)に限定されない。

【0096】

メモリセル21からデータの読み出しを行う場合、まず、デコーダ133、134およびセレクタ135によってメモリセル21を選択する。具体的には、デコーダ134によって、メモリセル21に接続されるワード線W3に所定の電圧Vyを印加する。また、デコーダ133とセレクタ135によって、メモリセル21に接続されるビット線B3を読み出し/書き込み回路136の端子Pに接続する。その結果、端子Pの電位Vpは、抵抗素子146(抵抗値Rr)とメモリセル21(抵抗値R0もしくはR1)による抵抗分割によって決定される値となる。従って、メモリセル21がデータ「0」を有する場合には、Vp0=Vy+(V0−Vy)×R0/(R0+Rr)となる。また、メモリセル21がデータ「1」を有する場合には、Vp1=Vy+(V0−Vy)×R1/(R1+Rr)となる。その結果、図4(B)では、VrefをVp0とVp1の間となるように選択することで、図4(C)では、クロックドインバータの変化点をVp0とVp1の間となるように選択することで、出力電位Voutとして、データ「0」/「1」に応じて、Lo/Hi(もしくはHi/Lo)が出力され、読み出しを行うことができる。

【0097】

例えば、差動増幅器をVdd=3Vで動作させ、Vy=0V、V0=3V、Vref=1.5Vとする。仮に、R0/Rr=Rr/R1=9とすると、メモリセルのデータが「0」の場合、Vp0=2.7VとなりVoutはHighが出力され、メモリセルのデータが「1」の場合、Vp1=0.3VとなりVoutはLowが出力される。こうして、メモリセルの読み出しを行うことができる。

【0098】

上記の方法によると、有機化合物を含む層105の電気抵抗は、抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。勿論、読み出し方法は、この方法に限定されない。例えば、電気抵抗の差を利用する以外に、電流値の差を利用して読み出しても構わない。また、メモリセルの電気特性が、データ「0」と「1」とで、しきい値電圧が異なるダイオード特性を有する場合には、しきい値電圧の差を利用して読み出しても構わない。

【0099】

以上により、記憶素子の記憶保持特性の経年変化を抑制することが可能であり、記憶機能の信頼性の高い記憶装置を作製することができる。また、素子層及び封止層を可撓性基板上に設けることにより、極めて薄く、フレキシブルで、且つ記憶保持能力の信頼性の高い記憶装置を作製することができる。

【0100】

(実施の形態2)

本実施の形態では、上記実施の形態で示した記憶装置において、メモリセルにスイッチング素子及び記憶素子を有するメモリセルアレイを有する記憶装置の主要な構成について、図5及び図6を用いて説明する。図5は本実施の形態の記憶装置の断面図を示し、図6は本実施の形態の記憶装置の構造を示す。

【0101】

なお、図5においては、図2(C)に示す形態の変形例であり、可撓性基板で封止されている素子層及び封止層の形態について示す。また図5では、図1、図2(A)、及び図2(B)に示すような記憶装置の素子層の中にスイッチング素子及び記憶素子が形成されている状態が示されている。

【0102】

図6(A)に示すように、本実施の形態の記憶装置221はメモリセルアレイ222及びメモリセルアレイ222を駆動する駆動回路を有する。メモリセルアレイ222は、複数のメモリセル220がマトリクス状に設けられている。また、図6(A)及び図5に示すように、記憶装置221は、下地膜として機能する絶縁層150上に、駆動回路を構成するトランジスタ、(例えばデコーダ224を構成するトランジスタ152、スイッチング素子として機能するトランジスタ151)及び当該トランジスタ151に接続された記憶素子107が形成される。記憶素子107は、絶縁層205上に形成される第1の電極層103、有機化合物を含む層105、及び第2の電極層106を有する。なお、有機化合物を含む層105は、第1の電極層103、及び第1の電極層103の一部を覆う隔壁として機能する絶縁層104上に形成される。また、トランジスタ151として、薄膜トランジスタを用いている。また、第2の電極層106を覆って保護層として機能する絶縁層(図示せず)を有してもよい。

【0103】

また、下地膜として機能する絶縁層150から第2の電極層106の積層体を覆うように、吸湿材108が含まれる封止層111が形成される。ここでは、封止層111に覆われる積層体を素子層201と示す。

【0104】

また、素子層201及び封止層111は可撓性基板120、125で封止されている。なお、可撓性基板120は接着材122で素子層201及び封止層111に貼り付けられており、可撓性基板125は接着材123で封止層111に貼り付けられている。

【0105】

封止層111に吸湿材108が含まれることによって、封止層111で吸収した水分を吸湿材108で吸着、吸収することが可能である。このため、記憶装置の外気に含まれる水分が第1の電極層、第2の電極層、有機化合物を含む層等が形成されている素子層201に侵入することを抑制することが可能であり、これらの劣化を防ぐことができる。

【0106】

トランジスタ151、152は、Siウエハーを用いたMOSトランジスタ、SOI基板を用いたMOSトランジスタ、薄膜トランジスタ、有機半導体トランジスタ等を適宜用いることができる。ここでは、トランジスタ151、152として薄膜トランジスタを用いて示す。なお、ここでは、薄膜トランジスタとしてトップゲート型の薄膜トランジスタを示しているがこれに限定される物ではない。ボトムゲート型の薄膜トランジスタを適用することが可能である。

【0107】

記憶素子107は、絶縁層205上に形成される。このように、絶縁層205を設けることによって第1の電極層103を自由にレイアウトすることができる。つまり、トランジスタ151の上方に記憶素子107を形成することが可能となる。その結果、記憶装置をより高集積化することが可能となる。

【0108】

絶縁層205は、上記実施の形態で示した絶縁層104と同様の材料および形成方法を適宜用いて形成することができる。

【0109】

素子層201及び封止層111に貼り付ける可撓性を有する基板としては、実施の形態1の可撓性基板120で示した可撓性基板、熱可塑性樹脂を有するフィルム、繊維質な材料からなる紙、セラミックシート等を用いることで、記憶装置の小型、薄型、軽量化を図ることが可能である。

【0110】

次に、本実施の形態で示す記憶装置のデータの書き込み動作及び読み出し動作について図6を用いて示す。

【0111】

メモリセル220は、ワード線Wy(1≦y≦n)に接続する第1の電極層と、ビット線Bx(1≦x≦m)に接続する第2の電極層と、トランジスタ151と、記憶素子107とを有する。記憶素子107は、一対の導電層の間に、有機化合物を含む層が挟まれた構造を有する。トランジスタ151のゲート電極はワード線と接続され、ソース電極もしくはドレイン電極のいずれか一方はビット線と接続され、残る一方は記憶素子107が有する第1の電極層と接続される。記憶素子の残る第2の電極層は接続端子と接続される。また、接続端子は共通電極(電位Vcom)と接続される。

【0112】

次に、メモリセルアレイ222にデータの書き込みを行うときの動作について説明する。

【0113】

ここでは、3行3列目のメモリセル220に電気的作用によりデータを書き込む場合について説明する。なお、書き込みはメモリセルの電気特性を変化させることで行うが、メモリセルの初期状態(電気的作用を加えていない状態)をデータ「0」、電気特性を変化させた状態を「1」とする。

【0114】

メモリセル220にデータ「1」を書き込む場合、まず、デコーダ223、224およびセレクタ225によってメモリセル220を選択する。具体的には、デコーダ224によって、メモリセル220に接続されるワード線W3に所定の電圧V22を印加する。また、デコーダ223とセレクタ225によって、メモリセル220に接続されるビット線B3を読み出し/書き込み回路226に接続する。そして、読み出し/書き込み回路226からビット線B3へ書き込み電圧V21を出力する。

【0115】

こうして、メモリセルを構成するトランジスタ151をオン状態とし、記憶素子107に、ビット線を電気的に接続し、おおむねVw=Vcom−V21の電圧を印加する。なお、記憶素子107の第2の電極層は電位Vcomの共通電極に接続されている。電位Vwを適切に選ぶことで、当該導電層間に設けられた有機化合物を含む層105の特性を物理的もしくは電気的に変化させ、データ「1」の書き込みを行う。具体的には、読み出し動作電圧において、データ「1」の状態の第1の電極層と第2の電極層の間の電気抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化させるとよく、従って、単に短絡(ショート)させてもよい。なお、電位は、(V21、V22、Vcom)=(5〜15V、5〜15V、0V)、あるいは(−12〜0V、−12〜0V、3〜5V)の範囲から適宜選べば良い。電圧Vwは5〜15V、あるいは−5〜−15Vとすればよい。

【0116】

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「1」が書き込まれないよう制御する。具体的には、非選択のワード線には接続されるメモリセルのトランジスタをオフ状態とする電位(例えば0V)を印加し、非選択のビット線は浮遊状態とするか、Vcomと同程度の電位を印加するとよい。

【0117】

一方、メモリセル220にデータ「0」を書き込む場合は、メモリセル220には電気的作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコーダ223、224およびセレクタ225によってメモリセル220を選択するが、読み出し/書き込み回路226からビット線B3への出力電位をVcomと同程度とするか、ビット線B3を浮遊状態とする。その結果、記憶素子107には、小さい電圧(例えば−5〜5V)が印加されるか、電圧が印加されないため、電気特性が変化せず、データ「0」書き込みが実現される。

【0118】

次に、電気的作用により、データの読み出しを行う際の動作について説明する。データの読み出しは、電気特性が、データ「0」を有する記憶素子とデータ「1」を有する記憶素子とで異なることを利用して行う。例えば、データ「0」を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧においてR0、データ「1」を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧においてR1とし、電気抵抗の差を利用して読み出す方法を説明する。なお、R1<<R0とする。読み出し/書き込み回路は、読み出し部分の構成として、例えば、図6(B)に示す抵抗素子246と差動増幅器247を用いた回路226を考えることができる。抵抗素子246は抵抗値Rrを有し、R1<Rr<R0であるとする。抵抗素子246の代わりに、トランジスタ250を用いても良いし、差動増幅器の代わりにクロックドインバータ251を用いることも可能である(図6(C))。勿論、回路構成は図6(B)及び(C)に限定されない。

【0119】

3列3行目メモリセル220からデータの読み出しを行う場合、まず、デコーダ223、224およびセレクタ225によってメモリセル220を選択する。具体的には、デコーダ224によって、メモリセル220に接続されるワード線W3に所定の電圧V24を印加し、トランジスタ151をオン状態にする。また、デコーダ223とセレクタ225によって、メモリセル220に接続されるビット線B3を読み出し/書き込み回路226の端子Pに接続する。その結果、端子Pの電位Vpは、VcomとV0が抵抗素子246(抵抗値Rr)と記憶素子107(抵抗値R0もしくはR1)による抵抗分割によって決定される値となる。従って、メモリセル220がデータ「0」を有する場合には、Vp0=Vcom+(V0−Vcom)×R0/(R0+Rr)となる。また、メモリセル220がデータ「1」を有する場合には、Vp1=Vcom+(V0−Vcom)×R1/(R1+Rr)となる。その結果、図6(B)では、VrefをVp0とVp1の間となるように選択することで、図6(C)では、クロックドインバータの変化点をVp0とVp1の間となるように選択することで、出力電位Voutが、データ「0」/「1」に応じて、Lo/Hi(もしくはHi/Lo)が出力され、読み出しを行うことができる。

【0120】

例えば、差動増幅器をVdd=3Vで動作させ、Vcom=0V、V0=3V、Vref=1.5Vとする。仮に、R0/Rr=Rr/R1=9とし、トランジスタ151のオン抵抗を無視できるとすると、メモリセルのデータが「0」の場合、Vp0=2.7VとなりVoutはHighが出力され、メモリセルのデータが「1」の場合、Vp1=0.3VとなりVoutはLowが出力される。こうして、メモリセルの読み出しを行うことができる。

【0121】

上記の方法によると、記憶素子107の抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。勿論、読み出し方法は、この方法に限定されない。例えば、電気抵抗の差を利用する以外に、電流値の差を利用して読み出しても構わない。また、メモリセルの電気特性が、データ「0」と「1」とで、しきい値電圧が異なるダイオード特性を有する場合には、しきい値電圧の差を利用して読み出しても構わない。

【0122】

以上により、記憶素子の記憶保持特性の経年変化を抑制することが可能であり、記憶保持機能の信頼性の高い記憶装置を作製することができる。また、素子層及び封止層を可撓性基板上に設けることにより、極めて薄く、フレキシブルで、且つ記憶保持能力の信頼性の高い記憶装置を作製することができる。

【0123】

(実施の形態3)

本実施の形態では、上記実施の形態で示した剥離方法を用いて形成した半導体装置の一形態について以下に説明する。代表的には、無線信号により命令やデータの送受信を行うことのできる半導体装置の主要な構成について、図7及び図8を用いて説明する。図7は本実施の形態の半導体装置の断面図を示し、図8は本実施の形態の半導体装置の構造を示す。なお、本実施の形態の半導体装置は上記実施の形態で示すメモリセルアレイからなるメモリ部を有する。

【0124】

図8は、無線信号により命令やデータの送受信を行うことのできる半導体装置の一構成例を示すブロック図である。このような半導体装置は、アンテナ312、高周波回路部313、電源回路部315、ロジック回路部317を要素として含んでいる。アンテナ312は、リーダライタとも呼ばれる通信装置と信号の送受信を行う。信号を送る搬送波の周波帯は、長波帯の30〜135kHz、短波帯の6.78MHz、13.56MHz、27.125MHz、40.68MHz、5.0MHz、マイクロ波帯の2.45GHz、5.8GHz、24.125GHz等が適用される。アンテナ312は通信周波数帯に応じてコイル型やモノポール若しくはダイポール型の形態となる。

【0125】

アンテナ312が受信した搬送波は、検波容量部314を介して電源回路部315と、ロジック回路部317に分流する。電源回路部315では整流回路部320によって半波整流され、それが保持容量部322に充電される。定電圧回路部324は受信した搬送波の電力によってある一定以上の電力が供給されても、一定電圧を出力してこの半導体装置にあるロジック回路部317等の動作に必要な電力を供給する。

【0126】

高周波回路部313における復調回路部318は、搬送波を復調してロジック回路部317の動作に必要なクロック信号を生成し、さらにそれを補正する機能を有するPLL回路部328と、コード認識及び判定回路部326に信号を出力する。例えば、復調回路部318は、振幅変調(ASK)の受信信号から、振幅の変動を”0”又は”1”の受信データとして検出する。復調回路部318は、例えばローパスフィルターを含んで構成されている。また、変調回路部316は送信データを振幅変調(ASK)の送信信号として送信する。

【0127】

コード認識及び判定回路部326は、命令コードを認識し判定する。各コード認識及び判定回路部326が認識及び判定する命令コードは、フレーム終了信号(EOF、end of frame)、フレーム開始信号(SOF、start of frame)、フラグ、コマンドコード、マスク長(mask length)、マスク値(mask value)等である。また、各コード認識及び判定回路部326は、送信エラーを識別する巡回冗長検査(CRC、cyclic redundancy check)機能も含む。コード認識及び判定回路部326からの結果は、メモリコントローラ部330に出力される。メモリコントローラ部330は、判定結果に基づいて、メモリ部332の読み出しを制御する。メモリ部332から読み出されたデータは、符号化回路部334にて符号化され、変調回路部316によって変調を行い、応答信号が生成する。

【0128】

メモリ部332の構成としては、実施の形態1で示すような記憶素子を有するメモリセルや、実施の形態2で示すようなスイッチング素子に接続される記憶素子を有するメモリセルを適宜用いることができる。また、上記実施の形態で示すようなメモリセルの他に固定データのみを記憶するマスクROM(Read Only Memory)、SRAM(Static Random Access Memory)などの任意読み出し書き込み可能メモリ、電荷蓄積浮遊電極を有する不揮発性メモリなどを適用することができる。

【0129】

このように、図8で示す半導体装置は、リーダライタとも呼ばれる通信装置からの命令を受信して、メモリ部332にデータを書き込み、若しくはメモリ部332からデータを読み出す機能を有している。

【0130】

次に、本実施の形態の半導体装置の断面構造について、図7を用いて説明する。

【0131】

なお、図7においては、図2(C)に示す形態の変形例であり、可撓性基板で封止されている素子層及び封止層の形態について示す。しかし、この実施の形態では、図1、図2(A)、及び図2(B)に示すような記憶装置の素子層に以下の実施の形態に示す記憶装置、アンテナ、半導体素子等が形成される。

【0132】

ここで、半導体装置の一部として、メモリコントローラ部330、メモリ部332、アンテナ312、及び検波容量部314の断面図を示す(図7参照)。代表的には、下地膜として機能する絶縁層321上に、メモリコントローラ部330を構成するトランジスタ152、メモリ部332を構成するトランジスタ151及び当該トランジスタ151に接続された記憶素子107、検波容量部314の容量素子331及び薄膜トランジスタ333、アンテナ312を示す。なお、ここでは図示しないが、アンテナ312及び薄膜トランジスタ333は電気的に接続している。

【0133】

記憶素子107は、絶縁層205上に形成される第1の電極層103、有機化合物を含む層105、及び第2の電極層106を有する。第2の電極層106は、スズ合金層で形成される。なお、有機化合物を含む層105は、第1の電極層103、及び第1の電極層103の一部を覆う隔壁として機能する絶縁層104上に形成される。また、スイッチング素子として機能するトランジスタ151は、薄膜トランジスタを用いて形成する。また、第2の電極層106を及びアンテナ312を覆って保護層として機能する絶縁層を有してもよい。なお、下地膜として機能する絶縁層150からアンテナ312までの積層体を素子層341と示す。

【0134】

また、素子層341を覆うように吸湿材108が含まれる封止層111が形成される。

【0135】

封止層111に吸湿材108が含まれることによって、封止層111で吸収した水分を吸湿材108で吸着、吸収することが可能である。このため、半導体装置の外気に含まれる水分が第1の電極層、第2の電極層、有機化合物を含む層等が形成されている素子層110に侵入することを抑制することが可能であり、これらの劣化を防ぐことができる。

【0136】

また、素子層341及び封止層111が可撓性基板120、125で封止されている。なお、可撓性基板120は接着材122で素子層341及び封止層111に貼り付けられており、可撓性基板125は接着材123で封止層111に貼り付けられている。

【0137】

本実施の形態により、記憶素子の記憶保持特性の経年変化を抑制することが可能であり、無線で情報を送受信することが可能で、記憶機能の信頼性の高い半導体装置を作製することができる。また、素子層及び封止層を可撓性基板上に設けることにより、極めて薄く、フレキシブルで、無線で情報を送受信することが可能で、且つ記憶保持能力の信頼性の高い半導体装置を作製することができる。

【実施例1】

【0138】

本実施例では、無線信号により命令やデータの送受信を行うことのできる半導体装置において、スイッチング素子に接続される記憶素子がマトリクス状に配置されたメモリセルアレイを有する半導体装置の作製方法について、図9〜図15を用いて以下に説明する。

【0139】

基板501上に剥離層502を形成する。基板501としてはガラス基板を用いる。また、剥離層502としては、金属層及び金属酸化物層の積層構造とする。金属層としては、スパッタリング法により得られる30nm〜200nmのタングステン層、窒化タングステン層、またはモリブデン層を用いる。

【0140】

次に、金属酸化物層としては、金属層の表面を酸化させて金属酸化物層を形成する。金属酸化物層の形成方法は、酸素を含有する純水やオゾン水を用いて表面を酸化して形成してもよいし、酸素プラズマで酸化して形成してもよい。また、酸素を含む雰囲気で加熱を行って金属酸化物層を形成してもよい。また、後の絶縁層の形成工程で形成してもよい。この場合、絶縁層として酸化珪素層や酸化窒化珪素層をプラズマCVD法で形成する際に、剥離層502表面が酸化されて金属酸化物層が形成される。

【0141】

次に、金属酸化物層上に第1絶縁層503を形成する。第1絶縁層503としては、酸化珪素層、窒化珪素層または酸化窒化珪素層等の絶縁層を用いる。代表的な一例は第1絶縁層503として2層構造から成り、PCVD法によりSiH4、NH3、及びN2Oを反応ガスとして成膜される窒化酸化珪素層を50〜100nm、SiH4、及びN2Oを反応ガスとして成膜される酸化窒化珪素層を100〜150nmの厚さに積層形成する構造が採用される。また、第1絶縁層503の一層として膜厚10nm以下の窒化珪素層、或いは酸化窒化珪素層を用いることが好ましい。また、窒化酸化珪素層と、酸化窒化珪素層と、窒化珪素層とを順次積層した3層構造を用いてもよい。ここでは下地絶縁膜として第1絶縁層503を形成した例を示したが、特に必要でなければ設ける必要はない。

【0142】

次に、第1絶縁層503上に半導体層を形成する。半導体層は、非晶質構造を有する半導体層をスパッタリング法、LPCVD法、またはプラズマCVD法等により成膜する。次に、結晶化処理(レーザ結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体層上に第1のフォトマスクを用いてレジストマスクを形成した後、所望の形状にエッチングして、半導体層を形成する。なお、プラズマCVD法を用いれば、第1絶縁層と、非晶質構造を有する半導体層とを大気に触れることなく連続的に積層することができる。この半導体層の厚さは25〜80nm(好ましくは30〜70nm)の厚さで形成する。結晶質半導体層の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム合金などで形成すると良い。

【0143】

また、非晶質構造を有する半導体層を結晶化するために連続発振のレーザを用いてもよく、非晶質半導体層の結晶化に際し、大粒径に結晶を得るためには、連続発振が可能な固体レーザを用い、基本波の第2高調波〜第4高調波を適用するのが好ましい。代表的には、Nd:YVO4レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を適用すればよい。連続発振のレーザを用いる場合には、出力10Wの連続発振のYVO4レーザから射出されたレーザ光を非線形光学素子により高調波に変換する。また、共振器の中にYVO4結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または楕円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01〜100MW/cm2程度(好ましくは0.1〜10MW/cm2)が必要である。そして、10〜2000cm/s程度の速度でレーザ光に対して相対的に半導体層を移動させながら照射すればよい。

【0144】

また、非晶質構造を有する半導体層の結晶化処理としてSLS方式(Sequential Lateral Solidification method)を用いてもよい。SLS法は、パルス発振のエキシマレーザー光を、スリット状のマスクを介して、試料に照射するものである。1ショット毎に、試料とレーザ光の相対位置をスーパーラテラル成長による結晶長さ程度ずらして結晶化を行うことで、人工的に制御したスーパーラテラル成長による結晶を連続的に形成させる方法である。

【0145】

次に、必要があれば薄膜トランジスタのしきい値を制御するために、微量な不純物元素(ボロンまたはリン)のドーピングを半導体層に対して行う。ここでは、ジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法を用いる。

【0146】

次に、後に容量素子の容量電極となる半導体層に第2フォトマスクを用いてレジストマスクを形成し、不純物元素を導入することにより低濃度不純物領域を形成する。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いることができる。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。ここでは、半導体層にリン(P)を1×1015〜1×1019/cm3の濃度で含まれるように導入することによりn型を示す不純物領域を形成する。

【0147】

次に、フッ酸を含むエッチャントで半導体層表面の酸化層を除去すると同時に半導体層の表面を洗浄する。

【0148】

次に、半導体層を覆う第2絶縁層を形成する。第2絶縁層はプラズマCVD法またはスパッタリング法を用い、厚さを1〜200nmとする。好ましくは10nm〜50nmと薄くしてシリコンを含む絶縁層の単層または積層構造で形成した後にマイクロ波によるプラズマを用いた表面窒化処理を行う。第2絶縁層は、後に形成される薄膜トランジスタのゲート絶縁層として機能する。

【0149】

次に、第2絶縁層上にゲート電極504〜507、容量電極508を形成する。スパッタリング法によって膜厚100nm〜500nmで導電層を形成し、この上に第3のフォトマスクを用いてレジストマスクを形成する。そして導電層を所望の形状にエッチングして、ゲート電極504〜507、及び容量電極508を形成する。

【0150】

ゲート電極504〜507及び容量電極508の材料としては、シリコンとシリサイド反応する材料であればよく、Ti、W、Ni、Cr、Mo、Ta、Co、Zr、V、Pd、Hf、Pt、Feから選ばれた元素、または前記元素を主成分とする合金若しくは化合物の単層、またはこれらの積層で形成してもよい。ただし、薄膜トランジスタのゲート電極としては高融点金属が好ましく、WまたはMoを用いる。ゲート電極504〜507及び容量電極508を積層とする場合には、上層となる材料層が上述した材料であれば、下層となる材料層は、リン等の不純物元素をドーピングした多結晶シリコン層としてもよい。また、上層に上記材料を用い、下層に上記材料の窒化物で形成してもよい。このとき下層を金属窒化物とすることで、上層の金属が、ゲート絶縁層やその下層の半導体層に拡散することを防ぐことができる。

【0151】

次に、pチャネル型薄膜トランジスタとする領域の半導体層を覆うように第4のフォトマスクを用いてレジストマスクを形成し、nチャネル型薄膜トランジスタとする領域の半導体層にゲート電極505〜507をマスクとして不純物元素を導入することにより低濃度不純物領域を形成する。ここでは、nチャネル型薄膜トランジスタとする領域の半導体層にリン(P)を1×1015〜1×1019/cm3の濃度で含まれるように導入することによりn型を示す不純物領域を形成する。

【0152】

次に、レジストマスクを除去して、nチャネル型薄膜トランジスタとする半導体層を覆うように第5のフォトマスクを用いてレジストマスクを形成し、pチャネル型薄膜トランジスタとする領域の半導体層にゲート電極504をマスクとして不純物元素を導入することによりp型を示す不純物領域を形成する。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。ここでは、pチャネル型薄膜トランジスタとする領域の半導体層にボロン(B)を1×1019〜1×1020/cm3の濃度で含まれるように導入することによって、p型を示す不純物領域を形成することができる。その結果、pチャネル型薄膜トランジスタとする領域の半導体層に、ソース領域又はドレイン領域514、515、及びチャネル形成領域516が形成される。

【0153】

次に、ゲート電極504〜507及び容量電極508の両側面にサイドウォール510を形成する。サイドウォール510は、まず、第2絶縁層、ゲート電極504〜507、及び容量電極508を覆うように、珪素の酸化物又は珪素の窒化物の無機材料を含む層や、有機樹脂等の有機材料を含む層を単層又は積層して第3絶縁層を形成する。第3の絶縁層はプラズマCVD法やスパッタリング法等を適用して形成することができる。次に、第3絶縁層を、垂直方向を主体とした異方性エッチングにより選択的にエッチングすることによって、ゲート電極504〜507、容量電極508の側面に接する絶縁層(サイドウォール510)を形成する。なお、サイドウォール510の形成と同時に、第2絶縁層の一部をエッチングして除去する。第2絶縁層の一部が除去されることによって、残存するゲート絶縁層512は、ゲート電極504〜507、容量電極508、及びサイドウォール510の下方に形成される。

【0154】

次に、pチャネル型薄膜トランジスタとする半導体層を覆うように第6のフォトマスクを用いてレジストマスクを形成し、nチャネル型薄膜トランジスタとする領域の半導体層にゲート電極504〜507、容量電極508、及びサイドウォール510をマスクとして不純物元素を導入することにより高濃度不純物領域を形成する。不純物元素の導入後にレジストマスクは除去する。ここでは、nチャネル型薄膜トランジスタとする領域の半導体層にリン(P)を1×1019〜1×1020/cm3の濃度で含まれるように導入することによって、n型を示す高濃度不純物領域を形成することができる。その結果、nチャネル型薄膜トランジスタとする領域の半導体層に、ソース領域又はドレイン領域517、518、LDD領域519、520、チャネル形成領域521が形成される。サイドウォール510の下方にLDD領域519、520が形成される。また、容量素子の容量電極となる半導体層に低濃度不純物領域511及び高濃度不純物領域513が形成される。

【0155】

nチャネル型薄膜トランジスタに含まれる半導体層にLDD領域を形成し、pチャネル型薄膜トランジスタに含まれる半導体層にLDD領域を設けない構造を示したが、もちろんこれに限られず、nチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタの両方の半導体層にLDD領域を形成してもよい。

【0156】

次に、スパッタリング法、LPCVD法、またはプラズマCVD法等を用いて、水素を含む第4絶縁層522を成膜した後、半導体層に添加された不純物元素の活性化処理および水素化処理を行う。不純物元素の活性化処理および水素化処理は、炉での熱処理(300〜550℃で1〜12時間の熱処理)または、ランプ光源を用いたラピッドサーマルアニール法(RTA法)を用いる。水素を含む第4絶縁層522は、PCVD法により得られる窒化酸化珪素層を用いる。ここでは、水素を含む第4絶縁層522の膜厚は、50nm〜200nmとする。加えて、結晶化を助長する金属元素、代表的にはニッケルを用いて半導体層を結晶化させている場合、活性化と同時にチャネル形成領域におけるニッケルの濃度の低減を行うゲッタリングをも行うことができる。なお、水素を含む第4絶縁層522は、層間絶縁層の1層目である。

【0157】

次に、スパッタリング法、LPCVD法、またはプラズマCVD法等を用いて層間絶縁層の2層目となる第5絶縁層523及び3層目となる第6絶縁層524を形成する。第5絶縁層523及び第6絶縁層524としては、酸化珪素層、窒化珪素層または酸化窒化珪素層などの絶縁層の単層または積層を用いる。ここでは第5絶縁層523の膜厚は50〜200nm、第6絶縁層524の膜厚は300nm〜800nmとする。

【0158】

ここまでの工程を経た半導体装置の断面図が図9(A)に相当する。

【0159】

次に、第9のフォトマスクを用いてレジストマスクを形成し、選択的に第4絶縁層522、第5絶縁層523、及び第6絶縁層524をエッチングして、半導体層に達するコンタクトホール、ゲート電極に達するコンタクトホールをそれぞれ形成する。そして、エッチング後にレジストマスクを除去する。

【0160】

次に、フッ酸を含むエッチャントで露呈している半導体層表面の酸化層を除去すると同時に露呈している半導体層の表面を洗浄する。

【0161】

次に、スパッタリング法を用いて導電層を形成する。この導電層は、Ti、W、Ni、Cr、Mo、Ta、Co、Zr、V、Pd、Hf、Pt、Fe、Al、Cuから選ばれた元素、または前記元素を主成分とする合金若しくは化合物の単層、またはこれらの積層で形成する。

【0162】

次に、第10のフォトマスクを用いてレジストマスクを形成し、選択的に導電層をエッチングして、ソース電極またはドレイン電極525〜532、ゲート引出配線535〜538、容量素子の容量配線533、534、539、記憶素子の第2の電極の引出配線541、導電層542を形成する。なお、ここでは図示しないが、導電層542は、アンテナ及び電源回路部の薄膜トランジスタと電気的に接続している。導電層のエッチング後にレジストマスクを除去する。

【0163】

ここまでの工程を経た半導体装置の断面図が図9(B)に相当する。本実施例では10枚のフォトマスクを用いて、同一基板上にロジック回路部の薄膜トランジスタと、メモリ部の薄膜トランジスタと、アンテナ及び電源回路部の薄膜トランジスタ及び容量素子とを形成することができる。

【0164】

次に、ロジック回路部601の薄膜トランジスタと、メモリ部602の薄膜トランジスタと、アンテナ及び電源部603の薄膜トランジスタ及び容量素子を覆う第7絶縁層540を形成する。第7絶縁層540は、酸化珪素を含む絶縁層または有機樹脂層を用いる。無線チップの信頼性を向上させる上では酸化珪素を含む絶縁層を用いることが好ましい。また、後に形成するアンテナをスクリーン印刷法で形成する場合には平坦面を有していることが望ましいため、塗布法を用いる有機樹脂層を用いることが好ましい。第7絶縁層540を用いるかどうかは、実施者が適宜、選択すればよい。また、本実施例では後に形成するアンテナが駆動回路及びメモリ部と重なる例を示しているため、第7絶縁層540は、アンテナとの絶縁を図る層間絶縁層として機能している。輪状(例えば、ループアンテナ)又はらせん状のアンテナとする場合には、アンテナの両端のうち一方を下層の配線で引き回すため、第7絶縁層540を設けることが好ましい。ただし、マイクロ波方式を適用し、線状(例えば、ダイポールアンテナ)、平坦な形状(例えば、パッチアンテナ)等のアンテナとする場合には、後に形成するアンテナが駆動回路及びメモリ部と重ならないように配置できるため、第7絶縁層540は特に設けなくともよい。

【0165】

次に、第11のフォトマスクを用いてレジストマスクを形成し、選択的に第7絶縁層540をエッチングして、引出配線541に達する開口と、導電層542に達する開口を形成する。そして、エッチング後にレジストマスクを除去する。

【0166】

次に、第7絶縁層540上に金属層を形成する。金属層としては、Ti、Ni、Auから選ばれる単層またはそれらの積層を用いる。次に、第12のフォトマスクを用いてレジストマスクを形成し、選択的に金属層をエッチングして、記憶素子の第1の電極層543、引出配線541に接続する導電層544、及びアンテナの下地膜545を形成する。なお、ここでの第1の電極層543、導電層544、及び下地膜545は、レジストマスクを用いることなく、メタルマスクを用いたスパッタリング法で選択的に形成することもできる。アンテナの下地膜545を設けることで、アンテナとの接触面積を広く確保することができる。また、回路設計のレイアウトによっては、特に導電層544及び引出配線541を形成しなくともよい。

【0167】

ここまでの工程を経た半導体装置の断面図が図9(C)に相当する。

【0168】

次に、第1の電極層543、導電層544、アンテナの下地膜545、及び第7絶縁層540を覆うように、第8絶縁層548を形成する。第8絶縁層としては、第7絶縁層540と同様の材料を用いて形成することができる。ここでは、0.8〜1.5μmの感光性ポリイミドを塗布し第13のフォトマスクを用いて感光性ポリイミドを露光及び現像した後、200〜350℃で加熱して、第8絶縁層548を形成する。

【0169】

次に、下地膜545上にアンテナ546を形成する。アンテナ546はスパッタリング法を用いてAlまたはAgなど金属層を形成した後、フォトマスクを用いてレジストマスクを形成し、当該レジストマスクを用いてエッチングする方法、或いはスクリーン印刷法を用いることができる。フォトマスク数を削減することを優先するのであれば、スクリーン印刷法を用いてアンテナを形成すればよい。ここでは、銀ペーストを用いて印刷したのち、200〜350℃で焼成して、厚さ5〜20μmのアンテナ546を形成する。

【0170】

次に、第1の電極層543及び第8絶縁層548の一部に有機化合物を含む層549を形成する。有機化合物を含む層549は、蒸着法、塗布法、液滴吐出法、印刷法等を適宜用いることができる。ここでは、厚さ1〜4nmのフッ化カルシウム層を蒸着法により蒸着した後、厚さ5〜20nmのCzPAを蒸着して有機化合物を含む層549を形成する。なお、図10(A)に示すように、アンテナ546を形成した後、または有機化合物を含む層549を形成した後、下地膜545にアンテナ546が重畳している領域にレーザビーム547を照射してもよい。このプロセスにより、アンテナ546及び下地膜545の密着性が向上し、アンテナ546及び下地膜545の接触抵抗を下げることができる。

【0171】

ここまでの工程を経た半導体装置の断面図が図10(A)に相当する。

【0172】

次に、有機化合物を含む層549、導電層544、及び第8絶縁層548の一部に記憶素子の第2の電極550を形成する。第2の電極550は導電層544にも接続する。第2の電極550は、蒸着法、スパッタリング法、塗布法、液滴吐出法、印刷法等を適宜用いることができる。ここでは、厚さ50〜200nmのスズ及び銀の合金層を蒸着法により蒸着して第2の電極550を形成する。

【0173】

ここまでの工程を経た半導体装置の断面図が図10(B)に相当する。本実施例では、同一基板上にロジック回路部601の薄膜トランジスタと、メモリ部602の薄膜トランジスタ及び記憶素子600と、アンテナ、及び電源回路部603の薄膜トランジスタとを形成することができる。

【0174】

また、本実施例では、フォトマスクを用いてレジストマスクを形成した例を示したが、特に当該技術に限定されず、フォトマスクを用いることなくレジスト材料を液滴吐出法で選択的に形成してレジストマスクを形成してもよい。

【0175】

次に、第8絶縁層548、第2の電極550、アンテナ546を覆うように吸湿材555を含む第9絶縁層551を形成する。第9絶縁層551としては、外部からの水分等が素子層へ侵入するのを妨げる機能を有する封止層で形成する。ここでは、吸湿材555として平均粒径が40μmの酸化カルシウム微粒子を用い、第9絶縁層551としては酸化カルシウムを含むエポキシ樹脂を印刷法により印刷し、160度30分で焼成して厚さ10〜30μmのエポキシ樹脂層を形成する。なお、第1絶縁層から第2の電極までの積層体を素子層554と示す。また、第9絶縁層551は素子層554を封止する封止層として機能する。

【0176】

次に、後の剥離工程を容易に行うために、レーザ光213を照射して、溝を形成する(図示しない。)

【0177】

次に、第9絶縁層551上に支持部材552を設ける。ここでは、支持部材552として粘着層553を有するフィルムを第9絶縁層551に貼り付ける。

【0178】

ここまでの工程を経た半導体装置の断面図が図11(A)に相当し、半導体装置の斜視図が図14(A)に相当する。また、図14(A)のA−Bの断面図が図14(B)に相当する。

【0179】

次に、基板501から素子層及び封止層を剥離する。具体的には、剥離層502において、基板501と、素子層554及び絶縁層551を物理的手段により剥離する。物理的手段とは、力学的手段または機械的手段を指し、何らかの力学的エネルギー(機械的エネルギー)を半導体装置に与える手段を指している。物理的手段は、代表的には機械的な力を加えること(例えば人間の手や把持具による剥離や、ローラを回転させる分離処理)である。ここでは、粘着性を有するローラ561を支持部材552表面に貼り付け、ローラ561を回転させることで、基板501から、素子層554及び絶縁層551、具体的には金属酸化物層内、第1絶縁層503と剥離層502の界面、又は剥離層502内で剥離が生じ、比較的小さな力で素子層554及び絶縁層551を基板501から引き剥がすことができる。

【0180】

ここまでの工程を経た半導体装置の断面図が図11(B)に相当し、半導体装置の斜視図が図14(C)に相当する。また、図14(C)のA−Bの断面図が図14(D)に相当する。

【0181】

次に、剥離層からはがれた素子層554及び絶縁層551に第1の可撓性基板を接着させる。ここでは、接着剤563を用いて素子層554及び絶縁層551表面に第1の可撓性基板562を貼り付ける。

【0182】

第1の可撓性基板562としては、実施の形態1で示す可撓性基板120を適宜用いることができる。また、紙、プリプレグ、セラミックシートなどを用いることができる。接着剤563としては、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

【0183】

ここまでの工程を経た半導体装置の断面図が図12(A)に相当し、半導体装置の斜視図が図14(E)に相当する。また、図14(E)のA−Bの断面図が図14(F)に相当する。

【0184】

次に、図14(G)及び(H)に示すように、第1の可撓性基板562が上側、支持部材552が下側になるようにひっくり返し、第1の可撓性基板562、素子層554、及び絶縁層551を切断手段564により切断し、個々の薄膜集積回路に分断する。切断手段564としては、レーザカット法、ダイシング法、スクライビング法等を適宜用いることができる。ここでは、支持部材552を分断せず、第1の可撓性基板562、絶縁層551、及び素子層554を分断するようにカッターを用いて切断する。

【0185】

この結果、図15(A)及び(B)に示すように、素子層及び封止樹脂に溝571が形成される。分断された素子層を薄膜集積回路572と示し、分断された封止樹脂を樹脂層575と示し、薄膜集積回路572、樹脂層575、及び分断された第1の可撓性基板573を積層体586と示す。

【0186】

ここまでの工程を経た積層体586の断面図が図12(B)に相当する。

【0187】

次に、図15(C)に示すように、支持部材552上に設けられる積層体586をピックアップ装置でピックアップし、第2の可撓性基板583上に貼り付ける。なお、第2の可撓性基板583は供給ロール581から繰り出される。また、積層体586が貼り付けられた第2の可撓性基板583は回収ロール582に回収される。また、第2の可撓性基板583の表面には接着層584(図12(B))があり、図15(C)のC−Dの断面図である図15(D)に示すように、当該接着層により第2の可撓性基板583に積層体586を貼り付けることができる。

【0188】

第2の可撓性基板583としては、プラスチック、紙、プリプレグ、セラミックシートなどを用いることができる。接着層としては、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

【0189】

また、紙の形成途中に積層体を配置して、1枚の紙の内部に積層体を設けることもできる。

【0190】

次に、15(E)に示すように、第2の可撓性基板583で積層体586が設けられる面に第3の可撓性基板593を貼り付ける。具体的には、積層体586が設けられる第2の可撓性基板583が供給用ロール591から繰り出される。また、第3の可撓性基板593が供給用ロール592から繰り出させる。第2の可撓性基板及び第3の可撓性基板は一対のローラ595、596により互いに接着される。なお、一対のローラ595、596の圧力や回転スピードは適宜コントロールされる。これにより、第2の可撓性基板583及び第3の可撓性基板593で積層体586を封止すると共に第2の可撓性基板583及び第3の可撓性基板593を接着することができる。

【0191】

ここまでの工程を経た半導体装置の断面図が図13に相当する。また、図15(E)のC−Dの断面図を図15(F)示す。

【0192】

この後、第2の可撓性基板583及び第3の可撓性基板593が接する領域で切断手段を用いて切断することで、無線で情報を送受信することが可能で、記憶機能の信頼性が高い、フレキシブルな半導体装置を作製することができる。

【実施例2】

【0193】

本発明の非接触でデータの送受信が可能な半導体装置は、例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。これらの例に関して図16及び図17を用いて説明する。

【0194】

図16(A)は、本発明に係る半導体装置9010を内蔵したラベルの完成品の状態の一例である。ラベル台紙(セパレート紙)9118上に、半導体装置9010を内蔵したラベル9020が形成されている。ラベル9020は、ボックス9119内に収納されている。また、ラベル上には、その商品や役務に関する情報(商品名、ブランド、商標、商標権者、販売者、製造者等)が記されており、一方、半導体装置9010には、その商品(または商品の種類)固有のIDナンバーが付されており、偽造や、商標権、特許権等の知的財産権侵害、不正競争等の不法行為を容易に把握することができる。また、半導体装置9010内には、商品の容器やラベルに明記しきれない多大な情報、例えば、商品の産地、販売地、品質、原材料、効能、用途、数量、形状、価格、生産方法、使用方法、生産時期、使用時期、賞味期限、取扱説明、商品に関する知的財産情報等を入力しておくことができ、取引者や消費者は、簡易なリーダによって、それらの情報にアクセスすることができる。また、生産者側からは容易に書換え、消去等も可能であるが、取引者、消費者側からは書換え、消去等ができない仕組みになっている。

【0195】

図16(B)は、半導体装置を内蔵したタグ9120を示している。半導体装置を内蔵したタグを商品に備え付けることにより、商品管理が容易になる。例えば、商品が盗難された場合に、商品の経路を辿ることによって、その犯人を迅速に把握することができる。このように、半導体装置を内蔵したタグを備えることにより、所謂トレーサビリティ(traceablity;複雑化した製造、流通の各段階で問題が生じた場合に、経路を遡ることによって、その原因を迅速に把握できる態勢を整えること。)に優れた商品を流通させることができる。

【0196】

図16(C)は、本発明に係る半導体装置を内蔵したIDカード9141の完成品の状態の一例である。上記IDカードとしては、キャッシュカード、クレジットカード、プリペイドカード、電子乗車券、電子マネー、テレフォンカード、会員カード等のあらゆるカード類が含まれる。

【0197】

図16(D)は、本発明に係る半導体装置9010を内蔵した無記名債券9122の完成品の状態の一例である。上記無記名債券類には、切手、切符、チケット、入場券、商品券、図書券、文具券、ビール券、おこめ券、各種ギフト券、各種サービス券等が含まれるが、勿論これらに限定されるものではない。また、無記名債権に限らず小切手、証券、約束手形等の有価証券類、運転免許証、住民票等の証書類等に設けることもできる。

【0198】

図16(E)は、半導体装置9110を内蔵した商品を包装するための包装用フィルム類9127を示している。包装用フィルム類9127は、例えば、下層フィルム上に、半導体装置9010を任意にばらまき、上層フィルムで覆うことによって作製することができる。包装用フィルム類9127は、ボックス9129に収納されており、所望の量だけカッター9128で切り離して利用することができる。なお、包装用フィルム類9127としての素材は特に制限されない。例えば、薄膜樹脂、アルミ箔、紙等を用いることができる。

【0199】

図17(A)、(B)は、本発明に係る半導体装置9010を内蔵したラベル9020を貼付した書籍9123、ペットボトル9124を示している。なお、もちろんこれらに限定されず、お弁当等の包装紙等の包装用容器類、DVDソフト、ビデオテープ等の記録媒体、自転車等の車両、船舶等の乗物類、鞄、眼鏡等の身の回り品、食料品、飲料等の食品類、衣服、履物等の衣類、医療器具、健康器具等の保健用品類、家具、照明器具等の生活用品類、医薬品、農薬等の薬品類、液晶表示装置、EL表示装置、テレビジョン装置(テレビ受像機、薄型テレビ受像機)、携帯電話等の電子機器等様々な物品に設けることができる。本発明に用いられる半導体装置は非常に薄いため、上記書籍等の物品にラベルを搭載しても、機能、デザイン性を損ねることがない。更に、本発明の半導体装置の場合、アンテナ及びチップを一体形成でき、曲面を有する商品に直接半導体装置を転写することが容易になる。

【0200】

図17(C)は、果物類9131の生鮮食品に、直接ラベル9020を貼り付けた状態を示している。また、なお、ラベルを商品に貼り付けた場合、剥がされる可能性があるが、包装用フィルム類によって商品をくるむと、包装用フィルム類を剥がすのは困難であるため、防犯対策上多少のメリットがある。

【0201】

紙幣、硬貨、有価証券類、証書類、無記名債券類等に本発明の半導体装置を設けることにより、偽造を防止することができる。また、包装用容器類、書籍類、記録媒体等、身の回り品、食品類、衣類、生活用品類、電子機器等に本発明の半導体装置を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。乗物類、保健用品類、薬品類等に本発明の半導体装置を設けることにより、偽造や盗難の防止、薬品類ならば、薬の服用の間違いを防止することができる。

【0202】

以上のように、本発明の半導体装置は物品あればどのようなものにでも設けて使用することができる。本発明の半導体装置は、より薄く湾曲しやすいため、物品に貼り付けた際に違和感なく用いることができる。なお、本実施の形態は、他の実施の形態、実施例と自由に組み合わせて行うことができる。

【実施例3】

【0203】

本実施例では、実施例1を用いて作製した半導体装置の剥離工程について、図9〜図13を用いて以下に説明する。はじめに半導体装置の作製工程について以下に示す。

【0204】

基板501上に絶縁膜(図示しない。)を形成し、絶縁膜上に剥離層502を形成する。ここでは、基板501としては一辺が126.6mmの正方形のガラス基板(EAGLE−2000(コーニング社製)を用いた。絶縁膜としては、シランガス、一酸化二窒素を用いたプラズマCVD法により、厚さ100nmの酸化窒化珪素膜を形成した。剥離層502としては、タングステンターゲットをアルゴンガスでスパッタリングして厚さ30nmのタングステン層を形成した。

【0205】

次に、剥離層上に第1絶縁層503を形成する。第1絶縁層503としては、シリコンターゲットを酸素及びアルゴンでスパッタリングして、厚さ200nmの酸化珪素層を形成し、SiH4、NH3、及びN2Oを用いたプラズマCVD法により厚さ50nmの窒化酸化珪素層を形成し、SiH4、及びN2Oを用いたプラズマCVD法により厚さ100nmの酸化窒化珪素層を形成した。なお、スパッタリング法で厚さ200nmの酸化珪素層を形成する際に、タングステン層表面が酸素プラズマ処理され、タングステン層の表面に数nmの酸化タングステン層が形成される。

【0206】

次に、第1絶縁層503上に半導体層を形成する。ここでは、半導体層として、シランガスを用いたプラズマCVD法により非晶質珪素層を形成した後、500℃1時間及び550℃4時間の加熱により非晶質珪素層に含まれる水素を除去した。次に、フッ酸で非晶質珪素層表面の酸化膜を除去した後、Nd:YVO4レーザの第2高調波(532nm)の連続発振のレーザビームを非晶質珪素層に照射して結晶性珪素層を形成した。

【0207】

次に、薄膜トランジスタのしきい値を制御するために、結晶性珪素層に微量な不純物元素(ボロンまたはリン)のドーピングを行う。ここでは、2.5%のジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法を用い、1×1017/cm3〜7×1017/cm3のボロンを結晶性珪素層にドーピングした。

【0208】

次に、結晶性珪素層上にレジストを塗布した後、フォトマスクを用いて露光した後現像を行って、レジストマスクを形成し、結晶性珪素層を選択的にエッチングして、分離された結晶性珪素層を形成する。ここでは、結晶性珪素層の表面の酸化膜を除去し、フッ酸及び過酸化水素の溶液を用いて結晶性珪素層表面に酸化膜を形成した後、レジストを塗布し、フォトマスクを用いてレジストを露光した後現像して、レジストマスクを形成した。次に、レジストマスクを用いて結晶性珪素層をSF6及びO2を用いてドライエッチングして、分離された結晶性珪素層を形成した。この後、レジストマスクを除去した。

【0209】

次に、分離された結晶性珪素層上にゲート絶縁膜として機能する第2絶縁層を形成する。ここでは、第2絶縁層として、SiH4、及びN2Oを用いたプラズマCVD法により厚さ20nmの酸化窒化珪素層を形成した。

【0210】

次に、フォトマスクを用いてレジストマスクを形成し、容量素子の容量電極となる結晶性珪素層に不純物元素(ボロンまたはリン)を導入することにより低濃度不純物領域511を形成する。ここでは、結晶性珪素層にリン(P)が1×1015〜1×1019/cm3の濃度で含まれるように、5%のフォスフィンをイオンドープすることにより、n型を示す低濃度不純物領域511を形成した。この後、レジストマスクを除去した。

【0211】

次に、第2絶縁層上にゲート電極504〜507、容量電極508を形成する。ここでは、窒化タンタルをターゲットとしスパッタリングガスにアルゴンを用いてスパッタリングを行い、厚さ30nmの窒化タンタル層を形成した後、タングステンをターゲットとしアルゴンを用いてスパッタリングを行い、厚さ370nmのタングステン層を形成した。次に、タングステン層の表面にレジストを塗布したのち、フォトマスクを用いて露光した後現像を行って、レジストマスクを形成した。次に、当該レジストマスクを用いてタングステン層及び窒化タンタル層を、Cl2、SF6、及びO2を用いてドライエッチングしてゲート電極504〜507、容量電極508を形成した。この後、レジストマスクを除去した。

【0212】

次に、pチャネル型薄膜トランジスタとする領域の半導体層を覆うようにフォトマスクを用いてレジストマスクを形成し、nチャネル型薄膜トランジスタとする領域の半導体層にゲート電極505〜507をマスクとして不純物元素を導入することにより低濃度不純物領域を形成する。ここでは、nチャネル型薄膜トランジスタとする領域の半導体層にリン(P)を1×1015〜1×1019/cm3の濃度で含まれるように5%のフォスフィンをイオンドープすることによりn型を示す不純物領域を形成する。この後、レジストマスクを除去した。

【0213】

次に、nチャネル型薄膜トランジスタとする半導体層を覆うようにフォトマスクを用いてレジストマスクを形成し、pチャネル型薄膜トランジスタとする領域の半導体層にゲート電極504をマスクとして不純物元素を導入することによりp型を示す不純物領域514、515を形成する。ここでは、pチャネル型薄膜トランジスタとする領域の半導体層にボロン(B)を1×1019〜1×1020/cm3の濃度で含まれるように15%のジボランをイオンドープすることによって、p型を示す不純物領域514、515を形成することができる。また、チャネル形成領域516が形成される。

【0214】

次に、ゲート電極504〜507及び容量電極508の両側面にサイドウォール510を形成する。ここでは、SiH4、及びN2Oを用いたプラズマCVD法により厚さ100nmの酸化窒化珪素層を形成した後、LPCVD法により厚さ200nmの酸化珪素層を形成した。次に、酸化珪素層上にレジストを塗布した後、基板の裏面に形成された酸化珪素層をウエットエッチングした。次に、酸化珪素層上のレジストを除去した後、酸化珪素層及び酸化窒化珪素層をCHF3及びO2を用いてドライエッチングしてサイドウォール510を形成する。なお、サイドウォール510の形成と同時に、第2絶縁層の一部をエッチングして除去する。第2絶縁層の一部が除去されることによって、残存するゲート絶縁層512は、ゲート電極504〜507、容量電極508、及びサイドウォール510の下方に形成される。

【0215】

次に、pチャネル型薄膜トランジスタとする半導体層を覆うようにフォトマスクを用いてレジストマスクを形成し、nチャネル型薄膜トランジスタとする領域の半導体層にゲート電極504〜507、容量電極508、及びサイドウォール510をマスクとして不純物元素を導入することにより高濃度不純物領域を形成する。ここでは、nチャネル型薄膜トランジスタとする領域の結晶性珪素層にリンを1×1019〜1×1020/cm3の濃度で含まれるように5%のフォスフィンをイオンドープすることによって、n型を示す高濃度不純物領域を形成することができる。具体的には、nチャネル型薄膜トランジスタとする領域の半導体層に、ソース領域又はドレイン領域513、517、518、LDD領域519、520、チャネル形成領域521が形成される。サイドウォール510の下方にLDD領域519、520が形成される。また、容量素子の容量電極となる半導体層に低濃度不純物領域511及び高濃度不純物領域513が形成される。

【0216】

次に、水素を含む第4絶縁層522を成膜した後、半導体層に添加された不純物元素の活性化処理を行う。ここでは、SiH4、及びN2Oを用いたプラズマCVD法により厚さ50nmの酸化窒化珪素層を形成した後、窒素雰囲気で550℃で4時間加熱して不純物元素の活性化処理をした。

【0217】

次に、層間絶縁層の2層目となる第5絶縁層523及び3層目となる第6絶縁層524を形成する。ここでは、第5絶縁層523として、SiH4、NH3、及びN2Oを用いたプラズマCVD法により厚さ100nmの窒化酸化珪素層を形成した後、第6絶縁層524として、SiH4、及びN2Oを用いたプラズマCVD法により厚さ600nmの酸化窒化珪素層を形成した。

【0218】

次に、結晶性珪素層の水素化処理を行う。ここでは、窒素雰囲気で410℃1時間の加熱を行った。

【0219】

ここまでの工程を経た半導体装置の断面図が図9(A)に相当する。

【0220】

次に、第6絶縁層524上にレジストを塗布した後、フォトマスクを用いてレジストを露光し現像してレジストマスクを形成し、選択的に第4絶縁層522、第5絶縁層523、及び第6絶縁層524をエッチングして、半導体層に達するコンタクトホール、ゲート電極に達するコンタクトホールをそれぞれ形成する。ここでは、CHF3及びH2を用いたドライエッチングにより第4絶縁層522、第5絶縁層523、及び第6絶縁層524をエッチングした。次に、エッチング後にレジストマスクを除去した。

【0221】

次に、フッ酸を含むエッチャントで露呈している半導体層表面の酸化層を除去すると同時に露呈している半導体層の表面を洗浄する。

【0222】

次に、スパッタリング法を用いて導電層を形成する。ここでは、ターゲットにチタンを用いたスパッタリング法により厚さ60nmのチタン層を形成し、ターゲットに窒化チタンを用いたスパッタリング法により厚さ40nmの窒化チタン層を形成し、ターゲットにアルミニウムを用いたスパッタリング法により厚さ500nmのアルミニウム層を形成し、ターゲットにチタンを用いて厚さ100nmのチタン層を形成した。

【0223】

次に、レジストを塗布した後、フォトマスクを用いてレジストを露光した後現像してレジストマスクを形成し、選択的に導電層をエッチングして、ソース電極またはドレイン電極525〜532、ゲート引出配線535〜538、容量素子の容量配線533、534、539、記憶素子の第2の電極の引出配線541、導電層542を形成する。この後にレジストマスクを除去する。

【0224】

ここまでの工程を経た半導体装置の断面図が図9(B)に相当する。同一基板上にロジック回路部601の薄膜トランジスタと、メモリ部602の薄膜トランジスタと、アンテナ及び電源部603の薄膜トランジスタ及び容量素子とを形成することができる。

【0225】

次に、第6絶縁層524、ソース電極またはドレイン電極525〜532、ゲート引出配線535〜538、容量素子の容量配線533、534、539、記憶素子の第2の電極の引出配線541、及び導電層542を覆う第7絶縁層540を形成する。ここでは、第7絶縁層540として、感光性ポリイミドを塗布した後、フォトマスクを用いて感光性ポリイミドを露光した後現像した後、300℃で1時間加熱して感光性ポリイミドを焼成して、引出配線541に達する開口と、導電層542に達する開口を有する厚さ1500nmの第7絶縁層540を形成した。

【0226】

次に、第7絶縁層540上に記憶素子の第1の電極層543、引出配線541に接続する導電層544、及びアンテナの下地膜545を形成する。ここでは、チタンをターゲットとして厚さ100nmのチタン層を形成した後、チタン層上にレジストを塗布し、レジストをフォトマスクで露光した後現像してレジストマスクを形成する。次に、レジストマスクを用いてチタン層を、BCl3及びCl2を用いてドライエッチングして、記憶素子の第1の電極層543、引出配線541に接続する導電層544、及びアンテナの下地膜545を形成した。この後、レジストマスクを除去した。

【0227】

ここまでの工程を経た半導体装置の断面図が図9(C)に相当する。

【0228】

次に、第1の電極層543、導電層544、アンテナの下地膜545、及び第7絶縁層540を覆うように、第8絶縁層548を形成する。ここでは、第8絶縁層としては、感光性ポリイミドを塗布しフォトマスクを用いて感光性ポリイミドを露光及び現像した後、250℃で1時間加熱して、厚さ800nmの第8絶縁層548を形成した。

【0229】

次に、下地膜545上にアンテナ546を形成する。ここでは、アルミニウムをターゲットとしたスパッタリング法により厚さ5μmのアルミニウム層を成膜する。次に、アルミニウム層上にレジストを塗布し、フォトマスクを用いてレジストを露光した後現像し、150℃で30分加熱してレジストを焼成し、酸素アッシングによりレジスト残渣を除去する。次に、アルミニウム層を酢酸、硝酸、リン酸、及び水を混合したエッチャントを用いてエッチングしてアンテナ546を形成した。

【0230】

次に、第1の電極層543及び第8絶縁層548の一部に有機化合物を含む層549を形成する。ここでは、厚さ1nmのフッ化カルシウム層を蒸着し、厚さ10nmのCzPA層を蒸着し、厚さ1nmのフッ化カルシウム層を蒸着して有機化合物を含む層549を形成した。

【0231】

ここまでの工程を経た半導体装置の断面図が図10(A)に相当する。

【0232】

次に、有機化合物を含む層549、導電層544、及び第8絶縁層548の一部に記憶素子の第2の電極550を形成する。第2の電極550は導電層544にも接続する。ここでは、厚さ200nmのスズ及び銀の合金で第2の電極500を形成した。

【0233】

ここまでの工程を経た半導体装置の断面図が図10(B)に相当する。本実施例では、同一基板上にロジック回路部601の薄膜トランジスタと、メモリ部602の薄膜トランジスタ及び記憶素子600と、アンテナ、及び電源部603の薄膜トランジスタとを形成することができる。

【0234】

次に、第8絶縁層548、第2の電極550、アンテナ546を覆うように吸湿材555を含む第9絶縁層551を形成する。第9絶縁層551としては、外部からの水分等が素子層554へ侵入するのを妨げる機能を有する封止層で形成する。ここでは、吸湿材555として平均粒径が40μmの酸化カルシウム微粒子を含むエポキシ樹脂(Hicap2000(日本化成工業製))を印刷法により印刷し、160℃30分で焼成して、第9絶縁層551として厚さ10〜30μmの第9の絶縁層を形成した。なお、第1絶縁層から第2の電極までの積層体を素子層554と示す。また、第9絶縁層551は素子層554を封止する封止層として機能する。

【0235】

次に、後の剥離工程を容易に行うために、レーザ光を剥離層に照射して、溝を形成した。

【0236】

次に、第9絶縁層551上に支持部材552を設ける。ここでは、支持部材552として熱剥離フィルムを第9絶縁層551に貼り付けた。

【0237】

ここまでの工程を経た半導体装置の断面図が図11(A)に相当する。

【0238】

次に、基板501から素子層及び封止層を剥離する。具体的には、剥離層502において、基板501と、素子層554及び絶縁層551を物理的手段により剥離する。ここでは、粘着性を有するローラ561を支持部材552表面に設け、ローラ561を回転させることで、素子層554及び絶縁層551を基板501から引き剥がすことができた。

【0239】

ここまでの工程を経た半導体装置の断面図が図11(B)に相当する。

【0240】

次に、剥離層から剥れた素子層554及び絶縁層551に第1の可撓性基板562を接着させる。ここでは、素子層554及び絶縁層551表面に第1の可撓性基板として熱可塑性接着層を含むラミネートフィルムを設け、135℃に加熱されたローラを押しつけて、ラミネートフィルムを素子層554及び絶縁層551の表面に固着した。

【0241】

ここまでの工程を経た半導体装置の断面図が図12(A)に相当する。この後、支持部材552に熱を加えて、支持部材552を第9絶縁層551から剥した。

【0242】

次に、絶縁層551に第2の可撓性基板583を接着させる。ここでは、絶縁層551表面に第2の可撓性基板として熱可塑性接着層を含むラミネートフィルムを設け、135℃に加熱されたローラを押しつけて、ラミネートフィルムを絶縁層551の表面に固着した。

【0243】

この後、第1の可撓性基板、素子層、及び第2の可撓性基板583が重畳する部分に選択的にUVレーザ光を照射して分断することで、半導体装置を作製することができた。

【0244】

このときの剥離歩留まりについて以下に示す。ここでは、一枚の基板上に50個の半導体装置が配置されている。基板一枚あたり74〜78%の半導体装置が、正常に剥離された。素子層の保護層として、吸湿材を含有する封止層を用いて、正常に剥離が行われたことがわかる。

【図面の簡単な説明】

【0245】

【図1】本発明の記憶装置を示した断面図である。

【図2】本発明の記憶装置を示した断面図である。

【図3】本発明に適用可能な記憶素子の構造を示した断面図である。

【図4】本発明の記憶装置の構成を示した図である。

【図5】本発明の記憶装置の構成を示した断面図である。

【図6】本発明の記憶装置の構成を示した図である。

【図7】本発明の半導体装置の構成を示した断面図である。

【図8】本発明の半導体装置の構成を示した図である。

【図9】本発明の半導体装置の作製工程を示した断面図である。

【図10】本発明の半導体装置の作製工程を示した断面図である。

【図11】本発明の半導体装置の作製工程を示した断面図である。

【図12】本発明の半導体装置の作製工程を示した断面図である。

【図13】本発明の半導体装置の作製工程を示した断面図である。

【図14】本発明の半導体装置の作製工程を示した斜視図及び断面図である。

【図15】本発明の半導体装置の作製工程を示した斜視図及び断面図である。

【図16】本発明の半導体装置の応用例を示した図である。

【図17】本発明の半導体装置の応用例を示した図である。

【技術分野】

【0001】

本発明は、有機化合物を含む層を有する記憶素子を備えた記憶装置及び半導体装置に関する。

【背景技術】

【0002】

近年、制御回路や記憶回路等に有機化合物を用いた有機薄膜トランジスタや記憶素子等の開発が盛んに行われている(例えば特許文献1)。

【0003】

また、絶縁表面上に複数の回路が集積され、様々な機能を有する半導体装置の開発が進められている。また、アンテナを設けることにより、無線によるデータの送受信が可能な半導体装置の開発が進められている。このような半導体装置は、無線チップ(IDタグ、ICタグ、ICチップ、RF(Radio Frequency)タグ、無線タグ、電子タグ、RFID(Radio Frequency Identification)タグともよばれる)とよばれ、既に一部の市場で導入されている。

【0004】

現在実用化されているこれらの半導体装置の多くは、Si等の半導体を用いた回路(IC(Integrated Circuit)チップとも呼ばれる)とアンテナとを有し、当該ICチップは記憶回路(メモリとも呼ぶ)や制御回路等から構成されている。

【特許文献1】特開2006−148080号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1で示すような有機化合物を含む層を有する記憶素子は、使用される環境によりダメージを受ける恐れがあり、その結果、記憶装置及び半導体装置の記憶機能、具体的には書込み特性、読み出し特性、記憶保持特性等の信頼性の低下を招く恐れがある。

【0006】

上記問題を鑑み、本発明は、有機化合物を含む層を有する素子が設けられた記憶装置及び半導体装置において、フレキシブルで記憶機能の信頼性の高い記憶装置及び半導体装置を提供する。

【課題を解決するための手段】

【0007】

第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子と、当該記憶素子を有する素子層と、素子層上に形成される封止層を有し、封止層には吸湿材が含まれていることを特徴とする記憶装置である。

【0008】

また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子と、当該記憶素子及び半導体素子を有する素子層と、素子層上に形成される封止層とを有し、封止層には吸湿材が含まれていることを特徴とする半導体装置である。

【0009】

吸湿材としては、溶融シリカ、結晶シリカ、アルミナ、窒化珪素、窒化アルミニウム、窒化ホウ素、ゼオライト、アルカリ土類金属の酸化物、金属の硫酸塩、または高吸水性ポリマーの粒子で形成される。吸湿材の粒径は、粒径1μm以上100μm以下、好ましくは5μm以上30μm以下、更に好ましくは5μm以上10μm以下である。

【0010】

封止層としては、フッ素含有ポリマー―、ポリオレフィン、ポリアクリロニトリル、ポリアミド、ポリエステル、エポキシ樹脂の高分子材料で形成される。

【0011】

また、半導体素子としては、MOSトランジスタ、薄膜トランジスタ、有機半導体トランジスタ等のトランジスタ、容量素子、抵抗素子等がある。また、素子層には、アンテナを含んでもよい。

【0012】

また、本発明の記憶装置及び半導体装置は情報を記憶する機能を有する。また、本発明の記憶装置及び半導体装置は、無線信号により命令やデータの送受信を行うと共に、当該無線信号で送受信した情報や、命令による処理結果を記憶する機能を有する。

【発明の効果】

【0013】

本発明の記憶装置及び半導体装置は、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子と、記憶素子を有する素子層と、素子層上に形成される封止層を有し、当該封止層には吸湿材が含まれている。封止層に吸湿材が含まれていることにより、記憶装置または半導体装置に曝される雰囲気中の水分が封止層に侵入しても、封止層に含まれる吸湿材で当該水分を吸収することができる。このため、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子が、水分に接触することを低減することが可能である。

【0014】

この結果、第1の電極、第2の電極、有機化合物を含む層等が水分や蒸気により劣化することを低減することが可能である。また、記憶素子の記憶保持特性の経年変化を抑制することが可能であり、記憶機能の信頼性の高い記憶装置及び半導体装置を作製することができる。また、素子層及び封止層を可撓性基板上に設けることにより、極めて薄く、フレキシブルで、且つ記憶保持能力の信頼性の高い記憶装置及び半導体装置を作製することができる。

【発明を実施するための最良の形態】

【0015】

本発明の実施の形態について図面を参照して説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

【0016】

(実施の形態1)

本実施の形態では、本発明の記憶装置の主要な構成について示す。代表的形態として、記憶素子が設けられたメモリセルを有する記憶装置を図1、2、及び4を用いて説明する。なお、各メモリ素子は、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有しており、メモリセルは記憶装置内でマトリクス状に配列されている。また、記憶素子の構造については、図3を用いて説明する。

【0017】

図4(A)に示すように、記憶装置127はメモリセルアレイ132及びメモリセルアレイを駆動する駆動回路を有する。メモリセルアレイ132には、メモリセル21がマトリクス状に設けられている。メモリセル21は、記憶素子107を有する(図1参照。)。記憶素子107は、基板101上に、第1の方向に延びた第1の電極層103と、第1の電極層103を覆う有機化合物を含む層105と、第1の方向と交差する第2の方向に延びた第2の電極層106とを有する。また、第2の電極層106を覆うように、保護膜として機能する絶縁層を設けてもよい。

【0018】

図4(A)に示すメモリセルアレイ132の断面構造について、図1及び2を用いて説明する。

【0019】

図1に示すように、基板101上に下地膜として機能する絶縁層102が形成される。絶縁層102上に第1の電極層103が形成され、第1の電極層103及び下地膜として機能する絶縁層102上に、絶縁層(または隔壁)104が形成される。なお、絶縁層(または隔壁)104は第1の電極層103を露出するように開口部が形成される。絶縁層(または隔壁)104及び第1の電極層上に有機化合物を含む層105が形成される。有機化合物を含む層105、絶縁層(または隔壁)104、及び下地膜として機能する絶縁層102上に第2の電極層106が形成される。

【0020】

第1の電極層103、有機化合物を含む層105、及び第2の電極層106により、記憶素子107を構成する。ここでは、下地膜として機能する絶縁層102から第2の電極層106までの積層物を素子層110という。

【0021】

また、素子層110上に吸湿材108を含む封止層111が形成される。

【0022】

封止層111は、塗布法を用いて組成物を塗布し、加熱または光照射による硬化により形成することが好ましい。封止層111は、後の剥離工程での保護層として設けるため、表面の凹凸の少ない絶縁層であることが好ましい。このような絶縁層は、塗布法により形成することができる。

【0023】

塗布法を用いて形成された封止層111は、フッ素含有ポリマー、ポリオレフィン、ポリアクリロニトリル、ポリアミド、ポリエステル、エポキシ樹脂、あるいはシロキサンポリマーを出発材料として形成された、シリカガラスに代表される無機シロキサンポリマー、又はアルキルシロキサンポリマー、アルキルシルセスキオキサンポリマー、水素化シルセスキオキサンポリマー、水素化アルキルシルセスキオキサンポリマーに代表される、珪素上の水素がメチル基やフェニル基のような有機基によって置換された有機シロキサンポリマーで形成される。

【0024】

フッ素含有ポリマーの代表例としては、ポリテトラフルオロエチレン、ポリクロロトリフルオロエチレン、ポリビニデンフルオライド、エチレン−テトラフルオロエチレン共重合体等がある。

【0025】

ポリオレフィンの代表例としては、ポリエチレン、ポリプロピレン、ポリブタジエン、ポリイソプレン、ポリスチレン等の重合体およびこれらの共重合体がある。

【0026】

エポキシ樹脂の代表例としては、クレゾールノボラック型エポキシ樹脂、ジシクロペンタジエン型エポキシ樹脂、トリフェニルメタン型エポキシ樹脂、ブロム含有エポキシ樹脂、ナフタレン環を有するエポキシ樹脂等がある。

【0027】

吸湿材108としては、粒径1μm以上100μm以下、好ましくは5μm以上30μm以下、更に好ましくは5μm以上10μm以下の吸湿性の高い粒子を用いることができる。吸湿性の高い粒子の代表例としては、溶融シリカ、結晶シリカ、アルミナ、窒化珪素、窒化アルミニウム、窒化ホウ素、ゼオライト、アルカリ土類金属の酸化物、金属の硫酸塩、高吸水性ポリマー等の粒子がある。

【0028】

アルカリ土類金属の酸化物の代表例としては、酸化カルシウム、酸化バリウム、酸化マグネシウム、酸化ストロンチウム等がある。

【0029】

金属の硫酸塩の代表例としては、硫酸リチウム、硫酸ナトリウム、硫酸カルシウム、硫酸マグネシウム、硫酸コバルト、硫酸ガリウム、硫酸チタン、硫酸ニッケル等がある。

【0030】

高吸水性ポリマーの代表例としては、ポリビニルアルコールやポリビニルピロリドン等のビニルポリマー、或いはポリエーテル、ポリエステル、ポリアミドなどの縮合系ポリマー等がある。なお、高吸水性ポリマーとは、水に溶けることなく、自重の1〜数100倍もの水を吸収し、且つ保持する能力を有するポリマーである。

【0031】

また、吸湿材108の形状は、球状、柱状、または多面体等である。また、水分を吸着する面積を増大させるため、表面が凹凸状であってもよい。また、吸湿材の表面に細孔が形成されていてもよい。

【0032】

また、封止層111における吸湿材108の割合は限定的ではないが、封止層111を形成する高分子材料、無機シロキサンポリマー、有機シロキサンポリマーに対して1〜20wt%、さらには5〜15wt%含まれることが好ましい。

【0033】

封止層111に吸湿材108が含まれることによって、封止層111が吸収した水分を吸湿材108で吸着、吸収することが可能である。このため、記憶装置の外気に含まれる水分が第1の電極層、第2の電極層、有機化合物を含む層等が形成されている素子層110に侵入することを抑制することが可能であり、これらの劣化を防ぐことができる。

【0034】

ここでは、封止層111は、吸湿材108として酸化カルシウム粒子が含まれたエポキシ樹脂を塗布法により塗布し、乾燥し焼成して形成する。

【0035】

基板101としては、ガラス基板、石英基板、金属基板やステンレス基板の一表面に絶縁層を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いる。上記に挙げた基板101には、大きさや形状に制約がないため、例えば、基板101として、1辺が1メートル以上であって、矩形状のものを用いれば、生産性を格段に向上させることができる。この利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。

【0036】

下地膜として機能する絶縁層102は、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、無機化合物を用いて単層又は多層で形成する。無機化合物の代表例としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素等がある。なお、下地膜として機能する絶縁層102に、窒化珪素、窒化酸化珪素、酸化窒化珪素等を用いることにより、後に形成される素子層へ水分や、酸素、二酸化炭素等の気体が外部から侵入することを防止することができる。

【0037】

さらには、下地膜として機能する絶縁層102を積層構造としても良い。例えば、無機化合物を用いて積層してもよく、代表的には、酸化珪素、窒化酸化珪素、及び酸化窒化珪素を積層して形成しても良い。

【0038】

第1の電極層103は、スパッタリング法やプラズマCVD法、塗布法、印刷法、電解メッキ法、無電解メッキ法等を用い、導電性の高い金属、合金、化合物等からなる単層または多層構造を用いて形成することができる。

【0039】

第1の電極層103としては、インジウム錫酸化物(以下、ITOと示す)、または酸化珪素を含有したインジウム錫酸化物、2〜20atomic%の酸化亜鉛(ZnO)を含む酸化インジウム等が挙げられる。また、チタン(Ti)、金(Au)、白金(Pt)、ニッケル(Ni)、タングステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、または金属材料の窒化物(例えば、窒化チタン、窒化タングステン、窒化モリブデン)等を用いることも可能である。

【0040】

また、第1の電極層103としては、リチウム(Li)やセシウム(Cs)等のアルカリ金属、およびマグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)等のアルカリ土類金属、アルミニウム(Al)およびこれらのいずれかを含む合金、ユーロピウム(Eu)、イッテルビウム(Yb)等の希土類金属およびこれらのいずれかを含む合金等が挙げられる。

【0041】

また、第1の電極層103として、スズ合金で形成することができる。スズ合金の代表例としては、スズ及び銀の合金、スズ及びビスマスの合金、スズ及びアンチモンの合金、スズ及び銅の合金、スズ及び金の合金、スズ及び亜鉛の合金、スズ及びインジウムの合金等がある。

【0042】

有機化合物を含む層105は、蒸着法、電子ビーム蒸着法、塗布法等を用いて形成することができる。

【0043】

ここでは、50〜200nmのチタン層をスパッタリング法により成膜した後、フォトリソグラフィ法により所望の形状にエッチングして第1の電極層103を形成する。次に、蒸着法によりNPBで形成される有機化合物を含む層を形成する。

【0044】

第2の電極層106は、蒸着法、スパッタリング法、CVD法、印刷法、塗布法等を用いて形成することができる。第2の電極層106は、第1の電極層103と同様の材料を適宜用いて形成することができる。また、第2の電極層106は、スズ合金で形成することができる。スズ合金の代表例としては、スズ及び銀の合金、スズ及びビスマスの合金、スズ及びアンチモンの合金、スズ及び銅の合金、スズ及び金の合金、スズ及び亜鉛の合金、スズ及びインジウムの合金等がある。さらには、銀、ビスマス、アンチモン、銅、金、亜鉛、及びインジウムから選ばれる複種類の元素及びスズとの合金を用いて第2の電極層106を形成してもよい。

【0045】

また、第2の電極層106を積層構造とすることもできる。代表的には、第1の層としてスズ合金層を形成した後、第2の層としてチタン(Ti)、金(Au)、白金(Pt)、ニッケル(Ni)、タングステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、アルミニウム(Al)、マグネシウム(Mg)、または金属材料の窒化物(例えば、窒化チタン、窒化タングステン、窒化モリブデン)等の金属層を形成してもよい。第2の層を形成することで、記憶素子にデータを書き込むときに高電流の通電が生じた場合、第1の層であるスズ合金層が剥れることを防止することができる。

【0046】

ここでは、蒸着法によりスズ及び銀を同時に蒸着して、スズ及び銀合金で第2の電極層106を形成する。

【0047】

ここで、記憶素子107のより具体的な構造について図3を用いて以下に示す。

【0048】

図3(A)に示すように、第1の電極層103及び第2の電極層106に印加された電圧により、結晶状態や導電性、形状が変化するような有機化合物を含む層105を形成することで、記憶素子107が形成される。第1の電極層103及び第2の電極層106に印加された電圧により、有機化合物を含む層105の結晶状態や導電性、形状が変化することで、記憶素子の電気抵抗が変化する。当該変化を用いて、0または1のデータを記録することができる。

【0049】

ここでは、有機化合物を含む層105は有機化合物層300で形成される。なお、有機化合物層300は、単層の有機化合物層または複数の有機化合物層で形成することができる。

【0050】

有機化合物を含む層105の厚さは、第1の電極層103及び第2の電極層106への電圧印加により記憶素子の電気抵抗が変化する厚さが好ましい。有機化合物を含む層105の代表的な膜厚は、1nmから100nm、好ましくは10nmから60nm、更に好ましくは5〜30nmである。

【0051】

有機化合物層300は、正孔輸送性を有する有機化合物又は電子輸送性を有する有機化合物を用いて形成することができる。

【0052】

正孔輸送性の有機化合物としては、例えば、フタロシアニン(略称:H2Pc)、銅フタロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VOPc)の他、4,4’,4’’−トリス(N,N−ジフェニルアミノ)トリフェニルアミン(略称:TDATA)、4,4’,4’’−トリス[N−(3−メチルフェニル)−N−フェニルアミノ]トリフェニルアミン(略称:MTDATA)、1,3,5−トリス[N,N−ジ(m−トリル)アミノ]ベンゼン(略称:m−MTDAB)、N,N’−ジフェニル−N,N’−ビス(3−メチルフェニル)−1,1’−ビフェニル−4,4’−ジアミン(略称:TPD)、4,4’−ビス[N−(1−ナフチル)−N−フェニルアミノ]ビフェニル(略称:NPB)、4,4’−ビス{N−[4−ジ(m−トリル)アミノ]フェニル−N−フェニルアミノ}ビフェニル(略称:DNTPD)、4,4’−ビス[N−(4−ビフェニリル)−N−フェニルアミノ]ビフェニル(略称:BBPB)、4,4’,4’’−トリ(N−カルバゾリル)トリフェニルアミン(略称:TCTA)などが挙げられるが、これらに限定されることはない。ここに述べた物質は、主に10−6cm2/Vs以上の正孔移動度を有する物質である。

【0053】

電子輸送性を有する有機化合物としては、トリス(8−キノリノラト)アルミニウム(略称:Alq3)、トリス(4−メチル−8−キノリノラト)アルミニウム(略称:Almq3)、ビス(10−ヒドロキシベンゾ[h]−キノリナト)ベリリウム(略称:BeBq2)、ビス(2−メチル−8−キノリノラト)−4−フェニルフェノラト−アルミニウム(略称:BAlq)等キノリン骨格またはベンゾキノリン骨格を有する金属錯体を用いることができる。また、この他、ビス[2−(2−ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称:Zn(BOX)2)、ビス[2−(2−ヒドロキシフェニル)ベンゾチアゾラト]亜鉛(略称:Zn(BTZ)2)などのオキサゾール、チアゾール配位子を有する金属錯体などの材料も用いることができる。さらに、金属錯体以外にも、2−(4−ビフェニリル)−5−(4−tert−ブチルフェニル)−1,3,4−オキサジアゾール(略称:PBD)、1,3−ビス[5−(p−tert−ブチルフェニル)−1,3,4−オキサジアゾール−2−イル]ベンゼン(略称:OXD−7)、3−(4−tert−ブチルフェニル)−4−フェニル−5−(4−ビフェニリル)−1,2,4−トリアゾール(略称:TAZ)、3−(4−tert−ブチルフェニル)−4−(4−エチルフェニル)−5−(4−ビフェニリル)−1,2,4−トリアゾール(略称:p−EtTAZ)、バソフェナントロリン(略称:BPhen)、バソキュプロイン(略称:BCP)等を用いることができる。ここに述べた物質は、主に10−6cm2/Vs以上の電子移動度を有する物質である。

【0054】

なお、上記範囲外の移動度を有する物質であっても良く、例えば2,3−ビス(4−ジフェニルアミノフェニル)キノキサリン(略称:TPAQn)、9−[4−(N−カルバゾリル)]フェニル−10−フェニルアントラセン(以下、CzPAと記す。)等を用いて形成してもよい。

【0055】

また、有機化合物層300は上記に示す有機化合物を複数混合して形成してもよい。また、上記に示す有機化合物を積層して形成してもよい。

【0056】

また、有機化合物層300は、正孔輸送性もしくは電子輸送性を有する有機化合物に絶縁物が混合されていても良い。なお、絶縁物は、均一に分散されている必要はない。絶縁物を混合することにより、有機化合物層300のモルフォロジーを向上することができる。よって、部分的な膜の結晶化を抑制することができるため、さらに記憶素子毎の挙動のばらつきを抑制することができる。

【0057】

また、図3(B)に示すように、有機化合物を含む層105として、有機化合物層300及びバッファ層301で形成してもよい。バッファ層301は、熱的及び化学的に安定な無機化合物または有機化合物で形成する。代表的には、無機絶縁物、無機半導体、または有機絶縁物で形成する。

【0058】

バッファ層301が無機絶縁物または有機絶縁物の場合は、トンネル効果により第1の電極層または第2の電極層から有機化合物層へ、正孔又は電子の電荷を注入する層である。バッファ層301は、所定の電圧において、トンネル効果により有機化合物層300へ電荷を注入することが可能な厚さで形成する。バッファ層301の代表的な厚さは、0.1nm以上4nm以下、好ましくは0.1nm以上2nm以下の絶縁層である。バッファ層301の膜厚は、0.1nm以上4nm以下と極めて薄いため、バッファ層301においてトンネル効果が生じ、有機化合物層300への電荷注入性が高まる。このため、バッファ層301は、厚さが4nmより厚くなると、バッファ層301におけるトンネル効果が生じず、有機化合物層300への電荷注入が困難となり、記憶素子の書き込み時の印加電圧が上昇する。

【0059】

バッファ層301を形成する無機絶縁物の代表例としては、酸化リチウム、酸化ナトリウム、酸化カリウム、酸化ルビジウム、酸化ベリリウム、酸化マグネシウム、酸化カルシウム、酸化ストロンチウム、酸化バリウム、酸化セシウム、酸化ジルコニウム、酸化ハフニウム、酸化フランシウム、酸化タンタル、酸化テクネチウム、酸化マンガン、酸化鉄、酸化コバルト、酸化パラジウム、酸化銀、アルミナ、酸化ガリウム、酸化ビスマス等に代表される絶縁性を有する酸化物が挙げられる。

【0060】

また、バッファ層301を形成する無機絶縁物の代表例としては、フッ化リチウム、フッ化ナトリウム、フッ化カリウム、フッ化セシウム、フッ化ベリリウム、フッ化マグネシウム、フッ化カルシウム、フッ化ストロンチウム、フッ化バリウム、フッ化アルミニウム、フッ化銀、フッ化マンガン等に代表される絶縁性を有するフッ化物、塩化リチウム、塩化ナトリウム、塩化カリウム、塩化セシウム、塩化ベリリウム、塩化カルシウム、塩化バリウム、塩化アルミニウム、塩化スズ、塩化銀、塩化亜鉛、塩化チタン、塩化ストロンチウム、塩化鉄、塩化パラジウム、塩化アンチモン、塩化ストロンチウム、塩化タリウム、塩化銅、塩化マンガン、塩化ルテニウム等に代表される絶縁性を有する塩化物、臭化カルシウム、臭化セシウム、臭化銀、臭化バリウム、臭化リチウム等に代表される絶縁性を有する臭化物、ヨウ化ナトリウム、ヨウ化カリウム、ヨウ化バリウム、ヨウ化タリウム、ヨウ化銀、ヨウ化チタン、ヨウ化カルシウム、ヨウ化珪素、ヨウ化セシウム等に代表される絶縁性を有するヨウ化物が挙げられる。

【0061】

また、バッファ層301を形成する無機絶縁物の代表例としては、炭酸リチウム、炭酸カルシウム、炭酸ナトリウム、炭酸マンガン、炭酸ストロンチウム、炭酸バリウム、炭酸鉄、炭酸コバルト、炭酸ニッケル、炭酸銅、炭酸銀、炭酸亜鉛等に代表される絶縁性を有する炭酸塩、硫化リチウム、硫化カルシウム、硫化ナトリウム、硫化マグネシウム、硫化ストロンチウム、硫化バリウム、硫化チタン、硫化ジルコニウム、硫化マンガン、硫化鉄、硫化コバルト、硫化ニッケル、硫化銅、硫化銀、硫化亜鉛、硫化アルミニウム、硫化インジウム、硫化スズ、硫化アンチモン、硫化ビスマス等に代表される絶縁性を有する硫酸塩、硝酸リチウム、硝酸カリウム、硝酸ナトリウム、硝酸マグネシウム、硝酸カルシウム、硝酸ストロンチウム、硝酸バリウム、硝酸チタン、硝酸ジルコニウム、硝酸マンガン、硝酸鉄、硝酸コバルト、硝酸ニッケル、硝酸銅、硝酸銀、硝酸亜鉛、硝酸アルミニウム、硝酸インジウム、硝酸スズ等に代表される絶縁性を有する硝酸塩、窒化アルミニウム、窒化珪素等に代表される絶縁性を有する窒化物が挙げられる。

【0062】

なお、バッファ層301を無機絶縁物で形成する場合、バッファ層301の膜厚は、0.1nm以上4nm以下が好ましい。絶縁層の膜厚が4nm以上になると、書き込み時の印加電圧が上昇する。

【0063】

バッファ層301を形成する有機絶縁物の代表例としては、ポリイミド、アクリル樹脂、ポリアミド、ベンゾシクロブテン樹脂、ポリエステル、ノボラック樹脂、メラミン樹脂、フェノール樹脂、エポキシ樹脂、シリコーン樹脂、フラン樹脂、ジアリルフタレート樹脂等に代表される有機化合物が挙げられる。

【0064】

バッファ層301を形成する無機半導体の代表例としては、シリコン、ゲルマニウム、酸化モリブデン、酸化スズ、酸化ビスマス、酸化バナジウム、酸化チタン、酸化鉄、酸化クロム、酸化銅、酸化マンガンシリコン、酸化ニッケル、酸化亜鉛、シリコンゲルマニウム、ヒ化ガリウム、窒化ガリウム、酸化インジウム、リン化インジウム、窒化インジウム、硫化カドミウム、テルル化カドミウム、チタン酸ストロンチウムなどの半導体を用いることができる。なお、バッファ層301は必ずしも一種の半導体から構成される必要はなく、複数の半導体材料が混合されていても良い。

【0065】

なお、バッファ層301を無機半導体で形成する場合、バッファ層301の膜厚は、0.1nm以上であれば特に限定されず、例えば10nm以下の薄い膜厚でも良いし、それ以上であっても良い。

【0066】

また、バッファ層301は異なる無機絶縁物、有機絶縁物、半導体で形成された層を単層で設けてもよいし、異なる無機絶縁物、有機絶縁物、半導体で形成された層を積層させて複数層としても良い。例えば、無機絶縁物層及び半導体層の積層、無機絶縁物層及び有機絶縁物層の積層、有機絶縁物層及び半導体層の積層等を適宜用いることができる。

【0067】

バッファ層301の形成方法としては、蒸着法、電子ビーム蒸着法、スパッタリング法、CVD法等を用いることができる。また、スピンコート法、ゾル−ゲル法、印刷法または液滴吐出法等を用いることができる。

【0068】

また、図3(C)に示すように、有機化合物を含む層105として、有機化合物層300及び凹凸を有する連続的なバッファ層302を用いて形成してもよい。但し、バッファ層の凸部における厚さは0.1nm以上10nm以下、好ましくは2nm以上8nm以下、凹部における厚さは、0.1nm以上4nm未満、好ましくは0.1nm以上2nm未満であることが好ましい。

【0069】

また、図3(D)に示すように、有機化合物を含む層105として、有機化合物層300及び分散された非連続な絶縁層303を用いて形成してもよい。非連続な絶縁層303は、島状、縞状、網目状等の形状を有してもよい。

【0070】

更には、バッファ層301〜303の代わりに、絶縁性粒子を設けてもよい。このときの絶縁性粒子は、粒径は0.1nm以上4nm以下であることが好ましい。

【0071】

なお、図3(B)〜(D)では、第1の電極層103及び有機化合物層300の間にバッファ層301〜303を設けたが、第2の電極層106及び有機化合物層300の間にバッファ層301〜303を設けてもよい。

【0072】

さらには、図3(E)に示すように、第1の電極層103及び有機化合物層300の間と、有機化合物層300及び第2の電極層106の間に、上記バッファ層301〜303または絶縁性粒子を設けてもよい。

【0073】

第1の電極層103及び有機化合物層300の間、または有機化合物層300及び第2の電極層106の間に、厚さが4nm以下、好ましくは2nm以下の無機絶縁物または有機絶縁物で形成されるバッファ層を設けることにより、当該絶縁層にトンネル電流が流れるため、記憶素子の書き込み時の印加電圧及び電流値のばらつきを低減することが可能である。また、第1の電極層103及び有機化合物層300の間、または有機化合物層300及び第2の電極層106の間に、厚さが4nm以下、好ましくは2nm以下の無機絶縁物または有機絶縁物で形成されるバッファ層を設けることにより、トンネル効果による電荷注入性が上昇し、有機化合物層300の膜厚を厚くすることが可能であり、初期状態でのショートを防止することが可能である。この結果、記憶装置及び半導体装置の信頼性を向上させることが可能である。

【0074】

また、上記構成とは異なる構成として、第1の電極層103及び有機化合物を含む層105の間、もしくは第2の電極層106と有機化合物を含む層105の間に、整流作用を有する素子を設けてもよい(図3(F))。整流作用を有する素子とは、代表的には、ショットキーダイオード、PN接合を有するダイオード、PIN接合を有するダイオード、あるいはゲート電極とドレイン電極を接続したトランジスタ等がある。もちろん、他の構成のダイオードでも構わない。ここでは、第1の電極層103と有機化合物を含む層105の間に、半導体層304、305を含むPN接合ダイオード306を設けた場合を示す。半導体層304、305のうち、一方はN型半導体であり、他方はP型半導体である。このように整流作用を有する素子を設けることにより、読み出し特性や書き込み特性を向上させることができる。

【0075】

また、基板上に形成した素子層及び封止層を剥して、図2(A)に示すような、可撓性を有する記憶装置113としてもよい。この場合、下地膜として機能する絶縁層102を、パッシベーション効果の有する層で形成することが好ましい。代表的な絶縁層102としては、窒化珪素層、窒化酸化珪素層を用いて形成することが好ましい。

【0076】

基板上に形成した素子層及び封止層を剥すために、基板及び下地膜として機能する絶縁層102の間に剥離層を形成することが好ましい。換言すると、基板から素子層及び封止層を容易に剥すために剥離層を用いることが好ましい。

【0077】

剥離層としては、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、タングステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、及び珪素(Si)の中から選択された元素、又は元素を主成分とする合金、又は元素を主成分とする化合物(代表的には、酸化物または窒化物)からなる層を、単層は複数の層を積層させて形成する。珪素を剥離層として用いる場合には、珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。

【0078】

剥離方法の一例としては、剥離層として上記金属のいずれかで形成される金属層及び当該金属酸化物層を形成し、剥離層を有する基板101及び素子層110を物理的手段により剥離する方法がある。物理的手段とは、力学的手段または機械的手段を指し、何らかの力学的エネルギー(機械的エネルギー)を半導体装置へ与える手段を指している。物理的手段は、代表的には機械的な力を加えること(例えば人間の手や把持具による剥離や、ローラを回転させる分離処理)である。

【0079】

また、他の剥離方法の一例としては、基板と素子層との間に、剥離層として水素を含む非晶質珪素層を設け、レーザ光の照射により非晶質珪素層に含まれる水素ガスを放出させて基板を剥離する方法がある。

【0080】

また、他の剥離方法の一例としては、基板と素子層との間に金属層及び金属酸化物層を有する剥離層を形成し、当該金属酸化物層を結晶化により脆弱化し、剥離層を液体のエッチャントやNF3、あるいはBrF3、ClF3等のフッ化ハロゲンガスによりエッチングで除去する方法がある。

【0081】

また、他の剥離方法の一例としては、素子層110及び封止層111が形成された基板101のみを機械的に削除する、又は基板101をエッチングで除去する方法がある。

【0082】

また、他の剥離方法の一例としては、基板101と素子層110との間に剥離層として金属層及び金属酸化物層を設け、当該金属酸化物層を結晶化により脆弱化し、金属層の一部を液体のエッチャントやNF3、あるいはBrF3、ClF3等のフッ化ハロゲンガスによりエッチングで除去した後、上記物理的方法を用いて脆弱化された金属酸化物層において物理的に剥離する方法がある。

【0083】

さらには、図2(B)に示すように、下地膜として機能する絶縁層102に可撓性基板120を接着材122を用いて貼りあわせて記憶装置128を形成してもよい。これにより、可撓性基板120上に素子層110及び封止層111が設けられる。このような記憶装置128は、薄型であり、且つ機械的強度の高い記憶装置である。

【0084】

可撓性基板120としては、可撓性を有する基板を用いることが好ましく、薄くて軽いものが好ましい。代表的には、PET(ポリエチレンテレフタレート)、PEN(ポリエチレンナフタレート)、PES(ポリエーテルスルホン)、ポリプロピレン、ポリプロピレンサルファイド、ポリカーボネート、ポリエーテルイミド、ポリフェニレンサルファイド、ポリフェニレンオキサイド、ポリサルフォン、ポリフタールアミド等のプラスチック基板、繊維質な材料からなる紙、セラミックシート等を用いることができる。当該基板を用いる場合、封止層111と可撓性基板120との間に接着材122を設けて、封止層111及び可撓性基板120を貼りあわせる。

【0085】

また、可撓性基板120として、繊維質な材料からなる紙または基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム等)と、接着性有機樹脂フィルム(アクリル樹脂、エポキシ樹脂等)との積層フィルムなどを用いることもできる。当該基板を用いる場合、可撓性基板120及び絶縁層102を熱圧着し、接着性有機樹脂フィルムを可塑化させた後、硬化させることで、積層フィルムに絶縁層102を固着させることができる。この場合は、絶縁層102及び可撓性基板120の間に接着材122を別途設ける必要は無い。

【0086】

素子層110または封止層111の一方の面に可撓性基板を有することで、このような記憶装置128の機械的強度を高めることが可能である。

【0087】

また、図2(C)に示すように、封止層111に接着材123を用いて可撓性基板125を貼り付けて、記憶装置126を形成することができる。即ち、可撓性基板120、125によって素子層110及び封止層111が封止されている。

【0088】

このような記憶装置126は素子層及び封止層111の周囲が可撓性基板で封止されているため、機械的強度及び外部環境に対する耐性を高めることが可能である。

【0089】

次に、上記で示す記憶装置のデータの書き込み動作及び読み出し動作について図4を用いて示す。

【0090】

図4(A)に示すように、メモリセル21は、ワード線Wy(1≦y≦n)に接続される第1の電極層と、ビット線Bx(1≦x≦m)に接続される第2の電極層と、有機化合物を含む層とを有する。有機化合物を含む層は、第1の電極層と第2の電極層の間に設けられる。

【0091】

メモリセルにデータの書き込みを行う際の動作について説明する。データの書き込みは、電気的作用によりデータの書き込みを行う場合について説明する。なお、書き込みはメモリセルの電気特性を変化させることで行うが、メモリセルの初期状態(電気的作用を加えていない状態)をデータ「0」、電気特性を変化させた状態を「1」とする。

【0092】

メモリセル21にデータ「1」を書き込む場合、まず、デコーダ133、134およびセレクタ135によってメモリセル21を選択する。例えば、デコーダ134によって、メモリセル131に接続されるワード線W3に所定の電圧V2が印加される。また、デコーダ133とセレクタ135によって、メモリセル21に接続されるビット線B3を読み出し/書き込み回路136に接続する。そして、読み出し/書き込み回路136からビット線B3へ書き込み電圧V1を出力する。こうして、当該メモリセル21を構成する第1の電極層と第2の電極層の間には電圧Vw=V1−V2を印加する。電位Vwを適切に選ぶことで、当該導電層間に設けられた有機化合物を含む層の特性を物理的もしくは電気的に変化させ、データ「1」の書き込みを行う。具体的には、読み出し動作電圧において、データ「1」の状態の第1の電極層と第2の電極層の間の電気抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化させるとよく、電圧Vwは5〜15V、あるいは−5〜−15Vとすればよい。例えば、(V1、V2)=(0V、5〜15V)、あるいは(3〜5V、−12〜−2V)などとすることができる。

【0093】

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「1」が書き込まれないよう制御する。例えば、非選択のワード線および非選択のビット線を浮遊状態とすればよい。メモリセル中のメモリ素子には、ダイオード特性など、選択性を確保できる特性を与える必要がある。

【0094】

一方、メモリセル21にデータ「0」を書き込む場合は、メモリセル21には電気的作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコーダ133、134およびセレクタ135によってメモリセル21を選択するが、読み出し/書き込み回路136からビット線B3への出力電位を、選択されたワード線W3の電位あるいは非選択ワード線の電位と同程度とする。すなわち、メモリセル131を構成する第1の電極層と第2の電極層の間に、メモリセル21の電気特性を変化させない程度の電圧(例えば−5〜5V)を印加すればよい。

【0095】

次に、メモリセルからデータの読み出しを行う際の動作について説明する(図4(B)、(C)参照)。データの読み出しは、メモリセルの電気特性が、データ「0」を有するメモリセルとデータ「1」を有するメモリセルとで異なることを利用して行う。例えば、データ「0」を有するメモリセルを構成する第1の電極層と第2の電極層の間の実効的な電気抵抗(以下、単にメモリセルの電気抵抗と呼ぶ)が、読み出し電圧においてR0、データ「1」を有するメモリセルの電気抵抗を、読み出し電圧においてR1とし、電気抵抗の差を利用して読み出す方法を説明する。なお、R1<<R0とする。読み出し/書き込み回路は、読み出し部分の構成として、例えば、図4(B)に示す抵抗素子146と差動増幅器147を用いた回路136を考えることができる。抵抗素子146は抵抗値Rrを有し、R1<Rr<R0であるとする。抵抗素子146の代わりにトランジスタ148を用いても良いし、差動増幅器の代わりにクロックドインバータ149を用いることも可能である(図4(C))。クロックドインバータ149には、読み出しを行うときにHi、行わないときにLowとなる信号又は反転信号が入力される。勿論、回路構成は図4(B)及び(C)に限定されない。

【0096】

メモリセル21からデータの読み出しを行う場合、まず、デコーダ133、134およびセレクタ135によってメモリセル21を選択する。具体的には、デコーダ134によって、メモリセル21に接続されるワード線W3に所定の電圧Vyを印加する。また、デコーダ133とセレクタ135によって、メモリセル21に接続されるビット線B3を読み出し/書き込み回路136の端子Pに接続する。その結果、端子Pの電位Vpは、抵抗素子146(抵抗値Rr)とメモリセル21(抵抗値R0もしくはR1)による抵抗分割によって決定される値となる。従って、メモリセル21がデータ「0」を有する場合には、Vp0=Vy+(V0−Vy)×R0/(R0+Rr)となる。また、メモリセル21がデータ「1」を有する場合には、Vp1=Vy+(V0−Vy)×R1/(R1+Rr)となる。その結果、図4(B)では、VrefをVp0とVp1の間となるように選択することで、図4(C)では、クロックドインバータの変化点をVp0とVp1の間となるように選択することで、出力電位Voutとして、データ「0」/「1」に応じて、Lo/Hi(もしくはHi/Lo)が出力され、読み出しを行うことができる。

【0097】

例えば、差動増幅器をVdd=3Vで動作させ、Vy=0V、V0=3V、Vref=1.5Vとする。仮に、R0/Rr=Rr/R1=9とすると、メモリセルのデータが「0」の場合、Vp0=2.7VとなりVoutはHighが出力され、メモリセルのデータが「1」の場合、Vp1=0.3VとなりVoutはLowが出力される。こうして、メモリセルの読み出しを行うことができる。

【0098】

上記の方法によると、有機化合物を含む層105の電気抵抗は、抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。勿論、読み出し方法は、この方法に限定されない。例えば、電気抵抗の差を利用する以外に、電流値の差を利用して読み出しても構わない。また、メモリセルの電気特性が、データ「0」と「1」とで、しきい値電圧が異なるダイオード特性を有する場合には、しきい値電圧の差を利用して読み出しても構わない。

【0099】

以上により、記憶素子の記憶保持特性の経年変化を抑制することが可能であり、記憶機能の信頼性の高い記憶装置を作製することができる。また、素子層及び封止層を可撓性基板上に設けることにより、極めて薄く、フレキシブルで、且つ記憶保持能力の信頼性の高い記憶装置を作製することができる。

【0100】

(実施の形態2)

本実施の形態では、上記実施の形態で示した記憶装置において、メモリセルにスイッチング素子及び記憶素子を有するメモリセルアレイを有する記憶装置の主要な構成について、図5及び図6を用いて説明する。図5は本実施の形態の記憶装置の断面図を示し、図6は本実施の形態の記憶装置の構造を示す。

【0101】

なお、図5においては、図2(C)に示す形態の変形例であり、可撓性基板で封止されている素子層及び封止層の形態について示す。また図5では、図1、図2(A)、及び図2(B)に示すような記憶装置の素子層の中にスイッチング素子及び記憶素子が形成されている状態が示されている。

【0102】

図6(A)に示すように、本実施の形態の記憶装置221はメモリセルアレイ222及びメモリセルアレイ222を駆動する駆動回路を有する。メモリセルアレイ222は、複数のメモリセル220がマトリクス状に設けられている。また、図6(A)及び図5に示すように、記憶装置221は、下地膜として機能する絶縁層150上に、駆動回路を構成するトランジスタ、(例えばデコーダ224を構成するトランジスタ152、スイッチング素子として機能するトランジスタ151)及び当該トランジスタ151に接続された記憶素子107が形成される。記憶素子107は、絶縁層205上に形成される第1の電極層103、有機化合物を含む層105、及び第2の電極層106を有する。なお、有機化合物を含む層105は、第1の電極層103、及び第1の電極層103の一部を覆う隔壁として機能する絶縁層104上に形成される。また、トランジスタ151として、薄膜トランジスタを用いている。また、第2の電極層106を覆って保護層として機能する絶縁層(図示せず)を有してもよい。

【0103】

また、下地膜として機能する絶縁層150から第2の電極層106の積層体を覆うように、吸湿材108が含まれる封止層111が形成される。ここでは、封止層111に覆われる積層体を素子層201と示す。

【0104】

また、素子層201及び封止層111は可撓性基板120、125で封止されている。なお、可撓性基板120は接着材122で素子層201及び封止層111に貼り付けられており、可撓性基板125は接着材123で封止層111に貼り付けられている。

【0105】

封止層111に吸湿材108が含まれることによって、封止層111で吸収した水分を吸湿材108で吸着、吸収することが可能である。このため、記憶装置の外気に含まれる水分が第1の電極層、第2の電極層、有機化合物を含む層等が形成されている素子層201に侵入することを抑制することが可能であり、これらの劣化を防ぐことができる。

【0106】

トランジスタ151、152は、Siウエハーを用いたMOSトランジスタ、SOI基板を用いたMOSトランジスタ、薄膜トランジスタ、有機半導体トランジスタ等を適宜用いることができる。ここでは、トランジスタ151、152として薄膜トランジスタを用いて示す。なお、ここでは、薄膜トランジスタとしてトップゲート型の薄膜トランジスタを示しているがこれに限定される物ではない。ボトムゲート型の薄膜トランジスタを適用することが可能である。

【0107】

記憶素子107は、絶縁層205上に形成される。このように、絶縁層205を設けることによって第1の電極層103を自由にレイアウトすることができる。つまり、トランジスタ151の上方に記憶素子107を形成することが可能となる。その結果、記憶装置をより高集積化することが可能となる。

【0108】

絶縁層205は、上記実施の形態で示した絶縁層104と同様の材料および形成方法を適宜用いて形成することができる。

【0109】

素子層201及び封止層111に貼り付ける可撓性を有する基板としては、実施の形態1の可撓性基板120で示した可撓性基板、熱可塑性樹脂を有するフィルム、繊維質な材料からなる紙、セラミックシート等を用いることで、記憶装置の小型、薄型、軽量化を図ることが可能である。

【0110】

次に、本実施の形態で示す記憶装置のデータの書き込み動作及び読み出し動作について図6を用いて示す。

【0111】

メモリセル220は、ワード線Wy(1≦y≦n)に接続する第1の電極層と、ビット線Bx(1≦x≦m)に接続する第2の電極層と、トランジスタ151と、記憶素子107とを有する。記憶素子107は、一対の導電層の間に、有機化合物を含む層が挟まれた構造を有する。トランジスタ151のゲート電極はワード線と接続され、ソース電極もしくはドレイン電極のいずれか一方はビット線と接続され、残る一方は記憶素子107が有する第1の電極層と接続される。記憶素子の残る第2の電極層は接続端子と接続される。また、接続端子は共通電極(電位Vcom)と接続される。

【0112】

次に、メモリセルアレイ222にデータの書き込みを行うときの動作について説明する。

【0113】

ここでは、3行3列目のメモリセル220に電気的作用によりデータを書き込む場合について説明する。なお、書き込みはメモリセルの電気特性を変化させることで行うが、メモリセルの初期状態(電気的作用を加えていない状態)をデータ「0」、電気特性を変化させた状態を「1」とする。

【0114】

メモリセル220にデータ「1」を書き込む場合、まず、デコーダ223、224およびセレクタ225によってメモリセル220を選択する。具体的には、デコーダ224によって、メモリセル220に接続されるワード線W3に所定の電圧V22を印加する。また、デコーダ223とセレクタ225によって、メモリセル220に接続されるビット線B3を読み出し/書き込み回路226に接続する。そして、読み出し/書き込み回路226からビット線B3へ書き込み電圧V21を出力する。

【0115】

こうして、メモリセルを構成するトランジスタ151をオン状態とし、記憶素子107に、ビット線を電気的に接続し、おおむねVw=Vcom−V21の電圧を印加する。なお、記憶素子107の第2の電極層は電位Vcomの共通電極に接続されている。電位Vwを適切に選ぶことで、当該導電層間に設けられた有機化合物を含む層105の特性を物理的もしくは電気的に変化させ、データ「1」の書き込みを行う。具体的には、読み出し動作電圧において、データ「1」の状態の第1の電極層と第2の電極層の間の電気抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化させるとよく、従って、単に短絡(ショート)させてもよい。なお、電位は、(V21、V22、Vcom)=(5〜15V、5〜15V、0V)、あるいは(−12〜0V、−12〜0V、3〜5V)の範囲から適宜選べば良い。電圧Vwは5〜15V、あるいは−5〜−15Vとすればよい。

【0116】

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「1」が書き込まれないよう制御する。具体的には、非選択のワード線には接続されるメモリセルのトランジスタをオフ状態とする電位(例えば0V)を印加し、非選択のビット線は浮遊状態とするか、Vcomと同程度の電位を印加するとよい。

【0117】

一方、メモリセル220にデータ「0」を書き込む場合は、メモリセル220には電気的作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコーダ223、224およびセレクタ225によってメモリセル220を選択するが、読み出し/書き込み回路226からビット線B3への出力電位をVcomと同程度とするか、ビット線B3を浮遊状態とする。その結果、記憶素子107には、小さい電圧(例えば−5〜5V)が印加されるか、電圧が印加されないため、電気特性が変化せず、データ「0」書き込みが実現される。

【0118】

次に、電気的作用により、データの読み出しを行う際の動作について説明する。データの読み出しは、電気特性が、データ「0」を有する記憶素子とデータ「1」を有する記憶素子とで異なることを利用して行う。例えば、データ「0」を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧においてR0、データ「1」を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧においてR1とし、電気抵抗の差を利用して読み出す方法を説明する。なお、R1<<R0とする。読み出し/書き込み回路は、読み出し部分の構成として、例えば、図6(B)に示す抵抗素子246と差動増幅器247を用いた回路226を考えることができる。抵抗素子246は抵抗値Rrを有し、R1<Rr<R0であるとする。抵抗素子246の代わりに、トランジスタ250を用いても良いし、差動増幅器の代わりにクロックドインバータ251を用いることも可能である(図6(C))。勿論、回路構成は図6(B)及び(C)に限定されない。

【0119】

3列3行目メモリセル220からデータの読み出しを行う場合、まず、デコーダ223、224およびセレクタ225によってメモリセル220を選択する。具体的には、デコーダ224によって、メモリセル220に接続されるワード線W3に所定の電圧V24を印加し、トランジスタ151をオン状態にする。また、デコーダ223とセレクタ225によって、メモリセル220に接続されるビット線B3を読み出し/書き込み回路226の端子Pに接続する。その結果、端子Pの電位Vpは、VcomとV0が抵抗素子246(抵抗値Rr)と記憶素子107(抵抗値R0もしくはR1)による抵抗分割によって決定される値となる。従って、メモリセル220がデータ「0」を有する場合には、Vp0=Vcom+(V0−Vcom)×R0/(R0+Rr)となる。また、メモリセル220がデータ「1」を有する場合には、Vp1=Vcom+(V0−Vcom)×R1/(R1+Rr)となる。その結果、図6(B)では、VrefをVp0とVp1の間となるように選択することで、図6(C)では、クロックドインバータの変化点をVp0とVp1の間となるように選択することで、出力電位Voutが、データ「0」/「1」に応じて、Lo/Hi(もしくはHi/Lo)が出力され、読み出しを行うことができる。

【0120】

例えば、差動増幅器をVdd=3Vで動作させ、Vcom=0V、V0=3V、Vref=1.5Vとする。仮に、R0/Rr=Rr/R1=9とし、トランジスタ151のオン抵抗を無視できるとすると、メモリセルのデータが「0」の場合、Vp0=2.7VとなりVoutはHighが出力され、メモリセルのデータが「1」の場合、Vp1=0.3VとなりVoutはLowが出力される。こうして、メモリセルの読み出しを行うことができる。

【0121】

上記の方法によると、記憶素子107の抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。勿論、読み出し方法は、この方法に限定されない。例えば、電気抵抗の差を利用する以外に、電流値の差を利用して読み出しても構わない。また、メモリセルの電気特性が、データ「0」と「1」とで、しきい値電圧が異なるダイオード特性を有する場合には、しきい値電圧の差を利用して読み出しても構わない。

【0122】

以上により、記憶素子の記憶保持特性の経年変化を抑制することが可能であり、記憶保持機能の信頼性の高い記憶装置を作製することができる。また、素子層及び封止層を可撓性基板上に設けることにより、極めて薄く、フレキシブルで、且つ記憶保持能力の信頼性の高い記憶装置を作製することができる。

【0123】

(実施の形態3)

本実施の形態では、上記実施の形態で示した剥離方法を用いて形成した半導体装置の一形態について以下に説明する。代表的には、無線信号により命令やデータの送受信を行うことのできる半導体装置の主要な構成について、図7及び図8を用いて説明する。図7は本実施の形態の半導体装置の断面図を示し、図8は本実施の形態の半導体装置の構造を示す。なお、本実施の形態の半導体装置は上記実施の形態で示すメモリセルアレイからなるメモリ部を有する。

【0124】

図8は、無線信号により命令やデータの送受信を行うことのできる半導体装置の一構成例を示すブロック図である。このような半導体装置は、アンテナ312、高周波回路部313、電源回路部315、ロジック回路部317を要素として含んでいる。アンテナ312は、リーダライタとも呼ばれる通信装置と信号の送受信を行う。信号を送る搬送波の周波帯は、長波帯の30〜135kHz、短波帯の6.78MHz、13.56MHz、27.125MHz、40.68MHz、5.0MHz、マイクロ波帯の2.45GHz、5.8GHz、24.125GHz等が適用される。アンテナ312は通信周波数帯に応じてコイル型やモノポール若しくはダイポール型の形態となる。

【0125】

アンテナ312が受信した搬送波は、検波容量部314を介して電源回路部315と、ロジック回路部317に分流する。電源回路部315では整流回路部320によって半波整流され、それが保持容量部322に充電される。定電圧回路部324は受信した搬送波の電力によってある一定以上の電力が供給されても、一定電圧を出力してこの半導体装置にあるロジック回路部317等の動作に必要な電力を供給する。

【0126】

高周波回路部313における復調回路部318は、搬送波を復調してロジック回路部317の動作に必要なクロック信号を生成し、さらにそれを補正する機能を有するPLL回路部328と、コード認識及び判定回路部326に信号を出力する。例えば、復調回路部318は、振幅変調(ASK)の受信信号から、振幅の変動を”0”又は”1”の受信データとして検出する。復調回路部318は、例えばローパスフィルターを含んで構成されている。また、変調回路部316は送信データを振幅変調(ASK)の送信信号として送信する。

【0127】

コード認識及び判定回路部326は、命令コードを認識し判定する。各コード認識及び判定回路部326が認識及び判定する命令コードは、フレーム終了信号(EOF、end of frame)、フレーム開始信号(SOF、start of frame)、フラグ、コマンドコード、マスク長(mask length)、マスク値(mask value)等である。また、各コード認識及び判定回路部326は、送信エラーを識別する巡回冗長検査(CRC、cyclic redundancy check)機能も含む。コード認識及び判定回路部326からの結果は、メモリコントローラ部330に出力される。メモリコントローラ部330は、判定結果に基づいて、メモリ部332の読み出しを制御する。メモリ部332から読み出されたデータは、符号化回路部334にて符号化され、変調回路部316によって変調を行い、応答信号が生成する。

【0128】

メモリ部332の構成としては、実施の形態1で示すような記憶素子を有するメモリセルや、実施の形態2で示すようなスイッチング素子に接続される記憶素子を有するメモリセルを適宜用いることができる。また、上記実施の形態で示すようなメモリセルの他に固定データのみを記憶するマスクROM(Read Only Memory)、SRAM(Static Random Access Memory)などの任意読み出し書き込み可能メモリ、電荷蓄積浮遊電極を有する不揮発性メモリなどを適用することができる。

【0129】

このように、図8で示す半導体装置は、リーダライタとも呼ばれる通信装置からの命令を受信して、メモリ部332にデータを書き込み、若しくはメモリ部332からデータを読み出す機能を有している。

【0130】

次に、本実施の形態の半導体装置の断面構造について、図7を用いて説明する。

【0131】

なお、図7においては、図2(C)に示す形態の変形例であり、可撓性基板で封止されている素子層及び封止層の形態について示す。しかし、この実施の形態では、図1、図2(A)、及び図2(B)に示すような記憶装置の素子層に以下の実施の形態に示す記憶装置、アンテナ、半導体素子等が形成される。

【0132】

ここで、半導体装置の一部として、メモリコントローラ部330、メモリ部332、アンテナ312、及び検波容量部314の断面図を示す(図7参照)。代表的には、下地膜として機能する絶縁層321上に、メモリコントローラ部330を構成するトランジスタ152、メモリ部332を構成するトランジスタ151及び当該トランジスタ151に接続された記憶素子107、検波容量部314の容量素子331及び薄膜トランジスタ333、アンテナ312を示す。なお、ここでは図示しないが、アンテナ312及び薄膜トランジスタ333は電気的に接続している。

【0133】

記憶素子107は、絶縁層205上に形成される第1の電極層103、有機化合物を含む層105、及び第2の電極層106を有する。第2の電極層106は、スズ合金層で形成される。なお、有機化合物を含む層105は、第1の電極層103、及び第1の電極層103の一部を覆う隔壁として機能する絶縁層104上に形成される。また、スイッチング素子として機能するトランジスタ151は、薄膜トランジスタを用いて形成する。また、第2の電極層106を及びアンテナ312を覆って保護層として機能する絶縁層を有してもよい。なお、下地膜として機能する絶縁層150からアンテナ312までの積層体を素子層341と示す。

【0134】

また、素子層341を覆うように吸湿材108が含まれる封止層111が形成される。

【0135】

封止層111に吸湿材108が含まれることによって、封止層111で吸収した水分を吸湿材108で吸着、吸収することが可能である。このため、半導体装置の外気に含まれる水分が第1の電極層、第2の電極層、有機化合物を含む層等が形成されている素子層110に侵入することを抑制することが可能であり、これらの劣化を防ぐことができる。

【0136】

また、素子層341及び封止層111が可撓性基板120、125で封止されている。なお、可撓性基板120は接着材122で素子層341及び封止層111に貼り付けられており、可撓性基板125は接着材123で封止層111に貼り付けられている。

【0137】

本実施の形態により、記憶素子の記憶保持特性の経年変化を抑制することが可能であり、無線で情報を送受信することが可能で、記憶機能の信頼性の高い半導体装置を作製することができる。また、素子層及び封止層を可撓性基板上に設けることにより、極めて薄く、フレキシブルで、無線で情報を送受信することが可能で、且つ記憶保持能力の信頼性の高い半導体装置を作製することができる。

【実施例1】

【0138】

本実施例では、無線信号により命令やデータの送受信を行うことのできる半導体装置において、スイッチング素子に接続される記憶素子がマトリクス状に配置されたメモリセルアレイを有する半導体装置の作製方法について、図9〜図15を用いて以下に説明する。

【0139】

基板501上に剥離層502を形成する。基板501としてはガラス基板を用いる。また、剥離層502としては、金属層及び金属酸化物層の積層構造とする。金属層としては、スパッタリング法により得られる30nm〜200nmのタングステン層、窒化タングステン層、またはモリブデン層を用いる。

【0140】

次に、金属酸化物層としては、金属層の表面を酸化させて金属酸化物層を形成する。金属酸化物層の形成方法は、酸素を含有する純水やオゾン水を用いて表面を酸化して形成してもよいし、酸素プラズマで酸化して形成してもよい。また、酸素を含む雰囲気で加熱を行って金属酸化物層を形成してもよい。また、後の絶縁層の形成工程で形成してもよい。この場合、絶縁層として酸化珪素層や酸化窒化珪素層をプラズマCVD法で形成する際に、剥離層502表面が酸化されて金属酸化物層が形成される。

【0141】

次に、金属酸化物層上に第1絶縁層503を形成する。第1絶縁層503としては、酸化珪素層、窒化珪素層または酸化窒化珪素層等の絶縁層を用いる。代表的な一例は第1絶縁層503として2層構造から成り、PCVD法によりSiH4、NH3、及びN2Oを反応ガスとして成膜される窒化酸化珪素層を50〜100nm、SiH4、及びN2Oを反応ガスとして成膜される酸化窒化珪素層を100〜150nmの厚さに積層形成する構造が採用される。また、第1絶縁層503の一層として膜厚10nm以下の窒化珪素層、或いは酸化窒化珪素層を用いることが好ましい。また、窒化酸化珪素層と、酸化窒化珪素層と、窒化珪素層とを順次積層した3層構造を用いてもよい。ここでは下地絶縁膜として第1絶縁層503を形成した例を示したが、特に必要でなければ設ける必要はない。

【0142】

次に、第1絶縁層503上に半導体層を形成する。半導体層は、非晶質構造を有する半導体層をスパッタリング法、LPCVD法、またはプラズマCVD法等により成膜する。次に、結晶化処理(レーザ結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体層上に第1のフォトマスクを用いてレジストマスクを形成した後、所望の形状にエッチングして、半導体層を形成する。なお、プラズマCVD法を用いれば、第1絶縁層と、非晶質構造を有する半導体層とを大気に触れることなく連続的に積層することができる。この半導体層の厚さは25〜80nm(好ましくは30〜70nm)の厚さで形成する。結晶質半導体層の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム合金などで形成すると良い。

【0143】

また、非晶質構造を有する半導体層を結晶化するために連続発振のレーザを用いてもよく、非晶質半導体層の結晶化に際し、大粒径に結晶を得るためには、連続発振が可能な固体レーザを用い、基本波の第2高調波〜第4高調波を適用するのが好ましい。代表的には、Nd:YVO4レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を適用すればよい。連続発振のレーザを用いる場合には、出力10Wの連続発振のYVO4レーザから射出されたレーザ光を非線形光学素子により高調波に変換する。また、共振器の中にYVO4結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または楕円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01〜100MW/cm2程度(好ましくは0.1〜10MW/cm2)が必要である。そして、10〜2000cm/s程度の速度でレーザ光に対して相対的に半導体層を移動させながら照射すればよい。

【0144】