記憶装置及び記憶装置の製造方法

【課題】低電圧で動作する分極率の高い強誘電体メモリを提供する。

【解決手段】基板の上に形成された下部電極と、前記下部電極上に形成された強誘電体膜と、前記強誘電体膜上に形成された上部電極と、を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする記憶装置により上記課題を解決する。

【解決手段】基板の上に形成された下部電極と、前記下部電極上に形成された強誘電体膜と、前記強誘電体膜上に形成された上部電極と、を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする記憶装置により上記課題を解決する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、記憶装置及び記憶装置の製造方法に関するものである。

【背景技術】

【0002】

電源を切断しても情報の記憶が維持される不揮発性メモリとして、フラッシュメモリや強誘電体メモリが知られている。フラッシュメモリは、絶縁ゲート型電界効果トランジスタ(IGFET:Insulated-Gate Field-Effect Transistor)のゲート絶縁膜中に埋め込まれたフローティングゲートを有しており、フローティングゲートに記憶情報を表わす電荷を蓄積して情報を記憶する。このため、フラッシュメモリでは、情報の書き込み及び消去において、絶縁膜を通過するトンネル電流を流す必要があり、比較的高い電圧を必要とする。

【0003】

一方、強誘電体メモリは、強誘電体のヒステリシス特性を利用して情報を記憶するものであり、強誘電体膜を一対の電極により挟んだ構造のものである。このように電極により挟まれた強誘電体膜を有する強誘電体キャパシタにおいては、電極間に印加される電圧に応じて分極が生じ、分極が生じた後には、電圧の印加がされていなくとも自発分極が生じている。強誘電体メモリにおいては、この自発分極を検出することにより、情報を読み出すことができ、印加電圧の極性を反転することにより、自発分極の極性を反転させることができる。

【0004】

このような強誘電体メモリは、フラッシュメモリに比べて低電圧で動作し、省電力で高速の書き込みができるといった特徴を有しており、更なる高集積化・省電力化のために、低電圧で大きな分極値を有するものが求められている。PZT(PbZrTiO3:チタン酸ジルコン酸鉛)は、比較的低電圧で大きな分極値が得られることから、このような強誘電体メモリに用いられる強誘電体材料として、多く用いられている(例えば、特許文献1、2)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−223667号公報

【特許文献2】国際公開第04/053991号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、このPZT膜を強誘電体メモリに用いた場合、PZT膜を薄くすることにより、強誘電体メモリをより低電圧で動作させることが可能である。しかしながら、PZT膜を薄くすると、分極値が減少し、また、リーク電流が増加してしまい、不揮発性メモリとして十分な特性を得ることができなくなる場合がある。

【0007】

このため、低電圧であっても大きな分極値が得られる強誘電体メモリである記憶装置及び記憶装置の製造方法が求められている。

【課題を解決するための手段】

【0008】

本実施の形態の一観点によれば、基板の上に形成された下部電極と、前記下部電極上に形成された強誘電体膜と、前記強誘電体膜上に形成された上部電極と、を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする。

【0009】

また、本実施の形態の他の一観点によれば、基板の上に形成された下部電極と、前記下部電極上に形成された強誘電体膜と、前記強誘電体膜上に形成された上部電極と、を有し、前記強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされており、前記Ruは、前記強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、前記強誘電体膜をPb(Zr1−YTiY−XRuX)O3とした場合、0<X≦0.1であることを特徴とする。

【0010】

また、本実施の形態の他の一観点によれば、基板の上に、下部電極を形成する工程と、前記下部電極上に、強誘電体膜を形成する工程と、前記強誘電体膜を形成した後、前記強誘電体膜を結晶化させる熱処理を行なう工程と、前記熱処理の行なわれた前記強誘電体膜上に、上部電極を形成する工程と、を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とが積層されたものであって、前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されているものであることを特徴とする。

【発明の効果】

【0011】

開示の記憶装置及び記憶装置の製造方法によれば、低電圧であっても大きな分極値を得ることができるため、低電圧で動作可能な不揮発性メモリである記憶装置を提供することができる。

【図面の簡単な説明】

【0012】

【図1】第1の実施の形態における記憶装置の製造方法の工程図(1)

【図2】第1の実施の形態における記憶装置の製造方法の工程図(2)

【図3】第1の実施の形態における記憶装置の製造方法の工程図(3)

【図4】第1の実施の形態における記憶装置の強誘電体キャパシタの拡大図

【図5】PZT及びRuドープされたPZTにおける回折ピークのシミュレーション結果

【図6】RuドープされたPZTにおける異常分散測定の結果

【図7】第2の実施の形態における記憶装置の製造方法の工程図(1)

【図8】第2の実施の形態における記憶装置の製造方法の工程図(2)

【図9】第2の実施の形態における記憶装置の製造方法の工程図(3)

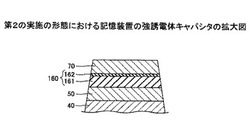

【図10】第2の実施の形態における記憶装置の強誘電体キャパシタの拡大図

【図11】第3の実施の形態における記憶装置の構造図

【図12】第3の実施の形態における記憶装置の強誘電体キャパシタの拡大図

【図13】第4の実施の形態における記憶装置の構造図

【図14】第4の実施の形態における記憶装置の強誘電体キャパシタの拡大図

【発明を実施するための形態】

【0013】

実施するための形態について、以下に説明する。尚、同じ部材等については、同一の符号を付して説明を省略する。

【0014】

〔第1の実施の形態〕

(記憶装置)

第1の実施の形態における記憶装置である強誘電体メモリの製造方法について、図1から図3に基づき説明する。

【0015】

最初に、図1(a)に示すように、基板となるシリコン基板等の半導体基板10の表面にMOS(Metal-Oxide-Semiconductor)トランジスタ20を作製し、更に、Wプラグ30を形成する。具体的には、シリコン基板等の半導体基板10の表面に、STI(Shallow Trench Isolation)により素子分離領域11を形成し、素子分離領域11に区画された素子活性領域において、半導体基板10の表面にウェル12を形成する。次に、ゲート絶縁膜13、ゲート電極14、シリサイド層15、低濃度拡散層16、サイドウォール17及び高濃度拡散層18をウェル12の表面に形成することにより、MOSトランジスタ20を形成する。次に、MOSトランジスタ20を覆うように全面にシリコン酸窒化膜21を形成し、更に、全面にシリコン酸化膜22を例えば、有機CVD(Chemical Vapor Deposition)により形成する。シリコン酸窒化膜21は、シリコン酸化膜22を形成する際のゲート絶縁膜13等の水素劣化を防ぐために形成されている。この後、各々の高濃度拡散層18に到達するコンタクトホールとなる開口部をシリコン酸化膜22及びシリコン酸窒化膜21を除去することにより形成する。次に、コンタクトホール内に50nmのTiN膜と30nmのTi膜により形成されるグルー膜31を形成し、更に、CVD法によりW膜を埋め込み、CMP(Chemical Mechanical Polishing:化学機械研磨)を行なうことにより平坦化し、Wプラグ30を形成する。

【0016】

次に、図1(b)に示すように、強誘電体キャパシタを形成する。具体的には、シリコン酸化膜22及びWプラグ30等の表面に、密着層40を形成し、更に、下部電極50、強誘電体膜60、上部電極70の順に積層形成する。

【0017】

密着層40は、TiN/TiAlN膜により形成されている。例えば、TiN膜は、スパッタリングによりTi膜を20nmの厚さ成膜した後、窒素(N2)雰囲気中において、高速アニール(RTA:Rapid Thermal Annealing)によって、650℃に加熱することにより形成する。また、TiAlN膜は、TiN膜の上に、スパッタリングにより100nmの厚さ成膜することにより形成する。

【0018】

下部電極50は、スパッタリングにより、表1に示される成膜条件で、Ir膜を約200nm成膜することにより形成する。

【0019】

【表1】

【0020】

強誘電体膜60は、スパッタリングにより、表2に示される成膜条件で、RuがドープされたPZT(PbZrTiO3:チタン酸ジルコン酸鉛)膜を約80nm成膜することにより形成する。尚、本願においては、RuがドープされたPZTをRuドープPZTと記載する場合がある。また、強誘電体膜60は、PZT膜に、La、Ca、Sr等がドープされているものに、更にRuがドープされているもの、即ち、RuがドープされているPLZT(PbLaZrTiO3)膜等であってもよい。また、本願において、PZTと記載する場合には、PZTにLa、Ca、Sr等がドープされているものも含むものを意味する場合がある。

【0021】

【表2】

【0022】

強誘電体膜60を成膜した後、ArとO2との混合雰囲気中(O2:濃度2.5%)において、600℃の温度で90秒の急速熱処理を行なう。尚、昇温温度は、125℃/secである。このように、急速熱処理を行なうことにより、PZT膜が結晶化するとともに、ドープされているRuをPb、Zr、Tiのいずれかのサイトに置換して入れることができる。尚、急速熱処理の温度は、550℃以上、800℃以下が好ましい。550℃未満では、強誘電体膜60を所望の結晶化状態にすることができず、また、800℃を超える温度では、強誘電体膜60における酸素成分が抜けて組成ずれ等が生じる場合があるからである。本実施の形態では、スパッタリングにより、RuがドープされたPZT膜を常温で成膜した後、急速熱処理を行なう方法について説明したが、RuをPb、Zr、Tiのサイトに置換して入れることができる方法であれば、他の方法であってもよい。尚、強誘電体膜60の詳細については後述する。

【0023】

上部電極70は、急速熱処理の行なわれた強誘電体膜60上に、スパッタリングにより、表3に示される成膜条件で、IrO2膜を約200nm成膜することにより形成する。

【0024】

【表3】

【0025】

尚、上部電極70として、Pt膜等ではなくIrO2膜を用いているのは、強誘電体膜60の水素劣化耐性を向上させるためである。Pt膜の場合、水素分子に対して触媒作用があるため、水素ラジカルが発生し、強誘電体膜60であるPZT膜を還元し劣化させやすい。これに対して、IrO2膜は触媒作用を有していないため、水素ラジカルが発生しにくく、強誘電体膜60の水素劣化耐性が格段に向上する。この後、上部電極70の成膜による強誘電体膜60へのダメージを回復するために、回復アニールを施す。本実施の形態では、例えば、ファーネスで650℃、O2雰囲気、60分の条件で行なう。

【0026】

次に、図1(c)に示すように、パターンニング、エッチング技術を用いて、スタック構造の強誘電体キャパシタを形成する。本実施の形態では、プラズマTEOS/TiNをハードマスクとして、上部電極70、強誘電体膜60、下部電極50、密着層40を一括でエッチングする。これにより、所定のWプラグ30の上の領域に、下部電極50、強誘電体膜60、上部電極70によりスタック構造の強誘電体キャパシタを形成することができる。このスタック構造の強誘電体キャパシタの拡大図を図4に示す。

【0027】

次に、図2(a)に示すように、保護膜80を形成した後、ファーネスで650℃、O2雰囲気、60分の条件でアニールを行なう。この保護膜80は、プロセスにおけるダメージより強誘電体キャパシタを保護するためのものであり、本実施の形態においては、保護膜80は、膜厚50nmの酸化アルミニウム(Al2O3)膜により形成されている。

【0028】

次に、図2(b)に示すように、層間絶縁膜90を形成した後、CMPにより平坦化を行なう。具体的には、層間絶縁膜90は、HDP(High Density Plasma)装置により形成された酸化膜であり、CMPは強誘電体キャパシタの上部電極70上において、層間絶縁膜90の膜厚が300nmになるまで行なう。

【0029】

次に、図2(c)に示すように、上部に強誘電体キャパシタが形成されていないWプラグ30と接続されるWプラグ100を形成する。具体的には、パターンニング、エッチング技術を用いて、上部に強誘電体キャパシタが形成されていないWプラグ30と接続するためのコンタクトホールを形成し、この後、グルー膜101、W膜を成膜した後に、W−CMPを行い、Wプラグ100を形成する。本実施の形態では、グルー膜101は、膜厚が50nmのTiN膜により形成されている。また、W−CMPを行なった後には、N2プラズマ、350℃、120秒を施す。このWプラグ100と、前述したWプラグ30の2つにより、via-to-viaコンタクトが形成され、後述するメタル配線110から基板10までのコンタクトを形成することができる。通常のメモリに比べて、強誘電体メモリの場合では、強誘電体キャパシタが形成される分だけ段差を有しているため、メタル配線110から基板10へのコンタクトのアスペクト比が大きくなる。このため、従来のように、コンタクトを形成するための開口部を一括のエッチングにより形成しようとしても、このようなエッチング自体が困難であり、また、このような開口部を形成することができたとしても、グルー膜の埋め込み形成することも困難である。よって、この場合には、歩留りの低下を招き、また、製造コストの上昇を招く。しかしながら、本実施の形態においては、via-to-viaコンタクトを形成することにより、強誘電体メモリの歩留りを向上させることができ、製造コストを低減することが可能となる。

【0030】

次に、図3に示すように、不図示のW酸化防止膜を成膜した後、強誘電体キャパシタの上部電極70と接続するためのコンタクトホールを形成し、この後、コンタクトホールが形成された領域にメタル配線110を形成する。W酸化防止膜は、膜厚が100nmのSiONにより形成されており、W酸化防止膜を成膜した後、パターンニング、エッチングにより、強誘電体キャパシタの上部電極70と接続するためのコンタクトホールを形成する。次に、ファーネスで550℃、O2雰囲気、60分の条件で回復アニールを行ない、その後、W酸化防止膜をエッチバックにより除去する。この後、メタル配線110を形成する。

【0031】

本実施の形態では、メタル配線110は、約70nmのTiN膜、約5nmのTi膜、約400nmのAl−Cu膜、約30nmのTiN膜、約60nmのTi膜の積層膜により形成されている。メタル配線110の形成方法は、メタル配線110を形成するための上述した積層膜を成膜した後、この積層膜上に誘電体膜を形成し、誘電体膜上にメタル配線110の形状に対応したレジストパターンを形成する。この後、エッチングによりレジストパターンの形成されていない領域の誘電体膜及び積層膜を除去することにより形成する。誘電体膜としては、約30nmのSiON膜が用いられる。尚、本実施の形態においては、図3に示されるように、形成されるメタル配線110は、下層グルー膜111、配線材料膜112及び上層グルー膜113が積層されたものである。よって、本実施の形態では、約70nmのTiN膜及び約5nmのTi膜により下層グルー膜111が形成され、約400nmのAl−Cu膜により配線材料膜112が形成され、約30nmのTiN膜及び約60nmのTi膜により上層グルー膜113が形成される。

【0032】

この後、図示しないが、同様の工程を所望の回数行なうことにより、更に2層以降の層間絶縁膜、コンタクトプラグ及びメタル配線を形成して、所望の層の多層配線構造を形成し、最後に、TEOSとSiNにより形成されるカバー膜を形成する。これにより、本実施の形態における記憶装置である強誘電体キャパシタを有する強誘電体メモリを作製することができる。

【0033】

このような方法により、強誘電体膜60におけるRuの組成の異なる強誘電体キャパシタを複数作製し、1.0Vで電気的特性の測定を行なった。尚、測定のために作製された強誘電体膜60は、(Pb0.9La0.1)(Zr0.4Ti0.6−XRuX)O3(以下、RuドープPLZTと記載する)膜である。

【0034】

強誘電体膜にRuドープされていないX=0のPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.6)O3膜を用いた場合では、分極量は7.0μC/cm2であった。一方、強誘電体膜60にX=0.05のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.55Ru0.05)O3膜を用いた場合では、分極量は15.2μC/cm2であった。また、強誘電体膜60にX=0.1のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.5Ru0.1)O3膜を用いた場合では、分極量は9.2μC/cm2であった。

【0035】

このように、PLZTにRuをドープすることにより、分極量が増加することが確認された。このように作製されたこれらの強誘電体メモリのリーク電流は、いずれも10−10A程度であり、顕著な違いは見られなかった。尚、PZTやPLZTにおいてRuを過剰にドープした場合、分極が生じなくなることから、PZTまたはPLZTにドープされるRuの量は、分極量が増加する0<X≦0.1が好ましい。即ち、RuドープされたPZTをPb(Zr1−YTiY−XRuX)O3と記載する場合には、0<X≦0.1が好ましく、RuドープされたPLZTを(Pb1−ZLaZ)(Zr1−YTiY−XRuX)O3と記載する場合には、0<X≦0.1が好ましい。

【0036】

(強誘電体膜60)

本実施の形態においては、強誘電体膜60は、強誘電体膜60にドープされるRuが、PZTの粒界ではなく、PZT結晶格子中に存在していること、即ち、PZT結晶におけるPb、Zr、Tiのいずれかと置換していることが重要である。また、強誘電体膜60がPLZTの場合には、強誘電体膜60にドープされているRuはPLZTの粒界ではなく、PLZT結晶格子中に存在していること、即ち、PLZT結晶におけるPb、La、Zr、Tiのいずれかと置換していることが重要である。

【0037】

このように、RuがPZT結晶格子中に存在しているか否かは、X線異常分散回折法を用いて確認することができる。具体的には、Ruの吸収端近傍のエネルギーのX線を用いて、PZTの回折ピーク強度のエネルギー依存性を測定することにより、PZT結晶格子中にRuがドープされているか否かを判別することが可能である。

【0038】

次に、PZT結晶格子中にRuがドープされているか否かの判別方法について説明する。最初に、PZT結晶格子中にRuが存在しているか否かにより、X線回折の強度にどのような変化が生じるか、シミュレーションを行なった。異常分散の効果が現れる吸収端近傍のエネルギーでは、回折ピークの強度は、数1に示す式により表わされる。尚、(h k l)は回折ピークの指数、(x y z)は原子位置である。また、原子散乱因子fは、f=f0+Δf'+iΔf''で表され、f0は非異常分散項、Δf'は異常分散項の実部、Δf''は異常分散項の虚部を意味する。

【0039】

【数1】

【0040】

上記の数1に示される式を用いて、PZT回折強度におけるRu吸収端近傍のエネルギー依存性を求めた。PZTの格子定数は、a=b=4.015Å(0.4015nm)、c=4.034Å(0.4034nm)、α=β=γ=90°とした。原子位置は、Pbは(0 0 0)、Zr及びTiは(0.5 0.5 0.52)、酸素は、(0.5 0.5 0)と(0.5 0 0.5)と(0 0.5 0.5)とした。組成は、Ruがドープされていない場合については、Pb(Zr0.4Ti0.6)O3であり、Ruがドープされている場合については、RuはいわゆるBサイトの約5%に置換しているPb(Zr0.4Ti0.55Ru0.05)O3とした。原子散乱因子は、NIST(National Institute of Standards and Technology)のホームページ等に記載されている公知な値を用いている。尚、本実施の形態では、PZTにおいて、Pbの位置をAサイト、Zr又はTiの位置をBサイトとして記載する。

【0041】

これらの条件を用いて、PZT(100)とPZT(110)の2種類の回折ピークについて計算を行なった。尚、本実施の形態においては、PZT(100)とは、PZTの(100)、(010)、(001)のすべて含む総称であり、PZT(110)とは、PZTの(110)、(101)、(011)のすべて含む総称であるものとする。

【0042】

このシミュレーションの結果を図5に示す。図5は、15400eVの強度の回折ピークにより規格化したものである。図5(a)は、Ruがドープされていないものの結果であり、図5(b)は、RuがX=0.05ドープされているものの結果である。図5(b)に示されるように、Ruをドープすることにより、Ruの吸収端のエネルギーにおいて、PZT(100)は上に凸のピークを示し、PZT(110)は下に凸のピークを示す。尚、図5(a)においては、PZT(100)とPZT(110)とが重なっている。

【0043】

図6は、RuがドープされているPZTにおいて、Ru吸収端近傍の異常分散測定を行った結果を示すものである。図6(a)は、PZT(100)における結果であり、図6(b)はPZT(110)における結果である。Ruの吸収端のエネルギーにおいて、破線で示される直線に対して、PZT(100)は上に凸のピークを示し、PZT(110)は下に凸のピークを示していることが確認されている。図6に示される結果は、図5(b)に示されるシミュレーションによる計算結果とよく一致しており、このようにして、PZT結晶格子中にRuがドープされていることを確認することができる。

【0044】

〔第2の実施の形態〕

(記憶装置)

第2の実施の形態における記憶装置である強誘電体メモリの製造方法について、図7から図9に基づき説明する。

【0045】

最初に、図7(a)に示すように、基板となるシリコン基板等の半導体基板10の表面にMOSトランジスタ20を作製し、更に、Wプラグ30を形成する。具体的には、シリコン基板等の半導体基板10の表面に、STIにより素子分離領域11を形成し、素子分離領域11に区画された素子活性領域において、半導体基板10の表面にウェル12を形成する。次に、ゲート絶縁膜13、ゲート電極14、シリサイド層15、低濃度拡散層16、サイドウォール17及び高濃度拡散層18をウェル12の表面に形成することにより、MOSトランジスタ20を形成する。次に、MOSトランジスタ20を覆うように全面にシリコン酸窒化膜21を形成し、更に、全面にシリコン酸化膜22を例えば、有機CVDにより形成する。シリコン酸窒化膜21は、シリコン酸化膜22を形成する際のゲート絶縁膜13等の水素劣化を防ぐために形成されている。この後、各々の高濃度拡散層18に到達するコンタクトホールとなる開口部をシリコン酸化膜22及びシリコン酸窒化膜21を除去することにより形成する。次に、コンタクトホール内に50nmのTiN膜と30nmのTi膜により形成されるグルー膜31を形成し、更に、CVD法によりW膜を埋め込み、CMPを行なうことにより平坦化し、Wプラグ30を形成する。

【0046】

次に、図7(b)に示すように、強誘電体キャパシタを形成する。具体的には、シリコン酸化膜22及びWプラグ30等の表面に、密着層40を形成し、更に、下部電極50、強誘電体膜160、上部電極70の順に積層形成する。

【0047】

密着層40は、TiN/TiAlN膜により形成されている。例えば、TiN膜は、スパッタリングによりTi膜を20nmの厚さ成膜した後、窒素(N2)雰囲気中において、高速アニール)によって、650℃に加熱することにより形成する。また、TiAlN膜は、TiN膜の上に、スパッタリングにより100nmの厚さ成膜することにより形成する。

【0048】

下部電極50は、スパッタリングにより、前述した表1に示される成膜条件で、Ir膜を約200nm成膜することにより形成する。

【0049】

強誘電体膜160は、第1の強誘電体膜161と第2の強誘電体膜162により形成されており、第1の強誘電体膜161は、Ruがドープされていない約70nmのPZT膜であり、第2の強誘電体膜162は、Ruがドープされた約10nmのPZT膜である。第1の強誘電体膜161及び第2の強誘電体膜162は、スパッタリングにより、前述した表2に示される成膜条件と同様の成膜条件で成膜することにより形成する。尚、第1の強誘電体膜161は、PZT膜に、La、Ca、Sr等がドープされているもの、即ち、PLZT膜等であってもよい。また、第2の強誘電体膜162は、PZT膜に、La、Ca、Sr等がドープされているものに、更にRuがドープされているもの、即ち、RuがドープされているPLZT膜等であってもよい。

【0050】

強誘電体膜160を形成する第1の強誘電体膜161及び第2の強誘電体膜162を成膜した後、ArとO2との混合雰囲気中(O2:濃度2.5%)において、600℃の温度で90秒の急速熱処理を行なう。尚、昇温温度は、125℃/secである。このように、急速熱処理を行なうことにより、PZT膜が結晶化すると共に、ドープされているRuをPb、Zr、Tiのいずれかのサイトに置換して入れることができる。尚、急速熱処理の温度は、550℃以上、800℃以下が好ましい。550℃未満では、強誘電体膜160を所望の結晶化状態にすることができず、また、800℃を超える温度では、強誘電体膜160における酸素成分が抜けて組成ずれ等が生じる場合があるからである。本実施の形態では、スパッタリングにより、RuがドープされたPZT膜を常温で成膜した後、急速熱処理を行なう方法について説明したが、RuをPb、Zr、Tiのサイトに置換して入れることができる方法であれば、他の方法であってもよい。

【0051】

上部電極70は、急速熱処理の行なわれた強誘電体膜160上に、スパッタリングにより、前述した表3に示される成膜条件で、IrO2膜を約200nm成膜することにより形成する。

【0052】

尚、上部電極70として、Pt膜等ではなくIrO2膜を用いているのは、強誘電体膜160の水素劣化耐性を向上させるためである。Pt膜の場合、水素分子に対して触媒作用があるため、水素ラジカルが発生し、強誘電体膜160であるPZT膜を還元し劣化させやすい。これに対して、IrO2膜は触媒作用を有していないため、水素ラジカルが発生しにくく、強誘電体膜160の水素劣化耐性が格段に向上する。この後、上部電極70の成膜による強誘電体膜160へのダメージを回復するために、回復アニールを施す。本実施の形態では、例えば、ファーネスで650℃、O2雰囲気、60分の条件で行なう。

【0053】

次に、図7(c)に示すように、パターンニング、エッチング技術を用いて、スタック構造の強誘電体キャパシタを形成する。本実施の形態では、プラズマTEOS/TiNをハードマスクとして、上部電極70、第2の強誘電体膜162、第1の強誘電体膜161、下部電極50、密着層40を一括でエッチングする。これにより、所定のWプラグ30の上の領域に、下部電極50、第2の強誘電体膜162、第1の強誘電体膜161、上部電極70によりスタック構造の強誘電体キャパシタを形成することができる。このスタック構造の強誘電体キャパシタの拡大図を図10に示す。このように、強誘電体膜160における第2の強誘電体膜162は、上部電極70と接して形成される。

【0054】

次に、図8(a)に示すように、保護膜80を形成した後、ファーネスで650℃、O2雰囲気、60分の条件でアニールを行なう。この保護膜80は、プロセスにおけるダメージより強誘電体キャパシタを保護するためのものであり、本実施の形態においては、保護膜80は、膜厚50nmの酸化アルミニウム(Al2O3)膜により形成されている。

【0055】

次に、図8(b)に示すように、層間絶縁膜90を形成した後、CMPにより平坦化を行なう。具体的には、層間絶縁膜90は、HDP装置により形成された酸化膜であり、CMPは強誘電体キャパシタの上部電極70上において、層間絶縁膜90の膜厚が300nmになるまで行なう。

【0056】

次に、図8(c)に示すように、上部に強誘電体キャパシタが形成されていないWプラグ30と接続されるWプラグ100を形成する。具体的には、パターンニング、エッチング技術を用いて、上部に強誘電体キャパシタが形成されていないWプラグ30と接続するためのコンタクトホールを形成し、この後、グルー膜101、W膜を成膜した後に、W−CMPを行い、Wプラグ100を形成する。本実施の形態では、グルー膜101は、膜厚が50nmのTiN膜により形成されている。また、W−CMPを行なった後には、N2プラズマ、350℃、120秒を施す。このWプラグ100と、前述したWプラグ30の2つにより、via-to-viaコンタクトが形成され、後述するメタル配線110から基板10までのコンタクトを形成することができる。通常のメモリに比べて、強誘電体メモリの場合では、強誘電体キャパシタが形成される分だけ段差を有しているため、メタル配線110から基板10へのコンタクトのアスペクト比が大きくなる。このため、従来のように、コンタクトを形成するための開口部を一括のエッチングにより形成しようとしても、このようなエッチング自体が困難であり、また、このような開口部を形成することができたとしても、グルー膜の埋め込み形成することも困難である。よって、この場合には、歩留りの低下を招き、また、製造コストの上昇を招く。しかしながら、本実施の形態においては、via-to-viaコンタクトを形成することにより、強誘電体メモリの歩留りを向上させることができ、製造コストを低減することが可能となる。

【0057】

次に、図9に示すように、不図示のW酸化防止膜を成膜した後、強誘電体キャパシタの上部電極70と接続するためのコンタクトホールを形成し、この後、コンタクトホールが形成された領域にメタル配線110を形成する。W酸化防止膜は、膜厚が100nmのSiONにより形成されており、W酸化防止膜を成膜した後、パターンニング、エッチングにより、強誘電体キャパシタの上部電極70と接続するためのコンタクトホールを形成する。次に、ファーネスで550℃、O2雰囲気、60分の条件で回復アニールを行ない、その後、W酸化防止膜をエッチバックにより除去する。この後、メタル配線110を形成する。

【0058】

本実施の形態では、メタル配線110は、約70nmのTiN膜、約5nmのTi膜、約400nmのAl−Cu膜、約30nmのTiN膜、約60nmのTi膜の積層膜により形成されている。具体的には、メタル配線110の形成方法は、メタル配線110を形成するための上述した積層膜を成膜した後、この積層膜上に誘電体膜を形成し、誘電体膜上にメタル配線110の形状に対応したレジストパターンを形成する。この後、エッチングによりレジストパターンの形成されていない領域の誘電体膜及び積層膜を除去することにより形成する。誘電体膜としては、約30nmのSiON膜が用いられる。尚、本実施の形態においては、図9に示されるように、形成されるメタル配線110は、下層グルー膜111、配線材料膜112及び上層グルー膜113が積層されたものである。よって、本実施の形態では、約70nmのTiN膜及び約5nmのTi膜により下層グルー膜111が形成され、約400nmのAl−Cu膜により配線材料膜112が形成され、約30nmのTiN膜及び約60nmのTi膜により上層グルー膜113が形成される。

【0059】

この後、図示しないが、同様の工程を所望の回数行なうことにより、更に2層以降の層間絶縁膜、コンタクトプラグ及びメタル配線を形成して所望の層の多層配線構造を形成し、最後に、TEOSとSiNにより形成されるカバー膜を形成する。これにより、本実施の形態における記憶装置である強誘電体キャパシタを有する強誘電体メモリを作製することができる。

【0060】

このような方法により、第2の強誘電体膜162におけるRuの組成の異なる強誘電体キャパシタを複数作製し、1.0Vで電気的特性の測定を行なった。尚、測定のために作製された第2の強誘電体膜162は、RuドープPLZT膜であり、第1の強誘電体膜161は、RuドープされていないPLZT膜である。

【0061】

第1の強誘電体膜及び第2の強誘電体膜に相当する強誘電体膜をともに、RuドープされていないPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.6)O3膜により形成した場合では、分極量は7.0μC/cm2であった。一方、第2の強誘電体膜162にX=0.05のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.55Ru0.05)O3膜を用いた場合では、分極量は18.3μC/cm2であった。

【0062】

第1の強誘電体膜161をRuドープされていないPLZT膜により形成し、第2の強誘電体膜162をRuドープPLZT膜により形成することにより、より一層分極量が増加することが確認された。このように作製されたこれらの強誘電体メモリのリーク電流は、いずれも10−10A程度であり、顕著な違いは見られなかった。

【0063】

尚、上記以外の内容については、第1の実施の形態と同様である。

【0064】

〔第3の実施の形態〕

次に、第3の実施の形態について説明する。本実施の形態は、図11及び図12に示すように、強誘電体膜260は、第1の強誘電体膜261と第2の強誘電体膜262を有しており、RuドープPLZT膜である第2の強誘電体膜262が下部電極50と接して形成されている。尚、図12は、本実施の形態における強誘電体メモリにおけるスタック構造の強誘電体キャパシタの拡大図を示す。

【0065】

具体的には、本実施の形態においては、下部電極50上に第2の強誘電体膜262、第1の強誘電体膜261がこの順で積層形成されており、第1の強誘電体膜261上に上部電極70が形成されている。第1の強誘電体膜261は、Ruがドープされていない約70nmのPZT膜であり、第2の強誘電体膜262は、Ruがドープされた約10nmのPZT膜である。尚、第1の強誘電体膜261及び第2の強誘電体膜262は、第2の実施の形態と同様の成膜方法及び成膜条件により形成することができる。また、本実施の形態における記憶装置である強誘電体メモリの製造方法は、強誘電体膜260を除き、第2の実施の形態と同様である。

【0066】

本実施の形態における記憶装置における強誘電体キャパシタとして、第2の強誘電体膜262におけるRuの組成の異なる強誘電体キャパシタを作製し、1.0Vで電気的特性の測定を行なった。尚、測定のために作製された第2の強誘電体膜262は、RuドープPLZT膜であり、第1の強誘電体膜261は、RuドープされていないPLZT膜である。

【0067】

第1の強誘電体膜及び第2の強誘電体膜に相当する強誘電体膜をともに、RuドープされていないPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.6)O3膜により形成した場合では、分極量は7.0μC/cm2であった。一方、第2の強誘電体膜262にX=0.05のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.55Ru0.05)O3膜を用いた場合では、分極量は16.3μC/cm2であった。

【0068】

第1の強誘電体膜261をRuドープされていないPLZT膜により形成し、第2の強誘電体膜262をRuドープPLZT膜により形成することにより、より一層分極量が増加することが確認された。このように作製されたこれらの強誘電体メモリのリーク電流は、いずれも10−10A程度であり、顕著な違いは見られなかった。

【0069】

尚、本実施の形態においては、下部電極50上にRuドープPZT膜等が形成されているものであるため、下部電極50上のPZT結晶の配位方向のばらつきについて、第1及び第2の実施の形態と比較を行った。この結果、本実施の形態における(111)回折ピークにおけるロッキングカーブの半値幅は、3.8°であったのに対し、第1の実施の形態及び第2の実施の形態における(111)回折ピークにおけるロッキングカーブの半値幅は、4.5°であった。PZT結晶の配位方向のばらつきの減少は、分極量のばらつきが減少することを意味している。つまり、強誘電体キャパシタのサイズが小さくなり、1つのキャパシタあたりの結晶粒の数が少なくなったときに、分極量がキャパシタ毎に一様になる効果が期待できる。よって、本実施の形態における記憶装置である強誘電体メモリは、より一層均一性を高め、歩留りを向上させることができる。

【0070】

尚、上記以外の内容については、第2の実施の形態と同様である。

【0071】

〔第4の実施の形態〕

次に、第4の実施の形態について説明する。本実施の形態は、図13及び図14に示すように、強誘電体膜360は、第1の強誘電体膜361と第2の強誘電体膜362と第3の強誘電体膜363を有している。また、RuドープPLZT膜である第2の強誘電体膜362が下部電極50と接して形成されており、RuドープPLZT膜である第3の強誘電体膜363が上部電極70と接して形成されている。尚、図14は、本実施の形態における強誘電体メモリにおけるスタック構造の強誘電体キャパシタの拡大図を示す。

【0072】

具体的には、本実施の形態においては、下部電極50上に第2の強誘電体膜362、第1の強誘電体膜361、第3の強誘電体膜363が、この順で積層形成されており、第3の強誘電体膜363上に上部電極70が形成されている。第1の強誘電体膜361は、Ruがドープされていない約60nmのPZT膜であり、第2の強誘電体膜362及び第3の強誘電体膜363は、Ruがドープされた約10nmのPZT膜である。尚、第1の強誘電体膜361、第2の強誘電体膜362及び第3の強誘電体膜363は、第2の実施の形態と同様の成膜方法及び成膜条件により形成することができる。また、本実施の形態における記憶装置である強誘電体メモリの製造方法は、強誘電体膜360を除き、第2の実施の形態と同様である。

【0073】

本実施の形態における記憶装置における強誘電体キャパシタとして、第2の強誘電体膜362及び第3の強誘電体膜363におけるRuの組成の異なる強誘電体キャパシタを作製し、1.0Vで電気的特性の測定を行なった。尚、測定のために作製された第2の強誘電体膜362及び第3の強誘電体膜363は、RuドープPLZT膜であり、第1の強誘電体膜361は、RuドープされていないPLZT膜である。

【0074】

第1の強誘電体膜、第2の強誘電体膜及び第3の強誘電体膜に相当する強誘電体膜をRuドープされていないPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.6)O3膜により形成した場合では、分極量は7.0μC/cm2であった。一方、第2の強誘電体膜362及び第3の強誘電体膜363にX=0.05のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.55Ru0.05)O3膜を用いた場合では、分極量は17.8μC/cm2であった。

【0075】

第1の強誘電体膜361をRuドープされていないPLZT膜により形成し、第1の強誘電体膜361の両側に、第2の強誘電体膜362及び第3の強誘電体膜363をRuドープPLZT膜により形成することにより、より一層分極量が増加することが確認された。このように作製されたこれらの強誘電体メモリのリーク電流は、いずれも10−10A程度であり、顕著な違いは見られなかった。

【0076】

尚、本実施の形態においては、下部電極50上にRuドープPZT膜等が形成されているものであるため、下部電極50上のPZT結晶の配位方向のばらつきについて、第1及び第2の実施の形態と比較を行った。この結果、本実施の形態における(111)回折ピークにおけるロッキングカーブの半値幅は、3.8°であったのに対し、第1の実施の形態及び第2の実施の形態における(111)回折ピークにおけるロッキングカーブの半値幅は、4.5°であった。PZT結晶の配位方向のばらつきの減少は、分極量のばらつきが減少することを意味している。つまり、強誘電体キャパシタのサイズが小さくなり、1つのキャパシタあたりの結晶粒の数が少なくなったときに、分極量がキャパシタ毎に一様になる効果が期待できる。よって、本実施の形態における記憶装置である強誘電体メモリは、より一層均一性を高め、歩留りを向上させることができる。

【0077】

尚、上記以外の内容については、第2の実施の形態と同様である。

【0078】

以上、実施の形態について詳述したが、特定の実施形態に限定されるものではなく、特許請求の範囲に記載された範囲内において、種々の変形及び変更が可能である。

【0079】

上記の説明に関し、更に以下の付記を開示する。

(付記1)

基板の上に形成された下部電極と、

前記下部電極上に形成された強誘電体膜と、

前記強誘電体膜上に形成された上部電極と、

を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、

前記第2の強誘電体膜は、PbZrTiO3を含む材料にRuがドープされているものにより形成されており、

前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする記憶装置。

(付記2)

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛にLa、Ca、Srのうちから選ばれる1または2以上の元素が含まれる材料により形成されており、

前記第2の強誘電体膜は、チタン酸ジルコン酸鉛にLa、Ca、Srのうちから選ばれる1または2以上の元素が含まれる材料に、Ruがドープされているものより形成されていることを特徴とする付記1に記載の記憶装置。

(付記3)

前記第2の強誘電体膜は、前記下部電極または前記上部電極と接していることを特徴とする付記1または2に記載の記憶装置。

(付記4)

前記強誘電体膜は、更に、第3の強誘電体膜を有するものであって、

前記第3の強誘電体膜はチタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記Ruは前記第3の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、

前記第1の強誘電体膜の一方の面に前記第2の強誘電体膜が設けられており、前記第1の強誘電体膜の他方の面に前記第3の強誘電体膜が設けられていることを特徴とする付記1または2に記載の記憶装置。

(付記5)

前記第3の強誘電体膜は、チタン酸ジルコン酸鉛にLa、Ca、Srのうちから選ばれる1または2以上の元素が含まれる材料に、Ruがドープされているものであることを特徴とする付記4に記載の記憶装置。

(付記6)

前記第2の強誘電体膜は前記下部電極と接しており、前記第3の強誘電体膜は前記上部電極と接していることを特徴とする付記4または5に記載の記憶装置。

(付記7)

基板の上に形成された下部電極と、

前記下部電極上に形成された強誘電体膜と、

前記強誘電体膜上に形成された上部電極と、

を有し、前記強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされており、

前記Ruは、前記強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、

前記強誘電体膜をPb(Zr1−YTiY−XRuX)O3とした場合、0<X≦0.1であることを特徴とする記憶装置。

(付記8)

前記強誘電体膜は、チタン酸ジルコン酸鉛にLa、Ca、Srのうちから選ばれる1または2以上の元素が含まれる材料に、Ruがドープされているものであることを特徴とする付記7に記載の記憶装置。

(付記9)

前記基板上にはトランジスタが形成されており、

前記下部電極または前記上部電極は、前記トランジスタと接続されていることを特徴とする付記1から8のいずれかに記載の記憶装置。

(付記10)

前記下部電極は、前記トランジスタの上方に形成されていることを特徴とする付記9に記載の記憶装置。

(付記11)

基板の上に、下部電極を形成する工程と、

前記下部電極上に、強誘電体膜を形成する工程と、

前記強誘電体膜を形成した後、前記強誘電体膜を結晶化させる熱処理を行なう工程と、

前記熱処理の行なわれた前記強誘電体膜上に、上部電極を形成する工程と、

を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とが積層されたものであって、

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、

前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されているものであることを特徴とする記憶装置の製造方法。

(付記12)

前記強誘電体膜を形成する工程は、

前記下部電極上に、前記第2の強誘電体膜を形成する工程と、

前記第2の強誘電体膜上に、前記第1の強誘電体膜を形成する工程と、

前記第1の強誘電体膜上に、第3の強誘電体膜を形成する工程と、

を有するものであって、

前記上部電極は、前記第3の強誘電体膜上に形成されるものであって、

前記第3の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されているものであることを特徴とする付記11に記載の記憶装置の製造方法。

(付記13)

前記基板にトランジスタを形成する工程と、

前記トランジスタの上に層間絶縁膜を形成し、前記層間絶縁膜に開口部を形成し、前記開口部にW膜を形成することにより、前記トランジスタに接続されるWプラグを形成する工程と、

を有し、前記下部電極を形成する工程は、前記Wプラグの上部に、前記下部電極を形成するものであることを特徴とする付記11または12に記載の記憶装置の製造方法。

【符号の説明】

【0080】

10 半導体基板

11 素子分離領域

12 ウェル

13 ゲート絶縁膜

14 ゲート電極

15 シリサイド層

16 低濃度拡散層

17 サイドウォール

18 高濃度拡散層

20 MOSトランジスタ

21 シリコン酸窒化膜

22 シリコン酸化膜

30 Wプラグ

31 グルー膜

40 密着層

50 下部電極

60 強誘電体膜

70 上部電極

80 保護膜

90 層間絶縁膜

100 Wプラグ

110 メタル配線

111 下層グルー膜

112 配線材料膜

113 上層グルー膜

160 強誘電体膜

161 第1の強誘電体膜

162 第2の強誘電体膜

260 強誘電体膜

261 第1の強誘電体膜

262 第2の強誘電体膜

360 強誘電体膜

361 第1の強誘電体膜

362 第2の強誘電体膜

363 第3の強誘電体膜

【技術分野】

【0001】

本発明は、記憶装置及び記憶装置の製造方法に関するものである。

【背景技術】

【0002】

電源を切断しても情報の記憶が維持される不揮発性メモリとして、フラッシュメモリや強誘電体メモリが知られている。フラッシュメモリは、絶縁ゲート型電界効果トランジスタ(IGFET:Insulated-Gate Field-Effect Transistor)のゲート絶縁膜中に埋め込まれたフローティングゲートを有しており、フローティングゲートに記憶情報を表わす電荷を蓄積して情報を記憶する。このため、フラッシュメモリでは、情報の書き込み及び消去において、絶縁膜を通過するトンネル電流を流す必要があり、比較的高い電圧を必要とする。

【0003】

一方、強誘電体メモリは、強誘電体のヒステリシス特性を利用して情報を記憶するものであり、強誘電体膜を一対の電極により挟んだ構造のものである。このように電極により挟まれた強誘電体膜を有する強誘電体キャパシタにおいては、電極間に印加される電圧に応じて分極が生じ、分極が生じた後には、電圧の印加がされていなくとも自発分極が生じている。強誘電体メモリにおいては、この自発分極を検出することにより、情報を読み出すことができ、印加電圧の極性を反転することにより、自発分極の極性を反転させることができる。

【0004】

このような強誘電体メモリは、フラッシュメモリに比べて低電圧で動作し、省電力で高速の書き込みができるといった特徴を有しており、更なる高集積化・省電力化のために、低電圧で大きな分極値を有するものが求められている。PZT(PbZrTiO3:チタン酸ジルコン酸鉛)は、比較的低電圧で大きな分極値が得られることから、このような強誘電体メモリに用いられる強誘電体材料として、多く用いられている(例えば、特許文献1、2)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−223667号公報

【特許文献2】国際公開第04/053991号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、このPZT膜を強誘電体メモリに用いた場合、PZT膜を薄くすることにより、強誘電体メモリをより低電圧で動作させることが可能である。しかしながら、PZT膜を薄くすると、分極値が減少し、また、リーク電流が増加してしまい、不揮発性メモリとして十分な特性を得ることができなくなる場合がある。

【0007】

このため、低電圧であっても大きな分極値が得られる強誘電体メモリである記憶装置及び記憶装置の製造方法が求められている。

【課題を解決するための手段】

【0008】

本実施の形態の一観点によれば、基板の上に形成された下部電極と、前記下部電極上に形成された強誘電体膜と、前記強誘電体膜上に形成された上部電極と、を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする。

【0009】

また、本実施の形態の他の一観点によれば、基板の上に形成された下部電極と、前記下部電極上に形成された強誘電体膜と、前記強誘電体膜上に形成された上部電極と、を有し、前記強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされており、前記Ruは、前記強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、前記強誘電体膜をPb(Zr1−YTiY−XRuX)O3とした場合、0<X≦0.1であることを特徴とする。

【0010】

また、本実施の形態の他の一観点によれば、基板の上に、下部電極を形成する工程と、前記下部電極上に、強誘電体膜を形成する工程と、前記強誘電体膜を形成した後、前記強誘電体膜を結晶化させる熱処理を行なう工程と、前記熱処理の行なわれた前記強誘電体膜上に、上部電極を形成する工程と、を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とが積層されたものであって、前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されているものであることを特徴とする。

【発明の効果】

【0011】

開示の記憶装置及び記憶装置の製造方法によれば、低電圧であっても大きな分極値を得ることができるため、低電圧で動作可能な不揮発性メモリである記憶装置を提供することができる。

【図面の簡単な説明】

【0012】

【図1】第1の実施の形態における記憶装置の製造方法の工程図(1)

【図2】第1の実施の形態における記憶装置の製造方法の工程図(2)

【図3】第1の実施の形態における記憶装置の製造方法の工程図(3)

【図4】第1の実施の形態における記憶装置の強誘電体キャパシタの拡大図

【図5】PZT及びRuドープされたPZTにおける回折ピークのシミュレーション結果

【図6】RuドープされたPZTにおける異常分散測定の結果

【図7】第2の実施の形態における記憶装置の製造方法の工程図(1)

【図8】第2の実施の形態における記憶装置の製造方法の工程図(2)

【図9】第2の実施の形態における記憶装置の製造方法の工程図(3)

【図10】第2の実施の形態における記憶装置の強誘電体キャパシタの拡大図

【図11】第3の実施の形態における記憶装置の構造図

【図12】第3の実施の形態における記憶装置の強誘電体キャパシタの拡大図

【図13】第4の実施の形態における記憶装置の構造図

【図14】第4の実施の形態における記憶装置の強誘電体キャパシタの拡大図

【発明を実施するための形態】

【0013】

実施するための形態について、以下に説明する。尚、同じ部材等については、同一の符号を付して説明を省略する。

【0014】

〔第1の実施の形態〕

(記憶装置)

第1の実施の形態における記憶装置である強誘電体メモリの製造方法について、図1から図3に基づき説明する。

【0015】

最初に、図1(a)に示すように、基板となるシリコン基板等の半導体基板10の表面にMOS(Metal-Oxide-Semiconductor)トランジスタ20を作製し、更に、Wプラグ30を形成する。具体的には、シリコン基板等の半導体基板10の表面に、STI(Shallow Trench Isolation)により素子分離領域11を形成し、素子分離領域11に区画された素子活性領域において、半導体基板10の表面にウェル12を形成する。次に、ゲート絶縁膜13、ゲート電極14、シリサイド層15、低濃度拡散層16、サイドウォール17及び高濃度拡散層18をウェル12の表面に形成することにより、MOSトランジスタ20を形成する。次に、MOSトランジスタ20を覆うように全面にシリコン酸窒化膜21を形成し、更に、全面にシリコン酸化膜22を例えば、有機CVD(Chemical Vapor Deposition)により形成する。シリコン酸窒化膜21は、シリコン酸化膜22を形成する際のゲート絶縁膜13等の水素劣化を防ぐために形成されている。この後、各々の高濃度拡散層18に到達するコンタクトホールとなる開口部をシリコン酸化膜22及びシリコン酸窒化膜21を除去することにより形成する。次に、コンタクトホール内に50nmのTiN膜と30nmのTi膜により形成されるグルー膜31を形成し、更に、CVD法によりW膜を埋め込み、CMP(Chemical Mechanical Polishing:化学機械研磨)を行なうことにより平坦化し、Wプラグ30を形成する。

【0016】

次に、図1(b)に示すように、強誘電体キャパシタを形成する。具体的には、シリコン酸化膜22及びWプラグ30等の表面に、密着層40を形成し、更に、下部電極50、強誘電体膜60、上部電極70の順に積層形成する。

【0017】

密着層40は、TiN/TiAlN膜により形成されている。例えば、TiN膜は、スパッタリングによりTi膜を20nmの厚さ成膜した後、窒素(N2)雰囲気中において、高速アニール(RTA:Rapid Thermal Annealing)によって、650℃に加熱することにより形成する。また、TiAlN膜は、TiN膜の上に、スパッタリングにより100nmの厚さ成膜することにより形成する。

【0018】

下部電極50は、スパッタリングにより、表1に示される成膜条件で、Ir膜を約200nm成膜することにより形成する。

【0019】

【表1】

【0020】

強誘電体膜60は、スパッタリングにより、表2に示される成膜条件で、RuがドープされたPZT(PbZrTiO3:チタン酸ジルコン酸鉛)膜を約80nm成膜することにより形成する。尚、本願においては、RuがドープされたPZTをRuドープPZTと記載する場合がある。また、強誘電体膜60は、PZT膜に、La、Ca、Sr等がドープされているものに、更にRuがドープされているもの、即ち、RuがドープされているPLZT(PbLaZrTiO3)膜等であってもよい。また、本願において、PZTと記載する場合には、PZTにLa、Ca、Sr等がドープされているものも含むものを意味する場合がある。

【0021】

【表2】

【0022】

強誘電体膜60を成膜した後、ArとO2との混合雰囲気中(O2:濃度2.5%)において、600℃の温度で90秒の急速熱処理を行なう。尚、昇温温度は、125℃/secである。このように、急速熱処理を行なうことにより、PZT膜が結晶化するとともに、ドープされているRuをPb、Zr、Tiのいずれかのサイトに置換して入れることができる。尚、急速熱処理の温度は、550℃以上、800℃以下が好ましい。550℃未満では、強誘電体膜60を所望の結晶化状態にすることができず、また、800℃を超える温度では、強誘電体膜60における酸素成分が抜けて組成ずれ等が生じる場合があるからである。本実施の形態では、スパッタリングにより、RuがドープされたPZT膜を常温で成膜した後、急速熱処理を行なう方法について説明したが、RuをPb、Zr、Tiのサイトに置換して入れることができる方法であれば、他の方法であってもよい。尚、強誘電体膜60の詳細については後述する。

【0023】

上部電極70は、急速熱処理の行なわれた強誘電体膜60上に、スパッタリングにより、表3に示される成膜条件で、IrO2膜を約200nm成膜することにより形成する。

【0024】

【表3】

【0025】

尚、上部電極70として、Pt膜等ではなくIrO2膜を用いているのは、強誘電体膜60の水素劣化耐性を向上させるためである。Pt膜の場合、水素分子に対して触媒作用があるため、水素ラジカルが発生し、強誘電体膜60であるPZT膜を還元し劣化させやすい。これに対して、IrO2膜は触媒作用を有していないため、水素ラジカルが発生しにくく、強誘電体膜60の水素劣化耐性が格段に向上する。この後、上部電極70の成膜による強誘電体膜60へのダメージを回復するために、回復アニールを施す。本実施の形態では、例えば、ファーネスで650℃、O2雰囲気、60分の条件で行なう。

【0026】

次に、図1(c)に示すように、パターンニング、エッチング技術を用いて、スタック構造の強誘電体キャパシタを形成する。本実施の形態では、プラズマTEOS/TiNをハードマスクとして、上部電極70、強誘電体膜60、下部電極50、密着層40を一括でエッチングする。これにより、所定のWプラグ30の上の領域に、下部電極50、強誘電体膜60、上部電極70によりスタック構造の強誘電体キャパシタを形成することができる。このスタック構造の強誘電体キャパシタの拡大図を図4に示す。

【0027】

次に、図2(a)に示すように、保護膜80を形成した後、ファーネスで650℃、O2雰囲気、60分の条件でアニールを行なう。この保護膜80は、プロセスにおけるダメージより強誘電体キャパシタを保護するためのものであり、本実施の形態においては、保護膜80は、膜厚50nmの酸化アルミニウム(Al2O3)膜により形成されている。

【0028】

次に、図2(b)に示すように、層間絶縁膜90を形成した後、CMPにより平坦化を行なう。具体的には、層間絶縁膜90は、HDP(High Density Plasma)装置により形成された酸化膜であり、CMPは強誘電体キャパシタの上部電極70上において、層間絶縁膜90の膜厚が300nmになるまで行なう。

【0029】

次に、図2(c)に示すように、上部に強誘電体キャパシタが形成されていないWプラグ30と接続されるWプラグ100を形成する。具体的には、パターンニング、エッチング技術を用いて、上部に強誘電体キャパシタが形成されていないWプラグ30と接続するためのコンタクトホールを形成し、この後、グルー膜101、W膜を成膜した後に、W−CMPを行い、Wプラグ100を形成する。本実施の形態では、グルー膜101は、膜厚が50nmのTiN膜により形成されている。また、W−CMPを行なった後には、N2プラズマ、350℃、120秒を施す。このWプラグ100と、前述したWプラグ30の2つにより、via-to-viaコンタクトが形成され、後述するメタル配線110から基板10までのコンタクトを形成することができる。通常のメモリに比べて、強誘電体メモリの場合では、強誘電体キャパシタが形成される分だけ段差を有しているため、メタル配線110から基板10へのコンタクトのアスペクト比が大きくなる。このため、従来のように、コンタクトを形成するための開口部を一括のエッチングにより形成しようとしても、このようなエッチング自体が困難であり、また、このような開口部を形成することができたとしても、グルー膜の埋め込み形成することも困難である。よって、この場合には、歩留りの低下を招き、また、製造コストの上昇を招く。しかしながら、本実施の形態においては、via-to-viaコンタクトを形成することにより、強誘電体メモリの歩留りを向上させることができ、製造コストを低減することが可能となる。

【0030】

次に、図3に示すように、不図示のW酸化防止膜を成膜した後、強誘電体キャパシタの上部電極70と接続するためのコンタクトホールを形成し、この後、コンタクトホールが形成された領域にメタル配線110を形成する。W酸化防止膜は、膜厚が100nmのSiONにより形成されており、W酸化防止膜を成膜した後、パターンニング、エッチングにより、強誘電体キャパシタの上部電極70と接続するためのコンタクトホールを形成する。次に、ファーネスで550℃、O2雰囲気、60分の条件で回復アニールを行ない、その後、W酸化防止膜をエッチバックにより除去する。この後、メタル配線110を形成する。

【0031】

本実施の形態では、メタル配線110は、約70nmのTiN膜、約5nmのTi膜、約400nmのAl−Cu膜、約30nmのTiN膜、約60nmのTi膜の積層膜により形成されている。メタル配線110の形成方法は、メタル配線110を形成するための上述した積層膜を成膜した後、この積層膜上に誘電体膜を形成し、誘電体膜上にメタル配線110の形状に対応したレジストパターンを形成する。この後、エッチングによりレジストパターンの形成されていない領域の誘電体膜及び積層膜を除去することにより形成する。誘電体膜としては、約30nmのSiON膜が用いられる。尚、本実施の形態においては、図3に示されるように、形成されるメタル配線110は、下層グルー膜111、配線材料膜112及び上層グルー膜113が積層されたものである。よって、本実施の形態では、約70nmのTiN膜及び約5nmのTi膜により下層グルー膜111が形成され、約400nmのAl−Cu膜により配線材料膜112が形成され、約30nmのTiN膜及び約60nmのTi膜により上層グルー膜113が形成される。

【0032】

この後、図示しないが、同様の工程を所望の回数行なうことにより、更に2層以降の層間絶縁膜、コンタクトプラグ及びメタル配線を形成して、所望の層の多層配線構造を形成し、最後に、TEOSとSiNにより形成されるカバー膜を形成する。これにより、本実施の形態における記憶装置である強誘電体キャパシタを有する強誘電体メモリを作製することができる。

【0033】

このような方法により、強誘電体膜60におけるRuの組成の異なる強誘電体キャパシタを複数作製し、1.0Vで電気的特性の測定を行なった。尚、測定のために作製された強誘電体膜60は、(Pb0.9La0.1)(Zr0.4Ti0.6−XRuX)O3(以下、RuドープPLZTと記載する)膜である。

【0034】

強誘電体膜にRuドープされていないX=0のPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.6)O3膜を用いた場合では、分極量は7.0μC/cm2であった。一方、強誘電体膜60にX=0.05のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.55Ru0.05)O3膜を用いた場合では、分極量は15.2μC/cm2であった。また、強誘電体膜60にX=0.1のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.5Ru0.1)O3膜を用いた場合では、分極量は9.2μC/cm2であった。

【0035】

このように、PLZTにRuをドープすることにより、分極量が増加することが確認された。このように作製されたこれらの強誘電体メモリのリーク電流は、いずれも10−10A程度であり、顕著な違いは見られなかった。尚、PZTやPLZTにおいてRuを過剰にドープした場合、分極が生じなくなることから、PZTまたはPLZTにドープされるRuの量は、分極量が増加する0<X≦0.1が好ましい。即ち、RuドープされたPZTをPb(Zr1−YTiY−XRuX)O3と記載する場合には、0<X≦0.1が好ましく、RuドープされたPLZTを(Pb1−ZLaZ)(Zr1−YTiY−XRuX)O3と記載する場合には、0<X≦0.1が好ましい。

【0036】

(強誘電体膜60)

本実施の形態においては、強誘電体膜60は、強誘電体膜60にドープされるRuが、PZTの粒界ではなく、PZT結晶格子中に存在していること、即ち、PZT結晶におけるPb、Zr、Tiのいずれかと置換していることが重要である。また、強誘電体膜60がPLZTの場合には、強誘電体膜60にドープされているRuはPLZTの粒界ではなく、PLZT結晶格子中に存在していること、即ち、PLZT結晶におけるPb、La、Zr、Tiのいずれかと置換していることが重要である。

【0037】

このように、RuがPZT結晶格子中に存在しているか否かは、X線異常分散回折法を用いて確認することができる。具体的には、Ruの吸収端近傍のエネルギーのX線を用いて、PZTの回折ピーク強度のエネルギー依存性を測定することにより、PZT結晶格子中にRuがドープされているか否かを判別することが可能である。

【0038】

次に、PZT結晶格子中にRuがドープされているか否かの判別方法について説明する。最初に、PZT結晶格子中にRuが存在しているか否かにより、X線回折の強度にどのような変化が生じるか、シミュレーションを行なった。異常分散の効果が現れる吸収端近傍のエネルギーでは、回折ピークの強度は、数1に示す式により表わされる。尚、(h k l)は回折ピークの指数、(x y z)は原子位置である。また、原子散乱因子fは、f=f0+Δf'+iΔf''で表され、f0は非異常分散項、Δf'は異常分散項の実部、Δf''は異常分散項の虚部を意味する。

【0039】

【数1】

【0040】

上記の数1に示される式を用いて、PZT回折強度におけるRu吸収端近傍のエネルギー依存性を求めた。PZTの格子定数は、a=b=4.015Å(0.4015nm)、c=4.034Å(0.4034nm)、α=β=γ=90°とした。原子位置は、Pbは(0 0 0)、Zr及びTiは(0.5 0.5 0.52)、酸素は、(0.5 0.5 0)と(0.5 0 0.5)と(0 0.5 0.5)とした。組成は、Ruがドープされていない場合については、Pb(Zr0.4Ti0.6)O3であり、Ruがドープされている場合については、RuはいわゆるBサイトの約5%に置換しているPb(Zr0.4Ti0.55Ru0.05)O3とした。原子散乱因子は、NIST(National Institute of Standards and Technology)のホームページ等に記載されている公知な値を用いている。尚、本実施の形態では、PZTにおいて、Pbの位置をAサイト、Zr又はTiの位置をBサイトとして記載する。

【0041】

これらの条件を用いて、PZT(100)とPZT(110)の2種類の回折ピークについて計算を行なった。尚、本実施の形態においては、PZT(100)とは、PZTの(100)、(010)、(001)のすべて含む総称であり、PZT(110)とは、PZTの(110)、(101)、(011)のすべて含む総称であるものとする。

【0042】

このシミュレーションの結果を図5に示す。図5は、15400eVの強度の回折ピークにより規格化したものである。図5(a)は、Ruがドープされていないものの結果であり、図5(b)は、RuがX=0.05ドープされているものの結果である。図5(b)に示されるように、Ruをドープすることにより、Ruの吸収端のエネルギーにおいて、PZT(100)は上に凸のピークを示し、PZT(110)は下に凸のピークを示す。尚、図5(a)においては、PZT(100)とPZT(110)とが重なっている。

【0043】

図6は、RuがドープされているPZTにおいて、Ru吸収端近傍の異常分散測定を行った結果を示すものである。図6(a)は、PZT(100)における結果であり、図6(b)はPZT(110)における結果である。Ruの吸収端のエネルギーにおいて、破線で示される直線に対して、PZT(100)は上に凸のピークを示し、PZT(110)は下に凸のピークを示していることが確認されている。図6に示される結果は、図5(b)に示されるシミュレーションによる計算結果とよく一致しており、このようにして、PZT結晶格子中にRuがドープされていることを確認することができる。

【0044】

〔第2の実施の形態〕

(記憶装置)

第2の実施の形態における記憶装置である強誘電体メモリの製造方法について、図7から図9に基づき説明する。

【0045】

最初に、図7(a)に示すように、基板となるシリコン基板等の半導体基板10の表面にMOSトランジスタ20を作製し、更に、Wプラグ30を形成する。具体的には、シリコン基板等の半導体基板10の表面に、STIにより素子分離領域11を形成し、素子分離領域11に区画された素子活性領域において、半導体基板10の表面にウェル12を形成する。次に、ゲート絶縁膜13、ゲート電極14、シリサイド層15、低濃度拡散層16、サイドウォール17及び高濃度拡散層18をウェル12の表面に形成することにより、MOSトランジスタ20を形成する。次に、MOSトランジスタ20を覆うように全面にシリコン酸窒化膜21を形成し、更に、全面にシリコン酸化膜22を例えば、有機CVDにより形成する。シリコン酸窒化膜21は、シリコン酸化膜22を形成する際のゲート絶縁膜13等の水素劣化を防ぐために形成されている。この後、各々の高濃度拡散層18に到達するコンタクトホールとなる開口部をシリコン酸化膜22及びシリコン酸窒化膜21を除去することにより形成する。次に、コンタクトホール内に50nmのTiN膜と30nmのTi膜により形成されるグルー膜31を形成し、更に、CVD法によりW膜を埋め込み、CMPを行なうことにより平坦化し、Wプラグ30を形成する。

【0046】

次に、図7(b)に示すように、強誘電体キャパシタを形成する。具体的には、シリコン酸化膜22及びWプラグ30等の表面に、密着層40を形成し、更に、下部電極50、強誘電体膜160、上部電極70の順に積層形成する。

【0047】

密着層40は、TiN/TiAlN膜により形成されている。例えば、TiN膜は、スパッタリングによりTi膜を20nmの厚さ成膜した後、窒素(N2)雰囲気中において、高速アニール)によって、650℃に加熱することにより形成する。また、TiAlN膜は、TiN膜の上に、スパッタリングにより100nmの厚さ成膜することにより形成する。

【0048】

下部電極50は、スパッタリングにより、前述した表1に示される成膜条件で、Ir膜を約200nm成膜することにより形成する。

【0049】

強誘電体膜160は、第1の強誘電体膜161と第2の強誘電体膜162により形成されており、第1の強誘電体膜161は、Ruがドープされていない約70nmのPZT膜であり、第2の強誘電体膜162は、Ruがドープされた約10nmのPZT膜である。第1の強誘電体膜161及び第2の強誘電体膜162は、スパッタリングにより、前述した表2に示される成膜条件と同様の成膜条件で成膜することにより形成する。尚、第1の強誘電体膜161は、PZT膜に、La、Ca、Sr等がドープされているもの、即ち、PLZT膜等であってもよい。また、第2の強誘電体膜162は、PZT膜に、La、Ca、Sr等がドープされているものに、更にRuがドープされているもの、即ち、RuがドープされているPLZT膜等であってもよい。

【0050】

強誘電体膜160を形成する第1の強誘電体膜161及び第2の強誘電体膜162を成膜した後、ArとO2との混合雰囲気中(O2:濃度2.5%)において、600℃の温度で90秒の急速熱処理を行なう。尚、昇温温度は、125℃/secである。このように、急速熱処理を行なうことにより、PZT膜が結晶化すると共に、ドープされているRuをPb、Zr、Tiのいずれかのサイトに置換して入れることができる。尚、急速熱処理の温度は、550℃以上、800℃以下が好ましい。550℃未満では、強誘電体膜160を所望の結晶化状態にすることができず、また、800℃を超える温度では、強誘電体膜160における酸素成分が抜けて組成ずれ等が生じる場合があるからである。本実施の形態では、スパッタリングにより、RuがドープされたPZT膜を常温で成膜した後、急速熱処理を行なう方法について説明したが、RuをPb、Zr、Tiのサイトに置換して入れることができる方法であれば、他の方法であってもよい。

【0051】

上部電極70は、急速熱処理の行なわれた強誘電体膜160上に、スパッタリングにより、前述した表3に示される成膜条件で、IrO2膜を約200nm成膜することにより形成する。

【0052】

尚、上部電極70として、Pt膜等ではなくIrO2膜を用いているのは、強誘電体膜160の水素劣化耐性を向上させるためである。Pt膜の場合、水素分子に対して触媒作用があるため、水素ラジカルが発生し、強誘電体膜160であるPZT膜を還元し劣化させやすい。これに対して、IrO2膜は触媒作用を有していないため、水素ラジカルが発生しにくく、強誘電体膜160の水素劣化耐性が格段に向上する。この後、上部電極70の成膜による強誘電体膜160へのダメージを回復するために、回復アニールを施す。本実施の形態では、例えば、ファーネスで650℃、O2雰囲気、60分の条件で行なう。

【0053】

次に、図7(c)に示すように、パターンニング、エッチング技術を用いて、スタック構造の強誘電体キャパシタを形成する。本実施の形態では、プラズマTEOS/TiNをハードマスクとして、上部電極70、第2の強誘電体膜162、第1の強誘電体膜161、下部電極50、密着層40を一括でエッチングする。これにより、所定のWプラグ30の上の領域に、下部電極50、第2の強誘電体膜162、第1の強誘電体膜161、上部電極70によりスタック構造の強誘電体キャパシタを形成することができる。このスタック構造の強誘電体キャパシタの拡大図を図10に示す。このように、強誘電体膜160における第2の強誘電体膜162は、上部電極70と接して形成される。

【0054】

次に、図8(a)に示すように、保護膜80を形成した後、ファーネスで650℃、O2雰囲気、60分の条件でアニールを行なう。この保護膜80は、プロセスにおけるダメージより強誘電体キャパシタを保護するためのものであり、本実施の形態においては、保護膜80は、膜厚50nmの酸化アルミニウム(Al2O3)膜により形成されている。

【0055】

次に、図8(b)に示すように、層間絶縁膜90を形成した後、CMPにより平坦化を行なう。具体的には、層間絶縁膜90は、HDP装置により形成された酸化膜であり、CMPは強誘電体キャパシタの上部電極70上において、層間絶縁膜90の膜厚が300nmになるまで行なう。

【0056】

次に、図8(c)に示すように、上部に強誘電体キャパシタが形成されていないWプラグ30と接続されるWプラグ100を形成する。具体的には、パターンニング、エッチング技術を用いて、上部に強誘電体キャパシタが形成されていないWプラグ30と接続するためのコンタクトホールを形成し、この後、グルー膜101、W膜を成膜した後に、W−CMPを行い、Wプラグ100を形成する。本実施の形態では、グルー膜101は、膜厚が50nmのTiN膜により形成されている。また、W−CMPを行なった後には、N2プラズマ、350℃、120秒を施す。このWプラグ100と、前述したWプラグ30の2つにより、via-to-viaコンタクトが形成され、後述するメタル配線110から基板10までのコンタクトを形成することができる。通常のメモリに比べて、強誘電体メモリの場合では、強誘電体キャパシタが形成される分だけ段差を有しているため、メタル配線110から基板10へのコンタクトのアスペクト比が大きくなる。このため、従来のように、コンタクトを形成するための開口部を一括のエッチングにより形成しようとしても、このようなエッチング自体が困難であり、また、このような開口部を形成することができたとしても、グルー膜の埋め込み形成することも困難である。よって、この場合には、歩留りの低下を招き、また、製造コストの上昇を招く。しかしながら、本実施の形態においては、via-to-viaコンタクトを形成することにより、強誘電体メモリの歩留りを向上させることができ、製造コストを低減することが可能となる。

【0057】

次に、図9に示すように、不図示のW酸化防止膜を成膜した後、強誘電体キャパシタの上部電極70と接続するためのコンタクトホールを形成し、この後、コンタクトホールが形成された領域にメタル配線110を形成する。W酸化防止膜は、膜厚が100nmのSiONにより形成されており、W酸化防止膜を成膜した後、パターンニング、エッチングにより、強誘電体キャパシタの上部電極70と接続するためのコンタクトホールを形成する。次に、ファーネスで550℃、O2雰囲気、60分の条件で回復アニールを行ない、その後、W酸化防止膜をエッチバックにより除去する。この後、メタル配線110を形成する。

【0058】

本実施の形態では、メタル配線110は、約70nmのTiN膜、約5nmのTi膜、約400nmのAl−Cu膜、約30nmのTiN膜、約60nmのTi膜の積層膜により形成されている。具体的には、メタル配線110の形成方法は、メタル配線110を形成するための上述した積層膜を成膜した後、この積層膜上に誘電体膜を形成し、誘電体膜上にメタル配線110の形状に対応したレジストパターンを形成する。この後、エッチングによりレジストパターンの形成されていない領域の誘電体膜及び積層膜を除去することにより形成する。誘電体膜としては、約30nmのSiON膜が用いられる。尚、本実施の形態においては、図9に示されるように、形成されるメタル配線110は、下層グルー膜111、配線材料膜112及び上層グルー膜113が積層されたものである。よって、本実施の形態では、約70nmのTiN膜及び約5nmのTi膜により下層グルー膜111が形成され、約400nmのAl−Cu膜により配線材料膜112が形成され、約30nmのTiN膜及び約60nmのTi膜により上層グルー膜113が形成される。

【0059】

この後、図示しないが、同様の工程を所望の回数行なうことにより、更に2層以降の層間絶縁膜、コンタクトプラグ及びメタル配線を形成して所望の層の多層配線構造を形成し、最後に、TEOSとSiNにより形成されるカバー膜を形成する。これにより、本実施の形態における記憶装置である強誘電体キャパシタを有する強誘電体メモリを作製することができる。

【0060】

このような方法により、第2の強誘電体膜162におけるRuの組成の異なる強誘電体キャパシタを複数作製し、1.0Vで電気的特性の測定を行なった。尚、測定のために作製された第2の強誘電体膜162は、RuドープPLZT膜であり、第1の強誘電体膜161は、RuドープされていないPLZT膜である。

【0061】

第1の強誘電体膜及び第2の強誘電体膜に相当する強誘電体膜をともに、RuドープされていないPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.6)O3膜により形成した場合では、分極量は7.0μC/cm2であった。一方、第2の強誘電体膜162にX=0.05のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.55Ru0.05)O3膜を用いた場合では、分極量は18.3μC/cm2であった。

【0062】

第1の強誘電体膜161をRuドープされていないPLZT膜により形成し、第2の強誘電体膜162をRuドープPLZT膜により形成することにより、より一層分極量が増加することが確認された。このように作製されたこれらの強誘電体メモリのリーク電流は、いずれも10−10A程度であり、顕著な違いは見られなかった。

【0063】

尚、上記以外の内容については、第1の実施の形態と同様である。

【0064】

〔第3の実施の形態〕

次に、第3の実施の形態について説明する。本実施の形態は、図11及び図12に示すように、強誘電体膜260は、第1の強誘電体膜261と第2の強誘電体膜262を有しており、RuドープPLZT膜である第2の強誘電体膜262が下部電極50と接して形成されている。尚、図12は、本実施の形態における強誘電体メモリにおけるスタック構造の強誘電体キャパシタの拡大図を示す。

【0065】

具体的には、本実施の形態においては、下部電極50上に第2の強誘電体膜262、第1の強誘電体膜261がこの順で積層形成されており、第1の強誘電体膜261上に上部電極70が形成されている。第1の強誘電体膜261は、Ruがドープされていない約70nmのPZT膜であり、第2の強誘電体膜262は、Ruがドープされた約10nmのPZT膜である。尚、第1の強誘電体膜261及び第2の強誘電体膜262は、第2の実施の形態と同様の成膜方法及び成膜条件により形成することができる。また、本実施の形態における記憶装置である強誘電体メモリの製造方法は、強誘電体膜260を除き、第2の実施の形態と同様である。

【0066】

本実施の形態における記憶装置における強誘電体キャパシタとして、第2の強誘電体膜262におけるRuの組成の異なる強誘電体キャパシタを作製し、1.0Vで電気的特性の測定を行なった。尚、測定のために作製された第2の強誘電体膜262は、RuドープPLZT膜であり、第1の強誘電体膜261は、RuドープされていないPLZT膜である。

【0067】

第1の強誘電体膜及び第2の強誘電体膜に相当する強誘電体膜をともに、RuドープされていないPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.6)O3膜により形成した場合では、分極量は7.0μC/cm2であった。一方、第2の強誘電体膜262にX=0.05のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.55Ru0.05)O3膜を用いた場合では、分極量は16.3μC/cm2であった。

【0068】

第1の強誘電体膜261をRuドープされていないPLZT膜により形成し、第2の強誘電体膜262をRuドープPLZT膜により形成することにより、より一層分極量が増加することが確認された。このように作製されたこれらの強誘電体メモリのリーク電流は、いずれも10−10A程度であり、顕著な違いは見られなかった。

【0069】

尚、本実施の形態においては、下部電極50上にRuドープPZT膜等が形成されているものであるため、下部電極50上のPZT結晶の配位方向のばらつきについて、第1及び第2の実施の形態と比較を行った。この結果、本実施の形態における(111)回折ピークにおけるロッキングカーブの半値幅は、3.8°であったのに対し、第1の実施の形態及び第2の実施の形態における(111)回折ピークにおけるロッキングカーブの半値幅は、4.5°であった。PZT結晶の配位方向のばらつきの減少は、分極量のばらつきが減少することを意味している。つまり、強誘電体キャパシタのサイズが小さくなり、1つのキャパシタあたりの結晶粒の数が少なくなったときに、分極量がキャパシタ毎に一様になる効果が期待できる。よって、本実施の形態における記憶装置である強誘電体メモリは、より一層均一性を高め、歩留りを向上させることができる。

【0070】

尚、上記以外の内容については、第2の実施の形態と同様である。

【0071】

〔第4の実施の形態〕

次に、第4の実施の形態について説明する。本実施の形態は、図13及び図14に示すように、強誘電体膜360は、第1の強誘電体膜361と第2の強誘電体膜362と第3の強誘電体膜363を有している。また、RuドープPLZT膜である第2の強誘電体膜362が下部電極50と接して形成されており、RuドープPLZT膜である第3の強誘電体膜363が上部電極70と接して形成されている。尚、図14は、本実施の形態における強誘電体メモリにおけるスタック構造の強誘電体キャパシタの拡大図を示す。

【0072】

具体的には、本実施の形態においては、下部電極50上に第2の強誘電体膜362、第1の強誘電体膜361、第3の強誘電体膜363が、この順で積層形成されており、第3の強誘電体膜363上に上部電極70が形成されている。第1の強誘電体膜361は、Ruがドープされていない約60nmのPZT膜であり、第2の強誘電体膜362及び第3の強誘電体膜363は、Ruがドープされた約10nmのPZT膜である。尚、第1の強誘電体膜361、第2の強誘電体膜362及び第3の強誘電体膜363は、第2の実施の形態と同様の成膜方法及び成膜条件により形成することができる。また、本実施の形態における記憶装置である強誘電体メモリの製造方法は、強誘電体膜360を除き、第2の実施の形態と同様である。

【0073】

本実施の形態における記憶装置における強誘電体キャパシタとして、第2の強誘電体膜362及び第3の強誘電体膜363におけるRuの組成の異なる強誘電体キャパシタを作製し、1.0Vで電気的特性の測定を行なった。尚、測定のために作製された第2の強誘電体膜362及び第3の強誘電体膜363は、RuドープPLZT膜であり、第1の強誘電体膜361は、RuドープされていないPLZT膜である。

【0074】

第1の強誘電体膜、第2の強誘電体膜及び第3の強誘電体膜に相当する強誘電体膜をRuドープされていないPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.6)O3膜により形成した場合では、分極量は7.0μC/cm2であった。一方、第2の強誘電体膜362及び第3の強誘電体膜363にX=0.05のRuドープPLZT膜、即ち、(Pb0.9La0.1)(Zr0.4Ti0.55Ru0.05)O3膜を用いた場合では、分極量は17.8μC/cm2であった。

【0075】

第1の強誘電体膜361をRuドープされていないPLZT膜により形成し、第1の強誘電体膜361の両側に、第2の強誘電体膜362及び第3の強誘電体膜363をRuドープPLZT膜により形成することにより、より一層分極量が増加することが確認された。このように作製されたこれらの強誘電体メモリのリーク電流は、いずれも10−10A程度であり、顕著な違いは見られなかった。

【0076】

尚、本実施の形態においては、下部電極50上にRuドープPZT膜等が形成されているものであるため、下部電極50上のPZT結晶の配位方向のばらつきについて、第1及び第2の実施の形態と比較を行った。この結果、本実施の形態における(111)回折ピークにおけるロッキングカーブの半値幅は、3.8°であったのに対し、第1の実施の形態及び第2の実施の形態における(111)回折ピークにおけるロッキングカーブの半値幅は、4.5°であった。PZT結晶の配位方向のばらつきの減少は、分極量のばらつきが減少することを意味している。つまり、強誘電体キャパシタのサイズが小さくなり、1つのキャパシタあたりの結晶粒の数が少なくなったときに、分極量がキャパシタ毎に一様になる効果が期待できる。よって、本実施の形態における記憶装置である強誘電体メモリは、より一層均一性を高め、歩留りを向上させることができる。

【0077】

尚、上記以外の内容については、第2の実施の形態と同様である。

【0078】

以上、実施の形態について詳述したが、特定の実施形態に限定されるものではなく、特許請求の範囲に記載された範囲内において、種々の変形及び変更が可能である。

【0079】

上記の説明に関し、更に以下の付記を開示する。

(付記1)

基板の上に形成された下部電極と、

前記下部電極上に形成された強誘電体膜と、

前記強誘電体膜上に形成された上部電極と、

を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、

前記第2の強誘電体膜は、PbZrTiO3を含む材料にRuがドープされているものにより形成されており、

前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする記憶装置。

(付記2)

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛にLa、Ca、Srのうちから選ばれる1または2以上の元素が含まれる材料により形成されており、

前記第2の強誘電体膜は、チタン酸ジルコン酸鉛にLa、Ca、Srのうちから選ばれる1または2以上の元素が含まれる材料に、Ruがドープされているものより形成されていることを特徴とする付記1に記載の記憶装置。

(付記3)

前記第2の強誘電体膜は、前記下部電極または前記上部電極と接していることを特徴とする付記1または2に記載の記憶装置。

(付記4)

前記強誘電体膜は、更に、第3の強誘電体膜を有するものであって、

前記第3の強誘電体膜はチタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記Ruは前記第3の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、

前記第1の強誘電体膜の一方の面に前記第2の強誘電体膜が設けられており、前記第1の強誘電体膜の他方の面に前記第3の強誘電体膜が設けられていることを特徴とする付記1または2に記載の記憶装置。

(付記5)

前記第3の強誘電体膜は、チタン酸ジルコン酸鉛にLa、Ca、Srのうちから選ばれる1または2以上の元素が含まれる材料に、Ruがドープされているものであることを特徴とする付記4に記載の記憶装置。

(付記6)

前記第2の強誘電体膜は前記下部電極と接しており、前記第3の強誘電体膜は前記上部電極と接していることを特徴とする付記4または5に記載の記憶装置。

(付記7)

基板の上に形成された下部電極と、

前記下部電極上に形成された強誘電体膜と、

前記強誘電体膜上に形成された上部電極と、

を有し、前記強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされており、

前記Ruは、前記強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、

前記強誘電体膜をPb(Zr1−YTiY−XRuX)O3とした場合、0<X≦0.1であることを特徴とする記憶装置。

(付記8)

前記強誘電体膜は、チタン酸ジルコン酸鉛にLa、Ca、Srのうちから選ばれる1または2以上の元素が含まれる材料に、Ruがドープされているものであることを特徴とする付記7に記載の記憶装置。

(付記9)

前記基板上にはトランジスタが形成されており、

前記下部電極または前記上部電極は、前記トランジスタと接続されていることを特徴とする付記1から8のいずれかに記載の記憶装置。

(付記10)

前記下部電極は、前記トランジスタの上方に形成されていることを特徴とする付記9に記載の記憶装置。

(付記11)

基板の上に、下部電極を形成する工程と、

前記下部電極上に、強誘電体膜を形成する工程と、

前記強誘電体膜を形成した後、前記強誘電体膜を結晶化させる熱処理を行なう工程と、

前記熱処理の行なわれた前記強誘電体膜上に、上部電極を形成する工程と、

を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とが積層されたものであって、

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、

前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されているものであることを特徴とする記憶装置の製造方法。

(付記12)

前記強誘電体膜を形成する工程は、

前記下部電極上に、前記第2の強誘電体膜を形成する工程と、

前記第2の強誘電体膜上に、前記第1の強誘電体膜を形成する工程と、

前記第1の強誘電体膜上に、第3の強誘電体膜を形成する工程と、

を有するものであって、

前記上部電極は、前記第3の強誘電体膜上に形成されるものであって、

前記第3の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されているものであることを特徴とする付記11に記載の記憶装置の製造方法。

(付記13)

前記基板にトランジスタを形成する工程と、

前記トランジスタの上に層間絶縁膜を形成し、前記層間絶縁膜に開口部を形成し、前記開口部にW膜を形成することにより、前記トランジスタに接続されるWプラグを形成する工程と、

を有し、前記下部電極を形成する工程は、前記Wプラグの上部に、前記下部電極を形成するものであることを特徴とする付記11または12に記載の記憶装置の製造方法。

【符号の説明】

【0080】

10 半導体基板

11 素子分離領域

12 ウェル

13 ゲート絶縁膜

14 ゲート電極

15 シリサイド層

16 低濃度拡散層

17 サイドウォール

18 高濃度拡散層

20 MOSトランジスタ

21 シリコン酸窒化膜

22 シリコン酸化膜

30 Wプラグ

31 グルー膜

40 密着層

50 下部電極

60 強誘電体膜

70 上部電極

80 保護膜

90 層間絶縁膜

100 Wプラグ

110 メタル配線

111 下層グルー膜

112 配線材料膜

113 上層グルー膜

160 強誘電体膜

161 第1の強誘電体膜

162 第2の強誘電体膜

260 強誘電体膜

261 第1の強誘電体膜

262 第2の強誘電体膜

360 強誘電体膜

361 第1の強誘電体膜

362 第2の強誘電体膜

363 第3の強誘電体膜

【特許請求の範囲】

【請求項1】

基板の上に形成された下部電極と、

前記下部電極上に形成された強誘電体膜と、

前記強誘電体膜上に形成された上部電極と、

を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、

前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、

前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする記憶装置。

【請求項2】

前記第2の強誘電体膜は前記下部電極または前記上部電極と接していることを特徴とする請求項1に記載の記憶装置。

【請求項3】

前記強誘電体膜は、更に、第3の強誘電体膜を有するものであって、

前記第3の強誘電体膜はチタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記Ruは前記第3の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、

前記第1の強誘電体膜の一方の面に前記第2の強誘電体膜が設けられており、前記第1の強誘電体膜の他方の面に前記第3の強誘電体膜が設けられていることを特徴とする請求項1に記載の記憶装置。

【請求項4】

前記第2の強誘電体膜は前記下部電極と接しており、前記第3の強誘電体膜は前記上部電極と接していることを特徴とする請求項3に記載の記憶装置。

【請求項5】

基板の上に形成された下部電極と、

前記下部電極上に形成された強誘電体膜と、

前記強誘電体膜上に形成された上部電極と、

を有し、前記強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされており、

前記Ruは、前記強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、

前記強誘電体膜をPb(Zr1−YTiY−XRuX)O3とした場合、0<X≦0.1であることを特徴とする記憶装置。

【請求項6】

基板の上に、下部電極を形成する工程と、

前記下部電極上に、強誘電体膜を形成する工程と、

前記強誘電体膜を形成した後、前記強誘電体膜を結晶化させる熱処理を行なう工程と、

前記熱処理の行なわれた前記強誘電体膜上に、上部電極を形成する工程と、

を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とが積層されたものであって、

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、

前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されているものであることを特徴とする記憶装置の製造方法。

【請求項1】

基板の上に形成された下部電極と、

前記下部電極上に形成された強誘電体膜と、

前記強誘電体膜上に形成された上部電極と、

を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、

前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、

前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする記憶装置。

【請求項2】

前記第2の強誘電体膜は前記下部電極または前記上部電極と接していることを特徴とする請求項1に記載の記憶装置。

【請求項3】

前記強誘電体膜は、更に、第3の強誘電体膜を有するものであって、

前記第3の強誘電体膜はチタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記Ruは前記第3の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、

前記第1の強誘電体膜の一方の面に前記第2の強誘電体膜が設けられており、前記第1の強誘電体膜の他方の面に前記第3の強誘電体膜が設けられていることを特徴とする請求項1に記載の記憶装置。

【請求項4】

前記第2の強誘電体膜は前記下部電極と接しており、前記第3の強誘電体膜は前記上部電極と接していることを特徴とする請求項3に記載の記憶装置。

【請求項5】

基板の上に形成された下部電極と、

前記下部電極上に形成された強誘電体膜と、

前記強誘電体膜上に形成された上部電極と、

を有し、前記強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされており、

前記Ruは、前記強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであって、

前記強誘電体膜をPb(Zr1−YTiY−XRuX)O3とした場合、0<X≦0.1であることを特徴とする記憶装置。

【請求項6】

基板の上に、下部電極を形成する工程と、

前記下部電極上に、強誘電体膜を形成する工程と、

前記強誘電体膜を形成した後、前記強誘電体膜を結晶化させる熱処理を行なう工程と、

前記熱処理の行なわれた前記強誘電体膜上に、上部電極を形成する工程と、

を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とが積層されたものであって、

前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、

前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されているものであることを特徴とする記憶装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−48170(P2013−48170A)

【公開日】平成25年3月7日(2013.3.7)

【国際特許分類】

【出願番号】特願2011−186134(P2011−186134)

【出願日】平成23年8月29日(2011.8.29)

【出願人】(000005223)富士通株式会社 (25,993)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年3月7日(2013.3.7)

【国際特許分類】

【出願日】平成23年8月29日(2011.8.29)

【出願人】(000005223)富士通株式会社 (25,993)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]