設計支援プログラム、設計支援装置、および設計支援方法

【課題】回路の内部構成を意識することなく、LSIの消費電力の低減化および面積削減を図ること。

【解決手段】併合回路ABでは、組み合わせ回路LA0〜LA2と組み合わせ回路LB0〜LB2とが排他的な動作をするように、選択回路200〜202を挿入する。そして、選択回路200〜202の出力先にFF0〜FF2を接続する。併合回路ABでは、選択信号S=0のとき、組み合わせ回路LA0〜LA2が動作し、S=1のとき、組み合わせ回路LB0〜LB2が動作する。このように、組み合わせ回路LA0〜LA2,LB0〜LB2とFFA0〜FFA2,FFB0〜FFB2の接続関係さえ分かっていれば、その内部構成を意識する必要はない。

【解決手段】併合回路ABでは、組み合わせ回路LA0〜LA2と組み合わせ回路LB0〜LB2とが排他的な動作をするように、選択回路200〜202を挿入する。そして、選択回路200〜202の出力先にFF0〜FF2を接続する。併合回路ABでは、選択信号S=0のとき、組み合わせ回路LA0〜LA2が動作し、S=1のとき、組み合わせ回路LB0〜LB2が動作する。このように、組み合わせ回路LA0〜LA2,LB0〜LB2とFFA0〜FFA2,FFB0〜FFB2の接続関係さえ分かっていれば、その内部構成を意識する必要はない。

【発明の詳細な説明】

【技術分野】

【0001】

本開示技術は、LSI(Large Scale Integration)の設計を支援する設計支援プログラム、設計支援装置、および設計支援方法に関する。

【背景技術】

【0002】

LSIには、ブロックと呼ばれる機能モジュールが多数搭載されている。LSIに搭載された複数のブロックには、選択信号によって動作モードが使用/未使用に切り替わるものがある。選択信号によって未使用とされたブロックであっても、LSI上である程度の面積を占めており、またある程度の待機電流を消費している。未使用ブロックの消費電流削減方法は、クロックゲートによりクロック端子を制御する程度であったが、これではリーク電流低減や面積削減には繋がらない。また、消費電力の低減および面積削減のため、排他的に動作する複数のブロックから共有化できる資産情報を抜き出す技術が開示されている(たとえば、下記特許文献1を参照。)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2000−123059号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来技術では、まず、共有化に先だって、資産情報を抜き出すためにブロック内の内部構成を認識しなければならないという問題があった。特に、ブロック内に組み合わせ回路がある場合、組み合わせ回路の複雑度に比例して資産情報の抜き出しが困難であったり、できるとしても長期化したりするという問題があった。

【0005】

本開示技術は、上述した従来技術による問題点を解消するため、回路の内部構成を意識することなく、LSIの消費電力の低減化および面積削減を図ることができる設計支援プログラム、設計支援装置、および設計支援方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上述した課題を解決し、目的を達成するため、第1の開示技術は、排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、前記一方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「一方のパス情報」)と、前記他方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「他方のパス情報」)と、を入力し、入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成し、対象となる共通化テーブル群を参照することにより、前記対象となる共通化テーブルごとに、当該前記他方のパス情報内の前記他方の識別情報を前記一方の識別情報に変換し、前記一方のパス情報および変換後の他方のパス情報内における、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値を、前記共通化テーブルごとに算出し、算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成し、作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定し、設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択し、選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成することを要件とする。

【0007】

第2の開示技術は、排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、を入力し、入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成し、対象となる共通化テーブル群内の共通化テーブルごとに、当該共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した仮併合回路の回路情報を生成し、前記対象となる共通化テーブル群内の共通化テーブルごとに生成された前記仮併合回路の回路情報の論理合成結果を取得し、取得された前記仮併合回路の回路情報ごとの論理合成結果から得られる前記仮併合回路に関する面積情報に基づいて、論理合成による論理圧縮度合いをあらわす評価値を、前記対象となる共通化テーブル群内の共通化テーブルごとに算出し、算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成し、作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定し、設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択し、選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成することを要件とする。

【発明の効果】

【0008】

本設計支援プログラム、設計支援装置、および設計支援方法によれば、回路の内部構成を意識することなく、LSIの消費電力の低減化および面積削減を図ることができるという効果を奏する。

【図面の簡単な説明】

【0009】

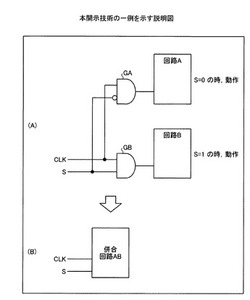

【図1】本開示技術の一例を示す説明図である。

【図2】図1(B)に示したマージの具体例を図形化した説明図である。

【図3】実施の形態1にかかる設計支援装置のハードウェア構成を示すブロック図である。

【図4−1】実施の形態1にかかる設計支援装置の機能的構成1を示すブロック図である。

【図4−2】実施の形態1にかかる設計支援装置の機能的構成2を示すブロック図である。

【図5】排他動作情報を示す説明図である。

【図6−1】FF情報抽出部によって抽出された回路Aに関するFF情報の一例を示す説明図である。

【図6−2】FF情報抽出部によって抽出された回路Bに関するFF情報の一例を示す説明図である。

【図7−1】パス情報抽出部によって抽出された回路Aに関するパス情報を示す説明図である。

【図7−2】パス情報抽出部によって抽出された回路Bに関するパス情報を示す説明図である。

【図8−1】回路AのFF情報に関するラベル化FF情報を示す説明図である。

【図8−2】回路BのFF情報に関するラベル化FF情報を示す説明図である。

【図9】第1世代の共通化テーブル群の一例を示す説明図である。

【図10−1】図7−1に示した回路Aのパス情報のラベル変換例を示す説明図である。

【図10−2】図7−2に示した回路Bのパス情報のラベル変換例を示す説明図である。

【図11−1】回路Aのパス情報をラベル化したラベル化パス情報を示す説明図である。

【図11−2】回路Bのパス情報をラベル化したラベル化パス情報を示す説明図である。

【図12】ラベル化パス情報の置換処理を示す説明図である。

【図13】カウント処理による計数テーブルを示す説明図である。

【図14】シグマスケーリング処理結果を示す説明図である。

【図15】選択処理の内容を示す説明図である。

【図16】次世代の親となる共通化テーブルを示す説明図である。

【図17】交叉の一例を示す説明図である。

【図18】突然変異の処理内容を示す説明図である。

【図19】次世代の共通化テーブル群を示す説明図である。

【図20】併合回路ABの接続イメージを示す説明図である。

【図21】共通化FFとセレクタの共通回路情報を示す説明図である。

【図22】出力ネット置換テーブルを示す説明図である。

【図23】回路Aの固有化前後の回路情報を示す説明図である。

【図24】回路Bの固有化前後の回路情報を示す説明図である。

【図25】併合回路ABの回路情報を示す説明図である。

【図26】実施の形態1にかかる設計支援装置の設計支援処理手順を示すフローチャートである。

【図27】図26に示した共通化テーブル評価/次世代作成処理(ステップS2605)の詳細な処理手順を示すフローチャートである。

【図28】図27に示した次世代作成処理(ステップS2706)の詳細な処理手順を示すフローチャートである。

【図29】図26に示したマージ処理(ステップS2606)の詳細な処理手順を示すフローチャートである。

【図30−1】実施の形態2にかかる設計支援装置の機能的構成1を示すブロック図である。

【図30−2】実施の形態2にかかる設計支援装置の機能的構成2を示すブロック図である。

【図31】セル面積を対応付けた第1世代の共通化テーブルを示す説明図である。

【図32】シグマスケーリング処理結果を示す説明図である。

【図33】実施の形態2にかかる設計支援装置の設計支援処理手順を示すフローチャートである。

【図34】図33に示した仮マージ処理(ステップS3304)の詳細な処理手順を示すフローチャートである。

【図35】図33に示した仮論理合成結果取得処理(ステップS3305)の詳細な処理手順を示すフローチャートである。

【発明を実施するための形態】

【0010】

以下に添付図面を参照して、本開示技術にかかる設計支援装置、設計支援方法、および設計支援プログラムの好適な実施の形態を詳細に説明する。

【0011】

<実施の形態1>

図1は、本開示技術の一例を示す説明図である。本開示技術は、排他的に動作しあう2つのブロックを1つのブロックにマージする技術である。(A)は、排他的に動作しあう回路を示している。回路Aは、クロックゲートGAにより動作制御されるブロックであり、回路Bは、クロックゲートGBにより動作制御されるブロックである。クロック信号CLKは選択信号Sに応じて回路Aまたは回路Bに供給される。これにより、回路Aおよび回路Bは排他的な動作をする。すなわち、回路Aが動作中であれば、回路Bは動作せず、回路Bが動作中であれば、回路Aは動作しない。

【0012】

図2は、図1(B)に示したマージの具体例を図形化した説明図である。図の簡略化のため、クロック信号CLKは省略している。回路Aは、組み合わせ回路LA0とその出力を保持して回路Aから出力するフリップフロップなどのデータ保持素子(以下、「FF」とする)FFA0を有する。また、回路Aは、組み合わせ回路LA1とその出力を保持して回路Aから出力するFFA1を有する。また、回路Aは、組み合わせ回路LA2とその出力を保持して回路Aから出力するFFA2を有する。

【0013】

回路Bは、組み合わせ回路LB0とその出力を保持して回路Bから出力するFFB0を有する。また、回路Bは、組み合わせ回路LB1とその出力を保持して回路Bから出力するFFB1を有する。また、回路Bは、組み合わせ回路LB2とその出力を保持して回路Bから出力するFFB2を有する。

【0014】

回路Aと回路Bは排他的な動作をするため、回路Aが動作するとは、その内部の組み合わせ回路LA0〜LA2が動作していることを意味しており、回路Bが動作するとは、その内部の組み合わせ回路LB0〜LB2が動作していることを意味している。

【0015】

したがって、併合回路ABでは、組み合わせ回路LA0〜LA2と組み合わせ回路LB0〜LB2とが排他的な動作をするように、選択回路200〜202を挿入する。そして、選択回路200〜202の出力先にFF0〜FF2を接続する。併合回路ABでは、選択信号S=0のとき、組み合わせ回路LA0〜LA2が動作し、S=1のとき、組み合わせ回路LB0〜LB2が動作する。

【0016】

このように、組み合わせ回路LA0〜LA2,LB0〜LB2とFFA0〜FFA2,FFB0〜FFB2の接続関係さえ分かっていれば、組み合わせ回路LA0〜LA2,LB0〜LB2の内部構成を意識する必要はない。また、マージ前の回路Aおよび回路Bと併合回路ABを比較すると、FFA0,FFB0がマージされてFF0となる。同様に、FFA1,FFB1がマージされてFF1となり、FFA2,FFB2がマージされてデータ保持素子FF2となる。

【0017】

このあと、論理合成ツールにより併合回路ABを論理圧縮することで、併合回路ABの回路規模が縮小化する。このように、本開示技術では、回路Aおよび回路Bの組み合わせ回路LA0〜LA2,LB0〜LB2の内部構成を意識しないアルゴリズムにより併合回路ABを生成して、リーク電流の低減化と回路面積の削減を図ることができる。

【0018】

(設計支援装置のハードウェア構成)

図3は、実施の形態1にかかる設計支援装置のハードウェア構成を示すブロック図である。図3において、設計支援装置は、CPU(Central Processing Unit)301と、ROM(Read‐Only Memory)302と、RAM(Random Access Memory)303と、磁気ディスクドライブ304と、磁気ディスク305と、光ディスクドライブ306と、光ディスク307と、ディスプレイ308と、I/F(Interface)309と、キーボード310と、マウス311と、スキャナ312と、プリンタ313と、を備えている。また、各構成部はバス300によってそれぞれ接続されている。

【0019】

ここで、CPU301は、設計支援装置の全体の制御を司る。ROM302は、ブートプログラムなどのプログラムを記憶している。RAM303は、CPU301のワークエリアとして使用される。磁気ディスクドライブ304は、CPU301の制御にしたがって磁気ディスク305に対するデータのリード/ライトを制御する。磁気ディスク305は、磁気ディスクドライブ304の制御で書き込まれたデータを記憶する。

【0020】

光ディスクドライブ306は、CPU301の制御にしたがって光ディスク307に対するデータのリード/ライトを制御する。光ディスク307は、光ディスクドライブ306の制御で書き込まれたデータを記憶したり、光ディスク307に記憶されたデータをコンピュータに読み取らせたりする。

【0021】

ディスプレイ308は、カーソル、アイコンあるいはツールボックスをはじめ、文書、画像、機能情報などのデータを表示する。このディスプレイ308は、たとえば、CRT、TFT液晶ディスプレイ、プラズマディスプレイなどを採用することができる。

【0022】

インターフェース(以下、「I/F」と略する。)309は、通信回線を通じてLAN(Local Area Network)、WAN(Wide Area Network)、インターネットなどのネットワーク314に接続され、このネットワーク314を介して他の装置に接続される。そして、I/F309は、ネットワーク314と内部のインターフェースを司り、外部装置からのデータの入出力を制御する。I/F309には、たとえばモデムやLANアダプタなどを採用することができる。

【0023】

キーボード310は、文字、数字、各種指示などの入力のためのキーを備え、データの入力をおこなう。また、タッチパネル式の入力パッドやテンキーなどであってもよい。マウス311は、カーソルの移動や範囲選択、あるいはウィンドウの移動やサイズの変更などをおこなう。ポインティングデバイスとして同様に機能を備えるものであれば、トラックボールやジョイスティックなどであってもよい。

【0024】

スキャナ312は、画像を光学的に読み取り、設計支援装置内に画像データを取り込む。なお、スキャナ312は、OCR(Optical Character Reader)機能を持たせてもよい。また、プリンタ313は、画像データや文書データを印刷する。プリンタ313には、たとえば、レーザプリンタやインクジェットプリンタを採用することができる。

【0025】

(設計支援装置の機能的構成)

図4−1は、実施の形態1にかかる設計支援装置の機能的構成1を示すブロック図である。図4−1において、設計支援装置400は、入力部401と、第1の作成部402と、評価関数情報作成部403と、共通化テーブル評価/再作成部404と、併合部405と、置換テーブル作成部406と、置換部407と、取得部408と、を備える。また、共通化テーブル評価/再作成部404の詳細は図4−2に示す。図4−1の各機能は、具体的には、たとえば、図3に示したROM302、RAM303、磁気ディスク305に記憶されたプログラムをCPU301に実行させることにより、またはI/F309により、その機能を実現する。

【0026】

また、設計支援装置400に与えられる初期情報として、互いに排他的動作をしあう回路Aおよび回路Bの回路情報(たとえば、ネットリストやRTL(Register Transfer Level)記述)DA,DBと、回路Aおよび回路Bの排他動作情報とを用意する。

【0027】

図5は、排他動作情報を示す説明図である。排他動作情報とは、互いに排他的に動作する回路の組み合わせを示す情報である。回路A項目と回路B項目には、それぞれの回路を一意に特定する識別情報が記憶されている。たとえば、1行目のレコードでは、回路C1と回路C2とが排他的に動作することを示している。設計者は、排他動作情報を参照して、回路A項目の回路(たとえば、回路C1)の回路情報と回路B項目の回路(たとえば、回路C2)の回路情報を設計支援装置に与える。

【0028】

図4−1に戻って、入力部401は、FF情報抽出部411と、パス情報抽出部412とを備える。FF情報抽出部411は、回路Aおよび回路Bに含まれているFFを回路情報DA,DBから抽出する機能を有する。具体的には、たとえば、FF情報抽出部411は既存のツールにより構成され、回路Aおよび回路Bに含まれているFFのインスタンス情報となるFF情報を回路情報DA,DBから抽出する。

【0029】

図6−1は、FF情報抽出部411によって抽出された回路Aに関するFF情報の一例を示す説明図である。図6−1に示したFF情報600Aには、回路Aに含まれているFFのインスタンス名(たとえば、“AAA_inst/ac01_reg/CLK”)が記述されている。

【0030】

図6−2は、FF情報抽出部411によって抽出された回路Bに関するFF情報の一例を示す説明図である。図6−2に示したFF情報600Bには、回路Bに含まれているFFのインスタンス名(たとえば、“BBB_inst/div01_reg/CLK”)が記述されている。

【0031】

また、図4−1において、パス情報抽出部412は、回路Aおよび回路Bに含まれているパスを回路情報DA,DBから抽出する機能を有する。具体的には、たとえば、パス情報抽出部412は既存のツールにより構成され、回路Aおよび回路Bに含まれているパス情報DPA,DPBを回路情報DA,DBから抽出する。パス情報DPA,DPBとは、パスの始点となるFFのインスタンス名とパスの終点となるFFのインスタンス名との組み合わせである。

【0032】

図7−1は、パス情報抽出部412によって抽出された回路Aに関するパス情報DPAを示す説明図である。図7−1に示したパス情報DPAには、出力先(図7−1では“Endpoint”と表記)となるFFのインスタンス名と、入力元(図7−1では“Startpoint”と表記)となるFFのインスタンス名を記憶している。

【0033】

図7−2は、パス情報抽出部412によって抽出された回路Bに関するパス情報DPBを示す説明図である。図7−2に示したパス情報DPBには、終点(図7−2では“Endpoint”と表記)となるFFのインスタンス名と、始点(図7−2では“Startpoint”と表記)となるFFのインスタンス名を記憶している。

【0034】

このように、入力部401により回路AのFF情報DFAおよびパス情報DPA、回路BのFF情報DFBおよびパス情報DPBを得ることができる。なお、回路情報DA,DBからの抽出ではなく、回路AのFF情報DFAおよびパス情報DPA、回路BのFF情報DFBおよびパス情報DPBを外部から入力することとしてもよい。

【0035】

図4−1において、第1の作成部402は、FF情報DFA,DFBから第1世代の共通化テーブル群T1を作成する機能を有する。第1世代の共通化テーブル群T1とは、回路AのFFと回路BのFFとの対応関係を定義するテーブルの集合である。第1世代としたのは、後述するように、第n世代までの共通化テーブル群Tnを作成するからである。

【0036】

第1世代の共通化テーブル群T1は、具体的には、たとえば、まず、入力されたFF情報DFA,DFBについて、回路A,B別にFFのインスタンスごとに固有のラベルを割り振る。ラベルは連続番号とする。また、入力ネットと出力ネットも回路情報DA,DBから抽出する。入力ネットとは、FFのデータ入力端子に接続されているネットである。また、出力ネットとは、FFのデータ出力端子に接続されているネットである。このように、FFごとにインスタンス名、入力ネット、出力ネット、ラベルを記述した情報を、ラベル化FF情報と称す。

【0037】

図8−1は、回路AのFF情報に関するラベル化FF情報を示す説明図である。ラベル化FF情報800Aにおいて、回路AのFFには、ラベル項目にラベルA0〜A9が割り当てられている。

【0038】

図8−2は、回路BのFF情報に関するラベル化FF情報を示す説明図である。ラベル化FF情報800Bにおいて、回路BのFFには、ラベル項目にラベルB0〜B7が割り当てられている。第1の作成部402は、ラベル化FF情報800A,800Bから第1世代の共通化テーブル群T1を作成する。

【0039】

図9は、第1世代の共通化テーブル群T1の一例を示す説明図である。第1の作成部402は、具体的には、たとえば、2つのラベル化FF情報800A,800BのうちFF数が多い方(同数であればどちらでもよい)のラベル化FF情報のラベル列を基準レコードとする。図9の場合は、回路Aのラベル化FF情報800AのラベルA0〜A9を基準レコードに割り当てている。

【0040】

そして、回路Bのラベル化FF情報800BのラベルB0〜B7を基準レコードのラベルにランダムに割り当てる。該当するラベルがない場合は、“*”(相手がいない)を割り当てる。そして、共通化テーブルをランダム発生でN個作成する。Nは任意のレコード数である。各共通化テーブルには、固有のテーブル番号(図9では、T1−01,T1−02,…,T1−N)を割り振る。テーブル番号ごとのレコードが共通化テーブルである。N個の共通化テーブルが第1世代の共通化テーブル群T1となる。

【0041】

図4−1において、評価関数情報作成部403は、パス情報DPA,DPBとラベル化FF情報800A,800Bとに基づいて、評価関数情報を作成する機能を有する。具体的には、たとえば、パス情報に記述されているFFのインスタンス名を、ラベル化FF情報800A,800Bのラベル項目を参照して、ラベルに変換する。

【0042】

図10−1は、図7−1に示した回路Aのパス情報DPAのラベル変換例を示す説明図である。たとえば、回路Aのラベル化FF情報800Aにおいて、インスタンス名:AAA_inst/ac01_regのFFのラベルは“A0”である。したがって、図10−1では、図7−1の「AAA_inst/ac01_reg」が「A0」に変換されている。

【0043】

図10−2は、図7−2に示した回路Bのパス情報DPBのラベル変換例を示す説明図である。たとえば、回路Bのラベル化FF情報800Bにおいて、インスタンス名:BBB_inst/div01_regのFFのラベルは“B0”である。したがって、図10−2では、図7−2の「BBB_inst/div01_reg」が「B0」に変換されている。また、出力先とその入力元を変換されたラベルで対応付けたラベル化パス情報を生成する。各ラベル化パス情報が評価関数情報となる。

【0044】

図11−1は、回路Aのパス情報DPAをラベル化したラベル化パス情報を示す説明図である。ラベル化パス情報1101Aにおいて、たとえば、一行目のレコードは、入力元がラベル名A0,A1,A4,A5,A7のFFであり、出力先がラベル名A0のFFとなるパスを示している。

【0045】

図11−2は、回路Bのパス情報DPBをラベル化したラベル化パス情報を示す説明図である。ラベル化パス情報1101Bにおいて、たとえば、一行目のレコードは、入力元がラベル名B0,B2,B3のFFであり、出力先がラベル名B0のFFとなるパスを示している。

【0046】

また、図4−1において、共通化テーブル評価/再作成部404は、共通化テーブル評価処理と次世代作成処理を実行する機能を有する。具体的には、以下の(1)〜(6)を実行する。

【0047】

(1)回路Aおよび回路Bから共通化可能な回路のFFをすべてリストアップする。

(2)つぎに、ランダム(もしくは任意)に共通化マッピングを行う。

(3)そして、FFにつながる入力の共通性をチェックして共通性が高いほど高得点をつける。

(4)すべてのFFの点数付けが終わったところで合計点を計算する。

(5)別の共通化マッピングを、遺伝的アルゴリズムを用いて作成し、(3)〜(4)を再度実行する。

(6)規定回数(世代数となる)(2)〜(5)を繰り返して、一番合計点の高かった共通化テーブルを採用する。

【0048】

図4−2は、実施の形態1にかかる設計支援装置の機能的構成2を示すブロック図である。図4−2では、共通化テーブル評価/再作成部404の詳細な機能的構成を示している。まず、変換部421は、対象となる共通化テーブル群を参照することにより、対象となる共通化テーブルごとに、当該他方のパス情報内の他方の識別情報を一方の識別情報に変換する機能を有する。対象となる共通化テーブル群は後述の設定部424により設定されるが、具体的には、作成された共通化テーブル群の中で最新世代の共通化テーブル群を対象となる共通化テーブル群とする。

【0049】

変換部421は、具体的には、たとえば、ラベル化パス情報1101A,1101Bの変換処理を実行する。ラベル化パス情報1101A,1101Bの変換処理では、変換対象をラベル化パス情報1101A,1101Bのうち基準レコードに選ばれなかった回路Bのラベル化パス情報1101Bとする。そして、選ばれた共通化テーブルにより、回路Bのラベル化パス情報1101Bを置換する。

【0050】

図12は、ラベル化パス情報の置換処理を示す説明図である。ここでは、共通化テーブルT1−01を例に挙げて説明する。回路Bのラベル化パス情報1101B内のラベルを、選択した共通化テーブルT1−01を参照して、基準レコードのラベルに置換する。たとえば、共通化テーブルT1−01のラベル“B3”は、基準レコードのラベル“A1”に対応している。したがって、回路Bのラベル化パス情報1101B内の“B3”を“A1”に置換する。置換後のラベル化パス情報1201Bは、回路AのラベルA0〜A9で表現されることとなる。

【0051】

また、図4−2において、算出部422は、一方のパス情報および変換部421による変換後の他方のパス情報内における、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値を、共通化テーブルごとに算出する機能を有する。

【0052】

算出部422は、具体的には、たとえば、カウント処理を実行する。カウント処理では、変換されていない方の回路Aのラベル化パス情報1101Aと変換後の回路Bのラベル化パス情報1201Bとを比較する。そして、出力先ごとに共通項となるラベルを抽出し、その数を計数する。出力先ごとの計数値の合計が、選択された共通化テーブルT1−01の得点、すなわち、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値となる。

【0053】

図13は、カウント処理による計数テーブルを示す説明図である。図13では、図12で示した置換後のラベル化パス情報1201Bを用いて説明する。カウント処理では、置換されていない回路Aのラベル化パス情報1101Aを呼び出す。そして、出力先ごとに、回路Aのラベル化パス情報1101Aの入力元と回路Bの置換後のラベル化パス情報1201Bの入力元を対応付ける。そして、出力先ごとに両入力元に共通に存在するラベルを共通項として抽出する。

【0054】

たとえば、ラベル:A0の出力先では、共通項は、ラベル:A0,A1の2個である。したがって計数値は2となる。このようにして、出力先ごとに計数値をカウントし、その総計が選択された評価テーブルT1−01の得点となる。図13の例では、19得点となる。共通化テーブル評価処理では、全共通化テーブルT1−01〜T1−Nに対し、変換処理とカウント処理を実行することで、共通化テーブルごとの得点を得ることができる。

【0055】

また、図4−2において、第2の作成部423は、算出部422によって算出された評価値に基づいて、遺伝的アルゴリズムにより、対象となる共通化テーブル群から次世代の共通化テーブル群を作成する機能を有する。

【0056】

第2の作成部423は、具体的には、たとえば、規定回数を超えていない場合、対象となる共通化テーブル群のうち、最高得点となった共通化テーブルを用いて、次世代作成処理を実行する。なお、最高得点が複数ある場合はランダムに選択する。規定回数を超えている場合は、最高得点となった共通化テーブルを最適な共通化テーブルとして併合部405に出力することとなる。規定回数とは上限世代数であり、次世代作成処理は規定回数まで繰り返し実行される。次世代作成処理は、スケーリング処理、選択処理、次世代テーブル生成処理を実行する。

【0057】

次世代作成処理には遺伝的アルゴリズムを適用する。遺伝的アルゴリズムとは、自然淘汰により最適な遺伝子が残ってきたようにシステムの中で自然淘汰のシミュレーションを実行し、最適解を求めようとするアルゴリズムである。遺伝的アルゴリズムは、広範囲の探索空間に対して少ない試行回数で最適解を求めやすい利点がある。必ず最適解が求まる訳ではないが、「最適ではないとしても効果が高いと思われる組み合わせ」を探す場合には単なるランダム検索よりも効率が良い。

【0058】

遺伝的アルゴリズムでは、解のセットをパラメータとして一つのデータにまとめて遺伝子に見立てる。はじめにいくつもの遺伝子を用意し、それぞれを評価関数にかけてより適合度の高いと思われる遺伝子を残す。実施の形態では、評価テーブルを遺伝子に見立て、今世代の生き残りとなる親の共通化テーブルを選択する。そして、親の遺伝子(親の共通化テーブル)を引き継ぐため、親間で交叉や突然変異をおこない、次世代の子となる共通化テーブルを生成する。

【0059】

最後に、親の共通化テーブルと子の共通化テーブルとを組み合わせることで、次世代の共通化テーブルを生成する。次世代の共通化テーブルは、規定回数を超えるまで共通化テーブル評価処理に与えられる。

【0060】

まず、スケーリング処理を実行する。スケーリング処理とは、つぎに実行する選択処理での選択格差を広げる処理である。スケーリング処理を実行することで、高得点の共通化テーブルを選択しやすくすることができる。実施の形態では、シグマスケーリングを例に挙げて説明する。シグマスケーリングでは、各共通化テーブルの得点を、下記式(1)を用いて変換する。

【0061】

f´=f−(favg−c×σ)・・・(1)

【0062】

ただし、f´はスケーリング処理後の得点(ただし、f´が負のときはf´=0とする)。fはスケーリング処理前の得点、favgはスケーリング処理前の得点の平均値、cは任意の変数(本例ではc=2)、σはスケーリング処理前の標準偏差(ただし、σ=0のときは、σ=1とする)である。

【0063】

図14は、シグマスケーリング処理結果を示す説明図である。図14では、共通化テーブルの個数NをN=20としている。平均値favgと標準偏差σは、共通化テーブルの全得点から算出する。なお、スケーリング処理では、シグマスケーリングのほか、線形スケーリングやべき乗スケーリングを用いてもよい。

【0064】

つぎに、選択処理を実行する。選択処理では、N個の共通化テーブルの中から次世代に残す一部(ここではN/2個)の共通化テーブルを選択する。選択処理では、スケーリング処理を実行した場合は、スケーリング処理後の得点を用い、スケーリング処理を実行していない場合は、共通化テーブルの得点をそのまま用いる。

【0065】

選択処理では、エリート選択とルーレット選択とを組み合わせる。エリート選択とは、最高得点のテーブルを無条件に選択する選択方法である。最高得点が複数ある場合にはランダムで1つ選択する。

【0066】

ルーレット選択とは、選択確率に基づいて共通化テーブルを選択する選択方法である。選択確率とは、共通化テーブルごとに、全得点の合計点を共通化テーブルの得点で割った値である。本例では、次世代に残す共通化テーブルの個数はN/2であり、エリート選択された共通化テーブルの個数は1であるため、(N/2−1)回分、ルーレット選択をおこなう。エリート選択では、高得点の共通化テーブルしか残らないが、ルーレット選択も適用することで、選択に多様性を残すことができる。すなわち、得点が低くても生き残る可能性を残すためである。

【0067】

ルーレット選択では、まず、ランダム関数により選択値s(0≦s≦1)を生成する。つぎに、選択確率の高い順から選択確率を選び、選ばれた選択確率を選択値sから引く。そして、選択値sが0以下となったときの共通化テーブルを次世代へ生き残る親の遺伝子として選択する。

【0068】

図15は、選択処理の内容を示す説明図である。図15の点数テーブルでは、共通化テーブルT1−10が最高得点(11.9357)であるため、エリート選択される。また、共通化テーブルごとに選択確率が算出されている。

【0069】

図16は、次世代の親となる共通化テーブルを示す説明図である。本例では、エリート選択された共通化テーブルT1−10とルーレット選択された9個の共通化テーブルが次世代の親の遺伝子として引き継がれる。

【0070】

つぎに、子の共通化テーブルを生成する。子の共通化テーブルの生成には、交叉と突然変異を適用する。遺伝的アルゴリズムの交叉手法は数多くあるが、実施の形態は配置を基準とした交叉を用いる。次世代の親となるN/2個の共通化テーブルを、2個ずつのペアに分ける。ペアの選択は適当でよいが、今回は選択順に(T1−10,T1−01),(T1−16,T1−17),(T1−05,T1−02),(T1−10,T1−20),(T1−02,T1−08)とする。

【0071】

図17は、交叉の一例を示す説明図である。(A)において親の共通化テーブルのペアを選ぶ。ここでは、親の共通化テーブルのペアを(親1,親2)とする。つぎに、(B)において、ペアとなった親どうしの対応するラベル((B)中、ハッチングを施した箇所)をランダムに選択する。選択個数もランダム(本例では4箇所)である。

【0072】

そして、(C)において、子のペア(子1,子2)を用意する。子のペアは初期状態では空である。子1のレコードに、(B)における親1の選択箇所のラベルを選択箇所と同位置に代入する。同様に、子2のレコードに、(B)における親2の選択箇所のラベルを選択箇所と同位置に代入する。それぞれ一方の親の遺伝子を残すためである。

【0073】

つぎに、(D)において、子1のレコードの空き領域に、子1にはない親2のラベルを左側から書き込む。すなわち、親2のラベル(B0,B3,B2,B6,B5,B4,*,B1,*,B7)から子1のラベル(B3,*,B0,B5)を除いたラベル(B2,B6,B4,B1,*,B7)を書き込む。他方の親である親2の遺伝子を残すためである。

【0074】

同様に、(E)において、子2のレコードの空き領域に、子2にはない親1のラベルを左側から書き込む。すなわち、親1のラベル(B4,B3,B2,*,B0,B6,*,B5,B1,B7)から子2のラベル(B3,B6,B5,B1)を除いたラベル(B4,B2,*,B0,*,B7)を書き込む。他方の親である親1の遺伝子を残すためである。

【0075】

このようにして、(F)に示したように、親1および親2の共通化テーブルから子1および子2の共通化テーブルが生成される。このような交叉を、親の共通化テーブルのペア(T1−10,T1−01),(T1−16,T1−17),(T1−05,T1−02),(T1−10,T1−20),(T1−02,T1−08)ごとに実行する。これにより、N/2個の子の共通化テーブルが生成されることとなる。

【0076】

つぎに、突然変異について説明する。突然変異では、新しく生成されたN/2個の子の共通化テーブルに対して、低確率でランダムに配置を入れ替える。突然変異を実行することで探索空間を広げることができる。

【0077】

図18は、突然変異の処理内容を示す説明図である。(A)は突然変異前の子の共通化テーブル群を示しており、(B)は突然変異後の子の共通化テーブル群を示している。(A)において、まず、子の共通化テーブル1つ1つに対して突然変異を発生させるかチェックをおこなう。発生確率は1%程度とする。具体的には、たとえば、確率t(0≦t≦1)をランダムに発生して、各子の共通化テーブルに割り当てる。

【0078】

そして、発生確率以下となる確率tを持つ子の共通化テーブルに対して、ランダムに2つの配置を選択する((A)のハッチングを施した箇所)。そして、選択箇所のラベルを入れ替える。これにより、(B)に示した突然変異後の子の共通化テーブル群を得ることができる。なお、突然変異の実行は任意である。最後に次世代の共通化テーブル群Tiの生成を実行する。

【0079】

図19は、次世代の共通化テーブル群Tiを示す説明図である。具体的には、たとえば、親の共通化テーブル(図16を参照)と子の共通化テーブル(図18を参照)を組み合わせることにより、次世代の共通化テーブル群Tiが生成される。

【0080】

また、図4−2において、設定部424は、第1および第2の作成部423によって作成された共通化テーブル群のうち最新世代の共通化テーブル群を対象となる共通化テーブル群に設定する機能を有する。具体的には、たとえば、第1世代の共通化テーブル群T1のみが作成されている場合、第1世代の共通化テーブル群T1が最新世代の共通化テーブル群となるため、対象とする共通化テーブル群として設定して、変換部421にわたす。また、第2の作成部423により次世代の共通化テーブル群Tiが順次作成された場合、最新世代の共通化テーブル群Tiを対象とする共通化テーブル群として設定して、変換部421にわたす。

【0081】

選択部425は、設定部424によって設定された対象となる共通化テーブル群の中から特定の共通化テーブルを選択する機能を有する。具体的には、たとえば、第2の作成部423により規定回数nを超えた場合、現時点での最新世代の共通化テーブル群Tnの中から、特定の共通化テーブルTn−xを選択する。より具体的には、共通化テーブル群Tnのうち、図13に示した計数値が最高得点となる共通化テーブルを特定の共通化テーブルTn−xとして選択する。選択された特定の共通化テーブルTn−xは記憶装置内の特定の領域に書き込まれる。

【0082】

また、図4−1において、併合部405は、選択部425によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報(たとえば、回路Aの回路情報DA)および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報(たとえば、回路Bの回路情報DB)を、一方の識別情報により特定されるデータ保持素子の入力ネットおよび他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換する。そして、変換された共通回路情報により、一方の回路情報および他方の回路情報を併合した併合回路の回路情報DABを生成する機能を有する。

【0083】

具体的には、たとえば、ラベル化FF情報800A,800Bと、共通化テーブル評価/再作成部404から最終出力される特定の共通化テーブルTn−xを用いて、回路AのFFと回路BのFFとを共通化した共通化FFとセレクタのネットリストを生成する。

【0084】

図20は、併合回路ABの接続イメージを示す説明図である。特定の共通化テーブルTn−xは、回路Aのラベル列からなる基準レコードと回路Bのラベル列からなる最高得点のレコードの組み合わせである。両レコードの上下のラベルが対応しあい、排他的な動作をする。したがって、上下のラベルに共通化するFFとそのFFの入力に接続される2入力1出力のセレクタを生成する。なお、いずれか一方のラベルが「*」である場合は、セレクタが不要となる。

【0085】

たとえば、共通化テーブルの一列目の上下のラベルペア(A0,B3)については、ラベルA0に対応する入力ネットac01_inをセレクタの一方の入力ネット(ac01_in_A)とする。同様に、ラベルB3に対応する入力ネットdiv04_inをセレクタの他方の入力ネット(div04_in_B)とする。入力ネット名を固有化するため、入力ネット名の末尾に“_A”、“_B”を付している。ff0_out〜ff9_outは共通化FF1〜9の出力ネットを示している。

【0086】

図21は、共通化FFとセレクタの共通回路情報(ネットリスト)を示す説明図である。図21に支援したネットリストは、併合部405により生成された、回路AのFFと回路BのFFとを共通化した共通化FFとセレクタのネットリスト(共通回路情報NFS)である。図21中、SFF ff0_reg〜SFF ff9_regは、共通化FF1〜9に関する記述である。また、MUX Usel0〜MUX Usel9は、共通化FF1〜FF9の入力に接続されるセレクタに関する記述である。

【0087】

また、図4−1において、置換テーブル作成部406は、併合部405によって得られた共通回路情報(たとえば、共通回路情報NFS)内の共通のデータ保持素子の出力ネットと、一方の識別情報により特定されるデータ保持素子の出力ネットと、他方の識別情報により特定されるデータ保持素子の出力ネットとを対応付ける置換テーブルTCを作成する機能を有する。

【0088】

図22は、出力ネット置換テーブルTCを示す説明図である。回路AのFFと回路BのFFとが共通化されるが、出力ネットは入力の選択に応じて切り替わるため、置換テーブル作成部406では、置換テーブルTCを作成して対応付けをおこなう。たとえば、最高得点の共通化テーブル中、ラベルA0,B3のペアについては、それぞれ出力ネットは、“ac01_out”と“div04_out”である(ラベル化パス情報800A,800Bを参照)。そして、この出力ネット“ac01_out”と“div04_out”を、対応する入力ネット“ac01_in”と“div04_in”の出力先となる共通化FFの出力ネット“ff0_out”のレコードに関連付ける。

【0089】

また、図4−1において、置換部407は、置換テーブル作成部406によって作成された置換テーブルTCを参照して、一方の回路情報(たとえば、回路Aの回路情報DA)に記述されている出力ネットを当該出力ネットに対応する共通のデータ保持素子の出力ネットに置換する機能を有する。また、他方の回路情報(たとえば、回路Bの回路情報DB)に記述されている出力ネットを当該出力ネットに対応する共通のデータ保持素子の出力ネットに置換する機能を有する。

【0090】

つぎに、置換部407では、回路Aおよび回路Bの固有化をおこなう。具体的には、回路Aの回路情報DAおよび回路Bの回路情報DBのインスタンス名とネット名の固有化をおこなう。たとえば、回路Aの回路情報DAおよび回路Bの回路情報DBから共通化するFFを削除する。また、インスタンス名やネット名の末尾に回路Aであれば“_A”、回路Bであれば“_B”を付す。また、FFの出力ネット名を、図22の置換テーブルTCを参照して、共通化FFの出力ネット名に変換する。

【0091】

図23は、回路Aの固有化前後の回路情報(ネットリスト)を示す説明図である。回路Aの回路情報DA(ネットリスト)の冒頭には、module文が記述されている。module文は、マージ処理の際に、回路Bのmodule文とマージされる。(A)が固有化前の回路Aの回路情報DAであり、(B)が固有化後の回路Aの回路情報NAである。図23では、共通化するFFの記述が削除され、出力ネット名が置換されている。

【0092】

図24は、回路Bの固有化前後の回路情報(ネットリスト)を示す説明図である。回路Bの回路情報DB(ネットリスト)の冒頭には、module文が記述されている。module文は、マージ処理の際に、回路Aのmodule文とマージされる。(A)が固有化前の回路Bの回路情報DBであり、(B)が固有化後の回路Bの回路情報NBである。図24でも、共通化するFFの記述が削除され、出力ネット名が置換されている。

【0093】

そして、図4−1において、併合部405は、置換部407による置換後の一方の回路情報(たとえば、回路Aの回路情報NA)と置換部407による置換後の他方の回路情報(たとえば、回路Bの回路情報NB)と共通回路情報(たとえば、共通回路情報NFS)とを統合することにより、併合回路ABの回路情報DABを生成する。

【0094】

図25は、マージした併合回路ABの回路情報DAB(ネットリスト)を示す説明図である。マージ処理では、回路Aの入力端子および出力端子と回路Bの入力端子および出力端子とをマージした記述をmodule文に記述する。このとき、共通化FFのクロック信号clockとリセット信号resetが重複しないように処理する。すなわち、clock,resetは共通化されるため、module文では1つだけ残す。また、あらたに、module文に選択信号selABを追加する。そして、回路Aの回路情報NA、回路Bの回路情報NB、共通回路情報NFS(共通化FFおよびセレクタのネットリスト)を追加する。これにより、併合回路ABの回路情報DABが生成される。

【0095】

図4−1において、取得部408は、併合部405により併合された併合回路ABの回路情報DABの論理合成結果dabを取得する機能を有する。論理合成は既存のツールにより実行される。論理合成ツールは自体は、設計支援装置400の外部にあってもよい。外部にある場合は、併合回路ABの回路情報DABを論理合成ツールを有する外部装置に送信し、当該外部装置から論理合成結果dabを受信することとしてもよい。論理合成結果dabはファイル化されて、図3に示したROM302、RAM303、磁気ディスク305などの記憶装置に保存される。これにより、論理合成された最終的なネットリストとして出力されることとなる。

【0096】

(設計支援処理手順)

図26は、実施の形態1にかかる設計支援装置400の設計支援処理手順を示すフローチャートである。まず、排他的な動作をする回路A,回路Bの回路情報(たとえば、ネットリスト)を取得しておき(ステップS2601)、入力部401により、図6−1〜図7−2に示したように、FF情報DFA,DFBおよびパス情報DPA,DPBを抽出する(ステップS2602)。

【0097】

そして、置換テーブル作成部406により、図8−1〜図9に示したように、共通化テーブル作成処理を実行する(ステップS2603)。これにより、第1世代の共通化テーブル群T1が作成される。つぎに、評価関数情報作成部403により、図10−1〜図11−2に示したように、評価関数情報(ラベル化パス情報1101A,1101B)を作成し(ステップS2604)、共通化テーブル評価/再作成部404により、図12〜図19に示したように、共通化テーブル評価処理と次世代作成処理を実行する(ステップS2605)。

【0098】

このあと、併合部405、置換テーブル作成部406および置換部407により、図20〜図25に示したように、マージ処理を実行する(ステップS2606)。これにより、図25に示したようなマージされた併合回路ABの回路情報DABが生成される。最後に、取得部408により、併合部405によって併合された併合回路ABの回路情報DABの論理合成結果dab取得して(ステップS2607)、最終的なネットリストを得ることとなる。

【0099】

図27は、図26に示した共通化テーブル評価/次世代作成処理(ステップS2605)の詳細な処理手順を示すフローチャートである。まず、未選択の共通化テーブルがあるか否かを判断する(ステップS2701)。未選択の共通化テーブルがある場合(ステップS2701:Yes)、未選択の共通化テーブルを1つ選択し(ステップS2702)、図12に示したように、ラベル化パス情報を置換する(ステップS2703)。そして、図13に示したように、共通項を抽出してカウントし(ステップS2704)、ステップS2701に戻る。ステップS2701〜S2704のループにより、共通化テーブルがなくなるまで、共通項を抽出してカウントすることとなる。

【0100】

一方、ステップS2701において、未選択の共通化テーブルがないと判断された場合(ステップS2701:No)、規定回数(n回)実行したか否かを判断する(ステップS2705)。すなわち、n世代分実行したか否かを判断する。規定回数に達していない場合(ステップS2705:No)、次世代作成処理を実行して(ステップS2706)、次世代の共通化テーブル群Tiを作成し、ステップS2701に戻る。これにより、次世代の共通化テーブル群Tiにより、ステップS2701〜ステップS2704のループが実行されることとなる。一方、規定回数を超えた場合(ステップS2705:Yes)、図26のマージ処理(ステップS2606)に移行する。

【0101】

図28は、図27に示した次世代作成処理(ステップS2706)の詳細な処理手順を示すフローチャートである。まず、図14に示したように、スケーリング処理を実行し(ステップS2801)、図15および図16に示したように、エリート選択やルーレット選択といった選択処理を実行する(ステップS2802)。そして、図17および図18に示したように、交叉/突然変異処理を実行し(ステップS2803)、図19に示したように、次世代の共通化テーブル群Tiを生成して(ステップS2804)、図27のステップS2701に戻る。

【0102】

図29は、図26に示したマージ処理(ステップS2606)の詳細な処理手順を示すフローチャートである。まず、対象となる共通化テーブル群Tiを取得し(ステップS2901)、図21に示したように、共通化FFおよびセレクタのネットリスト(共通回路情報NFS)を生成する(ステップS2902)。そして、図22に示したように、出力ネット置換テーブルTCを生成する(ステップS2903)。

【0103】

このあと、図23に示したように、回路Aの回路情報DAのインスタンス名とネット名を固有化し(ステップS2904)、図24に示したように、回路Bの回路情報DBのインスタンス名とネット名を固有化する(ステップS2905)。そして、図25に示したように、回路Aの回路情報NAと回路Bの回路情報NBを併合して(ステップS2906)、図26のステップS2607に移行する。これにより、マージされた併合回路ABの回路情報DABを得ることができる。

【0104】

このように、上述した実施の形態1によれば、リーク電流や面積を削減するために、使用/未使用が排他的な回路を共通化する。具体的には,FFに着目してFFを共通化する。FFを共通化することでFFに入力される信号を作り出す組み合わせ回路を論理圧縮することができる。

【0105】

また、FFの共通化には評価関数(ラベル化パス情報1101A,1101B)を用いる。評価関数による計算結果(点数)が高くなる組み合わせを探すことで組み合わせ回路の論理圧縮の可能性の向上を図ることができる。また、共通化した分だけFFの数は削減できるため、面積とリーク電流の削減を図ることができる。

【0106】

また、入力の共通性に着目しているため、論理圧縮の効果を上げ、組み合わせ回路の削減も期待することができる。また、上述した実施の形態1では、回路動作を理解していなくてもマージすることができる。

【0107】

<実施の形態2>

つぎに、実施の形態2について説明する。実施の形態1では、併合回路ABの回路情報DABを得たあとに、論理合成結果dabを取得することとした。これに対し、実施の形態2では、論理圧縮を試行してその圧縮度合いを評価関数として利用することとする。なお、実施の形態1と同一構成には同一符号を付し、その説明を省略する。

【0108】

図30−1は、実施の形態2にかかる設計支援装置の機能的構成1を示すブロック図である。設計支援装置3000は、FF情報抽出部411と、第1の作成部402と、仮併合部3001と、仮取得部3002と、共通化テーブル評価/再作成部404と、併合部405と、置換テーブル作成部406と、置換部407と、取得部408と、を備える。実施の形態2では、パス情報DPA,DPBを使用しないため、図4に示したパス情報抽出部412および評価関数情報作成部403は不要である。また、また、共通化テーブル評価/再作成部404の詳細は図30−2に示す。

【0109】

なお、各機能は、具体的には、たとえば、図3に示したROM302、RAM303、磁気ディスク305に記憶されたプログラムをCPU301に実行させることにより、またはI/F309により、その機能を実現する。実施の形態1との相違は、仮併合部3001、仮取得部3002および共通化テーブル評価/再作成部404であるため、仮併合部3001、仮取得部3002および共通化テーブル評価/再作成部404についてのみ説明し、他の機能の説明は実施の形態1と同じであるため省略する。

【0110】

図30−1において、仮併合部3001は、第1の作成部402によって作成された第1世代の共通化テーブル群T1を用いて、回路Aの回路情報DAと回路Bの回路情報DBとを併合(マージ)する機能を有する。具体的な動作は、併合部405と同一である。ただし、参照する共通化テーブルは、特定の共通化テーブルTn−xではなく、対象となる共通化テーブル群Ti内の各共通化テーブルである。

【0111】

したがって、併合された各回路情報は最終的な回路情報ではなく、中間的な回路情報である。以下、仮併合部3001による併合結果物を、「仮併合回路(AB)の回路情報(DAB)」とする。仮併合回路(AB)の回路情報(DAB)は、共通化テーブル群Ti内の共通化テーブルごとに得られる。

【0112】

仮取得部3002も、具体的な動作は、取得部408と同一である。ただし、取得対象となる論理合成結果は、仮併合回路(AB)の回路情報(DAB)の論理合成結果(dab)である。論理合成結果(dab)は、仮併合回路(AB)の回路情報(DAB)ごとに得られる。論理合成では論理圧縮後の面積が算出されるため、論理合成結果(dab)には、セルの面積の総和が記録されている。実施の形態2では、この面積の総和に応じた値を評価関数として用いる。したがって、仮併合回路(DAB)の論理圧縮度合いに応じて、回路Aと回路Bとを併合することができ、論理圧縮の効果を上げ、組み合わせ回路の削減も期待することができる。

【0113】

図30−2は、実施の形態2にかかる設計支援装置の機能的構成2を示すブロック図である。図30−2では、共通化テーブル評価/再作成部404の詳細な機能的構成を示している。共通化テーブル評価/再作成部404は、算出部422と、第2の作成部423と、設定部424と、選択部425とを備える。第2の作成部423、設定部424および選択部425は、実施の形態1と同一なので説明を省略する。なお、設定部424は、設定された対象となる共通化テーブル群Tiを仮併合部3001に渡すこととなる。

【0114】

算出部422は、仮取得部3002によって取得された仮併合回路(AB)の回路情報(DAB)ごとの論理合成結果(dab)から得られる仮併合回路(AB)に関する面積情報に基づいて、論理合成による論理圧縮度合いをあらわす評価値を、対象となる共通化テーブル群内の共通化テーブルごとに算出する機能を有する。具体的には、まず、対象となる共通化テーブル群Tiの各共通化テーブルに対し、論理合成結果から得られたセル面積の総和となる面積情報を関連付ける。

【0115】

図31は、セル面積を対応付けた共通化テーブル群を示す説明図である。図31では、第1世代の共通化テーブル群T1を例に挙げている。セル面積を対応付けた第1世代の共通化テーブルT1をTS1とする。同様に、セル面積を対応付けたi世代の共通化テーブルTiをTSiとする。

【0116】

つぎに、算出部422は、実施の形態1と同様、スケーリング処理を実行する。共通化テーブル評価/再作成部404では、セル面積の値が小さいほど,共通化テーブルとしては得点が大きくなるようにスケーリングを実行する。まず、対象とする共通化テーブル群TSi(ここでは第1世代の共通化テーブル群TS1)から選ばれた共通化テーブルのセル面積の値gについて、共通化テーブル群TSiのセル面積の最小値g_minで割る。割った結果を2から引く。

【0117】

g´=2−g/g_min・・・(2)

【0118】

ただし、g´はスケーリング処理後の得点である。これにより、セル面積の値gが小さいほど得点g´は大きくなる。このあと、上述したシグマスケーリングを実行して選択格差を広げる。

【0119】

図32は、シグマスケーリング処理結果を示す説明図である。具体的には、上記式(1)のfに得点g´の値を代入する。また、各セル面積の値gごとに得られたg´の平均値g´avgを算出し、上記式(1)のf´avgに代入する。これにより、共通化テーブルT1−01〜T1−20ごとに、得点f´を算出することができる。

【0120】

図32に示したように、得点f´が算出されたため、その後の処理は、実施の形態1と同様である。すなわち、図32に示した得点f´を用いて、第2の作成部423により、エリート選択およびルーレット選択(図15および図16を参照)、交叉(図17を参照)、突然変異(図18を参照)を実行する。そして、図19に示した場合と同様、エリート選択とルーレット選択により選択されたN/2個の次世代の親(生き残り)と,あらたに生成されたN/2個の次世代の子を合わせて、N個の共通化テーブルからなる次世代の共通化テーブル群Tiを生成する。

【0121】

この次世代の共通化テーブル群Tiの生成がn回に達した場合、第n世代の共通化テーブル群Tnの中から最高得点となる特定の共通化テーブルTn−xを選択する。そして、選択された特定の共通化テーブルTn−xを用いて、実施の形態1と同様、併合部405により回路Aと回路Bとの併合処理を実行する(図20〜図25を参照)。そして、併合処理によりマージされた回路情報DABの論理合成結果dabを取得部408が取得することで、最終的なネットリストを得ることとなる。

【0122】

(設計支援処理手順)

図33は、実施の形態2にかかる設計支援装置3000の設計支援処理手順を示すフローチャートである。まず、排他的な動作をする回路A,回路Bの回路情報(たとえば、ネットリスト)を取得しておき(ステップS3301)、FF情報抽出部411により、図6−1〜図6−2に示したように、FF情報を抽出する(ステップS3302)。

【0123】

そして、第1の作成部402により、図8−1〜図9に示したように、共通化テーブル作成処理を実行する(ステップS3303)。これにより、第1世代の共通化テーブル群T1が作成される。

【0124】

つぎに、仮併合部3001により、仮マージ処理を実行する(ステップS3304)。仮マージ処理(ステップS3304)では、対象とする現世代(第i世代)の共通化テーブル群Ti内のすべての共通化テーブルTi―01〜Ti−Nを用いて、回路Aと回路Bとのマージ処理を実行する。詳細は後述する。マージ処理(ステップS3304)により、対象とする第i世代の共通化テーブルごとに仮併合回路(AB)の回路情報(DAB)を得ることができる。

【0125】

つぎに、仮論理合成結果取得処理を実行する(ステップS3305)。仮論理合成結果取得処理(ステップS3305)では、仮マージ処理(ステップS3304)での仮併合回路(AB)の回路情報(DAB)ごとに論理合成結果(dab)を取得する。詳細は後述する。仮論理合成により回路(AB)の回路情報(DAB)は論理圧縮され、セル面積が算出される。

【0126】

そして、規定回数(n回)実行したか否かを判断する(ステップS3306)。規定回数に達していない場合(ステップS3306:No)、最新世代の各共通化テーブルに対応するセル面積を関連付ける(ステップS3307)。そして、上記式(2)を用いて、関連付けされた各セル面積の換算処理を実行する(ステップS3308)。この換算処理により得点g´が現世代の共通化テーブルごとに得られる。そして、次世代作成処理を実行する(ステップS3309)。

【0127】

次世代作成処理(ステップS3309)では、共通化テーブルごとの得点g´を式(1)のfとし、各セル面積の値gごとに得られたg´の平均値g´avgを上記式(1)のf´avgとして、スケーリング処理(ステップS2801)を実行することとなる。なお、次世代作成処理(ステップS3309)が実行されることにより、次世代の共通化テーブル群Tiが生成されて、ステップS3304に移行する。仮マージ処理(ステップS3304)では、ステップS3309で生成された次世代の共通化テーブル群Tiを現世代の共通化テーブル群として、併合処理を実行することとなる。

【0128】

一方、ステップS3306において、規定回数(n回)実行した場合(ステップS3306:Yes)、現世代(第n世代)の共通化テーブル群Tnの中から得点g´の値が最高得点となる共通化テーブルTngを抽出する(ステップS3310)。そして、併合部405により、図20〜図25に示したように、マージ処理を実行する(ステップS3311)。これにより、図25に示したようなマージされた併合回路ABの回路情報DABが生成される。最後に、取得部408により、併合回路ABの回路情報DABの論理合成結果dabを取得して(ステップS3312)、最終的なネットリストを得ることとなる。

【0129】

図34は、図33に示した仮マージ処理(ステップS3304)の詳細な処理手順を示すフローチャートである。まず、現世代の共通化テーブル群Tiにおいて、未選択の共通化テーブルがあるか否かを判断する(ステップS3401)。未選択の共通化テーブルがある場合(ステップS3401:Yes)、未選択の共通化テーブルを1つ取得する(ステップS3402)。つぎに、図21に示したように、共通化FFおよびセレクタの共通回路情報NFSを生成する(ステップS3403)。そして、図22に示したように、置換テーブルTCを生成する(ステップS3404)。

【0130】

このあと、図23に示したように、回路Aの回路情報DAのインスタンス名とネット名を固有化し(ステップS3405)、図24に示したように、回路Bの回路情報DBのインスタンス名とネット名を固有化する(ステップS3406)。そして、図25に示したように、回路Aの回路情報NAと回路Bの回路情報NBを併合して(ステップS3407)、併合回路ABの回路情報DABをメモリに保存する(ステップS3408)。そして、ステップS3401に戻る。

【0131】

このステップS3401〜S3408のループを実行することで、共通化テーブルごとの併合回路ABの回路情報DABを得ることができる。また、ステップS3401において、未選択の共通化テーブルがない場合(ステップS3401:No)、仮マージ処理を終了して仮論理合成結果取得処理(ステップS3305)に移行する。

【0132】

図35は、図33に示した仮論理合成結果取得処理(ステップS3305)の詳細な処理手順を示すフローチャートである。まず、未選択の仮併合回路(AB)の回路情報(DAB)があるか否かを判断し(ステップS3501)、未選択の仮併合回路(AB)の回路情報(DAB)がある場合(ステップS3501:Yes)、未選択の仮併合回路(AB)の回路情報(DAB)を取得する(ステップS3502)。そして、取得された仮併合回路(AB)の回路情報(DAB)について仮論理合成結果(dab)を取得し(ステップS3503)、仮論理合成結果(dab)をメモリに保存する(ステップS3504)。

【0133】

このステップS3501〜S3504のループを実行することで、仮併合回路(AB)の回路情報(DAB)ごとに論理圧縮することができる。また、ステップS3501において、未選択の仮併合回路(AB)の回路情報(DAB)がない場合(ステップS3501:No)、図33のステップS3306に移行することとなる。

【0134】

このように、実施の形態2によれば、リーク電流や面積を削減するために、使用/未使用が排他的な回路を共通化する。具体的には,FFに着目してFFを共通化する。FFを共通化することでFFに入力される信号を作り出す組み合わせ回路を論理圧縮することができる。

【0135】

また、FFの共通化には論理圧縮度合い(得点g´)を用いる。得点g´が小さくなる組み合わせを探すことで、実施の形態1よりもより効果的に組み合わせ回路の論理圧縮の可能性の向上を図ることができる。また、共通化した分だけFFの数は削減できるため、面積とリーク電流の削減を図ることができる。

【0136】

また、入力の共通性に着目しているため、論理圧縮の効果を上げ、組み合わせ回路の削減も期待することができる。また、実施の形態1と同様、論理圧縮度合いを用いた場合でも、回路動作を理解していなくても共通化マッピングをすることができる。

【0137】

以上のことから、実施の形態1,2によれば、排他的に動作しあう回路内部の入力の共通性を評価することにより、回路動作を理解していなくてもマージすることができる。したがって、回路の内部構成を意識することなく、LSIの消費電力の低減化および面積削減を図ることができるという効果を奏する。

【0138】

なお、実施の形態で説明した設計支援方法は、予め用意されたプログラムをパーソナル・コンピュータやワークステーション等のコンピュータで実行することにより実現することができる。このプログラムは、ハードディスク、フレキシブルディスク、CD−ROM、MO、DVD等のコンピュータで読み取り可能な記録媒体に記録され、コンピュータによって記録媒体から読み出されることによって実行される。またこのプログラムは、インターネット等のネットワークを介して配布することが可能な伝送媒体であってもよい。

【0139】

上述した実施の形態に関し、さらに以下の付記を開示する。

【0140】

(付記1)コンピュータを、

排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、前記一方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「一方のパス情報」)と、前記他方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「他方のパス情報」)と、を入力する入力手段、

前記入力手段によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成手段、

対象となる共通化テーブル群を参照することにより、前記対象となる共通化テーブルごとに、当該前記他方のパス情報内の前記他方の識別情報を前記一方の識別情報に変換する変換手段、

前記一方のパス情報および前記変換手段による変換後の他方のパス情報内における、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値を、前記共通化テーブルごとに算出する算出手段、

前記算出手段によって算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成する第2の作成手段、

前記第1および第2の作成手段によって作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定する設定手段、

前記設定手段によって設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択する選択手段、

前記選択手段によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成する併合手段、

として機能させることを特徴とする設計支援プログラム。

【0141】

(付記2)前記第2の作成手段は、

前記遺伝的アルゴリズムの交叉により、前記対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記1に記載の設計支援プログラム。

【0142】

(付記3)前記第2の作成手段は、

前記遺伝的アルゴリズムの突然変異により、前記対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記2に記載の設計支援プログラム。

【0143】

(付記4)前記第2の作成手段は、

前記遺伝的アルゴリズムのエリート選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を作成することを特徴とする付記2または3に記載の設計支援プログラム。

【0144】

(付記5)前記第2の作成手段は、

前記遺伝的アルゴリズムのルーレット選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を作成することを特徴とする付記2または3に記載の設計支援プログラム。

【0145】

(付記6)前記第2の作成手段は、

前記遺伝的アルゴリズムのエリート選択およびルーレット選択の混合選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を作成することを特徴とする付記2または3に記載の設計支援プログラム。

【0146】

(付記7)前記コンピュータを、

前記併合手段によって得られた共通回路情報内の共通のデータ保持素子の出力ネットと、前記一方の識別情報により特定されるデータ保持素子の出力ネットと、前記他方の識別情報により特定されるデータ保持素子の出力ネットとを対応付ける置換テーブルを作成する置換テーブル作成手段、

前記置換テーブル作成手段によって作成された置換テーブルを参照して、前記一方の回路情報に記述されている出力ネットを当該出力ネットに対応する前記共通のデータ保持素子の出力ネットに置換するとともに、前記他方の回路情報に記述されている出力ネットを当該出力ネットに対応する前記共通のデータ保持素子の出力ネットに置換する置換手段として機能させ、

前記併合手段は、

前記置換手段による置換後の前記一方の回路情報と前記置換手段による置換後の前記他方の回路情報と前記共通回路情報とを統合することにより、前記併合回路の回路情報を生成することを特徴とする付記1〜6のいずれか1つに記載の設計支援プログラム。

【0147】

(付記8)前記コンピュータを、

前記併合手段によって併合された併合回路の回路情報の論理合成結果を取得する取得手段として機能させることを特徴とする付記1〜7のいずれか1つに記載の設計支援プログラム。

【0148】

(付記9)コンピュータを、

排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、を入力する入力手段、

前記入力手段によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成手段、

対象となる共通化テーブル群内の共通化テーブルごとに、当該共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した仮併合回路の回路情報を生成する仮併合手段、

前記仮併合手段によって前記対象となる共通化テーブル群内の共通化テーブルごとに生成された前記仮併合回路の回路情報の論理合成結果を取得する仮取得手段、

前記仮取得手段によって取得された前記仮併合回路の回路情報ごとの論理合成結果から得られる前記仮併合回路に関する面積情報に基づいて、論理合成による論理圧縮度合いをあらわす評価値を、前記対象となる共通化テーブル群内の共通化テーブルごとに算出する算出手段、

前記算出手段によって算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成する第2の作成手段、

前記第1および第2の作成手段によって作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定する設定手段、

前記設定手段によって設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択する選択手段、

前記選択手段によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成する併合手段、

として機能させることを特徴とする設計支援プログラム。

【0149】

(付記10)前記生成手段は、

前記遺伝的アルゴリズムの交叉により、前記対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記9に記載の設計支援プログラム。

【0150】

(付記11)前記生成手段は、

前記遺伝的アルゴリズムの突然変異により、前記対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記10に記載の設計支援プログラム。

【0151】

(付記12)前記生成手段は、

前記遺伝的アルゴリズムのエリート選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記10または11に記載の設計支援プログラム。

【0152】

(付記13)前記生成手段は、

前記遺伝的アルゴリズムのルーレット選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記10または11に記載の設計支援プログラム。

【0153】

(付記14)前記生成手段は、

前記遺伝的アルゴリズムのエリート選択およびルーレット選択の混合選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記10または11に記載の設計支援プログラム。

【0154】

(付記15)前記コンピュータを、

前記併合手段によって得られた共通回路情報内の共通のデータ保持素子の出力ネットと、前記一方の識別情報により特定されるデータ保持素子の出力ネットと、前記他方の識別情報により特定されるデータ保持素子の出力ネットとを対応付ける置換テーブルを作成する置換テーブル作成手段、

前記置換テーブル作成手段によって作成された置換テーブルを参照して、前記一方の回路情報に記述されている出力ネットを当該出力ネットに対応する前記共通のデータ保持素子の出力ネットに置換するとともに、前記他方の回路情報に記述されている出力ネットを当該出力ネットに対応する前記共通のデータ保持素子の出力ネットに置換する置換手段として機能させ、

前記併合手段は、

前記置換手段による置換後の前記一方の回路情報と前記置換手段による置換後の前記他方の回路情報と前記共通回路情報とを統合することにより、前記併合回路の回路情報を生成することを特徴とする付記9〜14のいずれか1つに記載の設計支援プログラム。

【0155】

(付記16)前記コンピュータを、

前記併合手段によって併合された併合回路の回路情報の論理合成結果を取得する取得手段として機能させることを特徴とする付記9〜15のいずれか1つに記載の設計支援プログラム。

【0156】

(付記17)排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、前記一方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「一方のパス情報」)と、前記他方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「他方のパス情報」)と、を入力する入力手段と、

前記入力手段によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成手段と、

対象となる共通化テーブル群を参照することにより、前記対象となる共通化テーブルごとに、当該前記他方のパス情報内の前記他方の識別情報を前記一方の識別情報に変換する変換手段と、

前記一方のパス情報および前記変換手段による変換後の他方のパス情報内における、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値を、前記共通化テーブルごとに算出する算出手段と、

前記算出手段によって算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成する第2の作成手段と、

前記第1および第2の作成手段によって作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定する設定手段と、

前記設定手段によって設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択する選択手段と、

前記選択手段によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成する併合手段と、

を備えることを特徴とする設計支援装置。

【0157】

(付記18)排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、を入力する入力手段と、

前記入力手段によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成手段と、

対象となる共通化テーブル群内の共通化テーブルごとに、当該共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した仮併合回路の回路情報を生成する仮併合手段と、

前記仮併合手段によって前記対象となる共通化テーブル群内の共通化テーブルごとに生成された前記仮併合回路の回路情報の論理合成結果を取得する仮取得手段と、

前記仮取得手段によって取得された前記仮併合回路の回路情報ごとの論理合成結果から得られる前記仮併合回路に関する面積情報に基づいて、論理合成による論理圧縮度合いをあらわす評価値を、前記対象となる共通化テーブル群内の共通化テーブルごとに算出する算出手段と、

前記算出手段によって算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成する第2の作成手段と、

前記第1および第2の作成手段によって作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定する設定手段と、

前記設定手段によって設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択する選択手段と、

前記選択手段によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成する併合手段と、

を備えることを特徴とする設計支援装置。

【0158】

(付記19)コンピュータが、

排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、前記一方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「一方のパス情報」)と、前記他方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「他方のパス情報」)と、を入力する入力工程と、

前記入力工程によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成工程と、

対象となる共通化テーブル群を参照することにより、前記対象となる共通化テーブルごとに、当該前記他方のパス情報内の前記他方の識別情報を前記一方の識別情報に変換する変換工程と、

前記一方のパス情報および前記変換工程による変換後の他方のパス情報内における、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値を、前記共通化テーブルごとに算出する算出工程と、

前記算出工程によって算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成する第2の作成工程と、

前記第1および第2の作成工程によって作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定する設定工程と、

前記設定工程によって設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択する選択工程と、

前記選択工程によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成する併合工程と、

を実行することを特徴とする設計支援方法。

【0159】

(付記20)コンピュータが、

排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、を入力する入力工程と、

前記入力工程によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成工程と、

対象となる共通化テーブル群内の共通化テーブルごとに、当該共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した仮併合回路の回路情報を生成する仮併合工程と、

前記仮併合工程によって前記対象となる共通化テーブル群内の共通化テーブルごとに生成された前記仮併合回路の回路情報の論理合成結果を取得する仮取得工程と、

前記仮取得工程によって取得された前記仮併合回路の回路情報ごとの論理合成結果から得られる前記仮併合回路に関する面積情報に基づいて、論理合成による論理圧縮度合いをあらわす評価値を、前記対象となる共通化テーブル群内の共通化テーブルごとに算出する算出工程と、

前記算出工程によって算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成する第2の作成工程と、

前記第1および第2の作成工程によって作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定する設定工程と、

前記設定工程によって設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択する選択工程と、

前記選択工程によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成する併合工程と、

を実行することを特徴とする設計支援方法。

【符号の説明】

【0160】

400 設計支援装置

401 入力部

402 第1の作成部

403 評価関数情報作成部

404 共通化テーブル評価/再作成部

405 併合部

406 置換テーブル作成部

407 置換部

408 取得部

421 変換部

422 算出部

423 第2の作成部

424 設定部

425 選択部

3000 設計支援装置

3001 仮併合部

3002 仮取得部

【技術分野】

【0001】

本開示技術は、LSI(Large Scale Integration)の設計を支援する設計支援プログラム、設計支援装置、および設計支援方法に関する。

【背景技術】

【0002】

LSIには、ブロックと呼ばれる機能モジュールが多数搭載されている。LSIに搭載された複数のブロックには、選択信号によって動作モードが使用/未使用に切り替わるものがある。選択信号によって未使用とされたブロックであっても、LSI上である程度の面積を占めており、またある程度の待機電流を消費している。未使用ブロックの消費電流削減方法は、クロックゲートによりクロック端子を制御する程度であったが、これではリーク電流低減や面積削減には繋がらない。また、消費電力の低減および面積削減のため、排他的に動作する複数のブロックから共有化できる資産情報を抜き出す技術が開示されている(たとえば、下記特許文献1を参照。)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2000−123059号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来技術では、まず、共有化に先だって、資産情報を抜き出すためにブロック内の内部構成を認識しなければならないという問題があった。特に、ブロック内に組み合わせ回路がある場合、組み合わせ回路の複雑度に比例して資産情報の抜き出しが困難であったり、できるとしても長期化したりするという問題があった。

【0005】

本開示技術は、上述した従来技術による問題点を解消するため、回路の内部構成を意識することなく、LSIの消費電力の低減化および面積削減を図ることができる設計支援プログラム、設計支援装置、および設計支援方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上述した課題を解決し、目的を達成するため、第1の開示技術は、排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、前記一方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「一方のパス情報」)と、前記他方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「他方のパス情報」)と、を入力し、入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成し、対象となる共通化テーブル群を参照することにより、前記対象となる共通化テーブルごとに、当該前記他方のパス情報内の前記他方の識別情報を前記一方の識別情報に変換し、前記一方のパス情報および変換後の他方のパス情報内における、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値を、前記共通化テーブルごとに算出し、算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成し、作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定し、設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択し、選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成することを要件とする。

【0007】

第2の開示技術は、排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、を入力し、入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成し、対象となる共通化テーブル群内の共通化テーブルごとに、当該共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した仮併合回路の回路情報を生成し、前記対象となる共通化テーブル群内の共通化テーブルごとに生成された前記仮併合回路の回路情報の論理合成結果を取得し、取得された前記仮併合回路の回路情報ごとの論理合成結果から得られる前記仮併合回路に関する面積情報に基づいて、論理合成による論理圧縮度合いをあらわす評価値を、前記対象となる共通化テーブル群内の共通化テーブルごとに算出し、算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成し、作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定し、設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択し、選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成することを要件とする。

【発明の効果】

【0008】

本設計支援プログラム、設計支援装置、および設計支援方法によれば、回路の内部構成を意識することなく、LSIの消費電力の低減化および面積削減を図ることができるという効果を奏する。

【図面の簡単な説明】

【0009】

【図1】本開示技術の一例を示す説明図である。

【図2】図1(B)に示したマージの具体例を図形化した説明図である。

【図3】実施の形態1にかかる設計支援装置のハードウェア構成を示すブロック図である。

【図4−1】実施の形態1にかかる設計支援装置の機能的構成1を示すブロック図である。

【図4−2】実施の形態1にかかる設計支援装置の機能的構成2を示すブロック図である。

【図5】排他動作情報を示す説明図である。

【図6−1】FF情報抽出部によって抽出された回路Aに関するFF情報の一例を示す説明図である。

【図6−2】FF情報抽出部によって抽出された回路Bに関するFF情報の一例を示す説明図である。

【図7−1】パス情報抽出部によって抽出された回路Aに関するパス情報を示す説明図である。

【図7−2】パス情報抽出部によって抽出された回路Bに関するパス情報を示す説明図である。

【図8−1】回路AのFF情報に関するラベル化FF情報を示す説明図である。

【図8−2】回路BのFF情報に関するラベル化FF情報を示す説明図である。

【図9】第1世代の共通化テーブル群の一例を示す説明図である。

【図10−1】図7−1に示した回路Aのパス情報のラベル変換例を示す説明図である。

【図10−2】図7−2に示した回路Bのパス情報のラベル変換例を示す説明図である。

【図11−1】回路Aのパス情報をラベル化したラベル化パス情報を示す説明図である。

【図11−2】回路Bのパス情報をラベル化したラベル化パス情報を示す説明図である。

【図12】ラベル化パス情報の置換処理を示す説明図である。

【図13】カウント処理による計数テーブルを示す説明図である。

【図14】シグマスケーリング処理結果を示す説明図である。

【図15】選択処理の内容を示す説明図である。

【図16】次世代の親となる共通化テーブルを示す説明図である。

【図17】交叉の一例を示す説明図である。

【図18】突然変異の処理内容を示す説明図である。

【図19】次世代の共通化テーブル群を示す説明図である。

【図20】併合回路ABの接続イメージを示す説明図である。

【図21】共通化FFとセレクタの共通回路情報を示す説明図である。

【図22】出力ネット置換テーブルを示す説明図である。

【図23】回路Aの固有化前後の回路情報を示す説明図である。

【図24】回路Bの固有化前後の回路情報を示す説明図である。

【図25】併合回路ABの回路情報を示す説明図である。

【図26】実施の形態1にかかる設計支援装置の設計支援処理手順を示すフローチャートである。

【図27】図26に示した共通化テーブル評価/次世代作成処理(ステップS2605)の詳細な処理手順を示すフローチャートである。

【図28】図27に示した次世代作成処理(ステップS2706)の詳細な処理手順を示すフローチャートである。

【図29】図26に示したマージ処理(ステップS2606)の詳細な処理手順を示すフローチャートである。

【図30−1】実施の形態2にかかる設計支援装置の機能的構成1を示すブロック図である。

【図30−2】実施の形態2にかかる設計支援装置の機能的構成2を示すブロック図である。

【図31】セル面積を対応付けた第1世代の共通化テーブルを示す説明図である。

【図32】シグマスケーリング処理結果を示す説明図である。

【図33】実施の形態2にかかる設計支援装置の設計支援処理手順を示すフローチャートである。

【図34】図33に示した仮マージ処理(ステップS3304)の詳細な処理手順を示すフローチャートである。

【図35】図33に示した仮論理合成結果取得処理(ステップS3305)の詳細な処理手順を示すフローチャートである。

【発明を実施するための形態】

【0010】

以下に添付図面を参照して、本開示技術にかかる設計支援装置、設計支援方法、および設計支援プログラムの好適な実施の形態を詳細に説明する。

【0011】

<実施の形態1>

図1は、本開示技術の一例を示す説明図である。本開示技術は、排他的に動作しあう2つのブロックを1つのブロックにマージする技術である。(A)は、排他的に動作しあう回路を示している。回路Aは、クロックゲートGAにより動作制御されるブロックであり、回路Bは、クロックゲートGBにより動作制御されるブロックである。クロック信号CLKは選択信号Sに応じて回路Aまたは回路Bに供給される。これにより、回路Aおよび回路Bは排他的な動作をする。すなわち、回路Aが動作中であれば、回路Bは動作せず、回路Bが動作中であれば、回路Aは動作しない。

【0012】

図2は、図1(B)に示したマージの具体例を図形化した説明図である。図の簡略化のため、クロック信号CLKは省略している。回路Aは、組み合わせ回路LA0とその出力を保持して回路Aから出力するフリップフロップなどのデータ保持素子(以下、「FF」とする)FFA0を有する。また、回路Aは、組み合わせ回路LA1とその出力を保持して回路Aから出力するFFA1を有する。また、回路Aは、組み合わせ回路LA2とその出力を保持して回路Aから出力するFFA2を有する。

【0013】

回路Bは、組み合わせ回路LB0とその出力を保持して回路Bから出力するFFB0を有する。また、回路Bは、組み合わせ回路LB1とその出力を保持して回路Bから出力するFFB1を有する。また、回路Bは、組み合わせ回路LB2とその出力を保持して回路Bから出力するFFB2を有する。

【0014】

回路Aと回路Bは排他的な動作をするため、回路Aが動作するとは、その内部の組み合わせ回路LA0〜LA2が動作していることを意味しており、回路Bが動作するとは、その内部の組み合わせ回路LB0〜LB2が動作していることを意味している。

【0015】

したがって、併合回路ABでは、組み合わせ回路LA0〜LA2と組み合わせ回路LB0〜LB2とが排他的な動作をするように、選択回路200〜202を挿入する。そして、選択回路200〜202の出力先にFF0〜FF2を接続する。併合回路ABでは、選択信号S=0のとき、組み合わせ回路LA0〜LA2が動作し、S=1のとき、組み合わせ回路LB0〜LB2が動作する。

【0016】

このように、組み合わせ回路LA0〜LA2,LB0〜LB2とFFA0〜FFA2,FFB0〜FFB2の接続関係さえ分かっていれば、組み合わせ回路LA0〜LA2,LB0〜LB2の内部構成を意識する必要はない。また、マージ前の回路Aおよび回路Bと併合回路ABを比較すると、FFA0,FFB0がマージされてFF0となる。同様に、FFA1,FFB1がマージされてFF1となり、FFA2,FFB2がマージされてデータ保持素子FF2となる。

【0017】

このあと、論理合成ツールにより併合回路ABを論理圧縮することで、併合回路ABの回路規模が縮小化する。このように、本開示技術では、回路Aおよび回路Bの組み合わせ回路LA0〜LA2,LB0〜LB2の内部構成を意識しないアルゴリズムにより併合回路ABを生成して、リーク電流の低減化と回路面積の削減を図ることができる。

【0018】

(設計支援装置のハードウェア構成)

図3は、実施の形態1にかかる設計支援装置のハードウェア構成を示すブロック図である。図3において、設計支援装置は、CPU(Central Processing Unit)301と、ROM(Read‐Only Memory)302と、RAM(Random Access Memory)303と、磁気ディスクドライブ304と、磁気ディスク305と、光ディスクドライブ306と、光ディスク307と、ディスプレイ308と、I/F(Interface)309と、キーボード310と、マウス311と、スキャナ312と、プリンタ313と、を備えている。また、各構成部はバス300によってそれぞれ接続されている。

【0019】

ここで、CPU301は、設計支援装置の全体の制御を司る。ROM302は、ブートプログラムなどのプログラムを記憶している。RAM303は、CPU301のワークエリアとして使用される。磁気ディスクドライブ304は、CPU301の制御にしたがって磁気ディスク305に対するデータのリード/ライトを制御する。磁気ディスク305は、磁気ディスクドライブ304の制御で書き込まれたデータを記憶する。

【0020】

光ディスクドライブ306は、CPU301の制御にしたがって光ディスク307に対するデータのリード/ライトを制御する。光ディスク307は、光ディスクドライブ306の制御で書き込まれたデータを記憶したり、光ディスク307に記憶されたデータをコンピュータに読み取らせたりする。

【0021】

ディスプレイ308は、カーソル、アイコンあるいはツールボックスをはじめ、文書、画像、機能情報などのデータを表示する。このディスプレイ308は、たとえば、CRT、TFT液晶ディスプレイ、プラズマディスプレイなどを採用することができる。

【0022】

インターフェース(以下、「I/F」と略する。)309は、通信回線を通じてLAN(Local Area Network)、WAN(Wide Area Network)、インターネットなどのネットワーク314に接続され、このネットワーク314を介して他の装置に接続される。そして、I/F309は、ネットワーク314と内部のインターフェースを司り、外部装置からのデータの入出力を制御する。I/F309には、たとえばモデムやLANアダプタなどを採用することができる。

【0023】

キーボード310は、文字、数字、各種指示などの入力のためのキーを備え、データの入力をおこなう。また、タッチパネル式の入力パッドやテンキーなどであってもよい。マウス311は、カーソルの移動や範囲選択、あるいはウィンドウの移動やサイズの変更などをおこなう。ポインティングデバイスとして同様に機能を備えるものであれば、トラックボールやジョイスティックなどであってもよい。

【0024】

スキャナ312は、画像を光学的に読み取り、設計支援装置内に画像データを取り込む。なお、スキャナ312は、OCR(Optical Character Reader)機能を持たせてもよい。また、プリンタ313は、画像データや文書データを印刷する。プリンタ313には、たとえば、レーザプリンタやインクジェットプリンタを採用することができる。

【0025】

(設計支援装置の機能的構成)

図4−1は、実施の形態1にかかる設計支援装置の機能的構成1を示すブロック図である。図4−1において、設計支援装置400は、入力部401と、第1の作成部402と、評価関数情報作成部403と、共通化テーブル評価/再作成部404と、併合部405と、置換テーブル作成部406と、置換部407と、取得部408と、を備える。また、共通化テーブル評価/再作成部404の詳細は図4−2に示す。図4−1の各機能は、具体的には、たとえば、図3に示したROM302、RAM303、磁気ディスク305に記憶されたプログラムをCPU301に実行させることにより、またはI/F309により、その機能を実現する。

【0026】

また、設計支援装置400に与えられる初期情報として、互いに排他的動作をしあう回路Aおよび回路Bの回路情報(たとえば、ネットリストやRTL(Register Transfer Level)記述)DA,DBと、回路Aおよび回路Bの排他動作情報とを用意する。

【0027】

図5は、排他動作情報を示す説明図である。排他動作情報とは、互いに排他的に動作する回路の組み合わせを示す情報である。回路A項目と回路B項目には、それぞれの回路を一意に特定する識別情報が記憶されている。たとえば、1行目のレコードでは、回路C1と回路C2とが排他的に動作することを示している。設計者は、排他動作情報を参照して、回路A項目の回路(たとえば、回路C1)の回路情報と回路B項目の回路(たとえば、回路C2)の回路情報を設計支援装置に与える。

【0028】

図4−1に戻って、入力部401は、FF情報抽出部411と、パス情報抽出部412とを備える。FF情報抽出部411は、回路Aおよび回路Bに含まれているFFを回路情報DA,DBから抽出する機能を有する。具体的には、たとえば、FF情報抽出部411は既存のツールにより構成され、回路Aおよび回路Bに含まれているFFのインスタンス情報となるFF情報を回路情報DA,DBから抽出する。

【0029】

図6−1は、FF情報抽出部411によって抽出された回路Aに関するFF情報の一例を示す説明図である。図6−1に示したFF情報600Aには、回路Aに含まれているFFのインスタンス名(たとえば、“AAA_inst/ac01_reg/CLK”)が記述されている。

【0030】

図6−2は、FF情報抽出部411によって抽出された回路Bに関するFF情報の一例を示す説明図である。図6−2に示したFF情報600Bには、回路Bに含まれているFFのインスタンス名(たとえば、“BBB_inst/div01_reg/CLK”)が記述されている。

【0031】

また、図4−1において、パス情報抽出部412は、回路Aおよび回路Bに含まれているパスを回路情報DA,DBから抽出する機能を有する。具体的には、たとえば、パス情報抽出部412は既存のツールにより構成され、回路Aおよび回路Bに含まれているパス情報DPA,DPBを回路情報DA,DBから抽出する。パス情報DPA,DPBとは、パスの始点となるFFのインスタンス名とパスの終点となるFFのインスタンス名との組み合わせである。

【0032】

図7−1は、パス情報抽出部412によって抽出された回路Aに関するパス情報DPAを示す説明図である。図7−1に示したパス情報DPAには、出力先(図7−1では“Endpoint”と表記)となるFFのインスタンス名と、入力元(図7−1では“Startpoint”と表記)となるFFのインスタンス名を記憶している。

【0033】

図7−2は、パス情報抽出部412によって抽出された回路Bに関するパス情報DPBを示す説明図である。図7−2に示したパス情報DPBには、終点(図7−2では“Endpoint”と表記)となるFFのインスタンス名と、始点(図7−2では“Startpoint”と表記)となるFFのインスタンス名を記憶している。

【0034】

このように、入力部401により回路AのFF情報DFAおよびパス情報DPA、回路BのFF情報DFBおよびパス情報DPBを得ることができる。なお、回路情報DA,DBからの抽出ではなく、回路AのFF情報DFAおよびパス情報DPA、回路BのFF情報DFBおよびパス情報DPBを外部から入力することとしてもよい。

【0035】

図4−1において、第1の作成部402は、FF情報DFA,DFBから第1世代の共通化テーブル群T1を作成する機能を有する。第1世代の共通化テーブル群T1とは、回路AのFFと回路BのFFとの対応関係を定義するテーブルの集合である。第1世代としたのは、後述するように、第n世代までの共通化テーブル群Tnを作成するからである。

【0036】

第1世代の共通化テーブル群T1は、具体的には、たとえば、まず、入力されたFF情報DFA,DFBについて、回路A,B別にFFのインスタンスごとに固有のラベルを割り振る。ラベルは連続番号とする。また、入力ネットと出力ネットも回路情報DA,DBから抽出する。入力ネットとは、FFのデータ入力端子に接続されているネットである。また、出力ネットとは、FFのデータ出力端子に接続されているネットである。このように、FFごとにインスタンス名、入力ネット、出力ネット、ラベルを記述した情報を、ラベル化FF情報と称す。

【0037】

図8−1は、回路AのFF情報に関するラベル化FF情報を示す説明図である。ラベル化FF情報800Aにおいて、回路AのFFには、ラベル項目にラベルA0〜A9が割り当てられている。

【0038】

図8−2は、回路BのFF情報に関するラベル化FF情報を示す説明図である。ラベル化FF情報800Bにおいて、回路BのFFには、ラベル項目にラベルB0〜B7が割り当てられている。第1の作成部402は、ラベル化FF情報800A,800Bから第1世代の共通化テーブル群T1を作成する。

【0039】

図9は、第1世代の共通化テーブル群T1の一例を示す説明図である。第1の作成部402は、具体的には、たとえば、2つのラベル化FF情報800A,800BのうちFF数が多い方(同数であればどちらでもよい)のラベル化FF情報のラベル列を基準レコードとする。図9の場合は、回路Aのラベル化FF情報800AのラベルA0〜A9を基準レコードに割り当てている。

【0040】

そして、回路Bのラベル化FF情報800BのラベルB0〜B7を基準レコードのラベルにランダムに割り当てる。該当するラベルがない場合は、“*”(相手がいない)を割り当てる。そして、共通化テーブルをランダム発生でN個作成する。Nは任意のレコード数である。各共通化テーブルには、固有のテーブル番号(図9では、T1−01,T1−02,…,T1−N)を割り振る。テーブル番号ごとのレコードが共通化テーブルである。N個の共通化テーブルが第1世代の共通化テーブル群T1となる。

【0041】

図4−1において、評価関数情報作成部403は、パス情報DPA,DPBとラベル化FF情報800A,800Bとに基づいて、評価関数情報を作成する機能を有する。具体的には、たとえば、パス情報に記述されているFFのインスタンス名を、ラベル化FF情報800A,800Bのラベル項目を参照して、ラベルに変換する。

【0042】

図10−1は、図7−1に示した回路Aのパス情報DPAのラベル変換例を示す説明図である。たとえば、回路Aのラベル化FF情報800Aにおいて、インスタンス名:AAA_inst/ac01_regのFFのラベルは“A0”である。したがって、図10−1では、図7−1の「AAA_inst/ac01_reg」が「A0」に変換されている。

【0043】

図10−2は、図7−2に示した回路Bのパス情報DPBのラベル変換例を示す説明図である。たとえば、回路Bのラベル化FF情報800Bにおいて、インスタンス名:BBB_inst/div01_regのFFのラベルは“B0”である。したがって、図10−2では、図7−2の「BBB_inst/div01_reg」が「B0」に変換されている。また、出力先とその入力元を変換されたラベルで対応付けたラベル化パス情報を生成する。各ラベル化パス情報が評価関数情報となる。

【0044】

図11−1は、回路Aのパス情報DPAをラベル化したラベル化パス情報を示す説明図である。ラベル化パス情報1101Aにおいて、たとえば、一行目のレコードは、入力元がラベル名A0,A1,A4,A5,A7のFFであり、出力先がラベル名A0のFFとなるパスを示している。

【0045】

図11−2は、回路Bのパス情報DPBをラベル化したラベル化パス情報を示す説明図である。ラベル化パス情報1101Bにおいて、たとえば、一行目のレコードは、入力元がラベル名B0,B2,B3のFFであり、出力先がラベル名B0のFFとなるパスを示している。

【0046】

また、図4−1において、共通化テーブル評価/再作成部404は、共通化テーブル評価処理と次世代作成処理を実行する機能を有する。具体的には、以下の(1)〜(6)を実行する。

【0047】

(1)回路Aおよび回路Bから共通化可能な回路のFFをすべてリストアップする。

(2)つぎに、ランダム(もしくは任意)に共通化マッピングを行う。

(3)そして、FFにつながる入力の共通性をチェックして共通性が高いほど高得点をつける。

(4)すべてのFFの点数付けが終わったところで合計点を計算する。

(5)別の共通化マッピングを、遺伝的アルゴリズムを用いて作成し、(3)〜(4)を再度実行する。

(6)規定回数(世代数となる)(2)〜(5)を繰り返して、一番合計点の高かった共通化テーブルを採用する。

【0048】

図4−2は、実施の形態1にかかる設計支援装置の機能的構成2を示すブロック図である。図4−2では、共通化テーブル評価/再作成部404の詳細な機能的構成を示している。まず、変換部421は、対象となる共通化テーブル群を参照することにより、対象となる共通化テーブルごとに、当該他方のパス情報内の他方の識別情報を一方の識別情報に変換する機能を有する。対象となる共通化テーブル群は後述の設定部424により設定されるが、具体的には、作成された共通化テーブル群の中で最新世代の共通化テーブル群を対象となる共通化テーブル群とする。

【0049】

変換部421は、具体的には、たとえば、ラベル化パス情報1101A,1101Bの変換処理を実行する。ラベル化パス情報1101A,1101Bの変換処理では、変換対象をラベル化パス情報1101A,1101Bのうち基準レコードに選ばれなかった回路Bのラベル化パス情報1101Bとする。そして、選ばれた共通化テーブルにより、回路Bのラベル化パス情報1101Bを置換する。

【0050】

図12は、ラベル化パス情報の置換処理を示す説明図である。ここでは、共通化テーブルT1−01を例に挙げて説明する。回路Bのラベル化パス情報1101B内のラベルを、選択した共通化テーブルT1−01を参照して、基準レコードのラベルに置換する。たとえば、共通化テーブルT1−01のラベル“B3”は、基準レコードのラベル“A1”に対応している。したがって、回路Bのラベル化パス情報1101B内の“B3”を“A1”に置換する。置換後のラベル化パス情報1201Bは、回路AのラベルA0〜A9で表現されることとなる。

【0051】

また、図4−2において、算出部422は、一方のパス情報および変換部421による変換後の他方のパス情報内における、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値を、共通化テーブルごとに算出する機能を有する。

【0052】

算出部422は、具体的には、たとえば、カウント処理を実行する。カウント処理では、変換されていない方の回路Aのラベル化パス情報1101Aと変換後の回路Bのラベル化パス情報1201Bとを比較する。そして、出力先ごとに共通項となるラベルを抽出し、その数を計数する。出力先ごとの計数値の合計が、選択された共通化テーブルT1−01の得点、すなわち、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値となる。

【0053】

図13は、カウント処理による計数テーブルを示す説明図である。図13では、図12で示した置換後のラベル化パス情報1201Bを用いて説明する。カウント処理では、置換されていない回路Aのラベル化パス情報1101Aを呼び出す。そして、出力先ごとに、回路Aのラベル化パス情報1101Aの入力元と回路Bの置換後のラベル化パス情報1201Bの入力元を対応付ける。そして、出力先ごとに両入力元に共通に存在するラベルを共通項として抽出する。

【0054】

たとえば、ラベル:A0の出力先では、共通項は、ラベル:A0,A1の2個である。したがって計数値は2となる。このようにして、出力先ごとに計数値をカウントし、その総計が選択された評価テーブルT1−01の得点となる。図13の例では、19得点となる。共通化テーブル評価処理では、全共通化テーブルT1−01〜T1−Nに対し、変換処理とカウント処理を実行することで、共通化テーブルごとの得点を得ることができる。

【0055】

また、図4−2において、第2の作成部423は、算出部422によって算出された評価値に基づいて、遺伝的アルゴリズムにより、対象となる共通化テーブル群から次世代の共通化テーブル群を作成する機能を有する。

【0056】

第2の作成部423は、具体的には、たとえば、規定回数を超えていない場合、対象となる共通化テーブル群のうち、最高得点となった共通化テーブルを用いて、次世代作成処理を実行する。なお、最高得点が複数ある場合はランダムに選択する。規定回数を超えている場合は、最高得点となった共通化テーブルを最適な共通化テーブルとして併合部405に出力することとなる。規定回数とは上限世代数であり、次世代作成処理は規定回数まで繰り返し実行される。次世代作成処理は、スケーリング処理、選択処理、次世代テーブル生成処理を実行する。

【0057】

次世代作成処理には遺伝的アルゴリズムを適用する。遺伝的アルゴリズムとは、自然淘汰により最適な遺伝子が残ってきたようにシステムの中で自然淘汰のシミュレーションを実行し、最適解を求めようとするアルゴリズムである。遺伝的アルゴリズムは、広範囲の探索空間に対して少ない試行回数で最適解を求めやすい利点がある。必ず最適解が求まる訳ではないが、「最適ではないとしても効果が高いと思われる組み合わせ」を探す場合には単なるランダム検索よりも効率が良い。

【0058】

遺伝的アルゴリズムでは、解のセットをパラメータとして一つのデータにまとめて遺伝子に見立てる。はじめにいくつもの遺伝子を用意し、それぞれを評価関数にかけてより適合度の高いと思われる遺伝子を残す。実施の形態では、評価テーブルを遺伝子に見立て、今世代の生き残りとなる親の共通化テーブルを選択する。そして、親の遺伝子(親の共通化テーブル)を引き継ぐため、親間で交叉や突然変異をおこない、次世代の子となる共通化テーブルを生成する。

【0059】

最後に、親の共通化テーブルと子の共通化テーブルとを組み合わせることで、次世代の共通化テーブルを生成する。次世代の共通化テーブルは、規定回数を超えるまで共通化テーブル評価処理に与えられる。

【0060】

まず、スケーリング処理を実行する。スケーリング処理とは、つぎに実行する選択処理での選択格差を広げる処理である。スケーリング処理を実行することで、高得点の共通化テーブルを選択しやすくすることができる。実施の形態では、シグマスケーリングを例に挙げて説明する。シグマスケーリングでは、各共通化テーブルの得点を、下記式(1)を用いて変換する。

【0061】

f´=f−(favg−c×σ)・・・(1)

【0062】

ただし、f´はスケーリング処理後の得点(ただし、f´が負のときはf´=0とする)。fはスケーリング処理前の得点、favgはスケーリング処理前の得点の平均値、cは任意の変数(本例ではc=2)、σはスケーリング処理前の標準偏差(ただし、σ=0のときは、σ=1とする)である。

【0063】

図14は、シグマスケーリング処理結果を示す説明図である。図14では、共通化テーブルの個数NをN=20としている。平均値favgと標準偏差σは、共通化テーブルの全得点から算出する。なお、スケーリング処理では、シグマスケーリングのほか、線形スケーリングやべき乗スケーリングを用いてもよい。

【0064】

つぎに、選択処理を実行する。選択処理では、N個の共通化テーブルの中から次世代に残す一部(ここではN/2個)の共通化テーブルを選択する。選択処理では、スケーリング処理を実行した場合は、スケーリング処理後の得点を用い、スケーリング処理を実行していない場合は、共通化テーブルの得点をそのまま用いる。

【0065】

選択処理では、エリート選択とルーレット選択とを組み合わせる。エリート選択とは、最高得点のテーブルを無条件に選択する選択方法である。最高得点が複数ある場合にはランダムで1つ選択する。

【0066】

ルーレット選択とは、選択確率に基づいて共通化テーブルを選択する選択方法である。選択確率とは、共通化テーブルごとに、全得点の合計点を共通化テーブルの得点で割った値である。本例では、次世代に残す共通化テーブルの個数はN/2であり、エリート選択された共通化テーブルの個数は1であるため、(N/2−1)回分、ルーレット選択をおこなう。エリート選択では、高得点の共通化テーブルしか残らないが、ルーレット選択も適用することで、選択に多様性を残すことができる。すなわち、得点が低くても生き残る可能性を残すためである。

【0067】

ルーレット選択では、まず、ランダム関数により選択値s(0≦s≦1)を生成する。つぎに、選択確率の高い順から選択確率を選び、選ばれた選択確率を選択値sから引く。そして、選択値sが0以下となったときの共通化テーブルを次世代へ生き残る親の遺伝子として選択する。

【0068】

図15は、選択処理の内容を示す説明図である。図15の点数テーブルでは、共通化テーブルT1−10が最高得点(11.9357)であるため、エリート選択される。また、共通化テーブルごとに選択確率が算出されている。

【0069】

図16は、次世代の親となる共通化テーブルを示す説明図である。本例では、エリート選択された共通化テーブルT1−10とルーレット選択された9個の共通化テーブルが次世代の親の遺伝子として引き継がれる。

【0070】

つぎに、子の共通化テーブルを生成する。子の共通化テーブルの生成には、交叉と突然変異を適用する。遺伝的アルゴリズムの交叉手法は数多くあるが、実施の形態は配置を基準とした交叉を用いる。次世代の親となるN/2個の共通化テーブルを、2個ずつのペアに分ける。ペアの選択は適当でよいが、今回は選択順に(T1−10,T1−01),(T1−16,T1−17),(T1−05,T1−02),(T1−10,T1−20),(T1−02,T1−08)とする。

【0071】

図17は、交叉の一例を示す説明図である。(A)において親の共通化テーブルのペアを選ぶ。ここでは、親の共通化テーブルのペアを(親1,親2)とする。つぎに、(B)において、ペアとなった親どうしの対応するラベル((B)中、ハッチングを施した箇所)をランダムに選択する。選択個数もランダム(本例では4箇所)である。

【0072】

そして、(C)において、子のペア(子1,子2)を用意する。子のペアは初期状態では空である。子1のレコードに、(B)における親1の選択箇所のラベルを選択箇所と同位置に代入する。同様に、子2のレコードに、(B)における親2の選択箇所のラベルを選択箇所と同位置に代入する。それぞれ一方の親の遺伝子を残すためである。

【0073】

つぎに、(D)において、子1のレコードの空き領域に、子1にはない親2のラベルを左側から書き込む。すなわち、親2のラベル(B0,B3,B2,B6,B5,B4,*,B1,*,B7)から子1のラベル(B3,*,B0,B5)を除いたラベル(B2,B6,B4,B1,*,B7)を書き込む。他方の親である親2の遺伝子を残すためである。

【0074】

同様に、(E)において、子2のレコードの空き領域に、子2にはない親1のラベルを左側から書き込む。すなわち、親1のラベル(B4,B3,B2,*,B0,B6,*,B5,B1,B7)から子2のラベル(B3,B6,B5,B1)を除いたラベル(B4,B2,*,B0,*,B7)を書き込む。他方の親である親1の遺伝子を残すためである。

【0075】

このようにして、(F)に示したように、親1および親2の共通化テーブルから子1および子2の共通化テーブルが生成される。このような交叉を、親の共通化テーブルのペア(T1−10,T1−01),(T1−16,T1−17),(T1−05,T1−02),(T1−10,T1−20),(T1−02,T1−08)ごとに実行する。これにより、N/2個の子の共通化テーブルが生成されることとなる。

【0076】

つぎに、突然変異について説明する。突然変異では、新しく生成されたN/2個の子の共通化テーブルに対して、低確率でランダムに配置を入れ替える。突然変異を実行することで探索空間を広げることができる。

【0077】

図18は、突然変異の処理内容を示す説明図である。(A)は突然変異前の子の共通化テーブル群を示しており、(B)は突然変異後の子の共通化テーブル群を示している。(A)において、まず、子の共通化テーブル1つ1つに対して突然変異を発生させるかチェックをおこなう。発生確率は1%程度とする。具体的には、たとえば、確率t(0≦t≦1)をランダムに発生して、各子の共通化テーブルに割り当てる。

【0078】

そして、発生確率以下となる確率tを持つ子の共通化テーブルに対して、ランダムに2つの配置を選択する((A)のハッチングを施した箇所)。そして、選択箇所のラベルを入れ替える。これにより、(B)に示した突然変異後の子の共通化テーブル群を得ることができる。なお、突然変異の実行は任意である。最後に次世代の共通化テーブル群Tiの生成を実行する。

【0079】

図19は、次世代の共通化テーブル群Tiを示す説明図である。具体的には、たとえば、親の共通化テーブル(図16を参照)と子の共通化テーブル(図18を参照)を組み合わせることにより、次世代の共通化テーブル群Tiが生成される。

【0080】

また、図4−2において、設定部424は、第1および第2の作成部423によって作成された共通化テーブル群のうち最新世代の共通化テーブル群を対象となる共通化テーブル群に設定する機能を有する。具体的には、たとえば、第1世代の共通化テーブル群T1のみが作成されている場合、第1世代の共通化テーブル群T1が最新世代の共通化テーブル群となるため、対象とする共通化テーブル群として設定して、変換部421にわたす。また、第2の作成部423により次世代の共通化テーブル群Tiが順次作成された場合、最新世代の共通化テーブル群Tiを対象とする共通化テーブル群として設定して、変換部421にわたす。

【0081】

選択部425は、設定部424によって設定された対象となる共通化テーブル群の中から特定の共通化テーブルを選択する機能を有する。具体的には、たとえば、第2の作成部423により規定回数nを超えた場合、現時点での最新世代の共通化テーブル群Tnの中から、特定の共通化テーブルTn−xを選択する。より具体的には、共通化テーブル群Tnのうち、図13に示した計数値が最高得点となる共通化テーブルを特定の共通化テーブルTn−xとして選択する。選択された特定の共通化テーブルTn−xは記憶装置内の特定の領域に書き込まれる。

【0082】

また、図4−1において、併合部405は、選択部425によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報(たとえば、回路Aの回路情報DA)および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報(たとえば、回路Bの回路情報DB)を、一方の識別情報により特定されるデータ保持素子の入力ネットおよび他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換する。そして、変換された共通回路情報により、一方の回路情報および他方の回路情報を併合した併合回路の回路情報DABを生成する機能を有する。

【0083】

具体的には、たとえば、ラベル化FF情報800A,800Bと、共通化テーブル評価/再作成部404から最終出力される特定の共通化テーブルTn−xを用いて、回路AのFFと回路BのFFとを共通化した共通化FFとセレクタのネットリストを生成する。

【0084】

図20は、併合回路ABの接続イメージを示す説明図である。特定の共通化テーブルTn−xは、回路Aのラベル列からなる基準レコードと回路Bのラベル列からなる最高得点のレコードの組み合わせである。両レコードの上下のラベルが対応しあい、排他的な動作をする。したがって、上下のラベルに共通化するFFとそのFFの入力に接続される2入力1出力のセレクタを生成する。なお、いずれか一方のラベルが「*」である場合は、セレクタが不要となる。

【0085】

たとえば、共通化テーブルの一列目の上下のラベルペア(A0,B3)については、ラベルA0に対応する入力ネットac01_inをセレクタの一方の入力ネット(ac01_in_A)とする。同様に、ラベルB3に対応する入力ネットdiv04_inをセレクタの他方の入力ネット(div04_in_B)とする。入力ネット名を固有化するため、入力ネット名の末尾に“_A”、“_B”を付している。ff0_out〜ff9_outは共通化FF1〜9の出力ネットを示している。

【0086】

図21は、共通化FFとセレクタの共通回路情報(ネットリスト)を示す説明図である。図21に支援したネットリストは、併合部405により生成された、回路AのFFと回路BのFFとを共通化した共通化FFとセレクタのネットリスト(共通回路情報NFS)である。図21中、SFF ff0_reg〜SFF ff9_regは、共通化FF1〜9に関する記述である。また、MUX Usel0〜MUX Usel9は、共通化FF1〜FF9の入力に接続されるセレクタに関する記述である。

【0087】

また、図4−1において、置換テーブル作成部406は、併合部405によって得られた共通回路情報(たとえば、共通回路情報NFS)内の共通のデータ保持素子の出力ネットと、一方の識別情報により特定されるデータ保持素子の出力ネットと、他方の識別情報により特定されるデータ保持素子の出力ネットとを対応付ける置換テーブルTCを作成する機能を有する。

【0088】

図22は、出力ネット置換テーブルTCを示す説明図である。回路AのFFと回路BのFFとが共通化されるが、出力ネットは入力の選択に応じて切り替わるため、置換テーブル作成部406では、置換テーブルTCを作成して対応付けをおこなう。たとえば、最高得点の共通化テーブル中、ラベルA0,B3のペアについては、それぞれ出力ネットは、“ac01_out”と“div04_out”である(ラベル化パス情報800A,800Bを参照)。そして、この出力ネット“ac01_out”と“div04_out”を、対応する入力ネット“ac01_in”と“div04_in”の出力先となる共通化FFの出力ネット“ff0_out”のレコードに関連付ける。

【0089】

また、図4−1において、置換部407は、置換テーブル作成部406によって作成された置換テーブルTCを参照して、一方の回路情報(たとえば、回路Aの回路情報DA)に記述されている出力ネットを当該出力ネットに対応する共通のデータ保持素子の出力ネットに置換する機能を有する。また、他方の回路情報(たとえば、回路Bの回路情報DB)に記述されている出力ネットを当該出力ネットに対応する共通のデータ保持素子の出力ネットに置換する機能を有する。

【0090】

つぎに、置換部407では、回路Aおよび回路Bの固有化をおこなう。具体的には、回路Aの回路情報DAおよび回路Bの回路情報DBのインスタンス名とネット名の固有化をおこなう。たとえば、回路Aの回路情報DAおよび回路Bの回路情報DBから共通化するFFを削除する。また、インスタンス名やネット名の末尾に回路Aであれば“_A”、回路Bであれば“_B”を付す。また、FFの出力ネット名を、図22の置換テーブルTCを参照して、共通化FFの出力ネット名に変換する。

【0091】

図23は、回路Aの固有化前後の回路情報(ネットリスト)を示す説明図である。回路Aの回路情報DA(ネットリスト)の冒頭には、module文が記述されている。module文は、マージ処理の際に、回路Bのmodule文とマージされる。(A)が固有化前の回路Aの回路情報DAであり、(B)が固有化後の回路Aの回路情報NAである。図23では、共通化するFFの記述が削除され、出力ネット名が置換されている。

【0092】

図24は、回路Bの固有化前後の回路情報(ネットリスト)を示す説明図である。回路Bの回路情報DB(ネットリスト)の冒頭には、module文が記述されている。module文は、マージ処理の際に、回路Aのmodule文とマージされる。(A)が固有化前の回路Bの回路情報DBであり、(B)が固有化後の回路Bの回路情報NBである。図24でも、共通化するFFの記述が削除され、出力ネット名が置換されている。

【0093】

そして、図4−1において、併合部405は、置換部407による置換後の一方の回路情報(たとえば、回路Aの回路情報NA)と置換部407による置換後の他方の回路情報(たとえば、回路Bの回路情報NB)と共通回路情報(たとえば、共通回路情報NFS)とを統合することにより、併合回路ABの回路情報DABを生成する。

【0094】

図25は、マージした併合回路ABの回路情報DAB(ネットリスト)を示す説明図である。マージ処理では、回路Aの入力端子および出力端子と回路Bの入力端子および出力端子とをマージした記述をmodule文に記述する。このとき、共通化FFのクロック信号clockとリセット信号resetが重複しないように処理する。すなわち、clock,resetは共通化されるため、module文では1つだけ残す。また、あらたに、module文に選択信号selABを追加する。そして、回路Aの回路情報NA、回路Bの回路情報NB、共通回路情報NFS(共通化FFおよびセレクタのネットリスト)を追加する。これにより、併合回路ABの回路情報DABが生成される。

【0095】

図4−1において、取得部408は、併合部405により併合された併合回路ABの回路情報DABの論理合成結果dabを取得する機能を有する。論理合成は既存のツールにより実行される。論理合成ツールは自体は、設計支援装置400の外部にあってもよい。外部にある場合は、併合回路ABの回路情報DABを論理合成ツールを有する外部装置に送信し、当該外部装置から論理合成結果dabを受信することとしてもよい。論理合成結果dabはファイル化されて、図3に示したROM302、RAM303、磁気ディスク305などの記憶装置に保存される。これにより、論理合成された最終的なネットリストとして出力されることとなる。

【0096】

(設計支援処理手順)

図26は、実施の形態1にかかる設計支援装置400の設計支援処理手順を示すフローチャートである。まず、排他的な動作をする回路A,回路Bの回路情報(たとえば、ネットリスト)を取得しておき(ステップS2601)、入力部401により、図6−1〜図7−2に示したように、FF情報DFA,DFBおよびパス情報DPA,DPBを抽出する(ステップS2602)。

【0097】

そして、置換テーブル作成部406により、図8−1〜図9に示したように、共通化テーブル作成処理を実行する(ステップS2603)。これにより、第1世代の共通化テーブル群T1が作成される。つぎに、評価関数情報作成部403により、図10−1〜図11−2に示したように、評価関数情報(ラベル化パス情報1101A,1101B)を作成し(ステップS2604)、共通化テーブル評価/再作成部404により、図12〜図19に示したように、共通化テーブル評価処理と次世代作成処理を実行する(ステップS2605)。

【0098】

このあと、併合部405、置換テーブル作成部406および置換部407により、図20〜図25に示したように、マージ処理を実行する(ステップS2606)。これにより、図25に示したようなマージされた併合回路ABの回路情報DABが生成される。最後に、取得部408により、併合部405によって併合された併合回路ABの回路情報DABの論理合成結果dab取得して(ステップS2607)、最終的なネットリストを得ることとなる。

【0099】

図27は、図26に示した共通化テーブル評価/次世代作成処理(ステップS2605)の詳細な処理手順を示すフローチャートである。まず、未選択の共通化テーブルがあるか否かを判断する(ステップS2701)。未選択の共通化テーブルがある場合(ステップS2701:Yes)、未選択の共通化テーブルを1つ選択し(ステップS2702)、図12に示したように、ラベル化パス情報を置換する(ステップS2703)。そして、図13に示したように、共通項を抽出してカウントし(ステップS2704)、ステップS2701に戻る。ステップS2701〜S2704のループにより、共通化テーブルがなくなるまで、共通項を抽出してカウントすることとなる。

【0100】

一方、ステップS2701において、未選択の共通化テーブルがないと判断された場合(ステップS2701:No)、規定回数(n回)実行したか否かを判断する(ステップS2705)。すなわち、n世代分実行したか否かを判断する。規定回数に達していない場合(ステップS2705:No)、次世代作成処理を実行して(ステップS2706)、次世代の共通化テーブル群Tiを作成し、ステップS2701に戻る。これにより、次世代の共通化テーブル群Tiにより、ステップS2701〜ステップS2704のループが実行されることとなる。一方、規定回数を超えた場合(ステップS2705:Yes)、図26のマージ処理(ステップS2606)に移行する。

【0101】

図28は、図27に示した次世代作成処理(ステップS2706)の詳細な処理手順を示すフローチャートである。まず、図14に示したように、スケーリング処理を実行し(ステップS2801)、図15および図16に示したように、エリート選択やルーレット選択といった選択処理を実行する(ステップS2802)。そして、図17および図18に示したように、交叉/突然変異処理を実行し(ステップS2803)、図19に示したように、次世代の共通化テーブル群Tiを生成して(ステップS2804)、図27のステップS2701に戻る。

【0102】

図29は、図26に示したマージ処理(ステップS2606)の詳細な処理手順を示すフローチャートである。まず、対象となる共通化テーブル群Tiを取得し(ステップS2901)、図21に示したように、共通化FFおよびセレクタのネットリスト(共通回路情報NFS)を生成する(ステップS2902)。そして、図22に示したように、出力ネット置換テーブルTCを生成する(ステップS2903)。

【0103】

このあと、図23に示したように、回路Aの回路情報DAのインスタンス名とネット名を固有化し(ステップS2904)、図24に示したように、回路Bの回路情報DBのインスタンス名とネット名を固有化する(ステップS2905)。そして、図25に示したように、回路Aの回路情報NAと回路Bの回路情報NBを併合して(ステップS2906)、図26のステップS2607に移行する。これにより、マージされた併合回路ABの回路情報DABを得ることができる。

【0104】

このように、上述した実施の形態1によれば、リーク電流や面積を削減するために、使用/未使用が排他的な回路を共通化する。具体的には,FFに着目してFFを共通化する。FFを共通化することでFFに入力される信号を作り出す組み合わせ回路を論理圧縮することができる。

【0105】

また、FFの共通化には評価関数(ラベル化パス情報1101A,1101B)を用いる。評価関数による計算結果(点数)が高くなる組み合わせを探すことで組み合わせ回路の論理圧縮の可能性の向上を図ることができる。また、共通化した分だけFFの数は削減できるため、面積とリーク電流の削減を図ることができる。

【0106】

また、入力の共通性に着目しているため、論理圧縮の効果を上げ、組み合わせ回路の削減も期待することができる。また、上述した実施の形態1では、回路動作を理解していなくてもマージすることができる。

【0107】

<実施の形態2>

つぎに、実施の形態2について説明する。実施の形態1では、併合回路ABの回路情報DABを得たあとに、論理合成結果dabを取得することとした。これに対し、実施の形態2では、論理圧縮を試行してその圧縮度合いを評価関数として利用することとする。なお、実施の形態1と同一構成には同一符号を付し、その説明を省略する。

【0108】

図30−1は、実施の形態2にかかる設計支援装置の機能的構成1を示すブロック図である。設計支援装置3000は、FF情報抽出部411と、第1の作成部402と、仮併合部3001と、仮取得部3002と、共通化テーブル評価/再作成部404と、併合部405と、置換テーブル作成部406と、置換部407と、取得部408と、を備える。実施の形態2では、パス情報DPA,DPBを使用しないため、図4に示したパス情報抽出部412および評価関数情報作成部403は不要である。また、また、共通化テーブル評価/再作成部404の詳細は図30−2に示す。

【0109】

なお、各機能は、具体的には、たとえば、図3に示したROM302、RAM303、磁気ディスク305に記憶されたプログラムをCPU301に実行させることにより、またはI/F309により、その機能を実現する。実施の形態1との相違は、仮併合部3001、仮取得部3002および共通化テーブル評価/再作成部404であるため、仮併合部3001、仮取得部3002および共通化テーブル評価/再作成部404についてのみ説明し、他の機能の説明は実施の形態1と同じであるため省略する。

【0110】

図30−1において、仮併合部3001は、第1の作成部402によって作成された第1世代の共通化テーブル群T1を用いて、回路Aの回路情報DAと回路Bの回路情報DBとを併合(マージ)する機能を有する。具体的な動作は、併合部405と同一である。ただし、参照する共通化テーブルは、特定の共通化テーブルTn−xではなく、対象となる共通化テーブル群Ti内の各共通化テーブルである。

【0111】

したがって、併合された各回路情報は最終的な回路情報ではなく、中間的な回路情報である。以下、仮併合部3001による併合結果物を、「仮併合回路(AB)の回路情報(DAB)」とする。仮併合回路(AB)の回路情報(DAB)は、共通化テーブル群Ti内の共通化テーブルごとに得られる。

【0112】

仮取得部3002も、具体的な動作は、取得部408と同一である。ただし、取得対象となる論理合成結果は、仮併合回路(AB)の回路情報(DAB)の論理合成結果(dab)である。論理合成結果(dab)は、仮併合回路(AB)の回路情報(DAB)ごとに得られる。論理合成では論理圧縮後の面積が算出されるため、論理合成結果(dab)には、セルの面積の総和が記録されている。実施の形態2では、この面積の総和に応じた値を評価関数として用いる。したがって、仮併合回路(DAB)の論理圧縮度合いに応じて、回路Aと回路Bとを併合することができ、論理圧縮の効果を上げ、組み合わせ回路の削減も期待することができる。

【0113】

図30−2は、実施の形態2にかかる設計支援装置の機能的構成2を示すブロック図である。図30−2では、共通化テーブル評価/再作成部404の詳細な機能的構成を示している。共通化テーブル評価/再作成部404は、算出部422と、第2の作成部423と、設定部424と、選択部425とを備える。第2の作成部423、設定部424および選択部425は、実施の形態1と同一なので説明を省略する。なお、設定部424は、設定された対象となる共通化テーブル群Tiを仮併合部3001に渡すこととなる。

【0114】

算出部422は、仮取得部3002によって取得された仮併合回路(AB)の回路情報(DAB)ごとの論理合成結果(dab)から得られる仮併合回路(AB)に関する面積情報に基づいて、論理合成による論理圧縮度合いをあらわす評価値を、対象となる共通化テーブル群内の共通化テーブルごとに算出する機能を有する。具体的には、まず、対象となる共通化テーブル群Tiの各共通化テーブルに対し、論理合成結果から得られたセル面積の総和となる面積情報を関連付ける。

【0115】

図31は、セル面積を対応付けた共通化テーブル群を示す説明図である。図31では、第1世代の共通化テーブル群T1を例に挙げている。セル面積を対応付けた第1世代の共通化テーブルT1をTS1とする。同様に、セル面積を対応付けたi世代の共通化テーブルTiをTSiとする。

【0116】

つぎに、算出部422は、実施の形態1と同様、スケーリング処理を実行する。共通化テーブル評価/再作成部404では、セル面積の値が小さいほど,共通化テーブルとしては得点が大きくなるようにスケーリングを実行する。まず、対象とする共通化テーブル群TSi(ここでは第1世代の共通化テーブル群TS1)から選ばれた共通化テーブルのセル面積の値gについて、共通化テーブル群TSiのセル面積の最小値g_minで割る。割った結果を2から引く。

【0117】

g´=2−g/g_min・・・(2)

【0118】

ただし、g´はスケーリング処理後の得点である。これにより、セル面積の値gが小さいほど得点g´は大きくなる。このあと、上述したシグマスケーリングを実行して選択格差を広げる。

【0119】

図32は、シグマスケーリング処理結果を示す説明図である。具体的には、上記式(1)のfに得点g´の値を代入する。また、各セル面積の値gごとに得られたg´の平均値g´avgを算出し、上記式(1)のf´avgに代入する。これにより、共通化テーブルT1−01〜T1−20ごとに、得点f´を算出することができる。

【0120】

図32に示したように、得点f´が算出されたため、その後の処理は、実施の形態1と同様である。すなわち、図32に示した得点f´を用いて、第2の作成部423により、エリート選択およびルーレット選択(図15および図16を参照)、交叉(図17を参照)、突然変異(図18を参照)を実行する。そして、図19に示した場合と同様、エリート選択とルーレット選択により選択されたN/2個の次世代の親(生き残り)と,あらたに生成されたN/2個の次世代の子を合わせて、N個の共通化テーブルからなる次世代の共通化テーブル群Tiを生成する。

【0121】

この次世代の共通化テーブル群Tiの生成がn回に達した場合、第n世代の共通化テーブル群Tnの中から最高得点となる特定の共通化テーブルTn−xを選択する。そして、選択された特定の共通化テーブルTn−xを用いて、実施の形態1と同様、併合部405により回路Aと回路Bとの併合処理を実行する(図20〜図25を参照)。そして、併合処理によりマージされた回路情報DABの論理合成結果dabを取得部408が取得することで、最終的なネットリストを得ることとなる。

【0122】

(設計支援処理手順)

図33は、実施の形態2にかかる設計支援装置3000の設計支援処理手順を示すフローチャートである。まず、排他的な動作をする回路A,回路Bの回路情報(たとえば、ネットリスト)を取得しておき(ステップS3301)、FF情報抽出部411により、図6−1〜図6−2に示したように、FF情報を抽出する(ステップS3302)。

【0123】

そして、第1の作成部402により、図8−1〜図9に示したように、共通化テーブル作成処理を実行する(ステップS3303)。これにより、第1世代の共通化テーブル群T1が作成される。

【0124】

つぎに、仮併合部3001により、仮マージ処理を実行する(ステップS3304)。仮マージ処理(ステップS3304)では、対象とする現世代(第i世代)の共通化テーブル群Ti内のすべての共通化テーブルTi―01〜Ti−Nを用いて、回路Aと回路Bとのマージ処理を実行する。詳細は後述する。マージ処理(ステップS3304)により、対象とする第i世代の共通化テーブルごとに仮併合回路(AB)の回路情報(DAB)を得ることができる。

【0125】

つぎに、仮論理合成結果取得処理を実行する(ステップS3305)。仮論理合成結果取得処理(ステップS3305)では、仮マージ処理(ステップS3304)での仮併合回路(AB)の回路情報(DAB)ごとに論理合成結果(dab)を取得する。詳細は後述する。仮論理合成により回路(AB)の回路情報(DAB)は論理圧縮され、セル面積が算出される。

【0126】

そして、規定回数(n回)実行したか否かを判断する(ステップS3306)。規定回数に達していない場合(ステップS3306:No)、最新世代の各共通化テーブルに対応するセル面積を関連付ける(ステップS3307)。そして、上記式(2)を用いて、関連付けされた各セル面積の換算処理を実行する(ステップS3308)。この換算処理により得点g´が現世代の共通化テーブルごとに得られる。そして、次世代作成処理を実行する(ステップS3309)。

【0127】

次世代作成処理(ステップS3309)では、共通化テーブルごとの得点g´を式(1)のfとし、各セル面積の値gごとに得られたg´の平均値g´avgを上記式(1)のf´avgとして、スケーリング処理(ステップS2801)を実行することとなる。なお、次世代作成処理(ステップS3309)が実行されることにより、次世代の共通化テーブル群Tiが生成されて、ステップS3304に移行する。仮マージ処理(ステップS3304)では、ステップS3309で生成された次世代の共通化テーブル群Tiを現世代の共通化テーブル群として、併合処理を実行することとなる。

【0128】

一方、ステップS3306において、規定回数(n回)実行した場合(ステップS3306:Yes)、現世代(第n世代)の共通化テーブル群Tnの中から得点g´の値が最高得点となる共通化テーブルTngを抽出する(ステップS3310)。そして、併合部405により、図20〜図25に示したように、マージ処理を実行する(ステップS3311)。これにより、図25に示したようなマージされた併合回路ABの回路情報DABが生成される。最後に、取得部408により、併合回路ABの回路情報DABの論理合成結果dabを取得して(ステップS3312)、最終的なネットリストを得ることとなる。

【0129】

図34は、図33に示した仮マージ処理(ステップS3304)の詳細な処理手順を示すフローチャートである。まず、現世代の共通化テーブル群Tiにおいて、未選択の共通化テーブルがあるか否かを判断する(ステップS3401)。未選択の共通化テーブルがある場合(ステップS3401:Yes)、未選択の共通化テーブルを1つ取得する(ステップS3402)。つぎに、図21に示したように、共通化FFおよびセレクタの共通回路情報NFSを生成する(ステップS3403)。そして、図22に示したように、置換テーブルTCを生成する(ステップS3404)。

【0130】

このあと、図23に示したように、回路Aの回路情報DAのインスタンス名とネット名を固有化し(ステップS3405)、図24に示したように、回路Bの回路情報DBのインスタンス名とネット名を固有化する(ステップS3406)。そして、図25に示したように、回路Aの回路情報NAと回路Bの回路情報NBを併合して(ステップS3407)、併合回路ABの回路情報DABをメモリに保存する(ステップS3408)。そして、ステップS3401に戻る。

【0131】

このステップS3401〜S3408のループを実行することで、共通化テーブルごとの併合回路ABの回路情報DABを得ることができる。また、ステップS3401において、未選択の共通化テーブルがない場合(ステップS3401:No)、仮マージ処理を終了して仮論理合成結果取得処理(ステップS3305)に移行する。

【0132】

図35は、図33に示した仮論理合成結果取得処理(ステップS3305)の詳細な処理手順を示すフローチャートである。まず、未選択の仮併合回路(AB)の回路情報(DAB)があるか否かを判断し(ステップS3501)、未選択の仮併合回路(AB)の回路情報(DAB)がある場合(ステップS3501:Yes)、未選択の仮併合回路(AB)の回路情報(DAB)を取得する(ステップS3502)。そして、取得された仮併合回路(AB)の回路情報(DAB)について仮論理合成結果(dab)を取得し(ステップS3503)、仮論理合成結果(dab)をメモリに保存する(ステップS3504)。

【0133】

このステップS3501〜S3504のループを実行することで、仮併合回路(AB)の回路情報(DAB)ごとに論理圧縮することができる。また、ステップS3501において、未選択の仮併合回路(AB)の回路情報(DAB)がない場合(ステップS3501:No)、図33のステップS3306に移行することとなる。

【0134】

このように、実施の形態2によれば、リーク電流や面積を削減するために、使用/未使用が排他的な回路を共通化する。具体的には,FFに着目してFFを共通化する。FFを共通化することでFFに入力される信号を作り出す組み合わせ回路を論理圧縮することができる。

【0135】

また、FFの共通化には論理圧縮度合い(得点g´)を用いる。得点g´が小さくなる組み合わせを探すことで、実施の形態1よりもより効果的に組み合わせ回路の論理圧縮の可能性の向上を図ることができる。また、共通化した分だけFFの数は削減できるため、面積とリーク電流の削減を図ることができる。

【0136】

また、入力の共通性に着目しているため、論理圧縮の効果を上げ、組み合わせ回路の削減も期待することができる。また、実施の形態1と同様、論理圧縮度合いを用いた場合でも、回路動作を理解していなくても共通化マッピングをすることができる。

【0137】

以上のことから、実施の形態1,2によれば、排他的に動作しあう回路内部の入力の共通性を評価することにより、回路動作を理解していなくてもマージすることができる。したがって、回路の内部構成を意識することなく、LSIの消費電力の低減化および面積削減を図ることができるという効果を奏する。

【0138】

なお、実施の形態で説明した設計支援方法は、予め用意されたプログラムをパーソナル・コンピュータやワークステーション等のコンピュータで実行することにより実現することができる。このプログラムは、ハードディスク、フレキシブルディスク、CD−ROM、MO、DVD等のコンピュータで読み取り可能な記録媒体に記録され、コンピュータによって記録媒体から読み出されることによって実行される。またこのプログラムは、インターネット等のネットワークを介して配布することが可能な伝送媒体であってもよい。

【0139】

上述した実施の形態に関し、さらに以下の付記を開示する。

【0140】

(付記1)コンピュータを、

排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、前記一方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「一方のパス情報」)と、前記他方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「他方のパス情報」)と、を入力する入力手段、

前記入力手段によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成手段、

対象となる共通化テーブル群を参照することにより、前記対象となる共通化テーブルごとに、当該前記他方のパス情報内の前記他方の識別情報を前記一方の識別情報に変換する変換手段、

前記一方のパス情報および前記変換手段による変換後の他方のパス情報内における、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値を、前記共通化テーブルごとに算出する算出手段、

前記算出手段によって算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成する第2の作成手段、

前記第1および第2の作成手段によって作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定する設定手段、

前記設定手段によって設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択する選択手段、

前記選択手段によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成する併合手段、

として機能させることを特徴とする設計支援プログラム。

【0141】

(付記2)前記第2の作成手段は、

前記遺伝的アルゴリズムの交叉により、前記対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記1に記載の設計支援プログラム。

【0142】

(付記3)前記第2の作成手段は、

前記遺伝的アルゴリズムの突然変異により、前記対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記2に記載の設計支援プログラム。

【0143】

(付記4)前記第2の作成手段は、

前記遺伝的アルゴリズムのエリート選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を作成することを特徴とする付記2または3に記載の設計支援プログラム。

【0144】

(付記5)前記第2の作成手段は、

前記遺伝的アルゴリズムのルーレット選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を作成することを特徴とする付記2または3に記載の設計支援プログラム。

【0145】

(付記6)前記第2の作成手段は、

前記遺伝的アルゴリズムのエリート選択およびルーレット選択の混合選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を作成することを特徴とする付記2または3に記載の設計支援プログラム。

【0146】

(付記7)前記コンピュータを、

前記併合手段によって得られた共通回路情報内の共通のデータ保持素子の出力ネットと、前記一方の識別情報により特定されるデータ保持素子の出力ネットと、前記他方の識別情報により特定されるデータ保持素子の出力ネットとを対応付ける置換テーブルを作成する置換テーブル作成手段、

前記置換テーブル作成手段によって作成された置換テーブルを参照して、前記一方の回路情報に記述されている出力ネットを当該出力ネットに対応する前記共通のデータ保持素子の出力ネットに置換するとともに、前記他方の回路情報に記述されている出力ネットを当該出力ネットに対応する前記共通のデータ保持素子の出力ネットに置換する置換手段として機能させ、

前記併合手段は、

前記置換手段による置換後の前記一方の回路情報と前記置換手段による置換後の前記他方の回路情報と前記共通回路情報とを統合することにより、前記併合回路の回路情報を生成することを特徴とする付記1〜6のいずれか1つに記載の設計支援プログラム。

【0147】

(付記8)前記コンピュータを、

前記併合手段によって併合された併合回路の回路情報の論理合成結果を取得する取得手段として機能させることを特徴とする付記1〜7のいずれか1つに記載の設計支援プログラム。

【0148】

(付記9)コンピュータを、

排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、を入力する入力手段、

前記入力手段によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成手段、

対象となる共通化テーブル群内の共通化テーブルごとに、当該共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した仮併合回路の回路情報を生成する仮併合手段、

前記仮併合手段によって前記対象となる共通化テーブル群内の共通化テーブルごとに生成された前記仮併合回路の回路情報の論理合成結果を取得する仮取得手段、

前記仮取得手段によって取得された前記仮併合回路の回路情報ごとの論理合成結果から得られる前記仮併合回路に関する面積情報に基づいて、論理合成による論理圧縮度合いをあらわす評価値を、前記対象となる共通化テーブル群内の共通化テーブルごとに算出する算出手段、

前記算出手段によって算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成する第2の作成手段、

前記第1および第2の作成手段によって作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定する設定手段、

前記設定手段によって設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択する選択手段、

前記選択手段によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成する併合手段、

として機能させることを特徴とする設計支援プログラム。

【0149】

(付記10)前記生成手段は、

前記遺伝的アルゴリズムの交叉により、前記対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記9に記載の設計支援プログラム。

【0150】

(付記11)前記生成手段は、

前記遺伝的アルゴリズムの突然変異により、前記対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記10に記載の設計支援プログラム。

【0151】

(付記12)前記生成手段は、

前記遺伝的アルゴリズムのエリート選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記10または11に記載の設計支援プログラム。

【0152】

(付記13)前記生成手段は、

前記遺伝的アルゴリズムのルーレット選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記10または11に記載の設計支援プログラム。

【0153】

(付記14)前記生成手段は、

前記遺伝的アルゴリズムのエリート選択およびルーレット選択の混合選択により、前記対象となる共通化テーブル群の中から前記交叉の対象となる共通化テーブル群を選択し、前記交叉により、前記交叉の対象となる共通化テーブル群から前記次世代の共通化テーブル群を生成することを特徴とする付記10または11に記載の設計支援プログラム。

【0154】

(付記15)前記コンピュータを、

前記併合手段によって得られた共通回路情報内の共通のデータ保持素子の出力ネットと、前記一方の識別情報により特定されるデータ保持素子の出力ネットと、前記他方の識別情報により特定されるデータ保持素子の出力ネットとを対応付ける置換テーブルを作成する置換テーブル作成手段、

前記置換テーブル作成手段によって作成された置換テーブルを参照して、前記一方の回路情報に記述されている出力ネットを当該出力ネットに対応する前記共通のデータ保持素子の出力ネットに置換するとともに、前記他方の回路情報に記述されている出力ネットを当該出力ネットに対応する前記共通のデータ保持素子の出力ネットに置換する置換手段として機能させ、

前記併合手段は、

前記置換手段による置換後の前記一方の回路情報と前記置換手段による置換後の前記他方の回路情報と前記共通回路情報とを統合することにより、前記併合回路の回路情報を生成することを特徴とする付記9〜14のいずれか1つに記載の設計支援プログラム。

【0155】

(付記16)前記コンピュータを、

前記併合手段によって併合された併合回路の回路情報の論理合成結果を取得する取得手段として機能させることを特徴とする付記9〜15のいずれか1つに記載の設計支援プログラム。

【0156】

(付記17)排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、前記一方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「一方のパス情報」)と、前記他方の対象回路内の出力先となるデータ保持素子の識別情報とその入力元となるデータ保持素子の識別情報との対応関係を示すパス情報(以下、「他方のパス情報」)と、を入力する入力手段と、

前記入力手段によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成手段と、

対象となる共通化テーブル群を参照することにより、前記対象となる共通化テーブルごとに、当該前記他方のパス情報内の前記他方の識別情報を前記一方の識別情報に変換する変換手段と、

前記一方のパス情報および前記変換手段による変換後の他方のパス情報内における、同一出力先の識別情報に対する入力元の識別情報の共通性をあらわす評価値を、前記共通化テーブルごとに算出する算出手段と、

前記算出手段によって算出された評価値に基づいて、遺伝的アルゴリズムにより、前記対象となる共通化テーブル群から次世代の共通化テーブル群を作成する第2の作成手段と、

前記第1および第2の作成手段によって作成された共通化テーブル群のうち最新の共通化テーブル群を前記対象となる共通化テーブル群に設定する設定手段と、

前記設定手段によって設定された前記対象となる共通化テーブル群の中から特定の共通化テーブルを選択する選択手段と、

前記選択手段によって選択された特定の共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した併合回路の回路情報を生成する併合手段と、

を備えることを特徴とする設計支援装置。

【0157】

(付記18)排他的に動作しあう対象回路のうち、一方の対象回路内のデータ保持素子の識別情報(以下、「一方の識別情報」)と、他方の対象回路内のデータ保持素子の識別情報(以下、「他方の識別情報」)と、を入力する入力手段と、

前記入力手段によって入力された前記一方の識別情報に前記他方の識別情報をランダムに割り当てた共通化テーブルを複数とおり作成する第1の作成手段と、

対象となる共通化テーブル群内の共通化テーブルごとに、当該共通化テーブルにおいて一方の識別情報により特定されるデータ保持素子に関する一方の回路情報および当該一方の識別情報に対応する他方の識別情報により特定されるデータ保持素子に関する他方の回路情報を、前記一方の識別情報により特定されるデータ保持素子の入力ネットおよび前記他方の識別情報により特定されるデータ保持素子の入力ネットとを共通のデータ保持素子に排他的に接続する共通回路情報に変換することにより、前記一方の回路情報および前記他方の回路情報を併合した仮併合回路の回路情報を生成する仮併合手段と、

前記仮併合手段によって前記対象となる共通化テーブル群内の共通化テーブルごとに生成された前記仮併合回路の回路情報の論理合成結果を取得する仮取得手段と、