設計支援装置

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は設計支援装置に関し、特に半導体集積回路の設計支援装置に関する。

【背景技術】

【0002】

半導体集積回路の設計では、回路シミュレーションを行なうために、レイアウトパターンに基づいて配線寄生パラメータ(配線抵抗、配線容量および配線インダクタンス)の抽出(レイアウト寄生パラメータ抽出(LPE:layout Parasitic Extraction))が行なわれる。

【0003】

このLPEでは、製造プロセスの影響を受けて配線の実際の寸法が設計値(レイアウト寸法)からずれることも考慮される。たとえば、配線密度が高い場合、配線のCMP(Chemical Mechanical Polishing)プロセスにおいてエロージョン現象が起きる。そうなると、配線用の膜が周辺に比べて深く削り込まれることになり、配線の膜厚が薄くなる。このため、製造プロセスの影響を考慮しないと正確な寄生パラメータの抽出ができない。

【0004】

製造プロセスの影響をLPEに取込む具体的な方法として、たとえば、配線幅と配線密度を入力パラメータとして、配線膜厚と配線層間の絶縁層の膜厚を補正する。これによって、LPEによる配線寄生抵抗および配線寄生容量の値が実シリコン上で得られる値と一致するようにする。LPEソフトウェアのユーザは、TEG(Test Element Group)等で得られたデータを用いて、配線幅、配線間隔および配線密度と配線膜厚との関係、もしくは配線幅、配線間隔および配線密度と配線層間の絶縁層(層間絶縁層)の膜厚との関係を表わす数式または参照テーブルを作成し、LPEツールに与える。

【0005】

特開2009−217366号公報(特許文献1)は、上記のように製造プロセスの影響をLPEに取り込む際に、適切に配線データ率(配線密度)を算出可能とする方法を開示している。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−217366号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、発明者らは、CMPの影響を詳しく調べたところ、上記で説明した配線幅、配線間隔および配線密度と配線または層間絶縁層の膜厚との関係だけでは、実シリコン上での配線膜厚の測定結果または層間絶縁層の膜厚の測定結果を説明できないこと見出した。実際に測定された膜厚は、配線幅、配線間隔および配線密度に加えて、レイアウト形状(図形の形状そのもの)に依存している。このため、レイアウト形状に依存した効果をLPEに取込む手段が必要となる。

【0008】

レイアウト形状に依存した効果をLPEに反映させるためには、レイアウト形状を認識するとともに、認識したレイアウト形状から配線膜厚または配線層間の絶縁層の膜厚への影響度の計算をする必要がある。このためには、従来のDRC(Design Rule Check)/LVS(Layout Versus Schematic)用のソフトウェアに用いられているレイアウトパターン認識機能と同等の機能をLPE用のソフトウェアにも実装する必要があるため、そのための工数とコストとがかかることになる。

【0009】

この発明は上記の問題点を考慮してなされたものであり、その発明の目的は、配線のパターン形状に依存して生じる膜厚の設計値からのずれを、LPEに容易に取込むことが可能な半導体集積回路の設計支援装置を提供することである。

【課題を解決するための手段】

【0010】

この発明の実施の一形態による設計支援装置は、半導体集積回路のレイアウト情報を格納する記憶部と、図形演算機能を有する第1の情報処理部と、レイアウト情報に基づいて寄生パラメータを抽出する第2の情報処理部とを備える。第1の情報処理部は、記憶部から読み出したレイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出するパターン抽出部を含む。第2の情報処理部は、プロセス影響予測部と配線寄生パラメータ抽出部とを含む。プロセス影響予測部は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、パターン抽出部によって抽出された特定形状の配線パターンに関する情報とに基づいて予測する。配線寄生パラメータ抽出部は、プロセス影響予測部によって予測された設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

【発明の効果】

【0011】

上記の実施の形態によれば、図形演算機能を有する第1の情報処理部と、配線LPE用の第2の情報処理部とを連携させることによって、配線のパターン形状に依存した効果をLPEに容易に取込むことができる。

【図面の簡単な説明】

【0012】

【図1】本発明の実施の形態における半導体集積回路の設計支援装置の構成例を表わす図である。

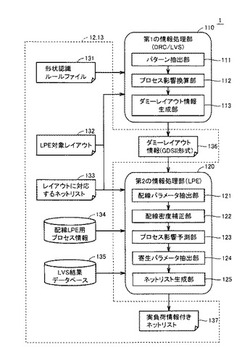

【図2】図1のCPU10が半導体集積回路の設計支援プログラムを実行することによって実現される機能を表わす機能ブロック図である。

【図3】図形演算処理によって、ある太さ以上の配線のコーナー内側部分を取り出す例について説明するための図である。

【図4】図3の図形演算処理を実行するためのルール(図形演算プログラム)を示す図である。

【図5】図3、図4の例で抽出した特定形状から決定された膜厚の補正量の情報を、LPEソフトウェアに引き渡すまでの手順を示すフローチャートである。

【図6】図5のステップS105で生成するダミー図形の一例を示す図である。

【図7】パターン抽出および受渡しデータ作成の他の例を説明するための図である。

【図8】図2の第2の情報処理部120が配線LPEを実行する手順を示すフローチャートである。

【図9】配線LPEソフトウェアによるダミーパターンファイルの読み込み機能について説明するための図である。

【図10】配線LPEソフトウェアによる配線膜厚の補正機能について説明するための図である。

【図11】配線密度の補正手順を具体的に説明するための図である。

【発明を実施するための形態】

【0013】

以下、この発明の実施の形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰返さない。

【0014】

[設計支援装置の構成]

図1は、本発明の実施の形態における半導体集積回路の設計支援装置の構成例を表わす図である。この設計支援装置は、コンピュータ本体1、ディスプレイ装置2、FD(Flexible Disk)4が装着されるFDドライブ3、キーボード5、マウス6、CD−ROM(Compact Disc-Read Only Memory)またはDVD(Digital Versatile Disk)などの光ディスク8が装着される光ディスクドライブ7、およびネットワーク通信装置9を含む。

【0015】

半導体集積回路の設計支援プログラムは、FD4または光ディスク8等の記録媒体によって供給される。設計支援プログラムがコンピュータ本体1によって実行されることによって、半導体集積回路の設計支援が行なわれる。設計支援プログラムは他のコンピュータより通信回線を経由し、コンピュータ本体1に供給されてもよい。

【0016】

コンピュータ本体1は、CPU(Central Processing Unit)10、ROM(Read Only Memory)11、RAM(Random Access Memory)12およびハードディスク13を含む。CPU10は、ディスプレイ装置2、FDドライブ3、キーボード5、マウス6、光ディスクドライブ7、ネットワーク通信装置9、ROM11、RAM12またはハードディスク13との間でデータを入出力しながら処理を行なう。FD4または光ディスク8に記録された半導体集積回路の設計プログラムは、CPU10によりFDドライブ3または光ディスクドライブ7を介して一旦ハードディスク13に格納される。CPU10が、ハードディスク13から適宜設計支援プログラムをRAM12にロードして実行することによって、半導体集積回路の設計が行なわれる。

【0017】

[設計支援装置の機能の概要]

図2は、図1のCPU10が半導体集積回路の設計支援プログラムを実行することによって実現される機能を表わす機能ブロック図である。図2では設計支援プログラムのうち、DRC(設計規則検査:Design Rule Check)/LVS(レイアウト・ネットリストの照合:Layout Versus Schematic)用のEDA(Electronic Design Automation)ソフトウェアを実行することによって実現される機能(第1の情報処理部110)と、LPE(レイアウト寄生パラメータ抽出:layout Parasitic Extraction)ソフトウェアを実行することによって実現される機能(第2の情報処理部120)とが図示されている。

【0018】

(第1の情報処理部110)

DRCは、作成されたパターンレイアウト情報132が、LSI(Large Scale Integration:この明細書では半導体集積回路と同義)の製造装置の制約から決まる幾何学的な設計ルールに違反していないかどうかをチェックするものである。パターンレイアウト情報132は、記憶部(図1のRAM12またはハードディスク13)からCPU10によって読み出される。LVSは、パターンレイアウト情報132から抽出されたネットリストと回路図のネットリスト133とを比較して、回路図における素子間の接続関係がレイアウト設計で正しく実現されているかを検証するものである。

【0019】

一般に、レイアウト情報は、マスク層ごとに分類された多角形の集合体であるので、DRCおよびLVSのための前処理として、複数の図形データの論理和(OR)、論理積(AND)、差分(SUB)などに代表される図形論理演算が行なわれる。通常、図形演算機能としてその他に、図形のエッジの抽出、図形の拡大・縮小などが実装されている。

【0020】

図2に示す第1の情報処理部110は、さらに、DRC/LVSソフトウェアに標準的に実装されているこのような図形演算機能を用いて、配線または層間絶縁層の膜厚に影響を及ぼす特定形状のレイアウトパターンを抽出する。配線パターンの形状に応じて、製造プロセス(特にCMP)の影響をどの程度受けるかについての情報は、TEG等を用いて実験的に予め得られる。具体例については、図4〜図7を参照して後述することとして、以下ではその概要について説明する。

【0021】

図2に示すように、第1の情報処理部110は、パターン抽出部111と、プロセス影響換算部112と、ダミーレイアウト情報生成部113とを含む。

【0022】

パターン抽出部111は、記憶部12,13から読み出したレイアウト情報132に含まれる各配線層(レイヤ)のレイアウトパターンに対して図形演算を施すことによって、ユーザが予め定めた特定形状の配線パターンを抽出する。具体的に、ユーザは特定形状の配線パターンを抽出するための図形演算プログラムに相当する形状認識ルールファイル131を予め作成し、記憶部12,13に格納しておく。パターン抽出部111は、この形状認識ルールファイルに従って特定形状の配線パターンを抽出する。

【0023】

プロセス影響換算部112は、抽出した配線パターンの情報を第2の情報処理部120(LPEソフトウェア)に引き渡すための処理を行なう。具体的に、プロセス影響換算部112は、TEG等を利用して予め実験的に得られた、配線または層間絶縁層の厚みの設計値からのずれの大きさと配線密度との関係に基づいて、特定形状の配線パターンによって生じる配線または層間絶縁層の厚みの設計値からのずれの大きさを、配線密度の大きさに換算する。

【0024】

ダミーレイアウト情報生成部113は、プロセス影響換算部112で換算した配線密度と同じ大きさのパターン密度を有するダミー図形が、特定形状の配線パターンの近辺に配置されているようなダミーレイアウト情報を生成する。このダミーレイアウト情報のデータ形式は、LSIのレイアウト情報のデータ形式と同じであり、汎用で用いられているGDSIIである。これによって、特定形状の配線パターンの膜厚に対する影響を、次のLPEソフトウェア(第2の情報処理部120)に引き渡すことができるようになる。ダミーレイアウト情報生成部113は、生成したダミーレイアウト情報を一旦、記憶部12,13に格納する。

【0025】

(第2の情報処理部120)

LPEソフトウェアによって実現される第2の情報処理部120は、製造プロセスに依存した配線または層間絶縁層の膜厚の設計値からのずれの大きさを予測し、予測したずれの大きさを取り入れて各配線の寄生パラメータ(配線抵抗、配線容量)を抽出する。設計値からの膜厚のずれの大きさを予測する際には、レイアウト情報132から抽出した配線幅、配線間隔および配線密度の情報(もしくは、配線幅および配線密度の情報)と、パターン抽出部に111よって抽出された特定形状の配線パターンに関する情報とに基づいて予測が行なわれる。具体例については、図8〜図11を参照して後述することとし、以下ではその概要について説明する。

【0026】

図2に示すように、第2の情報処理部120は、配線パラメータ抽出部121と、配線密度補正部122と、プロセス影響予測部と123と、寄生パラメータ抽出部124と、ネットリスト生成部125とを含む。

【0027】

配線パラメータ抽出部121(配線密度抽出部)は、各配線の幅、隣接する配線間の間隔および配線密度を、記憶部12,13から読み出したLSIのレイアウト情報132(GDSII形式)から抽出する。ここで、配線密度は、半導体集積回路が配置される各配線層のレイアウト領域を複数の領域に区分したとき、各区分領域の面積に対する配線パターン率として区分領域ごとに計算される。

【0028】

配線密度補正部122は、第1の情報処理部110のパターン抽出部111によって抽出された特定形状の配線パターンが配置されている区分領域において、配線パラメータ抽出部121によって抽出された配線密度の値を補正する。具体的には、配線密度補正部122は、記憶部12,13から読み出したダミーレイアウト情報136(GDSII形式)に基づいてダミー図形のパターン密度を算出し、ダミー図形が配置されている区分領域の本来の配線密度にダミー図形のパターン密度を加算することによって配線密度の値を補正する。

【0029】

プロセス影響予測部123は、レイアウト情報から抽出した配線幅および配線間隔の情報と、配線密度補正部122による補正後の配線密度の情報とに基づいて、配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを予測する。具体的には、TEG等を利用して予め実験的に取得した、配線または層間絶縁層の厚みの設計値からのずれの大きさと、配線幅、配線間隔および配線密度との関係(図2では、プロセス情報134として、数式またはテーブルの形式で予め準備される)に基づいて、設計値からのずれの大きさが推定される。

【0030】

配線寄生パラメータ抽出部124は、プロセス影響予測部によって予測された設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、各配線の寄生パラメータを抽出する。たとえば、配線抵抗は、予め規定されたシート抵抗値に基づいて決定され、配線容量は、電磁界解析ツールを利用して算出される。

【0031】

ネットリスト生成部125は、レイアウトに対応したネットリスト133とLVS結果データベースを利用して、LPEの結果を取込んだ実負荷情報付きのネットリスト137を生成する。以下、より詳細に説明する。

【0032】

[形状認識(特定形状の配線パターンの抽出)]

本実施の形態による設計支援装置では、既存のDRC/LVS用EDAソフトウェアを用いることにより、配線LPE用のソフトウェアに複雑な形状認識機能を追加することなく、高速かつユーザによる柔軟な形状認識規則の指定が可能なルールベースの形状認識を実現する。

【0033】

ルールベースの形状認識では、一般的な認識形状そのものを記憶して一致するものを認識するパターンマッチングと異なり、入力されたレイアウト情報にユーザの記述するルール(図形演算プログラム)に従って図形演算処理を行い、特定形状の配線パターンを抽出する。ルールベースの形状認識の例を以下に具体的に説明する。

【0034】

図3は、図形演算処理によって、ある太さ以上の配線のコーナー内側部分を取り出す例について説明するための図である。

【0035】

図4は、図3の図形演算処理を実行するためのルール(図形演算プログラム)を示す図である。図3、図4を参照して、図3(A)に示すような配線パターンのレイアウト情報が存在したとする。

【0036】

図3(A)を参照して、まず、対象レイヤに対して一定の幅以上の配線(ハッチングを付した配線201,202)のみを取り出す処理を行なう。この処理は、図4(A)に示すように、layer1に対して、幅(WIDTH)が1μmよりも大きい(LARGER)ものを取り出して、wide_lineと名付けるというルールとして記述される。

【0037】

図3(B)を参照して、次に、図3(A)で取り出した配線201,202のエッジ201x,201y,202x,202yを取り出す処理を行なう。この処理は、図4(B1),(B2)に示すように、wide_lineと名付けた配線に対して、x方向のエッジ(EDGE)を取り出してedgexと名付け、y方向のエッジ(EDGE)を取り出してedgeyと名付けるというルールとして記述される。

【0038】

図3(C)を参照して、次に、図3(B)で取り出した配線のエッジ201x,201y,202x,202yに対して幅を与える処理を行なう。この処理は、図4(C1),(C2)に示すように、edgexと名付けたエッジ部分201x、202xをY方向に0.001μm拡張(WIDEN)して(X方向には0)edgex2と名付け、edgeyと名付けたエッジ部分201y,202yをX方向に0.001μm拡張(WIDEN)して(X方向には0)edgey2と名付けるというルールとして記述される。

【0039】

図3(D)を参照して、次に、図3(C)で幅を広げたエッジ部分201xと201yの論理積をとる。この処理は、図4(D)に示すように、edgex2と名付けた部分とedgey2と名付けた部分との論理積(AND)を実行し、演算結果をcornerと名付けるというルールとして記述される。

【0040】

図3(E)を参照して、次に、図3(D)の図形演算結果203a〜203dのうち対象レイヤと重なる部分を取除く処理を行なうことによって、最終的にコーナー部分203bを得る。この処理は、対象レイヤ(layer1)とconrnerと名付けた部分との論理否定を実行し、演算結果をinner_cornerと名付けるというルールとして記述される。

【0041】

[DRC/LVS用ソフトウェアと配線LPEソフトウェアのデータ受渡し]

DRC/LVS用ソフトウェアと配線LPEソフトウェアの間での情報の受け渡しはGDSII形式のファイルを用いて行なう。具体的には、DRC/LVS用EDAソフトウェアは対象形状を認識した後、その形状によって生じる配線または層間絶縁層の厚みにおける設計値からのずれの大きさを決定する。そして、決定した設計値からのずれを、同じずれの大きさが生じる配線密度の大きさに換算する。その後、換算によって得られた配線密度と同じパターン密度を有するGDSIIファイルのダミー図形を生成する。生成したダミー図形のGDSIIファイル(ダミーレイアウト情報)を図2の第2の情報処理部120(配線LPEソフトウェア)に渡す。このとき、配線LPEソフトウェアの仕様に合わせてダミー図形情報を生成する必要があるので、GDSII形式としている。第2の情報処理部では、ダミー図形の密度を実際の配線密度に加算することによって実際の配線密度を補正する計算を行なう。以下、具体的に説明する。

【0042】

図5は、図3、図4の例で抽出した特定形状から決定された膜厚の補正量の情報を、LPEソフトウェアに引き渡すまでの手順を示すフローチャートである。図5を参照して、ステップS101で、図2の第1の情報処理部110は、図形演算ルールを用いて図3(E)に示す特定形状(配線のコーナー)の箇所203bを認識したとする。

【0043】

次のステップS102で、第1の情報処理部110は、図形演算ルールを用いて特定箇所における配線の太さを取得する。配線または層間絶縁層の厚みにおける設計値からのずれの大きさは、特定形状の箇所203bでの配線の太さに関係するからである。

【0044】

次のステップS103で、第1の情報処理部110は、配線幅wから膜厚補正量Δtを所定の計算式Δt=f(w)に従って計算する。この計算式は、事前にTEGなどを用いた測定結果から用意しておく必要がある。

【0045】

次のステップS104で、第1の情報処理部110は、ステップS103で計算した膜厚補正量Δtに相当する配線密度dを所定の計算式d=g(Δt)に従って計算する。この計算式は、事前にTEGなどを用いた測定結果から用意しておく必要がある。

【0046】

次のステップS105で、第1の情報処理部110は、ステップS104で計算した配線密度dと同じパターン密度を有するダミー図形を、抽出した特定箇所の周辺の座標に生成する。具体例を図6に示す。

【0047】

図6は、図5のステップS105で生成するダミー図形の一例を示す図である。抽出した配線のコーナーの近傍の領域204にダミー図形205が生成される。

【0048】

再び図5を参照して、次のステップS106で、第1の情報処理部110は、ステップS105で生成したダミー図形の情報(ダミーレイアウト情報)をGDSIIファイル形式で格納し、受け渡しデータとする。

【0049】

[パターン抽出および受渡しデータ作成の他の例]

図7は、パターン抽出および受渡しデータ作成の他の例を説明するための図である。図7(A)に示すような3重配線のコーナー部分が製造プロセスの影響を受けて設計値の膜厚からずれが生じるものとする。

【0050】

図7(B)を参照して、図2の第1の情報処理部110は、図3、図4で説明したのと同様の方法で各配線のコーナー内側部分301〜303を認識する。

【0051】

図7(C)を参照して、第1の情報処理部110は、各配線のコーナー内側部分をX方向、Y方向に所定の長さ伸張させた図形301e〜303eを生成する。そして、第1の情報処理部110は、生成した図形301e〜303eに基づいて、膜厚が製造プロセスに影響される領域304を認識する。

【0052】

図7(D)を参照して、第1の情報処理部110は、図7(C)で認識した領域304の近辺にダミー図形305を生成する。

【0053】

[配線LPEソフトウェア(第2の情報処理部120)による処理]

第2の情報処理部120は、第1の情報処理部(DRC/LVS用のEDAソフトウェア)で生成された補正情報(ダミーレイアウト情報)を受け取り、受取った補正情報から補正量を求めて膜厚補正を行なう。その後、実際のLPE処理が実行される。

【0054】

補正情報から補正量を求める方法は、配線LPEソフトウェア(第2の情報処理部120)が決定する。したがって、補正情報を生成するDRC/LVS用のEDAソフトウェア(第1の情報処理部110)側では、この方法に合うように補正情報のGDSIIファイル(ダミーレイアウト情報)を生成する必要がある。これは、適切な補正情報の計算式と図形形状の認識ルールとを、ユーザがDRC/LVS用のEDAソフトウェアに入力することで実現されるので、DRC/LVS用のEDAソフトウェアそのものを修正する必要はない。

【0055】

以下に具体例を示す。補正量を求める具体的方法は、ダミーレイアウト情報からパターン密度を計算し、計算したダミー図形の密度を実際の配線密度に加えることによるものとする。

【0056】

図8は、図2の第2の情報処理部120が配線LPEを実行する手順を示すフローチャートである。

【0057】

図8を参照して、第2の情報処理部120は、LSIのレイアウト情報132(GDSII形式)を読み込み(ステップS401)、読み込んだLSIのレイアウト情報132に基づいて配線幅、配線間隔、および配線密度を計算する(S402)。配線密度は、半導体集積回路が配置される各配線層のレイアウト領域を複数の領域に区分したとき、各区分領域の面積に対する配線パターン率として区分領域ごとに計算される。

【0058】

第2の情報処理部120は、さらに、ダミーレイアウト情報136(GDSII形式)を読み込み(ステップS403)、読み込んだダミーレイアウト情報136からダミー図形のパターン密度を実際の配線密度の補正量として計算する(ステップS404)。

【0059】

次のステップS405で、第2の情報処理部120は、ダミー図形の配置されている区分領域において実際の配線密度にダミー図形のパターン密度を加算することによって、配線密度の値を補正する。

【0060】

次にステップS406で、第2の情報処理部120は、ステップS402で計算した配線幅および配線間隔とステップS405による補正後の配線密度とを用いて、配線または層間絶縁層の膜厚の設計値を製造プロセスの影響を取り入れた値に補正する。

【0061】

次のステップS407で、第2の情報処理部120は、ステップS406による補正後の配線膜厚および層間絶縁層の膜厚を用いて、配線の寄生抵抗および寄生容量を抽出する。

【0062】

次のステップS408で、第2の情報処理部120は、ステップS407で抽出した実負荷情報(寄生パラメータ)を取り入れたネットリストを生成する。

【0063】

(1.配線LPEソフトウェアによるダミーパターンの読み込み機能について)

商用の配線LPEツールでは、LPE対象となるLSIのパターンレイアウトデータ(GDSIIファイル)に加えて、配線密度調整用のダミーパターンのみを含んだGDSIIファイルを追加で読み込む機能が既に実装されている。たとえば、CMP処理では、配線のメタル材料の分布がチップ全体にわたってほぼ均一であることが望ましいので、配線の無い領域にダミーメタルを挿入してメタル密度を均一にする処理が一般に行なわれている。このダミーメタルのGDSファイルは、LSIのパターンレイアウトデータとは別に作成されて、設計支援装置に読み込まれる。

【0064】

図9は、配線LPEソフトウェアによるダミーパターンファイルの読み込み機能について説明するための図である。図9を参照して、本来のLPE対象のレイアウト情報を表わすGDSファイルとは別に、ダミーパターンのGDSファイルを読み込み、これらのパターンを合わせたパターンレイアウトに対して配線密度計算およびLPEが実行される。

【0065】

このように、LPE対象のレイアウト情報に加えて別のダミーのレイアウト情報を読み込んで処理を行なう機能自体は既に実装されているため、本実施の形態による設計支援装置で用いられる配線LPE用ソフトウェアに、配線密度補正のためのダミーパターンを追加で読み込む機能を実装するのにかかるコストは小さいものと考えられる。一方で、既存の機能では追加的に読み込んだダミーレイアウトを本来のレイアウト情報にマージ(merge)する処理しか想定されていない。これに対して、本実施の形態の場合には、ダミーのレイアウト情報は配線密度の補正情報としてのみ取扱われ、本来のパターンレイアウトと同列に扱われるものでない。この点で本実施の形態による処理方法は、従来のLPE用ソフトウェアによる処理方法と異なっている。

【0066】

(2.配線密度に応じた配線膜厚の補正機能について)

商用LPEツールでは、配線密度に応じて配線の膜厚を補正する機能が既に実装されている。

【0067】

図10は、配線LPEソフトウェアによる配線膜厚の補正機能について説明するための図である。図10を参照して、配線膜厚を補正するために、まず、入力されたLSIのレイアウトが複数の領域311〜318に区分される。そして、区分領域311〜318ごとに配線密度(パターン占有率)d1〜d8(%)が計算される。次に、事前にテクノロジファイルの作成者が入力した膜厚の補正量を表わす式Δt=f(w,s,d)に従って、配線幅w、配線間隔s、および配線密度dから配線膜厚の補正量Δtが計算される。たとえば、図10の区分領域318では、配線320の幅がwであり、配線319,320間の間隔がsであり、これらの値と配線密度d8によって補正量Δtが計算される。そして、この補正量Δtを膜厚設計値に加算したものに対して、配線抵抗および配線容量を抽出する処理が行なわれる。

【0068】

本実施の形態による設計支援装置は、上記の配線密度dを補正するものであるので、容易に実装することが可能である。

【0069】

図11は、配線密度の補正手順を具体的に説明するための図である。

図2、図11を参照して、本実施の形態では、配線LPEを実行する図2の第2の情報処理部120は、従来必要としていたファイル(LPE対象レイアウト132、ネットリスト133、プロセス情報134、およびLVS結果135)に加えて、膜厚補正用のダミーパターンである第1の情報処理部110(DRC/LVS用ソフトウェア)が出力したダミーレイアウト情報136を読み込む。具体的に、図11(A)に示すように、配線レイアウト(331〜333など)と補正用ダミーレイアウト334とが読み込まれる。

【0070】

次に、図11(B)に示すように、配線膜厚および層間絶縁層の膜厚を補正する段階で、配線レイアウトから実配線密度が計算され、補正用ダミーレイアウトから334からダミー密度が計算される。ダミー密度は、補正用ダミーレイアウト334が存在する区分領域330でのみ計算されている。そして、この区分領域330では、実配線密度にダミー密度を加算することによって配線密度が補正される。

【0071】

次に、図11(C)に示すように、配線膜厚および補正後の配線密度の情報を用いて、膜厚補正値が決定される。したがって、ダミー図形334が配置されている区分領域330では、形状依存性を考慮した膜厚補正値が得られる。このように補正された膜厚を用いてLPEの処理を行い、配線の寄生抵抗、寄生容量が求められる。求めた寄生抵抗、寄生容量を含むネットリストを出力することによってLPE処理が完了する。

【0072】

今回開示された実施の形態はすべての点で例示であって制限的なものでないと考えられるべきである。この発明の範囲は上記した説明ではなくて請求の範囲によって示され、請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0073】

1 コンピュータ本体、10 CPU、12 RAM(記憶部)、13 ハードディスク(記憶部)、110 第1の情報処理部、111 パターン抽出部、112 プロセス影響換算部、113 ダミーレイアウト情報生成部、120 第2の情報処理部、121 配線パラメータ抽出部、122 配線密度補正部、123 プロセス影響予測部、124 配線寄生パラメータ抽出部、125 ネットリスト生成部、131 形状認識ルールファイル、132 LSIのレイアウト情報、133 ネットリスト、136 ダミーレイアウト情報、137 実負荷情報付きネットリスト、205,305,334 ダミー図形、311〜318 区分領域。

【技術分野】

【0001】

この発明は設計支援装置に関し、特に半導体集積回路の設計支援装置に関する。

【背景技術】

【0002】

半導体集積回路の設計では、回路シミュレーションを行なうために、レイアウトパターンに基づいて配線寄生パラメータ(配線抵抗、配線容量および配線インダクタンス)の抽出(レイアウト寄生パラメータ抽出(LPE:layout Parasitic Extraction))が行なわれる。

【0003】

このLPEでは、製造プロセスの影響を受けて配線の実際の寸法が設計値(レイアウト寸法)からずれることも考慮される。たとえば、配線密度が高い場合、配線のCMP(Chemical Mechanical Polishing)プロセスにおいてエロージョン現象が起きる。そうなると、配線用の膜が周辺に比べて深く削り込まれることになり、配線の膜厚が薄くなる。このため、製造プロセスの影響を考慮しないと正確な寄生パラメータの抽出ができない。

【0004】

製造プロセスの影響をLPEに取込む具体的な方法として、たとえば、配線幅と配線密度を入力パラメータとして、配線膜厚と配線層間の絶縁層の膜厚を補正する。これによって、LPEによる配線寄生抵抗および配線寄生容量の値が実シリコン上で得られる値と一致するようにする。LPEソフトウェアのユーザは、TEG(Test Element Group)等で得られたデータを用いて、配線幅、配線間隔および配線密度と配線膜厚との関係、もしくは配線幅、配線間隔および配線密度と配線層間の絶縁層(層間絶縁層)の膜厚との関係を表わす数式または参照テーブルを作成し、LPEツールに与える。

【0005】

特開2009−217366号公報(特許文献1)は、上記のように製造プロセスの影響をLPEに取り込む際に、適切に配線データ率(配線密度)を算出可能とする方法を開示している。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−217366号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、発明者らは、CMPの影響を詳しく調べたところ、上記で説明した配線幅、配線間隔および配線密度と配線または層間絶縁層の膜厚との関係だけでは、実シリコン上での配線膜厚の測定結果または層間絶縁層の膜厚の測定結果を説明できないこと見出した。実際に測定された膜厚は、配線幅、配線間隔および配線密度に加えて、レイアウト形状(図形の形状そのもの)に依存している。このため、レイアウト形状に依存した効果をLPEに取込む手段が必要となる。

【0008】

レイアウト形状に依存した効果をLPEに反映させるためには、レイアウト形状を認識するとともに、認識したレイアウト形状から配線膜厚または配線層間の絶縁層の膜厚への影響度の計算をする必要がある。このためには、従来のDRC(Design Rule Check)/LVS(Layout Versus Schematic)用のソフトウェアに用いられているレイアウトパターン認識機能と同等の機能をLPE用のソフトウェアにも実装する必要があるため、そのための工数とコストとがかかることになる。

【0009】

この発明は上記の問題点を考慮してなされたものであり、その発明の目的は、配線のパターン形状に依存して生じる膜厚の設計値からのずれを、LPEに容易に取込むことが可能な半導体集積回路の設計支援装置を提供することである。

【課題を解決するための手段】

【0010】

この発明の実施の一形態による設計支援装置は、半導体集積回路のレイアウト情報を格納する記憶部と、図形演算機能を有する第1の情報処理部と、レイアウト情報に基づいて寄生パラメータを抽出する第2の情報処理部とを備える。第1の情報処理部は、記憶部から読み出したレイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出するパターン抽出部を含む。第2の情報処理部は、プロセス影響予測部と配線寄生パラメータ抽出部とを含む。プロセス影響予測部は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、パターン抽出部によって抽出された特定形状の配線パターンに関する情報とに基づいて予測する。配線寄生パラメータ抽出部は、プロセス影響予測部によって予測された設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

【発明の効果】

【0011】

上記の実施の形態によれば、図形演算機能を有する第1の情報処理部と、配線LPE用の第2の情報処理部とを連携させることによって、配線のパターン形状に依存した効果をLPEに容易に取込むことができる。

【図面の簡単な説明】

【0012】

【図1】本発明の実施の形態における半導体集積回路の設計支援装置の構成例を表わす図である。

【図2】図1のCPU10が半導体集積回路の設計支援プログラムを実行することによって実現される機能を表わす機能ブロック図である。

【図3】図形演算処理によって、ある太さ以上の配線のコーナー内側部分を取り出す例について説明するための図である。

【図4】図3の図形演算処理を実行するためのルール(図形演算プログラム)を示す図である。

【図5】図3、図4の例で抽出した特定形状から決定された膜厚の補正量の情報を、LPEソフトウェアに引き渡すまでの手順を示すフローチャートである。

【図6】図5のステップS105で生成するダミー図形の一例を示す図である。

【図7】パターン抽出および受渡しデータ作成の他の例を説明するための図である。

【図8】図2の第2の情報処理部120が配線LPEを実行する手順を示すフローチャートである。

【図9】配線LPEソフトウェアによるダミーパターンファイルの読み込み機能について説明するための図である。

【図10】配線LPEソフトウェアによる配線膜厚の補正機能について説明するための図である。

【図11】配線密度の補正手順を具体的に説明するための図である。

【発明を実施するための形態】

【0013】

以下、この発明の実施の形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰返さない。

【0014】

[設計支援装置の構成]

図1は、本発明の実施の形態における半導体集積回路の設計支援装置の構成例を表わす図である。この設計支援装置は、コンピュータ本体1、ディスプレイ装置2、FD(Flexible Disk)4が装着されるFDドライブ3、キーボード5、マウス6、CD−ROM(Compact Disc-Read Only Memory)またはDVD(Digital Versatile Disk)などの光ディスク8が装着される光ディスクドライブ7、およびネットワーク通信装置9を含む。

【0015】

半導体集積回路の設計支援プログラムは、FD4または光ディスク8等の記録媒体によって供給される。設計支援プログラムがコンピュータ本体1によって実行されることによって、半導体集積回路の設計支援が行なわれる。設計支援プログラムは他のコンピュータより通信回線を経由し、コンピュータ本体1に供給されてもよい。

【0016】

コンピュータ本体1は、CPU(Central Processing Unit)10、ROM(Read Only Memory)11、RAM(Random Access Memory)12およびハードディスク13を含む。CPU10は、ディスプレイ装置2、FDドライブ3、キーボード5、マウス6、光ディスクドライブ7、ネットワーク通信装置9、ROM11、RAM12またはハードディスク13との間でデータを入出力しながら処理を行なう。FD4または光ディスク8に記録された半導体集積回路の設計プログラムは、CPU10によりFDドライブ3または光ディスクドライブ7を介して一旦ハードディスク13に格納される。CPU10が、ハードディスク13から適宜設計支援プログラムをRAM12にロードして実行することによって、半導体集積回路の設計が行なわれる。

【0017】

[設計支援装置の機能の概要]

図2は、図1のCPU10が半導体集積回路の設計支援プログラムを実行することによって実現される機能を表わす機能ブロック図である。図2では設計支援プログラムのうち、DRC(設計規則検査:Design Rule Check)/LVS(レイアウト・ネットリストの照合:Layout Versus Schematic)用のEDA(Electronic Design Automation)ソフトウェアを実行することによって実現される機能(第1の情報処理部110)と、LPE(レイアウト寄生パラメータ抽出:layout Parasitic Extraction)ソフトウェアを実行することによって実現される機能(第2の情報処理部120)とが図示されている。

【0018】

(第1の情報処理部110)

DRCは、作成されたパターンレイアウト情報132が、LSI(Large Scale Integration:この明細書では半導体集積回路と同義)の製造装置の制約から決まる幾何学的な設計ルールに違反していないかどうかをチェックするものである。パターンレイアウト情報132は、記憶部(図1のRAM12またはハードディスク13)からCPU10によって読み出される。LVSは、パターンレイアウト情報132から抽出されたネットリストと回路図のネットリスト133とを比較して、回路図における素子間の接続関係がレイアウト設計で正しく実現されているかを検証するものである。

【0019】

一般に、レイアウト情報は、マスク層ごとに分類された多角形の集合体であるので、DRCおよびLVSのための前処理として、複数の図形データの論理和(OR)、論理積(AND)、差分(SUB)などに代表される図形論理演算が行なわれる。通常、図形演算機能としてその他に、図形のエッジの抽出、図形の拡大・縮小などが実装されている。

【0020】

図2に示す第1の情報処理部110は、さらに、DRC/LVSソフトウェアに標準的に実装されているこのような図形演算機能を用いて、配線または層間絶縁層の膜厚に影響を及ぼす特定形状のレイアウトパターンを抽出する。配線パターンの形状に応じて、製造プロセス(特にCMP)の影響をどの程度受けるかについての情報は、TEG等を用いて実験的に予め得られる。具体例については、図4〜図7を参照して後述することとして、以下ではその概要について説明する。

【0021】

図2に示すように、第1の情報処理部110は、パターン抽出部111と、プロセス影響換算部112と、ダミーレイアウト情報生成部113とを含む。

【0022】

パターン抽出部111は、記憶部12,13から読み出したレイアウト情報132に含まれる各配線層(レイヤ)のレイアウトパターンに対して図形演算を施すことによって、ユーザが予め定めた特定形状の配線パターンを抽出する。具体的に、ユーザは特定形状の配線パターンを抽出するための図形演算プログラムに相当する形状認識ルールファイル131を予め作成し、記憶部12,13に格納しておく。パターン抽出部111は、この形状認識ルールファイルに従って特定形状の配線パターンを抽出する。

【0023】

プロセス影響換算部112は、抽出した配線パターンの情報を第2の情報処理部120(LPEソフトウェア)に引き渡すための処理を行なう。具体的に、プロセス影響換算部112は、TEG等を利用して予め実験的に得られた、配線または層間絶縁層の厚みの設計値からのずれの大きさと配線密度との関係に基づいて、特定形状の配線パターンによって生じる配線または層間絶縁層の厚みの設計値からのずれの大きさを、配線密度の大きさに換算する。

【0024】

ダミーレイアウト情報生成部113は、プロセス影響換算部112で換算した配線密度と同じ大きさのパターン密度を有するダミー図形が、特定形状の配線パターンの近辺に配置されているようなダミーレイアウト情報を生成する。このダミーレイアウト情報のデータ形式は、LSIのレイアウト情報のデータ形式と同じであり、汎用で用いられているGDSIIである。これによって、特定形状の配線パターンの膜厚に対する影響を、次のLPEソフトウェア(第2の情報処理部120)に引き渡すことができるようになる。ダミーレイアウト情報生成部113は、生成したダミーレイアウト情報を一旦、記憶部12,13に格納する。

【0025】

(第2の情報処理部120)

LPEソフトウェアによって実現される第2の情報処理部120は、製造プロセスに依存した配線または層間絶縁層の膜厚の設計値からのずれの大きさを予測し、予測したずれの大きさを取り入れて各配線の寄生パラメータ(配線抵抗、配線容量)を抽出する。設計値からの膜厚のずれの大きさを予測する際には、レイアウト情報132から抽出した配線幅、配線間隔および配線密度の情報(もしくは、配線幅および配線密度の情報)と、パターン抽出部に111よって抽出された特定形状の配線パターンに関する情報とに基づいて予測が行なわれる。具体例については、図8〜図11を参照して後述することとし、以下ではその概要について説明する。

【0026】

図2に示すように、第2の情報処理部120は、配線パラメータ抽出部121と、配線密度補正部122と、プロセス影響予測部と123と、寄生パラメータ抽出部124と、ネットリスト生成部125とを含む。

【0027】

配線パラメータ抽出部121(配線密度抽出部)は、各配線の幅、隣接する配線間の間隔および配線密度を、記憶部12,13から読み出したLSIのレイアウト情報132(GDSII形式)から抽出する。ここで、配線密度は、半導体集積回路が配置される各配線層のレイアウト領域を複数の領域に区分したとき、各区分領域の面積に対する配線パターン率として区分領域ごとに計算される。

【0028】

配線密度補正部122は、第1の情報処理部110のパターン抽出部111によって抽出された特定形状の配線パターンが配置されている区分領域において、配線パラメータ抽出部121によって抽出された配線密度の値を補正する。具体的には、配線密度補正部122は、記憶部12,13から読み出したダミーレイアウト情報136(GDSII形式)に基づいてダミー図形のパターン密度を算出し、ダミー図形が配置されている区分領域の本来の配線密度にダミー図形のパターン密度を加算することによって配線密度の値を補正する。

【0029】

プロセス影響予測部123は、レイアウト情報から抽出した配線幅および配線間隔の情報と、配線密度補正部122による補正後の配線密度の情報とに基づいて、配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを予測する。具体的には、TEG等を利用して予め実験的に取得した、配線または層間絶縁層の厚みの設計値からのずれの大きさと、配線幅、配線間隔および配線密度との関係(図2では、プロセス情報134として、数式またはテーブルの形式で予め準備される)に基づいて、設計値からのずれの大きさが推定される。

【0030】

配線寄生パラメータ抽出部124は、プロセス影響予測部によって予測された設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、各配線の寄生パラメータを抽出する。たとえば、配線抵抗は、予め規定されたシート抵抗値に基づいて決定され、配線容量は、電磁界解析ツールを利用して算出される。

【0031】

ネットリスト生成部125は、レイアウトに対応したネットリスト133とLVS結果データベースを利用して、LPEの結果を取込んだ実負荷情報付きのネットリスト137を生成する。以下、より詳細に説明する。

【0032】

[形状認識(特定形状の配線パターンの抽出)]

本実施の形態による設計支援装置では、既存のDRC/LVS用EDAソフトウェアを用いることにより、配線LPE用のソフトウェアに複雑な形状認識機能を追加することなく、高速かつユーザによる柔軟な形状認識規則の指定が可能なルールベースの形状認識を実現する。

【0033】

ルールベースの形状認識では、一般的な認識形状そのものを記憶して一致するものを認識するパターンマッチングと異なり、入力されたレイアウト情報にユーザの記述するルール(図形演算プログラム)に従って図形演算処理を行い、特定形状の配線パターンを抽出する。ルールベースの形状認識の例を以下に具体的に説明する。

【0034】

図3は、図形演算処理によって、ある太さ以上の配線のコーナー内側部分を取り出す例について説明するための図である。

【0035】

図4は、図3の図形演算処理を実行するためのルール(図形演算プログラム)を示す図である。図3、図4を参照して、図3(A)に示すような配線パターンのレイアウト情報が存在したとする。

【0036】

図3(A)を参照して、まず、対象レイヤに対して一定の幅以上の配線(ハッチングを付した配線201,202)のみを取り出す処理を行なう。この処理は、図4(A)に示すように、layer1に対して、幅(WIDTH)が1μmよりも大きい(LARGER)ものを取り出して、wide_lineと名付けるというルールとして記述される。

【0037】

図3(B)を参照して、次に、図3(A)で取り出した配線201,202のエッジ201x,201y,202x,202yを取り出す処理を行なう。この処理は、図4(B1),(B2)に示すように、wide_lineと名付けた配線に対して、x方向のエッジ(EDGE)を取り出してedgexと名付け、y方向のエッジ(EDGE)を取り出してedgeyと名付けるというルールとして記述される。

【0038】

図3(C)を参照して、次に、図3(B)で取り出した配線のエッジ201x,201y,202x,202yに対して幅を与える処理を行なう。この処理は、図4(C1),(C2)に示すように、edgexと名付けたエッジ部分201x、202xをY方向に0.001μm拡張(WIDEN)して(X方向には0)edgex2と名付け、edgeyと名付けたエッジ部分201y,202yをX方向に0.001μm拡張(WIDEN)して(X方向には0)edgey2と名付けるというルールとして記述される。

【0039】

図3(D)を参照して、次に、図3(C)で幅を広げたエッジ部分201xと201yの論理積をとる。この処理は、図4(D)に示すように、edgex2と名付けた部分とedgey2と名付けた部分との論理積(AND)を実行し、演算結果をcornerと名付けるというルールとして記述される。

【0040】

図3(E)を参照して、次に、図3(D)の図形演算結果203a〜203dのうち対象レイヤと重なる部分を取除く処理を行なうことによって、最終的にコーナー部分203bを得る。この処理は、対象レイヤ(layer1)とconrnerと名付けた部分との論理否定を実行し、演算結果をinner_cornerと名付けるというルールとして記述される。

【0041】

[DRC/LVS用ソフトウェアと配線LPEソフトウェアのデータ受渡し]

DRC/LVS用ソフトウェアと配線LPEソフトウェアの間での情報の受け渡しはGDSII形式のファイルを用いて行なう。具体的には、DRC/LVS用EDAソフトウェアは対象形状を認識した後、その形状によって生じる配線または層間絶縁層の厚みにおける設計値からのずれの大きさを決定する。そして、決定した設計値からのずれを、同じずれの大きさが生じる配線密度の大きさに換算する。その後、換算によって得られた配線密度と同じパターン密度を有するGDSIIファイルのダミー図形を生成する。生成したダミー図形のGDSIIファイル(ダミーレイアウト情報)を図2の第2の情報処理部120(配線LPEソフトウェア)に渡す。このとき、配線LPEソフトウェアの仕様に合わせてダミー図形情報を生成する必要があるので、GDSII形式としている。第2の情報処理部では、ダミー図形の密度を実際の配線密度に加算することによって実際の配線密度を補正する計算を行なう。以下、具体的に説明する。

【0042】

図5は、図3、図4の例で抽出した特定形状から決定された膜厚の補正量の情報を、LPEソフトウェアに引き渡すまでの手順を示すフローチャートである。図5を参照して、ステップS101で、図2の第1の情報処理部110は、図形演算ルールを用いて図3(E)に示す特定形状(配線のコーナー)の箇所203bを認識したとする。

【0043】

次のステップS102で、第1の情報処理部110は、図形演算ルールを用いて特定箇所における配線の太さを取得する。配線または層間絶縁層の厚みにおける設計値からのずれの大きさは、特定形状の箇所203bでの配線の太さに関係するからである。

【0044】

次のステップS103で、第1の情報処理部110は、配線幅wから膜厚補正量Δtを所定の計算式Δt=f(w)に従って計算する。この計算式は、事前にTEGなどを用いた測定結果から用意しておく必要がある。

【0045】

次のステップS104で、第1の情報処理部110は、ステップS103で計算した膜厚補正量Δtに相当する配線密度dを所定の計算式d=g(Δt)に従って計算する。この計算式は、事前にTEGなどを用いた測定結果から用意しておく必要がある。

【0046】

次のステップS105で、第1の情報処理部110は、ステップS104で計算した配線密度dと同じパターン密度を有するダミー図形を、抽出した特定箇所の周辺の座標に生成する。具体例を図6に示す。

【0047】

図6は、図5のステップS105で生成するダミー図形の一例を示す図である。抽出した配線のコーナーの近傍の領域204にダミー図形205が生成される。

【0048】

再び図5を参照して、次のステップS106で、第1の情報処理部110は、ステップS105で生成したダミー図形の情報(ダミーレイアウト情報)をGDSIIファイル形式で格納し、受け渡しデータとする。

【0049】

[パターン抽出および受渡しデータ作成の他の例]

図7は、パターン抽出および受渡しデータ作成の他の例を説明するための図である。図7(A)に示すような3重配線のコーナー部分が製造プロセスの影響を受けて設計値の膜厚からずれが生じるものとする。

【0050】

図7(B)を参照して、図2の第1の情報処理部110は、図3、図4で説明したのと同様の方法で各配線のコーナー内側部分301〜303を認識する。

【0051】

図7(C)を参照して、第1の情報処理部110は、各配線のコーナー内側部分をX方向、Y方向に所定の長さ伸張させた図形301e〜303eを生成する。そして、第1の情報処理部110は、生成した図形301e〜303eに基づいて、膜厚が製造プロセスに影響される領域304を認識する。

【0052】

図7(D)を参照して、第1の情報処理部110は、図7(C)で認識した領域304の近辺にダミー図形305を生成する。

【0053】

[配線LPEソフトウェア(第2の情報処理部120)による処理]

第2の情報処理部120は、第1の情報処理部(DRC/LVS用のEDAソフトウェア)で生成された補正情報(ダミーレイアウト情報)を受け取り、受取った補正情報から補正量を求めて膜厚補正を行なう。その後、実際のLPE処理が実行される。

【0054】

補正情報から補正量を求める方法は、配線LPEソフトウェア(第2の情報処理部120)が決定する。したがって、補正情報を生成するDRC/LVS用のEDAソフトウェア(第1の情報処理部110)側では、この方法に合うように補正情報のGDSIIファイル(ダミーレイアウト情報)を生成する必要がある。これは、適切な補正情報の計算式と図形形状の認識ルールとを、ユーザがDRC/LVS用のEDAソフトウェアに入力することで実現されるので、DRC/LVS用のEDAソフトウェアそのものを修正する必要はない。

【0055】

以下に具体例を示す。補正量を求める具体的方法は、ダミーレイアウト情報からパターン密度を計算し、計算したダミー図形の密度を実際の配線密度に加えることによるものとする。

【0056】

図8は、図2の第2の情報処理部120が配線LPEを実行する手順を示すフローチャートである。

【0057】

図8を参照して、第2の情報処理部120は、LSIのレイアウト情報132(GDSII形式)を読み込み(ステップS401)、読み込んだLSIのレイアウト情報132に基づいて配線幅、配線間隔、および配線密度を計算する(S402)。配線密度は、半導体集積回路が配置される各配線層のレイアウト領域を複数の領域に区分したとき、各区分領域の面積に対する配線パターン率として区分領域ごとに計算される。

【0058】

第2の情報処理部120は、さらに、ダミーレイアウト情報136(GDSII形式)を読み込み(ステップS403)、読み込んだダミーレイアウト情報136からダミー図形のパターン密度を実際の配線密度の補正量として計算する(ステップS404)。

【0059】

次のステップS405で、第2の情報処理部120は、ダミー図形の配置されている区分領域において実際の配線密度にダミー図形のパターン密度を加算することによって、配線密度の値を補正する。

【0060】

次にステップS406で、第2の情報処理部120は、ステップS402で計算した配線幅および配線間隔とステップS405による補正後の配線密度とを用いて、配線または層間絶縁層の膜厚の設計値を製造プロセスの影響を取り入れた値に補正する。

【0061】

次のステップS407で、第2の情報処理部120は、ステップS406による補正後の配線膜厚および層間絶縁層の膜厚を用いて、配線の寄生抵抗および寄生容量を抽出する。

【0062】

次のステップS408で、第2の情報処理部120は、ステップS407で抽出した実負荷情報(寄生パラメータ)を取り入れたネットリストを生成する。

【0063】

(1.配線LPEソフトウェアによるダミーパターンの読み込み機能について)

商用の配線LPEツールでは、LPE対象となるLSIのパターンレイアウトデータ(GDSIIファイル)に加えて、配線密度調整用のダミーパターンのみを含んだGDSIIファイルを追加で読み込む機能が既に実装されている。たとえば、CMP処理では、配線のメタル材料の分布がチップ全体にわたってほぼ均一であることが望ましいので、配線の無い領域にダミーメタルを挿入してメタル密度を均一にする処理が一般に行なわれている。このダミーメタルのGDSファイルは、LSIのパターンレイアウトデータとは別に作成されて、設計支援装置に読み込まれる。

【0064】

図9は、配線LPEソフトウェアによるダミーパターンファイルの読み込み機能について説明するための図である。図9を参照して、本来のLPE対象のレイアウト情報を表わすGDSファイルとは別に、ダミーパターンのGDSファイルを読み込み、これらのパターンを合わせたパターンレイアウトに対して配線密度計算およびLPEが実行される。

【0065】

このように、LPE対象のレイアウト情報に加えて別のダミーのレイアウト情報を読み込んで処理を行なう機能自体は既に実装されているため、本実施の形態による設計支援装置で用いられる配線LPE用ソフトウェアに、配線密度補正のためのダミーパターンを追加で読み込む機能を実装するのにかかるコストは小さいものと考えられる。一方で、既存の機能では追加的に読み込んだダミーレイアウトを本来のレイアウト情報にマージ(merge)する処理しか想定されていない。これに対して、本実施の形態の場合には、ダミーのレイアウト情報は配線密度の補正情報としてのみ取扱われ、本来のパターンレイアウトと同列に扱われるものでない。この点で本実施の形態による処理方法は、従来のLPE用ソフトウェアによる処理方法と異なっている。

【0066】

(2.配線密度に応じた配線膜厚の補正機能について)

商用LPEツールでは、配線密度に応じて配線の膜厚を補正する機能が既に実装されている。

【0067】

図10は、配線LPEソフトウェアによる配線膜厚の補正機能について説明するための図である。図10を参照して、配線膜厚を補正するために、まず、入力されたLSIのレイアウトが複数の領域311〜318に区分される。そして、区分領域311〜318ごとに配線密度(パターン占有率)d1〜d8(%)が計算される。次に、事前にテクノロジファイルの作成者が入力した膜厚の補正量を表わす式Δt=f(w,s,d)に従って、配線幅w、配線間隔s、および配線密度dから配線膜厚の補正量Δtが計算される。たとえば、図10の区分領域318では、配線320の幅がwであり、配線319,320間の間隔がsであり、これらの値と配線密度d8によって補正量Δtが計算される。そして、この補正量Δtを膜厚設計値に加算したものに対して、配線抵抗および配線容量を抽出する処理が行なわれる。

【0068】

本実施の形態による設計支援装置は、上記の配線密度dを補正するものであるので、容易に実装することが可能である。

【0069】

図11は、配線密度の補正手順を具体的に説明するための図である。

図2、図11を参照して、本実施の形態では、配線LPEを実行する図2の第2の情報処理部120は、従来必要としていたファイル(LPE対象レイアウト132、ネットリスト133、プロセス情報134、およびLVS結果135)に加えて、膜厚補正用のダミーパターンである第1の情報処理部110(DRC/LVS用ソフトウェア)が出力したダミーレイアウト情報136を読み込む。具体的に、図11(A)に示すように、配線レイアウト(331〜333など)と補正用ダミーレイアウト334とが読み込まれる。

【0070】

次に、図11(B)に示すように、配線膜厚および層間絶縁層の膜厚を補正する段階で、配線レイアウトから実配線密度が計算され、補正用ダミーレイアウトから334からダミー密度が計算される。ダミー密度は、補正用ダミーレイアウト334が存在する区分領域330でのみ計算されている。そして、この区分領域330では、実配線密度にダミー密度を加算することによって配線密度が補正される。

【0071】

次に、図11(C)に示すように、配線膜厚および補正後の配線密度の情報を用いて、膜厚補正値が決定される。したがって、ダミー図形334が配置されている区分領域330では、形状依存性を考慮した膜厚補正値が得られる。このように補正された膜厚を用いてLPEの処理を行い、配線の寄生抵抗、寄生容量が求められる。求めた寄生抵抗、寄生容量を含むネットリストを出力することによってLPE処理が完了する。

【0072】

今回開示された実施の形態はすべての点で例示であって制限的なものでないと考えられるべきである。この発明の範囲は上記した説明ではなくて請求の範囲によって示され、請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0073】

1 コンピュータ本体、10 CPU、12 RAM(記憶部)、13 ハードディスク(記憶部)、110 第1の情報処理部、111 パターン抽出部、112 プロセス影響換算部、113 ダミーレイアウト情報生成部、120 第2の情報処理部、121 配線パラメータ抽出部、122 配線密度補正部、123 プロセス影響予測部、124 配線寄生パラメータ抽出部、125 ネットリスト生成部、131 形状認識ルールファイル、132 LSIのレイアウト情報、133 ネットリスト、136 ダミーレイアウト情報、137 実負荷情報付きネットリスト、205,305,334 ダミー図形、311〜318 区分領域。

【特許請求の範囲】

【請求項1】

半導体集積回路のレイアウト情報を格納する記憶部と、

図形演算機能を有する第1の情報処理部と、

前記レイアウト情報に基づいて寄生パラメータを抽出する第2の情報処理部とを備え、

前記第1の情報処理部は、前記記憶部から読み出した前記レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出するパターン抽出部を含み、

前記第2の情報処理部は、

製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、前記レイアウト情報から抽出した配線幅および配線密度の情報と、前記パターン抽出部によって抽出された前記特定形状の配線パターンに関する情報とに基づいて予測するプロセス影響予測部と、

前記プロセス影響予測部によって予測された設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する配線寄生パラメータ抽出部とを含む、設計支援装置。

【請求項2】

前記第2の情報処理部は、さらに、

前記半導体集積回路が配置される各配線層のレイアウト領域を複数の領域に区分したとき、各区分領域における配線密度を前記レイアウト情報から抽出する配線密度抽出部と、

前記パターン抽出部によって抽出された前記特定形状の配線パターンが配置されている区分領域において、前記配線密度抽出部によって抽出された配線密度の値を補正する配線密度補正部とを含み、

前記プロセス影響予測部は、前記レイアウト情報から抽出した配線幅の情報と、前記配線密度補正部による補正後の配線密度の情報とに基づいて、配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを予測する、請求項1に記載の設計支援装置。

【請求項3】

前記第1の情報処理部は、さらに、

予め実験的に得られた配線または配線層間の絶縁層の厚みの設計値からのずれの大きさと配線密度との関係に基づいて、前記特定形状の配線パターンによって生じる配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、配線密度の大きさに換算するプロセス影響換算部と、

前記プロセス影響換算部で換算した配線密度と同じ大きさのパターン密度を有するダミー図形が、前記特定形状の配線パターンの近辺に配置されているようなダミーレイアウト情報を生成し、生成した前記ダミーレイアウト情報を前記記憶部に記憶させるダミーレイアウト情報生成部とを含み、

前記配線密度補正部は、前記記憶部から読み出した前記ダミーレイアウト情報に基づいて前記ダミー図形のパターン密度を算出し、前記ダミー図形が配置されている区分領域の本来の配線密度に前記ダミー図形のパターン密度を加算することによって、前記配線密度抽出部によって抽出された配線密度の値を補正する、請求項2に記載の設計支援装置。

【請求項4】

前記ダミーレイアウト情報のデータ形式は、前記半導体集積回路のレイアウト情報のデータ形式と同一である、請求項3に記載の設計支援装置。

【請求項5】

前記第1の情報処理部は、前記半導体集積回路のレイアウト情報に対して、前記図形演算機能を利用して設計規則検査およびレイアウト・ネットリストの照合を行なう、請求項1〜4のいずれか1項に記載の設計支援装置。

【請求項1】

半導体集積回路のレイアウト情報を格納する記憶部と、

図形演算機能を有する第1の情報処理部と、

前記レイアウト情報に基づいて寄生パラメータを抽出する第2の情報処理部とを備え、

前記第1の情報処理部は、前記記憶部から読み出した前記レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出するパターン抽出部を含み、

前記第2の情報処理部は、

製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、前記レイアウト情報から抽出した配線幅および配線密度の情報と、前記パターン抽出部によって抽出された前記特定形状の配線パターンに関する情報とに基づいて予測するプロセス影響予測部と、

前記プロセス影響予測部によって予測された設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する配線寄生パラメータ抽出部とを含む、設計支援装置。

【請求項2】

前記第2の情報処理部は、さらに、

前記半導体集積回路が配置される各配線層のレイアウト領域を複数の領域に区分したとき、各区分領域における配線密度を前記レイアウト情報から抽出する配線密度抽出部と、

前記パターン抽出部によって抽出された前記特定形状の配線パターンが配置されている区分領域において、前記配線密度抽出部によって抽出された配線密度の値を補正する配線密度補正部とを含み、

前記プロセス影響予測部は、前記レイアウト情報から抽出した配線幅の情報と、前記配線密度補正部による補正後の配線密度の情報とに基づいて、配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを予測する、請求項1に記載の設計支援装置。

【請求項3】

前記第1の情報処理部は、さらに、

予め実験的に得られた配線または配線層間の絶縁層の厚みの設計値からのずれの大きさと配線密度との関係に基づいて、前記特定形状の配線パターンによって生じる配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、配線密度の大きさに換算するプロセス影響換算部と、

前記プロセス影響換算部で換算した配線密度と同じ大きさのパターン密度を有するダミー図形が、前記特定形状の配線パターンの近辺に配置されているようなダミーレイアウト情報を生成し、生成した前記ダミーレイアウト情報を前記記憶部に記憶させるダミーレイアウト情報生成部とを含み、

前記配線密度補正部は、前記記憶部から読み出した前記ダミーレイアウト情報に基づいて前記ダミー図形のパターン密度を算出し、前記ダミー図形が配置されている区分領域の本来の配線密度に前記ダミー図形のパターン密度を加算することによって、前記配線密度抽出部によって抽出された配線密度の値を補正する、請求項2に記載の設計支援装置。

【請求項4】

前記ダミーレイアウト情報のデータ形式は、前記半導体集積回路のレイアウト情報のデータ形式と同一である、請求項3に記載の設計支援装置。

【請求項5】

前記第1の情報処理部は、前記半導体集積回路のレイアウト情報に対して、前記図形演算機能を利用して設計規則検査およびレイアウト・ネットリストの照合を行なう、請求項1〜4のいずれか1項に記載の設計支援装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−109498(P2013−109498A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−252888(P2011−252888)

【出願日】平成23年11月18日(2011.11.18)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月18日(2011.11.18)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]