設計装置及び設計プログラム

【課題】出力信号に含まれているノイズに係わらず、簡単な計算により最適な制御器を設計する。

【解決手段】入力信号u0を少なくとも1回入力して、制御対象Pから出力された出力信号y0を少なくとも1回計測することにより、少なくとも1回分の入出力データ(入力信号u0及び出力信号y0)を計測する。さらに、出力信号y0に対してスプラインフィッティングを行い、データを平滑化して、出力信号y0から雑音vを除去した出力データysを得る。さらに雑音vを除去した出力データysを線形独立なベクトルの組とし、制御対象Pの線形性に基づいて、目標出力信号y~との線形結合係数列θを算出し、当該線形結合係数列θを用いて、入力信号u0から目標入力信号u~を算出する。算出された1組の目標入力信号u~及び目標出力信号y~と参照モデルMに入力される参照信号r~との偏差e~から制御器Cの伝達関数を決定することにより、制御器Cを設計する。

【解決手段】入力信号u0を少なくとも1回入力して、制御対象Pから出力された出力信号y0を少なくとも1回計測することにより、少なくとも1回分の入出力データ(入力信号u0及び出力信号y0)を計測する。さらに、出力信号y0に対してスプラインフィッティングを行い、データを平滑化して、出力信号y0から雑音vを除去した出力データysを得る。さらに雑音vを除去した出力データysを線形独立なベクトルの組とし、制御対象Pの線形性に基づいて、目標出力信号y~との線形結合係数列θを算出し、当該線形結合係数列θを用いて、入力信号u0から目標入力信号u~を算出する。算出された1組の目標入力信号u~及び目標出力信号y~と参照モデルMに入力される参照信号r~との偏差e~から制御器Cの伝達関数を決定することにより、制御器Cを設計する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、設計装置及び設計プログラム、特に、制御器の設計装置及び設計プログラムに関する。

【背景技術】

【0002】

制御対象の特性が未知のフィードバック制御系において、制御器を適切に設計するために、複数回の実験を行い制御対象の伝達特性を同定する手法が通常用いられる。それに対し、制御対象を同定せずに実験データを直接用いて制御器を設計する方法がいくつか提案されている。それらの中でも特に1回の実験データ(制御器から出力された出力信号)から最適な制御器を設計する方法としてVRFT(Virtual Reference Fedback Tuning)(例えば、非特許文献1参照)や、NCbT(Noniterative Correlaion−based Tuning)(例えば、非特許文献2参照)等があり、制御器の設計にかかる時間やコストを低減することが期待されている。

【0003】

また、特許文献1には、過去の入出力の線形結合で次の出力値が決まる制御対象モデルを同定し、過去の入出力データを基に、目標出力を得るために必要な入力を逆算して制御する制御装置が記載されている。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】M. C. Campi, A. Lecchini, and S. M. Savaresi,”Virtual reference feedback tuning: a direct method for the design of feedback controllers”, Automatica, vol. 38, pp. 1337-1346, (2002)

【非特許文献2】A. Karimi, K. van Heusden, and D. Bonvin, “Noniterative Data-driven Controller Tuning Using the Correlation Approach”, Proc. Of European Control Conference 2007, pp. 5189-5195, (2007)

【特許文献】

【0005】

【特許文献1】特開2007−109103号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述の技術では、適切な制御器を設計できず、適切な制御が行われない懸念がある。

【0007】

例えば、上述のVRFTはPID制御器のようないくつかのパラメータで構成される制御器を含むフィードバック系の参照モデルを考え、その参照モデルの応答が実験により得られた出力データに一致するように最小二乗法を用いて制御器のパラメータを最適化する手法である。しかしながら、VRFTはデータが雑音を含む場合には最適な制御器を設計できないという問題がある。

【0008】

これに対し、上述のNCbは参照信号と雑音との間の相関関数を考え、両者が相関を持たないように制御器パラメータを決定することで雑音の影響をなくすという手法である。このNCbTは雑音を含むデータからでも最適な制御器を設計することができるが、雑音と参照信号の間に相関がない場合に限られるという問題がある。

【0009】

また例えば、VRFTやNCbTでは、非常に複雑な計算が必要になる等の問題がある。

【0010】

本発明は、出力信号に含まれているノイズに係わらず、簡単な計算により適切な制御器を設計することができる、設計装置及び設計プログラムを提供することを目的とする。

【課題を解決するための手段】

【0011】

請求項1に記載の設計装置は、線形性の伝達特性を有する制御対象のフィードバック制御において、前記制御対象に入力信号を少なくとも1回入力させ、前記制御対象から前記入力信号に応じて出力される出力信号を少なくとも1回計測する計測手段と、前記計測手段で計測した少なくとも1つの出力信号に含まれるノイズを除去するノイズ除去手段と、前記制御対象の線形性に基づいて、前記ノイズ除去手段によりノイズが除去された前記出力信号に基づいて、参照モデルの応答として演算される目標出力信号に応じた目標入力信号を演算する演算手段と、前記演算手段により演算された前記目標入力信号と、前記目標出力信号と前記参照モデルに入力される参照信号との偏差と、に基づいて、前記制御器の伝達関数を決定する決定手段と、を備えた。

【0012】

請求項2に記載の設計装置は、請求項1に記載の設計装置において、前記ノイズ除去手段は、最小二乗法によるスプラインフィッティングを用いて、前記計測手段で計測した出力信号からノイズを除去する。

【0013】

請求項3に記載の設計装置は、請求項1または請求項2に記載の設計装置において、前記演算手段は、ノイズが除去された前記出力信号を表す線形独立なベクトルの組と、前記目標出力信号と、前記入力信号と、を用いて前記目標入力信号を演算する。

【0014】

請求項4に記載の設計装置は、請求項3に記載の設計装置において、前記線形独立なベクトルの組は、ノイズが除去された前記出力信号を1時点ずつ後ろへずらしたデータ列を表したベクトルの組である。

【0015】

請求項5に記載の設計装置は、請求項1から請求項4のいずれか1項に記載の設計装置において、前記決定手段で決定した伝達関数を前記制御器に設定する設定手段を備えた。

【0016】

請求項6に記載の設計プログラムは、前記請求項1から前記請求項5のいずれか1項に記載の設計装置のノイズ除去手段、演算手段、及び決定手段として、コンピュータを機能させるためのものである。

【発明の効果】

【0017】

本発明によれば、出力信号に含まれているノイズに係わらず、簡単な計算により適切な制御器を設計することができる。

【図面の簡単な説明】

【0018】

【図1】本実施の形態のフィードバック制御系の一例の概略図である。

【図2】図1のフィードバック制御系に対して、本実施の形態で目的とする参照モデルの概略図である。

【図3】本実施の形態における制御器Cの設計装置の一例の概略構成図である。(A)は、制御器C及び制御対象Pを含むシステム、及び当該制御器Cを設計する設計装置の概略構成図を示しており、(B)は、設計装置のハードウエア構成の概略図を示している。

【図4】本実施の形態における制御器Cの設計装置のその他の例の概略構成図である。

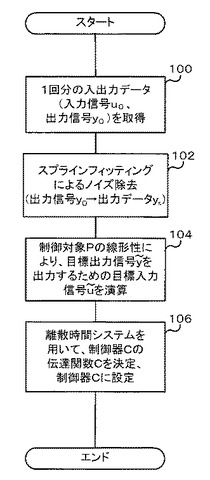

【図5】本実施の形態における設計装置において実行される設計処理の流れの一例のフローチャートである。

【図6】本実施の形態における設計方法を説明するための開ループ形のシステムを示した説明図である。

【図7】本実施の形態における目標出力を出力するための目標入力の求め方を説明するための説明図である。

【図8】実施例1における制御対象Pと参照モデルMそれぞれの5秒間の単位ステップ応答を示したグラフである。

【図9】実施例1における白色ガウス雑音を加えた場合の実験1に対する結果を表したグラフである。

【図10】実施例1における周期的な雑音を加えた場合の実験1に対する結果を表したグラフである。

【図11】実施例1における白色ガウス雑音を加えた場合の実験2に対する結果を表したグラフである。

【図12】実施例1における周期的な雑音を加えた場合の実験2に対する結果を表したグラフである。

【図13】実施例2の実験1におけるRC直列回路の概略を示す回路図である。

【図14】実験1における出力信号に雑音を含まない場合の伝達関数M(s)が1次系の場合に対する結果を表したグラフである。

【図15】実験1における出力信号に雑音を含まない場合の伝達関数M(s)が2次系の場合に対する結果を表したグラフである。

【図16】実施例2の実験2におけるRC直列回路の概略を示す回路図である。

【図17】実験2における出力信号に雑音vを含む場合の伝達関数M(s)が1次系の場合に対する結果を表したグラフである。

【図18】実験2における出力信号に雑音vを含む場合の伝達関数M(s)が2次系の場合に対する結果を表したグラフである。

【発明を実施するための形態】

【0019】

以下、図面を参照して本発明の実施の形態の一例を詳細に説明する。

【0020】

まず、本実施の形態の対象となるフィードバック制御系について説明する。図1に、本実施の形態のフィードバック制御系の一例の概略図を示す。図1では、Cは制御器、Pは制御対象、rは参照信号、eは偏差、uは入力信号、vは雑音、及びyは出力信号をそれぞれ示している。なおここでは、制御対象Pは線形な伝達特性を有しており、インパルス応答が0に収束する安定な制御対象であるものとしている。

【0021】

図2に、図1のフィードバック制御系に対して、本実施の形態で目的とする参照モデルの概略図を示す。図2に示した参照モデルMにおいて、伝達関数をM、そのときの参照信号をr~(rチルダ)とすると、目標とする目標出力信号y~(yチルダ)は次の(1)式で表される。

【0022】

y~=r~M ・・・(1)

【0023】

(1)式に示すように、参照信号r~及び伝達関数Mをそれぞれ設定すれば、目標出力信号y~は決定される。

【0024】

次に、図2に示した参照モデルMを実現する制御器Cを設計する場合について詳細に説明する。

【0025】

図3に、本実施の形態における制御器Cの設計装置の概略構成図を示す。図3(A)は、制御器C及び制御対象Pを含むシステム、及び当該制御器Cを設計する設計装置の概略構成図を示しており、(B)は、設計装置のハードウェア構成の概略図を示している。なお、本実施の形態では、設計装置は、制御対象Pから出力される出力信号yを目標値に追従させるべくフィードバック制御を行う制御器Cの制御用データ(制御器Cの伝達関数C)を設計する機能を有している。

【0026】

設計装置10は、図3に示すように、マイクロコンピュータとして構成されている。また、制御器Cは、MPU(マイクロプロセッサ)20、メモリ22、入力I/F(インターフェイス)24、及び出力I/F26を備えている。

【0027】

MPU20は、制御器C全体を制御する機能を有しており、本実施の形態では、設計装置10により設定された伝達関数Cを実現するための入力信号uを算出し、出力I/F26を介して制御対象Pに出力することにより、制御対象Pの制御を行っている。メモリ22は、伝達関数C等を記憶する機能を有している。出力I/F26は、制御器Cから制御対処Pに出力信号u等を出力するための機能を有する、いわゆるインターフェイスである。また、入力I/F24は、制御対象Pからデータ(制御対象Pの出力データy)等が入力されるための機能を有する、いわゆるインターフェイスである。

【0028】

設計装置10は、図3(B)に示すように、CPU30、ROM32、RAM34、HDD36、及び通信I/F38を備えており、CPU30、ROM32、RAM34、HDD36、及び通信I/F38は、バス39により、互いに情報等の授受が可能に接続されている。

【0029】

CPU30は、設計装置10全体を制御する機能を有すると共に、制御器Cを設計する機能を有している。具体的には、ROM32に格納されている設計プログラム40を実行することにより制御を行っている。なお、本実施の形態では、設計プログラム40は、予めROM32に格納されている構成としているがこれに限らず、設計プログラム40をCD−ROMやリムーバブルディスク、USB等の記録媒体等に記憶しておき、記録媒体からROM32等にインストールするようにしてもよいし、インターネット等の通信回線を介して外部装置からROM32等にインストールするようにしてもよい。RAM34は、CPU30で設計プログラム40を実行する際の作業用の領域を確保するものである。

【0030】

通信I/F38は、制御器Cとの間で各種データ等の通信を行うための機能を有している。本実施の形態では、制御器Cから入出力データ(制御対象Pの入力信号u及び出力信号y、詳細後述)が入力される。一方、設計プログラム40がCPU30で実行されることにより設計(決定)された制御用データ(制御器Cの伝達関数C)が制御器Cに出力される。

【0031】

また、設計装置10は、図3(B)には記載を省略したが、(A)に示すように、ディスプレイ等の表示部、及びキーボードやマウス等、ユーザからの指示を受け付ける受付部を備えている。

【0032】

なお、本実施の形態では、図3に示すように設計装置10を制御器Cの外部に設けるように構成したがこれに限らず、例えば、制御器C内部に設計装置としても機能を備えさせるように構成してもよい。このような場合の概略構成を図4に示す。図4に示すように、制御器Cのメモリ22内に、設計プログラム40を格納し、MPU20で当該設計プログラム40を実行することにより、制御器C内部で、伝達関数Cの演算・決定を行うようにすればよい。なお、このように構成した場合は、外部に設計装置を別途設ける必要が無い。そのため、図3で示した設計装置10に替わり、ディスプレイ等の表示部、及びキーボードやマウス等、ユーザからの指示を受け付ける受付部を備えた端末装置12を備えるようにしてもよい。

【0033】

次に、本実施の形態の制御器Cの設計方法について図面を参照して以下に説明する。

【0034】

図5に、本実施の形態の設計処理の流れの一例のフローチャートを示す。

【0035】

まずステップ100では、図6に示す開ループ形において、制御対象Pに所定の入力信号u0を印加し、出力信号y0を得ることにより1回分の入出力データを取得する。具体的に本実施の形態では、単位ステップ信号を用いて、所定の入力信号u0を制御対象Pに入力させた際に、入力信号u0の入力データ列に応じて出力された出力データ列からなる出力信号y0を1回分の実験データとして取得する。すなわち本実施の形態では、1回分の実験データ(1回の計測)に対応する出力信号y0は、時間毎の計測データ群(出力データ列)により構成される。なお、ここで、出力信号y0には雑音vが含まれているとする。

【0036】

次のステップ102では、出力信号y0にから雑音vを除去する。本実施の形態では、具体的には、区分的なスプライン関数(例えばBスプライン関数)を最小二乗法によって出力信号y0へフィッティングすることにより、出力信号y0に含まれる雑音vを除去している。また、雑音vの除去後、求められたスプライン曲線を離散化したデータ(出力信号)ysを求める。

【0037】

本実施の形態で用いたスプライン関数は、複数の節点によって分割された区分的な多項式であり、節点においてスプライン関数は連続かつ、平滑である。また、1区間(区分)のデータ変動がスプライン全体に及ぶことがないという特徴を有している。なお、各区画は、等間隔で設けるようにしてもよいし、データの変動が大きい領域においては、変動が小さい領域に比べて、細かく区分するように区画を設けてもよい。

【0038】

本実施の形態では、データの平滑化には3次のスプライン関数を用いている。なお、3次関数に限定されないが、3次関数とすることで滑らかな曲線で近似できるためで本実施の形態のように3次のスプライン関数を用いることが好ましい。

【0039】

なお、本実施の形態で用いたスプライン関数には、基底となる1つの多項式が限られた範囲内でのみ有効であるという特徴がある。そのため,最小二乗法によるデータ近似を行う際にデータの一部分が大きく振動していたとしてもその影響がスプライン全体に及ぶことはないので、その他の通常の多項式による近似よりもよい近似を行うことができる。本実施の形態では、その平滑化を出力信号y0に対して行うことにより、雑音vによる振動を抑制して制御器Cの設計への影響を低減している。最小二乗法によって求められたスプライン曲線を実験時と同じサンプリング時間で離散化したものを出力データysとする。これにより、出力信号ysから雑音vが除去された出力データysが得られる。

【0040】

次のステップ104では、制御対象Pに対する1回分の入出力データ(入力信号u0及び出力データys)を用いて、目標出力信号y~を出力するための目標入力信号u~(uチルダ)を求める。このとき、雑音vが含まれない場合を考えると、制御対象Pの線形性から目標入力信号u~は一意に定まるので、出力データysと目標出力信号y~の間の線形な関係式を定義できれば、当該関係式を用いて入力信号u0から目標入力信号u~を求めることができる。

【0041】

図7に示すように、制御対象Pが線形な制御対象であれば出力データysを出力するための入力信号u0は1通りしかなく、また、目標出力信号y~を出力するための目標入力信号u~も1通りしか存在しない。そのため、何らかの線形な関係式によって目標出力信号y~を出力データysから求められれば、同様の関係式を用いて入力信号u0から目標入力信号u~を求めることができる。なお、目標出力信号y~は、上述の(1)式に示したように、参照信号r~及び伝達関数Mをそれぞれ設定すれば決定される。

【0042】

本実施の形態では、入力信号u0から目標入力信号u~を求めるために、まず、出力データysを線形独立なベクトルの組として表現する。

【0043】

その方法の1つとして、例えば、出力データysのデータ列を、(2)式に示したベクトルで表現する。

【0044】

ys0=[ys(0)、ys(1)、ys(2)、・・・・・・、ys(n−1)] ・・・(2)

【0045】

ここで、かっこ内の数字は時間毎の計測データの番号、nはデータの要素数である。このys0からデータを1つずつ後ろへずらしたデータ列をそれぞれ、

ys1=[0、ys(0)、ys(1)、・・・・・・、ys(n−2)]

ys2=[0、0、ys(0)、ys(1)、・・・・・・、ys(n−3)]

・・・・・・

ys(n−1)=[0、0、0、0、・・・・・・、ys(0)]

とおく。

【0046】

なお、上記の方法でなくとも線形独立なベクトルの組ys0〜ys(n−1)が決まれば、目標出力信号y~をこれらの線形結合として、(3)式とする。

【0047】

【数1】

【0048】

これは、出力データysから目標出力信号y~への変換を意味している。そして、疑似逆行列Y+を用いて線形結合係数列θを(4)式により計算する。

【0049】

【数2】

【0050】

当該線形結合係数列θを用いることにより、入力信号u0から目標入力信号u~への変換も同様に、(5)式として計算することができる。

【0051】

【数3】

このようにすることにより、目標出力信号y~を出力するための目標入力信号u~を演算することができる。

【0052】

次のステップ106では、目標出力信号y~、及び目標入力信号u~ を用いて、制御器Cの離散時間伝達関数C(z)(以下、単に伝達関数Cという)を決定し、設定することにより、制御器Cをディジタルフィルタとして設計する。

【0053】

上記ステップ104で得られた目標入力信号u~と目標出力信号y~によって制御器Cを設計するにあたり、まず、目標出力信号y~、及び目標入力信号u~の各々をz変換し、u~(z)、y~(z)とする。図2に示した参照モデルMから、目標出力時の偏差e~(eチルダ)は、(6)式となる。

【0054】

【数4】

となる。また、制御器Cは伝達関数C(z)として、(7)式で与えることができる。

【0055】

【数5】

【0056】

当該伝達関数C(z)を図1に示す実際のフィードバック制御系に適用して制御を行う際の偏差をe(z)、入力信号をu(z)とすると、(8)式のように書くことができる。

【0057】

【数6】

【0058】

(8)式を差分方程式により表現すると、時刻t(t=0、1、2、・・・) の入力信号u(t)は、(9)式となる。

【0059】

【数7】

【0060】

(9)式中の、i、jの番号は、計測を開始してからのデータの番号を表す。目標入力信号u~及び目標出力信号y~は、入力信号u0及び出力信号y0と同じくn個のデータしか持っていないため、このままでは制御を行う際にn個分以上のデータ計測が行われるとそれ以降のu(t)を正確に計算できない。そこで本実施の形態では、目標入力信号u~及び偏差e~を無限時間分のデータに拡張する。そのために、目標入力信号u~及び偏差e~の最後のデータu~(n−1)、e~(n−1)が飽和値に十分近く収束しているとみなして、これらをn番目以降の目標入力信号u~及び偏差e~のデータとして使用することで無限時間分に拡張する。なお、これは簡単なプログラムで実現が可能である。また、目標入力信号u~及び偏差e~が収束するように参照信号r~を設定する必要がある。

【0061】

なお、ここでは、制御器Cが伝達関数Cを実現するように、(9)式の差分方程式により入力信号u(t)を求めているがこれに限らず、制御器CをPID制御により伝達関数Cを実現するものとして入力信号u(t)を求めるようにしてもよい。

【0062】

(実施例1)

実施例1では、シミュレーションによる実験を行った。ここでは簡単化のため入力信号u0、参照信号r~、参照信号rは全て単位ステップ信号を用いた。制御対象Pと参照モデルMの連続時間系における伝達関数をそれぞれ

P(s)=4/(s+2)、

M(s)=10/(s+10)

とした。

【0063】

制御対象Pと参照モデルMそれぞれの5秒間の単位ステップ応答を図8に示す。これらは、雑音vのない場合の出力信号y0(図8、実線:Pの応答、参照)と、目標出力信号y~(図8、破線:Mの応答、参照)と、に相当する。図8に示したPの応答をMの応答になるように制御器Cが制御するように、制御器Cを設計する。

【0064】

実験1として、出力信号y0を計測し、スプライン関数のフィッティングにより雑音vを除去した出力データysを計算(上述の図5、ステップ102の処理参照)して、図8の実線で示した応答を得た。データは、サンプリング時間Ts=0.05(s)毎に計測されるものとし、以下の2種類の雑音vをそれぞれ加えて実験を行った。一方は、平均0、標準偏差0.05の白色ガウス雑音とし、他方は、以下の(10)式に示す周期的な雑音とした。

【0065】

v(t)=0.05sin10t ・・・(10)

【0066】

実験1に対する結果を、図9及び図10に示す。図9は、白色ガウス雑音を加えた場合を表したグラフであり、図10は、(10)式の周期的な雑音を加えた場合を表したグラフである。黒丸は出力信号y0、実線は出力データys、破線は雑音vがない場合の出力(Pのステップ応答)を示す。計測時間は5(s)とした。図9及び図10に示したグラフから、スプライン関数をy0にフィッティングすることにより、雑音vが、白色雑音か、周期的な雑音かにかかわらず、いずれの場合においても雑音vをほぼ抑制できていることがわかる。

【0067】

さらに、実験2として、実験1で得られた出力データysから上述の図5に示したステップ104の処理及びステップ106の処理に従い、制御器Cを設計し、図1の制御系にその制御器Cを適用して応答(出力信号)yを計測し、図8の破線で示した目標出力信号y~との比較を行った。

【0068】

実験2に対する結果を、図11及び図12に示す。図11は、白色ガウス雑音を加えた場合を表したグラフであり、図12は、(10)の周期的な雑音を加えた場合を表したグラフである。黒丸は設計したフィードバック制御系の出力信号y、破線は目標出力信号y~である。なお、計測時間は、実験1の時の2倍の10(s)としている。

【0069】

図11及び図12に示したグラフから、いずれの場合も出力信号yは、目標出力信号y~とほぼ一致していることがわかる。すなわち、いずれの場合においても、設計した制御器Cによってほぼ最適な制御ができており、また実験1で得られた5(s)分のデータを用いてそれ以上の時間実験を行っても適切に制御ができていることがわかる。

(実施例2)

実施例2では、RC直列回路の入力電圧を入力信号u、及び出力電圧を出力信号yとして、実施例1と同様の手順で実験を行った。実施例2で用いたRC直列回路の概略の回路図を図13に示す。なお、ここでは、当該RC直列回路の回路定数を未知であるものとして、マイコンのプログラムによって計測及び制御を行った。具体的には、マイコンのD/A変換ポートから発生させた入力信号uを図13に示したRC直列回路に入力させ、当該RC直接回路から出力された出力信号yをマイコンのA/D変換ポートによって計測した。

【0070】

実験1は、出力信号にノイズが含まれていない場合である。参照モデルMの伝達関数M(s)が以下の1次系の場合と、2次系の場合と、2種類の場合に対して実験を行った。

M(s)=2/(s+2) ・・・1次系

M(s)=15/(s2+5S+15) ・・・2次系

【0071】

実験結果を図14及び図15に示す。図14は、伝達関数M(s)が1次系の場合を表したグラフであり、図15は、伝達関数M(s)が2次系の場合を表したグラフである。なお、サンプリング時間は0.05(s)とし、計測時間は、10(s)間とした。図14及び図15に示したグラフ中の出力信号y0は入力信号としてu0=1(V)を図13に示したRC直列回路に印加した際のステップ応答である。出力データysは、出力信号に対して、上述した図5のステップ102の処理によりスプライン関数近似を施したものである。出力データysから上述の図5に示したステップ104の処理及びステップ106の処理に従い、制御器Cを設計し、出力信号yを計測し、図14及び図15の破線で示した目標出力信号y~との比較を行った。目標出力信号y~は、設計した制御器Cを含む制御系のステップ応答(理想とする応答)である。また、出力信号yは、目標値r=1(V)で制御を行った際の出力応答である。

【0072】

図14及び図15に示したグラフから、いずれの場合も出力信号yは、目標出力信号y~とほぼ一致していることがわかる。すなわち、いずれの場合においても、設計した制御器Cによってほぼ最適な制御ができており、理想通りの応答(出力信号y)が得られた。

【0073】

さらに、実験2として、上述の図13に示したRC直列回路にリアルタイムで平均0、標準偏差0.01の白色雑音を加えて実験1と同様に同条件で実験を行った。なお、本実験2は、図16に示した、雑音vを含むRC直列回路に対する制御器Cの設計及び、制御器Cによる制御の実験とみなすことができる。

【0074】

実験結果を図17及び図18に示す。図17は、伝達関数M(s)が1次系の場合を表したグラフであり、図18は、伝達関数M(s)が2次系の場合を表したグラフである。

【0075】

図17及び図18に示したグラフから、わかるように、スプラインフィッティングにより、出力データvsは、雑音vが抑制されている。また、計測データ(出力信号y)は、伝達関数M(s)が1次系及び2次系のいずれの場合においても、雑音vによってばらつくものの、理想応答(目標出力信号y~)に追従できていることがわかる。

【0076】

従って、実施例2においても、本実施の形態の設計装置(設計方法)により設計した制御器Cによって制御対象を適切に制御できる。

【0077】

以上説明したように本実施の形態では、制御対象Pに入力信号u0を1回入力し、制御対象Pから出力された出力信号y0を1回計測することにより、1回分の入出力データ(入力信号u0及び出力信号y0)を計測する。さらに、出力信号y0に対してスプラインフィッティングを行い、データを平滑化して、出力信号y0から雑音vを除去した出力データysを得る。さらに雑音vを除去した出力データysを線形独立なベクトルの組とし、制御対象Pの線形性に基づいて、目標出力信号y~との線形結合係数列θを算出し、当該線形結合係数列θを用いて、入力信号u0から目標入力信号u~を算出する。算出された1組の目標入力信号u~及び目標出力信号y~と参照モデルMに入力される参照信号r~との偏差e~から制御器Cの伝達関数を決定することにより、制御器Cを設計する。

【0078】

これにより、出力信号に含まれているノイズを適切に除去・抑制することができるため、出力信号に含まれるノイズに係わらず例えば、雑音と参照信号の間に相関がある場合であっても、簡単な計算により、制御対象Pの特性が未知である制御対象Pから目標出力信号y~を出力させるように適切な制御を行うことができる制御器Cを設計することができる。

【0079】

なお、本実施の形態では、1回分の実験データを用いているが複数回分の実験データを用いる(複数回計測を行う)ようにしてもよい。なお、本実施の形態のように1回分の実験データを用いる場合であっても、上述のように、適切な制御を行うことができる制御器Cを設計することができる。

【符号の説明】

【0080】

10 設計装置

40 設計プログラム

C 制御器

P 制御対象

M 参照モデル

【技術分野】

【0001】

本発明は、設計装置及び設計プログラム、特に、制御器の設計装置及び設計プログラムに関する。

【背景技術】

【0002】

制御対象の特性が未知のフィードバック制御系において、制御器を適切に設計するために、複数回の実験を行い制御対象の伝達特性を同定する手法が通常用いられる。それに対し、制御対象を同定せずに実験データを直接用いて制御器を設計する方法がいくつか提案されている。それらの中でも特に1回の実験データ(制御器から出力された出力信号)から最適な制御器を設計する方法としてVRFT(Virtual Reference Fedback Tuning)(例えば、非特許文献1参照)や、NCbT(Noniterative Correlaion−based Tuning)(例えば、非特許文献2参照)等があり、制御器の設計にかかる時間やコストを低減することが期待されている。

【0003】

また、特許文献1には、過去の入出力の線形結合で次の出力値が決まる制御対象モデルを同定し、過去の入出力データを基に、目標出力を得るために必要な入力を逆算して制御する制御装置が記載されている。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】M. C. Campi, A. Lecchini, and S. M. Savaresi,”Virtual reference feedback tuning: a direct method for the design of feedback controllers”, Automatica, vol. 38, pp. 1337-1346, (2002)

【非特許文献2】A. Karimi, K. van Heusden, and D. Bonvin, “Noniterative Data-driven Controller Tuning Using the Correlation Approach”, Proc. Of European Control Conference 2007, pp. 5189-5195, (2007)

【特許文献】

【0005】

【特許文献1】特開2007−109103号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述の技術では、適切な制御器を設計できず、適切な制御が行われない懸念がある。

【0007】

例えば、上述のVRFTはPID制御器のようないくつかのパラメータで構成される制御器を含むフィードバック系の参照モデルを考え、その参照モデルの応答が実験により得られた出力データに一致するように最小二乗法を用いて制御器のパラメータを最適化する手法である。しかしながら、VRFTはデータが雑音を含む場合には最適な制御器を設計できないという問題がある。

【0008】

これに対し、上述のNCbは参照信号と雑音との間の相関関数を考え、両者が相関を持たないように制御器パラメータを決定することで雑音の影響をなくすという手法である。このNCbTは雑音を含むデータからでも最適な制御器を設計することができるが、雑音と参照信号の間に相関がない場合に限られるという問題がある。

【0009】

また例えば、VRFTやNCbTでは、非常に複雑な計算が必要になる等の問題がある。

【0010】

本発明は、出力信号に含まれているノイズに係わらず、簡単な計算により適切な制御器を設計することができる、設計装置及び設計プログラムを提供することを目的とする。

【課題を解決するための手段】

【0011】

請求項1に記載の設計装置は、線形性の伝達特性を有する制御対象のフィードバック制御において、前記制御対象に入力信号を少なくとも1回入力させ、前記制御対象から前記入力信号に応じて出力される出力信号を少なくとも1回計測する計測手段と、前記計測手段で計測した少なくとも1つの出力信号に含まれるノイズを除去するノイズ除去手段と、前記制御対象の線形性に基づいて、前記ノイズ除去手段によりノイズが除去された前記出力信号に基づいて、参照モデルの応答として演算される目標出力信号に応じた目標入力信号を演算する演算手段と、前記演算手段により演算された前記目標入力信号と、前記目標出力信号と前記参照モデルに入力される参照信号との偏差と、に基づいて、前記制御器の伝達関数を決定する決定手段と、を備えた。

【0012】

請求項2に記載の設計装置は、請求項1に記載の設計装置において、前記ノイズ除去手段は、最小二乗法によるスプラインフィッティングを用いて、前記計測手段で計測した出力信号からノイズを除去する。

【0013】

請求項3に記載の設計装置は、請求項1または請求項2に記載の設計装置において、前記演算手段は、ノイズが除去された前記出力信号を表す線形独立なベクトルの組と、前記目標出力信号と、前記入力信号と、を用いて前記目標入力信号を演算する。

【0014】

請求項4に記載の設計装置は、請求項3に記載の設計装置において、前記線形独立なベクトルの組は、ノイズが除去された前記出力信号を1時点ずつ後ろへずらしたデータ列を表したベクトルの組である。

【0015】

請求項5に記載の設計装置は、請求項1から請求項4のいずれか1項に記載の設計装置において、前記決定手段で決定した伝達関数を前記制御器に設定する設定手段を備えた。

【0016】

請求項6に記載の設計プログラムは、前記請求項1から前記請求項5のいずれか1項に記載の設計装置のノイズ除去手段、演算手段、及び決定手段として、コンピュータを機能させるためのものである。

【発明の効果】

【0017】

本発明によれば、出力信号に含まれているノイズに係わらず、簡単な計算により適切な制御器を設計することができる。

【図面の簡単な説明】

【0018】

【図1】本実施の形態のフィードバック制御系の一例の概略図である。

【図2】図1のフィードバック制御系に対して、本実施の形態で目的とする参照モデルの概略図である。

【図3】本実施の形態における制御器Cの設計装置の一例の概略構成図である。(A)は、制御器C及び制御対象Pを含むシステム、及び当該制御器Cを設計する設計装置の概略構成図を示しており、(B)は、設計装置のハードウエア構成の概略図を示している。

【図4】本実施の形態における制御器Cの設計装置のその他の例の概略構成図である。

【図5】本実施の形態における設計装置において実行される設計処理の流れの一例のフローチャートである。

【図6】本実施の形態における設計方法を説明するための開ループ形のシステムを示した説明図である。

【図7】本実施の形態における目標出力を出力するための目標入力の求め方を説明するための説明図である。

【図8】実施例1における制御対象Pと参照モデルMそれぞれの5秒間の単位ステップ応答を示したグラフである。

【図9】実施例1における白色ガウス雑音を加えた場合の実験1に対する結果を表したグラフである。

【図10】実施例1における周期的な雑音を加えた場合の実験1に対する結果を表したグラフである。

【図11】実施例1における白色ガウス雑音を加えた場合の実験2に対する結果を表したグラフである。

【図12】実施例1における周期的な雑音を加えた場合の実験2に対する結果を表したグラフである。

【図13】実施例2の実験1におけるRC直列回路の概略を示す回路図である。

【図14】実験1における出力信号に雑音を含まない場合の伝達関数M(s)が1次系の場合に対する結果を表したグラフである。

【図15】実験1における出力信号に雑音を含まない場合の伝達関数M(s)が2次系の場合に対する結果を表したグラフである。

【図16】実施例2の実験2におけるRC直列回路の概略を示す回路図である。

【図17】実験2における出力信号に雑音vを含む場合の伝達関数M(s)が1次系の場合に対する結果を表したグラフである。

【図18】実験2における出力信号に雑音vを含む場合の伝達関数M(s)が2次系の場合に対する結果を表したグラフである。

【発明を実施するための形態】

【0019】

以下、図面を参照して本発明の実施の形態の一例を詳細に説明する。

【0020】

まず、本実施の形態の対象となるフィードバック制御系について説明する。図1に、本実施の形態のフィードバック制御系の一例の概略図を示す。図1では、Cは制御器、Pは制御対象、rは参照信号、eは偏差、uは入力信号、vは雑音、及びyは出力信号をそれぞれ示している。なおここでは、制御対象Pは線形な伝達特性を有しており、インパルス応答が0に収束する安定な制御対象であるものとしている。

【0021】

図2に、図1のフィードバック制御系に対して、本実施の形態で目的とする参照モデルの概略図を示す。図2に示した参照モデルMにおいて、伝達関数をM、そのときの参照信号をr~(rチルダ)とすると、目標とする目標出力信号y~(yチルダ)は次の(1)式で表される。

【0022】

y~=r~M ・・・(1)

【0023】

(1)式に示すように、参照信号r~及び伝達関数Mをそれぞれ設定すれば、目標出力信号y~は決定される。

【0024】

次に、図2に示した参照モデルMを実現する制御器Cを設計する場合について詳細に説明する。

【0025】

図3に、本実施の形態における制御器Cの設計装置の概略構成図を示す。図3(A)は、制御器C及び制御対象Pを含むシステム、及び当該制御器Cを設計する設計装置の概略構成図を示しており、(B)は、設計装置のハードウェア構成の概略図を示している。なお、本実施の形態では、設計装置は、制御対象Pから出力される出力信号yを目標値に追従させるべくフィードバック制御を行う制御器Cの制御用データ(制御器Cの伝達関数C)を設計する機能を有している。

【0026】

設計装置10は、図3に示すように、マイクロコンピュータとして構成されている。また、制御器Cは、MPU(マイクロプロセッサ)20、メモリ22、入力I/F(インターフェイス)24、及び出力I/F26を備えている。

【0027】

MPU20は、制御器C全体を制御する機能を有しており、本実施の形態では、設計装置10により設定された伝達関数Cを実現するための入力信号uを算出し、出力I/F26を介して制御対象Pに出力することにより、制御対象Pの制御を行っている。メモリ22は、伝達関数C等を記憶する機能を有している。出力I/F26は、制御器Cから制御対処Pに出力信号u等を出力するための機能を有する、いわゆるインターフェイスである。また、入力I/F24は、制御対象Pからデータ(制御対象Pの出力データy)等が入力されるための機能を有する、いわゆるインターフェイスである。

【0028】

設計装置10は、図3(B)に示すように、CPU30、ROM32、RAM34、HDD36、及び通信I/F38を備えており、CPU30、ROM32、RAM34、HDD36、及び通信I/F38は、バス39により、互いに情報等の授受が可能に接続されている。

【0029】

CPU30は、設計装置10全体を制御する機能を有すると共に、制御器Cを設計する機能を有している。具体的には、ROM32に格納されている設計プログラム40を実行することにより制御を行っている。なお、本実施の形態では、設計プログラム40は、予めROM32に格納されている構成としているがこれに限らず、設計プログラム40をCD−ROMやリムーバブルディスク、USB等の記録媒体等に記憶しておき、記録媒体からROM32等にインストールするようにしてもよいし、インターネット等の通信回線を介して外部装置からROM32等にインストールするようにしてもよい。RAM34は、CPU30で設計プログラム40を実行する際の作業用の領域を確保するものである。

【0030】

通信I/F38は、制御器Cとの間で各種データ等の通信を行うための機能を有している。本実施の形態では、制御器Cから入出力データ(制御対象Pの入力信号u及び出力信号y、詳細後述)が入力される。一方、設計プログラム40がCPU30で実行されることにより設計(決定)された制御用データ(制御器Cの伝達関数C)が制御器Cに出力される。

【0031】

また、設計装置10は、図3(B)には記載を省略したが、(A)に示すように、ディスプレイ等の表示部、及びキーボードやマウス等、ユーザからの指示を受け付ける受付部を備えている。

【0032】

なお、本実施の形態では、図3に示すように設計装置10を制御器Cの外部に設けるように構成したがこれに限らず、例えば、制御器C内部に設計装置としても機能を備えさせるように構成してもよい。このような場合の概略構成を図4に示す。図4に示すように、制御器Cのメモリ22内に、設計プログラム40を格納し、MPU20で当該設計プログラム40を実行することにより、制御器C内部で、伝達関数Cの演算・決定を行うようにすればよい。なお、このように構成した場合は、外部に設計装置を別途設ける必要が無い。そのため、図3で示した設計装置10に替わり、ディスプレイ等の表示部、及びキーボードやマウス等、ユーザからの指示を受け付ける受付部を備えた端末装置12を備えるようにしてもよい。

【0033】

次に、本実施の形態の制御器Cの設計方法について図面を参照して以下に説明する。

【0034】

図5に、本実施の形態の設計処理の流れの一例のフローチャートを示す。

【0035】

まずステップ100では、図6に示す開ループ形において、制御対象Pに所定の入力信号u0を印加し、出力信号y0を得ることにより1回分の入出力データを取得する。具体的に本実施の形態では、単位ステップ信号を用いて、所定の入力信号u0を制御対象Pに入力させた際に、入力信号u0の入力データ列に応じて出力された出力データ列からなる出力信号y0を1回分の実験データとして取得する。すなわち本実施の形態では、1回分の実験データ(1回の計測)に対応する出力信号y0は、時間毎の計測データ群(出力データ列)により構成される。なお、ここで、出力信号y0には雑音vが含まれているとする。

【0036】

次のステップ102では、出力信号y0にから雑音vを除去する。本実施の形態では、具体的には、区分的なスプライン関数(例えばBスプライン関数)を最小二乗法によって出力信号y0へフィッティングすることにより、出力信号y0に含まれる雑音vを除去している。また、雑音vの除去後、求められたスプライン曲線を離散化したデータ(出力信号)ysを求める。

【0037】

本実施の形態で用いたスプライン関数は、複数の節点によって分割された区分的な多項式であり、節点においてスプライン関数は連続かつ、平滑である。また、1区間(区分)のデータ変動がスプライン全体に及ぶことがないという特徴を有している。なお、各区画は、等間隔で設けるようにしてもよいし、データの変動が大きい領域においては、変動が小さい領域に比べて、細かく区分するように区画を設けてもよい。

【0038】

本実施の形態では、データの平滑化には3次のスプライン関数を用いている。なお、3次関数に限定されないが、3次関数とすることで滑らかな曲線で近似できるためで本実施の形態のように3次のスプライン関数を用いることが好ましい。

【0039】

なお、本実施の形態で用いたスプライン関数には、基底となる1つの多項式が限られた範囲内でのみ有効であるという特徴がある。そのため,最小二乗法によるデータ近似を行う際にデータの一部分が大きく振動していたとしてもその影響がスプライン全体に及ぶことはないので、その他の通常の多項式による近似よりもよい近似を行うことができる。本実施の形態では、その平滑化を出力信号y0に対して行うことにより、雑音vによる振動を抑制して制御器Cの設計への影響を低減している。最小二乗法によって求められたスプライン曲線を実験時と同じサンプリング時間で離散化したものを出力データysとする。これにより、出力信号ysから雑音vが除去された出力データysが得られる。

【0040】

次のステップ104では、制御対象Pに対する1回分の入出力データ(入力信号u0及び出力データys)を用いて、目標出力信号y~を出力するための目標入力信号u~(uチルダ)を求める。このとき、雑音vが含まれない場合を考えると、制御対象Pの線形性から目標入力信号u~は一意に定まるので、出力データysと目標出力信号y~の間の線形な関係式を定義できれば、当該関係式を用いて入力信号u0から目標入力信号u~を求めることができる。

【0041】

図7に示すように、制御対象Pが線形な制御対象であれば出力データysを出力するための入力信号u0は1通りしかなく、また、目標出力信号y~を出力するための目標入力信号u~も1通りしか存在しない。そのため、何らかの線形な関係式によって目標出力信号y~を出力データysから求められれば、同様の関係式を用いて入力信号u0から目標入力信号u~を求めることができる。なお、目標出力信号y~は、上述の(1)式に示したように、参照信号r~及び伝達関数Mをそれぞれ設定すれば決定される。

【0042】

本実施の形態では、入力信号u0から目標入力信号u~を求めるために、まず、出力データysを線形独立なベクトルの組として表現する。

【0043】

その方法の1つとして、例えば、出力データysのデータ列を、(2)式に示したベクトルで表現する。

【0044】

ys0=[ys(0)、ys(1)、ys(2)、・・・・・・、ys(n−1)] ・・・(2)

【0045】

ここで、かっこ内の数字は時間毎の計測データの番号、nはデータの要素数である。このys0からデータを1つずつ後ろへずらしたデータ列をそれぞれ、

ys1=[0、ys(0)、ys(1)、・・・・・・、ys(n−2)]

ys2=[0、0、ys(0)、ys(1)、・・・・・・、ys(n−3)]

・・・・・・

ys(n−1)=[0、0、0、0、・・・・・・、ys(0)]

とおく。

【0046】

なお、上記の方法でなくとも線形独立なベクトルの組ys0〜ys(n−1)が決まれば、目標出力信号y~をこれらの線形結合として、(3)式とする。

【0047】

【数1】

【0048】

これは、出力データysから目標出力信号y~への変換を意味している。そして、疑似逆行列Y+を用いて線形結合係数列θを(4)式により計算する。

【0049】

【数2】

【0050】

当該線形結合係数列θを用いることにより、入力信号u0から目標入力信号u~への変換も同様に、(5)式として計算することができる。

【0051】

【数3】

このようにすることにより、目標出力信号y~を出力するための目標入力信号u~を演算することができる。

【0052】

次のステップ106では、目標出力信号y~、及び目標入力信号u~ を用いて、制御器Cの離散時間伝達関数C(z)(以下、単に伝達関数Cという)を決定し、設定することにより、制御器Cをディジタルフィルタとして設計する。

【0053】

上記ステップ104で得られた目標入力信号u~と目標出力信号y~によって制御器Cを設計するにあたり、まず、目標出力信号y~、及び目標入力信号u~の各々をz変換し、u~(z)、y~(z)とする。図2に示した参照モデルMから、目標出力時の偏差e~(eチルダ)は、(6)式となる。

【0054】

【数4】

となる。また、制御器Cは伝達関数C(z)として、(7)式で与えることができる。

【0055】

【数5】

【0056】

当該伝達関数C(z)を図1に示す実際のフィードバック制御系に適用して制御を行う際の偏差をe(z)、入力信号をu(z)とすると、(8)式のように書くことができる。

【0057】

【数6】

【0058】

(8)式を差分方程式により表現すると、時刻t(t=0、1、2、・・・) の入力信号u(t)は、(9)式となる。

【0059】

【数7】

【0060】

(9)式中の、i、jの番号は、計測を開始してからのデータの番号を表す。目標入力信号u~及び目標出力信号y~は、入力信号u0及び出力信号y0と同じくn個のデータしか持っていないため、このままでは制御を行う際にn個分以上のデータ計測が行われるとそれ以降のu(t)を正確に計算できない。そこで本実施の形態では、目標入力信号u~及び偏差e~を無限時間分のデータに拡張する。そのために、目標入力信号u~及び偏差e~の最後のデータu~(n−1)、e~(n−1)が飽和値に十分近く収束しているとみなして、これらをn番目以降の目標入力信号u~及び偏差e~のデータとして使用することで無限時間分に拡張する。なお、これは簡単なプログラムで実現が可能である。また、目標入力信号u~及び偏差e~が収束するように参照信号r~を設定する必要がある。

【0061】

なお、ここでは、制御器Cが伝達関数Cを実現するように、(9)式の差分方程式により入力信号u(t)を求めているがこれに限らず、制御器CをPID制御により伝達関数Cを実現するものとして入力信号u(t)を求めるようにしてもよい。

【0062】

(実施例1)

実施例1では、シミュレーションによる実験を行った。ここでは簡単化のため入力信号u0、参照信号r~、参照信号rは全て単位ステップ信号を用いた。制御対象Pと参照モデルMの連続時間系における伝達関数をそれぞれ

P(s)=4/(s+2)、

M(s)=10/(s+10)

とした。

【0063】

制御対象Pと参照モデルMそれぞれの5秒間の単位ステップ応答を図8に示す。これらは、雑音vのない場合の出力信号y0(図8、実線:Pの応答、参照)と、目標出力信号y~(図8、破線:Mの応答、参照)と、に相当する。図8に示したPの応答をMの応答になるように制御器Cが制御するように、制御器Cを設計する。

【0064】

実験1として、出力信号y0を計測し、スプライン関数のフィッティングにより雑音vを除去した出力データysを計算(上述の図5、ステップ102の処理参照)して、図8の実線で示した応答を得た。データは、サンプリング時間Ts=0.05(s)毎に計測されるものとし、以下の2種類の雑音vをそれぞれ加えて実験を行った。一方は、平均0、標準偏差0.05の白色ガウス雑音とし、他方は、以下の(10)式に示す周期的な雑音とした。

【0065】

v(t)=0.05sin10t ・・・(10)

【0066】

実験1に対する結果を、図9及び図10に示す。図9は、白色ガウス雑音を加えた場合を表したグラフであり、図10は、(10)式の周期的な雑音を加えた場合を表したグラフである。黒丸は出力信号y0、実線は出力データys、破線は雑音vがない場合の出力(Pのステップ応答)を示す。計測時間は5(s)とした。図9及び図10に示したグラフから、スプライン関数をy0にフィッティングすることにより、雑音vが、白色雑音か、周期的な雑音かにかかわらず、いずれの場合においても雑音vをほぼ抑制できていることがわかる。

【0067】

さらに、実験2として、実験1で得られた出力データysから上述の図5に示したステップ104の処理及びステップ106の処理に従い、制御器Cを設計し、図1の制御系にその制御器Cを適用して応答(出力信号)yを計測し、図8の破線で示した目標出力信号y~との比較を行った。

【0068】

実験2に対する結果を、図11及び図12に示す。図11は、白色ガウス雑音を加えた場合を表したグラフであり、図12は、(10)の周期的な雑音を加えた場合を表したグラフである。黒丸は設計したフィードバック制御系の出力信号y、破線は目標出力信号y~である。なお、計測時間は、実験1の時の2倍の10(s)としている。

【0069】

図11及び図12に示したグラフから、いずれの場合も出力信号yは、目標出力信号y~とほぼ一致していることがわかる。すなわち、いずれの場合においても、設計した制御器Cによってほぼ最適な制御ができており、また実験1で得られた5(s)分のデータを用いてそれ以上の時間実験を行っても適切に制御ができていることがわかる。

(実施例2)

実施例2では、RC直列回路の入力電圧を入力信号u、及び出力電圧を出力信号yとして、実施例1と同様の手順で実験を行った。実施例2で用いたRC直列回路の概略の回路図を図13に示す。なお、ここでは、当該RC直列回路の回路定数を未知であるものとして、マイコンのプログラムによって計測及び制御を行った。具体的には、マイコンのD/A変換ポートから発生させた入力信号uを図13に示したRC直列回路に入力させ、当該RC直接回路から出力された出力信号yをマイコンのA/D変換ポートによって計測した。

【0070】

実験1は、出力信号にノイズが含まれていない場合である。参照モデルMの伝達関数M(s)が以下の1次系の場合と、2次系の場合と、2種類の場合に対して実験を行った。

M(s)=2/(s+2) ・・・1次系

M(s)=15/(s2+5S+15) ・・・2次系

【0071】

実験結果を図14及び図15に示す。図14は、伝達関数M(s)が1次系の場合を表したグラフであり、図15は、伝達関数M(s)が2次系の場合を表したグラフである。なお、サンプリング時間は0.05(s)とし、計測時間は、10(s)間とした。図14及び図15に示したグラフ中の出力信号y0は入力信号としてu0=1(V)を図13に示したRC直列回路に印加した際のステップ応答である。出力データysは、出力信号に対して、上述した図5のステップ102の処理によりスプライン関数近似を施したものである。出力データysから上述の図5に示したステップ104の処理及びステップ106の処理に従い、制御器Cを設計し、出力信号yを計測し、図14及び図15の破線で示した目標出力信号y~との比較を行った。目標出力信号y~は、設計した制御器Cを含む制御系のステップ応答(理想とする応答)である。また、出力信号yは、目標値r=1(V)で制御を行った際の出力応答である。

【0072】

図14及び図15に示したグラフから、いずれの場合も出力信号yは、目標出力信号y~とほぼ一致していることがわかる。すなわち、いずれの場合においても、設計した制御器Cによってほぼ最適な制御ができており、理想通りの応答(出力信号y)が得られた。

【0073】

さらに、実験2として、上述の図13に示したRC直列回路にリアルタイムで平均0、標準偏差0.01の白色雑音を加えて実験1と同様に同条件で実験を行った。なお、本実験2は、図16に示した、雑音vを含むRC直列回路に対する制御器Cの設計及び、制御器Cによる制御の実験とみなすことができる。

【0074】

実験結果を図17及び図18に示す。図17は、伝達関数M(s)が1次系の場合を表したグラフであり、図18は、伝達関数M(s)が2次系の場合を表したグラフである。

【0075】

図17及び図18に示したグラフから、わかるように、スプラインフィッティングにより、出力データvsは、雑音vが抑制されている。また、計測データ(出力信号y)は、伝達関数M(s)が1次系及び2次系のいずれの場合においても、雑音vによってばらつくものの、理想応答(目標出力信号y~)に追従できていることがわかる。

【0076】

従って、実施例2においても、本実施の形態の設計装置(設計方法)により設計した制御器Cによって制御対象を適切に制御できる。

【0077】

以上説明したように本実施の形態では、制御対象Pに入力信号u0を1回入力し、制御対象Pから出力された出力信号y0を1回計測することにより、1回分の入出力データ(入力信号u0及び出力信号y0)を計測する。さらに、出力信号y0に対してスプラインフィッティングを行い、データを平滑化して、出力信号y0から雑音vを除去した出力データysを得る。さらに雑音vを除去した出力データysを線形独立なベクトルの組とし、制御対象Pの線形性に基づいて、目標出力信号y~との線形結合係数列θを算出し、当該線形結合係数列θを用いて、入力信号u0から目標入力信号u~を算出する。算出された1組の目標入力信号u~及び目標出力信号y~と参照モデルMに入力される参照信号r~との偏差e~から制御器Cの伝達関数を決定することにより、制御器Cを設計する。

【0078】

これにより、出力信号に含まれているノイズを適切に除去・抑制することができるため、出力信号に含まれるノイズに係わらず例えば、雑音と参照信号の間に相関がある場合であっても、簡単な計算により、制御対象Pの特性が未知である制御対象Pから目標出力信号y~を出力させるように適切な制御を行うことができる制御器Cを設計することができる。

【0079】

なお、本実施の形態では、1回分の実験データを用いているが複数回分の実験データを用いる(複数回計測を行う)ようにしてもよい。なお、本実施の形態のように1回分の実験データを用いる場合であっても、上述のように、適切な制御を行うことができる制御器Cを設計することができる。

【符号の説明】

【0080】

10 設計装置

40 設計プログラム

C 制御器

P 制御対象

M 参照モデル

【特許請求の範囲】

【請求項1】

線形性の伝達特性を有する制御対象のフィードバック制御において、前記制御対象に入力信号を少なくとも1回入力させ、前記制御対象から前記入力信号に応じて出力される出力信号を少なくとも1回計測する計測手段と、

前記計測手段で計測した少なくとも1つの出力信号に含まれるノイズを除去するノイズ除去手段と、

前記制御対象の線形性に基づいて、前記ノイズ除去手段によりノイズが除去された前記出力信号に基づいて、参照モデルの応答として演算される目標出力信号に応じた目標入力信号を演算する演算手段と、

前記演算手段により演算された前記目標入力信号と、前記目標出力信号と前記参照モデルに入力される参照信号との偏差と、に基づいて、前記制御器の伝達関数を決定する決定手段と、

を備えた、設計装置。

【請求項2】

前記ノイズ除去手段は、最小二乗法によるスプラインフィッティングを用いて、前記計測手段で計測した出力信号からノイズを除去する、請求項1に記載の設計装置。

【請求項3】

前記演算手段は、ノイズが除去された前記出力信号を表す線形独立なベクトルの組と、前記目標出力信号と、前記入力信号と、を用いて前記目標入力信号を演算する、請求項1または請求項2に記載の設計装置。

【請求項4】

前記線形独立なベクトルの組は、ノイズが除去された前記出力信号を1時点ずつ後ろへずらしたデータ列を表したベクトルの組である、請求項3に記載の設計装置。

【請求項5】

前記決定手段で決定した伝達関数を前記制御器に設定する設定手段を備えた、請求項1から請求項4のいずれか1項に記載の設計装置。

【請求項6】

前記請求項1から前記請求項5のいずれか1項に記載の設計装置のノイズ除去手段、演算手段、及び決定手段として、コンピュータを機能させるための設計プログラム。

【請求項1】

線形性の伝達特性を有する制御対象のフィードバック制御において、前記制御対象に入力信号を少なくとも1回入力させ、前記制御対象から前記入力信号に応じて出力される出力信号を少なくとも1回計測する計測手段と、

前記計測手段で計測した少なくとも1つの出力信号に含まれるノイズを除去するノイズ除去手段と、

前記制御対象の線形性に基づいて、前記ノイズ除去手段によりノイズが除去された前記出力信号に基づいて、参照モデルの応答として演算される目標出力信号に応じた目標入力信号を演算する演算手段と、

前記演算手段により演算された前記目標入力信号と、前記目標出力信号と前記参照モデルに入力される参照信号との偏差と、に基づいて、前記制御器の伝達関数を決定する決定手段と、

を備えた、設計装置。

【請求項2】

前記ノイズ除去手段は、最小二乗法によるスプラインフィッティングを用いて、前記計測手段で計測した出力信号からノイズを除去する、請求項1に記載の設計装置。

【請求項3】

前記演算手段は、ノイズが除去された前記出力信号を表す線形独立なベクトルの組と、前記目標出力信号と、前記入力信号と、を用いて前記目標入力信号を演算する、請求項1または請求項2に記載の設計装置。

【請求項4】

前記線形独立なベクトルの組は、ノイズが除去された前記出力信号を1時点ずつ後ろへずらしたデータ列を表したベクトルの組である、請求項3に記載の設計装置。

【請求項5】

前記決定手段で決定した伝達関数を前記制御器に設定する設定手段を備えた、請求項1から請求項4のいずれか1項に記載の設計装置。

【請求項6】

前記請求項1から前記請求項5のいずれか1項に記載の設計装置のノイズ除去手段、演算手段、及び決定手段として、コンピュータを機能させるための設計プログラム。

【図1】

【図2】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図3】

【図4】

【図15】

【図17】

【図18】

【図2】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図3】

【図4】

【図15】

【図17】

【図18】

【公開番号】特開2013−109519(P2013−109519A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253113(P2011−253113)

【出願日】平成23年11月18日(2011.11.18)

【出願人】(803000115)学校法人東京理科大学 (545)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月18日(2011.11.18)

【出願人】(803000115)学校法人東京理科大学 (545)

【Fターム(参考)】

[ Back to top ]