試験装置

【課題】プローブ検査においても、理想の電源環境を提供する。

【解決手段】試験装置は、ウエハ上に形成されたDUT1を試験する。電源補償回路20は、制御信号SCNT1、SCNT2に応じて制御されるソーススイッチSW1、シンクスイッチSW2を含み、それぞれがオンした状態において補償パルス電流ISRC、ISINKを生成し、補償パルス電流ISRCをメイン電源とは別経路からDUT1の電源端子P1に注入し、またはメイン電源からDUT1へ流れる電源電流から、補償パルス電流ISINKをDUT1とは別経路に引きこむ。電源補償回路20のうち、ソーススイッチSW1、シンクスイッチSW2を含む一部は、ウエハW上に形成される。ウエハには、ウエハ上に形成される電源補償回路20の一部に信号を印加するためのパッドP5〜P7が設けられる。

【解決手段】試験装置は、ウエハ上に形成されたDUT1を試験する。電源補償回路20は、制御信号SCNT1、SCNT2に応じて制御されるソーススイッチSW1、シンクスイッチSW2を含み、それぞれがオンした状態において補償パルス電流ISRC、ISINKを生成し、補償パルス電流ISRCをメイン電源とは別経路からDUT1の電源端子P1に注入し、またはメイン電源からDUT1へ流れる電源電流から、補償パルス電流ISINKをDUT1とは別経路に引きこむ。電源補償回路20のうち、ソーススイッチSW1、シンクスイッチSW2を含む一部は、ウエハW上に形成される。ウエハには、ウエハ上に形成される電源補償回路20の一部に信号を印加するためのパッドP5〜P7が設けられる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源の安定化技術に関する。

【背景技術】

【0002】

CMOS(Complementary Metal Oxide Semiconductor)テクノロジを用いたCPU(Central Processing Unit)、DSP(Digital Signal Processor)、メモリなどの半導体集積回路(以下、DUTという)を試験する際、DUT内のフリップフロップやラッチは、クロックが供給される動作中は電流が流れ、クロックが停止すると回路が静的な状態となって電流が減少する。したがって、DUTの動作電流(負荷電流)の合計は、試験の内容などに応じて時々刻々と変動する。

【0003】

DUTに電力を供給する電源回路はたとえばレギュレータを用いて構成され、理想的には負荷電流にかかわらず一定の電力を供給可能である。しかしながら実際の電源回路は、無視できない出力インピーダンスを有し、また電源回路とDUTの間にも無視できないインピーダンス成分が存在するため、負荷変動によって電源電圧が変動してしまう。

【0004】

電源電圧の変動は、DUTの試験マージンに深刻な影響を及ぼす。また電源電圧の変動は、試験装置内のその他の回路ブロック、たとえばDUTに供給するパターンを生成するパターン発生器や、パターンの遷移タイミングを制御するためのタイミング発生器の動作に影響を及ぼし、試験精度を悪化させる。

【0005】

特許文献2に記載の技術では、被試験デバイスに電源電圧を供給するメインの電源に加えて、ドライバの出力によってオン、オフが制御されるスイッチを含む補償回路が設けられる。そして、被試験デバイスに供給されるテストパターンに応じて発生しうる電源電圧の変動をキャンセルするように、スイッチ素子に対する補償用の制御パターンをテストパターンに対応付けて定義しておく。実試験時には、テストパターンを被試験デバイスに供給しつつ、補償回路のスイッチを制御パターンに応じてスイッチングすることにより、電源電圧を一定に保つことができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−205813号公報

【特許文献2】国際公開第10/029709A1号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明者らは、特許文献2の試験装置について検討し、以下の課題を認識するに至った。 半導体デバイスの試験には、組み立て工程後のパッケージされた被試験デバイスを対象とする検査(F検)と、組み立て工程前のウエハ状態の被試験デバイスを対象とするプローブ検査(P検)が存在する。そして、電源環境は、P検のときの方がF検のときよりも厳しいため、電源電圧の補償技術は、F検のみならずP検においても重要となる。

【0008】

ここでP検は、ウエハ状態の被試験デバイスに設けられたパッドに、プローブを接触させて行われる。したがって、プローブ自身の抵抗成分、インダクタンス成分、あるいはプローブとチップの間の接触抵抗の影響によって、補償電流による補正が影響を受け、電源電圧を一定に保ち、あるいは所望の電源環境をエミュレートすることが困難となる。

【0009】

本発明は係る状況に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、P検時においても、理想の電源環境、あるいは任意の電源環境をエミュレート可能な試験装置の提供にある。

【課題を解決するための手段】

【0010】

本発明のある態様は、ウエハ上に形成された被試験デバイスを試験する試験装置に関する。被試験デバイスの電源端子に電力を供給するメイン電源と、制御信号に応じて制御されるスイッチ素子を含み、スイッチ素子がオンした状態において補償パルス電流を生成し、補償パルス電流をメイン電源とは別経路から電源端子に注入し、またはメイン電源から被試験デバイスへ流れる電源電流から、補償パルス電流を被試験デバイスとは別経路に引きこむ電源補償回路と、そのひとつがスイッチ素子に割り当てられ、別の少なくともひとつがそれぞれ被試験デバイスの少なくともひとつの入出力端子に割り当てられる、複数のドライバと、それぞれがドライバごとに設けられた複数のインタフェース回路であって、それぞれが入力されたパターン信号を整形して対応するドライバへと出力する、複数のインタフェース回路と、被試験デバイスの入出力端子に割り当てられたドライバが出力すべき試験信号を記述するテストパターンを、そのドライバに対応するインタフェース回路に対して出力するとともに、テストパターンに応じて定められた制御パターンを、スイッチ素子に割り当てられたドライバに対応するインタフェース回路に対して出力するパターン発生器と、を備える。電源補償回路のうち、スイッチ素子を含む少なくとも一部は、ウエハ上に形成される。ウエハには、ウエハ上に形成される電源補償回路の一部に信号を印加するための補償用パッドが設けられる。

【0011】

この態様によると、ウエハ上に電源補償回路の一部を形成することにより、プローブ検査時において、補償パルス電流をウエハ上、つまり被試験デバイスの直近で生成することができる。その結果、プローブのインピーダンスの影響を抑えつつ、電源補償を行うことができる。

また、ウエハに形成される電源補償回路の素子は、被試験デバイスの素子と同様のばらつきを有することになる。したがって、被試験デバイスのばらつきに追従した適切な補償電流を供給することができる。

【0012】

ウエハ上に形成される電源補償回路の少なくとも一部および補償用パッドは、被試験デバイスが形成されるチップの内部に形成されてもよい。

【0013】

補償用パッドは、プローブは接触可能なサイズであって、被試験デバイスがパッケージングされるときに、外部接続用の端子と接続される機能パッドよりも小さなサイズを有してもよい。

チップ内部に形成される電源補償回路が、プローブ検査時のみに必要である場合、補償用パッドを十分小さく形成することにより、チップサイズの増大を抑制できる。

【0014】

補償用パッドは、被試験デバイスがパッケージングされるときに、外部接続用の端子と接続されてもよい。この場合、組み立て工程後の試験においても、チップ内部に形成される電源補償回路を利用して、電源補償を行うことができる。

【0015】

ウエハ上に形成される電源補償回路の少なくとも一部および補償用パッドは、被試験デバイスが形成されるチップの外部のダイシングエリアに形成されてもよい。

ウエハに形成される電源補償回路が、プローブ検査のみに必要である場合、それをダイシングエリアに形成することにより、チップ面積の増大を抑制できる。

【0016】

ウエハ上に形成される電源補償回路の少なくとも一部および補償用パッドは、被試験デバイスが形成されるチップとは別の電源補償用のチップに形成されてもよい。

ウエハ上に形成される電源補償回路の少なくとも一部および補償用パッドは、複数の被試験デバイスにより共有されてもよい。電源補償回路用のチップを設けると、それにより製品の取れ数が減少するところ、複数のチップで電源補償回路用のチップを共有すれば、取れ数の減少を抑制できる。

【0017】

ウエハ上に形成される電源補償回路の一部および補償用パッドに接続される配線のうち、チップの境界を跨ぐ配線は、アルミ配線であってもよい。配線がダイシングラインを横切る場合、ダイシング後に配線の断面が空気や水分にさらされ、長期的信頼性が低下するおそれがある。そこでこのような配線に、第1層のアルミ配線を用いることにより、信頼性の低下を抑えることができる。

【0018】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置などの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0019】

本発明のある態様によれば、P検時おいても、理想の電源環境、あるいは任意の電源環境をエミュレートできる。

【図面の簡単な説明】

【0020】

【図1】実施の形態に係る試験装置の構成を示す回路図である。

【図2】制御パターンを計算する方法の一例を示すフローチャートである。

【図3】動作電流IOP、電源電流IDD、ソース補償電流ICMPおよびソースパルス電流ISRCの一例を示す波形図である。

【図4】図4(a)、(b)は、電源補償回路の構成例を示す回路図である。

【図5】図5(a)〜(c)は、電源補償回路の別の構成例を示す回路図である。

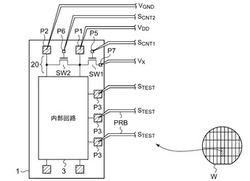

【図6】図4(a)の電源補償回路の一部がウエハ上に形成される第1の例を示す図である。

【図7】図4(a)の電源補償回路の一部がウエハ上に形成される第2の例を示す図である。

【図8】図4(a)の電源補償回路の一部がウエハ上に形成される第3の例を示す図である。

【発明を実施するための形態】

【0021】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0022】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合や、部材Aと部材Bが、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

【0023】

図1は、実施の形態に係る試験装置2の構成を示す回路図である。図1には試験装置2に加えて、試験対象の半導体デバイス(以下、DUTと称す)1が示される。

【0024】

DUT1は、複数のピンを備え、その中の少なくともひとつが電源電圧VDDを受けるための電源端子P1であり、別の少なくともひとつが接地端子P2である。複数の入出力(I/O)端子P3は、外部からのデータを受け、あるいは外部にデータを出力するために設けられており、試験時においては、試験装置2から出力される試験信号(テストパターン)STESTを受け、あるいは試験信号STESTに応じたデータを試験装置2に対して出力する。図1には、試験装置2の構成のうち、DUT1に対して試験信号を与える構成が示されており、DUT1からの信号を評価するための構成は省略されている。

【0025】

試験装置2は、メイン電源10、パターン発生器PG、複数のタイミング発生器TGおよび波形整形器FC、複数のドライバDR、電源補償回路20を備える。

【0026】

試験装置2は複数n個のチャンネルCH1〜CHnを備えており、その中のいくつか(CH1〜CH4)がDUT1の複数のI/O端子P3に割り当てられる。図1では、n=6の場合が示されるが、実際の試験装置2のチャンネル数は、数百〜数千のオーダーである。

【0027】

メイン電源10は、DUT1の電源端子P1に供給すべき電源電圧VDDを生成する。たとえばメイン電源10は、リニアレギュレータやスイッチングレギュレータなどで構成され、電源端子P1に供給される電源電圧VDDを、目標値と一致するようにフィードバック制御する。キャパシタCsは、電源電圧VDDを平滑化するために設けられる。メイン電源10は、DUT1に対する電源電圧の他、試験装置2内部のその他のブロックに対する電源電圧も生成する。メイン電源10からDUT1の電源端子P1への出力電流を、電源電流IDDと称する。

【0028】

メイン電源10は、有限の応答速度を有する電圧・電流源であるため、その負荷電流、つまりDUT1の動作電流IOPの急峻な変化に追従できない場合がある。たとえば動作電流IOPがステップ状に変化するとき、電源電圧VDDはオーバーシュート、あるいはアンダーシュートしたり、その後のリンギングをともなったりする。電源電圧VDDの変動は、DUT1の正確な試験を妨げる。なぜならDUT1にエラーが検出されたとき、それがDUT1の製造不良によるものなのか、電源電圧VDDの変動によるものなのかを区別することができないからである。

【0029】

電源補償回路20は、メイン電源10の応答速度を補うために設けられる。DUT1の設計者は、ある既知の試験信号STEST(テストパターンSPTN)が供給された状態において、DUT1の内部回路の動作率などの時間推移を推定可能であるから、DUT1の動作電流IOPの時間波形を正確に予測することができる。ここでの予測とは、コンピュータシミュレーションを用いた計算や、同じ構成を有するデバイスを対象とした実測などが含まれ、特にその手法は限定されない。

【0030】

一方、メイン電源10の応答速度(利得、フィードバック帯域)が既知であれば、予測される動作電流IOPに応答してメイン電源10が生成する電源電流IDDもまた予測することができる。そうすると、予測される動作電流IOPと電源電流IDDの差分を、電源補償回路20によって補うことにより、電源電圧VDDを安定化することができる。

なお電源電圧VDD’と電源電流IDDの間には微分、もしくは積分関係が成り立つ。具体的には、メイン電源10ならびにメイン電源10から電源端子P1までの経路のインピーダンスが、容量性、誘導性、抵抗性のいずれが支配的であるかによって、電圧と電流の微分、積分の関係が定まる。

【0031】

電源補償回路20は、ソース補償回路20aおよびシンク補償回路20bを備える。ソース補償回路20aは、制御信号SCNT1に応じてオン、オフが切りかえ可能となっている。ソース補償回路20aが制御信号SCNT1に応じてオンすると、補償パルス電流(ソースパルス電流ともいう)ISRCが生成される。電源補償回路20は、ソースパルス電流ISRCをメイン電源10とは別経路から電源端子P1に注入する。

【0032】

同様にシンク補償回路20bは制御信号SCNT2に応じてオン、オフが切りかえ可能となっている。シンク補償回路20bが制御信号SCNT2に応じてオンすると、補償パルス電流ISINK(シンクパルス電流ともいう)が生成される。電源補償回路20は、電源端子P1に流れ込む電源電流IDDから、シンクパルス電流ISINKを、DUT1とは別経路に引きこむ。

【0033】

DUT1の電源端子P1に流れ込む動作電流IOP、メイン電源10が出力する電源電流IDD、および電源補償回路20が出力する補償電流ICMPの間には、電流保存則から、式(1)、(2)が成り立つ。

IOP=IDD+ICMP …(1)

ICMP=ISRC−ISINK …(2)

つまり、補償電流ICMPの正の成分が、ソースパルス電流ISRCとしてソース補償回路20aから供給され、補償電流ICMPの負の成分が、シンクパルス電流ISINKとしてシンク補償回路20bから供給される。

【0034】

ドライバDR1〜DR6のうち、ドライバDR6は、ソース補償回路20aに割り当てられ、ドライバDR5はシンク補償回路20bに割り当てられる。別の少なくともひとつのドライバDR1〜DR4は、それぞれ、DUT1の少なくともひとつのI/O端子P3に割り当てられる。パターン発生器PGおよびドライバDR5、DR6、インタフェース回路45、46は、電源補償回路20を制御する制御回路と把握することができる。

【0035】

波形整形器FCおよびタイミング発生器TGをインタフェース回路4と総称する。複数の41〜46は、チャンネルCH1〜CH6ごと、言い換えればドライバDR1〜DR6ごとに設けられる。i番目(1≦i≦6)のインタフェース回路4iは、入力されたパターン信号SPTNiをドライバDRに適した信号形式に整形し、対応するドライバDRiへと出力する。

【0036】

パターン発生器PGは、テストプログラムにもとづき、インタフェース回路41〜46に対するパターン信号SPTNを生成する。具体的にパターン発生器PGは、DUT1のI/O端子P3に割り当てられたドライバDR1〜DR4に対しては、各ドライバDRiが生成すべき試験信号STESTiを記述するテストパターンSPTNiを、そのドライバDRiに対応するインタフェース回路4iに対して出力する。テストパターンSPTNiは、試験信号STESTiの各サイクル(ユニットインターバル)におけるレベルを示すデータと、信号レベルが遷移するタイミングを記述するデータを含む。

【0037】

またパターン発生器PGは、必要な補償電流ICMPに応じて定められた補償用の制御パターンSPTN_CMPを生成する。制御パターンSPTN_CMPは、ソース補償回路20aに割り当てられたドライバDR6が生成すべき制御信号SCNT1を記述する制御パターンSPTN_CMP1と、シンク補償回路20bに割り当てられたドライバDR5が生成すべき制御信号SCNT2を記述する制御パターンSPTN_CMP2を含む。制御パターンSPTN_CMP1、SPTN_CMP2はそれぞれ、各サイクルにおけるソース補償回路20a、シンク補償回路20bのオン、オフ状態を指定するデータと、オンオフを切りかえるタイミングを記述するデータを含む。

【0038】

パターン発生器PGは、テストパターンSPTN1〜SPTN4にもとづいて、つまりDUT1の動作電流の変動に応じて、それを補償しうる制御パターンSPTN_CMP1、SPTN_CMP2を生成し、対応するインタフェース回路46、45に出力する。

【0039】

上述のように、テストパターンSPTN1〜SPTN4が既知であれば、DUT1の動作電流IOPの時間波形が予測でき、電源電圧VDDを一定に保つために発生すべき補償電流ICMP、すなわちISRC、ISINKの時間波形を計算することができる。

予測される動作電流IOPが電源電流IDDより大きい場合、電源補償回路20はソース補償電流ISRCを発生して不足する電流を補う。ソース補償電流ISRCに必要な電流波形は予測可能であるから、それが適切に得られるようにソース補償回路20aを制御する。たとえばソース補償回路20aを、パルス幅変調によって制御してもよい。あるいはパルス振幅変調、ΔΣ変調、パルス密度変調、パルス周波数変調などを利用してもよい。

【0040】

図2は、制御パターンを計算する方法の一例を示すフローチャートである。DUT1に入力されるテストパターンや回路情報にもとづいて、DUT1の動作電流IOPが推定される(S100)。またメイン電源10に負荷としてDUT1が接続された状態において、DUT1にそのイベントが発生したときに、メイン電源10から出力される電源電流IDDを計算する(S102)。そして、理想電源を実現したい場合には、推定される動作電流IOPと電源電流IDDの差分を、電源補償回路20によって生成すべき補償電流ICMPとする(S104)。

【0041】

そして、生成すべき補償電流ICMPの波形に、ΔΣ変調、PWM(パルス幅変調)、PDM(パルス密度変調)、PAM(パルス振幅変調)、PFM(パルス周波数変調)などを施すことにより、ビットストリームの制御パターンSPTN_CMPを生成する(S106)。たとえば、補償電流ICMPをテストサイクルごとにサンプリングし、サンプリングされた補償電流ICMPをパルス変調してもよい。

【0042】

図3は、動作電流IOP、電源電流IDD、ソース補償電流ICMPおよびソースパルス電流ISRCの一例を示す波形図である。ある試験信号STESTが供給されたDUT1の動作電流IOPがステップ状に増加したとする。これに応答して、メイン電源10から電源電流IDDが供給されるが、それは応答速度の制限から、理想的なステップ波形とはならず、DUT1に供給すべき電流が不足する。その結果、補償電流ISRCを供給しなければ、電源電圧VDDは破線で示すように低下する。

【0043】

電源補償回路20は、動作電流IOPと電源電流IDDの差分に対応するソース補償電流ICMPを生成する。ソース補償電流ICMPは、制御信号SCNT1に応じて生成されるソースパルス電流ISRCで与えられる。ソース補償電流ICMPは、動作電流IOPの変化直後に最大量必要であり、その後、徐々に低下させる必要がある。そこで、たとえばPWM(パルス幅変調)を用いてソース補償回路20aのオン時間(デューティ比)を、時間とともに低下させることにより、必要なソース補償電流ICMPを生成できる。

【0044】

試験装置2のすべてのチャンネルがテストレートに応じて同期動作する場合、制御信号SCNT1の周期は、DUT1に供給されるデータの周期(ユニットインターバル)、もしくはその整数倍、あるいは整数分の1に相当する。たとえばユニットインターバルが4nsのシステムにおいて、制御信号SCNT1の周期が4nsであれば、制御信号SCNT1に含まれる各パルスのオン期間TONが、0〜4nsの間で調節されうる。メイン電源10の応答速度は数百ns〜数μsのオーダーであるため、補償電流ICMPの波形は、制御信号SCNT1に含まれる数百個のパルスによって制御できる。ソース補償電流ISRCの波形から、それを生成するために必要な制御信号SCNT1を導出する方法については後述する。

【0045】

反対に動作電流IOPが電源電流IDDより小さい場合、電源補償回路20はシンク補償電流ICMPが得られるように、シンクパルス電流ISINKを発生して、過剰な電流を引き抜く。

【0046】

電源補償回路20を設けることにより、メイン電源10の応答速度の不足を補い、図3に実線で示すように、電源電圧VDDを一定に保つことができる。また上述したように、電源補償回路20は安定した振幅のパルス電流を生成できるため、高い精度で電源電圧を補償できる。

【0047】

以上が試験装置2の全体の説明である。

【0048】

続いて電源補償回路20の具体的な構成例について説明する。

図4(a)、(b)は、電源補償回路20の構成例を示す回路図である。

図4(a)を参照する。ソース補償回路20aは、電源電圧VDDより高い電圧Vxを生成する電圧源22と、ソーススイッチSW1を含む。ソーススイッチSW1は、電圧源22の出力端子と電源端子P1の間に設けられる。

電圧Vxおよび電源電圧VDDが一定であれば、ソーススイッチSW1がオンの状態において、ソース電流ISRCの振幅は、

ISRC=(Vx−VDD)/RON1

で与えられる。RON1はソーススイッチSW1のオン抵抗である。図4(a)、(b)では、電源補償回路20を小さく構成できるという利点がある。

【0049】

シンク補償回路20bは、電源端子P1と接地端子の間に設けられたシンクスイッチSW2を含む。電源電圧VDDが一定であれば、シンクスイッチSW2がオンした状態において、シンク電流ISINKの振幅は、

ISINK=VDD/RON2

で与えられる。RON2はシンクスイッチSW2のオン抵抗である。

【0050】

図4(b)に移る。ソース補償回路20aは、ソース電流源24aおよびソーススイッチSW1を含む。ソース電流源24aは、ソースパルス電流ISRCの振幅を規定する基準電流を生成する。ソーススイッチSW1はソース電流源24aからの基準電流の経路上に設けられる。

シンク補償回路20bは、シンクスイッチSW2およびシンク電流源24bを含む。シンク電流源24bは、シンクパルス電流ISINKの振幅を規定する基準電流を生成する。シンクスイッチSW2は、シンク電流源24bからの基準電流の経路上に設けられる。

【0051】

ソースパルス電流ISRC、シンクパルス電流ISINKの振幅は、数A程度が必要とされる場合がある。この場合、図4(a)、(b)におけるソーススイッチSW1、シンクスイッチSW2のサイズは大きくなり、そのゲート容量も大きくなる。このゲート容量によってソーススイッチSW1、シンクスイッチSW2のスイッチングの応答速度が低下し、所望の電流を生成できなくなる可能性がある。

また、ソーススイッチSW1、シンクスイッチSW2のオン抵抗RON1、RON2がばらついたり、制御信号SCNT1、SCNT2の振幅が変動すると、各スイッチのオンの程度が変動し、パルス電流ISRC、ISINKの振幅が変動するおそれがある。

【0052】

このよう問題が顕著となる場合、それを解決するために以下の技術を用いてもよい。図5(a)〜(c)は、電源補償回路20の別の構成例を示す回路図である。

図5(a)のソース補償回路20aは、電流D/Aコンバータ26a、第1トランジスタM1a、第2トランジスタM2a、ソーススイッチSW1を備える。

【0053】

電流D/Aコンバータ26aは、デジタル設定信号DSETに応じた基準電流IREFを生成する。第1トランジスタM1aおよび第2トランジスタM2aは、カレントミラー回路を形成し、基準電流IREFを所定係数(ミラー比K)倍したシンクパルス電流ISINKを生成する。

【0054】

具体的に第1トランジスタM1aは、PチャンネルMOSFETであり、基準電流IREFの経路上に設けられる。第2トランジスタM2もPチャンネルMOSFETであり、そのゲートは、第1トランジスタM1aのゲートおよびドレインと共通に接続される。

【0055】

図5(a)において、ソーススイッチSW1は、第1トランジスタM1aのゲートと、第2トランジスタM2aのゲートの間に設けられる。たとえばソーススイッチSW1は、図5(a)のようなトランスファゲートで構成してもよいし、NチャンネルMOSFETのみで構成してもよいし、PチャンネルMOSFETのみで構成してもよい。ソーススイッチSW1のオン、オフ状態は、制御信号SCNT1に応じて切りかえられる。

【0056】

図5(a)において、第1トランジスタM1aのドレインN2は、ソーススイッチSW1の第1トランジスタM1aのゲート側の端子N1と接続される。

【0057】

制御信号SCNT1がハイレベルの期間、ソーススイッチSW1がオンとなる。そうするとソース補償回路20aの出力端子P4から、基準電流IREFに比例したソースパルス電流ISRCが吐き出される。制御信号SCNT1がローレベルの期間、ソーススイッチSW1がオフとなり、カレントミラー回路が動作しなくなるため、ソースパルス電流ISRCがゼロとなる。

【0058】

このように図5(a)のソース補償回路20aによれば、制御信号SCNT1に応じてスイッチングするソースパルス電流ISRCを生成できる。

図5(a)のソース補償回路20aによれば、ソースパルス電流ISRCの振幅の安定性を高めることができる。また、ドライバDRの駆動対象は、大電流が流れるスイッチではなく、カレントミラー回路のゲートに設けられたスイッチであるため、高速なスイッチングが可能となる。

【0059】

また、図5(a)のソース補償回路20aでは、ソーススイッチSW1がオフ状態においても、基準電流IREFが第1トランジスタM1aに流れ続け、第1トランジスタM1aのバイアス状態が維持される。したがって、ソーススイッチSW1のスイッチングに対するソース補償回路20aのスイッチングの応答速度が高いという利点がある。

【0060】

シンク補償回路20bは、ソース補償回路20aのトランジスタの導電性を入れ替え、天地反転することで構成できる。図5(a)には、シンク補償回路20bの構成例が示される。シンク補償回路20bは、電流D/Aコンバータ26b、NチャンネルMOSFETのトランジスタM1b、M2bおよびシンクスイッチSW2を含む。シンク補償回路20bは、ソース補償回路20aと同様の利点を有する。

【0061】

図5(b)、(c)には、シンク補償回路20bの構成のみが示され、ソース補償回路20aは省略されている。

図5(b)では、シンクスイッチSW2の位置が、図5(a)と異なっている。図5(b)では、第1トランジスタM1bのドレインN2は、シンクスイッチSW2の第2トランジスタM2bのゲート側の端子N3と接続される。

この構成によっても、図5(a)の構成と同様に、安定した振幅を有し、高速にスイッチングするシンクパルス電流ISINKを生成できる。

また、図5(b)では、シンクスイッチSW2がオフのとき、基準電流IREFは遮断される。したがって回路の消費電流を低減できるという利点がある。

【0062】

図5(c)において、シンクスイッチSW2は、第1トランジスタM1bおよび第2トランジスタM2bの共通接続されるゲートN4と、接地端子をはじめとする固定電圧端子の間に設けられる。制御信号SCNT2#(#は論理反転を示す)がハイレベルの期間、シンクスイッチSW2がオンすると、第1トランジスタM1、第2トランジスタM2のゲート電圧が接地電圧となるため、カレントミラー回路がオフし、シンクパルス電流ISINKが遮断する。制御信号SCNT2#がローレベルのとき、シンクスイッチSW2がオフすると、カレントミラー回路がオンし、シンクパルス電流ISINKが流れる。

【0063】

図5(c)の構成によれば、図5(a)、(b)と同様に、安定した振幅を有し、高速にスイッチングするシンクパルス電流ISINKを生成できる。図5(b)、(c)の変形が、ソース補償回路20aにも適用可能であることはいうまでもない。

さらに図5(c)の構成を、図5(a)もしくは(b)の構成と組み合わせてもよい。

【0064】

また、DUT1を構成する内部素子に流れる電流、つまり動作電流IOPは、プロセスばらつきによって変動する。つまり、あるテストパターンが供給されたDUT1の動作電流の波形は、プロセスばらつきによって増減する。そこで、DUT1の試験工程に先立ち、キャリブレーション工程を行いって補償パルス電流の振幅を調節することにより、プロセスばらつきによってDUT1の動作電流IOPがばらついたとしても、電源環境を一定に保つことができる。このキャリブレーションは、電流D/Aコンバータ26a、26bに対するデジタル設定値DSETの値を変更することで実現できる。

【0065】

以上が電源補償回路20の構成例である。

【0066】

半導体デバイスの試験には、組み立て工程後のパッケージされた被試験デバイスを対象とする検査(F検)と、組み立て工程前のウエハ状態の被試験デバイスを対象とするプローブ検査(P検)が存在する。そして、電源環境は、P検のときの方がF検のときよりも厳しいため、電源電圧の補償技術は、F検のみならずP検においても重要となる。

【0067】

ここでP検は、ウエハ状態の被試験デバイスに設けられたパッドに、プローブを接触させて行われる。したがって、プローブ自身の抵抗成分、インダクタンス成分、あるいはプローブとチップの間の接触抵抗の影響によって、補償電流による補正が影響を受け、電源電圧を一定に保つことが困難となる。

【0068】

そこで、プローブ検査における電源補償をより正確に行うために、図4(a)、(b)および図5(a)〜(c)に例示される電源補償回路20の少なくとも一部を、ウエハ上に形成する。

【0069】

図6は、図4(a)の電源補償回路20の一部がウエハ上に形成される第1の例を示す図である。図6において、電源補償回路20の一部は、DUT1のチップ内に形成される。DUT1のチップは、本来の機能のために必要な電源端子P1、接地端子P2およびI/O端子P3それぞれに対応するパッド(以下、機能パッドとも称する)と、内部回路3を備える。さらに、DUT1のチップには、ソーススイッチSW1、シンクスイッチSW2と、補償用パッドP5〜P7が形成される。

補償用パッドP5、P6はそれぞれ、ソーススイッチSW1、シンクスイッチSW2それぞれのゲートに接続され、制御信号SCNT1、SCNT2を印加するために設けられる。補償用パッドP7はソーススイッチSW1の一端に接続され、電圧Vxを印加するために設けられる。

【0070】

機能パッドP1〜P3および補償用パッドP5〜P7にはプローブPRBを介して、各種信号が印加される。機能パッドP1〜P3は、パッケージングされた状態において、リードやバンプなどの外部接続用の端子と接続される。一方、補償用パッドP5〜P7は、DUT1の本来の機能には不要なものであり、外部接続用の端子とは接続する必要はない。そこで、DUT1のチップ面積を小さくするために、補償用パッドP5〜P7のサイズを、プローブは接触可能であるが、DUT1がパッケージングされるときに、外部接続用の端子とは接続できない程度に小さくすることが望ましい。

【0071】

この構成によれば、ウエハ上に電源補償回路20の一部を形成することにより、プローブ検査時において、補償パルス電流ISRC、ISINKをウエハ上、つまりDUT1の内部回路3の直近で生成することができる。その結果、プローブのインピーダンスの影響を抑えつつ、電源補償を行うことができる。

【0072】

また、電源補償回路20の一部をウエハに形成することにより、電源補償回路20の素子ばらつきと、DUT1の素子ばらつきは連動する。したがって、DUT1の動作電流IOPが大きくなるようにばらつくときには、ソーススイッチSW1、シンクスイッチSW2に流れる電流ISRC、ISINKも同様に大きくなる方向にばらつくため、正確な電流補償が可能となる。

【0073】

さらにチップ内に形成される電源補償回路20の一部が、プローブ検査時のみに必要である場合、補償用パッドP5〜P7を十分小さく形成することにより、チップサイズの増大を抑えることができる。

【0074】

なお、チップサイズに余裕がある場合には、補償用パッドP5〜P7を、通常の機能パッドと同程度のサイズとしてもよい。さらに補償用パッドP5〜P7を、それぞれに対応する外部接続用の端子と接続してもよい。この場合、パッケージング後の検査(F検)においても、DUT1のチップ内部に形成された電源補償回路20を用いて電源補償を行うことができる。

【0075】

図7は、図4(a)の電源補償回路20の一部がウエハW上に形成される第2の例を示す図である。ウエハからダイシングされる前のチップの周辺には、ダイシングエリア(スクライブ領域)DAが存在する。図7では、電源補償回路20の一部(ソーススイッチSW1、シンクスイッチSW2、補償用パッドP5〜P7)は、DUT1のチップの外部の、ダイシングエリアDAに形成される。

【0076】

電源補償回路20の一部および補償用パッドP5〜P7に接続される配線のうち、チップの境界を跨ぐ配線W1は、アルミ配線とすることが望ましい。配線W1がチップの境界を横切る場合、ダイシング後に配線W1の断面が空気や水分にさらされ、長期的信頼性が低下するおそれがある。そこでこのような配線に、Cu配線ではなく、第1層のアルミ配線を用いることにより、信頼性の低下を抑えることができる。

【0077】

ウエハWに形成される電源補償回路20が、プローブ検査のみに必要である場合、それをダイシングエリアに形成することにより、チップ面積の増大を抑制できる。

【0078】

図8は、図4(a)の電源補償回路20の一部がウエハW上に形成される第3の例を示す図である。図8において、ウエハ上に形成される電源補償回路20の一部(SW1、SW2)および補償用パッドP5〜P7は、DUT1が形成されるチップC1とは別のチップC2に形成される。

【0079】

チップC1の機能パッドP1、P2と、電源補償回路20の間は、ダイシングエリアDAに形成される配線W2を介して接続される。

【0080】

好ましくは、ウエハのあるチップC2に形成される電源補償回路20の少なくとも一部(SW1、SW2)および補償用パッドP5〜P7は、それと隣接する複数のチップによって共有されてもよい。図8では、チップC2の電源補償回路が、チップC1、C3により共有される場合が示されるが、さらに多くのチップ、たとえば縦横に隣接する4個のチップ、あるいは縦横斜めに隣接する8個のチップ、あるいはさらに多くのチップによって、ひとつの電源補償用チップC2を共有してもよい。

【0081】

また図8には、チップC2の電源補償回路がチップC1、C3により共有され、補償電流がチップC1、C2それぞれに供給される場合を示すが、本発明はそれに限定されない。チップC2の電源補償回路からチップC1、C2それぞれに至る経路上に、さらに制御スイッチを追加し、それぞれの制御スイッチを制御することにより、補償電流を供給するチップを選択/切りかえできるようにしてもよい。この場合、制御スイッチの状態を切りかえるための制御信号を与えるための補償用パッドは、チップC2のエリア内に配置してもよい。

【0082】

電源補償回路用のチップC2を設けると、それにより製品の取れ数が減少するところ、複数のチップで電源補償回路用のチップC2を共有すれば、取れ数の減少を抑制できる。プローブ検査においては、複数のチップが同時測定される場合がある。

【0083】

図8のように電源補償用のチップC2を設ける場合、電源補償用のチップC2と、被試験デバイスのチップC1、C3との間の配線は省略し、プローブを介して接続するようにしてもよい。この場合、電源補償がプローブの影響を受けることになるが、電源補償回路20とDUT1が同様にばらつくという利点は享受することができる。

【0084】

実施の形態にもとづき本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【0085】

図6〜図8では、図4(a)の電源補償回路20を例に説明したが、図4(b)、図5(a)〜(c)の電源補償回路20についても、その一部、あるいは全部を、ウエハ上に形成することができる。

たとえば、図4(b)の電源補償回路20の場合、ソーススイッチSW1、シンクスイッチSW2をウエハ上に形成し、ソース電流源24a、シンク電流源24bをウエハの外部に設けてもよい。反対に、ソース電流源24a、シンク電流源24bをウエハ上に形成し、ソーススイッチSW1、シンクスイッチSW2をウエハの外側に形成してもよい。あるいは全部をウエハに形成してもよい。

【0086】

図5(a)〜(c)の電源補償回路20の場合、第1トランジスタM1、第2トランジスタM2およびソーススイッチSW1、シンクスイッチSW2をウエハ上に形成するとよい。これにより、第1トランジスタM1、第2トランジスタM2が、DUT1と同様のばらつきを有するため、電源補償の精度を高めることができる。さらに電流D/Aコンバータ26a、26bをウエハ上に形成してもよい。

【0087】

電源補償回路20が、その他の構成であっても、その一部、あるいは全部をウエハ上に形成することにより、プローブ検査における電源補償を正確に行うことが可能となる。

【0088】

実施の形態では、補償電流ICMPによって、電源電圧の変動がゼロであるような、つまり出力インピーダンスがゼロの理想電源の環境を実現する場合を説明したが、本発明はそれに限定されない。つまり、意図的な電源電圧変動を引き起こすような補償電流ICMPの波形を計算し、その補償電流波形が得られるように制御パターンSPTN_CMPを規定しておいてもよい。この場合、制御パターンSPTN_CMPに応じて任意の電源環境をエミュレートすることが可能となる。

【0089】

実施の形態では、電源補償回路20がソース補償回路20aとシンク補償回路20bを含む場合を説明したが本発明はそれには限定されず、いずれか一方のみの構成としてもよい。

【0090】

ソース補償回路20aのみ設ける場合、ソース補償回路20aに定常的な電流IDCを発生させてもよい。そして、電源電流IDDが動作電流IOPに対して不足するときは、ソース補償回路20aが発生する電流ISRCを、定常的な電流IDCから相対的に増加させてもよい。反対に、電源電流IDDが動作電流IOPに対して過剰なときは、ソース補償回路20aが発生する電流ISRCを、定常的な電流IDCから相対的に減少させてもよい。

シンク補償回路20bのみ設ける場合、シンク補償回路20bに定常的な電流IDCを発生させてもよい。そして、電源電流IDDが動作電流IOPに対して不足するときは、シンク補償回路20bが発生する電流ISINKを、定常的な電流IDCから相対的に減少させてもよい。反対に、電源電流IDDが動作電流IOPに対して過剰なときは、シンク補償回路20bが発生する電流ISINKを、定常的な電流IDCから相対的に増加させてもよい。

これにより、試験装置全体の消費電流は、定常的な電流IDC分増加するが、それと引きかえに、単一のスイッチのみで、補償電流ISRC、ISINKを発生させることができる。

【符号の説明】

【0091】

1…DUT、2…試験装置、PG…パターン発生器、TG…タイミング発生器、FC…波形整形器、4…インタフェース回路、DR…ドライバ、10…メイン電源、12…電源補償回路、20a…ソース補償回路、20b…シンク補償回路、P1…電源端子、P2…接地端子、P3…I/O端子、M1…第1トランジスタ、M2…第2トランジスタ。

【技術分野】

【0001】

本発明は、電源の安定化技術に関する。

【背景技術】

【0002】

CMOS(Complementary Metal Oxide Semiconductor)テクノロジを用いたCPU(Central Processing Unit)、DSP(Digital Signal Processor)、メモリなどの半導体集積回路(以下、DUTという)を試験する際、DUT内のフリップフロップやラッチは、クロックが供給される動作中は電流が流れ、クロックが停止すると回路が静的な状態となって電流が減少する。したがって、DUTの動作電流(負荷電流)の合計は、試験の内容などに応じて時々刻々と変動する。

【0003】

DUTに電力を供給する電源回路はたとえばレギュレータを用いて構成され、理想的には負荷電流にかかわらず一定の電力を供給可能である。しかしながら実際の電源回路は、無視できない出力インピーダンスを有し、また電源回路とDUTの間にも無視できないインピーダンス成分が存在するため、負荷変動によって電源電圧が変動してしまう。

【0004】

電源電圧の変動は、DUTの試験マージンに深刻な影響を及ぼす。また電源電圧の変動は、試験装置内のその他の回路ブロック、たとえばDUTに供給するパターンを生成するパターン発生器や、パターンの遷移タイミングを制御するためのタイミング発生器の動作に影響を及ぼし、試験精度を悪化させる。

【0005】

特許文献2に記載の技術では、被試験デバイスに電源電圧を供給するメインの電源に加えて、ドライバの出力によってオン、オフが制御されるスイッチを含む補償回路が設けられる。そして、被試験デバイスに供給されるテストパターンに応じて発生しうる電源電圧の変動をキャンセルするように、スイッチ素子に対する補償用の制御パターンをテストパターンに対応付けて定義しておく。実試験時には、テストパターンを被試験デバイスに供給しつつ、補償回路のスイッチを制御パターンに応じてスイッチングすることにより、電源電圧を一定に保つことができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−205813号公報

【特許文献2】国際公開第10/029709A1号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明者らは、特許文献2の試験装置について検討し、以下の課題を認識するに至った。 半導体デバイスの試験には、組み立て工程後のパッケージされた被試験デバイスを対象とする検査(F検)と、組み立て工程前のウエハ状態の被試験デバイスを対象とするプローブ検査(P検)が存在する。そして、電源環境は、P検のときの方がF検のときよりも厳しいため、電源電圧の補償技術は、F検のみならずP検においても重要となる。

【0008】

ここでP検は、ウエハ状態の被試験デバイスに設けられたパッドに、プローブを接触させて行われる。したがって、プローブ自身の抵抗成分、インダクタンス成分、あるいはプローブとチップの間の接触抵抗の影響によって、補償電流による補正が影響を受け、電源電圧を一定に保ち、あるいは所望の電源環境をエミュレートすることが困難となる。

【0009】

本発明は係る状況に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、P検時においても、理想の電源環境、あるいは任意の電源環境をエミュレート可能な試験装置の提供にある。

【課題を解決するための手段】

【0010】

本発明のある態様は、ウエハ上に形成された被試験デバイスを試験する試験装置に関する。被試験デバイスの電源端子に電力を供給するメイン電源と、制御信号に応じて制御されるスイッチ素子を含み、スイッチ素子がオンした状態において補償パルス電流を生成し、補償パルス電流をメイン電源とは別経路から電源端子に注入し、またはメイン電源から被試験デバイスへ流れる電源電流から、補償パルス電流を被試験デバイスとは別経路に引きこむ電源補償回路と、そのひとつがスイッチ素子に割り当てられ、別の少なくともひとつがそれぞれ被試験デバイスの少なくともひとつの入出力端子に割り当てられる、複数のドライバと、それぞれがドライバごとに設けられた複数のインタフェース回路であって、それぞれが入力されたパターン信号を整形して対応するドライバへと出力する、複数のインタフェース回路と、被試験デバイスの入出力端子に割り当てられたドライバが出力すべき試験信号を記述するテストパターンを、そのドライバに対応するインタフェース回路に対して出力するとともに、テストパターンに応じて定められた制御パターンを、スイッチ素子に割り当てられたドライバに対応するインタフェース回路に対して出力するパターン発生器と、を備える。電源補償回路のうち、スイッチ素子を含む少なくとも一部は、ウエハ上に形成される。ウエハには、ウエハ上に形成される電源補償回路の一部に信号を印加するための補償用パッドが設けられる。

【0011】

この態様によると、ウエハ上に電源補償回路の一部を形成することにより、プローブ検査時において、補償パルス電流をウエハ上、つまり被試験デバイスの直近で生成することができる。その結果、プローブのインピーダンスの影響を抑えつつ、電源補償を行うことができる。

また、ウエハに形成される電源補償回路の素子は、被試験デバイスの素子と同様のばらつきを有することになる。したがって、被試験デバイスのばらつきに追従した適切な補償電流を供給することができる。

【0012】

ウエハ上に形成される電源補償回路の少なくとも一部および補償用パッドは、被試験デバイスが形成されるチップの内部に形成されてもよい。

【0013】

補償用パッドは、プローブは接触可能なサイズであって、被試験デバイスがパッケージングされるときに、外部接続用の端子と接続される機能パッドよりも小さなサイズを有してもよい。

チップ内部に形成される電源補償回路が、プローブ検査時のみに必要である場合、補償用パッドを十分小さく形成することにより、チップサイズの増大を抑制できる。

【0014】

補償用パッドは、被試験デバイスがパッケージングされるときに、外部接続用の端子と接続されてもよい。この場合、組み立て工程後の試験においても、チップ内部に形成される電源補償回路を利用して、電源補償を行うことができる。

【0015】

ウエハ上に形成される電源補償回路の少なくとも一部および補償用パッドは、被試験デバイスが形成されるチップの外部のダイシングエリアに形成されてもよい。

ウエハに形成される電源補償回路が、プローブ検査のみに必要である場合、それをダイシングエリアに形成することにより、チップ面積の増大を抑制できる。

【0016】

ウエハ上に形成される電源補償回路の少なくとも一部および補償用パッドは、被試験デバイスが形成されるチップとは別の電源補償用のチップに形成されてもよい。

ウエハ上に形成される電源補償回路の少なくとも一部および補償用パッドは、複数の被試験デバイスにより共有されてもよい。電源補償回路用のチップを設けると、それにより製品の取れ数が減少するところ、複数のチップで電源補償回路用のチップを共有すれば、取れ数の減少を抑制できる。

【0017】

ウエハ上に形成される電源補償回路の一部および補償用パッドに接続される配線のうち、チップの境界を跨ぐ配線は、アルミ配線であってもよい。配線がダイシングラインを横切る場合、ダイシング後に配線の断面が空気や水分にさらされ、長期的信頼性が低下するおそれがある。そこでこのような配線に、第1層のアルミ配線を用いることにより、信頼性の低下を抑えることができる。

【0018】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置などの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0019】

本発明のある態様によれば、P検時おいても、理想の電源環境、あるいは任意の電源環境をエミュレートできる。

【図面の簡単な説明】

【0020】

【図1】実施の形態に係る試験装置の構成を示す回路図である。

【図2】制御パターンを計算する方法の一例を示すフローチャートである。

【図3】動作電流IOP、電源電流IDD、ソース補償電流ICMPおよびソースパルス電流ISRCの一例を示す波形図である。

【図4】図4(a)、(b)は、電源補償回路の構成例を示す回路図である。

【図5】図5(a)〜(c)は、電源補償回路の別の構成例を示す回路図である。

【図6】図4(a)の電源補償回路の一部がウエハ上に形成される第1の例を示す図である。

【図7】図4(a)の電源補償回路の一部がウエハ上に形成される第2の例を示す図である。

【図8】図4(a)の電源補償回路の一部がウエハ上に形成される第3の例を示す図である。

【発明を実施するための形態】

【0021】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0022】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合や、部材Aと部材Bが、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

【0023】

図1は、実施の形態に係る試験装置2の構成を示す回路図である。図1には試験装置2に加えて、試験対象の半導体デバイス(以下、DUTと称す)1が示される。

【0024】

DUT1は、複数のピンを備え、その中の少なくともひとつが電源電圧VDDを受けるための電源端子P1であり、別の少なくともひとつが接地端子P2である。複数の入出力(I/O)端子P3は、外部からのデータを受け、あるいは外部にデータを出力するために設けられており、試験時においては、試験装置2から出力される試験信号(テストパターン)STESTを受け、あるいは試験信号STESTに応じたデータを試験装置2に対して出力する。図1には、試験装置2の構成のうち、DUT1に対して試験信号を与える構成が示されており、DUT1からの信号を評価するための構成は省略されている。

【0025】

試験装置2は、メイン電源10、パターン発生器PG、複数のタイミング発生器TGおよび波形整形器FC、複数のドライバDR、電源補償回路20を備える。

【0026】

試験装置2は複数n個のチャンネルCH1〜CHnを備えており、その中のいくつか(CH1〜CH4)がDUT1の複数のI/O端子P3に割り当てられる。図1では、n=6の場合が示されるが、実際の試験装置2のチャンネル数は、数百〜数千のオーダーである。

【0027】

メイン電源10は、DUT1の電源端子P1に供給すべき電源電圧VDDを生成する。たとえばメイン電源10は、リニアレギュレータやスイッチングレギュレータなどで構成され、電源端子P1に供給される電源電圧VDDを、目標値と一致するようにフィードバック制御する。キャパシタCsは、電源電圧VDDを平滑化するために設けられる。メイン電源10は、DUT1に対する電源電圧の他、試験装置2内部のその他のブロックに対する電源電圧も生成する。メイン電源10からDUT1の電源端子P1への出力電流を、電源電流IDDと称する。

【0028】

メイン電源10は、有限の応答速度を有する電圧・電流源であるため、その負荷電流、つまりDUT1の動作電流IOPの急峻な変化に追従できない場合がある。たとえば動作電流IOPがステップ状に変化するとき、電源電圧VDDはオーバーシュート、あるいはアンダーシュートしたり、その後のリンギングをともなったりする。電源電圧VDDの変動は、DUT1の正確な試験を妨げる。なぜならDUT1にエラーが検出されたとき、それがDUT1の製造不良によるものなのか、電源電圧VDDの変動によるものなのかを区別することができないからである。

【0029】

電源補償回路20は、メイン電源10の応答速度を補うために設けられる。DUT1の設計者は、ある既知の試験信号STEST(テストパターンSPTN)が供給された状態において、DUT1の内部回路の動作率などの時間推移を推定可能であるから、DUT1の動作電流IOPの時間波形を正確に予測することができる。ここでの予測とは、コンピュータシミュレーションを用いた計算や、同じ構成を有するデバイスを対象とした実測などが含まれ、特にその手法は限定されない。

【0030】

一方、メイン電源10の応答速度(利得、フィードバック帯域)が既知であれば、予測される動作電流IOPに応答してメイン電源10が生成する電源電流IDDもまた予測することができる。そうすると、予測される動作電流IOPと電源電流IDDの差分を、電源補償回路20によって補うことにより、電源電圧VDDを安定化することができる。

なお電源電圧VDD’と電源電流IDDの間には微分、もしくは積分関係が成り立つ。具体的には、メイン電源10ならびにメイン電源10から電源端子P1までの経路のインピーダンスが、容量性、誘導性、抵抗性のいずれが支配的であるかによって、電圧と電流の微分、積分の関係が定まる。

【0031】

電源補償回路20は、ソース補償回路20aおよびシンク補償回路20bを備える。ソース補償回路20aは、制御信号SCNT1に応じてオン、オフが切りかえ可能となっている。ソース補償回路20aが制御信号SCNT1に応じてオンすると、補償パルス電流(ソースパルス電流ともいう)ISRCが生成される。電源補償回路20は、ソースパルス電流ISRCをメイン電源10とは別経路から電源端子P1に注入する。

【0032】

同様にシンク補償回路20bは制御信号SCNT2に応じてオン、オフが切りかえ可能となっている。シンク補償回路20bが制御信号SCNT2に応じてオンすると、補償パルス電流ISINK(シンクパルス電流ともいう)が生成される。電源補償回路20は、電源端子P1に流れ込む電源電流IDDから、シンクパルス電流ISINKを、DUT1とは別経路に引きこむ。

【0033】

DUT1の電源端子P1に流れ込む動作電流IOP、メイン電源10が出力する電源電流IDD、および電源補償回路20が出力する補償電流ICMPの間には、電流保存則から、式(1)、(2)が成り立つ。

IOP=IDD+ICMP …(1)

ICMP=ISRC−ISINK …(2)

つまり、補償電流ICMPの正の成分が、ソースパルス電流ISRCとしてソース補償回路20aから供給され、補償電流ICMPの負の成分が、シンクパルス電流ISINKとしてシンク補償回路20bから供給される。

【0034】

ドライバDR1〜DR6のうち、ドライバDR6は、ソース補償回路20aに割り当てられ、ドライバDR5はシンク補償回路20bに割り当てられる。別の少なくともひとつのドライバDR1〜DR4は、それぞれ、DUT1の少なくともひとつのI/O端子P3に割り当てられる。パターン発生器PGおよびドライバDR5、DR6、インタフェース回路45、46は、電源補償回路20を制御する制御回路と把握することができる。

【0035】

波形整形器FCおよびタイミング発生器TGをインタフェース回路4と総称する。複数の41〜46は、チャンネルCH1〜CH6ごと、言い換えればドライバDR1〜DR6ごとに設けられる。i番目(1≦i≦6)のインタフェース回路4iは、入力されたパターン信号SPTNiをドライバDRに適した信号形式に整形し、対応するドライバDRiへと出力する。

【0036】

パターン発生器PGは、テストプログラムにもとづき、インタフェース回路41〜46に対するパターン信号SPTNを生成する。具体的にパターン発生器PGは、DUT1のI/O端子P3に割り当てられたドライバDR1〜DR4に対しては、各ドライバDRiが生成すべき試験信号STESTiを記述するテストパターンSPTNiを、そのドライバDRiに対応するインタフェース回路4iに対して出力する。テストパターンSPTNiは、試験信号STESTiの各サイクル(ユニットインターバル)におけるレベルを示すデータと、信号レベルが遷移するタイミングを記述するデータを含む。

【0037】

またパターン発生器PGは、必要な補償電流ICMPに応じて定められた補償用の制御パターンSPTN_CMPを生成する。制御パターンSPTN_CMPは、ソース補償回路20aに割り当てられたドライバDR6が生成すべき制御信号SCNT1を記述する制御パターンSPTN_CMP1と、シンク補償回路20bに割り当てられたドライバDR5が生成すべき制御信号SCNT2を記述する制御パターンSPTN_CMP2を含む。制御パターンSPTN_CMP1、SPTN_CMP2はそれぞれ、各サイクルにおけるソース補償回路20a、シンク補償回路20bのオン、オフ状態を指定するデータと、オンオフを切りかえるタイミングを記述するデータを含む。

【0038】

パターン発生器PGは、テストパターンSPTN1〜SPTN4にもとづいて、つまりDUT1の動作電流の変動に応じて、それを補償しうる制御パターンSPTN_CMP1、SPTN_CMP2を生成し、対応するインタフェース回路46、45に出力する。

【0039】

上述のように、テストパターンSPTN1〜SPTN4が既知であれば、DUT1の動作電流IOPの時間波形が予測でき、電源電圧VDDを一定に保つために発生すべき補償電流ICMP、すなわちISRC、ISINKの時間波形を計算することができる。

予測される動作電流IOPが電源電流IDDより大きい場合、電源補償回路20はソース補償電流ISRCを発生して不足する電流を補う。ソース補償電流ISRCに必要な電流波形は予測可能であるから、それが適切に得られるようにソース補償回路20aを制御する。たとえばソース補償回路20aを、パルス幅変調によって制御してもよい。あるいはパルス振幅変調、ΔΣ変調、パルス密度変調、パルス周波数変調などを利用してもよい。

【0040】

図2は、制御パターンを計算する方法の一例を示すフローチャートである。DUT1に入力されるテストパターンや回路情報にもとづいて、DUT1の動作電流IOPが推定される(S100)。またメイン電源10に負荷としてDUT1が接続された状態において、DUT1にそのイベントが発生したときに、メイン電源10から出力される電源電流IDDを計算する(S102)。そして、理想電源を実現したい場合には、推定される動作電流IOPと電源電流IDDの差分を、電源補償回路20によって生成すべき補償電流ICMPとする(S104)。

【0041】

そして、生成すべき補償電流ICMPの波形に、ΔΣ変調、PWM(パルス幅変調)、PDM(パルス密度変調)、PAM(パルス振幅変調)、PFM(パルス周波数変調)などを施すことにより、ビットストリームの制御パターンSPTN_CMPを生成する(S106)。たとえば、補償電流ICMPをテストサイクルごとにサンプリングし、サンプリングされた補償電流ICMPをパルス変調してもよい。

【0042】

図3は、動作電流IOP、電源電流IDD、ソース補償電流ICMPおよびソースパルス電流ISRCの一例を示す波形図である。ある試験信号STESTが供給されたDUT1の動作電流IOPがステップ状に増加したとする。これに応答して、メイン電源10から電源電流IDDが供給されるが、それは応答速度の制限から、理想的なステップ波形とはならず、DUT1に供給すべき電流が不足する。その結果、補償電流ISRCを供給しなければ、電源電圧VDDは破線で示すように低下する。

【0043】

電源補償回路20は、動作電流IOPと電源電流IDDの差分に対応するソース補償電流ICMPを生成する。ソース補償電流ICMPは、制御信号SCNT1に応じて生成されるソースパルス電流ISRCで与えられる。ソース補償電流ICMPは、動作電流IOPの変化直後に最大量必要であり、その後、徐々に低下させる必要がある。そこで、たとえばPWM(パルス幅変調)を用いてソース補償回路20aのオン時間(デューティ比)を、時間とともに低下させることにより、必要なソース補償電流ICMPを生成できる。

【0044】

試験装置2のすべてのチャンネルがテストレートに応じて同期動作する場合、制御信号SCNT1の周期は、DUT1に供給されるデータの周期(ユニットインターバル)、もしくはその整数倍、あるいは整数分の1に相当する。たとえばユニットインターバルが4nsのシステムにおいて、制御信号SCNT1の周期が4nsであれば、制御信号SCNT1に含まれる各パルスのオン期間TONが、0〜4nsの間で調節されうる。メイン電源10の応答速度は数百ns〜数μsのオーダーであるため、補償電流ICMPの波形は、制御信号SCNT1に含まれる数百個のパルスによって制御できる。ソース補償電流ISRCの波形から、それを生成するために必要な制御信号SCNT1を導出する方法については後述する。

【0045】

反対に動作電流IOPが電源電流IDDより小さい場合、電源補償回路20はシンク補償電流ICMPが得られるように、シンクパルス電流ISINKを発生して、過剰な電流を引き抜く。

【0046】

電源補償回路20を設けることにより、メイン電源10の応答速度の不足を補い、図3に実線で示すように、電源電圧VDDを一定に保つことができる。また上述したように、電源補償回路20は安定した振幅のパルス電流を生成できるため、高い精度で電源電圧を補償できる。

【0047】

以上が試験装置2の全体の説明である。

【0048】

続いて電源補償回路20の具体的な構成例について説明する。

図4(a)、(b)は、電源補償回路20の構成例を示す回路図である。

図4(a)を参照する。ソース補償回路20aは、電源電圧VDDより高い電圧Vxを生成する電圧源22と、ソーススイッチSW1を含む。ソーススイッチSW1は、電圧源22の出力端子と電源端子P1の間に設けられる。

電圧Vxおよび電源電圧VDDが一定であれば、ソーススイッチSW1がオンの状態において、ソース電流ISRCの振幅は、

ISRC=(Vx−VDD)/RON1

で与えられる。RON1はソーススイッチSW1のオン抵抗である。図4(a)、(b)では、電源補償回路20を小さく構成できるという利点がある。

【0049】

シンク補償回路20bは、電源端子P1と接地端子の間に設けられたシンクスイッチSW2を含む。電源電圧VDDが一定であれば、シンクスイッチSW2がオンした状態において、シンク電流ISINKの振幅は、

ISINK=VDD/RON2

で与えられる。RON2はシンクスイッチSW2のオン抵抗である。

【0050】

図4(b)に移る。ソース補償回路20aは、ソース電流源24aおよびソーススイッチSW1を含む。ソース電流源24aは、ソースパルス電流ISRCの振幅を規定する基準電流を生成する。ソーススイッチSW1はソース電流源24aからの基準電流の経路上に設けられる。

シンク補償回路20bは、シンクスイッチSW2およびシンク電流源24bを含む。シンク電流源24bは、シンクパルス電流ISINKの振幅を規定する基準電流を生成する。シンクスイッチSW2は、シンク電流源24bからの基準電流の経路上に設けられる。

【0051】

ソースパルス電流ISRC、シンクパルス電流ISINKの振幅は、数A程度が必要とされる場合がある。この場合、図4(a)、(b)におけるソーススイッチSW1、シンクスイッチSW2のサイズは大きくなり、そのゲート容量も大きくなる。このゲート容量によってソーススイッチSW1、シンクスイッチSW2のスイッチングの応答速度が低下し、所望の電流を生成できなくなる可能性がある。

また、ソーススイッチSW1、シンクスイッチSW2のオン抵抗RON1、RON2がばらついたり、制御信号SCNT1、SCNT2の振幅が変動すると、各スイッチのオンの程度が変動し、パルス電流ISRC、ISINKの振幅が変動するおそれがある。

【0052】

このよう問題が顕著となる場合、それを解決するために以下の技術を用いてもよい。図5(a)〜(c)は、電源補償回路20の別の構成例を示す回路図である。

図5(a)のソース補償回路20aは、電流D/Aコンバータ26a、第1トランジスタM1a、第2トランジスタM2a、ソーススイッチSW1を備える。

【0053】

電流D/Aコンバータ26aは、デジタル設定信号DSETに応じた基準電流IREFを生成する。第1トランジスタM1aおよび第2トランジスタM2aは、カレントミラー回路を形成し、基準電流IREFを所定係数(ミラー比K)倍したシンクパルス電流ISINKを生成する。

【0054】

具体的に第1トランジスタM1aは、PチャンネルMOSFETであり、基準電流IREFの経路上に設けられる。第2トランジスタM2もPチャンネルMOSFETであり、そのゲートは、第1トランジスタM1aのゲートおよびドレインと共通に接続される。

【0055】

図5(a)において、ソーススイッチSW1は、第1トランジスタM1aのゲートと、第2トランジスタM2aのゲートの間に設けられる。たとえばソーススイッチSW1は、図5(a)のようなトランスファゲートで構成してもよいし、NチャンネルMOSFETのみで構成してもよいし、PチャンネルMOSFETのみで構成してもよい。ソーススイッチSW1のオン、オフ状態は、制御信号SCNT1に応じて切りかえられる。

【0056】

図5(a)において、第1トランジスタM1aのドレインN2は、ソーススイッチSW1の第1トランジスタM1aのゲート側の端子N1と接続される。

【0057】

制御信号SCNT1がハイレベルの期間、ソーススイッチSW1がオンとなる。そうするとソース補償回路20aの出力端子P4から、基準電流IREFに比例したソースパルス電流ISRCが吐き出される。制御信号SCNT1がローレベルの期間、ソーススイッチSW1がオフとなり、カレントミラー回路が動作しなくなるため、ソースパルス電流ISRCがゼロとなる。

【0058】

このように図5(a)のソース補償回路20aによれば、制御信号SCNT1に応じてスイッチングするソースパルス電流ISRCを生成できる。

図5(a)のソース補償回路20aによれば、ソースパルス電流ISRCの振幅の安定性を高めることができる。また、ドライバDRの駆動対象は、大電流が流れるスイッチではなく、カレントミラー回路のゲートに設けられたスイッチであるため、高速なスイッチングが可能となる。

【0059】

また、図5(a)のソース補償回路20aでは、ソーススイッチSW1がオフ状態においても、基準電流IREFが第1トランジスタM1aに流れ続け、第1トランジスタM1aのバイアス状態が維持される。したがって、ソーススイッチSW1のスイッチングに対するソース補償回路20aのスイッチングの応答速度が高いという利点がある。

【0060】

シンク補償回路20bは、ソース補償回路20aのトランジスタの導電性を入れ替え、天地反転することで構成できる。図5(a)には、シンク補償回路20bの構成例が示される。シンク補償回路20bは、電流D/Aコンバータ26b、NチャンネルMOSFETのトランジスタM1b、M2bおよびシンクスイッチSW2を含む。シンク補償回路20bは、ソース補償回路20aと同様の利点を有する。

【0061】

図5(b)、(c)には、シンク補償回路20bの構成のみが示され、ソース補償回路20aは省略されている。

図5(b)では、シンクスイッチSW2の位置が、図5(a)と異なっている。図5(b)では、第1トランジスタM1bのドレインN2は、シンクスイッチSW2の第2トランジスタM2bのゲート側の端子N3と接続される。

この構成によっても、図5(a)の構成と同様に、安定した振幅を有し、高速にスイッチングするシンクパルス電流ISINKを生成できる。

また、図5(b)では、シンクスイッチSW2がオフのとき、基準電流IREFは遮断される。したがって回路の消費電流を低減できるという利点がある。

【0062】

図5(c)において、シンクスイッチSW2は、第1トランジスタM1bおよび第2トランジスタM2bの共通接続されるゲートN4と、接地端子をはじめとする固定電圧端子の間に設けられる。制御信号SCNT2#(#は論理反転を示す)がハイレベルの期間、シンクスイッチSW2がオンすると、第1トランジスタM1、第2トランジスタM2のゲート電圧が接地電圧となるため、カレントミラー回路がオフし、シンクパルス電流ISINKが遮断する。制御信号SCNT2#がローレベルのとき、シンクスイッチSW2がオフすると、カレントミラー回路がオンし、シンクパルス電流ISINKが流れる。

【0063】

図5(c)の構成によれば、図5(a)、(b)と同様に、安定した振幅を有し、高速にスイッチングするシンクパルス電流ISINKを生成できる。図5(b)、(c)の変形が、ソース補償回路20aにも適用可能であることはいうまでもない。

さらに図5(c)の構成を、図5(a)もしくは(b)の構成と組み合わせてもよい。

【0064】

また、DUT1を構成する内部素子に流れる電流、つまり動作電流IOPは、プロセスばらつきによって変動する。つまり、あるテストパターンが供給されたDUT1の動作電流の波形は、プロセスばらつきによって増減する。そこで、DUT1の試験工程に先立ち、キャリブレーション工程を行いって補償パルス電流の振幅を調節することにより、プロセスばらつきによってDUT1の動作電流IOPがばらついたとしても、電源環境を一定に保つことができる。このキャリブレーションは、電流D/Aコンバータ26a、26bに対するデジタル設定値DSETの値を変更することで実現できる。

【0065】

以上が電源補償回路20の構成例である。

【0066】

半導体デバイスの試験には、組み立て工程後のパッケージされた被試験デバイスを対象とする検査(F検)と、組み立て工程前のウエハ状態の被試験デバイスを対象とするプローブ検査(P検)が存在する。そして、電源環境は、P検のときの方がF検のときよりも厳しいため、電源電圧の補償技術は、F検のみならずP検においても重要となる。

【0067】

ここでP検は、ウエハ状態の被試験デバイスに設けられたパッドに、プローブを接触させて行われる。したがって、プローブ自身の抵抗成分、インダクタンス成分、あるいはプローブとチップの間の接触抵抗の影響によって、補償電流による補正が影響を受け、電源電圧を一定に保つことが困難となる。

【0068】

そこで、プローブ検査における電源補償をより正確に行うために、図4(a)、(b)および図5(a)〜(c)に例示される電源補償回路20の少なくとも一部を、ウエハ上に形成する。

【0069】

図6は、図4(a)の電源補償回路20の一部がウエハ上に形成される第1の例を示す図である。図6において、電源補償回路20の一部は、DUT1のチップ内に形成される。DUT1のチップは、本来の機能のために必要な電源端子P1、接地端子P2およびI/O端子P3それぞれに対応するパッド(以下、機能パッドとも称する)と、内部回路3を備える。さらに、DUT1のチップには、ソーススイッチSW1、シンクスイッチSW2と、補償用パッドP5〜P7が形成される。

補償用パッドP5、P6はそれぞれ、ソーススイッチSW1、シンクスイッチSW2それぞれのゲートに接続され、制御信号SCNT1、SCNT2を印加するために設けられる。補償用パッドP7はソーススイッチSW1の一端に接続され、電圧Vxを印加するために設けられる。

【0070】

機能パッドP1〜P3および補償用パッドP5〜P7にはプローブPRBを介して、各種信号が印加される。機能パッドP1〜P3は、パッケージングされた状態において、リードやバンプなどの外部接続用の端子と接続される。一方、補償用パッドP5〜P7は、DUT1の本来の機能には不要なものであり、外部接続用の端子とは接続する必要はない。そこで、DUT1のチップ面積を小さくするために、補償用パッドP5〜P7のサイズを、プローブは接触可能であるが、DUT1がパッケージングされるときに、外部接続用の端子とは接続できない程度に小さくすることが望ましい。

【0071】

この構成によれば、ウエハ上に電源補償回路20の一部を形成することにより、プローブ検査時において、補償パルス電流ISRC、ISINKをウエハ上、つまりDUT1の内部回路3の直近で生成することができる。その結果、プローブのインピーダンスの影響を抑えつつ、電源補償を行うことができる。

【0072】

また、電源補償回路20の一部をウエハに形成することにより、電源補償回路20の素子ばらつきと、DUT1の素子ばらつきは連動する。したがって、DUT1の動作電流IOPが大きくなるようにばらつくときには、ソーススイッチSW1、シンクスイッチSW2に流れる電流ISRC、ISINKも同様に大きくなる方向にばらつくため、正確な電流補償が可能となる。

【0073】

さらにチップ内に形成される電源補償回路20の一部が、プローブ検査時のみに必要である場合、補償用パッドP5〜P7を十分小さく形成することにより、チップサイズの増大を抑えることができる。

【0074】

なお、チップサイズに余裕がある場合には、補償用パッドP5〜P7を、通常の機能パッドと同程度のサイズとしてもよい。さらに補償用パッドP5〜P7を、それぞれに対応する外部接続用の端子と接続してもよい。この場合、パッケージング後の検査(F検)においても、DUT1のチップ内部に形成された電源補償回路20を用いて電源補償を行うことができる。

【0075】

図7は、図4(a)の電源補償回路20の一部がウエハW上に形成される第2の例を示す図である。ウエハからダイシングされる前のチップの周辺には、ダイシングエリア(スクライブ領域)DAが存在する。図7では、電源補償回路20の一部(ソーススイッチSW1、シンクスイッチSW2、補償用パッドP5〜P7)は、DUT1のチップの外部の、ダイシングエリアDAに形成される。

【0076】

電源補償回路20の一部および補償用パッドP5〜P7に接続される配線のうち、チップの境界を跨ぐ配線W1は、アルミ配線とすることが望ましい。配線W1がチップの境界を横切る場合、ダイシング後に配線W1の断面が空気や水分にさらされ、長期的信頼性が低下するおそれがある。そこでこのような配線に、Cu配線ではなく、第1層のアルミ配線を用いることにより、信頼性の低下を抑えることができる。

【0077】

ウエハWに形成される電源補償回路20が、プローブ検査のみに必要である場合、それをダイシングエリアに形成することにより、チップ面積の増大を抑制できる。

【0078】

図8は、図4(a)の電源補償回路20の一部がウエハW上に形成される第3の例を示す図である。図8において、ウエハ上に形成される電源補償回路20の一部(SW1、SW2)および補償用パッドP5〜P7は、DUT1が形成されるチップC1とは別のチップC2に形成される。

【0079】

チップC1の機能パッドP1、P2と、電源補償回路20の間は、ダイシングエリアDAに形成される配線W2を介して接続される。

【0080】

好ましくは、ウエハのあるチップC2に形成される電源補償回路20の少なくとも一部(SW1、SW2)および補償用パッドP5〜P7は、それと隣接する複数のチップによって共有されてもよい。図8では、チップC2の電源補償回路が、チップC1、C3により共有される場合が示されるが、さらに多くのチップ、たとえば縦横に隣接する4個のチップ、あるいは縦横斜めに隣接する8個のチップ、あるいはさらに多くのチップによって、ひとつの電源補償用チップC2を共有してもよい。

【0081】

また図8には、チップC2の電源補償回路がチップC1、C3により共有され、補償電流がチップC1、C2それぞれに供給される場合を示すが、本発明はそれに限定されない。チップC2の電源補償回路からチップC1、C2それぞれに至る経路上に、さらに制御スイッチを追加し、それぞれの制御スイッチを制御することにより、補償電流を供給するチップを選択/切りかえできるようにしてもよい。この場合、制御スイッチの状態を切りかえるための制御信号を与えるための補償用パッドは、チップC2のエリア内に配置してもよい。

【0082】

電源補償回路用のチップC2を設けると、それにより製品の取れ数が減少するところ、複数のチップで電源補償回路用のチップC2を共有すれば、取れ数の減少を抑制できる。プローブ検査においては、複数のチップが同時測定される場合がある。

【0083】

図8のように電源補償用のチップC2を設ける場合、電源補償用のチップC2と、被試験デバイスのチップC1、C3との間の配線は省略し、プローブを介して接続するようにしてもよい。この場合、電源補償がプローブの影響を受けることになるが、電源補償回路20とDUT1が同様にばらつくという利点は享受することができる。

【0084】

実施の形態にもとづき本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【0085】

図6〜図8では、図4(a)の電源補償回路20を例に説明したが、図4(b)、図5(a)〜(c)の電源補償回路20についても、その一部、あるいは全部を、ウエハ上に形成することができる。

たとえば、図4(b)の電源補償回路20の場合、ソーススイッチSW1、シンクスイッチSW2をウエハ上に形成し、ソース電流源24a、シンク電流源24bをウエハの外部に設けてもよい。反対に、ソース電流源24a、シンク電流源24bをウエハ上に形成し、ソーススイッチSW1、シンクスイッチSW2をウエハの外側に形成してもよい。あるいは全部をウエハに形成してもよい。

【0086】

図5(a)〜(c)の電源補償回路20の場合、第1トランジスタM1、第2トランジスタM2およびソーススイッチSW1、シンクスイッチSW2をウエハ上に形成するとよい。これにより、第1トランジスタM1、第2トランジスタM2が、DUT1と同様のばらつきを有するため、電源補償の精度を高めることができる。さらに電流D/Aコンバータ26a、26bをウエハ上に形成してもよい。

【0087】

電源補償回路20が、その他の構成であっても、その一部、あるいは全部をウエハ上に形成することにより、プローブ検査における電源補償を正確に行うことが可能となる。

【0088】

実施の形態では、補償電流ICMPによって、電源電圧の変動がゼロであるような、つまり出力インピーダンスがゼロの理想電源の環境を実現する場合を説明したが、本発明はそれに限定されない。つまり、意図的な電源電圧変動を引き起こすような補償電流ICMPの波形を計算し、その補償電流波形が得られるように制御パターンSPTN_CMPを規定しておいてもよい。この場合、制御パターンSPTN_CMPに応じて任意の電源環境をエミュレートすることが可能となる。

【0089】

実施の形態では、電源補償回路20がソース補償回路20aとシンク補償回路20bを含む場合を説明したが本発明はそれには限定されず、いずれか一方のみの構成としてもよい。

【0090】

ソース補償回路20aのみ設ける場合、ソース補償回路20aに定常的な電流IDCを発生させてもよい。そして、電源電流IDDが動作電流IOPに対して不足するときは、ソース補償回路20aが発生する電流ISRCを、定常的な電流IDCから相対的に増加させてもよい。反対に、電源電流IDDが動作電流IOPに対して過剰なときは、ソース補償回路20aが発生する電流ISRCを、定常的な電流IDCから相対的に減少させてもよい。

シンク補償回路20bのみ設ける場合、シンク補償回路20bに定常的な電流IDCを発生させてもよい。そして、電源電流IDDが動作電流IOPに対して不足するときは、シンク補償回路20bが発生する電流ISINKを、定常的な電流IDCから相対的に減少させてもよい。反対に、電源電流IDDが動作電流IOPに対して過剰なときは、シンク補償回路20bが発生する電流ISINKを、定常的な電流IDCから相対的に増加させてもよい。

これにより、試験装置全体の消費電流は、定常的な電流IDC分増加するが、それと引きかえに、単一のスイッチのみで、補償電流ISRC、ISINKを発生させることができる。

【符号の説明】

【0091】

1…DUT、2…試験装置、PG…パターン発生器、TG…タイミング発生器、FC…波形整形器、4…インタフェース回路、DR…ドライバ、10…メイン電源、12…電源補償回路、20a…ソース補償回路、20b…シンク補償回路、P1…電源端子、P2…接地端子、P3…I/O端子、M1…第1トランジスタ、M2…第2トランジスタ。

【特許請求の範囲】

【請求項1】

ウエハ上に形成された被試験デバイスを試験する試験装置であって、

前記被試験デバイスの電源端子に電力を供給するメイン電源と、

制御信号に応じて制御されるスイッチ素子を含み、前記スイッチ素子がオンした状態において補償パルス電流を生成し、前記補償パルス電流を前記メイン電源とは別経路から前記電源端子に注入し、または前記メイン電源から前記被試験デバイスへ流れる電源電流から、前記補償パルス電流を前記被試験デバイスとは別経路に引きこむ電源補償回路と、

そのひとつが前記スイッチ素子に割り当てられ、別の少なくともひとつがそれぞれ前記被試験デバイスの少なくともひとつの入出力端子に割り当てられる、複数のドライバと、

それぞれが前記ドライバごとに設けられた複数のインタフェース回路であって、それぞれが入力されたパターン信号を整形して対応するドライバへと出力する、複数のインタフェース回路と、

前記被試験デバイスの入出力端子に割り当てられた前記ドライバが出力すべき試験信号を記述するテストパターンを、そのドライバに対応する前記インタフェース回路に対して出力するとともに、前記テストパターンに応じて定められた制御パターンを、前記スイッチ素子に割り当てられたドライバに対応する前記インタフェース回路に対して出力するパターン発生器と、

を備え、

前記電源補償回路のうち、前記スイッチ素子を含む少なくとも一部は、前記ウエハ上に形成され、

前記ウエハには、前記ウエハ上に形成される前記電源補償回路の一部に信号を印加するための補償用パッドが設けられることを特徴とする試験装置。

【請求項2】

前記ウエハ上に形成される前記電源補償回路の少なくとも一部および前記補償用パッドは、前記被試験デバイスが形成されるチップの内部に形成されることを特徴とする請求項1に記載の試験装置。

【請求項3】

前記補償用パッドは、プローブが接触可能なサイズであって、前記被試験デバイスがパッケージングされるときに、外部接続用の端子と接続される機能パッドよりも小さなサイズを有することを特徴とする請求項2に記載の試験装置。

【請求項4】

前記補償用パッドは、前記被試験デバイスがパッケージングされるときに、外部接続用の端子と接続されることを特徴とする請求項2に記載の試験装置。

【請求項5】

前記ウエハ上に形成される前記電源補償回路の少なくとも一部および前記補償用パッドは、前記被試験デバイスが形成されるチップの外部のダイシングエリアに形成されることを特徴とする請求項1に記載の試験装置。

【請求項6】

前記ウエハ上に形成される前記電源補償回路の少なくとも一部および前記補償用パッドは、前記被試験デバイスが形成されるチップとは別の電源補償用のチップに形成されることを特徴とする請求項1に記載の試験装置。

【請求項7】

前記ウエハ上に形成される前記電源補償回路の少なくとも一部および前記補償用パッドは、複数の被試験デバイスにより共有されることを特徴とする請求項6に記載の試験装置。

【請求項8】

前記ウエハ上に形成される前記電源補償回路の一部および前記補償用パッドに接続される配線のうち、チップの境界を跨ぐ配線は、アルミ配線であることを特徴とする請求項5から7のいずれかに記載の試験装置。

【請求項1】

ウエハ上に形成された被試験デバイスを試験する試験装置であって、

前記被試験デバイスの電源端子に電力を供給するメイン電源と、

制御信号に応じて制御されるスイッチ素子を含み、前記スイッチ素子がオンした状態において補償パルス電流を生成し、前記補償パルス電流を前記メイン電源とは別経路から前記電源端子に注入し、または前記メイン電源から前記被試験デバイスへ流れる電源電流から、前記補償パルス電流を前記被試験デバイスとは別経路に引きこむ電源補償回路と、

そのひとつが前記スイッチ素子に割り当てられ、別の少なくともひとつがそれぞれ前記被試験デバイスの少なくともひとつの入出力端子に割り当てられる、複数のドライバと、

それぞれが前記ドライバごとに設けられた複数のインタフェース回路であって、それぞれが入力されたパターン信号を整形して対応するドライバへと出力する、複数のインタフェース回路と、

前記被試験デバイスの入出力端子に割り当てられた前記ドライバが出力すべき試験信号を記述するテストパターンを、そのドライバに対応する前記インタフェース回路に対して出力するとともに、前記テストパターンに応じて定められた制御パターンを、前記スイッチ素子に割り当てられたドライバに対応する前記インタフェース回路に対して出力するパターン発生器と、

を備え、

前記電源補償回路のうち、前記スイッチ素子を含む少なくとも一部は、前記ウエハ上に形成され、

前記ウエハには、前記ウエハ上に形成される前記電源補償回路の一部に信号を印加するための補償用パッドが設けられることを特徴とする試験装置。

【請求項2】

前記ウエハ上に形成される前記電源補償回路の少なくとも一部および前記補償用パッドは、前記被試験デバイスが形成されるチップの内部に形成されることを特徴とする請求項1に記載の試験装置。

【請求項3】

前記補償用パッドは、プローブが接触可能なサイズであって、前記被試験デバイスがパッケージングされるときに、外部接続用の端子と接続される機能パッドよりも小さなサイズを有することを特徴とする請求項2に記載の試験装置。

【請求項4】

前記補償用パッドは、前記被試験デバイスがパッケージングされるときに、外部接続用の端子と接続されることを特徴とする請求項2に記載の試験装置。

【請求項5】

前記ウエハ上に形成される前記電源補償回路の少なくとも一部および前記補償用パッドは、前記被試験デバイスが形成されるチップの外部のダイシングエリアに形成されることを特徴とする請求項1に記載の試験装置。

【請求項6】

前記ウエハ上に形成される前記電源補償回路の少なくとも一部および前記補償用パッドは、前記被試験デバイスが形成されるチップとは別の電源補償用のチップに形成されることを特徴とする請求項1に記載の試験装置。

【請求項7】

前記ウエハ上に形成される前記電源補償回路の少なくとも一部および前記補償用パッドは、複数の被試験デバイスにより共有されることを特徴とする請求項6に記載の試験装置。

【請求項8】

前記ウエハ上に形成される前記電源補償回路の一部および前記補償用パッドに接続される配線のうち、チップの境界を跨ぐ配線は、アルミ配線であることを特徴とする請求項5から7のいずれかに記載の試験装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−98220(P2012−98220A)

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願番号】特願2010−247788(P2010−247788)

【出願日】平成22年11月4日(2010.11.4)

【出願人】(390005175)株式会社アドバンテスト (1,005)

【Fターム(参考)】

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願日】平成22年11月4日(2010.11.4)

【出願人】(390005175)株式会社アドバンテスト (1,005)

【Fターム(参考)】

[ Back to top ]