認証装置、認証方法および認証プログラム

【課題】フォルトインジェクション攻撃による改ざんが行われた場合に、改ざんが行われたことを検知する。

【解決手段】複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行う認証装置が、認証条件または認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列を記憶し、認証処理の際には、記憶したビット列から、認証条件または認証値に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれるビット列を読み出し、同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に認証処理を行う。

【解決手段】複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行う認証装置が、認証条件または認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列を記憶し、認証処理の際には、記憶したビット列から、認証条件または認証値に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれるビット列を読み出し、同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に認証処理を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、定められた認証条件と、入力される認証値とを比較して認証処理を行う技術に関する。

【背景技術】

【0002】

高い耐タンパ性が要求されるIC(integrated circuit)デバイスにおいて、そのICデバイスに記憶されている情報が読み出される際に、定められた認証処理を行って認証成功と判定した場合にのみ情報を出力するような制御が行われている。このような制御を行うICデバイスは、例えば、複数のビット列によって定められた認証条件を予め記憶し、このような認証条件と、入力される複数のビット列である認証値とを比較し、認証値が認証条件を満たす場合に認証成功と判定する。

特許文献1には、認証処理を行う際に用いる暗号鍵やそれに付帯する情報をアクセス制限のある特殊なエリアに記憶させ、安全な認証処理を行おうとする技術が記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−20676号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、近年、フォルトインジェクション等の攻撃手法が高度化しており、このような攻撃へのさらなる対策が必要である。例えば、ICデバイスの半導体に対して物理的に電圧や光線等を当てて、半導体内部のビットデータを書き換えて改ざんしてしまうという攻撃手法が現実的なものとなってきている。例えば、このような手法によりICデバイス内の認証条件や認証値が改ざんされてしまえば、本来意図しない手順により認証が成功してしまうことがあると考えられる。ただし、このような攻撃を行う場合、半導体内部のデータを1ビット単位で書き換えることは非常に困難であり、攻撃によるデータ書き換えの対象であるビットの前後1ビットずつ(計3ビット)が改ざんされる。ここで、このようなフォルトインジェクション攻撃による改ざんが行われた場合に、改ざんが行われたことを検知し、改ざんが行われた場合には認証を成功しないようにすることが望ましい。

【0005】

本発明は、このような状況に鑑みてなされたもので、フォルトインジェクション攻撃による改ざんが行われた場合に、改ざんが行われたか否かを判定する認証装置、認証方法および認証プログラムを提供する。

【課題を解決するための手段】

【0006】

上述した課題を解決するために、本発明は、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行う認証装置であって、認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する認証条件改ざん判定部と、付加ビット付認証値記憶部に記憶されている付加ビット付認証値から、認証値に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する認証値改ざん判定部と、認証条件改ざん判定部が、認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、認証値改ざん判定部が、認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、認証処理を行う認証処理部と、を備えることを特徴とする。

【0007】

また、本発明は、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件に含まれる付加ビット列は、偶数個のビットであり、付加ビット付認証値記憶部に記憶されている付加ビット付認証値に含まれる付加ビット列は、偶数個のビットであることを特徴とする。

【0008】

また、本発明は、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件に含まれる付加ビット列は、奇数個のビットであり、付加ビット列は、認証条件に含まれるビットの前後で反転値であり、付加ビット付認証値記憶部に記憶されている付加ビット付認証値に含まれる付加ビット列は、奇数個のビットであり、付加ビット列は、認証値に含まれるビットの前後で反転値であることを特徴とする。

【0009】

また、本発明は、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件に含まれる付加ビット列は、2個のビットであり、付加ビット付認証値記憶部に記憶されている付加ビット付認証値に含まれる付加ビット列は、2個のビットであることを特徴とする。

【0010】

また、本発明は、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行い、認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、を備えた認証装置の認証方法であって、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、付加ビット付認証値記憶部に記憶されている付加ビット付認証値から、認証値に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、認証処理を行うステップと、を備えることを特徴とする。

【0011】

また、本発明は、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行い、認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、を備えた認証装置のコンピュータに、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、付加ビット付認証値記憶部に記憶されている付加ビット付認証値から、認証値に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、認証処理を行うステップと、を実行させる認証プログラムである。

【発明の効果】

【0012】

以上説明したように、本発明によれば、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行う認証装置が、認証条件または認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列を記憶し、認証処理の際には、記憶したビット列から、認証条件または認証値に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれるビット列を読み出し、同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に認証処理を行うようにしたので、フォルトインジェクション攻撃により少なくとも3ビットの改ざんが行われた場合に改ざんが行われたことを検知することができる。

【図面の簡単な説明】

【0013】

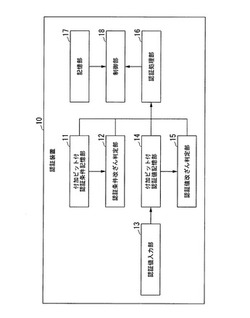

【図1】本発明の一実施形態による認証装置の構成例を示すブロック図である。

【図2】本発明の一実施形態による認証条件のデータ例を示す図である。

【図3】本発明の一実施形態による付加ビット付認証条件のデータ例を示す図である。

【図4】本発明の一実施形態による認証装置の動作例を示すフローチャートである。

【図5】本発明の一実施形態による付加ビット付認証条件のデータ例を示す図である。

【発明を実施するための形態】

【0014】

以下、本発明の一実施形態について、図面を参照して説明する。

<第1の実施形態>

図1は、本実施形態による認証装置10の構成を示すブロック図である。認証装置10は、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行うコンピュータ装置である。具体的には、認証装置10には、USB(Universal Serial Bus)メモリやTPM(Trusted Platform Module)、ICカードなどの、ICチップの機能によって認証処理を行う各種ICデバイスが適用できる。認証装置10には、例えばISO/IEC7816−4に示されるような階層構造によりデータが記憶されており、階層の区画毎にアクセス制限が設定される。ここでは、このような区画にアクセスするためのコマンドごとに、認証条件のいずれのビットのフラグを用いるか、また各領域のフラグをどのように演算するかを示す条件が定められている。

【0015】

図2を参照して、このような認証処理の概要を説明する。例えば、認証装置10は、この図に示すような情報を認証条件として予め記憶している。認証条件は、AカテゴリとBカテゴリとに分類されたA0〜A3とB0〜B3との計8ビットの情報である。A0、B0はそれぞれANDフラグであり、A1〜A3、B1〜B3はそれぞれアクセス制御フラグである。ANDフラグは、それぞれのカテゴリにおけるアクセス制御フラグの結合関係を示すフラグであり、1ならANDを示し、0ならORを示す。AカテゴリとBカテゴリとはANDにより結合される。本実施形態ではアクセス制御フラグは3ビットとして説明するが、制御内容に応じて任意の数のビットをアクセス制御フラグとすることができる。

【0016】

認証装置10は、A1〜A3、B1〜B3をそれぞれ権限に対応する値とし、PIN認証や指紋認証、署名認証などに応じて、認証されたユーザの権限に対応するビットのフラグを立てる(0を1にする)。このようなフラグによって、特定の情報にアクセスすることが許可されているか否かを判定するアクセス制限を行う。例えば、このようなビット列によって、「(A1 OR A2) AND B2」のような権限によるアクセス制限を行うことができる。すなわち、多様な権限の組み合わせに応じて、特定の情報にアクセスすることを許可するように制御することができる。このような処理を行うため、認証装置10は、付加ビット付認証条件記憶部11と、認証条件改ざん判定部12と、認証値入力部13と、付加ビット付認証値記憶部14と、認証値改ざん判定部15と、認証処理部16と、記憶部17と、制御部18とを備えている。

【0017】

付加ビット付認証条件記憶部11には、定められた認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される。図3は、付加ビット付認証条件記憶部11に記憶される付加ビット付認証条件のデータ例を示す図である。ここでは、付加ビット列は2個のビットであり、「01」の値である。図では、認証条件のビットと付加ビット列のビットとを区別して示すために認証条件のビットと付加ビット列とを区切って示しているが、データとして区切りはなく、付加ビット付認証条件は連続する26ビットのデータ(010011010・・・)である。付加ビット付認証条件記憶部11には、このようなフォーマットによって認証条件が記憶されており、付加ビット列が2ビットである場合には、3(付加ビット列のビット数+1)の倍数の箇所のビットが認証条件であることが予め定義されている。ただし、付加ビット列は隣り合うビットが異なる値を示す偶数個のビット列であれば良く、例えば「10」、「0101」、「1010」などでも良い。

【0018】

認証条件改ざん判定部12は、付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する。図3の例では、認証条件に含まれるA1の値を読み出す場合には、A1に隣り合う前後の付加ビットを2ビットずつが含まれるビット列「01101」を認証条件ビット列として読み出す。そして、認証条件改ざん判定部12は、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列(「111」または「000」)が含まれるか否かを判定する。ここで、付加ビットは隣り合うビットが異なる値を示すビット列(01)であるため、通常の動作を行っている限りは、同値が少なくとも3ビット連続するビット列が検出されることはない。このような認証条件改ざん判定処理により、同値が少なくとも3ビット連続するビット列が検出された場合には、何らかの改ざんが行われたと判定する。同値が少なくとも3ビット連続するビット列が検出されない場合には、改ざんが行われていないと判定する。

【0019】

認証値入力部13は、ユーザからの認証値の入力を受付け、入力に応じた付加ビット付き認証値を付加ビット付認証値記憶部14に記憶させる。認証値入力部13が付加ビット付認証値記憶部14に記憶させる付加ビット付き認証値のフォーマットは、図3に示した付加ビット付認証条件と同様である。ここでは、認証値入力部13は、例えば、PIN認証や指紋認証、署名認証などの処理を行い、認証結果に応じて、付加ビット付き認証値に含まれる認証値の該当箇所のフラグを立てる。例えばPIN認証を行う場合、認証値入力部13はPINの入力を受付け、定められた認証処理によりPIN認証を行う。そして、「A1」カテゴリの認証成功と判定した場合には、付加ビット付き認証値に含まれるA1の箇所のビットを1にして、付加ビット付認証値記憶部14に記憶させる。

【0020】

付加ビット付認証値記憶部14には、認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される。上述したように、付加ビット付認証値記憶部14に記憶される付加ビット付き認証値のフォーマットは、図3に示した付加ビット付認証条件と同様である。

【0021】

認証値改ざん判定部15は、付加ビット付認証値記憶部14に記憶されている付加ビット付認証値から、認証値に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する。認証値改ざん判定部15が行う認証値改ざん判定処理は、認証条件改ざん判定部12が行う認証条件改ざん判定と同様である。

【0022】

認証処理部16は、認証条件改ざん判定部12が、認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定し、かつ、認証値改ざん判定部15が、認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、認証条件改ざん判定部12に記憶されている認証条件と、付加ビット付認証値記憶部14に記憶されている認証値とを比較する認証処理を行う。認証処理部16は、認証条件改ざん判定部12に記憶されている認証条件を、付加ビット付認証値記憶部14に記憶されている認証値が満たすと判定した場合には、認証成功と判定する。

【0023】

記憶部17には、読み出しの対象となる情報が記憶されている。例えば、記憶部17には、階層構造によりデータが記憶されるようにしても良く、特定の階層の区画毎に異なるアクセス制限を設定することができる。すなわち、付加ビット付認証条件記憶部11には、記憶部17に記憶されている情報の区画毎に、対応する付加ビット付認証条件が記憶されている。

制御部18は、認証処理部16によって認証成功と判定されると、対応する区画の情報を記憶部17から読み出し、読み出した情報を出力する。

【0024】

次に、本実施形態による認証装置10の動作例を説明する。図4は、認証装置10による認証処理の動作例を示すフローチャートである。

ここでは、認証装置10はUSBメモリであり、PIN認証を行う場合を説明する。USBメモリである認証装置10が、例えばPC(パーソナルコンピュータ)に接続され、認証装置10の記憶部17に記憶されているデータの読み出し要求が入力されると、その要求に応じて、認証装置10の認証値入力部13は、PCにPIN入力画面を表示させる。ユーザからPINが入力されると、認証値入力部13は、PIN認証の処理を行う。例えば、認証値入力部13には予め定められたPINが記憶されており、入力されたPINと予め記憶されているPINとが一致するか否かを判定する。そして、認証成功と判定すれば、付加ビット付認証値記憶部14に記憶されている付加ビット付認証値の対応箇所のビットに1を記憶させる(ステップS1)。認証失敗と判定すれば、何もしない。

【0025】

次に、認証条件改ざん判定部12は、付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件を読み出し、認証条件改ざん判定処理を行う(ステップS2)。認証条件改ざん判定部12が、改ざんが行われたと判定すれば(ステップS2:NO)、接続されたPCにエラーを出力して処理を終了する(ステップS3)。認証条件改ざん判定部12が、改ざんが行われていないと判定すれば(ステップS2:YES)、認証値改ざん判定部15が、付加ビット付認証値記憶部14に記憶されている付加ビット付認証値を読み出し、認証値改ざん判定処理を行う(ステップS4)。認証値改ざん判定部15が、改ざんが行われたと判定すれば(ステップS4:NO)、接続されたPCにエラーを出力して処理を終了する(ステップS3)。認証値改ざん判定部15が、改ざんが行われていないと判定すれば(ステップS4:YES)、認証処理部16は、付加ビット付認証条件記憶部11に記憶されている認証条件と、付加ビット付認証値記憶部14に記憶されている認証値とを比較して認証処理を行う(ステップS5)。

【0026】

認証処理部16が、認証失敗と判定すれば(ステップS5:NO)、接続されたPCにエラーを出力して処理を終了する(ステップS3)。認証処理部16が、認証成功と判定すれば(ステップS5:YES)、制御部18は、記憶部17に記憶されている情報を読み出して、接続されたPCに出力する(ステップS6)。

このように、本実施形態によれば、フォルトインジェクション攻撃により、認証条件または認証値の3ビットの改ざんが行われた場合に、改ざんがあったことを検知することができる。これにより、例えばフォルトインジェクション攻撃により認証条件の値を全て0(認証不要)にして、アクセス制限を解除して情報が読み出されるようなことを防ぐことが可能となる。

【0027】

<第2の実施形態>

次に、本発明の第2の実施形態について説明する。第1の実施形態では、改ざん判定のために、認証条件および認証値に含まれるそれぞれのビットを、隣り合うビットが異なる値を示す偶数個のビットである付加ビット列によって挟むようにしたが、本実施形態では、奇数個のビットである付加ビット列によって挟む例を説明する。本実施形態における認証装置10の構成、動作は第1の実施形態と同様であるが、付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件に含まれる付加ビット列は、奇数個のビットであり、この付加ビット列は、認証条件に含まれるビットの前後で反転値である。

【0028】

図5は、本実施形態の付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件のデータ例を示す図である。フォルトインジェクション攻撃により3ビットのデータが同値に改ざんされ書き換えられた場合に、改ざんがあったことを検知するために、認証条件の前後の付加ビットが異なる値となるように認証条件の前後の付加ビットを反転値としている。例えば、図に示すように、A0のビットの前にビット列「101」を付加し、A0のビットの後ろに反転値であるビット列「010」を付加すれば、A0が0であっても1であっても、正常な状態で同値が3ビット連続することはない。図では、認証条件のビットと付加ビット列のビットとを区別して示すために認証条件のビットと付加ビット列とを区切って示しているが、データとして区切りはなく、付加ビット付認証条件は連続する35ビットのデータ(101001011010・・・)である。付加ビット付認証条件記憶部11には、このようなフォーマットによって認証条件が記憶されており、付加ビット列が3ビットである場合には、4(付加ビット列のビット数+1)の倍数の箇所のビットが認証条件であることが予め定義されている。

同様に、付加ビット付認証値記憶部14に記憶されている付加ビット付認証値に含まれる付加ビット列は、奇数個のビットであり、この付加ビット列は、認証値に含まれるビットの前後で反転値である。

【0029】

なお、本実施形態では、認証条件改ざん判定部12が認証条件の改ざんを判定し、認証値改ざん判定部15が認証値の改ざんを判定することにより認証条件と認証値との双方の改ざんを判定する例を説明したが、認証条件と認証値とのいずれかのみの改ざんを判定するようにしても良い。例えば、認証条件改ざん判定部12が認証条件の改ざんのみを判定し、改ざんが行われていないと判定すれば認証処理を行い、改ざんが行われたと判定すればエラーを出力するようにしても良い。あるいは、認証値改ざん判定部15が認証値の改ざんのみを判定し、改ざんが行われていないと判定すれば認証処理を行い、改ざんが行われたと判定すればエラーを出力するようにしても良い。あるいは、認証条件と認証値との双方の改ざん判定を行い、少なくともいずれかが改ざんされたと判定された場合には、エラーを出力するようにしても良い。

【0030】

本実施形態においても、認証条件改ざん判定部12は、付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した当該認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する。ここで、認証条件改ざん判定部12が読み出す認証条件ビット列は、認証条件に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれるビット列であれば良い。例えば、認証条件に含まれる1ビットと、その1ビットに隣り合う前後の3ビットずつである計7ビットのビット列でも良いし、認証条件に含まれる1ビットと、その1ビットに隣り合う前2ビットと後3ビット、あるいは前3ビットと後2ビットである計6ビットのビット列でも良い。

【0031】

なお、本発明における処理部の機能を実現するためのプログラムをコンピュータ読み取り可能な記録媒体に記録して、この記録媒体に記録されたプログラムをコンピュータシステムに読み込ませ、実行することにより認証処理を行ってもよい。なお、ここでいう「コンピュータシステム」とは、OSや周辺機器等のハードウェアを含むものとする。また、「コンピュータシステム」は、ホームページ提供環境(あるいは表示環境)を備えたWWWシステムも含むものとする。また、「コンピュータ読み取り可能な記録媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、CD−ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。さらに「コンピュータ読み取り可能な記録媒体」とは、インターネット等のネットワークや電話回線等の通信回線を介してプログラムが送信された場合のサーバやクライアントとなるコンピュータシステム内部の揮発性メモリ(RAM)のように、一定時間プログラムを保持しているものも含むものとする。

【0032】

また、上記プログラムは、このプログラムを記憶装置等に格納したコンピュータシステムから、伝送媒体を介して、あるいは、伝送媒体中の伝送波により他のコンピュータシステムに伝送されてもよい。ここで、プログラムを伝送する「伝送媒体」は、インターネット等のネットワーク(通信網)や電話回線等の通信回線(通信線)のように情報を伝送する機能を有する媒体のことをいう。また、上記プログラムは、前述した機能の一部を実現するためのものであっても良い。さらに、前述した機能をコンピュータシステムにすでに記録されているプログラムとの組み合わせで実現できるもの、いわゆる差分ファイル(差分プログラム)であっても良い。

【符号の説明】

【0033】

10 認証装置

11 付加ビット付認証条件記憶部

12 認証条件改ざん判定部

13 認証値入力部

14 付加ビット付認証値記憶部

15 認証値改ざん判定部

16 認証処理部

17 記憶部

18 制御部

【技術分野】

【0001】

本発明は、定められた認証条件と、入力される認証値とを比較して認証処理を行う技術に関する。

【背景技術】

【0002】

高い耐タンパ性が要求されるIC(integrated circuit)デバイスにおいて、そのICデバイスに記憶されている情報が読み出される際に、定められた認証処理を行って認証成功と判定した場合にのみ情報を出力するような制御が行われている。このような制御を行うICデバイスは、例えば、複数のビット列によって定められた認証条件を予め記憶し、このような認証条件と、入力される複数のビット列である認証値とを比較し、認証値が認証条件を満たす場合に認証成功と判定する。

特許文献1には、認証処理を行う際に用いる暗号鍵やそれに付帯する情報をアクセス制限のある特殊なエリアに記憶させ、安全な認証処理を行おうとする技術が記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−20676号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、近年、フォルトインジェクション等の攻撃手法が高度化しており、このような攻撃へのさらなる対策が必要である。例えば、ICデバイスの半導体に対して物理的に電圧や光線等を当てて、半導体内部のビットデータを書き換えて改ざんしてしまうという攻撃手法が現実的なものとなってきている。例えば、このような手法によりICデバイス内の認証条件や認証値が改ざんされてしまえば、本来意図しない手順により認証が成功してしまうことがあると考えられる。ただし、このような攻撃を行う場合、半導体内部のデータを1ビット単位で書き換えることは非常に困難であり、攻撃によるデータ書き換えの対象であるビットの前後1ビットずつ(計3ビット)が改ざんされる。ここで、このようなフォルトインジェクション攻撃による改ざんが行われた場合に、改ざんが行われたことを検知し、改ざんが行われた場合には認証を成功しないようにすることが望ましい。

【0005】

本発明は、このような状況に鑑みてなされたもので、フォルトインジェクション攻撃による改ざんが行われた場合に、改ざんが行われたか否かを判定する認証装置、認証方法および認証プログラムを提供する。

【課題を解決するための手段】

【0006】

上述した課題を解決するために、本発明は、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行う認証装置であって、認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する認証条件改ざん判定部と、付加ビット付認証値記憶部に記憶されている付加ビット付認証値から、認証値に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する認証値改ざん判定部と、認証条件改ざん判定部が、認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、認証値改ざん判定部が、認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、認証処理を行う認証処理部と、を備えることを特徴とする。

【0007】

また、本発明は、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件に含まれる付加ビット列は、偶数個のビットであり、付加ビット付認証値記憶部に記憶されている付加ビット付認証値に含まれる付加ビット列は、偶数個のビットであることを特徴とする。

【0008】

また、本発明は、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件に含まれる付加ビット列は、奇数個のビットであり、付加ビット列は、認証条件に含まれるビットの前後で反転値であり、付加ビット付認証値記憶部に記憶されている付加ビット付認証値に含まれる付加ビット列は、奇数個のビットであり、付加ビット列は、認証値に含まれるビットの前後で反転値であることを特徴とする。

【0009】

また、本発明は、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件に含まれる付加ビット列は、2個のビットであり、付加ビット付認証値記憶部に記憶されている付加ビット付認証値に含まれる付加ビット列は、2個のビットであることを特徴とする。

【0010】

また、本発明は、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行い、認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、を備えた認証装置の認証方法であって、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、付加ビット付認証値記憶部に記憶されている付加ビット付認証値から、認証値に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、認証処理を行うステップと、を備えることを特徴とする。

【0011】

また、本発明は、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行い、認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、を備えた認証装置のコンピュータに、付加ビット付認証条件記憶部に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、付加ビット付認証値記憶部に記憶されている付加ビット付認証値から、認証値に含まれる1ビットと、1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、認証処理を行うステップと、を実行させる認証プログラムである。

【発明の効果】

【0012】

以上説明したように、本発明によれば、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行う認証装置が、認証条件または認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列を記憶し、認証処理の際には、記憶したビット列から、認証条件または認証値に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれるビット列を読み出し、同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に認証処理を行うようにしたので、フォルトインジェクション攻撃により少なくとも3ビットの改ざんが行われた場合に改ざんが行われたことを検知することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の一実施形態による認証装置の構成例を示すブロック図である。

【図2】本発明の一実施形態による認証条件のデータ例を示す図である。

【図3】本発明の一実施形態による付加ビット付認証条件のデータ例を示す図である。

【図4】本発明の一実施形態による認証装置の動作例を示すフローチャートである。

【図5】本発明の一実施形態による付加ビット付認証条件のデータ例を示す図である。

【発明を実施するための形態】

【0014】

以下、本発明の一実施形態について、図面を参照して説明する。

<第1の実施形態>

図1は、本実施形態による認証装置10の構成を示すブロック図である。認証装置10は、複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行うコンピュータ装置である。具体的には、認証装置10には、USB(Universal Serial Bus)メモリやTPM(Trusted Platform Module)、ICカードなどの、ICチップの機能によって認証処理を行う各種ICデバイスが適用できる。認証装置10には、例えばISO/IEC7816−4に示されるような階層構造によりデータが記憶されており、階層の区画毎にアクセス制限が設定される。ここでは、このような区画にアクセスするためのコマンドごとに、認証条件のいずれのビットのフラグを用いるか、また各領域のフラグをどのように演算するかを示す条件が定められている。

【0015】

図2を参照して、このような認証処理の概要を説明する。例えば、認証装置10は、この図に示すような情報を認証条件として予め記憶している。認証条件は、AカテゴリとBカテゴリとに分類されたA0〜A3とB0〜B3との計8ビットの情報である。A0、B0はそれぞれANDフラグであり、A1〜A3、B1〜B3はそれぞれアクセス制御フラグである。ANDフラグは、それぞれのカテゴリにおけるアクセス制御フラグの結合関係を示すフラグであり、1ならANDを示し、0ならORを示す。AカテゴリとBカテゴリとはANDにより結合される。本実施形態ではアクセス制御フラグは3ビットとして説明するが、制御内容に応じて任意の数のビットをアクセス制御フラグとすることができる。

【0016】

認証装置10は、A1〜A3、B1〜B3をそれぞれ権限に対応する値とし、PIN認証や指紋認証、署名認証などに応じて、認証されたユーザの権限に対応するビットのフラグを立てる(0を1にする)。このようなフラグによって、特定の情報にアクセスすることが許可されているか否かを判定するアクセス制限を行う。例えば、このようなビット列によって、「(A1 OR A2) AND B2」のような権限によるアクセス制限を行うことができる。すなわち、多様な権限の組み合わせに応じて、特定の情報にアクセスすることを許可するように制御することができる。このような処理を行うため、認証装置10は、付加ビット付認証条件記憶部11と、認証条件改ざん判定部12と、認証値入力部13と、付加ビット付認証値記憶部14と、認証値改ざん判定部15と、認証処理部16と、記憶部17と、制御部18とを備えている。

【0017】

付加ビット付認証条件記憶部11には、定められた認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される。図3は、付加ビット付認証条件記憶部11に記憶される付加ビット付認証条件のデータ例を示す図である。ここでは、付加ビット列は2個のビットであり、「01」の値である。図では、認証条件のビットと付加ビット列のビットとを区別して示すために認証条件のビットと付加ビット列とを区切って示しているが、データとして区切りはなく、付加ビット付認証条件は連続する26ビットのデータ(010011010・・・)である。付加ビット付認証条件記憶部11には、このようなフォーマットによって認証条件が記憶されており、付加ビット列が2ビットである場合には、3(付加ビット列のビット数+1)の倍数の箇所のビットが認証条件であることが予め定義されている。ただし、付加ビット列は隣り合うビットが異なる値を示す偶数個のビット列であれば良く、例えば「10」、「0101」、「1010」などでも良い。

【0018】

認証条件改ざん判定部12は、付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する。図3の例では、認証条件に含まれるA1の値を読み出す場合には、A1に隣り合う前後の付加ビットを2ビットずつが含まれるビット列「01101」を認証条件ビット列として読み出す。そして、認証条件改ざん判定部12は、読み出した認証条件ビット列に、同値が少なくとも3ビット連続するビット列(「111」または「000」)が含まれるか否かを判定する。ここで、付加ビットは隣り合うビットが異なる値を示すビット列(01)であるため、通常の動作を行っている限りは、同値が少なくとも3ビット連続するビット列が検出されることはない。このような認証条件改ざん判定処理により、同値が少なくとも3ビット連続するビット列が検出された場合には、何らかの改ざんが行われたと判定する。同値が少なくとも3ビット連続するビット列が検出されない場合には、改ざんが行われていないと判定する。

【0019】

認証値入力部13は、ユーザからの認証値の入力を受付け、入力に応じた付加ビット付き認証値を付加ビット付認証値記憶部14に記憶させる。認証値入力部13が付加ビット付認証値記憶部14に記憶させる付加ビット付き認証値のフォーマットは、図3に示した付加ビット付認証条件と同様である。ここでは、認証値入力部13は、例えば、PIN認証や指紋認証、署名認証などの処理を行い、認証結果に応じて、付加ビット付き認証値に含まれる認証値の該当箇所のフラグを立てる。例えばPIN認証を行う場合、認証値入力部13はPINの入力を受付け、定められた認証処理によりPIN認証を行う。そして、「A1」カテゴリの認証成功と判定した場合には、付加ビット付き認証値に含まれるA1の箇所のビットを1にして、付加ビット付認証値記憶部14に記憶させる。

【0020】

付加ビット付認証値記憶部14には、認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される。上述したように、付加ビット付認証値記憶部14に記憶される付加ビット付き認証値のフォーマットは、図3に示した付加ビット付認証条件と同様である。

【0021】

認証値改ざん判定部15は、付加ビット付認証値記憶部14に記憶されている付加ビット付認証値から、認証値に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する。認証値改ざん判定部15が行う認証値改ざん判定処理は、認証条件改ざん判定部12が行う認証条件改ざん判定と同様である。

【0022】

認証処理部16は、認証条件改ざん判定部12が、認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定し、かつ、認証値改ざん判定部15が、認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、認証条件改ざん判定部12に記憶されている認証条件と、付加ビット付認証値記憶部14に記憶されている認証値とを比較する認証処理を行う。認証処理部16は、認証条件改ざん判定部12に記憶されている認証条件を、付加ビット付認証値記憶部14に記憶されている認証値が満たすと判定した場合には、認証成功と判定する。

【0023】

記憶部17には、読み出しの対象となる情報が記憶されている。例えば、記憶部17には、階層構造によりデータが記憶されるようにしても良く、特定の階層の区画毎に異なるアクセス制限を設定することができる。すなわち、付加ビット付認証条件記憶部11には、記憶部17に記憶されている情報の区画毎に、対応する付加ビット付認証条件が記憶されている。

制御部18は、認証処理部16によって認証成功と判定されると、対応する区画の情報を記憶部17から読み出し、読み出した情報を出力する。

【0024】

次に、本実施形態による認証装置10の動作例を説明する。図4は、認証装置10による認証処理の動作例を示すフローチャートである。

ここでは、認証装置10はUSBメモリであり、PIN認証を行う場合を説明する。USBメモリである認証装置10が、例えばPC(パーソナルコンピュータ)に接続され、認証装置10の記憶部17に記憶されているデータの読み出し要求が入力されると、その要求に応じて、認証装置10の認証値入力部13は、PCにPIN入力画面を表示させる。ユーザからPINが入力されると、認証値入力部13は、PIN認証の処理を行う。例えば、認証値入力部13には予め定められたPINが記憶されており、入力されたPINと予め記憶されているPINとが一致するか否かを判定する。そして、認証成功と判定すれば、付加ビット付認証値記憶部14に記憶されている付加ビット付認証値の対応箇所のビットに1を記憶させる(ステップS1)。認証失敗と判定すれば、何もしない。

【0025】

次に、認証条件改ざん判定部12は、付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件を読み出し、認証条件改ざん判定処理を行う(ステップS2)。認証条件改ざん判定部12が、改ざんが行われたと判定すれば(ステップS2:NO)、接続されたPCにエラーを出力して処理を終了する(ステップS3)。認証条件改ざん判定部12が、改ざんが行われていないと判定すれば(ステップS2:YES)、認証値改ざん判定部15が、付加ビット付認証値記憶部14に記憶されている付加ビット付認証値を読み出し、認証値改ざん判定処理を行う(ステップS4)。認証値改ざん判定部15が、改ざんが行われたと判定すれば(ステップS4:NO)、接続されたPCにエラーを出力して処理を終了する(ステップS3)。認証値改ざん判定部15が、改ざんが行われていないと判定すれば(ステップS4:YES)、認証処理部16は、付加ビット付認証条件記憶部11に記憶されている認証条件と、付加ビット付認証値記憶部14に記憶されている認証値とを比較して認証処理を行う(ステップS5)。

【0026】

認証処理部16が、認証失敗と判定すれば(ステップS5:NO)、接続されたPCにエラーを出力して処理を終了する(ステップS3)。認証処理部16が、認証成功と判定すれば(ステップS5:YES)、制御部18は、記憶部17に記憶されている情報を読み出して、接続されたPCに出力する(ステップS6)。

このように、本実施形態によれば、フォルトインジェクション攻撃により、認証条件または認証値の3ビットの改ざんが行われた場合に、改ざんがあったことを検知することができる。これにより、例えばフォルトインジェクション攻撃により認証条件の値を全て0(認証不要)にして、アクセス制限を解除して情報が読み出されるようなことを防ぐことが可能となる。

【0027】

<第2の実施形態>

次に、本発明の第2の実施形態について説明する。第1の実施形態では、改ざん判定のために、認証条件および認証値に含まれるそれぞれのビットを、隣り合うビットが異なる値を示す偶数個のビットである付加ビット列によって挟むようにしたが、本実施形態では、奇数個のビットである付加ビット列によって挟む例を説明する。本実施形態における認証装置10の構成、動作は第1の実施形態と同様であるが、付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件に含まれる付加ビット列は、奇数個のビットであり、この付加ビット列は、認証条件に含まれるビットの前後で反転値である。

【0028】

図5は、本実施形態の付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件のデータ例を示す図である。フォルトインジェクション攻撃により3ビットのデータが同値に改ざんされ書き換えられた場合に、改ざんがあったことを検知するために、認証条件の前後の付加ビットが異なる値となるように認証条件の前後の付加ビットを反転値としている。例えば、図に示すように、A0のビットの前にビット列「101」を付加し、A0のビットの後ろに反転値であるビット列「010」を付加すれば、A0が0であっても1であっても、正常な状態で同値が3ビット連続することはない。図では、認証条件のビットと付加ビット列のビットとを区別して示すために認証条件のビットと付加ビット列とを区切って示しているが、データとして区切りはなく、付加ビット付認証条件は連続する35ビットのデータ(101001011010・・・)である。付加ビット付認証条件記憶部11には、このようなフォーマットによって認証条件が記憶されており、付加ビット列が3ビットである場合には、4(付加ビット列のビット数+1)の倍数の箇所のビットが認証条件であることが予め定義されている。

同様に、付加ビット付認証値記憶部14に記憶されている付加ビット付認証値に含まれる付加ビット列は、奇数個のビットであり、この付加ビット列は、認証値に含まれるビットの前後で反転値である。

【0029】

なお、本実施形態では、認証条件改ざん判定部12が認証条件の改ざんを判定し、認証値改ざん判定部15が認証値の改ざんを判定することにより認証条件と認証値との双方の改ざんを判定する例を説明したが、認証条件と認証値とのいずれかのみの改ざんを判定するようにしても良い。例えば、認証条件改ざん判定部12が認証条件の改ざんのみを判定し、改ざんが行われていないと判定すれば認証処理を行い、改ざんが行われたと判定すればエラーを出力するようにしても良い。あるいは、認証値改ざん判定部15が認証値の改ざんのみを判定し、改ざんが行われていないと判定すれば認証処理を行い、改ざんが行われたと判定すればエラーを出力するようにしても良い。あるいは、認証条件と認証値との双方の改ざん判定を行い、少なくともいずれかが改ざんされたと判定された場合には、エラーを出力するようにしても良い。

【0030】

本実施形態においても、認証条件改ざん判定部12は、付加ビット付認証条件記憶部11に記憶されている付加ビット付認証条件から、認証条件に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した当該認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する。ここで、認証条件改ざん判定部12が読み出す認証条件ビット列は、認証条件に含まれる1ビットと、その1ビットに隣り合う前後の付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれるビット列であれば良い。例えば、認証条件に含まれる1ビットと、その1ビットに隣り合う前後の3ビットずつである計7ビットのビット列でも良いし、認証条件に含まれる1ビットと、その1ビットに隣り合う前2ビットと後3ビット、あるいは前3ビットと後2ビットである計6ビットのビット列でも良い。

【0031】

なお、本発明における処理部の機能を実現するためのプログラムをコンピュータ読み取り可能な記録媒体に記録して、この記録媒体に記録されたプログラムをコンピュータシステムに読み込ませ、実行することにより認証処理を行ってもよい。なお、ここでいう「コンピュータシステム」とは、OSや周辺機器等のハードウェアを含むものとする。また、「コンピュータシステム」は、ホームページ提供環境(あるいは表示環境)を備えたWWWシステムも含むものとする。また、「コンピュータ読み取り可能な記録媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、CD−ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。さらに「コンピュータ読み取り可能な記録媒体」とは、インターネット等のネットワークや電話回線等の通信回線を介してプログラムが送信された場合のサーバやクライアントとなるコンピュータシステム内部の揮発性メモリ(RAM)のように、一定時間プログラムを保持しているものも含むものとする。

【0032】

また、上記プログラムは、このプログラムを記憶装置等に格納したコンピュータシステムから、伝送媒体を介して、あるいは、伝送媒体中の伝送波により他のコンピュータシステムに伝送されてもよい。ここで、プログラムを伝送する「伝送媒体」は、インターネット等のネットワーク(通信網)や電話回線等の通信回線(通信線)のように情報を伝送する機能を有する媒体のことをいう。また、上記プログラムは、前述した機能の一部を実現するためのものであっても良い。さらに、前述した機能をコンピュータシステムにすでに記録されているプログラムとの組み合わせで実現できるもの、いわゆる差分ファイル(差分プログラム)であっても良い。

【符号の説明】

【0033】

10 認証装置

11 付加ビット付認証条件記憶部

12 認証条件改ざん判定部

13 認証値入力部

14 付加ビット付認証値記憶部

15 認証値改ざん判定部

16 認証処理部

17 記憶部

18 制御部

【特許請求の範囲】

【請求項1】

複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行う認証装置であって、

前記認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、

前記認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件から、前記認証条件に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した当該認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する認証条件改ざん判定部と、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値から、前記認証値に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した当該認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する認証値改ざん判定部と、

前記認証条件改ざん判定部が、前記認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、前記認証値改ざん判定部が、前記認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、前記認証処理を行う認証処理部と、

を備えることを特徴とする認証装置。

【請求項2】

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件に含まれる前記付加ビット列は、偶数個のビットであり、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値に含まれる前記付加ビット列は、偶数個のビットである

ことを特徴とする請求項1に記載の認証装置。

【請求項3】

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件に含まれる前記付加ビット列は、奇数個のビットであり、当該付加ビット列は、前記認証条件に含まれるビットの前後で反転値であり、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値に含まれる前記付加ビット列は、奇数個のビットであり、当該付加ビット列は、前記認証値に含まれるビットの前後で反転値である

ことを特徴とする請求項1に記載の認証装置。

【請求項4】

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件に含まれる前記付加ビット列は、2個のビットであり、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値に含まれる前記付加ビット列は、2個のビットである

ことを特徴とする請求項1または請求項2のいずれかに記載の認証装置。

【請求項5】

複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行い、前記認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、前記認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、を備えた認証装置の認証方法であって、

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件から、前記認証条件に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した当該認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値から、前記認証値に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した当該認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、

前記認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、前記認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、前記認証処理を行うステップと、

を備えることを特徴とする認証方法。

【請求項6】

複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行い、前記認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、前記認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、を備えた認証装置のコンピュータに、

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件から、前記認証条件に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した当該認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値から、前記認証値に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した当該認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、

前記認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、前記認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、前記認証処理を行うステップと、

を実行させる認証プログラム。

【請求項1】

複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行う認証装置であって、

前記認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、

前記認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件から、前記認証条件に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した当該認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する認証条件改ざん判定部と、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値から、前記認証値に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した当該認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定する認証値改ざん判定部と、

前記認証条件改ざん判定部が、前記認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、前記認証値改ざん判定部が、前記認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、前記認証処理を行う認証処理部と、

を備えることを特徴とする認証装置。

【請求項2】

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件に含まれる前記付加ビット列は、偶数個のビットであり、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値に含まれる前記付加ビット列は、偶数個のビットである

ことを特徴とする請求項1に記載の認証装置。

【請求項3】

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件に含まれる前記付加ビット列は、奇数個のビットであり、当該付加ビット列は、前記認証条件に含まれるビットの前後で反転値であり、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値に含まれる前記付加ビット列は、奇数個のビットであり、当該付加ビット列は、前記認証値に含まれるビットの前後で反転値である

ことを特徴とする請求項1に記載の認証装置。

【請求項4】

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件に含まれる前記付加ビット列は、2個のビットであり、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値に含まれる前記付加ビット列は、2個のビットである

ことを特徴とする請求項1または請求項2のいずれかに記載の認証装置。

【請求項5】

複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行い、前記認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、前記認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、を備えた認証装置の認証方法であって、

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件から、前記認証条件に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した当該認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値から、前記認証値に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した当該認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、

前記認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、前記認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、前記認証処理を行うステップと、

を備えることを特徴とする認証方法。

【請求項6】

複数のビットが含まれるビット列によって予め定められた認証条件と、入力されるビット列である認証値とを比較して認証処理を行い、前記認証条件に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証条件が記憶される付加ビット付認証条件記憶部と、前記認証値に含まれる複数のビットのそれぞれの前後に、隣り合うビットが異なる値を示す付加ビット列が付加されたビット列である付加ビット付認証値が記憶される付加ビット付認証値記憶部と、を備えた認証装置のコンピュータに、

前記付加ビット付認証条件記憶部に記憶されている前記付加ビット付認証条件から、前記認証条件に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証条件ビット列を読み出し、読み出した当該認証条件ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、

前記付加ビット付認証値記憶部に記憶されている前記付加ビット付認証値から、前記認証値に含まれる1ビットと、当該1ビットに隣り合う前後の前記付加ビットのうち少なくとも2ビットずつとの少なくとも5ビットが含まれる認証値ビット列を読み出し、読み出した当該認証値ビット列に、同値が少なくとも3ビット連続するビット列が含まれるか否かを判定するステップと、

前記認証条件ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合、または、前記認証値ビット列に同値が少なくとも3ビット連続するビット列が含まれないと判定した場合に、前記認証処理を行うステップと、

を実行させる認証プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−78990(P2012−78990A)

【公開日】平成24年4月19日(2012.4.19)

【国際特許分類】

【出願番号】特願2010−222291(P2010−222291)

【出願日】平成22年9月30日(2010.9.30)

【出願人】(000102728)株式会社エヌ・ティ・ティ・データ (438)

【Fターム(参考)】

【公開日】平成24年4月19日(2012.4.19)

【国際特許分類】

【出願日】平成22年9月30日(2010.9.30)

【出願人】(000102728)株式会社エヌ・ティ・ティ・データ (438)

【Fターム(参考)】

[ Back to top ]