誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、誘導性負荷駆動装置に関する。

【背景技術】

【0002】

下記特許文献1には、誘導性負荷の一端と外部供給電源との間に介挿された第1のスイッチング素子と、誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、第1のスイッチング素子がオフ及び第2のスイッチング素子がオンの時に誘導性負荷に生じる逆起電流をアースを介して誘導性負荷に還流させる還流回路と、第1及び第2のスイッチング素子の両方がオフの時に誘導性負荷に生じる逆起電流を外部供給電源に還元(回生)させる逆起電流還元回路とを備えた誘導性負荷駆動装置が開示されている。

【0003】

このような構成の誘導性負荷駆動装置では、第2のスイッチング素子をオン状態に維持しながら第1のスイッチング素子のオン/オフ期間の比率(デューティ比)を制御することにより、負荷電流の立上がり特性を制御することができる。また、第1のスイッチング素子をオフ状態に維持しながら第2のスイッチング素子のデューティ比を制御することにより、負荷電流の立下がり特性を制御しながら誘導性負荷に生じる逆起電流を外部供給電源に回生させることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−85046号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記特許文献1には明記されていないが、誘導性負荷に流れる負荷電流の波形を任意に制御する手法として、第2のスイッチング素子とアース間にシャント抵抗を設け、このシャント抵抗の端子間電圧をサンプルホールド回路によってサンプリングし、そのサンプリング値(つまり負荷電流値)をスイッチング制御を行うマイコンにフィードバックする手法が挙げられる。

【0006】

上記特許文献1の技術では、第1のスイッチング素子をオフ状態に維持しながら第2のスイッチング素子のデューティ比を制御する期間(負荷電流の立下り波形を制御する期間)において、第2のスイッチング素子がオンの時、負荷電流は、誘導性負荷→第2のスイッチング素子→アース→還流回路→誘導性負荷、というルート(電流還流ルート)で流れ、第2のスイッチング素子がオフの時、負荷電流は、アース→還流回路→誘導性負荷→逆起電流還元回路→外部供給電源、というルート(電流回生ルート)で流れる。

【0007】

そのため、負荷電流の立下り波形を制御する期間に負荷電流値をサンプリングするには、電流還流ルートで負荷電流が流れる期間にサンプルホールド回路のサンプルスイッチをオンにしてシャント抵抗の端子間電圧をサンプリングし、電流回生ルートで負荷電流が流れる期間にサンプルスイッチをオフにしてシャント抵抗の端子間電圧をホールドする(ホールドコンデンサに電荷を保持する)必要がある。

【0008】

ここで、電流回生ルートから電流還流ルートへ切替える時、つまり第2のスイッチング素子をオフからオンに切替える時に、回路的な要因によってサンプリングタイミング(サンプルスイッチのオンタイミング)から遅れて第2のスイッチング素子がオンに切替わると、ホールドコンデンサの電荷抜けが発生してしまい、電流値サンプリングの追従性が低下する(電流検出精度が低下する)という問題がある。

【0009】

本発明は、上述した事情に鑑みてなされたものであり、電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記目的を達成するために、本発明では、誘導性負荷駆動装置に係る第1の解決手段として、電源と誘導性負荷の一端との間に介挿された第1のスイッチング素子と、前記誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、前記第1のスイッチング素子がオフ及び前記第2のスイッチング素子がオンの時に前記誘導性負荷の他端から出力される逆起電流を、前記アースを介して前記誘導性負荷の一端へ還流させる還流回路と、前記第1及び第2のスイッチング素子の両方がオフの時に前記誘導性負荷の他端から出力される逆起電流を前記電源に回生させる逆起電流回生回路と、前記第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から前記誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、2つの入力端子が前記シャント抵抗の両端に接続された差動増幅器と、前記第1及び第2のスイッチング素子を制御するプロセッサと前記差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、前記プロセッサから前記第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後に前記サンプルスイッチをオンにさせる遅延回路とを備える、という手段を採用する。

【0011】

また、本発明では、誘導性負荷駆動装置に係る第2の解決手段として、上記第1の解決手段において、前記遅延回路は、前記プロセッサから前記第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから、コンデンサの容量で定まる遅延時間の経過後に前記サンプルスイッチをオンにさせる、という手段を採用する。

【0012】

また、本発明では、誘導性負荷駆動装置に係る第3の解決手段として、上記第2の解決手段において、前記遅延回路と前記コンデンサを外付けするために用いられる外付け端子と、前記外付け端子に接続された外付けコンデンサとを備える、という手段を採用する。

【発明の効果】

【0013】

本発明によれば、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせるので、回路的な要因によって制御信号がオンレベルに遷移してから第2のスイッチング素子が実際にオンに切替わるタイミングが遅れたとしても、サンプリングタイミングと第2のスイッチング素子のオンタイミングとを一致させることができ、その結果、電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現できる。

【図面の簡単な説明】

【0014】

【図1】本実施形態に係る誘導性負荷駆動装置1の概略構成図である。

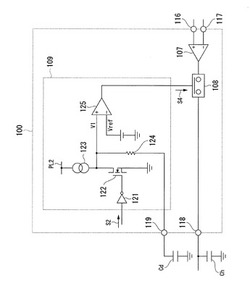

【図2】制御回路100に設けられた遅延回路109の詳細な回路構成を示す図である。

【図3】制御回路100から誘導負荷駆動回路200へ出力される第1の制御信号S1、第2の制御信号S2及び第3の制御信号S3と、誘導性負荷Lに流れる駆動電流との時間的な対応関係を示すタイミングチャートである。

【図4】本実施形態の効果(電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサChの電荷抜け抑制効果)を示す図である。

【発明を実施するための形態】

【0015】

以下、本発明の一実施形態について、図面を参照しながら説明する。

図1は、本実施形態に係る誘導性負荷駆動装置1の概略構成図である。この図1に示すように、誘導性負荷駆動装置1は、制御回路100、誘導性負荷駆動回路200及び例えばCPU等のプロセッサ300を備えている。誘導性負荷駆動回路200は、プロセッサ300による制御の下、ソレノイドコイル或いはモータコイル等の誘導性負荷Lに駆動電流を供給するものであり、誘導性負荷Lの一端に接続された第1の負荷接続端子201と、誘導性負荷Lの他端に接続された第2の負荷接続端子202と、第1のスイッチング素子203と、第2のスイッチング素子204と、第3のスイッチング素子205と、回生ダイオード206と、シャント抵抗207とを備えている。

【0016】

第1のスイッチング素子203は、比較的高い電源電圧(例えば30V)が印加された電源PL1と第1の負荷接続端子201(つまり誘導性負荷Lの一端)との間に介挿されたn型MOS−FETであり、ドレイン端子が電源PL1に接続され、ソース端子が第1の負荷接続端子201に接続され、ゲート端子が制御回路100(第1の制御信号出力端子113)に接続されている。この第1のスイッチング素子203は、プロセッサ300から制御回路100を介して入力される第1の制御信号(パルス幅変調された信号)S1に応じてオン/オフ状態が切替わる。

【0017】

第2のスイッチング素子204は、第2の負荷接続端子202(つまり誘導性負荷Lの他端)とアースとの間に介挿されたn型MOS−FETであり、ドレイン端子が第2の負荷接続端子202に接続され、ソース端子がシャント抵抗207を介してアースに接続され、ゲート端子が制御回路100(第2の制御信号出力端子114)に接続されている。この第2のスイッチング素子204は、プロセッサ300から制御回路100を介して入力される第2の制御信号S2に応じてオン/オフ状態が切替わる。

【0018】

第3のスイッチング素子205は、第1の負荷接続端子201(つまり誘導性負荷Lの一端)とアースとの間に介挿され、第1のスイッチング素子203に対してオンオフ状態が反転するように制御されるn型MOS−FETであり、ドレイン端子が第1の負荷接続端子201に接続され、ソース端子がアースに接続され、ゲート端子が制御回路100(第3の制御信号出力端子115)に接続されている。

【0019】

この第3のスイッチング素子205は、制御回路100から入力される第3の制御信号S3(第1の制御信号S1に対してレベルが反転する信号)に応じてオン/オフ状態が切替わる。なお、この第3のスイッチング素子205は、第1のスイッチング素子203がオフ且つ第2のスイッチング素子204がオンの時に誘導性負荷Lの他端から出力される逆起電流を、アースを介して誘導性負荷Lの一端へ還流させる還流回路として設けられたものである。

【0020】

回生ダイオード206は、アノード端子が第2の負荷接続端子202に接続され、カソード端子が電源PL1に接続されている。この回生ダイオード206は、第1及び第2のスイッチング素子203、204の両方がオフの時に誘導性負荷Lの他端から出力される逆起電流を電源PL1に回生させる逆起電流回生回路として設けられたものである。シャント抵抗207は、制御回路100によって誘導性負荷Lに流れる駆動電流を検出するために用いられる抵抗素子であり、一端が第2のスイッチング素子204のソース端子に接続され、他端がアースに接続されている。

【0021】

一方、制御回路100は、上述した誘導性負荷駆動回路200から誘導性負荷Lに供給される駆動電流を検出するカスタムICであり、第1の入力回路101と、第2の入力回路102と、第1の出力回路103と、第2の出力回路104と、第1のインバータ105と、第3の出力回路106と、オペアンプ107と、サンプルスイッチ108と、遅延回路109とを備えている。

【0022】

また、この制御回路100は、プロセッサ300から第1の制御信号S1を入力するための第1の制御信号入力端子111と、プロセッサ300から第2の制御信号S2を入力するための第2の制御信号入力端子112と、第1のスイッチング素子203のゲート端子に接続された第1の制御信号出力端子113と、第2のスイッチング素子204のゲート端子に接続された第2の制御信号出力端子114と、第3のスイッチング素子205のゲート端子に接続された第3の制御信号出力端子115と、シャント抵抗207の一端に接続された第1の抵抗接続端子116と、シャント抵抗207の他端に接続された第2の抵抗接続端子117と、プロセッサ300のA/D入力ポートに接続されると共にホールドコンデンサChが接続されたサンプル出力端子118と、コンデンサCdを外付けするために用いられる外付け端子119とを備えている。

【0023】

プロセッサ300から第1の制御信号入力端子111に入力された第1の制御信号S1は、第1の入力回路101及び第1の出力回路103を通過した後、第1の制御信号出力端子113を介して第1のスイッチング素子203に出力される。一方、プロセッサ300から第2の制御信号入力端子112に入力された第2の制御信号S2は、第2の入力回路102及び第2の出力回路104を通過した後、第2の制御信号出力端子114を介して第2のスイッチング素子204に出力される。

【0024】

また、第1の制御信号S1は、第1の入力回路101から分岐して第1のインバータ105に入力される。第1のインバータ105は、第1の入力回路101から入力された第1の制御信号S1のレベルを反転させ、レベル反転後の第1の制御信号S1を第3の制御信号S3として第3の出力回路106に出力する。第3の制御信号S3は、第3の出力回路106を通過した後、第3の制御信号出力端子115を介して第3のスイッチング素子205に出力される。

【0025】

なお、第1の入力回路101及び第2の入力回路102は、例えばプルダウン抵抗やシュミット回路等から構成されており、第1の出力回路103、第2の出力回路104及び第3の出力回路106は、例えばレベルシフタや出力バッファ等から構成されている。

【0026】

オペアンプ107は、非反転入力端子が第1の抵抗接続端子116(つまりシャント抵抗207の一端)に接続され、反転入力端子が第2の抵抗接続端子117(つまりシャント抵抗207の他端)に接続された差動増幅器であり、シャント抵抗207の端子間電圧を増幅して出力する。

【0027】

サンプルスイッチ108は、オペアンプ107の出力端子とプロセッサ300とを結ぶ配線(より詳細にはオペアンプ107の出力端子とサンプル出力端子118とを結ぶ配線)に介挿されたサンプル・ホールド用のスイッチング素子であり、後述の遅延回路109から入力されるサンプルタイミング信号S4に応じてオン/オフ状態が切替わる。

【0028】

遅延回路109は、第2の入力回路102から分岐した第2の制御信号S2が入力されており、この第2の制御信号S2がオンレベル(本実施形態ではハイレベル)に遷移してから、外付け端子119に外付けされたコンデンサCdの容量で定まる遅延時間の経過後にサンプルスイッチ108をオンにさせるためのサンプルタイミング信号S4をサンプルスイッチ108に出力する。

【0029】

詳細には、遅延回路109は、図2に示すように、第2のインバータ121と、例えばn型MOS−FETである制御用スイッチング素子122と、定電流源123と、抵抗素子124と、コンパレータ125とを備えている。第2のインバータ121は、第2の入力回路102から入力される第2の制御信号S2のレベルを反転させて制御用スイッチング素子122のゲート端子に出力するレベル反転回路である。

【0030】

制御用スイッチング素子122は、ドレイン端子が定電流源123を介して低電圧(例えば3.3V)の電源PL2に接続され、ソース端子がアースに接続され、ゲート端子が第2のインバータ121の出力端子に接続されており、第2のインバータ121から入力されるレベル反転後の第2の制御信号S2に応じてオン/オフ状態が切替わる。定電流源123は、定電流を発生するものであり、一端が電源PL2に接続され、他端が制御用スイッチング素子122のドレイン端子に接続されている。

【0031】

抵抗素子124は、一端が定電流源123の他端に接続され、他端がコンデンサCdを外付けするための外付け端子119に接続されている。コンパレータ125は、非反転入力端子が定電流源123の他端に接続されており、非反転入力端子に印加される参照電圧V1が、反転入力端子に印加される基準電圧Vref以上となった時にサンプルスイッチ108をオンにさせるためのオンレベル(ハイレベル)のサンプルタイミング信号S4を出力し、参照電圧V1が基準電圧Vref未満となった時にサンプルスイッチ108をオフにさせるためのオフレベル(ローレベル)のサンプルタイミング信号S4を出力する。

【0032】

このような構成の遅延回路109によれば、第2の制御信号S2がハイレベルに遷移すると、制御用スイッチング素子122がオフとなり、外付けされたコンデンサCdに電荷が充電され始める。そして、コンデンサCdの充電に伴って、コンパレータ125の非反転入力端子に印加される参照電圧V1が上昇し、参照電圧V1が基準電圧Vref以上となった時点でコンパレータ125の出力であるサンプルタイミング信号S4がハイレベルに切替わる。

【0033】

一方、第2の制御信号S2がローレベルに遷移すると、制御用スイッチング素子122がオンとなり、コンデンサCdに貯まっていた電荷がアースに放電され始める。そして、コンデンサCdの放電に伴って、コンパレータ125の非反転入力端子に印加される参照電圧V1が下降し、参照電圧V1が基準電圧Vref未満となった時点でサンプルタイミング信号S4がローレベルに切替わる。

【0034】

このように、本実施形態の遅延回路109を採用することにより、第2の制御信号S2がハイレベルに遷移してから、外付け端子119に外付けされたコンデンサCdの容量で定まる遅延時間(参照電圧V1が上昇を開始してから基準電圧Vref以上となるまでの時間)の経過後にサンプルスイッチ108をオンに切替えることができる。

【0035】

なお、プロセッサ300は、A/D入力ポートへの入力電圧をA/D変換することでシャント抵抗207の端子間電圧を検知すると共に、このシャント抵抗207の端子間電圧を駆動電流値に換算し、その駆動電流値が目標値と一致するように第1及び第2のスイッチング素子203、204のフィードバック制御(第1及び第2の制御信号S1、S2のデューティ比制御)を行う。

【0036】

次に、上記のように構成された誘導性負荷駆動装置1の動作について図3を参照しながら詳細に説明する。

図3は、制御回路100から誘導負荷駆動回路200へ出力される第1の制御信号S1、第2の制御信号S2及び第3の制御信号S3と、誘導性負荷Lに流れる駆動電流との時間的な対応関係を示すタイミングチャートである。

【0037】

この図3に示すように、時刻t1から時刻t2までの期間において、所定のデューティ比を有し、互いにレベルが反転するパルス状の第1の制御信号S1及び第3の制御信号S3と、オンレベル(ハイレベル)一定の第2の制御信号S2が制御回路100から誘導負荷駆動回路200へ出力される。つまり、時刻t1から時刻t2までの期間では、第2のスイッチング素子204がオン状態に維持されながら、第1のスイッチング素子203及び第3のスイッチング素子205が、所定のデューティ比でオン/オフ制御される。なお、第3のスイッチング素子205のオン/オフ状態は、第1のスイッチング素子203に対して反転していることに注意されたい。

【0038】

このような時刻t1から時刻t2までの期間において、第1のスイッチング素子203がオン及び第3のスイッチング素子205がオフの時、誘導性負荷Lの一端は第1のスイッチング素子203を介して電源PL1に接続され、誘導性負荷Lの他端は第2のスイッチング素子204を介してアースに接続される。この時、誘導性負荷Lに電源電圧(約30V)が印加されるため、誘導性負荷Lに流れる駆動電流は一定の傾きで増加する。なお、この時の駆動電流は、電源PL1→第1のスイッチング素子203→誘導性負荷L→第2のスイッチング素子204→アース、というルート(負荷通電ルート)で流れる。

【0039】

一方、時刻t1から時刻t2までの期間において、第1のスイッチング素子203がオフ及び第3のスイッチング素子205がオンの時、誘導性負荷Lの一端は第3のスイッチング素子205を介してアースに接続される(誘導性負荷Lの他端は第2のスイッチング素子204を介してアースに接続されたまま)。この時、誘導性負荷Lに電源電圧が印加されないので、誘導性負荷Lに逆起電圧が発生し、誘導性負荷Lの他端から逆起電流が出力される。

【0040】

この逆起電流は、第2のスイッチング素子204を介してアースに流入し、さらに第3のスイッチング素子205を介して誘導性負荷Lの一端に還流する。つまり、駆動電流は、誘導性負荷L→第2のスイッチング素子204→アース→第3のスイッチング素子205→誘導性負荷L、というルート(電流還流ルート)で流れる。これにより、第1のスイッチング素子203がオフとなっても、誘導性負荷Lの駆動電流は一定に保持される(厳密には減少するが無視できる)。

【0041】

このように、時刻t1から時刻t2までの期間において、第2のスイッチング素子204をオン状態に維持しながら、互いにオン/オフ状態が反転するように第1のスイッチング素子203及び第3のスイッチング素子205をPWM制御またはオン/オフ制御することにより、誘導性負荷Lに流れる駆動電流の立上がり特性を制御することができる。

【0042】

なお、このような時刻t1から時刻t2までの期間(第2の制御信号S2が常時ハイレベルの期間)では、遅延回路109から常時ハイレベルのサンプルタイミング信号S4が出力されるため、サンプルスイッチ108も常時オンとなり、オペアンプ107からプロセッサ300のA/D入力ポートへシャント抵抗207の端子間電圧が常時入力され続ける。つまり、プロセッサ300は、時刻t1から時刻t2までの期間において、第2の制御信号S2を常時ハイレベルに維持すると共に、シャント抵抗207の端子間電圧から換算した駆動電流値が目標値と一致するように第1のスイッチング素子203のフィードバック制御(第1の制御信号S1のデューティ比制御)を行っている。

【0043】

続いて、時刻t2から時刻t3までの期間において、ハイレベル一定の第1の制御信号S1と、ハイレベル一定の第3の制御信号S3と、所定のデューティ比を有するパルス状の第2の制御信号S2とが制御回路100から誘導負荷駆動回路200へ出力される。つまり、時刻t2から時刻t3までの期間では、第1のスイッチング素子203がオフ状態且つ第3のスイッチング素子205がオン状態に維持されながら、第2のスイッチング素子204が所定のデューティ比でオン/オフ制御される。

【0044】

このような時刻t2から時刻t3までの期間において、第2のスイッチング素子204がオフの時、誘導性負荷Lの一端は第3のスイッチング素子205を介してアースに接続され、誘導性負荷Lの他端は回生ダイオード206を介して電源PL1に接続される。この時、誘導性負荷Lに電源電圧が印加されないので、誘導性負荷Lに逆起電圧が生じる。

【0045】

この逆起電圧が電源電圧より大きくなると、回生ダイオード206を介して誘導性負荷Lの他端から電源PL1に逆起電流が回生される。つまり、誘導性負荷Lに流れる駆動電流は、アース→第3のスイッチング素子205→誘導性負荷L→回生ダイオード206→電源PL1、というルート(電流回生ルート)で流れる。これにより、誘導性負荷Lの駆動電流は一定の傾きで減少する。

【0046】

一方、時刻t2から時刻t3までの期間において、第2のスイッチング素子204がオンの時、誘導性負荷Lの他端は第2のスイッチング素子204を介してアースに接続される(誘導性負荷Lの一端は第3のスイッチング素子205を介してアースに接続されたまま)。この時、誘導性負荷Lに電源電圧が印加されないため、誘導性負荷Lに逆起電圧が発生し、誘導性負荷Lの他端から逆起電流が第2のスイッチング素子205を介してアースに流入し、さらに第3のスイッチング素子205を介して誘導性負荷Lの一端に還流する(電流還流ルートで駆動電流が流れる)。これにより、駆動電流は一定に保持される(厳密には減少するが無視できる)。

【0047】

このように、時刻t2から時刻t3までの期間において、第1のスイッチング素子203をオフ状態且つ第3のスイッチング素子205をオン状態に維持しながら、第2のスイッチング素子204をPWM制御することにより、誘導性負荷Lに流れる駆動電流の立下がり特性を制御することができる。

【0048】

このような時刻t2から時刻t3までの期間(駆動電流の立下り波形を制御する期間)においては、電流還流ルートで駆動電流が流れる期間(第2のスイッチング素子204がオンの期間)と、電流回生ルートで駆動電流が流れる期間(第2のスイッチング素子204がオフの期間)とが交互に現れる。

【0049】

そのため、駆動電流の立下り波形を制御する期間に駆動電流値をサンプリングするには、電流還流ルートで駆動電流が流れる期間にサンプルスイッチ108をオンにしてシャント抵抗207の端子間電圧をサンプリングし、電流回生ルートで駆動電流が流れる期間にサンプルスイッチ108をオフにしてシャント抵抗207の端子間電圧をホールドする(ホールドコンデンサChに電荷を保持する)必要がある。

【0050】

ここで、従来では、図4(a)に示すように、電流回生ルートから電流還流ルートへ切替える時、つまり第2のスイッチング素子204をオフからオンに切替える時に、回路的な要因によってサンプリングタイミング(サンプルスイッチ108のオンタイミング)から遅れて第2のスイッチング素子204がオンに切替わると、ホールドコンデンサChの電荷抜けが発生してしまい、電流値サンプリングの追従性が低下する(電流検出精度が低下する)という問題があった。

【0051】

これに対して、本実施形態における遅延回路109は、上述したように、第2の制御信号S2がハイレベルに遷移してから、外付け端子119に外付けされたコンデンサCdの容量で定まる遅延時間の経過後にハイレベルのサンプルタイミング信号S4を出力して、サンプルスイッチ108をオンに切替えることができる。

【0052】

つまり、コンデンサCdの容量を調整して、第2の制御信号S2がハイレベルに遷移してからサンプルタイミング信号S4がハイレベルに切替わるまでの遅延時間を、第2の制御信号S2がハイレベルに遷移してから実際に第2のスイッチング素子204がオンに切替わるまでの遅延時間と一致させることにより、図4(b)に示すように、サンプリングタイミング(サンプルスイッチ108のオンタイミング)と第2のスイッチング素子204のオンタイミングとを一致させることができる。

【0053】

以上のように、本実施形態によれば、回路的な要因によって第2の制御信号S2がハイレベルに遷移してから第2のスイッチング素子204が実際にオンに切替わるタイミングが遅れたとしても、サンプリングタイミングと第2のスイッチング素子204のオンタイミングとを一致させることができ、その結果、電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサChの電荷抜けを抑制して電流検出精度の向上を実現することができる。

【0054】

なお、本発明は上記実施形態に限定されず、以下のような変形例が挙げられる。

(1)上記実施形態では、遅延回路109の具体例として図2に示すような回路構成を挙げたが、第2のスイッチング素子204に出力される第2の制御信号S2がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチ108をオンにさせることができれば、どのような回路構成を採用しても良い。

また、必ずしもコンデンサCdを外付けとする必要はなく、予め遅延回路109の内部に容量を最適化したコンデンサCdを設けておく構成を採用しても良い。また、ホールドコンデンサChを制御回路100の内部に設けておく構成を採用しても良い。

【0055】

(2)上記実施形態では、回生ダイオード206からなる逆起電流回生回路を例示したが、第1及び第2のスイッチング素子203、204の両方がオフの時に誘導性負荷Lの他端から出力される逆起電流を電源PL1に回生させることができれば、逆起電流回生回路の構成はこれに限定されない。例えば、特開2008−85046号公報に記載されているような逆起電流還元回路(逆起電流回生回路と同義)を用いても良い。

【0056】

(3)上記実施形態では、第3のスイッチング素子205からなる還流回路を例示したが、第1のスイッチング素子203がオフ及び第2のスイッチング素子204がオンの時に誘導性負荷Lの他端から出力される逆起電流を、アースを介して誘導性負荷Lの一端へ還流させることができれば、還流回路の構成はこれに限定されない。例えば、特開2008−85046号公報に記載されているような還流回路を用いても良い。

【符号の説明】

【0057】

1・誘導性負荷駆動装置、100・制御回路、200・誘導性負荷駆動回路、300・プロセッサ、107・オペアンプ(差動増幅器)、108・サンプルスイッチ、109・遅延回路、119・外付け端子、203・第1のスイッチング素子、204・第2のスイッチング素子、205・第3のスイッチング素子(還流回路)、206・回生ダイオード(逆起電流回生回路)、207・シャント抵抗、Cd・コンデンサ、Ch・ホールドコンデンサ

【技術分野】

【0001】

本発明は、誘導性負荷駆動装置に関する。

【背景技術】

【0002】

下記特許文献1には、誘導性負荷の一端と外部供給電源との間に介挿された第1のスイッチング素子と、誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、第1のスイッチング素子がオフ及び第2のスイッチング素子がオンの時に誘導性負荷に生じる逆起電流をアースを介して誘導性負荷に還流させる還流回路と、第1及び第2のスイッチング素子の両方がオフの時に誘導性負荷に生じる逆起電流を外部供給電源に還元(回生)させる逆起電流還元回路とを備えた誘導性負荷駆動装置が開示されている。

【0003】

このような構成の誘導性負荷駆動装置では、第2のスイッチング素子をオン状態に維持しながら第1のスイッチング素子のオン/オフ期間の比率(デューティ比)を制御することにより、負荷電流の立上がり特性を制御することができる。また、第1のスイッチング素子をオフ状態に維持しながら第2のスイッチング素子のデューティ比を制御することにより、負荷電流の立下がり特性を制御しながら誘導性負荷に生じる逆起電流を外部供給電源に回生させることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−85046号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記特許文献1には明記されていないが、誘導性負荷に流れる負荷電流の波形を任意に制御する手法として、第2のスイッチング素子とアース間にシャント抵抗を設け、このシャント抵抗の端子間電圧をサンプルホールド回路によってサンプリングし、そのサンプリング値(つまり負荷電流値)をスイッチング制御を行うマイコンにフィードバックする手法が挙げられる。

【0006】

上記特許文献1の技術では、第1のスイッチング素子をオフ状態に維持しながら第2のスイッチング素子のデューティ比を制御する期間(負荷電流の立下り波形を制御する期間)において、第2のスイッチング素子がオンの時、負荷電流は、誘導性負荷→第2のスイッチング素子→アース→還流回路→誘導性負荷、というルート(電流還流ルート)で流れ、第2のスイッチング素子がオフの時、負荷電流は、アース→還流回路→誘導性負荷→逆起電流還元回路→外部供給電源、というルート(電流回生ルート)で流れる。

【0007】

そのため、負荷電流の立下り波形を制御する期間に負荷電流値をサンプリングするには、電流還流ルートで負荷電流が流れる期間にサンプルホールド回路のサンプルスイッチをオンにしてシャント抵抗の端子間電圧をサンプリングし、電流回生ルートで負荷電流が流れる期間にサンプルスイッチをオフにしてシャント抵抗の端子間電圧をホールドする(ホールドコンデンサに電荷を保持する)必要がある。

【0008】

ここで、電流回生ルートから電流還流ルートへ切替える時、つまり第2のスイッチング素子をオフからオンに切替える時に、回路的な要因によってサンプリングタイミング(サンプルスイッチのオンタイミング)から遅れて第2のスイッチング素子がオンに切替わると、ホールドコンデンサの電荷抜けが発生してしまい、電流値サンプリングの追従性が低下する(電流検出精度が低下する)という問題がある。

【0009】

本発明は、上述した事情に鑑みてなされたものであり、電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記目的を達成するために、本発明では、誘導性負荷駆動装置に係る第1の解決手段として、電源と誘導性負荷の一端との間に介挿された第1のスイッチング素子と、前記誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、前記第1のスイッチング素子がオフ及び前記第2のスイッチング素子がオンの時に前記誘導性負荷の他端から出力される逆起電流を、前記アースを介して前記誘導性負荷の一端へ還流させる還流回路と、前記第1及び第2のスイッチング素子の両方がオフの時に前記誘導性負荷の他端から出力される逆起電流を前記電源に回生させる逆起電流回生回路と、前記第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から前記誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、2つの入力端子が前記シャント抵抗の両端に接続された差動増幅器と、前記第1及び第2のスイッチング素子を制御するプロセッサと前記差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、前記プロセッサから前記第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後に前記サンプルスイッチをオンにさせる遅延回路とを備える、という手段を採用する。

【0011】

また、本発明では、誘導性負荷駆動装置に係る第2の解決手段として、上記第1の解決手段において、前記遅延回路は、前記プロセッサから前記第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから、コンデンサの容量で定まる遅延時間の経過後に前記サンプルスイッチをオンにさせる、という手段を採用する。

【0012】

また、本発明では、誘導性負荷駆動装置に係る第3の解決手段として、上記第2の解決手段において、前記遅延回路と前記コンデンサを外付けするために用いられる外付け端子と、前記外付け端子に接続された外付けコンデンサとを備える、という手段を採用する。

【発明の効果】

【0013】

本発明によれば、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせるので、回路的な要因によって制御信号がオンレベルに遷移してから第2のスイッチング素子が実際にオンに切替わるタイミングが遅れたとしても、サンプリングタイミングと第2のスイッチング素子のオンタイミングとを一致させることができ、その結果、電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現できる。

【図面の簡単な説明】

【0014】

【図1】本実施形態に係る誘導性負荷駆動装置1の概略構成図である。

【図2】制御回路100に設けられた遅延回路109の詳細な回路構成を示す図である。

【図3】制御回路100から誘導負荷駆動回路200へ出力される第1の制御信号S1、第2の制御信号S2及び第3の制御信号S3と、誘導性負荷Lに流れる駆動電流との時間的な対応関係を示すタイミングチャートである。

【図4】本実施形態の効果(電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサChの電荷抜け抑制効果)を示す図である。

【発明を実施するための形態】

【0015】

以下、本発明の一実施形態について、図面を参照しながら説明する。

図1は、本実施形態に係る誘導性負荷駆動装置1の概略構成図である。この図1に示すように、誘導性負荷駆動装置1は、制御回路100、誘導性負荷駆動回路200及び例えばCPU等のプロセッサ300を備えている。誘導性負荷駆動回路200は、プロセッサ300による制御の下、ソレノイドコイル或いはモータコイル等の誘導性負荷Lに駆動電流を供給するものであり、誘導性負荷Lの一端に接続された第1の負荷接続端子201と、誘導性負荷Lの他端に接続された第2の負荷接続端子202と、第1のスイッチング素子203と、第2のスイッチング素子204と、第3のスイッチング素子205と、回生ダイオード206と、シャント抵抗207とを備えている。

【0016】

第1のスイッチング素子203は、比較的高い電源電圧(例えば30V)が印加された電源PL1と第1の負荷接続端子201(つまり誘導性負荷Lの一端)との間に介挿されたn型MOS−FETであり、ドレイン端子が電源PL1に接続され、ソース端子が第1の負荷接続端子201に接続され、ゲート端子が制御回路100(第1の制御信号出力端子113)に接続されている。この第1のスイッチング素子203は、プロセッサ300から制御回路100を介して入力される第1の制御信号(パルス幅変調された信号)S1に応じてオン/オフ状態が切替わる。

【0017】

第2のスイッチング素子204は、第2の負荷接続端子202(つまり誘導性負荷Lの他端)とアースとの間に介挿されたn型MOS−FETであり、ドレイン端子が第2の負荷接続端子202に接続され、ソース端子がシャント抵抗207を介してアースに接続され、ゲート端子が制御回路100(第2の制御信号出力端子114)に接続されている。この第2のスイッチング素子204は、プロセッサ300から制御回路100を介して入力される第2の制御信号S2に応じてオン/オフ状態が切替わる。

【0018】

第3のスイッチング素子205は、第1の負荷接続端子201(つまり誘導性負荷Lの一端)とアースとの間に介挿され、第1のスイッチング素子203に対してオンオフ状態が反転するように制御されるn型MOS−FETであり、ドレイン端子が第1の負荷接続端子201に接続され、ソース端子がアースに接続され、ゲート端子が制御回路100(第3の制御信号出力端子115)に接続されている。

【0019】

この第3のスイッチング素子205は、制御回路100から入力される第3の制御信号S3(第1の制御信号S1に対してレベルが反転する信号)に応じてオン/オフ状態が切替わる。なお、この第3のスイッチング素子205は、第1のスイッチング素子203がオフ且つ第2のスイッチング素子204がオンの時に誘導性負荷Lの他端から出力される逆起電流を、アースを介して誘導性負荷Lの一端へ還流させる還流回路として設けられたものである。

【0020】

回生ダイオード206は、アノード端子が第2の負荷接続端子202に接続され、カソード端子が電源PL1に接続されている。この回生ダイオード206は、第1及び第2のスイッチング素子203、204の両方がオフの時に誘導性負荷Lの他端から出力される逆起電流を電源PL1に回生させる逆起電流回生回路として設けられたものである。シャント抵抗207は、制御回路100によって誘導性負荷Lに流れる駆動電流を検出するために用いられる抵抗素子であり、一端が第2のスイッチング素子204のソース端子に接続され、他端がアースに接続されている。

【0021】

一方、制御回路100は、上述した誘導性負荷駆動回路200から誘導性負荷Lに供給される駆動電流を検出するカスタムICであり、第1の入力回路101と、第2の入力回路102と、第1の出力回路103と、第2の出力回路104と、第1のインバータ105と、第3の出力回路106と、オペアンプ107と、サンプルスイッチ108と、遅延回路109とを備えている。

【0022】

また、この制御回路100は、プロセッサ300から第1の制御信号S1を入力するための第1の制御信号入力端子111と、プロセッサ300から第2の制御信号S2を入力するための第2の制御信号入力端子112と、第1のスイッチング素子203のゲート端子に接続された第1の制御信号出力端子113と、第2のスイッチング素子204のゲート端子に接続された第2の制御信号出力端子114と、第3のスイッチング素子205のゲート端子に接続された第3の制御信号出力端子115と、シャント抵抗207の一端に接続された第1の抵抗接続端子116と、シャント抵抗207の他端に接続された第2の抵抗接続端子117と、プロセッサ300のA/D入力ポートに接続されると共にホールドコンデンサChが接続されたサンプル出力端子118と、コンデンサCdを外付けするために用いられる外付け端子119とを備えている。

【0023】

プロセッサ300から第1の制御信号入力端子111に入力された第1の制御信号S1は、第1の入力回路101及び第1の出力回路103を通過した後、第1の制御信号出力端子113を介して第1のスイッチング素子203に出力される。一方、プロセッサ300から第2の制御信号入力端子112に入力された第2の制御信号S2は、第2の入力回路102及び第2の出力回路104を通過した後、第2の制御信号出力端子114を介して第2のスイッチング素子204に出力される。

【0024】

また、第1の制御信号S1は、第1の入力回路101から分岐して第1のインバータ105に入力される。第1のインバータ105は、第1の入力回路101から入力された第1の制御信号S1のレベルを反転させ、レベル反転後の第1の制御信号S1を第3の制御信号S3として第3の出力回路106に出力する。第3の制御信号S3は、第3の出力回路106を通過した後、第3の制御信号出力端子115を介して第3のスイッチング素子205に出力される。

【0025】

なお、第1の入力回路101及び第2の入力回路102は、例えばプルダウン抵抗やシュミット回路等から構成されており、第1の出力回路103、第2の出力回路104及び第3の出力回路106は、例えばレベルシフタや出力バッファ等から構成されている。

【0026】

オペアンプ107は、非反転入力端子が第1の抵抗接続端子116(つまりシャント抵抗207の一端)に接続され、反転入力端子が第2の抵抗接続端子117(つまりシャント抵抗207の他端)に接続された差動増幅器であり、シャント抵抗207の端子間電圧を増幅して出力する。

【0027】

サンプルスイッチ108は、オペアンプ107の出力端子とプロセッサ300とを結ぶ配線(より詳細にはオペアンプ107の出力端子とサンプル出力端子118とを結ぶ配線)に介挿されたサンプル・ホールド用のスイッチング素子であり、後述の遅延回路109から入力されるサンプルタイミング信号S4に応じてオン/オフ状態が切替わる。

【0028】

遅延回路109は、第2の入力回路102から分岐した第2の制御信号S2が入力されており、この第2の制御信号S2がオンレベル(本実施形態ではハイレベル)に遷移してから、外付け端子119に外付けされたコンデンサCdの容量で定まる遅延時間の経過後にサンプルスイッチ108をオンにさせるためのサンプルタイミング信号S4をサンプルスイッチ108に出力する。

【0029】

詳細には、遅延回路109は、図2に示すように、第2のインバータ121と、例えばn型MOS−FETである制御用スイッチング素子122と、定電流源123と、抵抗素子124と、コンパレータ125とを備えている。第2のインバータ121は、第2の入力回路102から入力される第2の制御信号S2のレベルを反転させて制御用スイッチング素子122のゲート端子に出力するレベル反転回路である。

【0030】

制御用スイッチング素子122は、ドレイン端子が定電流源123を介して低電圧(例えば3.3V)の電源PL2に接続され、ソース端子がアースに接続され、ゲート端子が第2のインバータ121の出力端子に接続されており、第2のインバータ121から入力されるレベル反転後の第2の制御信号S2に応じてオン/オフ状態が切替わる。定電流源123は、定電流を発生するものであり、一端が電源PL2に接続され、他端が制御用スイッチング素子122のドレイン端子に接続されている。

【0031】

抵抗素子124は、一端が定電流源123の他端に接続され、他端がコンデンサCdを外付けするための外付け端子119に接続されている。コンパレータ125は、非反転入力端子が定電流源123の他端に接続されており、非反転入力端子に印加される参照電圧V1が、反転入力端子に印加される基準電圧Vref以上となった時にサンプルスイッチ108をオンにさせるためのオンレベル(ハイレベル)のサンプルタイミング信号S4を出力し、参照電圧V1が基準電圧Vref未満となった時にサンプルスイッチ108をオフにさせるためのオフレベル(ローレベル)のサンプルタイミング信号S4を出力する。

【0032】

このような構成の遅延回路109によれば、第2の制御信号S2がハイレベルに遷移すると、制御用スイッチング素子122がオフとなり、外付けされたコンデンサCdに電荷が充電され始める。そして、コンデンサCdの充電に伴って、コンパレータ125の非反転入力端子に印加される参照電圧V1が上昇し、参照電圧V1が基準電圧Vref以上となった時点でコンパレータ125の出力であるサンプルタイミング信号S4がハイレベルに切替わる。

【0033】

一方、第2の制御信号S2がローレベルに遷移すると、制御用スイッチング素子122がオンとなり、コンデンサCdに貯まっていた電荷がアースに放電され始める。そして、コンデンサCdの放電に伴って、コンパレータ125の非反転入力端子に印加される参照電圧V1が下降し、参照電圧V1が基準電圧Vref未満となった時点でサンプルタイミング信号S4がローレベルに切替わる。

【0034】

このように、本実施形態の遅延回路109を採用することにより、第2の制御信号S2がハイレベルに遷移してから、外付け端子119に外付けされたコンデンサCdの容量で定まる遅延時間(参照電圧V1が上昇を開始してから基準電圧Vref以上となるまでの時間)の経過後にサンプルスイッチ108をオンに切替えることができる。

【0035】

なお、プロセッサ300は、A/D入力ポートへの入力電圧をA/D変換することでシャント抵抗207の端子間電圧を検知すると共に、このシャント抵抗207の端子間電圧を駆動電流値に換算し、その駆動電流値が目標値と一致するように第1及び第2のスイッチング素子203、204のフィードバック制御(第1及び第2の制御信号S1、S2のデューティ比制御)を行う。

【0036】

次に、上記のように構成された誘導性負荷駆動装置1の動作について図3を参照しながら詳細に説明する。

図3は、制御回路100から誘導負荷駆動回路200へ出力される第1の制御信号S1、第2の制御信号S2及び第3の制御信号S3と、誘導性負荷Lに流れる駆動電流との時間的な対応関係を示すタイミングチャートである。

【0037】

この図3に示すように、時刻t1から時刻t2までの期間において、所定のデューティ比を有し、互いにレベルが反転するパルス状の第1の制御信号S1及び第3の制御信号S3と、オンレベル(ハイレベル)一定の第2の制御信号S2が制御回路100から誘導負荷駆動回路200へ出力される。つまり、時刻t1から時刻t2までの期間では、第2のスイッチング素子204がオン状態に維持されながら、第1のスイッチング素子203及び第3のスイッチング素子205が、所定のデューティ比でオン/オフ制御される。なお、第3のスイッチング素子205のオン/オフ状態は、第1のスイッチング素子203に対して反転していることに注意されたい。

【0038】

このような時刻t1から時刻t2までの期間において、第1のスイッチング素子203がオン及び第3のスイッチング素子205がオフの時、誘導性負荷Lの一端は第1のスイッチング素子203を介して電源PL1に接続され、誘導性負荷Lの他端は第2のスイッチング素子204を介してアースに接続される。この時、誘導性負荷Lに電源電圧(約30V)が印加されるため、誘導性負荷Lに流れる駆動電流は一定の傾きで増加する。なお、この時の駆動電流は、電源PL1→第1のスイッチング素子203→誘導性負荷L→第2のスイッチング素子204→アース、というルート(負荷通電ルート)で流れる。

【0039】

一方、時刻t1から時刻t2までの期間において、第1のスイッチング素子203がオフ及び第3のスイッチング素子205がオンの時、誘導性負荷Lの一端は第3のスイッチング素子205を介してアースに接続される(誘導性負荷Lの他端は第2のスイッチング素子204を介してアースに接続されたまま)。この時、誘導性負荷Lに電源電圧が印加されないので、誘導性負荷Lに逆起電圧が発生し、誘導性負荷Lの他端から逆起電流が出力される。

【0040】

この逆起電流は、第2のスイッチング素子204を介してアースに流入し、さらに第3のスイッチング素子205を介して誘導性負荷Lの一端に還流する。つまり、駆動電流は、誘導性負荷L→第2のスイッチング素子204→アース→第3のスイッチング素子205→誘導性負荷L、というルート(電流還流ルート)で流れる。これにより、第1のスイッチング素子203がオフとなっても、誘導性負荷Lの駆動電流は一定に保持される(厳密には減少するが無視できる)。

【0041】

このように、時刻t1から時刻t2までの期間において、第2のスイッチング素子204をオン状態に維持しながら、互いにオン/オフ状態が反転するように第1のスイッチング素子203及び第3のスイッチング素子205をPWM制御またはオン/オフ制御することにより、誘導性負荷Lに流れる駆動電流の立上がり特性を制御することができる。

【0042】

なお、このような時刻t1から時刻t2までの期間(第2の制御信号S2が常時ハイレベルの期間)では、遅延回路109から常時ハイレベルのサンプルタイミング信号S4が出力されるため、サンプルスイッチ108も常時オンとなり、オペアンプ107からプロセッサ300のA/D入力ポートへシャント抵抗207の端子間電圧が常時入力され続ける。つまり、プロセッサ300は、時刻t1から時刻t2までの期間において、第2の制御信号S2を常時ハイレベルに維持すると共に、シャント抵抗207の端子間電圧から換算した駆動電流値が目標値と一致するように第1のスイッチング素子203のフィードバック制御(第1の制御信号S1のデューティ比制御)を行っている。

【0043】

続いて、時刻t2から時刻t3までの期間において、ハイレベル一定の第1の制御信号S1と、ハイレベル一定の第3の制御信号S3と、所定のデューティ比を有するパルス状の第2の制御信号S2とが制御回路100から誘導負荷駆動回路200へ出力される。つまり、時刻t2から時刻t3までの期間では、第1のスイッチング素子203がオフ状態且つ第3のスイッチング素子205がオン状態に維持されながら、第2のスイッチング素子204が所定のデューティ比でオン/オフ制御される。

【0044】

このような時刻t2から時刻t3までの期間において、第2のスイッチング素子204がオフの時、誘導性負荷Lの一端は第3のスイッチング素子205を介してアースに接続され、誘導性負荷Lの他端は回生ダイオード206を介して電源PL1に接続される。この時、誘導性負荷Lに電源電圧が印加されないので、誘導性負荷Lに逆起電圧が生じる。

【0045】

この逆起電圧が電源電圧より大きくなると、回生ダイオード206を介して誘導性負荷Lの他端から電源PL1に逆起電流が回生される。つまり、誘導性負荷Lに流れる駆動電流は、アース→第3のスイッチング素子205→誘導性負荷L→回生ダイオード206→電源PL1、というルート(電流回生ルート)で流れる。これにより、誘導性負荷Lの駆動電流は一定の傾きで減少する。

【0046】

一方、時刻t2から時刻t3までの期間において、第2のスイッチング素子204がオンの時、誘導性負荷Lの他端は第2のスイッチング素子204を介してアースに接続される(誘導性負荷Lの一端は第3のスイッチング素子205を介してアースに接続されたまま)。この時、誘導性負荷Lに電源電圧が印加されないため、誘導性負荷Lに逆起電圧が発生し、誘導性負荷Lの他端から逆起電流が第2のスイッチング素子205を介してアースに流入し、さらに第3のスイッチング素子205を介して誘導性負荷Lの一端に還流する(電流還流ルートで駆動電流が流れる)。これにより、駆動電流は一定に保持される(厳密には減少するが無視できる)。

【0047】

このように、時刻t2から時刻t3までの期間において、第1のスイッチング素子203をオフ状態且つ第3のスイッチング素子205をオン状態に維持しながら、第2のスイッチング素子204をPWM制御することにより、誘導性負荷Lに流れる駆動電流の立下がり特性を制御することができる。

【0048】

このような時刻t2から時刻t3までの期間(駆動電流の立下り波形を制御する期間)においては、電流還流ルートで駆動電流が流れる期間(第2のスイッチング素子204がオンの期間)と、電流回生ルートで駆動電流が流れる期間(第2のスイッチング素子204がオフの期間)とが交互に現れる。

【0049】

そのため、駆動電流の立下り波形を制御する期間に駆動電流値をサンプリングするには、電流還流ルートで駆動電流が流れる期間にサンプルスイッチ108をオンにしてシャント抵抗207の端子間電圧をサンプリングし、電流回生ルートで駆動電流が流れる期間にサンプルスイッチ108をオフにしてシャント抵抗207の端子間電圧をホールドする(ホールドコンデンサChに電荷を保持する)必要がある。

【0050】

ここで、従来では、図4(a)に示すように、電流回生ルートから電流還流ルートへ切替える時、つまり第2のスイッチング素子204をオフからオンに切替える時に、回路的な要因によってサンプリングタイミング(サンプルスイッチ108のオンタイミング)から遅れて第2のスイッチング素子204がオンに切替わると、ホールドコンデンサChの電荷抜けが発生してしまい、電流値サンプリングの追従性が低下する(電流検出精度が低下する)という問題があった。

【0051】

これに対して、本実施形態における遅延回路109は、上述したように、第2の制御信号S2がハイレベルに遷移してから、外付け端子119に外付けされたコンデンサCdの容量で定まる遅延時間の経過後にハイレベルのサンプルタイミング信号S4を出力して、サンプルスイッチ108をオンに切替えることができる。

【0052】

つまり、コンデンサCdの容量を調整して、第2の制御信号S2がハイレベルに遷移してからサンプルタイミング信号S4がハイレベルに切替わるまでの遅延時間を、第2の制御信号S2がハイレベルに遷移してから実際に第2のスイッチング素子204がオンに切替わるまでの遅延時間と一致させることにより、図4(b)に示すように、サンプリングタイミング(サンプルスイッチ108のオンタイミング)と第2のスイッチング素子204のオンタイミングとを一致させることができる。

【0053】

以上のように、本実施形態によれば、回路的な要因によって第2の制御信号S2がハイレベルに遷移してから第2のスイッチング素子204が実際にオンに切替わるタイミングが遅れたとしても、サンプリングタイミングと第2のスイッチング素子204のオンタイミングとを一致させることができ、その結果、電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサChの電荷抜けを抑制して電流検出精度の向上を実現することができる。

【0054】

なお、本発明は上記実施形態に限定されず、以下のような変形例が挙げられる。

(1)上記実施形態では、遅延回路109の具体例として図2に示すような回路構成を挙げたが、第2のスイッチング素子204に出力される第2の制御信号S2がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチ108をオンにさせることができれば、どのような回路構成を採用しても良い。

また、必ずしもコンデンサCdを外付けとする必要はなく、予め遅延回路109の内部に容量を最適化したコンデンサCdを設けておく構成を採用しても良い。また、ホールドコンデンサChを制御回路100の内部に設けておく構成を採用しても良い。

【0055】

(2)上記実施形態では、回生ダイオード206からなる逆起電流回生回路を例示したが、第1及び第2のスイッチング素子203、204の両方がオフの時に誘導性負荷Lの他端から出力される逆起電流を電源PL1に回生させることができれば、逆起電流回生回路の構成はこれに限定されない。例えば、特開2008−85046号公報に記載されているような逆起電流還元回路(逆起電流回生回路と同義)を用いても良い。

【0056】

(3)上記実施形態では、第3のスイッチング素子205からなる還流回路を例示したが、第1のスイッチング素子203がオフ及び第2のスイッチング素子204がオンの時に誘導性負荷Lの他端から出力される逆起電流を、アースを介して誘導性負荷Lの一端へ還流させることができれば、還流回路の構成はこれに限定されない。例えば、特開2008−85046号公報に記載されているような還流回路を用いても良い。

【符号の説明】

【0057】

1・誘導性負荷駆動装置、100・制御回路、200・誘導性負荷駆動回路、300・プロセッサ、107・オペアンプ(差動増幅器)、108・サンプルスイッチ、109・遅延回路、119・外付け端子、203・第1のスイッチング素子、204・第2のスイッチング素子、205・第3のスイッチング素子(還流回路)、206・回生ダイオード(逆起電流回生回路)、207・シャント抵抗、Cd・コンデンサ、Ch・ホールドコンデンサ

【特許請求の範囲】

【請求項1】

電源と誘導性負荷の一端との間に介挿された第1のスイッチング素子と、

前記誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、

前記第1のスイッチング素子がオフ及び前記第2のスイッチング素子がオンの時に前記誘導性負荷の他端から出力される逆起電流を、前記アースを介して前記誘導性負荷の一端へ還流させる還流回路と、

前記第1及び第2のスイッチング素子の両方がオフの時に前記誘導性負荷の他端から出力される逆起電流を前記電源に回生させる逆起電流回生回路と、

前記第2のスイッチング素子とアースとの間に介挿されたシャント抵抗と、

を備えた誘導性負荷駆動回路から前記誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、

2つの入力端子が前記シャント抵抗の両端に接続された差動増幅器と、

前記第1及び第2のスイッチング素子を制御するプロセッサと前記差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、

前記プロセッサから前記第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後に前記サンプルスイッチをオンにさせる遅延回路と、

を備えることを特徴とする誘導性負荷駆動装置。

【請求項2】

前記遅延回路は、前記プロセッサから前記第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから、コンデンサの容量で定まる遅延時間の経過後に前記サンプルスイッチをオンにさせることを特徴とする請求項1に記載の誘導性負荷駆動装置。

【請求項3】

前記遅延回路と前記コンデンサを外付けするために用いられる外付け端子と、

前記外付け端子に接続された外付けコンデンサとを備えることを特徴とする請求項2に記載の誘導性負荷駆動装置。

【請求項1】

電源と誘導性負荷の一端との間に介挿された第1のスイッチング素子と、

前記誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、

前記第1のスイッチング素子がオフ及び前記第2のスイッチング素子がオンの時に前記誘導性負荷の他端から出力される逆起電流を、前記アースを介して前記誘導性負荷の一端へ還流させる還流回路と、

前記第1及び第2のスイッチング素子の両方がオフの時に前記誘導性負荷の他端から出力される逆起電流を前記電源に回生させる逆起電流回生回路と、

前記第2のスイッチング素子とアースとの間に介挿されたシャント抵抗と、

を備えた誘導性負荷駆動回路から前記誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、

2つの入力端子が前記シャント抵抗の両端に接続された差動増幅器と、

前記第1及び第2のスイッチング素子を制御するプロセッサと前記差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、

前記プロセッサから前記第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後に前記サンプルスイッチをオンにさせる遅延回路と、

を備えることを特徴とする誘導性負荷駆動装置。

【請求項2】

前記遅延回路は、前記プロセッサから前記第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから、コンデンサの容量で定まる遅延時間の経過後に前記サンプルスイッチをオンにさせることを特徴とする請求項1に記載の誘導性負荷駆動装置。

【請求項3】

前記遅延回路と前記コンデンサを外付けするために用いられる外付け端子と、

前記外付け端子に接続された外付けコンデンサとを備えることを特徴とする請求項2に記載の誘導性負荷駆動装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−93669(P2013−93669A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−233117(P2011−233117)

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000141901)株式会社ケーヒン (1,140)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000141901)株式会社ケーヒン (1,140)

【Fターム(参考)】

[ Back to top ]