誤り検出回路及び集積回路

【課題】メモリ等の入力対象に入力される信号の誤判定を行うのに好適な誤り検出回路を提供する。

【解決手段】集積回路1を、誤り検出回路2A〜2Cとメモリ回路3とを含み、誤り検出回路2A〜2Cを、クロック信号CKの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第1信号IN_A0〜IN_Anを出力するラッチ回路21A0〜21Anと、クロック信号CKを遅延時間t1だけ遅延させる遅延回路20Aと、遅延クロック信号CK_Aの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第2信号IN_B0〜IN_Bnを出力するラッチ回路21B0〜21Bnと、第1信号IN_A0〜IN_Anと第2信号IN_B0〜IN_Bnとが一致しているか否かを比較判定し、判定結果を示す第3信号COMP0〜COMPnを出力する比較回路24_0〜24_nとを含む構成とした。

【解決手段】集積回路1を、誤り検出回路2A〜2Cとメモリ回路3とを含み、誤り検出回路2A〜2Cを、クロック信号CKの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第1信号IN_A0〜IN_Anを出力するラッチ回路21A0〜21Anと、クロック信号CKを遅延時間t1だけ遅延させる遅延回路20Aと、遅延クロック信号CK_Aの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第2信号IN_B0〜IN_Bnを出力するラッチ回路21B0〜21Bnと、第1信号IN_A0〜IN_Anと第2信号IN_B0〜IN_Bnとが一致しているか否かを比較判定し、判定結果を示す第3信号COMP0〜COMPnを出力する比較回路24_0〜24_nとを含む構成とした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力対象に入力される信号の誤りを検出する誤り検出回路に関する。

【背景技術】

【0002】

従来、SRAM(Static Random Access Memory)などのメモリを内蔵する集積回路において、メモリにデータを書き込む際や、メモリに格納されたデータを読み出す際に、メモリへの入力信号やメモリからの出力信号が、ノイズによって変化する恐れがあった。ここで、ノイズとしては、P&Rツールを用いた自動配置配線が要因のクロストークノイズや、トランジスタの高集積化が要因のスイッチングノイズなどが挙げられる。

【0003】

このようなノイズ等による信号の変化は、誤ったデータのメモリへの格納や、誤ったデータ信号の出力による後段のシステムの誤動作などを引き起こす恐れがある。

この問題に対して、信号の誤りを検出する技術として、例えば、特許文献1のメモリの異常動作検出回路、特許文献2の誤動作防止用外部メモリインターフェース回路などが開示されている。

【0004】

特許文献1の技術では、メモリの出力データを所定時間遅延して、遅延データを出力し、この遅延データとメモリの出力データとを比較して、不一致の場合に不一致信号を出力することで出力データの誤りを検出している。

また、特許文献2の技術では、外部メモリから出力されたデータをクロックを用いてサンプリングするデータ入力同期回路が、少なくとも2回連続して同じデータをサンプリングしたときにそのデータを有効なデータと判定している。つまり、2回連続して同じデータをサンプリングできなかったときに出力データに誤りがあると判定している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−62389号公報

【特許文献2】特開2005−78209号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記特許文献1及び特許文献2の技術は、いずれもメモリから出力されるデータ信号について誤判定を行うものであり、メモリに入力されるデータ信号については誤判定を行っていない。そのため、ノイズ等の影響によって入力信号が変化した場合に、誤ったデータがメモリに保持されるのを防ぐことは困難であった。

そこで、本発明の目的の一つは、メモリ等の入力対象に入力される信号の誤判定を行うのに好適な誤り検出回路を提供することにある。

なお、前記目的に限らず、後述する発明を実施するための形態に示す各構成により導かれる作用効果であって、従来の技術によっては得られない作用効果を奏することも本発明の他の目的の一つとして位置付けることができる。

【課題を解決するための手段】

【0007】

〔形態1〕 上記目的を達成するために、形態1の誤り検出回路は、入力対象に入力する入力信号の状態を、第1クロック信号のエッジに基づく第1のタイミングで保持し、保持した状態を示す第1信号を出力する第1のラッチ回路と、

前記入力信号の状態を、第2クロック信号のエッジに基づく第2のタイミングで保持し、保持した状態を示す第2信号を出力する第2のラッチ回路と、

前記第1信号と前記第2信号とを比較して、比較結果に基づき両者が一致しているか否かを示す第3信号を出力する比較回路と、を備え、

前記第2のタイミングは、前記第1のタイミングから所定時間遅延したタイミングである。

【0008】

このような構成であれば、上記第1のタイミング又は上記第2のタイミングにおいてノイズ等が原因で入力信号が変化した場合に、第1信号と第2信号とが異なる状態となるため、比較回路において、第1信号と第2信号とが不一致であることを示す第3信号が出力される。

これにより、第1のラッチ回路の出力する第1信号を入力対象の入力信号として入力する構成とすることで、入力対象に入力される入力信号にノイズ等が原因で誤りが生じているか否かを検出することができる。

【0009】

また、第3信号が不一致を示す場合に、入力信号の発信元に対して第3信号を渡すなどすることで、発信元に入力信号の再送を行わせることができる。これにより、入力信号の誤りが原因で、入力対象が誤動作したり、入力対象から誤ったデータ信号が後段のシステムに出力されたりするのを未然に防ぐことができる。

また、入力対象がメモリ回路である場合は、誤ったデータが記憶されるのを防ぐことができる。

ここで、第1のラッチ回路及び第2のラッチ回路は、例えば、入力信号がデジタル信号である場合に、信号のHighレベル及びLowレベルの2状態を保持する。

【0010】

また、エッジに基づくタイミングとは、第1クロック及び第2クロックの立ち上がりエッジ又は立ち下がりエッジに基づくタイミングである。そして、第1のラッチ回路が第1クロックの立ち上がりエッジに基づき状態を保持する場合は、第2のラッチ回路も第2クロックの立ち上がりエッジに基づき状態を保持する。また、第1のラッチ回路が第1クロックの立ち下がりエッジに基づき状態を保持する場合は、第2のラッチ回路も第2クロックの立ち下がりエッジに基づき状態を保持する。なお、保持する条件(2状態を判断する電圧閾値等)は、第1のラッチ回路及び第2のラッチ回路で同じ条件とすることが望ましい。

【0011】

〔形態2〕 更に、形態2の誤り検出回路は、形態の1の誤り検出回路において、前記第1クロック信号と前記第2クロック信号とは同一のクロック信号である。

このような構成であれば、同一のクロック信号をそのまま第1のラッチ回路に供給し、同一のクロック信号を所定時間遅延させたクロック信号を第2のラッチ回路に供給することで、第1のタイミングと第2のタイミングとを簡易に生成することができる。

【0012】

〔形態3〕 また、上記目的を達成するために、形態3の誤り検出回路は、複数の前記入力信号に対応する複数の形態1又は2に記載の誤り検出回路と、

前記複数の誤り検出回路の各比較回路から出力される前記第3信号に基づき、前記入力信号の誤りの有無を示す誤り検出信号を出力する出力回路と、を備える。

このような構成であれば、出力回路によって、例えば、複数の第3信号のうち1つでも不一致となるものがあった場合に、誤りが有ることを示す誤り検出信号を出力するといったように厳密な誤り検出を行うことができる。また、複数の第3信号のうち所定数の不一致となるものがあった場合に誤りが有ることを示す誤り検出信号を出力するといったように、後段のシステムが必要とする精度に応じた誤り検出を行うこともできる。

【0013】

〔形態4〕 更に、形態4の誤り検出回路は、形態3の誤り検出回路において、前記第2クロック信号を所定時間遅延させた第3クロック信号のエッジに基づく第3のタイミングで、前記誤り検出信号の状態を保持し、保持した状態を示す第4の信号を出力する第3のラッチ回路を備える。

このような構成であれば、第1クロックと第2クロックとの遅延期間において、意図しない状態を示す誤り検出信号が出力されるのを防ぐことができる。

【0014】

〔形態5〕 更に、形態5の誤り検出回路は、形態4の誤り検出回路において、前記第2のラッチ回路の前段において、前記入力信号と制御信号とを受信し、受信した制御信号に基づき、受信した入力信号又は前記受信した制御信号に対応する状態を示すテスト入力信号を前記第2のラッチ回路に出力するテスト回路を備える。

このような構成であれば、テスト回路によって、個々の誤り検出回路が正常に動作しているか否かを試験することができる。

【0015】

〔形態6〕 一方、上記目的を達成するために、形態6の集積回路は、形態3乃至5のいずれか1に記載の誤り検出回路と、

前記入力信号の入力対象であって、前記複数の誤り検出回路を介して受信した前記入力信号の状態に対応する情報を記憶するメモリ回路と、を備える。

このような構成であれば、上記形態3乃至5のいずれか1に記載の誤り検出回路と同等の作用及び効果を得ることができる。

【図面の簡単な説明】

【0016】

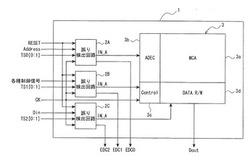

【図1】本発明に係る集積回路1の構成を示すブロック図である。

【図2】誤り検出回路2の詳細な構成を示すブロック図である。

【図3】ラッチ回路21の回路構成例を示す図である。

【図4】(a)は、テスト回路27_0〜27_2の回路構成例を示す図であり、(b)は、(a)のテスト回路27_0〜27_2の真理値表である。

【図5】第1のラッチタイミングで誤りが発生した場合のタイミングチャートの一例を示す図である。

【図6】第2のラッチタイミングで誤りが発生した場合のタイミングチャートの一例を示す図である。

【図7】ラッチ回路21Cを設けなかった場合のタイミングチャートの一例を示す図である。

【図8】図4(a)のテスト回路27を用いたテスト内容の具体例の一覧を示す図である。

【図9】ラッチ回路21Bとテスト回路27とを合成した合成回路例を示す図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施の形態を図面に基づき説明する。図1〜図8は、本発明に係る誤り検出回路及び集積回路の実施の形態を示す図である。

(集積回路の構成)

まず、本発明に係る集積回路の構成を図1に基づき説明する。図1は、本発明に係る集積回路1の構成を示すブロック図である。

集積回路1は、図1に示すように、誤り検出回路2A〜2Cと、メモリ回路3とを含んだ構成となっている。以下、本実施の形態では、メモリ回路3を、同期型SRAMの回路として説明する。

【0018】

誤り検出回路2Aは、外部ホスト装置(不図示)から入力された、メモリ回路3のアドレスを指定するアドレス信号(図1中のAddress)の誤りを検出する回路である。

誤り検出回路2Bは、外部ホスト装置から入力された、各種セレクト信号、各種イネーブル信号などのメモリ回路3を制御する各種制御信号の誤りを検出する回路である。

誤り検出回路2Cは、外部ホスト装置から入力された、メモリ回路3に記憶するデータのデータ信号(図1中のDin)の誤りを検出する回路である。

【0019】

メモリ回路3は、メモリ・セル・アレイ(図1中のMCA)3aと、アドレスデコーダー(図1中のADEC)3bと、制御部(図1中のControl)3cと、データR/W部(図1中のDATA R/W)3dとを含んで構成される。

MCA3aは、SRAMの回路構成を有したメモリセルが複数アレイ状に配列された構成を有している。ここで、SRAMのメモリセルの回路構成として、図示しないが、4つのMOSトランジスタと2つの高抵抗から構成される高抵抗負荷型、又は6つのMOSトランジスタで構成されるCMOS型などがある。

【0020】

ADEC3bは、図示しないが、行アドレス・バッファー、行アドレス・レジスター、行アドレス・デコーダー、列アドレス・バッファー、列アドレス・レジスター、列アドレス・デコーダー等を含んで構成される。そして、ADEC3bは、制御部3cからの制御信号に応じて、入力されたアドレス信号の示すアドレスに対応するメモリセルをデータ書込可能な状態又はデータ読出可能な状態となるアクティブ状態となるように駆動する。

制御部3cは、入力された各種制御信号に応じて、ADEC3bの動作、データR/W部3dの動作を制御する。

データR/W部3dは、不図示のデータコントロール部とセンスアンプとを含んで構成され、制御部3cからの制御信号に応じて、アクティブ状態のメモリセルへのデータの書き込み、アクティブ状態のメモリセルからのデータの読み出しを行う。

【0021】

(誤り検出回路の構成)

次に、図2に基づき、誤り検出回路2A〜2Cの詳細な構成について説明する。

ここで、図2は、誤り検出回路2の詳細な構成を示すブロック図である。なお、誤り検出回路2A〜2Cは、誤りを検出するデータの種類が異なるだけで、構成は同様となるので、これらを総称して誤り検出回路2として説明する。

誤り検出回路2は、図2に示すように、遅延回路20A及び20Bと、ラッチ回路21A0〜21An(nは1以上の自然数)と、ラッチ回路21B0〜21Bnと、比較回路24_0〜24_nと、OR回路25と、ラッチ回路21Cとを含んで構成される。

【0022】

遅延回路20Aは、入力されたクロック信号CKを所定時間t1(t1<th(クロック信号CKの1周期の期間))だけ遅延させて、この遅延させたクロック信号である遅延クロック信号CK_Aを出力する回路である。

遅延回路20Bは、入力されたクロック信号CKを所定時間t2(t1<t2<th)だけ遅延させて、この遅延させたクロック信号である遅延クロック信号XCK_Bを出力する回路である。

【0023】

ラッチ回路21A0は、クロック信号CKの立ち上がりエッジ又は立ち下がりエッジに基づく第1のラッチタイミングにおいて、入力信号IN0の状態(Highレベル又はLowレベル)を保持するようになっている。そして、保持した状態(Highレベル又はLowレベル)を示す信号(以下、第1信号IN_A0と称す)を、比較回路24_0及びメモリ回路3にそれぞれ出力するようになっている。

具体的に、メモリ回路3における第1信号IN_A0の出力先は、誤り検出回路2Aの場合はADEC3bとなり、誤り検出回路2Bの場合は制御部3cとなり、誤り検出回路2Cの場合はデータR/W部3dとなる。

【0024】

ラッチ回路21A1〜21Anも同様に、各々が、クロック信号CKの立ち上がりエッジ又は立ち下がりエッジに基づく第1のラッチタイミングにおいて、入力信号IN1〜INnのうち末尾の数字が同じ入力信号の状態を保持するようになっている。そして、保持した状態を示す信号(以下、第1信号IN_A1〜Anと称す)を、比較回路24_1〜24_nのうち末尾の数字が同じ比較回路及びメモリ回路3にそれぞれ出力するようになっている。

【0025】

なお、本実施の形態において、入力信号IN0〜INnは、それぞれnビットのデジタル信号の各ビットの信号である(例えば、IN0は0ビット目、INnはnビット目の信号となる)。また、本実施の形態において、入力信号IN0〜INnは、アドレス信号Address、各種制御信号、データ信号Din(MCA3aに書き込むデータの信号)のいずれかのデジタル信号の各ビットの信号となる。

ラッチ回路21B0は、遅延クロック信号CK_Aの立ち上がりエッジ又は立ち下がりエッジに基づく第2のラッチタイミングにおいて、入力信号IN0の状態を保持するようになっている。そして、保持した状態を示す信号(以下、第2信号IN_B0と称す)を、比較回路24_0に出力するようになっている。

【0026】

ラッチ回路21B1〜21Bnも同様に、各々が、遅延クロック信号CK_Aの立ち上がりエッジ又は立ち下がりエッジに基づく第2のラッチタイミングにおいて、入力信号IN1〜INnのうち末尾の数字が同じ入力信号の状態を保持するようになっている。そして、保持した状態を示す信号(以下、第2信号IN_B1〜Bnと称す)を、比較回路24_1〜24_nのうち末尾の数字が同じ比較回路に出力するようになっている。

【0027】

比較回路24_0は、ラッチ回路21A0から入力された第1信号IN_A0と、ラッチ回路21B0から入力された第2信号IN_B0とを比較して、両者が一致しているか否かを示す信号(以下、第3信号COMP0と称す)を出力するようになっている。

比較回路24_1〜24_nも同様に、各々が、ラッチ回路21A1〜21Anから入力された第1信号IN_A1〜IN_Anのうち末尾が同じ数字の第1信号と、ラッチ回路21B1〜21Bnから入力された第2信号IN_B1〜IN_Bnのうち末尾の数字が同じ第2信号とを比較して、両者が一致しているか否かを示す信号(以下、第3信号COPM1〜COMPnと称す)を出力するようになっている。

【0028】

本実施の形態では、比較回路24_0〜24_nは、第1信号と第2信号とが一致しているときにLowレベルの第3信号を出力し、不一致のときにHighレベルの第3信号を出力するようになっている。

例えば、上記第1のラッチタイミングで入力信号IN0がノイズ等によって誤った状態になり、この状態がラッチ回路21A0で保持され、上記第2のラッチタイミングで入力信号IN0が正常な状態でラッチ回路21B0で保持されたとする。この場合に、ラッチ回路21A0の第1信号IN_A0とラッチ回路21B0の第2信号IN_B0とは不一致となり、比較回路24_0からはHighレベルの第3信号COMP0が出力される。つまり、入力信号IN0に誤りがあることを検出することができる。

なお、遅延時間t1及びt2の遅延量を調整することによって、どの程度の幅のノイズまでを誤りとして検出するかを設定することができる。

【0029】

OR回路25は、比較回路21_0〜21_nから入力された第3信号COMP0〜COMPnを論理和した結果を示す信号(以下、第4信号EDC’と称す)を出力する。具体的に、第4信号EDC’は、第3信号COPM1〜COMPnのなかに1つでも不一致(Highレベル)の状態のものがあるときは、Highレベルの信号となり、第3信号COPM1〜COMPnが全て同じ状態(Lowレベルの状態)であるときは、Lowレベルの信号となる。つまり、入力信号IN0〜INnに1つでも誤りがあるときは、Highレベルの第4信号EDC’を出力する。

【0030】

ラッチ回路21Cは、遅延クロック信号CK_Bの立ち上がりエッジ又は立ち下がりエッジに基づく第3のタイミングにおいて、OR回路25から出力される第4信号EDC’の状態を保持するようになっている。そして、保持した状態を示す信号を誤り検出信号EDCとして出力するようになっている。

なお、図1に示すように、誤り検出回路2Aからは入力信号Addressの誤りの有無を示す誤り検出信号EDC0が、誤り検出回路2Bからは各種制御信号の誤りの有無を示す誤り検出信号EDC1が、誤り検出回路2Cからは、入力信号Dinの誤りの有無を示す誤り検出信号EDC2が出力される。

【0031】

図2に示すように、誤り検出回路2は、更に、TS回路27_0〜27_nを含んで構成される。

TS回路27_0〜27_nは、2ビットの制御信号TS0[0:1]〜TSn[0:1]に応じて、ラッチ回路21B1〜21Bnの出力信号を、強制的にHighレベル又はLowレベルに固定する機能を有する回路である。これにより、誤り検出回路の動作試験を行うことができる。なお、通常動作時は、第2のラッチタイミングで保持した入力信号IN0〜INnの状態を示す第2信号IN_B1〜IN_Bnをそのまま出力するように動作する。

【0032】

(ラッチ回路の構成)

次に、図3に基づき、ラッチ回路21A0〜21An、21B0〜21Bn及び21Cの回路構成を説明する。なお、本実施の形態において、これらラッチ回路の構成はいずれも同様となるので、これらを総称してラッチ回路21とし回路構成を説明する。

ここで、図3は、ラッチ回路21の回路構成例を示す図である。

ラッチ回路21は、図3に示すように、伝送ゲートT0〜T3(以下、単にT0〜T3という)と、NOTゲートN0〜N1(以下、単にN0〜N1という)とを含んで構成される。

【0033】

T0〜T3は、第1〜第3の入力端子と、出力端子とを有しており、第1及び第3の入力端子に入力される信号(図中のLAT、XLAT)の状態に応じて、第2の入力端子に入力される信号(図中のIN)を出力端子から出力する状態と、出力しない状態とのいずれか一方の状態に遷移する伝送ゲートである。

T0は、出力端子がT1の出力端子及びN0の入力端子と電気的に接続されており、第2の入力端子で入力信号INを負論理で受け、第3の入力端子で入力信号XLATを正論理で受け、第1の入力端子で入力信号LATを負論理で受けるようになっている。

【0034】

T1は、第2の入力端子がN0の出力端子と電気的に接続されており、出力端子がT0の出力端子とN0の入力端子とにそれぞれ電気的に接続されている。更に、T1は、第1の入力端子で入力信号LATを正論理で受け、第2の入力端子でN0の出力信号を負論理で受け、第3の入力端子で入力信号XLATを負論理で受けるようになっている。

T2は、第2の入力端子がN0の出力端子と電気的に接続され、出力端子がN1の入力端子とT3の出力端子とにそれぞれ電気的に接続されている。更に、T2は、第1の入力端子で入力信号LATを正論理で受け、第2の入力端子でN0の出力信号を負論理で受け、第3の入力端子で入力信号XLATを負論理で受けるようになっている。

【0035】

T3は、入力端子がN1の出力端子と電気的に接続され、出力端子がN1の入力端子とT2の出力端子とにそれぞれ電気的に接続されている。更に、T3は、第1の入力端子で入力信号LATを負論理で受け、第2の入力端子でN1の出力信号を負論理で受け、第3の入力端子で入力信号XLATを正論理で受けるようになっている。

N0は、負論理で信号を受け、正論理で信号を出力するNOTゲートであり、入力端子がT0の出力端子と電気的に接続され、出力端子がT1の第2の入力端子とT2の第2の入力端子とにそれぞれ電気的に接続されている。

N1は、負論理で信号を受け、正論理で信号を出力するNOTゲートであり、入力端子がT2の出力端子とT3の出力端子とにそれぞれ電気的に接続され、出力端子がT3の第2の入力端子と電気的に接続されている。

【0036】

そして、N0、T0及びT1から第1のラッチ回路が構成され、N1、T2及びT3から第2のラッチ回路が構成され、第1のラッチ回路と第2のラッチ回路とはT2を介して電気的に接続されている。

このような構成によって、ラッチ回路21は、入力信号LATの立ち上がりエッジのタイミングにおいて、入力信号INの状態(High又はLow)を保持し、その他のタイミングにおいて、前記保持したINの状態を示す信号を常時、出力信号OUTとして出力する。従って、入力信号INの変化によって、比較回路24、メモリ回路3等の後段の回路が意図しないタイミングで動いてしまい電流消費が増大することを防止することができる。また、入力信号INの変化によって、誤り検出信号EDCが一時的にHighとなってエラー出力となるのを防ぐことができる。

【0037】

なお、入力信号LATとXLATとは相互に反転した関係の信号であり、ラッチ回路21A0〜21Anの場合は、クロック信号CKとCKを反転させた信号XCKとなり、ラッチ回路21B0〜21Bnの場合は、遅延クロック信号CK_AとCK_Aを反転させた信号XCK_Aとなる。また、ラッチ回路21Cの場合は、遅延クロック信号XCK_BとXCK_Bを反転させた信号CK_Bとなる。

また、入力信号INは、検出回路2Aの場合は入力信号Addressに、検出回路2Bの場合は各種制御信号に、検出回路2Cの場合は入力信号Dinとなる。

また、入力信号INは、ラッチ回路21Cの場合は、検出回路2A〜2CのいずれもOR回路25から出力される第4信号EDC’となる。

【0038】

(テスト回路の構成)

次に、図4に基づき、テスト回路27_0〜27_nの詳細な構成を説明する。以下、説明の便宜上、「n=2」として、テスト回路27_0〜27_2の構成を説明する。

ここで、図4(a)は、テスト回路27_0〜27_2の回路構成例を示す図であり、(b)は、(a)のテスト回路27_0〜27_2の真理値表である。

テスト回路27_0〜27_2は、図4(a)に示すように、NOTゲートN2〜N5(以下、単にN2〜N5と称す)と、2入力且つ1出力のNORゲートNR0〜NR1(以下、単にNR0〜NR1と称す)とから構成される共通の信号入力部を含んで構成されている。

【0039】

更に、テスト回路27_0〜27_2は、2入力且つ1出力のNANDゲートNA0〜NA5(以下、単にNA0〜NA5という)を含んで構成されている。

具体的に、テスト回路27_0はNA0及びNA3を含んで構成され、テスト回路27_1はNA1及びNA4を含んで構成され、テスト回路27_2はNA2及びNA5を含んで構成されている。

ここで、N2〜N5は、正論理で信号を受け、負論理で信号を出力するNOTゲートである。

【0040】

また、NR0〜NR1は、正論理で受けた2つの信号の論理和を演算して、演算結果を負論理で出力するNORゲートである。

また、NA0〜NA5は、正論理で受けた2つの信号の論理積を演算して、演算結果を負論理で出力するNANDゲートである。

N2は、出力端子がNR0の第1の入力端子と電気的に接続されており、その入力端子にはテスト信号TS[1]が入力され、入力された信号を反転して出力端子から出力する。

N3は、入力端子がNR0の出力端子と電気的に接続され、出力端子がNA3〜NA5の第1の入力端子にそれぞれ電気的に接続されており、その入力端子にはNR0の出力信号が入力され、入力された信号を反転して出力端子から出力する。

【0041】

N4は、出力端子がNR1の第1の入力端子と電気的に接続されており、その入力端子にはテスト信号TS[0]が入力され、入力された信号を反転して出力端子から出力する。

N5は、入力端子がNR1の出力端子と電気的に接続され、出力端子がNA0〜NA2の第1の入力端子にそれぞれ電気的に接続されており、その入力端子にはNR1の出力信号が入力され、入力された信号を反転して出力端子から出力する。

【0042】

NR0は、第1の入力端子がN2の出力端子と電気的に接続され、出力端子がN3の入力端子と電気的に接続されている。そして、第1の入力端子にはN2の出力信号が入力され、第2の入力端子にはテスト信号TS[0]が入力され、これら入力信号を論理和した結果を反転した信号を出力端子から出力する。

NR1は、第1の入力端子がN4の出力端子と電気的に接続され、出力端子がN5の入力端子と電気的に接続されている。そして、第1の入力端子にはテスト信号TS[1]が入力され、第2の入力端子にはN4の出力信号が入力され、これら入力信号を論理和した結果を反転した信号を出力端子から出力する。

【0043】

NA0は、出力端子がNA3の第2の入力端子と電気的に接続されており、その第1の入力端子にはN5の出力信号が入力され、その第2の入力端子には入力信号IN0が入力され、これら入力信号を論理積した結果を反転した信号を出力端子から出力する。

NA1は、出力端子がNA4の第2の入力端子と電気的に接続されており、その第1の入力端子にはN5の出力信号が入力され、その第2の入力端子には入力信号IN1が入力され、これら入力信号を論理積した結果を反転した信号を出力端子から出力する。

【0044】

NA2は、出力端子がNA5の第2の入力端子と電気的に接続されており、その第1の入力端子にはN5の出力信号が入力され、その第2の入力端子には入力信号IN2が入力され、これら入力信号を論理積した結果を反転した信号を出力端子から出力する。

NA3は、第1の入力端子にN3の出力信号が入力され、第2の入力端子にNA0の出力信号が入力され、これら入力信号を論理積した結果を反転した信号を、TS回路27_0の出力信号である出力信号OUT0として出力端子から出力する。

【0045】

NA4は、第1の入力端子にN3の出力信号が入力され、第2の入力端子にNA1の出力信号が入力され、これら入力信号を論理積した結果を反転した信号を、TS回路27_1の出力信号である出力信号OUT1として出力端子から出力する。

NA5は、第1の入力端子にN3の出力信号が入力され、第2の入力端子にNA2の出力信号が入力され、これら入力信号を論理積した結果を反転した信号を、TS回路27_2の出力信号である出力信号OUT2として出力端子から出力する。

このような構成によって、テスト回路27_0〜27_2は、図4(b)に示す真理値表に従った動作をする。

【0046】

具体的に、テスト回路27_0〜27_2は、図4(b)に示すように、2ビットのテスト信号TS[0](下位ビット),TS[1](上位ビット)が共にLowレベルの信号(偽値(0,0))又は共にHighレベルの信号(真値(1,1))のときに、出力信号OUT0が入力信号IN0となり、出力信号OUT1が入力信号IN1となり、出力信号OUT2が入力信号IN2となる。

ここで、テスト回路27_0〜27_2によって、通常動作時に、ラッチ回路21Bの出力を誤って全て「0」又は「1」にしてしまうと、入力信号は正しいのに誤り検出信号EDCがエラー出力となるような誤動作が発生してしまう。

【0047】

そこで、本実施の形態では、テスト信号TS[0],TS[1]が共に同じ信号となるときに入力信号IN0〜IN2をそのまま出力するような真理値表となる構成とすることで、誤動作の発生を低減している。

また、テスト回路27_0〜27_2は、テスト信号TS[0],TS[1]が(1,0)のときに、テストモードとなって、出力信号OUT0〜OUT1がHighレベルの信号(真値「1」)に固定される。

【0048】

また、テスト回路27_0〜27_2は、テスト信号TS[0],TS[1]が(0,1)のときに、テストモードとなって、出力信号OUT0〜OUT1がLowレベルの信号(偽値「0」)に固定される。

つまり、テスト回路27_0〜27_nによって、ラッチ回路21B0〜21Bnの出力を、Lowレベル及びHighレベルの状態のうちテスト信号TS[0],TS[1]の内容で決まる任意の一方の状態に強制的に固定することができる。

【0049】

(集積回路1の主要部分の具体的な動作例)

次に、図5〜図8に基づき、本実施の形態の集積回路1の主要部分である誤り検出回路2の具体的な動作を説明する。

ここで、図5は、第1のラッチタイミングで誤りが発生した場合のタイミングチャートの一例を示す図である。また、図6は、第2のラッチタイミングで誤りが発生した場合のタイミングチャートの一例を示す図である。また、図7は、ラッチ回路21Cを設けなかった場合のタイミングチャートの一例を示す図である。また、図8は、図4(a)のテスト回路27を用いたテスト内容の具体例の一覧を示す図である。

なお、以下の動作説明において、「n=2」とする。

【0050】

集積回路1に電源が供給され、各回路が動作を開始すると、まず、外部ホスト装置からのリセット信号RESETの入力によって、誤り検出回路2の状態が初期化される。

更に、外部ホスト装置から、クロック信号CKが誤り検出回路2及びメモリ回路3に入力され、入力信号IN0〜IN2が誤り検出回路2に入力され、テスト信号TS[0]、TS[1]が誤り検出回路2に入力される。

誤り検出回路2に入力されたクロック信号CK(以下、単にCKという)は、ラッチ回路21A0〜21A2と、遅延回路20A及び20Bとにそれぞれ入力される。

【0051】

また、誤り検出回路2に入力された入力信号IN0は、ラッチ回路21A0とTS回路27_0に入力され、入力信号IN1は、ラッチ回路21A1とTS回路27_1に入力され、入力信号IN2は、ラッチ回路21A2とTS回路27_2とに入力される。

また、誤り検出回路2に入力されたテスト信号TS[0]、TS[1]は、テスト回路27_0〜27_2にそれぞれ入力される。

ここでは、テスト信号TS[0]、TS[1]は、いずれもLowレベルの信号(偽値(0,0))に設定されているとする。従って、テスト回路27_0〜27_2に入力された入力信号IN0〜IN2はそのままラッチ回路21B0〜21B2に出力される。

【0052】

以下、共通の動作説明時において、入力信号IN0〜IN2は入力信号INといい、第1信号IN_A0〜IN_A2は第1信号IN_Aといい、第2信号IN_B0〜IN_B2は第2信号IN_Bといい、第3信号COMP0〜COMP2は第3信号COMPという。また、ラッチ回路21A0〜21A2はラッチ回路21Aといい、ラッチ回路21B0〜21B2はラッチ回路21Bといい、比較回路24_0〜24_2は比較回路24という。

【0053】

まず、図5に基づき、第1のラッチタイミングにおいて入力信号INに誤りが発生した場合の動作例を説明する。

ラッチ回路21Aは、図5に示すように、図中の左から順にCKの1番目の立ち上がりエッジであるCKの第1の立ち上がりエッジで、入力信号INの状態(High)を保持し、保持した状態を示すHighレベルの信号を第1信号IN_Aとして比較回路24とメモリ回路3とにそれぞれ出力する。

【0054】

一方、遅延回路20Aは、図5に示すように、CKを時間「t1」だけ遅延させた遅延クロック信号CK_A(以下、単にCK_Aという)を出力する。

また、遅延回路20Bは、図5に示すように、CKを時間「t2」だけ遅延させた遅延クロック信号XCK_Bを出力する。

また、ラッチ回路21Bは、図5に示すように、図中の左から順にCK_Aの1番目の立ち上がりエッジであるCK_Aの第1の立ち上がりエッジで、入力信号INの状態(High)を保持し、保持した状態を示すHighレベルの信号を第2信号IN_Bとして比較回路24に出力する。

【0055】

このとき、比較回路24は、第1信号IN_A及び第2信号IN_Bが共にHighレベルであるため、両者が一致すると比較判定し、Lowレベルの第3信号COMPを出力する。ここでは、比較回路24_0〜24_2が、いずれもLowレベルの第3信号COMP0〜COMP2を出力したとする。

従って、OR回路25は、比較回路24_0〜24_2の出力する第3信号COMP0〜COMP2がいずれもLowレベルであるため、これらを論理和した結果を示すLowレベルの第4信号EDC’をラッチ回路21Cに出力する。

【0056】

そして、ラッチ回路21Cは、図中の左から順にXCK_Bの1番目の立ち上がりエッジであるXCK_Bの第1の立ち上がりエッジにおいて、第4信号EDC’がLowレベルの信号であるため、図5に示すように、この状態を保持し、保持した状態を示すLowレベルの信号を、誤り検出信号EDCとして外部ホスト装置に出力する。

引き続き、ラッチ回路21Aは、CKの第2の立ち上がりエッジで、入力信号INの状態(Low)を保持するが、このタイミングを含む期間において、図5の点線波形に示すように、ノイズ等が原因で入力信号が一時的にHighレベルに変化したとする。この場合に、ラッチ回路21Aは、図5に示すように、入力信号INの変化したHighレベルの状態を保持し、保持した状態を示すHighレベルの信号を第1信号IN_Aとして出力する。

【0057】

引き続き、ラッチ回路21Bは、CK_Aの第2の立ち上がりエッジで、入力信号INの状態(Low)を保持し、保持した状態を示すLowレベルの第2信号IN_Bを出力する。

このとき、比較回路24は、第1信号IN_AがHighレベルで、第2信号IN_BがLowレベルであるため、両者が不一致であると比較判定し、Highレベルの第3信号COMPを出力する。ここでは、比較回路24_0〜24_2が、いずれもHighレベルの第3信号COMP0〜COMP2を出力したとする。

【0058】

従って、OR回路25は、比較回路24_0〜24_2の出力する第3信号COMP0〜COMP2がいずれもHighレベルであるため、これらを論理和した結果を示すHighレベルの第4信号EDC’をラッチ回路21Cに出力する。

そして、ラッチ回路21Cは、XCK_Bの第2の立ち上がりエッジにおいて、第4信号EDC’がHighレベルの信号であるため、図5に示すように、この状態を保持し、保持した状態を示すHighレベルの信号を、誤り検出信号EDCとして外部ホスト装置に出力する。

【0059】

なお、ラッチ回路21AでHighレベルの入力信号INのラッチ時に、ノイズ等が原因で入力信号INがHighレベルからLowレベルに一時的に変化した場合も第1信号IN_Aと第2信号IN_Bとが不一致となるので同様の結果となる。

このように、誤り検出信号EDCがHighレベルのときは、外部ホスト装置において、入力信号INの誤りの発生を検出することができるので、誤りのあった入力信号IN0〜IN2を集積回路1に再送するなどの処置を行うことができる。

【0060】

このとき、メモリ回路3へのデータの書込時においては、誤りの発生を検出するごとに、入力信号IN0〜IN2の単位で再送を行うことが可能である。しかし、nビットの単位で連続して信号が入力される状態で途中の一部のデータのみを再送するような場合に、外部ホスト装置側で誤りの発生した入力信号の識別を行う必要がある。このような識別を行うための負荷を考慮すると、誤りの発生したデータ信号を含む、ある程度のまとまったデータ単位(ブロック単位)で再送を行うことが望ましい。例えば、映像データをメモリ回路3に記憶するような場合は、1フレーム分のデータ単位などフレーム単位で再送を行う。

【0061】

次に、図6に基づき、第2のラッチタイミングにおいて入力信号INに誤りが発生した場合の動作例を説明する。

なお、CKの第1の立ち上がりエッジ、CK_Aの第1の立ち上がりエッジ、XCK_Bの第1の立ち上がりエッジにおける動作については、図5の例と同様となるので、第2の立ち上がりエッジからの動作を説明する。

ラッチ回路21Aは、図6に示すように、CKの第2の立ち上がりエッジで、入力信号INの状態(Low)を保持し、保持した状態を示すLowレベルの第1信号IN_Aを出力する。

【0062】

一方、ラッチ回路21Bは、CK_Aの第2の立ち上がりエッジで、入力信号INの状態(Low)を保持するが、このタイミングを含む期間において、図6の点線波形に示すように、ノイズ等が原因で入力信号が一時的にHighレベルに変化したとする。この場合に、ラッチ回路21Bは、図6に示すように、入力信号INの変化したHighレベルの状態を保持し、保持した状態を示すHighレベルの信号を第2信号IN_Bとして出力する。

【0063】

このとき、比較回路24は、第1信号IN_AがLowレベルで、第2信号IN_BがHighレベルであるため、両者が不一致であると比較判定し、Highレベルの第3信号COMPを出力する。ここでは、比較回路24_0〜24_2が、いずれもHighレベルの第3信号COMP0〜COMP2を出力したとする。

従って、OR回路25は、比較回路24_0〜24_2の出力する第3信号COMP0〜COMP2がいずれもHighレベルであるため、これらを論理和した結果を示すHighレベルの第4信号EDC’をラッチ回路21Cに出力する。

【0064】

そして、ラッチ回路21Cは、XCK_Bの第2の立ち上がりエッジにおいて、第4信号EDC’がHighレベルの信号であるため、図5に示すように、この状態を保持し、保持した状態を示すHighレベルの信号を、誤り検出信号EDCとして外部ホスト装置に出力する。

なお、ラッチ回路21BでHighレベルの入力信号INのラッチ時に、ノイズ等が原因で入力信号INがHighレベルからLowレベルに一時的に変化した場合も、第1信号IN_Aと第2信号IN_Bとが不一致となるので同様の結果となる。

【0065】

この場合も、外部ホスト装置において、入力信号INの誤りの発生を検出することができるので、誤りのあった入力信号IN0〜IN2を集積回路1に再送するなどの処置を行う。

このように、本実施の形態の集積回路1は、誤り検出回路2によって、ラッチ回路21Aの第1のラッチタイミングに発生した入力信号INの誤り、又はラッチ回路21Bの第2のラッチタイミングに発生した入力信号INの誤りのいずれか一方を検出することができる。

【0066】

次に、図7に基づき、ラッチ回路21C及び遅延回路20Bの役割について説明する。

まず、ラッチ回路21Cを設けずに、OR回路25の出力をそのまま誤り検出信号EDCとして出力した場合の動作について説明する。

この場合は、図7に示すように、まず、CKの立ち上がりエッジにおいて、ラッチ回路21Aで入力信号INのLowレベルの状態が保持され、保持された状態を示すLowレベルの第1信号IN_Aが出力される。

【0067】

このとき、遅延時間t1の経過前において第2信号IN_BがHighレベルの状態である場合に、t1の経過中において、入力信号INがLowレベルであるにも係わらず、第1信号IN_AがLowレベルで且つ第2信号IN_BがHighレベルという状態が発生する。

このような状態が発生すると、入力信号INに誤りが無いにも係わらず、比較回路24で不一致と比較判定され、図7に示すように、遅延時間t1の期間に、OR回路25からはHighレベルの誤り検出信号EDCが出力されてしまう。つまり、入力信号INに誤りが検出されたとして、Highレベルの誤り検出信号EDCが外部ホスト装置に出力されて、無用な再送動作が行われるなどの不具合が生じる恐れがある。

【0068】

一方、ラッチ回路21C及び遅延回路20Bを設けた場合は、図5及び図6に示すように、OR回路25の出力信号である第4信号EDC’の状態を、XCK_Bの立ち上がりエッジにおいて保持し、保持した状態を示す信号を誤り検出信号EDCとして出力することができる。

ここで、XCK_Bは、遅延時間t1よりも長い遅延時間t2でCKを遅延させた信号である。従って、遅延時間t2においては、比較回路24は、遅延時間t1の経過後における第1信号IN_A及び第2信号IN_Bの比較判定結果を示す第3信号COMPをOR回路25に出力している。

【0069】

従って、OR回路25は、遅延時間t1の経過後における第3信号COMPを論理和した結果を示す第4信号EDC’を出力しており、ラッチ回路21Cは、この第4信号EDC’の状態を保持し、保持した状態を示す信号を誤り検出信号EDCとして出力することになる。

これにより、遅延時間t1の期間においては、誤り検出信号EDCを前回の状態(または初期状態)のまま保持し続けることができるので、t1の期間において入力信号INに誤りが無いのにHighレベルの誤り検出信号EDCが出力されるのを防ぐことができる。

【0070】

次に、図8に基づき、本実施の形態の集積回路1の動作試験時の動作について説明する。なお、図8は、n=2の場合の動作試験の内容例を示しており、且つ入力信号IN0〜IN2が、MCA3aに書き込まれるライトデータWD0〜WD2の信号である場合の動作試験の内容例を示している。

外部ホスト装置は、テスト回路27_0〜27_2に供給する2ビットのテスト信号TS[0:1]の設定内容によって、図8に示すような動作試験を行うことができる。

【0071】

図8に示すように、入力信号IN0,IN1,IN2が(0,0,0)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはPass(Lowレベルの信号)となる。

これにより、入力信号IN0〜IN2が、出力信号OUT0〜OUT2としてそのまま出力される場合の動作試験を行うことができる。

【0072】

また、入力信号IN0,IN1,IN2が(1,0,0)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN0に対応するライトデータW0がHighデータとなるときの動作試験を行うことができる。

【0073】

また、入力信号IN0,IN1,IN2が(0,1,0)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN1に対応するライトデータW1がHighデータとなるときの動作試験を行うことができる。

【0074】

また、入力信号IN0,IN1,IN2が(0,0,1)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN2に対応するライトデータW2がHighデータとなるときの動作試験を行うことができる。

【0075】

また、入力信号IN0,IN1,IN2が(1,1,1)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN0〜IN2と異なる出力信号OUT0〜OUT2が出力されるときの動作試験を行うことができる。

【0076】

また、入力信号IN0,IN1,IN2が(0,0,0)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN0〜IN2と異なる出力信号OUT0〜OUT2が出力されるときの動作試験を行うことができる。

【0077】

また、入力信号IN0,IN1,IN2が(1,0,0)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN0に対応するライトデータW0がLowデータとなるときの動作試験を行うことができる。

【0078】

また、入力信号IN0,IN1,IN2が(0,1,0)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN1に対応するライトデータW1がLowデータとなるときの動作試験を行うことができる。

【0079】

また、入力信号IN0,IN1,IN2が(0,0,1)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN2に対応するライトデータW2がLowデータとなるときの動作試験を行うことができる。

【0080】

また、入力信号IN0,IN1,IN2が(1,1,1)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはPass(Lowレベルの信号)となる。

これにより、入力信号IN0〜IN2が、出力信号OUT0〜OUT2としてそのまま出力される場合の動作試験を行うことができる。

上記実施の形態において、メモリ回路3は、形態1の入力対象に対応し、ラッチ回路21Aは、第1のラッチ回路に対応し、ラッチ回路21Bは、第2のラッチ回路に対応し、ラッチ回路21Cは、第3のラッチ回路に対応し、OR回路25は、出力回路に対応する。

【0081】

また、上記実施の形態において、第1信号IN_Aは、第1信号に対応し、第2信号IN_Bは第2信号に対応し、第3信号COMPは、第3信号に対応し、第4信号EDC’は、形態2の誤り検出信号に対応し、誤り検出信号EDCは、形態3の第4信号に対応する。

なお、上記実施の形態において、ラッチ回路21Bと、テスト回路27とを別々の回路として構成したが、この構成に限らない。

【0082】

例えば、図9に示すように、ラッチ回路21Bとテスト回路27とを合成して、1つの回路としてまとめた構成としてもよい。ここで、図9は、ラッチ回路21Bとテスト回路27とを合成した合成回路例を示す図である。なお、図9では、テスト回路27_0〜27_nに共通のテスト信号TS[0:1]の入力部と、ラッチ回路21B0に対応するテスト回路27_0の回路部分のみを図示している。

図9に例示した合成回路は、図4に示す共通の信号入力部と、図3に示すラッチ回路21において、第1のラッチ回路のNOTゲートN0をNANDゲートNA6に、第2のラッチ回路のNOTゲートN1をNANDゲートNA7に置換した回路とを含んだ構成となっている。更に、第2のラッチ回路の出力段にNOTゲートN6を加えた構成となっている。

【0083】

具体的に、N5の出力端子とNA6の第1の入力端子とが電気的に接続され、T0及びT1の出力端子がNA6の第2の入力端子と電気的に接続されている。

更に、N3の出力端子とNA7の第1の入力端子とが電気的に接続され、T2及びT3の出力端子とNA7の第2の入力端子とが電気的に接続されている。

NA7の出力端子は、N6の入力端子に電気的に接続されており、N6の出力端子から出力信号OUT0が出力される。

上記構成により、図9に例示した合成回路は、図3のラッチ回路21の機能と、図4のテスト回路27_0の機能との双方の機能を発揮することができる。

【0084】

また、上記実施の形態において、誤り検出信号EDCとして、第3信号COMP0〜COMPnをOR回路25において1ビットにまとめた信号を出力する構成としたが、この構成に限らず、入力信号の1ビットごとに誤り検出信号EDCを出力する構成としてもよい。例えば、第3信号COMP0〜COMPnを個別にラッチ回路21C(要ビット数分)で受けて、ビットごとの誤り検出信号EDCとして出力する構成としてもよい。

【0085】

また、上記実施の形態において、メモリ回路3への全ての入力信号に対して、誤り検出回路2を設ける構成としたが、この構成に限らず、入力信号Adrressと入力信号Dinとにのみ誤り検出回路2を設けるなど、入力対象の複数の入力部に対して選択的に設ける構成としてもよい。

これにより、全ての入力に対して誤り検出回路2を設けた構成と比較して、回路面積を低減することができる。

【0086】

また、上記実施の形態において、遅延回路20A及び20Bを設けて、クロック信号CKを遅延させることで、ラッチ回路21B及びラッチ回路21Cのラッチ動作のタイミングを決定する構成としたが、この構成に限らない。

例えば、ラッチ回路21Bであれば、クロック信号CKの立ち下がりエッジのタイミングでラッチ動作を行う構成としてもよい。また、ラッチ回路21Cであれば、遅延クロック信号CK_Aの立ち下がりエッジのタイミングでラッチ動作を行う構成としてもよい。

また、上記実施の形態において、集積回路1をSRAMのメモリ回路3を入力信号の入力対象として含む構成を例に挙げて説明したが、この構成に限らない。

例えば、SRAM以外のDRAM等のメモリ回路を含む構成や、メモリ回路3に代えて、演算回路等のメモリ回路以外の回路を含む構成としてもよい。

【0087】

また、上記実施の形態は、本発明の好適な具体例であり、技術的に好ましい種々の限定が付されているが、本発明の範囲は、上記の説明において特に本発明を限定する旨の記載がない限り、これらの形態に限られるものではない。また、上記の説明で用いる図面は、図示の便宜上、部材ないし部分の縦横の縮尺は実際のものとは異なる模式図である。

また、本発明は上記実施の形態に限定されるものではなく、本発明の目的を達成できる範囲での変形、改良等は本発明に含まれるものである。

【符号の説明】

【0088】

1…集積回路、2,2A〜2C…誤り検出回路、3…メモリ回路、3a…メモリ・セル・アレイ(MCA)、3b…アドレス・デコーダー(ADEC)、3c…制御部(Control)、3d…データR/W部(DATA R/W)、20A,20B…遅延回路、21A,21A0〜21An…ラッチ回路、21B,21B0〜21Bn…ラッチ回路、21C…ラッチ回路、24,24_0〜24_n…比較回路、25…OR回路、27_0〜27_n…テスト回路、N0〜N6…NOTゲート、T0〜T3…伝送ゲート、NR0〜NR1…NORゲート、NA0〜NA7…NANDゲート

【技術分野】

【0001】

本発明は、入力対象に入力される信号の誤りを検出する誤り検出回路に関する。

【背景技術】

【0002】

従来、SRAM(Static Random Access Memory)などのメモリを内蔵する集積回路において、メモリにデータを書き込む際や、メモリに格納されたデータを読み出す際に、メモリへの入力信号やメモリからの出力信号が、ノイズによって変化する恐れがあった。ここで、ノイズとしては、P&Rツールを用いた自動配置配線が要因のクロストークノイズや、トランジスタの高集積化が要因のスイッチングノイズなどが挙げられる。

【0003】

このようなノイズ等による信号の変化は、誤ったデータのメモリへの格納や、誤ったデータ信号の出力による後段のシステムの誤動作などを引き起こす恐れがある。

この問題に対して、信号の誤りを検出する技術として、例えば、特許文献1のメモリの異常動作検出回路、特許文献2の誤動作防止用外部メモリインターフェース回路などが開示されている。

【0004】

特許文献1の技術では、メモリの出力データを所定時間遅延して、遅延データを出力し、この遅延データとメモリの出力データとを比較して、不一致の場合に不一致信号を出力することで出力データの誤りを検出している。

また、特許文献2の技術では、外部メモリから出力されたデータをクロックを用いてサンプリングするデータ入力同期回路が、少なくとも2回連続して同じデータをサンプリングしたときにそのデータを有効なデータと判定している。つまり、2回連続して同じデータをサンプリングできなかったときに出力データに誤りがあると判定している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−62389号公報

【特許文献2】特開2005−78209号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記特許文献1及び特許文献2の技術は、いずれもメモリから出力されるデータ信号について誤判定を行うものであり、メモリに入力されるデータ信号については誤判定を行っていない。そのため、ノイズ等の影響によって入力信号が変化した場合に、誤ったデータがメモリに保持されるのを防ぐことは困難であった。

そこで、本発明の目的の一つは、メモリ等の入力対象に入力される信号の誤判定を行うのに好適な誤り検出回路を提供することにある。

なお、前記目的に限らず、後述する発明を実施するための形態に示す各構成により導かれる作用効果であって、従来の技術によっては得られない作用効果を奏することも本発明の他の目的の一つとして位置付けることができる。

【課題を解決するための手段】

【0007】

〔形態1〕 上記目的を達成するために、形態1の誤り検出回路は、入力対象に入力する入力信号の状態を、第1クロック信号のエッジに基づく第1のタイミングで保持し、保持した状態を示す第1信号を出力する第1のラッチ回路と、

前記入力信号の状態を、第2クロック信号のエッジに基づく第2のタイミングで保持し、保持した状態を示す第2信号を出力する第2のラッチ回路と、

前記第1信号と前記第2信号とを比較して、比較結果に基づき両者が一致しているか否かを示す第3信号を出力する比較回路と、を備え、

前記第2のタイミングは、前記第1のタイミングから所定時間遅延したタイミングである。

【0008】

このような構成であれば、上記第1のタイミング又は上記第2のタイミングにおいてノイズ等が原因で入力信号が変化した場合に、第1信号と第2信号とが異なる状態となるため、比較回路において、第1信号と第2信号とが不一致であることを示す第3信号が出力される。

これにより、第1のラッチ回路の出力する第1信号を入力対象の入力信号として入力する構成とすることで、入力対象に入力される入力信号にノイズ等が原因で誤りが生じているか否かを検出することができる。

【0009】

また、第3信号が不一致を示す場合に、入力信号の発信元に対して第3信号を渡すなどすることで、発信元に入力信号の再送を行わせることができる。これにより、入力信号の誤りが原因で、入力対象が誤動作したり、入力対象から誤ったデータ信号が後段のシステムに出力されたりするのを未然に防ぐことができる。

また、入力対象がメモリ回路である場合は、誤ったデータが記憶されるのを防ぐことができる。

ここで、第1のラッチ回路及び第2のラッチ回路は、例えば、入力信号がデジタル信号である場合に、信号のHighレベル及びLowレベルの2状態を保持する。

【0010】

また、エッジに基づくタイミングとは、第1クロック及び第2クロックの立ち上がりエッジ又は立ち下がりエッジに基づくタイミングである。そして、第1のラッチ回路が第1クロックの立ち上がりエッジに基づき状態を保持する場合は、第2のラッチ回路も第2クロックの立ち上がりエッジに基づき状態を保持する。また、第1のラッチ回路が第1クロックの立ち下がりエッジに基づき状態を保持する場合は、第2のラッチ回路も第2クロックの立ち下がりエッジに基づき状態を保持する。なお、保持する条件(2状態を判断する電圧閾値等)は、第1のラッチ回路及び第2のラッチ回路で同じ条件とすることが望ましい。

【0011】

〔形態2〕 更に、形態2の誤り検出回路は、形態の1の誤り検出回路において、前記第1クロック信号と前記第2クロック信号とは同一のクロック信号である。

このような構成であれば、同一のクロック信号をそのまま第1のラッチ回路に供給し、同一のクロック信号を所定時間遅延させたクロック信号を第2のラッチ回路に供給することで、第1のタイミングと第2のタイミングとを簡易に生成することができる。

【0012】

〔形態3〕 また、上記目的を達成するために、形態3の誤り検出回路は、複数の前記入力信号に対応する複数の形態1又は2に記載の誤り検出回路と、

前記複数の誤り検出回路の各比較回路から出力される前記第3信号に基づき、前記入力信号の誤りの有無を示す誤り検出信号を出力する出力回路と、を備える。

このような構成であれば、出力回路によって、例えば、複数の第3信号のうち1つでも不一致となるものがあった場合に、誤りが有ることを示す誤り検出信号を出力するといったように厳密な誤り検出を行うことができる。また、複数の第3信号のうち所定数の不一致となるものがあった場合に誤りが有ることを示す誤り検出信号を出力するといったように、後段のシステムが必要とする精度に応じた誤り検出を行うこともできる。

【0013】

〔形態4〕 更に、形態4の誤り検出回路は、形態3の誤り検出回路において、前記第2クロック信号を所定時間遅延させた第3クロック信号のエッジに基づく第3のタイミングで、前記誤り検出信号の状態を保持し、保持した状態を示す第4の信号を出力する第3のラッチ回路を備える。

このような構成であれば、第1クロックと第2クロックとの遅延期間において、意図しない状態を示す誤り検出信号が出力されるのを防ぐことができる。

【0014】

〔形態5〕 更に、形態5の誤り検出回路は、形態4の誤り検出回路において、前記第2のラッチ回路の前段において、前記入力信号と制御信号とを受信し、受信した制御信号に基づき、受信した入力信号又は前記受信した制御信号に対応する状態を示すテスト入力信号を前記第2のラッチ回路に出力するテスト回路を備える。

このような構成であれば、テスト回路によって、個々の誤り検出回路が正常に動作しているか否かを試験することができる。

【0015】

〔形態6〕 一方、上記目的を達成するために、形態6の集積回路は、形態3乃至5のいずれか1に記載の誤り検出回路と、

前記入力信号の入力対象であって、前記複数の誤り検出回路を介して受信した前記入力信号の状態に対応する情報を記憶するメモリ回路と、を備える。

このような構成であれば、上記形態3乃至5のいずれか1に記載の誤り検出回路と同等の作用及び効果を得ることができる。

【図面の簡単な説明】

【0016】

【図1】本発明に係る集積回路1の構成を示すブロック図である。

【図2】誤り検出回路2の詳細な構成を示すブロック図である。

【図3】ラッチ回路21の回路構成例を示す図である。

【図4】(a)は、テスト回路27_0〜27_2の回路構成例を示す図であり、(b)は、(a)のテスト回路27_0〜27_2の真理値表である。

【図5】第1のラッチタイミングで誤りが発生した場合のタイミングチャートの一例を示す図である。

【図6】第2のラッチタイミングで誤りが発生した場合のタイミングチャートの一例を示す図である。

【図7】ラッチ回路21Cを設けなかった場合のタイミングチャートの一例を示す図である。

【図8】図4(a)のテスト回路27を用いたテスト内容の具体例の一覧を示す図である。

【図9】ラッチ回路21Bとテスト回路27とを合成した合成回路例を示す図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施の形態を図面に基づき説明する。図1〜図8は、本発明に係る誤り検出回路及び集積回路の実施の形態を示す図である。

(集積回路の構成)

まず、本発明に係る集積回路の構成を図1に基づき説明する。図1は、本発明に係る集積回路1の構成を示すブロック図である。

集積回路1は、図1に示すように、誤り検出回路2A〜2Cと、メモリ回路3とを含んだ構成となっている。以下、本実施の形態では、メモリ回路3を、同期型SRAMの回路として説明する。

【0018】

誤り検出回路2Aは、外部ホスト装置(不図示)から入力された、メモリ回路3のアドレスを指定するアドレス信号(図1中のAddress)の誤りを検出する回路である。

誤り検出回路2Bは、外部ホスト装置から入力された、各種セレクト信号、各種イネーブル信号などのメモリ回路3を制御する各種制御信号の誤りを検出する回路である。

誤り検出回路2Cは、外部ホスト装置から入力された、メモリ回路3に記憶するデータのデータ信号(図1中のDin)の誤りを検出する回路である。

【0019】

メモリ回路3は、メモリ・セル・アレイ(図1中のMCA)3aと、アドレスデコーダー(図1中のADEC)3bと、制御部(図1中のControl)3cと、データR/W部(図1中のDATA R/W)3dとを含んで構成される。

MCA3aは、SRAMの回路構成を有したメモリセルが複数アレイ状に配列された構成を有している。ここで、SRAMのメモリセルの回路構成として、図示しないが、4つのMOSトランジスタと2つの高抵抗から構成される高抵抗負荷型、又は6つのMOSトランジスタで構成されるCMOS型などがある。

【0020】

ADEC3bは、図示しないが、行アドレス・バッファー、行アドレス・レジスター、行アドレス・デコーダー、列アドレス・バッファー、列アドレス・レジスター、列アドレス・デコーダー等を含んで構成される。そして、ADEC3bは、制御部3cからの制御信号に応じて、入力されたアドレス信号の示すアドレスに対応するメモリセルをデータ書込可能な状態又はデータ読出可能な状態となるアクティブ状態となるように駆動する。

制御部3cは、入力された各種制御信号に応じて、ADEC3bの動作、データR/W部3dの動作を制御する。

データR/W部3dは、不図示のデータコントロール部とセンスアンプとを含んで構成され、制御部3cからの制御信号に応じて、アクティブ状態のメモリセルへのデータの書き込み、アクティブ状態のメモリセルからのデータの読み出しを行う。

【0021】

(誤り検出回路の構成)

次に、図2に基づき、誤り検出回路2A〜2Cの詳細な構成について説明する。

ここで、図2は、誤り検出回路2の詳細な構成を示すブロック図である。なお、誤り検出回路2A〜2Cは、誤りを検出するデータの種類が異なるだけで、構成は同様となるので、これらを総称して誤り検出回路2として説明する。

誤り検出回路2は、図2に示すように、遅延回路20A及び20Bと、ラッチ回路21A0〜21An(nは1以上の自然数)と、ラッチ回路21B0〜21Bnと、比較回路24_0〜24_nと、OR回路25と、ラッチ回路21Cとを含んで構成される。

【0022】

遅延回路20Aは、入力されたクロック信号CKを所定時間t1(t1<th(クロック信号CKの1周期の期間))だけ遅延させて、この遅延させたクロック信号である遅延クロック信号CK_Aを出力する回路である。

遅延回路20Bは、入力されたクロック信号CKを所定時間t2(t1<t2<th)だけ遅延させて、この遅延させたクロック信号である遅延クロック信号XCK_Bを出力する回路である。

【0023】

ラッチ回路21A0は、クロック信号CKの立ち上がりエッジ又は立ち下がりエッジに基づく第1のラッチタイミングにおいて、入力信号IN0の状態(Highレベル又はLowレベル)を保持するようになっている。そして、保持した状態(Highレベル又はLowレベル)を示す信号(以下、第1信号IN_A0と称す)を、比較回路24_0及びメモリ回路3にそれぞれ出力するようになっている。

具体的に、メモリ回路3における第1信号IN_A0の出力先は、誤り検出回路2Aの場合はADEC3bとなり、誤り検出回路2Bの場合は制御部3cとなり、誤り検出回路2Cの場合はデータR/W部3dとなる。

【0024】

ラッチ回路21A1〜21Anも同様に、各々が、クロック信号CKの立ち上がりエッジ又は立ち下がりエッジに基づく第1のラッチタイミングにおいて、入力信号IN1〜INnのうち末尾の数字が同じ入力信号の状態を保持するようになっている。そして、保持した状態を示す信号(以下、第1信号IN_A1〜Anと称す)を、比較回路24_1〜24_nのうち末尾の数字が同じ比較回路及びメモリ回路3にそれぞれ出力するようになっている。

【0025】

なお、本実施の形態において、入力信号IN0〜INnは、それぞれnビットのデジタル信号の各ビットの信号である(例えば、IN0は0ビット目、INnはnビット目の信号となる)。また、本実施の形態において、入力信号IN0〜INnは、アドレス信号Address、各種制御信号、データ信号Din(MCA3aに書き込むデータの信号)のいずれかのデジタル信号の各ビットの信号となる。

ラッチ回路21B0は、遅延クロック信号CK_Aの立ち上がりエッジ又は立ち下がりエッジに基づく第2のラッチタイミングにおいて、入力信号IN0の状態を保持するようになっている。そして、保持した状態を示す信号(以下、第2信号IN_B0と称す)を、比較回路24_0に出力するようになっている。

【0026】

ラッチ回路21B1〜21Bnも同様に、各々が、遅延クロック信号CK_Aの立ち上がりエッジ又は立ち下がりエッジに基づく第2のラッチタイミングにおいて、入力信号IN1〜INnのうち末尾の数字が同じ入力信号の状態を保持するようになっている。そして、保持した状態を示す信号(以下、第2信号IN_B1〜Bnと称す)を、比較回路24_1〜24_nのうち末尾の数字が同じ比較回路に出力するようになっている。

【0027】

比較回路24_0は、ラッチ回路21A0から入力された第1信号IN_A0と、ラッチ回路21B0から入力された第2信号IN_B0とを比較して、両者が一致しているか否かを示す信号(以下、第3信号COMP0と称す)を出力するようになっている。

比較回路24_1〜24_nも同様に、各々が、ラッチ回路21A1〜21Anから入力された第1信号IN_A1〜IN_Anのうち末尾が同じ数字の第1信号と、ラッチ回路21B1〜21Bnから入力された第2信号IN_B1〜IN_Bnのうち末尾の数字が同じ第2信号とを比較して、両者が一致しているか否かを示す信号(以下、第3信号COPM1〜COMPnと称す)を出力するようになっている。

【0028】

本実施の形態では、比較回路24_0〜24_nは、第1信号と第2信号とが一致しているときにLowレベルの第3信号を出力し、不一致のときにHighレベルの第3信号を出力するようになっている。

例えば、上記第1のラッチタイミングで入力信号IN0がノイズ等によって誤った状態になり、この状態がラッチ回路21A0で保持され、上記第2のラッチタイミングで入力信号IN0が正常な状態でラッチ回路21B0で保持されたとする。この場合に、ラッチ回路21A0の第1信号IN_A0とラッチ回路21B0の第2信号IN_B0とは不一致となり、比較回路24_0からはHighレベルの第3信号COMP0が出力される。つまり、入力信号IN0に誤りがあることを検出することができる。

なお、遅延時間t1及びt2の遅延量を調整することによって、どの程度の幅のノイズまでを誤りとして検出するかを設定することができる。

【0029】

OR回路25は、比較回路21_0〜21_nから入力された第3信号COMP0〜COMPnを論理和した結果を示す信号(以下、第4信号EDC’と称す)を出力する。具体的に、第4信号EDC’は、第3信号COPM1〜COMPnのなかに1つでも不一致(Highレベル)の状態のものがあるときは、Highレベルの信号となり、第3信号COPM1〜COMPnが全て同じ状態(Lowレベルの状態)であるときは、Lowレベルの信号となる。つまり、入力信号IN0〜INnに1つでも誤りがあるときは、Highレベルの第4信号EDC’を出力する。

【0030】

ラッチ回路21Cは、遅延クロック信号CK_Bの立ち上がりエッジ又は立ち下がりエッジに基づく第3のタイミングにおいて、OR回路25から出力される第4信号EDC’の状態を保持するようになっている。そして、保持した状態を示す信号を誤り検出信号EDCとして出力するようになっている。

なお、図1に示すように、誤り検出回路2Aからは入力信号Addressの誤りの有無を示す誤り検出信号EDC0が、誤り検出回路2Bからは各種制御信号の誤りの有無を示す誤り検出信号EDC1が、誤り検出回路2Cからは、入力信号Dinの誤りの有無を示す誤り検出信号EDC2が出力される。

【0031】

図2に示すように、誤り検出回路2は、更に、TS回路27_0〜27_nを含んで構成される。

TS回路27_0〜27_nは、2ビットの制御信号TS0[0:1]〜TSn[0:1]に応じて、ラッチ回路21B1〜21Bnの出力信号を、強制的にHighレベル又はLowレベルに固定する機能を有する回路である。これにより、誤り検出回路の動作試験を行うことができる。なお、通常動作時は、第2のラッチタイミングで保持した入力信号IN0〜INnの状態を示す第2信号IN_B1〜IN_Bnをそのまま出力するように動作する。

【0032】

(ラッチ回路の構成)

次に、図3に基づき、ラッチ回路21A0〜21An、21B0〜21Bn及び21Cの回路構成を説明する。なお、本実施の形態において、これらラッチ回路の構成はいずれも同様となるので、これらを総称してラッチ回路21とし回路構成を説明する。

ここで、図3は、ラッチ回路21の回路構成例を示す図である。

ラッチ回路21は、図3に示すように、伝送ゲートT0〜T3(以下、単にT0〜T3という)と、NOTゲートN0〜N1(以下、単にN0〜N1という)とを含んで構成される。

【0033】

T0〜T3は、第1〜第3の入力端子と、出力端子とを有しており、第1及び第3の入力端子に入力される信号(図中のLAT、XLAT)の状態に応じて、第2の入力端子に入力される信号(図中のIN)を出力端子から出力する状態と、出力しない状態とのいずれか一方の状態に遷移する伝送ゲートである。

T0は、出力端子がT1の出力端子及びN0の入力端子と電気的に接続されており、第2の入力端子で入力信号INを負論理で受け、第3の入力端子で入力信号XLATを正論理で受け、第1の入力端子で入力信号LATを負論理で受けるようになっている。

【0034】

T1は、第2の入力端子がN0の出力端子と電気的に接続されており、出力端子がT0の出力端子とN0の入力端子とにそれぞれ電気的に接続されている。更に、T1は、第1の入力端子で入力信号LATを正論理で受け、第2の入力端子でN0の出力信号を負論理で受け、第3の入力端子で入力信号XLATを負論理で受けるようになっている。

T2は、第2の入力端子がN0の出力端子と電気的に接続され、出力端子がN1の入力端子とT3の出力端子とにそれぞれ電気的に接続されている。更に、T2は、第1の入力端子で入力信号LATを正論理で受け、第2の入力端子でN0の出力信号を負論理で受け、第3の入力端子で入力信号XLATを負論理で受けるようになっている。

【0035】

T3は、入力端子がN1の出力端子と電気的に接続され、出力端子がN1の入力端子とT2の出力端子とにそれぞれ電気的に接続されている。更に、T3は、第1の入力端子で入力信号LATを負論理で受け、第2の入力端子でN1の出力信号を負論理で受け、第3の入力端子で入力信号XLATを正論理で受けるようになっている。

N0は、負論理で信号を受け、正論理で信号を出力するNOTゲートであり、入力端子がT0の出力端子と電気的に接続され、出力端子がT1の第2の入力端子とT2の第2の入力端子とにそれぞれ電気的に接続されている。

N1は、負論理で信号を受け、正論理で信号を出力するNOTゲートであり、入力端子がT2の出力端子とT3の出力端子とにそれぞれ電気的に接続され、出力端子がT3の第2の入力端子と電気的に接続されている。

【0036】

そして、N0、T0及びT1から第1のラッチ回路が構成され、N1、T2及びT3から第2のラッチ回路が構成され、第1のラッチ回路と第2のラッチ回路とはT2を介して電気的に接続されている。

このような構成によって、ラッチ回路21は、入力信号LATの立ち上がりエッジのタイミングにおいて、入力信号INの状態(High又はLow)を保持し、その他のタイミングにおいて、前記保持したINの状態を示す信号を常時、出力信号OUTとして出力する。従って、入力信号INの変化によって、比較回路24、メモリ回路3等の後段の回路が意図しないタイミングで動いてしまい電流消費が増大することを防止することができる。また、入力信号INの変化によって、誤り検出信号EDCが一時的にHighとなってエラー出力となるのを防ぐことができる。

【0037】

なお、入力信号LATとXLATとは相互に反転した関係の信号であり、ラッチ回路21A0〜21Anの場合は、クロック信号CKとCKを反転させた信号XCKとなり、ラッチ回路21B0〜21Bnの場合は、遅延クロック信号CK_AとCK_Aを反転させた信号XCK_Aとなる。また、ラッチ回路21Cの場合は、遅延クロック信号XCK_BとXCK_Bを反転させた信号CK_Bとなる。

また、入力信号INは、検出回路2Aの場合は入力信号Addressに、検出回路2Bの場合は各種制御信号に、検出回路2Cの場合は入力信号Dinとなる。

また、入力信号INは、ラッチ回路21Cの場合は、検出回路2A〜2CのいずれもOR回路25から出力される第4信号EDC’となる。

【0038】

(テスト回路の構成)

次に、図4に基づき、テスト回路27_0〜27_nの詳細な構成を説明する。以下、説明の便宜上、「n=2」として、テスト回路27_0〜27_2の構成を説明する。

ここで、図4(a)は、テスト回路27_0〜27_2の回路構成例を示す図であり、(b)は、(a)のテスト回路27_0〜27_2の真理値表である。

テスト回路27_0〜27_2は、図4(a)に示すように、NOTゲートN2〜N5(以下、単にN2〜N5と称す)と、2入力且つ1出力のNORゲートNR0〜NR1(以下、単にNR0〜NR1と称す)とから構成される共通の信号入力部を含んで構成されている。

【0039】

更に、テスト回路27_0〜27_2は、2入力且つ1出力のNANDゲートNA0〜NA5(以下、単にNA0〜NA5という)を含んで構成されている。

具体的に、テスト回路27_0はNA0及びNA3を含んで構成され、テスト回路27_1はNA1及びNA4を含んで構成され、テスト回路27_2はNA2及びNA5を含んで構成されている。

ここで、N2〜N5は、正論理で信号を受け、負論理で信号を出力するNOTゲートである。

【0040】

また、NR0〜NR1は、正論理で受けた2つの信号の論理和を演算して、演算結果を負論理で出力するNORゲートである。

また、NA0〜NA5は、正論理で受けた2つの信号の論理積を演算して、演算結果を負論理で出力するNANDゲートである。

N2は、出力端子がNR0の第1の入力端子と電気的に接続されており、その入力端子にはテスト信号TS[1]が入力され、入力された信号を反転して出力端子から出力する。

N3は、入力端子がNR0の出力端子と電気的に接続され、出力端子がNA3〜NA5の第1の入力端子にそれぞれ電気的に接続されており、その入力端子にはNR0の出力信号が入力され、入力された信号を反転して出力端子から出力する。

【0041】

N4は、出力端子がNR1の第1の入力端子と電気的に接続されており、その入力端子にはテスト信号TS[0]が入力され、入力された信号を反転して出力端子から出力する。

N5は、入力端子がNR1の出力端子と電気的に接続され、出力端子がNA0〜NA2の第1の入力端子にそれぞれ電気的に接続されており、その入力端子にはNR1の出力信号が入力され、入力された信号を反転して出力端子から出力する。

【0042】

NR0は、第1の入力端子がN2の出力端子と電気的に接続され、出力端子がN3の入力端子と電気的に接続されている。そして、第1の入力端子にはN2の出力信号が入力され、第2の入力端子にはテスト信号TS[0]が入力され、これら入力信号を論理和した結果を反転した信号を出力端子から出力する。

NR1は、第1の入力端子がN4の出力端子と電気的に接続され、出力端子がN5の入力端子と電気的に接続されている。そして、第1の入力端子にはテスト信号TS[1]が入力され、第2の入力端子にはN4の出力信号が入力され、これら入力信号を論理和した結果を反転した信号を出力端子から出力する。

【0043】

NA0は、出力端子がNA3の第2の入力端子と電気的に接続されており、その第1の入力端子にはN5の出力信号が入力され、その第2の入力端子には入力信号IN0が入力され、これら入力信号を論理積した結果を反転した信号を出力端子から出力する。

NA1は、出力端子がNA4の第2の入力端子と電気的に接続されており、その第1の入力端子にはN5の出力信号が入力され、その第2の入力端子には入力信号IN1が入力され、これら入力信号を論理積した結果を反転した信号を出力端子から出力する。

【0044】

NA2は、出力端子がNA5の第2の入力端子と電気的に接続されており、その第1の入力端子にはN5の出力信号が入力され、その第2の入力端子には入力信号IN2が入力され、これら入力信号を論理積した結果を反転した信号を出力端子から出力する。

NA3は、第1の入力端子にN3の出力信号が入力され、第2の入力端子にNA0の出力信号が入力され、これら入力信号を論理積した結果を反転した信号を、TS回路27_0の出力信号である出力信号OUT0として出力端子から出力する。

【0045】

NA4は、第1の入力端子にN3の出力信号が入力され、第2の入力端子にNA1の出力信号が入力され、これら入力信号を論理積した結果を反転した信号を、TS回路27_1の出力信号である出力信号OUT1として出力端子から出力する。

NA5は、第1の入力端子にN3の出力信号が入力され、第2の入力端子にNA2の出力信号が入力され、これら入力信号を論理積した結果を反転した信号を、TS回路27_2の出力信号である出力信号OUT2として出力端子から出力する。

このような構成によって、テスト回路27_0〜27_2は、図4(b)に示す真理値表に従った動作をする。

【0046】

具体的に、テスト回路27_0〜27_2は、図4(b)に示すように、2ビットのテスト信号TS[0](下位ビット),TS[1](上位ビット)が共にLowレベルの信号(偽値(0,0))又は共にHighレベルの信号(真値(1,1))のときに、出力信号OUT0が入力信号IN0となり、出力信号OUT1が入力信号IN1となり、出力信号OUT2が入力信号IN2となる。

ここで、テスト回路27_0〜27_2によって、通常動作時に、ラッチ回路21Bの出力を誤って全て「0」又は「1」にしてしまうと、入力信号は正しいのに誤り検出信号EDCがエラー出力となるような誤動作が発生してしまう。

【0047】

そこで、本実施の形態では、テスト信号TS[0],TS[1]が共に同じ信号となるときに入力信号IN0〜IN2をそのまま出力するような真理値表となる構成とすることで、誤動作の発生を低減している。

また、テスト回路27_0〜27_2は、テスト信号TS[0],TS[1]が(1,0)のときに、テストモードとなって、出力信号OUT0〜OUT1がHighレベルの信号(真値「1」)に固定される。

【0048】

また、テスト回路27_0〜27_2は、テスト信号TS[0],TS[1]が(0,1)のときに、テストモードとなって、出力信号OUT0〜OUT1がLowレベルの信号(偽値「0」)に固定される。

つまり、テスト回路27_0〜27_nによって、ラッチ回路21B0〜21Bnの出力を、Lowレベル及びHighレベルの状態のうちテスト信号TS[0],TS[1]の内容で決まる任意の一方の状態に強制的に固定することができる。

【0049】

(集積回路1の主要部分の具体的な動作例)

次に、図5〜図8に基づき、本実施の形態の集積回路1の主要部分である誤り検出回路2の具体的な動作を説明する。

ここで、図5は、第1のラッチタイミングで誤りが発生した場合のタイミングチャートの一例を示す図である。また、図6は、第2のラッチタイミングで誤りが発生した場合のタイミングチャートの一例を示す図である。また、図7は、ラッチ回路21Cを設けなかった場合のタイミングチャートの一例を示す図である。また、図8は、図4(a)のテスト回路27を用いたテスト内容の具体例の一覧を示す図である。

なお、以下の動作説明において、「n=2」とする。

【0050】

集積回路1に電源が供給され、各回路が動作を開始すると、まず、外部ホスト装置からのリセット信号RESETの入力によって、誤り検出回路2の状態が初期化される。

更に、外部ホスト装置から、クロック信号CKが誤り検出回路2及びメモリ回路3に入力され、入力信号IN0〜IN2が誤り検出回路2に入力され、テスト信号TS[0]、TS[1]が誤り検出回路2に入力される。

誤り検出回路2に入力されたクロック信号CK(以下、単にCKという)は、ラッチ回路21A0〜21A2と、遅延回路20A及び20Bとにそれぞれ入力される。

【0051】

また、誤り検出回路2に入力された入力信号IN0は、ラッチ回路21A0とTS回路27_0に入力され、入力信号IN1は、ラッチ回路21A1とTS回路27_1に入力され、入力信号IN2は、ラッチ回路21A2とTS回路27_2とに入力される。

また、誤り検出回路2に入力されたテスト信号TS[0]、TS[1]は、テスト回路27_0〜27_2にそれぞれ入力される。

ここでは、テスト信号TS[0]、TS[1]は、いずれもLowレベルの信号(偽値(0,0))に設定されているとする。従って、テスト回路27_0〜27_2に入力された入力信号IN0〜IN2はそのままラッチ回路21B0〜21B2に出力される。

【0052】

以下、共通の動作説明時において、入力信号IN0〜IN2は入力信号INといい、第1信号IN_A0〜IN_A2は第1信号IN_Aといい、第2信号IN_B0〜IN_B2は第2信号IN_Bといい、第3信号COMP0〜COMP2は第3信号COMPという。また、ラッチ回路21A0〜21A2はラッチ回路21Aといい、ラッチ回路21B0〜21B2はラッチ回路21Bといい、比較回路24_0〜24_2は比較回路24という。

【0053】

まず、図5に基づき、第1のラッチタイミングにおいて入力信号INに誤りが発生した場合の動作例を説明する。

ラッチ回路21Aは、図5に示すように、図中の左から順にCKの1番目の立ち上がりエッジであるCKの第1の立ち上がりエッジで、入力信号INの状態(High)を保持し、保持した状態を示すHighレベルの信号を第1信号IN_Aとして比較回路24とメモリ回路3とにそれぞれ出力する。

【0054】

一方、遅延回路20Aは、図5に示すように、CKを時間「t1」だけ遅延させた遅延クロック信号CK_A(以下、単にCK_Aという)を出力する。

また、遅延回路20Bは、図5に示すように、CKを時間「t2」だけ遅延させた遅延クロック信号XCK_Bを出力する。

また、ラッチ回路21Bは、図5に示すように、図中の左から順にCK_Aの1番目の立ち上がりエッジであるCK_Aの第1の立ち上がりエッジで、入力信号INの状態(High)を保持し、保持した状態を示すHighレベルの信号を第2信号IN_Bとして比較回路24に出力する。

【0055】

このとき、比較回路24は、第1信号IN_A及び第2信号IN_Bが共にHighレベルであるため、両者が一致すると比較判定し、Lowレベルの第3信号COMPを出力する。ここでは、比較回路24_0〜24_2が、いずれもLowレベルの第3信号COMP0〜COMP2を出力したとする。

従って、OR回路25は、比較回路24_0〜24_2の出力する第3信号COMP0〜COMP2がいずれもLowレベルであるため、これらを論理和した結果を示すLowレベルの第4信号EDC’をラッチ回路21Cに出力する。

【0056】

そして、ラッチ回路21Cは、図中の左から順にXCK_Bの1番目の立ち上がりエッジであるXCK_Bの第1の立ち上がりエッジにおいて、第4信号EDC’がLowレベルの信号であるため、図5に示すように、この状態を保持し、保持した状態を示すLowレベルの信号を、誤り検出信号EDCとして外部ホスト装置に出力する。

引き続き、ラッチ回路21Aは、CKの第2の立ち上がりエッジで、入力信号INの状態(Low)を保持するが、このタイミングを含む期間において、図5の点線波形に示すように、ノイズ等が原因で入力信号が一時的にHighレベルに変化したとする。この場合に、ラッチ回路21Aは、図5に示すように、入力信号INの変化したHighレベルの状態を保持し、保持した状態を示すHighレベルの信号を第1信号IN_Aとして出力する。

【0057】

引き続き、ラッチ回路21Bは、CK_Aの第2の立ち上がりエッジで、入力信号INの状態(Low)を保持し、保持した状態を示すLowレベルの第2信号IN_Bを出力する。

このとき、比較回路24は、第1信号IN_AがHighレベルで、第2信号IN_BがLowレベルであるため、両者が不一致であると比較判定し、Highレベルの第3信号COMPを出力する。ここでは、比較回路24_0〜24_2が、いずれもHighレベルの第3信号COMP0〜COMP2を出力したとする。

【0058】

従って、OR回路25は、比較回路24_0〜24_2の出力する第3信号COMP0〜COMP2がいずれもHighレベルであるため、これらを論理和した結果を示すHighレベルの第4信号EDC’をラッチ回路21Cに出力する。

そして、ラッチ回路21Cは、XCK_Bの第2の立ち上がりエッジにおいて、第4信号EDC’がHighレベルの信号であるため、図5に示すように、この状態を保持し、保持した状態を示すHighレベルの信号を、誤り検出信号EDCとして外部ホスト装置に出力する。

【0059】

なお、ラッチ回路21AでHighレベルの入力信号INのラッチ時に、ノイズ等が原因で入力信号INがHighレベルからLowレベルに一時的に変化した場合も第1信号IN_Aと第2信号IN_Bとが不一致となるので同様の結果となる。

このように、誤り検出信号EDCがHighレベルのときは、外部ホスト装置において、入力信号INの誤りの発生を検出することができるので、誤りのあった入力信号IN0〜IN2を集積回路1に再送するなどの処置を行うことができる。

【0060】

このとき、メモリ回路3へのデータの書込時においては、誤りの発生を検出するごとに、入力信号IN0〜IN2の単位で再送を行うことが可能である。しかし、nビットの単位で連続して信号が入力される状態で途中の一部のデータのみを再送するような場合に、外部ホスト装置側で誤りの発生した入力信号の識別を行う必要がある。このような識別を行うための負荷を考慮すると、誤りの発生したデータ信号を含む、ある程度のまとまったデータ単位(ブロック単位)で再送を行うことが望ましい。例えば、映像データをメモリ回路3に記憶するような場合は、1フレーム分のデータ単位などフレーム単位で再送を行う。

【0061】

次に、図6に基づき、第2のラッチタイミングにおいて入力信号INに誤りが発生した場合の動作例を説明する。

なお、CKの第1の立ち上がりエッジ、CK_Aの第1の立ち上がりエッジ、XCK_Bの第1の立ち上がりエッジにおける動作については、図5の例と同様となるので、第2の立ち上がりエッジからの動作を説明する。

ラッチ回路21Aは、図6に示すように、CKの第2の立ち上がりエッジで、入力信号INの状態(Low)を保持し、保持した状態を示すLowレベルの第1信号IN_Aを出力する。

【0062】

一方、ラッチ回路21Bは、CK_Aの第2の立ち上がりエッジで、入力信号INの状態(Low)を保持するが、このタイミングを含む期間において、図6の点線波形に示すように、ノイズ等が原因で入力信号が一時的にHighレベルに変化したとする。この場合に、ラッチ回路21Bは、図6に示すように、入力信号INの変化したHighレベルの状態を保持し、保持した状態を示すHighレベルの信号を第2信号IN_Bとして出力する。

【0063】

このとき、比較回路24は、第1信号IN_AがLowレベルで、第2信号IN_BがHighレベルであるため、両者が不一致であると比較判定し、Highレベルの第3信号COMPを出力する。ここでは、比較回路24_0〜24_2が、いずれもHighレベルの第3信号COMP0〜COMP2を出力したとする。

従って、OR回路25は、比較回路24_0〜24_2の出力する第3信号COMP0〜COMP2がいずれもHighレベルであるため、これらを論理和した結果を示すHighレベルの第4信号EDC’をラッチ回路21Cに出力する。

【0064】

そして、ラッチ回路21Cは、XCK_Bの第2の立ち上がりエッジにおいて、第4信号EDC’がHighレベルの信号であるため、図5に示すように、この状態を保持し、保持した状態を示すHighレベルの信号を、誤り検出信号EDCとして外部ホスト装置に出力する。

なお、ラッチ回路21BでHighレベルの入力信号INのラッチ時に、ノイズ等が原因で入力信号INがHighレベルからLowレベルに一時的に変化した場合も、第1信号IN_Aと第2信号IN_Bとが不一致となるので同様の結果となる。

【0065】

この場合も、外部ホスト装置において、入力信号INの誤りの発生を検出することができるので、誤りのあった入力信号IN0〜IN2を集積回路1に再送するなどの処置を行う。

このように、本実施の形態の集積回路1は、誤り検出回路2によって、ラッチ回路21Aの第1のラッチタイミングに発生した入力信号INの誤り、又はラッチ回路21Bの第2のラッチタイミングに発生した入力信号INの誤りのいずれか一方を検出することができる。

【0066】

次に、図7に基づき、ラッチ回路21C及び遅延回路20Bの役割について説明する。

まず、ラッチ回路21Cを設けずに、OR回路25の出力をそのまま誤り検出信号EDCとして出力した場合の動作について説明する。

この場合は、図7に示すように、まず、CKの立ち上がりエッジにおいて、ラッチ回路21Aで入力信号INのLowレベルの状態が保持され、保持された状態を示すLowレベルの第1信号IN_Aが出力される。

【0067】

このとき、遅延時間t1の経過前において第2信号IN_BがHighレベルの状態である場合に、t1の経過中において、入力信号INがLowレベルであるにも係わらず、第1信号IN_AがLowレベルで且つ第2信号IN_BがHighレベルという状態が発生する。

このような状態が発生すると、入力信号INに誤りが無いにも係わらず、比較回路24で不一致と比較判定され、図7に示すように、遅延時間t1の期間に、OR回路25からはHighレベルの誤り検出信号EDCが出力されてしまう。つまり、入力信号INに誤りが検出されたとして、Highレベルの誤り検出信号EDCが外部ホスト装置に出力されて、無用な再送動作が行われるなどの不具合が生じる恐れがある。

【0068】

一方、ラッチ回路21C及び遅延回路20Bを設けた場合は、図5及び図6に示すように、OR回路25の出力信号である第4信号EDC’の状態を、XCK_Bの立ち上がりエッジにおいて保持し、保持した状態を示す信号を誤り検出信号EDCとして出力することができる。

ここで、XCK_Bは、遅延時間t1よりも長い遅延時間t2でCKを遅延させた信号である。従って、遅延時間t2においては、比較回路24は、遅延時間t1の経過後における第1信号IN_A及び第2信号IN_Bの比較判定結果を示す第3信号COMPをOR回路25に出力している。

【0069】

従って、OR回路25は、遅延時間t1の経過後における第3信号COMPを論理和した結果を示す第4信号EDC’を出力しており、ラッチ回路21Cは、この第4信号EDC’の状態を保持し、保持した状態を示す信号を誤り検出信号EDCとして出力することになる。

これにより、遅延時間t1の期間においては、誤り検出信号EDCを前回の状態(または初期状態)のまま保持し続けることができるので、t1の期間において入力信号INに誤りが無いのにHighレベルの誤り検出信号EDCが出力されるのを防ぐことができる。

【0070】

次に、図8に基づき、本実施の形態の集積回路1の動作試験時の動作について説明する。なお、図8は、n=2の場合の動作試験の内容例を示しており、且つ入力信号IN0〜IN2が、MCA3aに書き込まれるライトデータWD0〜WD2の信号である場合の動作試験の内容例を示している。

外部ホスト装置は、テスト回路27_0〜27_2に供給する2ビットのテスト信号TS[0:1]の設定内容によって、図8に示すような動作試験を行うことができる。

【0071】

図8に示すように、入力信号IN0,IN1,IN2が(0,0,0)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはPass(Lowレベルの信号)となる。

これにより、入力信号IN0〜IN2が、出力信号OUT0〜OUT2としてそのまま出力される場合の動作試験を行うことができる。

【0072】

また、入力信号IN0,IN1,IN2が(1,0,0)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN0に対応するライトデータW0がHighデータとなるときの動作試験を行うことができる。

【0073】

また、入力信号IN0,IN1,IN2が(0,1,0)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN1に対応するライトデータW1がHighデータとなるときの動作試験を行うことができる。

【0074】

また、入力信号IN0,IN1,IN2が(0,0,1)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN2に対応するライトデータW2がHighデータとなるときの動作試験を行うことができる。

【0075】

また、入力信号IN0,IN1,IN2が(1,1,1)のときに、テスト信号TS[0],TS[1]が(1,0)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「0」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(0,0,0)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN0〜IN2と異なる出力信号OUT0〜OUT2が出力されるときの動作試験を行うことができる。

【0076】

また、入力信号IN0,IN1,IN2が(0,0,0)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN0〜IN2と異なる出力信号OUT0〜OUT2が出力されるときの動作試験を行うことができる。

【0077】

また、入力信号IN0,IN1,IN2が(1,0,0)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN0に対応するライトデータW0がLowデータとなるときの動作試験を行うことができる。

【0078】

また、入力信号IN0,IN1,IN2が(0,1,0)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN1に対応するライトデータW1がLowデータとなるときの動作試験を行うことができる。

【0079】

また、入力信号IN0,IN1,IN2が(0,0,1)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはFail(Highレベルの信号)となる。

これにより、入力信号IN2に対応するライトデータW2がLowデータとなるときの動作試験を行うことができる。

【0080】

また、入力信号IN0,IN1,IN2が(1,1,1)のときに、テスト信号TS[0],TS[1]が(0,1)となるテスト信号を供給することで、ラッチ回路21B0〜21B2の出力を強制的に「1」に固定する。これにより、出力信号OUT0,OUT1,OUT2が(1,1,1)となり、誤り検出信号EDCはPass(Lowレベルの信号)となる。

これにより、入力信号IN0〜IN2が、出力信号OUT0〜OUT2としてそのまま出力される場合の動作試験を行うことができる。

上記実施の形態において、メモリ回路3は、形態1の入力対象に対応し、ラッチ回路21Aは、第1のラッチ回路に対応し、ラッチ回路21Bは、第2のラッチ回路に対応し、ラッチ回路21Cは、第3のラッチ回路に対応し、OR回路25は、出力回路に対応する。

【0081】

また、上記実施の形態において、第1信号IN_Aは、第1信号に対応し、第2信号IN_Bは第2信号に対応し、第3信号COMPは、第3信号に対応し、第4信号EDC’は、形態2の誤り検出信号に対応し、誤り検出信号EDCは、形態3の第4信号に対応する。

なお、上記実施の形態において、ラッチ回路21Bと、テスト回路27とを別々の回路として構成したが、この構成に限らない。

【0082】

例えば、図9に示すように、ラッチ回路21Bとテスト回路27とを合成して、1つの回路としてまとめた構成としてもよい。ここで、図9は、ラッチ回路21Bとテスト回路27とを合成した合成回路例を示す図である。なお、図9では、テスト回路27_0〜27_nに共通のテスト信号TS[0:1]の入力部と、ラッチ回路21B0に対応するテスト回路27_0の回路部分のみを図示している。

図9に例示した合成回路は、図4に示す共通の信号入力部と、図3に示すラッチ回路21において、第1のラッチ回路のNOTゲートN0をNANDゲートNA6に、第2のラッチ回路のNOTゲートN1をNANDゲートNA7に置換した回路とを含んだ構成となっている。更に、第2のラッチ回路の出力段にNOTゲートN6を加えた構成となっている。

【0083】

具体的に、N5の出力端子とNA6の第1の入力端子とが電気的に接続され、T0及びT1の出力端子がNA6の第2の入力端子と電気的に接続されている。

更に、N3の出力端子とNA7の第1の入力端子とが電気的に接続され、T2及びT3の出力端子とNA7の第2の入力端子とが電気的に接続されている。

NA7の出力端子は、N6の入力端子に電気的に接続されており、N6の出力端子から出力信号OUT0が出力される。

上記構成により、図9に例示した合成回路は、図3のラッチ回路21の機能と、図4のテスト回路27_0の機能との双方の機能を発揮することができる。

【0084】

また、上記実施の形態において、誤り検出信号EDCとして、第3信号COMP0〜COMPnをOR回路25において1ビットにまとめた信号を出力する構成としたが、この構成に限らず、入力信号の1ビットごとに誤り検出信号EDCを出力する構成としてもよい。例えば、第3信号COMP0〜COMPnを個別にラッチ回路21C(要ビット数分)で受けて、ビットごとの誤り検出信号EDCとして出力する構成としてもよい。

【0085】

また、上記実施の形態において、メモリ回路3への全ての入力信号に対して、誤り検出回路2を設ける構成としたが、この構成に限らず、入力信号Adrressと入力信号Dinとにのみ誤り検出回路2を設けるなど、入力対象の複数の入力部に対して選択的に設ける構成としてもよい。

これにより、全ての入力に対して誤り検出回路2を設けた構成と比較して、回路面積を低減することができる。

【0086】

また、上記実施の形態において、遅延回路20A及び20Bを設けて、クロック信号CKを遅延させることで、ラッチ回路21B及びラッチ回路21Cのラッチ動作のタイミングを決定する構成としたが、この構成に限らない。

例えば、ラッチ回路21Bであれば、クロック信号CKの立ち下がりエッジのタイミングでラッチ動作を行う構成としてもよい。また、ラッチ回路21Cであれば、遅延クロック信号CK_Aの立ち下がりエッジのタイミングでラッチ動作を行う構成としてもよい。

また、上記実施の形態において、集積回路1をSRAMのメモリ回路3を入力信号の入力対象として含む構成を例に挙げて説明したが、この構成に限らない。

例えば、SRAM以外のDRAM等のメモリ回路を含む構成や、メモリ回路3に代えて、演算回路等のメモリ回路以外の回路を含む構成としてもよい。

【0087】

また、上記実施の形態は、本発明の好適な具体例であり、技術的に好ましい種々の限定が付されているが、本発明の範囲は、上記の説明において特に本発明を限定する旨の記載がない限り、これらの形態に限られるものではない。また、上記の説明で用いる図面は、図示の便宜上、部材ないし部分の縦横の縮尺は実際のものとは異なる模式図である。

また、本発明は上記実施の形態に限定されるものではなく、本発明の目的を達成できる範囲での変形、改良等は本発明に含まれるものである。

【符号の説明】

【0088】

1…集積回路、2,2A〜2C…誤り検出回路、3…メモリ回路、3a…メモリ・セル・アレイ(MCA)、3b…アドレス・デコーダー(ADEC)、3c…制御部(Control)、3d…データR/W部(DATA R/W)、20A,20B…遅延回路、21A,21A0〜21An…ラッチ回路、21B,21B0〜21Bn…ラッチ回路、21C…ラッチ回路、24,24_0〜24_n…比較回路、25…OR回路、27_0〜27_n…テスト回路、N0〜N6…NOTゲート、T0〜T3…伝送ゲート、NR0〜NR1…NORゲート、NA0〜NA7…NANDゲート

【特許請求の範囲】

【請求項1】

入力対象に入力する入力信号の状態を、第1クロック信号のエッジに基づく第1のタイミングで保持し、保持した状態を示す第1信号を出力する第1のラッチ回路と、

前記入力信号の状態を、第2クロック信号のエッジに基づく第2のタイミングで保持し、保持した状態を示す第2信号を出力する第2のラッチ回路と、

前記第1信号と前記第2信号とを比較して、比較結果に基づき両者が一致しているか否かを示す第3信号を出力する比較回路と、を備え、

前記第2のタイミングは、前記第1のタイミングから所定時間遅延したタイミングであることを特徴とする誤り検出回路。

【請求項2】

前記第1クロック信号と前記第2クロック信号とは同一のクロック信号であることを特徴とする請求項1に記載の誤り検出回路。

【請求項3】

複数の前記入力信号に対応する複数の請求項1又は請求項2に記載の誤り検出回路と、

前記複数の誤り検出回路の各比較回路から出力される前記第3信号に基づき、前記入力信号の誤りの有無を示す誤り検出信号を出力する出力回路と、を備えることを特徴とする誤り検出回路。

【請求項4】

前記第2クロック信号を所定時間遅延させた第3クロック信号のエッジに基づく第3のタイミングで、前記誤り検出信号の状態を保持し、保持した状態を示す第4の信号を出力する第3のラッチ回路を備えることを特徴とする請求項3に記載の誤り検出回路。

【請求項5】

前記第2のラッチ回路の前段において、前記入力信号と制御信号とを受信し、受信した制御信号に基づき、受信した入力信号又は前記受信した制御信号に対応する状態を示すテスト入力信号を前記第2のラッチ回路に出力するテスト回路を備えることを特徴とする請求項1乃至請求項4のいずれか1項に記載の誤り検出回路。

【請求項6】

請求項3乃至5のいずれか1項に記載の誤り検出回路と、

前記入力信号の入力対象であって、前記複数の誤り検出回路を介して受信した前記入力信号の状態に対応する情報を記憶するメモリ回路と、を備えることを特徴とする集積回路。

【請求項1】

入力対象に入力する入力信号の状態を、第1クロック信号のエッジに基づく第1のタイミングで保持し、保持した状態を示す第1信号を出力する第1のラッチ回路と、

前記入力信号の状態を、第2クロック信号のエッジに基づく第2のタイミングで保持し、保持した状態を示す第2信号を出力する第2のラッチ回路と、

前記第1信号と前記第2信号とを比較して、比較結果に基づき両者が一致しているか否かを示す第3信号を出力する比較回路と、を備え、

前記第2のタイミングは、前記第1のタイミングから所定時間遅延したタイミングであることを特徴とする誤り検出回路。

【請求項2】

前記第1クロック信号と前記第2クロック信号とは同一のクロック信号であることを特徴とする請求項1に記載の誤り検出回路。

【請求項3】

複数の前記入力信号に対応する複数の請求項1又は請求項2に記載の誤り検出回路と、

前記複数の誤り検出回路の各比較回路から出力される前記第3信号に基づき、前記入力信号の誤りの有無を示す誤り検出信号を出力する出力回路と、を備えることを特徴とする誤り検出回路。

【請求項4】

前記第2クロック信号を所定時間遅延させた第3クロック信号のエッジに基づく第3のタイミングで、前記誤り検出信号の状態を保持し、保持した状態を示す第4の信号を出力する第3のラッチ回路を備えることを特徴とする請求項3に記載の誤り検出回路。

【請求項5】

前記第2のラッチ回路の前段において、前記入力信号と制御信号とを受信し、受信した制御信号に基づき、受信した入力信号又は前記受信した制御信号に対応する状態を示すテスト入力信号を前記第2のラッチ回路に出力するテスト回路を備えることを特徴とする請求項1乃至請求項4のいずれか1項に記載の誤り検出回路。

【請求項6】

請求項3乃至5のいずれか1項に記載の誤り検出回路と、

前記入力信号の入力対象であって、前記複数の誤り検出回路を介して受信した前記入力信号の状態に対応する情報を記憶するメモリ回路と、を備えることを特徴とする集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2011−229051(P2011−229051A)

【公開日】平成23年11月10日(2011.11.10)

【国際特許分類】

【出願番号】特願2010−98567(P2010−98567)

【出願日】平成22年4月22日(2010.4.22)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成23年11月10日(2011.11.10)

【国際特許分類】

【出願日】平成22年4月22日(2010.4.22)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]