誤ロック防止回路、防止方法及びそれを利用した遅延ロックループ

【課題】遅延ロックループにおいて誤ロックが生じた場合、そこから抜け出すために使用される誤ロック防止回路、防止方法及びそれを利用した遅延ロックループを提供する。

【解決手段】誤ロック防止回路はハーモニックロックを検出する検出器とスタックロックを検出する検出器とで構成される。ハーモニックロック検出器は前記遅延クロックを本発明の特徴的な方法でサンプリングする複数個のフリップフロップ及び論理部で構成される。ハーモニックロック検出器では基準クロックと基準クロックから遅延された複数個の遅延クロックの立ち上がりエッジを比較してこれらの立ち上がりエッジが基準クロックの1周期から離れた場合を検出する。スタックロック検出器は位相検出器の出力信号と前記遅延クロックのうち1つを利用した論理回路であり、論理演算の結果で位相検出器をリセットさせる。

【解決手段】誤ロック防止回路はハーモニックロックを検出する検出器とスタックロックを検出する検出器とで構成される。ハーモニックロック検出器は前記遅延クロックを本発明の特徴的な方法でサンプリングする複数個のフリップフロップ及び論理部で構成される。ハーモニックロック検出器では基準クロックと基準クロックから遅延された複数個の遅延クロックの立ち上がりエッジを比較してこれらの立ち上がりエッジが基準クロックの1周期から離れた場合を検出する。スタックロック検出器は位相検出器の出力信号と前記遅延クロックのうち1つを利用した論理回路であり、論理演算の結果で位相検出器をリセットさせる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は遅延ロックループ(DLL:Delay Locked Loop)に関し、特に基準クロックを用いて多相クロック(Multi−phasec lock)を生成する時の誤ロック(False Lock)を防止する技術に関する。

【背景技術】

【0002】

一般に遅延ロックループは遅延ライン(delay line)を利用して基準クロック(REF:Reference Clock)が遅延された多相クロックを生成する回路をいう。

【0003】

図1は、従来の技術による遅延ロックループの構成を示すブロック図である。

【0004】

図1を参照すると、従来の技術による遅延ロックループ30は基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジの位相差を比較して位相差に相応する位相差信号UP、DOWNを出力する位相検出器31、位相差信号UP、DOWNに相応する位相差電流を生成するチャージポンプ(charge pump)32、位相差電流を電圧信号に変換して制御電圧Vctrlを生成する低域フィルタ33及び制御電圧Vctrlに応じて基準クロックREFの遅延を調節することによって多相クロックを生成する電圧制御遅延ライン34を備える。

【0005】

多相クロックは基準クロックREFを所定の位相差で遅延させた遅延クロックで構成される。多相クロックのうち基準クロックREFを1周期だけ遅延させることによって基準クロックREFに同期化された最後の遅延クロックは位相検出器31に提供されるフィードバッククロックFEBになる。

【0006】

図2は、図1に示した位相検出器の構成を示すブロック図である。

【0007】

図2を参照すると、基準クロックREFがフィードバッククロックFEBより位相が先行していると、第1フリップフロップFF1は先ずアップ信号UPを活性化させて出力する。第2フリップフロップFF2は基準クロックREFとフィードバッククロックFEBの位相差による時間が経過した後にダウン信号DOWNを活性化させて出力する。ANDゲートADはアップ信号UPとダウン信号DOWNがすべて活性化されると第1フリップフロップFF1と第2フリップフロップFF2をリセット(reset)させる。

【0008】

フィードバッククロックFEBが基準クロックREFより位相が先行していると、第2フリップフロップFF2は先ずダウン信号DOWNを活性化させて出力する。第1フリップフロップFF1が位相差による時間が経過した後にアップ信号UPを活性化させて出力すると、ANDゲートADは第1フリップフロップFF1と第2フリップフロップFF2をリセットさせる。

【0009】

基準クロックREFとフィードバッククロックFEBの位相が同じ場合、第1フリップフロップFF1と第2フリップフロップFF2はそれぞれアップ信号UPとダウン信号DOWNを同時に活性化させてANDゲートADによって自らリセットされる。フィードバッククロックFEBが基準クロックREFより1周期だけ遅延されて基準クロックREFに同期されると遅延ロックループ30は正常なロック状態になる。

【0010】

遅延ロックループ30の設計時において重要なのは誤ロックが生じないように設計することである。遅延ロックループ30の誤ロック問題(false lock problem)はハーモニックロック(harmonic lock)とスタックロック(stuck lock)とを含む。

【0011】

ハーモニックロックとは基準クロックREFから遅延された信号であるフィードバッククロックFEBの遅延時間が基準クロックREFの1周期T1ではなく2周期T2、3周期T4及び4周期T4など1周期の整数倍の遅延時間である場合に遅延ロックループ30が誤ロックされた状態を維持することをいう。ハーモニックロックは基準クロックREFとフィードバッククロックFEBとが互いに位相差無く同期化された状態であるので、遅延ロックループ30はハーモニックロック状態を正常なロック状態と判断してしまう。

【0012】

図3は、従来の遅延ロックループが正常ロック状態である場合の多相クロックのタイミング図を示したものであり、図4は、従来の遅延ロックループがハーモニックロック状態(2周期)である場合の多相クロックのタイミング図を示したものであり、図5は、従来の遅延ロックループが他のハーモニックロック状態(3周期)である場合の多相クロックのタイミング図を示したものである。

【0013】

図3乃至5で多相クロックは第1遅延クロック乃至第14遅延クロックCLK1〜CLK14で構成され、第14遅延クロックは基準クロックREFを最終的に遅延させたフィードバッククロックFEBになる。ダウン信号DOWNの下部に表示された矢印はそれぞれ基準クロックREFと第1遅延クロック乃至第14遅延クロックCLK1〜CLK14の立ち上がりエッジ(positive edge)を示す。ここで14個の遅延クロックCLK1〜CLK14で構成された多相クロックを例に挙げたが、各矢印間の位相差は同じである。したがって、図3のように正常ロックの場合はその位相差はクロック1周期1Tを14個に均分した値になる。さらに、同じ方式で、図4のようにクロック2周期2Tのハーモニックロック状態ではその位相差がクロック2周期2Tを14個に均分した値になり、図5のようにクロック3周期3Tのハーモニックロック状態ではその位相差がクロック3周期3Tを14個に均分した値になる。

【0014】

図3乃至図5を参照すると、従来の遅延ロックループの正常なロック状態とハーモニックロック状態では共通的に基準クロックREFとフィードバッククロックFEBの位相が互いに一致する。したがって、従来の遅延ロックループはロック状態とハーモニックロック状態をすべて正常なロック状態と判断する問題点がある。

【0015】

スタックロックは電圧制御遅延ライン34の遅延時間が既に最小遅延時間に到達したにもかかわらず遅延ロックループ30が継続的に遅延時間を減らす方向に動作する場合に発生する。位相検出器31は基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジの位相を比較して位相差信号UP、DOWNを生成するが、位相検出器31が基準クロックREFとフィードバッククロックFEBとを誤って比較して誤った位相差信号UP、DOWNを生成するとスタックロック状態が発生する。例えば、電圧制御遅延ライン34が最小遅延を有する遅延ロックループで、制御電圧Vctrlが電源電圧VDDに既に到達した場合を仮定してみると、正しい動作のために位相検出器31はダウン信号DOWNを発生させて制御電圧Vctrlが低くなるようにすることで遅延時間を増加させなければならない。ところが、位相検出器31が基準クロックREFとフィードバッククロックFEBとを誤って比較した結果、制御電圧Vctrlを高めるアップ信号UPを発生させると制御電圧Vctrlは既に最高電圧の電源電圧に到達しているため、それに固定されてしまい遅延ロックループ30はこれ以上動作できないスタックロック状態に陥ることになる。

【0016】

図6は、従来の遅延ロックループがスタックロック状態である場合の多相クロック、非正常位相差信号及び正常位相差信号のタイミング図を示したものであり、制御電圧が電源電圧の時に電圧制御遅延ラインが最小遅延を有する遅延ロックループを例に上げたものである。

【0017】

図6を参照すると、位相検出器31が基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとを比較してフィードバッククロックFEBが基準クロックREFより位相が先行していると判断してダウン信号DOWNである正常位相差信号(Normal Signal)を出力すると遅延ロックループ30が正しく動作する。

【0018】

一方、位相検出器31が基準クロックREFとフィードバッククロックFEBの位相を比較する時、基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN番目の立ち上がりエッジとを比較して基準クロックREFがフィードバッククロックFEBより位相が先行していると誤って判断して非正常なアップUP信号を出力すると遅延ロックループ30はスタックロック状態になって正しく動作できなくなる。

【0019】

図6に図示してはいないが、スタックロックは制御電圧Vctrlが接地電圧VSSの時に電圧制御遅延ライン34が最小遅延を有する遅延ロックループでも発生し得る。

【0020】

制御電圧Vctrlが接地電圧VSSである場合、正しい動作のために位相検出器31はアップ信号UPを発生させて制御電圧Vctrlを上げて遅延時間を減少させなければならない。ところが、位相検出器31が基準クロックREFとフィードバッククロックFEBとを誤って比較して制御電圧Vctrlが低くなるようにするダウン信号DOWNを発生させると制御電圧Vctrlは既に最低電圧である接地電圧VSSに到達しているため、それに固定されてしまい遅延ロックループ30はこれ以上動作できないスタックロック状態に陥ることになる。

【0021】

図7は、従来の遅延ロックループの位相検出器の状態図(state diagram)である。

【0022】

図7を参照すると、基準クロックREFがフィードバッククロックFEBより位相が先行していると(Early REF)アップ信号UPが活性化(「1」)され、フィードバッククロックFEBが基準クロックREFより位相が先行していると(Late REF)ダウン信号DOWNが活性化(「1」)される。基準クロックREFとフィードバッククロックFEBの位相が一致して互いに同期化すると(Same REF&FEB)最終的にアップ信号UPとダウン信号DOWNが非活性化(「0」)状態に維持されてロック状態をそのまま維持するようになる。しかし、図7の従来の遅延ロックループの位相検出器の状態図からはハーモニックロック及びスタックロックなどの誤ロックを防止するための機能が備えられていないことがわかる。

【0023】

近年、遅延ロックループ(DLL)で誤ロックを防止しロックレンジ(lock range)を拡大するための研究が活発に進められている。そのうち1つはリセット回路(reset circuitry)を備えた位相検出器を用いる方法である(非特許文献1)。

【0024】

しかし、非特許文献1に開示された方法は、最初遅延ロックループが動作する前に常に電圧制御遅延ライン(VCDL:Voltage Controlled Delay Line)の遅延が最も小さい時点から開始しなければならない点と、電圧制御遅延ラインの遅延範囲VCDL_delayは「0<VCDL_delay<1.5周期」を満たさなければならないという制約がある。

【0025】

また、非特許文献1に開示された方法は何らかの理由によって遅延ロックループの初期状態が変わるか、遅延ロックループの動作中に様々な要因によって位相検出器がフィードバッククロックと基準クロックとを誤って比較する動作が一度だけでも発生した場合にはスタックロックが生じ得る。

【0026】

遅延ロックループで誤ロックを防止しロックレンジを拡大するための他の例としてはレプリカ遅延ライン(Replica Delay Line)を利用した方法を挙げることができる(非特許文献2)。

【0027】

非特許文献2ではレプリカ遅延ラインを利用した広帯域遅延ロックループ(wide−range DLL)を提案している。参考文献2に開示された方法でレプリカ遅延ラインは電流制御型位相検出器(CSPD:Current Steering Phase Detector)と低域フィルタとで構成され、電流制御型位相検出器のチャージポンプの電流比率(Ip:In)を正確に設定されなければならない問題点がある。

【0028】

しかし、非特許文献2で提案する広帯域遅延ロックループは基準クロックのデューティ比が所定の比率、例えば50%の時にのみ使用可能で、レプリカ遅延ラインで使用される電流ポンプの電流比率も正確に設計しなければならないなど多くの難点がある。

【先行技術文献】

【非特許文献】

【0029】

【非特許文献1】IEEE JOURNAL OF SOLID−STATE CIRCUITS,VOL.37,NO.11,NOVEMBER 2002(名称:A Low−Power Small−Area+−7.28−ps−Jitter 1−GHz DLL−Based Clock Generator)

【非特許文献2】IEEE JOURNAL OF SOLID−STATECIRCUITS,VOL.35,NO.3,MARCH 2000(名称:An All−Analog Multiphase Delay−Locked Loop Usinga Replica Delay Line for Wide−Range Operation and Low−Jitter Performance)

【発明の概要】

【発明が解決しようとする課題】

【0030】

したがって、本発明の目的は、基準クロックを遅延させて同期化された多相クロックを生成する時、ハーモニックロック状態を検出して誤ロックを防止する誤ロック防止回路及び遅延ロックループを提供することにある。

【0031】

本発明の他の目的は、基準クロックを遅延させて同期化された多相クロックを生成する時、スタックロック状態を検出してスタックロック状態を防止する誤ロック防止回路及び遅延ロックループを提供することにある。

【0032】

本発明の目的は上述した目的に制限されない。本発明の他の目的及び長所は以下の説明によってより明らかに理解されるであろう。

【課題を解決するための手段】

【0033】

上記した技術的課題を解決するための本発明の誤ロック防止回路は、基準クロック信号から遅延された複数個の遅延クロック信号を作り、この複数個の遅延クロック信号のうち少なくとも1つ以上のクロックの遷移エッジ(transition edge)が基準クロック信号の1周期内から離れて2周期、3周期などの整数倍の周期で誤ロックされたロック状態を検出し、そこから脱出させる検出器を備える。この検出器の一実施形態は複数個のフリップフロップからなるクロックサンプラと、複数個のフリップフロップからなる他のサンプラと、論理演算部と、で構成され、遅延クロックのサンプリングによって誤ロック状態を検出する。

【0034】

上記した本発明の他の技術的課題を解決するための本発明の遅延ロックループは、基準クロックと前記フィードバッククロックの位相差を検出する位相検出器、この検出の結果に応じて電流をソース(source)するか電流をシンク(sink)するチャージポンプ、制御電圧を発生させる低域通過フィルタ、制御電圧の変化に沿って各遅延時間間隔が増えるか減る複数個の遅延クロックを発生する電圧制御遅延ラインの複数個の遅延クロックを用いて基準クロックとフィードバッククロックの誤ロックを検出する誤ロック防止回路を備える。該誤ロック防止回路には互いに異なる原因を有する2つの誤ロックをそれぞれ検出する検出器が1つ以上が含まれる。

【0035】

上記したさらに他の技術的課題を解決するための本発明の誤ロック防止回路は、位相検出器の出力信号と基準クロックから遅延された複数個の遅延クロックのうち1つを選択してから論理演算を行い、演算結果によって誤ロックが発生したことを検出し、この検出によって、結果的に位相検出器はリセットされて誤ロックからの脱出を可能にする誤ロック検出器が含まれる。

【発明の効果】

【0036】

本発明は遅延ロックループのハーモニックロック状態を検出するにあたって遅延クロックの立ち上がりエッジを用いてハーモニックロック状態を検出するので基準クロックのデューティ比に影響されず誤ロックを防止でき、遅延クロックのうち1つを選択してハーモニックロック状態検出のためのサンプリングクロックとして使用することによって最大遅延範囲を拡張させることができる効果がある。

【0037】

また、本発明は基準クロックとフィードバッククロックとを誤って比較する場合に活性化されるスタックロック信号を用いて位相検出器をリセットさせることができるので、遅延ロックループがスタックロック状態に陥ることを防止できる効果もある。

【図面の簡単な説明】

【0038】

【図1】従来の技術による遅延ロックループの構成を示すブロック図である。

【図2】図1に示す位相検出器の構成を示すブロック図である。

【図3】従来の遅延ロックループが正常なロック状態である場合の多相クロックのタイミング図である。

【図4】従来の遅延ロックループがハーモニックロック状態(2周期)である場合の多相クロックのタイミング図である。

【図5】従来の遅延ロックループがハーモニックロック状態(3周期)である場合の多相クロックのタイミング図である。

【図6】従来の遅延ロックループがスタックロック状態である場合の多相クロック、非正常位相差信号及び正常位相差信号のタイミング図である。

【図7】従来の遅延ロックループの位相検出器の状態図である。

【図8】本発明の一実施形態による遅延ロックループのブロック図である。

【図9】図8の誤ロック防止回路の構成を示すブロック図である。

【図10】図9に示すハーモニックロック検出器の一実施形態による具現例を示す回路図である。

【図11】正常ロック状態時のハーモニックロック検出器の動作タイミング図である。

【図12】正常ロック状態を検出できる最大範囲を示すハーモニックロック検出器の動作タイミング図である。

【図13】正常ロック状態を検出できる最大範囲から離れた場合のハーモニックロック検出器の動作タイミング図である。

【図14】電圧制御遅延ラインで出力されるフィードバッククロックの遅延時間が基準クロックの2周期の間にある場合のハーモニックロック検出器の動作タイミング図である。

【図15】電圧制御遅延ラインで出力されるフィードバッククロックの遅延時間が基準クロックの3周期の間にある場合のハーモニックロック検出器の動作タイミング図である。

【図16】フィードバッククロックの遅延時間が基準クロックの1周期より小さい場合のハーモニックロック検出器の動作タイミング図である。

【図17】図9に示すスタックロック検出器の一実施形態による具現例を示す回路図である。

【図18】図8に示す位相検出器のブロック図である。

【図19】電圧制御遅延ラインの遅延時間が基準クロックの0.5周期より小さい時、基準クロックとフィードバッククロックとを正しく比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【図20】電圧制御遅延ラインの遅延時間が基準クロックの0.5周期より小さい時、基準クロックとフィードバッククロックとを誤って比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【図21】正常ロック状態を判断できる最大範囲内で、基準クロックとフィードバッククロックとを正しく比較する場合の位相検出器とスタックロック検出器の動作タイミングである。

【図22】正常ロック状態を判断できる最大範囲内で、基準クロックとフィードバッククロックとを誤って比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【図23】図8に示す位相検出器の状態図である。

【発明を実施するための形態】

【0039】

以下、添付図面を参照して、本発明の好ましい実施形態を詳細に説明すると次のとおりである。本明細書を説明する過程で用いられる数字、例えば、第1、第2などは同一又は類似の個体を区分するための識別記号に過ぎないものである。

【0040】

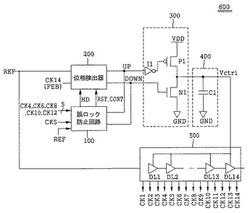

図8は、本発明の一実施形態による遅延ロックループのブロック図である。

【0041】

図8を参照すると、本発明の一実施形態による遅延ロックループ600は誤ロック防止回路100、位相検出器200、チャージポンプ300、低域フィルタ400及び電圧制御遅延ライン500を含む。遅延ロックループ600は電圧制御遅延ライン500を介して基準クロックREFを1周期だけ遅延させてフィードバッククロックFEBを生成し基準クロックREFとフィードバッククロックFEBとを同期化させる動作をする。

【0042】

電圧制御遅延ライン500は第1遅延素子DL1乃至第14遅延素子DL14を含み、低域フィルタ400を介して供給される制御電圧Vctrlに応じて基準クロックREFの位相遅延を調節して遅延クロックCK1〜CK14を生成する。電圧制御遅延ライン500は制御電圧Vctrlが電源電圧VDDの時に最小遅延を有し、制御電圧Vctrlが次第に低くなると遅延時間が増加する構造を有する。

【0043】

制御電圧Vctrlが電源電圧VDDである時、電圧制御遅延ライン500が最小遅延を有するようにするか、または制御電圧Vctrlが接地電圧VSSである時、電圧制御遅延ライン500が最小遅延を有するようにするかは設計者の選択によって変わり得る。

【0044】

遅延クロックCK1〜CK14は第1遅延素子DL1乃至第14遅延素子DL14に対応して生成された第1遅延クロックCK1乃至第14遅延クロックCK14を含む。第1遅延クロックCK1乃至第14遅延クロックCK14の間の位相差は互いに同じである。正常ロック状態で遅延クロックCK1〜CK14の間の位相差は基準クロックREFの1周期時間を遅延クロック個数である14で割った値であることがある。

【0045】

遅延クロックCK1〜CK14のうち最後に出力される最後の遅延クロックである第14遅延クロックCK14は位相検出器200に入力されるフィードバッククロックFEBとして使用され得る。遅延クロックCK1〜CK14のうち第4遅延クロックCK4、第6遅延クロックCK6、第8遅延クロックCK8、第10遅延クロックCK10及び第12遅延クロックCK12は誤ロック防止回路100に入力されるサンプリングクロックとして使用され得る。遅延クロックCK1〜CK14のうち中間程度の遅延を有する遅延クロック、例えば第5遅延クロックCK5は誤ロック防止回路100に入力される中間遅延クロックとして使用され得る。

【0046】

誤ロック防止回路100では基準クロックREFをクロックCK4、CK6、CK8、CK10及びCK12を用いてサンプリングした後、ハーモニックロック信号HDを生成し、位相差信号UP、DOWNと中間遅延クロックCK5を用いてスタックロック信号RST_CONTを生成する。位相差信号UP、DOWNは制御電圧Vctrlを下げるダウン信号DOWNと制御電圧Vctrlを上げるアップ信号UPとを含む。

【0047】

位相検出器200は基準クロックREFとフィードバッククロックFEBの位相差を比較して基準クロックREFとフィードバッククロックFEBの位相差による位相差信号UP、DOWNを出力する。位相検出器200は基準クロックREFの位相がフィードバッククロックFEBの位相より先行している場合はアップ信号UPを活性化させて出力し、フィードバッククロックFEBの位相が基準クロックREFの位相より先行している場合ダウン信号DOWNを活性化させて出力する。

【0048】

位相検出器200は基準クロックREFとフィードバッククロックFEBとを正しく比較するために基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとを比較する。フィードバッククロックFEBのN−1番目の立ち上がりエッジは基準クロックのREFのN番目の立ち上がりエッジが電圧制御遅延ライン500を介して1周期1T遅延されたものである。

【0049】

位相検出器200はハーモニックロック信号が活性化されて入力されると、電圧制御遅延ライン500の位相遅延を減らすことができる位相差信号UPを生成する。位相検出器200はスタックロック信号RST_CONTが活性化されて入力されると、リセットされて基準クロックREFとフィードバッククロックFEBとを正しく比較する動作を最初からやり直す。

【0050】

チャージポンプ300はアップ信号UPに応じてアップ電流(up current)を生成し、ダウン信号DOWNに応じてダウン電流(down current)を生成する。チャージポンプ300は電源電圧VDDとグラウンドGNDの間に直列に連結されたPMOSトランジスタP1とNMOSトランジスタN1を含むことができる。PMOSトランジスタP1の制御端子にはインバータI1を介してアップ信号UPが入力され、NMOSトランジスタN1の制御端子にはダウン信号DOWNが入力されることが好ましい。

【0051】

低域フィルタ400はアップ電流又はダウン電流を電圧信号に変換した後、高周波成分が除去された制御電圧Vctrlを生成する。低域フィルタ400はチャージポンプ300の出力端に一端が連結されグラウンドGNDに他端が連結されたキャパシタC1を含むことができる。

【0052】

図9は、図8の誤ロック防止回路の構成を示すブロック図である。

【0053】

図9を参照すると、誤ロック防止回路100はクロック信号CK4、CK6、CK8、CK10及びCK12で基準クロックREFをサンプリングした後、ハーモニックロック信号HDを生成するハーモニックロック検出器110を含む。誤ロック防止回路100は位相差信号UP、DOWNと中間遅延クロックCK5とを用いてスタックロック信号RST_CONTを生成するスタックロック検出器120を含む。誤ロック防止回路100はハーモニックロック検出器110又はスタックロック検出器120のみを備えても良く、ハーモニックロック検出器110及びスタックロック検出器120を両方備えても良い。

【0054】

図10は、図9に示すハーモニックロック検出器の一実施形態による具現例を示す回路図である。

【0055】

図10を参照すると、ハーモニックロック検出器110は分周器111、第1サンプラ112A及び第2サンプラ112B、ANDゲート113を含む。

【0056】

分周器111は基準クロックREFから2分周された2分周信号REF_2を出力する。

【0057】

第1サンプラ112Aは第1乃至第5フリップフロップFF11〜FF15を含む。2分周信号REF_2はクロック信号CK4、CK6、CK8、CK10、CK12によって第1乃至第5フリップフロップFF11〜FF15でそれぞれサンプリングされた後、出力信号Q11〜Q15に変換される。第1乃至第5フリップフロップFF11〜FF15はD型フリップフロップであることが好ましい。

【0058】

第2サンプラ112Bは第6乃至第9フリップフロップFF21〜FF24を含む。第1サンプラ112Aの出力信号Q11〜Q15のうちQ11、Q12、Q13、Q14はQ12、Q13、Q14及びQ15をクロック信号として認識するように設計された第6乃至第9フリップフロップFF21〜FF24で再びそれぞれサンプリングされた後、出力信号Q21〜Q24に変換される。第6乃至第9フリップフロップFF21〜FF24はD型フリップフロップであることが好ましい。

【0059】

ANDゲート113は第6乃至第9フリップフロップFF21〜FF24で出力される出力信号Q21〜Q24をAND演算してハーモニックロック信号HDを出力する。

【0060】

以下、ハーモニックロック検出器110がハーモニックロックを検出する原理に対してさらに詳細に説明すると次のとおりである。

【0061】

第1サンプラ112Aで使用されるクロック信号CK4、CK6、CK8、CK10及びCK12の立ち上がりエッジが基準クロックREFの1周期区間内にすべて存在する時、ハーモニックロック検出器110はハーモニックロック信号HDを「ハイ」にして出力して遅延ロックループ(DLL)600が正常動作するようにする。ハーモニックロック信号HDが「ハイ」にして出力される時、位相検出器200は基準クロックREFとフィードバッククロックFEBの位相を比較してアップ信号UPまたはダウン信号DOWNを出力する。すなわち、ハーモニックロックが生じていない状態であるので遅延ロックループはアップ信号UP又はダウン信号DOWNによって基準クロックREFとフィードバッククロックFEBの同期状態を持続的に維持する正常ロック状態にある。

【0062】

第1サンプラ112Aで使用されるクロックCK4、CK6、CK8、CK10及びCK12の立ち上がりエッジのうち1つ以上が基準クロックREFの1周期区間内に存在しない時、ハーモニックロック検出器110はハーモニックロック状態が発生したか、又は正しいロック状態を検出できる範囲から離れたと判断してハーモニックロック信号HDを「ロー」に活性化させて出力する(active low)。ハーモニックロック信号HDが「ロー」にして出力されるとハーモニックロックが生じたことを意味するので位相検出器200は基準クロックREFとフィードバッククロックFEBの位相差がどのようであるかにかかわらず電圧制御遅延ライン500の遅延時間を減らす位相差信号DOWNを出力する。この動作によってフィードバッククロックFEBの遅延時間は次第に減り、最終的には基準クロックREFから1周期の遅延を有する時に正常なロック状態に留まるようになる。

【0063】

以上の説明ではクロックの立ち上がりエッジ(rising edge)の存在の有無でハーモニックロックの発生の有無を判断したが設計の変更によってはクロックの立ち下がりエッジ(falling edge)の存在の有無でハーモニックロックの発生び有無を判断可能であることは無論である。

【0064】

本実施形態のハーモニックロック検出器110はハーモニックロック状態を検出するとハーモニックロック信号HDを「ロー」に活性化させて出力し、ハーモニックロック状態を検出できなかった場合はハーモニックロック信号を「ハイ」にして出力することを例示的に説明したが、本発明はこれに限定されず、ハーモニックロック信号HDを他のロジックレベルで出力することもできる。

【0065】

また、第1サンプラ112Aが5個のフリップフロップFF11〜FF15を用いて2分周信号REF_2をサンプリングし、第2サンプラ112Bが4個のフリップフロップFF21〜FF24を用いて第1乃至第4サンプリング信号Q11〜Q14をサンプリングする場合を例にあげて説明したが、フリップフロップの個数及び分周信号は適用する回路及び環境に沿って様々に変わることができる。

【0066】

図11は、正常ロック状態時のハーモニックロック検出器の動作タイミング図である。図11に示す「4」、「6」、「8」、「10」、「12」はハーモニックロック検出に用いられたクロック信号CK4、CK6、CK8、CK10及びCK12の立ち上がりエッジ(positive edge、rising edge)を意味する。

【0067】

図11を参照すると、基準クロックREFの毎周期内にクロック信号CK2、CK4、CK6、CK8、CK10及びCK12の全ての立ち上がりエッジが存在するのでハーモニックロック検出器110はハーモニックロック信号HDを「ハイ」にして出力する。これは遅延ロックループ600が正常動作状態であることを意味する。この場合、第1サンプラ112Aの第1乃至第5フリップフロップFF11〜FF15はクロック信号CK4、CK6、CK8、CK10及びCK12の間の遅延間隔と同じ遅延間隔を有する第1乃至第5出力信号Q11〜Q15を出力する。

【0068】

第2サンプラ112Bの第6乃至第9フリップフロップFF21〜FF24は第1乃至第4出力信号Q11〜Q14を第2乃至第5出力信号Q12〜Q15でそれぞれサンプリングする。第2乃至第5出力信号Q12〜Q15の立ち上がりエッジ地点で第1乃至第4出力信号Q11〜Q14がそれぞれ「ハイ」状態であるので第6乃至第9出力信号Q21〜Q24をすべて「ハイ」にして出力する。したがって、ANDゲート113はハーモニックロック信号HDを「ハイ」にして出力して正常なロック状態であることを知らせる。

【0069】

図12は、正常ロック状態を検出できる最大範囲を示すハーモニックロック検出器の動作タイミング図である。

【0070】

図12を参照すると、第1乃至第5フリップフロップFF11〜FF15のクロックCK4、CK6、CK8、CK10及びCK12の立ち上がりエッジのうち位相が最も遅い第12遅延クロックCK12の立ち上がりエッジ「12」が基準クロックREFの立ち上がりエッジと一致する地点に位置する。このような状態はハーモニックロック検出器110が正しいロック状態を検出できる最大範囲を示す。このような場合、全てのクロック信号CK4、CK6、CK8、CK10及びCK12の立ち上がりエッジが基準クロックREFの毎周期区間内に存在するのでハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ハイ」にして出力する。したがって、遅延クロックCK1〜CK14のうちクロック信号CK4、CK6、CK8、CK10及びCK12とは異なる位相を有する遅延クロックをサンプリングクロックとして使用する場合、ハーモニックロック検出器110が正常ロック状態を検出できる最大範囲は変更され得る。

【0071】

図13は、正常ロック状態を検出できる最大範囲から離れた場合のハーモニックロック検出器の動作タイミング図である。

【0072】

図13を参照すると、クロック信号CK4、CK6、CK8、CK10及びCK12の立ち上がりエッジのうち位相が最も遅い第12遅延クロックCK12の立ち上がりエッジ「12」は基準クロックREFの1周期から離れることに比べ、第2遅延クロックCK2から第10遅延クロックCK10の立ち上がりエッジ「10」までは基準クロックREFの1周期内に属することがわかる。

【0073】

基準クロックREFの毎周期内にクロックCK4、CK6、CK8、CK10及びCK12の全ての立ち上がりエッジが存在しないのでハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ロー」に活性化させて出力する。これはハーモニックロックが生じたことを意味する。ハーモニックロック信号HDが「ロー」に活性化されて出力されると、遅延ロックループ600の位相検出器200はハーモニックロックを除去できるように電圧制御遅延ライン500の遅延時間を減らす方向に動作する。

【0074】

これをより具体的に説明する。上記のようにハーモニックロックが生じた場合、第1サンプラ112Aの第5フリップフロップFF15は第12遅延クロックCK12の立ち上がりエッジ地点で2分周信号REF_2の論理レベルをサンプリングして第5出力信号Q15を出力する。

【0075】

第2サンプラ112Bの第6乃至第9フリップフロップFF21〜FF24は第1乃至第4出力信号Q11〜Q14を第2乃至第5出力信号Q12〜Q15でそれぞれサンプリングする。第2乃至第4出力信号Q12〜Q14の立ち上がりエッジ地点で第1乃至第3出力信号Q11〜Q13がそれぞれ「ハイ」状態であるので第6乃至第8フリップフロップFF21〜FF23は第6乃至第8出力信号Q21〜Q23を「ハイ」にして出力する。一方、第5出力信号Q15の立ち上がりエッジ地点で第4出力信号Q14が「ロー」状態であるので第9フリップフロップFF24は第9出力信号Q24を「ロー」にして出力する。したがって、ハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ロー」にして出力してハーモニックロックが生じたことを知らせる。

【0076】

図14及び図15は、電圧制御遅延ラインで出力されるフィードバッククロックFEBの遅延時間がそれぞれ基準クロックの2周期及び3周期の間にある場合のハーモニックロック検出器110の動作タイミング図である。

【0077】

図14を参照すると、フィードバッククロックFEBの遅延時間が基準クロックREFの2周期の間にある場合、基準クロックREFの1周期範囲から離れて最初に迎える信号である第8遅延クロックCK8によって第2サンプラ112Bの第7フリップフロップFF22で「ロー」の信号が出力される。これにより、ハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ロー」にして出力してハーモニックロック状態が生じたことを知らせる。

【0078】

図15を参照すると、フィードバッククロックFEBの遅延時間が基準クロックREFの3周期の間にある場合、基準クロックREFの1周期範囲から始めて離れて最初に迎える信号である第6遅延クロックCK6によって第2サンプラ112Bの第6フリップフロップFF21で「ロー」の信号Q21が出力される。これにより、ハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ロー」にして出力してハーモニックロック状態が生じたことを知らせる。

【0079】

図16は、フィードバッククロックFEBの遅延時間が基準クロックの1周期より小さい場合のハーモニックロック検出器の動作タイミング図である。

【0080】

図16を参照すると、全ての遅延クロックCK1〜CK14の立ち上がりエッジが基準クロックREFの1周期内に存在するのでハーモニックロック検出器110は正常ロック状態であると判断してハーモニックロック信号HDを「ハイ」にして出力する。

【0081】

ところが、仮に全ての遅延クロックCK1〜CK14の立ち上がりエッジが基準クロックREFの1周期内に存在し、さらにフィードバッククロックFEBの遅延時間も基準クロックREFの1周期より小さいとしても、位相検出器200が誤った位相差信号、例えばアップ信号UPを生成してしまうと、遅延ロックループ600が電圧制御遅延ライン500の遅延時間を減らす方向に動作するようになるので、スタックロック状態が生じ得る。

【0082】

以下、スタックロックの発生に対して説明する。図17は、図9に示すスタックロック検出器の一実施形態による具現例を示す回路図である。

【0083】

図17を参照すると、スタックロック検出器120は中間遅延クロックCK5の立ち上がりエッジを基準にして予め設定された幅を有する立ち上がりエッジ検出信号RST_CKを生成する立ち上がりエッジ検出部121、アップ信号UPと立ち上がりエッジ検出信号RST_CKをAND演算する第2ANDゲートAD12、ダウン信号DOWNと立ち上がりエッジ検出信号RST_CKをAND演算する第3ANDゲートAD13及び第2ANDゲートAD12の出力と第3ANDゲートAD13の出力とをOR演算する第1ORゲートOR11を含む。

【0084】

立ち上がりエッジ検出部121は中間遅延クロックCK5の位相を反転させる第1インバータI11、第1インバータI11の出力を遅延させる第1遅延器DL11及び第1遅延器DL11の出力D_CK5_Bと中間遅延クロックCK5をAND演算して立ち上がりエッジ検出信号RST_CKとして出力する第1ANDゲートAD11を含む。予め設定された幅は第1遅延器DL11により決定されることができる。本実施形態では中間遅延クロックCK5が第5遅延クロックCK5である場合を例に挙げて説明したが、これに限定されず第1遅延クロックCK1より遅延時間が大きく第14遅延クロックCK14より遅延時間が小さい他の遅延クロックCK2〜CK4、CK6〜CK13のいずれかを使用しても同じ効果を得ることができる。

【0085】

図18は、図8に示す位相検出器のブロック図である。

【0086】

図18を参照すると、位相検出器200は第1フリップフロップFF1、第2フリップフロップFF2、アップ信号出力部211、ダウン信号出力部212及びリセット制御部213を含む。

【0087】

第1フリップフロップFF1のデータ入力端子Dには電源電圧VDDが、クロック端子CKには基準クロックREFが連結され、出力信号としてはアップ信号UPが出力端子Qで生成される。第2フリップフロップFF2のデータ入力端子Dには電源電圧VDDが、クロック端子CKにはフィードバッククロックFEBが連結され、ダウン信号DOWNは出力端子Qで生成される。基準クロックREFの位相がフィードバッククロックFEBの位相より先行している場合は第1フリップフロップFF1からアップ信号UPが出力され、フィードバッククロックFEBの位相が基準クロックREFの位相より先行している場合は第2フリップフロップFF2からダウン信号DOWNが出力される。

【0088】

アップ信号出力部211の第1スイッチTG1は第1フリップフロップFF1の出力端子Qとアップ信号UP出力端子の間に位置しハーモニックロック信号対HD、HD_Bに応じてアップ信号UPの出力を断続する。アップ信号出力部211の第2スイッチTG2は電源電圧VDDとアップ信号出力端子の間に位置しハーモニックロック信号対HD_B、HDに応じて電源電圧VDDの出力を断続する。第1スイッチTG1と第2スイッチTG2はハーモニックロック信号対HD、HD_Bに応じて相補的に動作することが好ましい。

【0089】

ダウン信号出力部212の第3スイッチTG3は第2フリップフロップFF2の出力端子Qとダウン信号出力端子の間に位置しハーモニックロック信号対HD、HD_Bに応じてダウン信号DOWNの出力を断続する。第4スイッチTG4はグラウンドGNDとダウン信号出力端子の間に位置しハーモニックロック信号対HD_B、HDに応じてグラウンドGNDとダウン信号出力パッドの連結を断続する。第3スイッチTG3と第4スイッチTG4はハーモニックロック信号対HD、HD_Bに応じて相補的に動作することが好ましい。

【0090】

リセット制御部213は第1フリップフロップFF1及び第2フリップフロップFF2の出力端子Qから出力される出力信号をAND演算するANDゲートAD1及びスタックロック信号RST_CONSTとANDゲートAD1の出力をOR演算するORゲートOR1を含む。

【0091】

電圧制御遅延ライン500の遅延時間が正常ロック状態を検出できる最大範囲内に存在する時、誤ロック防止回路100のハーモニックロック検出器110は位相検出器200にハーモニックロック信号HDを「ハイ」にして供給する。したがって、電源電圧VDDはアップ信号出力部211の第2スイッチTG2によってアップ信号UPに出力されないように遮断され、接地電源GNDはダウン信号出力部212の第4スイッチTG4によって遮断されてダウン信号DOWNに出力されない。第1フリップフロップFF1で出力されるアップ信号UPはアップ信号出力部211の第1スイッチTG1を介してチャージポンプ300側に出力され、第2フリップフロップFF2で出力されるダウン信号DOWNはダウン信号出力部212の第3スイッチTG3を介してチャージポンプ300側に出力される。

【0092】

ハーモニックロック信号HDが「ロー」に活性化されて位相検出器200に供給されると、基準クロックREFの遅延時間が基準クロックREFの1周期を超えたかハーモニックロックが生じた状態であることを意味するので位相検出器200は遅延時間を減らすために制御電圧Vctrlのレベルを上げなければならない。このために、アップ信号出力部211は電源電圧VDDを第2スイッチTG2を介してアップ信号UPで出力し、ダウン信号出力部212は接地電源GNDを第4スイッチTG4を介してダウン信号DOWNに出力する。これにより、電圧制御遅延ライン500で基準クロックREFの遅延時間が迅速に減ってハーモニックロック状態を防止できるようになる。

【0093】

一方、電圧制御遅延ライン500の遅延時間が誤ロック検出器100のハーモニックロック検出器110が正常ロック状態を検出できる最大範囲内に存在する時、誤ロック防止回路100内のハーモニックロック検出器110は位相検出器200に活性化されたリセット信号RST_CONTを供給しない。これにより、位相検出器200の第1及び第2フリップフロップFF1、FF2はリセット制御部213のアップ信号UPとダウン信号DOWNの演算結果による出力信号によってのみリセットされる。しかし、誤ロック防止回路100のハーモニックロック検出器110が位相検出器200にスタックロック信号RST_CONTを供給すると、リセット制御部213を介して第1及び第2フリップフロップFF1、FF2がリセットされ、程なく位相検出器200全体がリセットされる。

【0094】

図19は、電圧制御遅延ラインの遅延時間が基準クロックの0.5周期より小さい時、基準クロックとフィードバッククロックを正しく比較する場合の位相検出器及びスタックロック検出器の動作タイミング図である。

【0095】

図19を参照すると、基準クロックREFのN番目の立ち上がりエッジ位相よりフィードバッククロックFEBのN−1番目の立ち上がりエッジ位相が先行しているので、位相検出器200は位相差に該当する区間の間ダウン信号DOWNを「ハイ」に活性化させて出力し、ダウン信号DOWNが「ロー」に遷移された立ち下がりエッジに同期された瞬間的パルスをアップ信号UP(図示せず)に出力する。ここで位相差は正常ロック状態のために増加させるべき遅延量を示す。

【0096】

本実施形態は制御電圧Vctrlが増加するほど電圧制御遅延ライン500の遅延時間が減少するように設計された場合であるので正常信号(Normal signal)はダウン信号DOWNになる。アップ信号UPはダウン信号DOWNが「ハイ」から「ロー」になる時、非常に短い時間の間「ロー」から「ハイ」になり再び「ロー」となる。この時、ダウン信号DOWNが「ハイ」から「ロー」になる時間とアップ信号UPが「ハイ」から「ロー」になる時間は一致する。アップ信号UPの「ハイ」区間は位相検出器200のフリップフロップをリセットさせるために必要な非常に短い時間である。

【0097】

ハーモニックロック検出器110はサンプリングクロックCK1〜CK14のすべてが基準クロックREFの1周期内にあるのでハーモニックロック信号HDを「ハイ」にして出力してハーモニックロック状態ではないことを知らせる。スタックロック検出器120の立ち上がりエッジ検出部121は中間遅延信号CK5と、中間遅延信号CK5を反転させて遅延させた信号D_CK5_BとをAND演算して立ち上がりエッジ検出信号RST_CKパルスを生成する。立ち上がりエッジ検出信号RST_CKは電圧制御遅延ライン500によって遅延された時間内に生成される。

【0098】

スタックロック検出器120のORゲートOR1は立ち上がりエッジ検出信号RST_CKとダウン信号DOWNが同時に「ハイ」の区間が発生するとスタックロック信号RST_CONTを「ハイ」に活性化させる。本実施形態では、ダウン信号DOWNと立ち上がりエッジ検出信号RST_CKの「ハイ」区間が重複しないのでスタックロック信号RST_CONTは「ロー」状態を維持する。この場合、ダウン信号DOWN及び基準クロックREFの立ち上がりエッジで第1フリップフロップFF1が瞬間的に発生するアップ信号UPのAND演算によって位相検出器200はリセットされる。

【0099】

図20は、電圧制御遅延ラインの遅延時間が基準クロックの0.5周期より小さい時、基準クロックとフィードバッククロックを誤って比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【0100】

図20を参照すると、位相検出器200が初期値の誤りなどの何らかの理由によって基準クロックREFのN−1番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとを比較するようになると、基準クロックREFのN−1番目の立ち上がりエッジの位相がフィードバッククロックFEBの位相より先行しているので位相検出器200は電圧制御遅延ライン500によって遅延された遅延時間を減少させなければならない位相差であると判断する。

【0101】

したがって、位相検出器200は非正常アップ信号(Abnormal UP)を生成して制御電圧Vctrlを増加させ、遅延ロックループは制御電圧Vctrlに応じて基準クロックREFのN−1番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとの間の位相差を減らす方向に動作するようになる。非正常アップ信号が「ハイ」である区間は位相検出器200が減少させなければならない位相差であると認識する遅延時間である。非正常ダウン信号(Abnormal DOWN)は遅延時間が経過した後フィードバッククロックFEBの立ち上がりエッジによって生成される信号である。

【0102】

ここで、非正常アップ信号とは誤ロック状態でのアップUP信号を意味し、正常なロック状態であれば発生すべきではない信号状態をいう。非正常ダウン信号も同様であり、以下ですべて同じ意味に使われる。

【0103】

もし、従来の遅延ロックループのように、本実施形態によるスタックロック検出器120が存在しない場合、位相検出器200は基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN番目の立ち上がりエッジとを再び比較するようになり、遅延ロックループ600は継続的に電圧制御遅延ライン500の遅延時間を減らす方向に動作するようになってスタックロック状態から抜け出すことができなくなる。

【0104】

しかし、本発明の一実施形態によるスタックロック検出器120を備えた場合、スタックロック検出器120の立ち上がりエッジ検出部121は電圧制御遅延ライン500によって遅延された遅延時間区間内に立ち上がりエッジ検出信号RST_CKを生成する。スタックロック検出器120はAND演算を介して非正常アップ信号と立ち上がりエッジ検出信号RST_CKの「ハイ」が重複する区間で活性化されるスタックロック信号RST_CONTを出力する。スタックロック信号RST_CONTはリセット制御部213のORゲートOR1を介して位相検出器200の第1フリップフロップFF1と第2フリップフロップFF2をリセットさせ、非正常アップ信号が正常アップ信号に訂正されることができるようにする。

【0105】

その後、スタックロック信号RST_CONTによってリセットされた位相検出器200はフィードバッククロックFEBのN−1番目の立ち上がりエッジと基準クロックREFのN番目の立ち上がりエッジとを比較するようになるので、遅延ロックループ600が電圧制御遅延ライン500の遅延時間を増加させる方向に動作するようにする訂正された正常ダウン信号(Corrected DOWN)と訂正された正常アップ信号(Corrected UP)を生成して正常なロック状態に戻る。

【0106】

したがって、本実施形態による遅延ロックループ600は位相検出器200が何らかの理由によって基準クロックのN−1番目の立ち上がりエッジとフィードバッククロックのN−1番目の立ち上がりエッジとを比較して誤ったアップ信号を生成しても、スタックロック検出器120で生成されたリセット信号RST_CONTによって位相検出器200がリセットされて基準クロックのN番目の立ち上がりエッジとフィードバッククロックのN−1番目の立ち上がりエッジとを正しく比較することができる。そして、遅延ロックループ600でスタックロック状態が生じることを防止できるようになり、基準クロックREFを1周期だけ遅延させてその基準クロックREFとフィードバッククロックFEBを同期化させることができるようになる。

【0107】

図21は、正常ロック状態を判断できる最大範囲内で、基準クロックとフィードバッククロックを正しく比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【0108】

図21を参照すると、基準クロックREFのN番目の立ち上がりエッジの位相がフィードバッククロックFEBN−1番目の立ち上がりエッジの位相より先行しているので、位相検出器200はアップ信号UPを生成して制御電圧Vctrlによって電圧制御遅延ライン500の遅延が減少する方向に動作する。アップ信号UPの「ハイ」区間は電圧制御遅延ライン500が減少させるべき遅延量に対応する。スタックロック検出器120の立ち上がりエッジ検出部121は電圧制御遅延ライン500によって遅延された遅延時間区間内に立ち上がりエッジ検出信号RST_CKを生成する。

【0109】

ハーモニックロック検出器110が正常ロック状態であると判断できる最大範囲内で、位相検出器200が基準クロックREFとフィードバッククロックFEBとを正しく比較判断すると、立ち上がりエッジ検出信号RST_CKとアップ信号UPの「ハイ」が重複する区間が存在しないのでスタックロック検出器120はスタックロック信号RST_CONTを活性化させない。

【0110】

したがって、位相検出器200はスタックロック信号RST_CONTによってリセットされず基準クロックREFとフィードバッククロックFEBの位相差を減らす方向に正常動作するようになる。

【0111】

図22は、正常ロック状態を判断できる最大範囲内で、基準クロックとフィードバッククロックを誤って比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【0112】

図22を参照すると、基準クロックREFがフィードバッククロックFEBより基準クロックREFのN番目の立ち上がりエッジからフィードバッククロックFEBのN−1番目の立ち上がりエッジまでの間の区間だけ先行しているので、基準クロックREFとフィードバッククロックFEBの同期を合わせるためにはフィードバッククロックFEBの遅延を減少させなければならないことがわかる。

【0113】

ところが、位相検出器200が初期値の誤りなどの何らかの理由によって基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−2番目の立ち上がりエッジとを比較するようになると、フィードバッククロックFEBが基準クロックREFよりフィードバッククロックFEBのN−2番目の立ち上がりエッジから基準クロックREFの立ち上がりエッジまでの間の区間だけ先行しているので、位相検出器200は基準クロックREFとフィードバッククロックFEBの同期を合わせるためにフィードバッククロックFEBの遅延を増加させるべきであると判断するようになり非正常ダウン信号を生成するようになる。

【0114】

本実施形態によるスタックロック検出器120が存在しない従来の遅延ロックループでは、位相検出器200は引続き基準クロックのN+1番目の立ち上がりエッジとフィードバッククロックのN−1番目の立ち上がりエッジとを比較した後、引き続き基準クロックのN+2番目の立ち上がりエッジとフィードバッククロックのN番目の立ち上がりエッジとを比較するようになるので遅延ロックループ500はスタックロック状態から抜け出すことができなくなる。

【0115】

本発明の一実施形態によるスタックロック検出器120を備えた場合、スタックロック検出器120の立ち上がりエッジ検出部121は電圧制御遅延ライン500によって遅延された遅延時間区間内に立ち上がりエッジ検出信号RST_CKを生成する。スタックロック検出器120は立ち上がりエッジ検出信号RST_CKと非正常ダウン信号をAND演算して非正常ダウン信号と立ち上がりエッジ検出信号RST_CKの「ハイ」が重複する区間で活性化されるスタックロック信号RST_CONTを出力する。スタックロック信号RST_CONTはリセット制御部213のORゲートOR1を介して位相検出器200の第1フリップフロップFF1と第2フリップフロップFF2をリセットさせ、非正常ダウン信号を正常ダウン信号に訂正する。

【0116】

その後、スタックロック信号RST_CONTによってリセットされた位相検出器200はフィードバッククロックFEBのN−1番目の立ち上がりエッジと基準クロックREFのN番目の立ち上がりエッジとを比較するようになるので、遅延ロックループ600が電圧制御遅延ライン500の遅延時間を減少させる方向に動作するようにする正常ダウン信号を生成する。

【0117】

したがって、上記のように位相検出器200が基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−2番目の立ち上がりエッジとを誤って比較判断する場合にもスタックロック状態が生じることを防止できるようになり、基準クロックREFを1周期だけ遅延させてその基準クロックREFとフィードバッククロックFEBを同期化させることができるようになる。

【0118】

本発明の実施形態による遅延ロックループ600は次の2つの状態のうちいずれかの状態になることができる。

【0119】

第一、誤ロック防止回路100がハーモニックロック信号HDとスタックロック信号RST_CONTをすべて「ハイ」にして出力すると、位相検出器200は図20のように基準クロックREFのN−1番目の立ち上がりエッジと前記フィードバッククロックFEBのN−1番目の立ち上がりエッジの位相を比較する場合、及び図22のように基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−2番目の立ち上がりエッジの位相を比較する場合にもすべてスタックロック信号RST_CONTによってリセットされ得る。位相検出器200がスタックロック信号RST_CONTによってリセットされたので、その後は基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとを正常に比較できるようになる。すなわち、基準クロックREFとフィードバッククロックFEBの位相を正しく比較して遅延ロックループ600が正常にロック状態になることができる。

【0120】

第二、誤ロック防止回路100がハーモニックロック信号HDを「ハイ」にして出力し、スタックロック信号RST_CONTを引き続き「ロー」にして出力する場合、基準クロックREFとフィードバッククロックFEBの位相を正しく比較している状態であるので位相検出器200の動作によって遅延ロックループ600は正常にロック状態になることができる。

【0121】

図23は、図8に示す位相検出器の状態図である。

【0122】

図23を参照すると、本実施形態による位相検出器200はハーモニックロック信号HDが「0」(ロジック「ロー」)であれば遅延ロックループ600がいかなる状態にあってもアップ信号UPは「1」(ロジック「ハイ」)で、ダウン信号DOWNは「0」になるロジックを含む。したがって、本実施形態による固定遅延ループ600はハーモニックロック状態で基準クロックREFとフィードバッククロックFEBの位相を同期させるために電圧制御遅延ライン500の遅延を減少させる方向に動作できるようになる。

【0123】

ハーモニックロック信号HDが「1」で、基準クロックREFとフィードバッククロックFEBの位相を比較して基準クロックREFが先行していると、アップ信号UPは「1」で、ダウン信号は「0」になる。ハーモニックロック信号HDが「1」で、基準クロックREFとフィードバッククロックFEBの位相を比較して基準クロックREFが遅れていると、アップ信号UPは「0」で、ダウン信号は「1」になる。ハーモニックロック信号HDが「1」で、基準クロックREFとフィードバッククロックFEBの位相を比較して互いに同じであると判明すると、アップ信号UPは「0」で、ダウン信号も「0」になる。

【0124】

アップ信号UPは「1」で、ダウン信号は「0」であるか、アップ信号UPは「0」で、ダウン信号は「1」である状態で、リセット信号RST_CONTが「1」になると、これは位相検出器200が基準クロックREFとフィードバッククロックFEBの位相を誤って比較したことを意味する。本実施形態による位相検出器200は何らかの理由によって基準クロックREFとフィードバッククロックFEBとを誤って比較してスタックロック状態に陥り得る状態になるとスタックロック信号RST_CONTによって訂正され得るロジックを含む。

【0125】

したがって、アップ信号UPは「1」で、ダウン信号は「0」である状態でリセット信号RST_CONTが「1」になると、アップ信号UPは「0」、ダウン信号は「1」の状態に訂正され、アップ信号UPは「0」で、ダウン信号は「1」である状態でリセット信号RST_CONTが「1」になると、アップ信号UPは「1」、ダウン信号は「0」の状態に訂正され、基準クロックREFとフィードバッククロックFEBの位相を同期させることができるようになる。

【0126】

ロック状態はアップ信号UPとダウン信号DOWNがすべて「0」である状態でハーモニックロック信号HDが「1」で基準クロックREFとフィードバッククロックFEBの位相差が「0」に維持される状態である。

【0127】

本発明の実施形態による誤ロック防止回路100が適用される遅延ロックループ600で電圧制御遅延ライン500の遅延範囲VCDL delayは0<VCDL delay<2*T*Nの範囲を有する。ここで、「N」は前記制御遅延ライン500の遅延素子DL1〜DLnの個数を意味する。したがって、図8のように前記制御遅延ライン500が14個の遅延素子を用いる場合、制御遅延ライン500の遅延範囲は0<VCDL delay<28*Tの範囲を有する。

【0128】

また、本発明の実施形態による誤ロック防止回路100のハーモニックロック検出器110とスタックロック検出器120は電圧制御遅延ライン500で生成された第1乃至第14クロックCK1〜CK14の立ち上がりエッジを使用してハーモニックロック及びスタックロック状態を検出するので、固定遅延ループ600は基準クロックのデューティ比に影響されず動作できる利点を有する。

【0129】

本実施形態で電圧制御遅延ライン500は制御電圧Vctrlが電源電圧VDDの時に最小遅延を有し、ダウン信号DOWNによって制御電圧Vctrlが次第に低くなると遅延時間が増加する構造を例示して説明したが、本発明はこれに限定されない。例えば、電圧制御遅延ライン500は制御電圧Vctrlが接地電圧VSSの時に最小遅延を有し、アップ信号UPによって制御電圧Vctrlが次第に高くなると遅延時間が増加する構造を有し得る。電圧制御遅延ライン500の制御電圧Vctrlが接地電圧VSSの時に最小遅延を有する場合の構成及び動作は電圧制御遅延ライン500が制御電圧Vctrlが電源電圧VDDの時に最小遅延を有する上記した説明から当業者が容易に理解できるものであるので詳細な説明は省略する。

【0130】

本実施形態で電圧制御遅延ライン500は14個の遅延素子を有し、遅延素子に対応して14個の遅延クロックを含む場合を例示して説明したが、本発明はこれに限定されず、適用されるシステムによって異なる個数の遅延素子を有し得る。

【0131】

以上、本発明の好ましい実施形態に対して詳細に説明したが、本発明の権利範囲はこれに限定されず下記の特許請求の範囲で定義する本発明の基本概念に基づいて様々な実施形態に具現されることができ、このような実施形態も本発明の権利範囲に属するものである。

【符号の説明】

【0132】

100:誤ロック防止回路

110:ハーモニックロック検出器

111:2分周器

112A:第1サンプラ

112B:第2サンプラ

113:ANDゲート

120:スタックロック検出器

200:位相検出器

300:チャージポンプ

400:低域フィルタ

500:電圧制御遅延ライン

600:遅延ロックループ

【技術分野】

【0001】

本発明は遅延ロックループ(DLL:Delay Locked Loop)に関し、特に基準クロックを用いて多相クロック(Multi−phasec lock)を生成する時の誤ロック(False Lock)を防止する技術に関する。

【背景技術】

【0002】

一般に遅延ロックループは遅延ライン(delay line)を利用して基準クロック(REF:Reference Clock)が遅延された多相クロックを生成する回路をいう。

【0003】

図1は、従来の技術による遅延ロックループの構成を示すブロック図である。

【0004】

図1を参照すると、従来の技術による遅延ロックループ30は基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジの位相差を比較して位相差に相応する位相差信号UP、DOWNを出力する位相検出器31、位相差信号UP、DOWNに相応する位相差電流を生成するチャージポンプ(charge pump)32、位相差電流を電圧信号に変換して制御電圧Vctrlを生成する低域フィルタ33及び制御電圧Vctrlに応じて基準クロックREFの遅延を調節することによって多相クロックを生成する電圧制御遅延ライン34を備える。

【0005】

多相クロックは基準クロックREFを所定の位相差で遅延させた遅延クロックで構成される。多相クロックのうち基準クロックREFを1周期だけ遅延させることによって基準クロックREFに同期化された最後の遅延クロックは位相検出器31に提供されるフィードバッククロックFEBになる。

【0006】

図2は、図1に示した位相検出器の構成を示すブロック図である。

【0007】

図2を参照すると、基準クロックREFがフィードバッククロックFEBより位相が先行していると、第1フリップフロップFF1は先ずアップ信号UPを活性化させて出力する。第2フリップフロップFF2は基準クロックREFとフィードバッククロックFEBの位相差による時間が経過した後にダウン信号DOWNを活性化させて出力する。ANDゲートADはアップ信号UPとダウン信号DOWNがすべて活性化されると第1フリップフロップFF1と第2フリップフロップFF2をリセット(reset)させる。

【0008】

フィードバッククロックFEBが基準クロックREFより位相が先行していると、第2フリップフロップFF2は先ずダウン信号DOWNを活性化させて出力する。第1フリップフロップFF1が位相差による時間が経過した後にアップ信号UPを活性化させて出力すると、ANDゲートADは第1フリップフロップFF1と第2フリップフロップFF2をリセットさせる。

【0009】

基準クロックREFとフィードバッククロックFEBの位相が同じ場合、第1フリップフロップFF1と第2フリップフロップFF2はそれぞれアップ信号UPとダウン信号DOWNを同時に活性化させてANDゲートADによって自らリセットされる。フィードバッククロックFEBが基準クロックREFより1周期だけ遅延されて基準クロックREFに同期されると遅延ロックループ30は正常なロック状態になる。

【0010】

遅延ロックループ30の設計時において重要なのは誤ロックが生じないように設計することである。遅延ロックループ30の誤ロック問題(false lock problem)はハーモニックロック(harmonic lock)とスタックロック(stuck lock)とを含む。

【0011】

ハーモニックロックとは基準クロックREFから遅延された信号であるフィードバッククロックFEBの遅延時間が基準クロックREFの1周期T1ではなく2周期T2、3周期T4及び4周期T4など1周期の整数倍の遅延時間である場合に遅延ロックループ30が誤ロックされた状態を維持することをいう。ハーモニックロックは基準クロックREFとフィードバッククロックFEBとが互いに位相差無く同期化された状態であるので、遅延ロックループ30はハーモニックロック状態を正常なロック状態と判断してしまう。

【0012】

図3は、従来の遅延ロックループが正常ロック状態である場合の多相クロックのタイミング図を示したものであり、図4は、従来の遅延ロックループがハーモニックロック状態(2周期)である場合の多相クロックのタイミング図を示したものであり、図5は、従来の遅延ロックループが他のハーモニックロック状態(3周期)である場合の多相クロックのタイミング図を示したものである。

【0013】

図3乃至5で多相クロックは第1遅延クロック乃至第14遅延クロックCLK1〜CLK14で構成され、第14遅延クロックは基準クロックREFを最終的に遅延させたフィードバッククロックFEBになる。ダウン信号DOWNの下部に表示された矢印はそれぞれ基準クロックREFと第1遅延クロック乃至第14遅延クロックCLK1〜CLK14の立ち上がりエッジ(positive edge)を示す。ここで14個の遅延クロックCLK1〜CLK14で構成された多相クロックを例に挙げたが、各矢印間の位相差は同じである。したがって、図3のように正常ロックの場合はその位相差はクロック1周期1Tを14個に均分した値になる。さらに、同じ方式で、図4のようにクロック2周期2Tのハーモニックロック状態ではその位相差がクロック2周期2Tを14個に均分した値になり、図5のようにクロック3周期3Tのハーモニックロック状態ではその位相差がクロック3周期3Tを14個に均分した値になる。

【0014】

図3乃至図5を参照すると、従来の遅延ロックループの正常なロック状態とハーモニックロック状態では共通的に基準クロックREFとフィードバッククロックFEBの位相が互いに一致する。したがって、従来の遅延ロックループはロック状態とハーモニックロック状態をすべて正常なロック状態と判断する問題点がある。

【0015】

スタックロックは電圧制御遅延ライン34の遅延時間が既に最小遅延時間に到達したにもかかわらず遅延ロックループ30が継続的に遅延時間を減らす方向に動作する場合に発生する。位相検出器31は基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジの位相を比較して位相差信号UP、DOWNを生成するが、位相検出器31が基準クロックREFとフィードバッククロックFEBとを誤って比較して誤った位相差信号UP、DOWNを生成するとスタックロック状態が発生する。例えば、電圧制御遅延ライン34が最小遅延を有する遅延ロックループで、制御電圧Vctrlが電源電圧VDDに既に到達した場合を仮定してみると、正しい動作のために位相検出器31はダウン信号DOWNを発生させて制御電圧Vctrlが低くなるようにすることで遅延時間を増加させなければならない。ところが、位相検出器31が基準クロックREFとフィードバッククロックFEBとを誤って比較した結果、制御電圧Vctrlを高めるアップ信号UPを発生させると制御電圧Vctrlは既に最高電圧の電源電圧に到達しているため、それに固定されてしまい遅延ロックループ30はこれ以上動作できないスタックロック状態に陥ることになる。

【0016】

図6は、従来の遅延ロックループがスタックロック状態である場合の多相クロック、非正常位相差信号及び正常位相差信号のタイミング図を示したものであり、制御電圧が電源電圧の時に電圧制御遅延ラインが最小遅延を有する遅延ロックループを例に上げたものである。

【0017】

図6を参照すると、位相検出器31が基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとを比較してフィードバッククロックFEBが基準クロックREFより位相が先行していると判断してダウン信号DOWNである正常位相差信号(Normal Signal)を出力すると遅延ロックループ30が正しく動作する。

【0018】

一方、位相検出器31が基準クロックREFとフィードバッククロックFEBの位相を比較する時、基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN番目の立ち上がりエッジとを比較して基準クロックREFがフィードバッククロックFEBより位相が先行していると誤って判断して非正常なアップUP信号を出力すると遅延ロックループ30はスタックロック状態になって正しく動作できなくなる。

【0019】

図6に図示してはいないが、スタックロックは制御電圧Vctrlが接地電圧VSSの時に電圧制御遅延ライン34が最小遅延を有する遅延ロックループでも発生し得る。

【0020】

制御電圧Vctrlが接地電圧VSSである場合、正しい動作のために位相検出器31はアップ信号UPを発生させて制御電圧Vctrlを上げて遅延時間を減少させなければならない。ところが、位相検出器31が基準クロックREFとフィードバッククロックFEBとを誤って比較して制御電圧Vctrlが低くなるようにするダウン信号DOWNを発生させると制御電圧Vctrlは既に最低電圧である接地電圧VSSに到達しているため、それに固定されてしまい遅延ロックループ30はこれ以上動作できないスタックロック状態に陥ることになる。

【0021】

図7は、従来の遅延ロックループの位相検出器の状態図(state diagram)である。

【0022】

図7を参照すると、基準クロックREFがフィードバッククロックFEBより位相が先行していると(Early REF)アップ信号UPが活性化(「1」)され、フィードバッククロックFEBが基準クロックREFより位相が先行していると(Late REF)ダウン信号DOWNが活性化(「1」)される。基準クロックREFとフィードバッククロックFEBの位相が一致して互いに同期化すると(Same REF&FEB)最終的にアップ信号UPとダウン信号DOWNが非活性化(「0」)状態に維持されてロック状態をそのまま維持するようになる。しかし、図7の従来の遅延ロックループの位相検出器の状態図からはハーモニックロック及びスタックロックなどの誤ロックを防止するための機能が備えられていないことがわかる。

【0023】

近年、遅延ロックループ(DLL)で誤ロックを防止しロックレンジ(lock range)を拡大するための研究が活発に進められている。そのうち1つはリセット回路(reset circuitry)を備えた位相検出器を用いる方法である(非特許文献1)。

【0024】

しかし、非特許文献1に開示された方法は、最初遅延ロックループが動作する前に常に電圧制御遅延ライン(VCDL:Voltage Controlled Delay Line)の遅延が最も小さい時点から開始しなければならない点と、電圧制御遅延ラインの遅延範囲VCDL_delayは「0<VCDL_delay<1.5周期」を満たさなければならないという制約がある。

【0025】

また、非特許文献1に開示された方法は何らかの理由によって遅延ロックループの初期状態が変わるか、遅延ロックループの動作中に様々な要因によって位相検出器がフィードバッククロックと基準クロックとを誤って比較する動作が一度だけでも発生した場合にはスタックロックが生じ得る。

【0026】

遅延ロックループで誤ロックを防止しロックレンジを拡大するための他の例としてはレプリカ遅延ライン(Replica Delay Line)を利用した方法を挙げることができる(非特許文献2)。

【0027】

非特許文献2ではレプリカ遅延ラインを利用した広帯域遅延ロックループ(wide−range DLL)を提案している。参考文献2に開示された方法でレプリカ遅延ラインは電流制御型位相検出器(CSPD:Current Steering Phase Detector)と低域フィルタとで構成され、電流制御型位相検出器のチャージポンプの電流比率(Ip:In)を正確に設定されなければならない問題点がある。

【0028】

しかし、非特許文献2で提案する広帯域遅延ロックループは基準クロックのデューティ比が所定の比率、例えば50%の時にのみ使用可能で、レプリカ遅延ラインで使用される電流ポンプの電流比率も正確に設計しなければならないなど多くの難点がある。

【先行技術文献】

【非特許文献】

【0029】

【非特許文献1】IEEE JOURNAL OF SOLID−STATE CIRCUITS,VOL.37,NO.11,NOVEMBER 2002(名称:A Low−Power Small−Area+−7.28−ps−Jitter 1−GHz DLL−Based Clock Generator)

【非特許文献2】IEEE JOURNAL OF SOLID−STATECIRCUITS,VOL.35,NO.3,MARCH 2000(名称:An All−Analog Multiphase Delay−Locked Loop Usinga Replica Delay Line for Wide−Range Operation and Low−Jitter Performance)

【発明の概要】

【発明が解決しようとする課題】

【0030】

したがって、本発明の目的は、基準クロックを遅延させて同期化された多相クロックを生成する時、ハーモニックロック状態を検出して誤ロックを防止する誤ロック防止回路及び遅延ロックループを提供することにある。

【0031】

本発明の他の目的は、基準クロックを遅延させて同期化された多相クロックを生成する時、スタックロック状態を検出してスタックロック状態を防止する誤ロック防止回路及び遅延ロックループを提供することにある。

【0032】

本発明の目的は上述した目的に制限されない。本発明の他の目的及び長所は以下の説明によってより明らかに理解されるであろう。

【課題を解決するための手段】

【0033】

上記した技術的課題を解決するための本発明の誤ロック防止回路は、基準クロック信号から遅延された複数個の遅延クロック信号を作り、この複数個の遅延クロック信号のうち少なくとも1つ以上のクロックの遷移エッジ(transition edge)が基準クロック信号の1周期内から離れて2周期、3周期などの整数倍の周期で誤ロックされたロック状態を検出し、そこから脱出させる検出器を備える。この検出器の一実施形態は複数個のフリップフロップからなるクロックサンプラと、複数個のフリップフロップからなる他のサンプラと、論理演算部と、で構成され、遅延クロックのサンプリングによって誤ロック状態を検出する。

【0034】

上記した本発明の他の技術的課題を解決するための本発明の遅延ロックループは、基準クロックと前記フィードバッククロックの位相差を検出する位相検出器、この検出の結果に応じて電流をソース(source)するか電流をシンク(sink)するチャージポンプ、制御電圧を発生させる低域通過フィルタ、制御電圧の変化に沿って各遅延時間間隔が増えるか減る複数個の遅延クロックを発生する電圧制御遅延ラインの複数個の遅延クロックを用いて基準クロックとフィードバッククロックの誤ロックを検出する誤ロック防止回路を備える。該誤ロック防止回路には互いに異なる原因を有する2つの誤ロックをそれぞれ検出する検出器が1つ以上が含まれる。

【0035】

上記したさらに他の技術的課題を解決するための本発明の誤ロック防止回路は、位相検出器の出力信号と基準クロックから遅延された複数個の遅延クロックのうち1つを選択してから論理演算を行い、演算結果によって誤ロックが発生したことを検出し、この検出によって、結果的に位相検出器はリセットされて誤ロックからの脱出を可能にする誤ロック検出器が含まれる。

【発明の効果】

【0036】

本発明は遅延ロックループのハーモニックロック状態を検出するにあたって遅延クロックの立ち上がりエッジを用いてハーモニックロック状態を検出するので基準クロックのデューティ比に影響されず誤ロックを防止でき、遅延クロックのうち1つを選択してハーモニックロック状態検出のためのサンプリングクロックとして使用することによって最大遅延範囲を拡張させることができる効果がある。

【0037】

また、本発明は基準クロックとフィードバッククロックとを誤って比較する場合に活性化されるスタックロック信号を用いて位相検出器をリセットさせることができるので、遅延ロックループがスタックロック状態に陥ることを防止できる効果もある。

【図面の簡単な説明】

【0038】

【図1】従来の技術による遅延ロックループの構成を示すブロック図である。

【図2】図1に示す位相検出器の構成を示すブロック図である。

【図3】従来の遅延ロックループが正常なロック状態である場合の多相クロックのタイミング図である。

【図4】従来の遅延ロックループがハーモニックロック状態(2周期)である場合の多相クロックのタイミング図である。

【図5】従来の遅延ロックループがハーモニックロック状態(3周期)である場合の多相クロックのタイミング図である。

【図6】従来の遅延ロックループがスタックロック状態である場合の多相クロック、非正常位相差信号及び正常位相差信号のタイミング図である。

【図7】従来の遅延ロックループの位相検出器の状態図である。

【図8】本発明の一実施形態による遅延ロックループのブロック図である。

【図9】図8の誤ロック防止回路の構成を示すブロック図である。

【図10】図9に示すハーモニックロック検出器の一実施形態による具現例を示す回路図である。

【図11】正常ロック状態時のハーモニックロック検出器の動作タイミング図である。

【図12】正常ロック状態を検出できる最大範囲を示すハーモニックロック検出器の動作タイミング図である。

【図13】正常ロック状態を検出できる最大範囲から離れた場合のハーモニックロック検出器の動作タイミング図である。

【図14】電圧制御遅延ラインで出力されるフィードバッククロックの遅延時間が基準クロックの2周期の間にある場合のハーモニックロック検出器の動作タイミング図である。

【図15】電圧制御遅延ラインで出力されるフィードバッククロックの遅延時間が基準クロックの3周期の間にある場合のハーモニックロック検出器の動作タイミング図である。

【図16】フィードバッククロックの遅延時間が基準クロックの1周期より小さい場合のハーモニックロック検出器の動作タイミング図である。

【図17】図9に示すスタックロック検出器の一実施形態による具現例を示す回路図である。

【図18】図8に示す位相検出器のブロック図である。

【図19】電圧制御遅延ラインの遅延時間が基準クロックの0.5周期より小さい時、基準クロックとフィードバッククロックとを正しく比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【図20】電圧制御遅延ラインの遅延時間が基準クロックの0.5周期より小さい時、基準クロックとフィードバッククロックとを誤って比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【図21】正常ロック状態を判断できる最大範囲内で、基準クロックとフィードバッククロックとを正しく比較する場合の位相検出器とスタックロック検出器の動作タイミングである。

【図22】正常ロック状態を判断できる最大範囲内で、基準クロックとフィードバッククロックとを誤って比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【図23】図8に示す位相検出器の状態図である。

【発明を実施するための形態】

【0039】

以下、添付図面を参照して、本発明の好ましい実施形態を詳細に説明すると次のとおりである。本明細書を説明する過程で用いられる数字、例えば、第1、第2などは同一又は類似の個体を区分するための識別記号に過ぎないものである。

【0040】

図8は、本発明の一実施形態による遅延ロックループのブロック図である。

【0041】

図8を参照すると、本発明の一実施形態による遅延ロックループ600は誤ロック防止回路100、位相検出器200、チャージポンプ300、低域フィルタ400及び電圧制御遅延ライン500を含む。遅延ロックループ600は電圧制御遅延ライン500を介して基準クロックREFを1周期だけ遅延させてフィードバッククロックFEBを生成し基準クロックREFとフィードバッククロックFEBとを同期化させる動作をする。

【0042】

電圧制御遅延ライン500は第1遅延素子DL1乃至第14遅延素子DL14を含み、低域フィルタ400を介して供給される制御電圧Vctrlに応じて基準クロックREFの位相遅延を調節して遅延クロックCK1〜CK14を生成する。電圧制御遅延ライン500は制御電圧Vctrlが電源電圧VDDの時に最小遅延を有し、制御電圧Vctrlが次第に低くなると遅延時間が増加する構造を有する。

【0043】

制御電圧Vctrlが電源電圧VDDである時、電圧制御遅延ライン500が最小遅延を有するようにするか、または制御電圧Vctrlが接地電圧VSSである時、電圧制御遅延ライン500が最小遅延を有するようにするかは設計者の選択によって変わり得る。

【0044】

遅延クロックCK1〜CK14は第1遅延素子DL1乃至第14遅延素子DL14に対応して生成された第1遅延クロックCK1乃至第14遅延クロックCK14を含む。第1遅延クロックCK1乃至第14遅延クロックCK14の間の位相差は互いに同じである。正常ロック状態で遅延クロックCK1〜CK14の間の位相差は基準クロックREFの1周期時間を遅延クロック個数である14で割った値であることがある。

【0045】

遅延クロックCK1〜CK14のうち最後に出力される最後の遅延クロックである第14遅延クロックCK14は位相検出器200に入力されるフィードバッククロックFEBとして使用され得る。遅延クロックCK1〜CK14のうち第4遅延クロックCK4、第6遅延クロックCK6、第8遅延クロックCK8、第10遅延クロックCK10及び第12遅延クロックCK12は誤ロック防止回路100に入力されるサンプリングクロックとして使用され得る。遅延クロックCK1〜CK14のうち中間程度の遅延を有する遅延クロック、例えば第5遅延クロックCK5は誤ロック防止回路100に入力される中間遅延クロックとして使用され得る。

【0046】

誤ロック防止回路100では基準クロックREFをクロックCK4、CK6、CK8、CK10及びCK12を用いてサンプリングした後、ハーモニックロック信号HDを生成し、位相差信号UP、DOWNと中間遅延クロックCK5を用いてスタックロック信号RST_CONTを生成する。位相差信号UP、DOWNは制御電圧Vctrlを下げるダウン信号DOWNと制御電圧Vctrlを上げるアップ信号UPとを含む。

【0047】

位相検出器200は基準クロックREFとフィードバッククロックFEBの位相差を比較して基準クロックREFとフィードバッククロックFEBの位相差による位相差信号UP、DOWNを出力する。位相検出器200は基準クロックREFの位相がフィードバッククロックFEBの位相より先行している場合はアップ信号UPを活性化させて出力し、フィードバッククロックFEBの位相が基準クロックREFの位相より先行している場合ダウン信号DOWNを活性化させて出力する。

【0048】

位相検出器200は基準クロックREFとフィードバッククロックFEBとを正しく比較するために基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとを比較する。フィードバッククロックFEBのN−1番目の立ち上がりエッジは基準クロックのREFのN番目の立ち上がりエッジが電圧制御遅延ライン500を介して1周期1T遅延されたものである。

【0049】

位相検出器200はハーモニックロック信号が活性化されて入力されると、電圧制御遅延ライン500の位相遅延を減らすことができる位相差信号UPを生成する。位相検出器200はスタックロック信号RST_CONTが活性化されて入力されると、リセットされて基準クロックREFとフィードバッククロックFEBとを正しく比較する動作を最初からやり直す。

【0050】

チャージポンプ300はアップ信号UPに応じてアップ電流(up current)を生成し、ダウン信号DOWNに応じてダウン電流(down current)を生成する。チャージポンプ300は電源電圧VDDとグラウンドGNDの間に直列に連結されたPMOSトランジスタP1とNMOSトランジスタN1を含むことができる。PMOSトランジスタP1の制御端子にはインバータI1を介してアップ信号UPが入力され、NMOSトランジスタN1の制御端子にはダウン信号DOWNが入力されることが好ましい。

【0051】

低域フィルタ400はアップ電流又はダウン電流を電圧信号に変換した後、高周波成分が除去された制御電圧Vctrlを生成する。低域フィルタ400はチャージポンプ300の出力端に一端が連結されグラウンドGNDに他端が連結されたキャパシタC1を含むことができる。

【0052】

図9は、図8の誤ロック防止回路の構成を示すブロック図である。

【0053】

図9を参照すると、誤ロック防止回路100はクロック信号CK4、CK6、CK8、CK10及びCK12で基準クロックREFをサンプリングした後、ハーモニックロック信号HDを生成するハーモニックロック検出器110を含む。誤ロック防止回路100は位相差信号UP、DOWNと中間遅延クロックCK5とを用いてスタックロック信号RST_CONTを生成するスタックロック検出器120を含む。誤ロック防止回路100はハーモニックロック検出器110又はスタックロック検出器120のみを備えても良く、ハーモニックロック検出器110及びスタックロック検出器120を両方備えても良い。

【0054】

図10は、図9に示すハーモニックロック検出器の一実施形態による具現例を示す回路図である。

【0055】

図10を参照すると、ハーモニックロック検出器110は分周器111、第1サンプラ112A及び第2サンプラ112B、ANDゲート113を含む。

【0056】

分周器111は基準クロックREFから2分周された2分周信号REF_2を出力する。

【0057】

第1サンプラ112Aは第1乃至第5フリップフロップFF11〜FF15を含む。2分周信号REF_2はクロック信号CK4、CK6、CK8、CK10、CK12によって第1乃至第5フリップフロップFF11〜FF15でそれぞれサンプリングされた後、出力信号Q11〜Q15に変換される。第1乃至第5フリップフロップFF11〜FF15はD型フリップフロップであることが好ましい。

【0058】

第2サンプラ112Bは第6乃至第9フリップフロップFF21〜FF24を含む。第1サンプラ112Aの出力信号Q11〜Q15のうちQ11、Q12、Q13、Q14はQ12、Q13、Q14及びQ15をクロック信号として認識するように設計された第6乃至第9フリップフロップFF21〜FF24で再びそれぞれサンプリングされた後、出力信号Q21〜Q24に変換される。第6乃至第9フリップフロップFF21〜FF24はD型フリップフロップであることが好ましい。

【0059】

ANDゲート113は第6乃至第9フリップフロップFF21〜FF24で出力される出力信号Q21〜Q24をAND演算してハーモニックロック信号HDを出力する。

【0060】

以下、ハーモニックロック検出器110がハーモニックロックを検出する原理に対してさらに詳細に説明すると次のとおりである。

【0061】

第1サンプラ112Aで使用されるクロック信号CK4、CK6、CK8、CK10及びCK12の立ち上がりエッジが基準クロックREFの1周期区間内にすべて存在する時、ハーモニックロック検出器110はハーモニックロック信号HDを「ハイ」にして出力して遅延ロックループ(DLL)600が正常動作するようにする。ハーモニックロック信号HDが「ハイ」にして出力される時、位相検出器200は基準クロックREFとフィードバッククロックFEBの位相を比較してアップ信号UPまたはダウン信号DOWNを出力する。すなわち、ハーモニックロックが生じていない状態であるので遅延ロックループはアップ信号UP又はダウン信号DOWNによって基準クロックREFとフィードバッククロックFEBの同期状態を持続的に維持する正常ロック状態にある。

【0062】

第1サンプラ112Aで使用されるクロックCK4、CK6、CK8、CK10及びCK12の立ち上がりエッジのうち1つ以上が基準クロックREFの1周期区間内に存在しない時、ハーモニックロック検出器110はハーモニックロック状態が発生したか、又は正しいロック状態を検出できる範囲から離れたと判断してハーモニックロック信号HDを「ロー」に活性化させて出力する(active low)。ハーモニックロック信号HDが「ロー」にして出力されるとハーモニックロックが生じたことを意味するので位相検出器200は基準クロックREFとフィードバッククロックFEBの位相差がどのようであるかにかかわらず電圧制御遅延ライン500の遅延時間を減らす位相差信号DOWNを出力する。この動作によってフィードバッククロックFEBの遅延時間は次第に減り、最終的には基準クロックREFから1周期の遅延を有する時に正常なロック状態に留まるようになる。

【0063】

以上の説明ではクロックの立ち上がりエッジ(rising edge)の存在の有無でハーモニックロックの発生の有無を判断したが設計の変更によってはクロックの立ち下がりエッジ(falling edge)の存在の有無でハーモニックロックの発生び有無を判断可能であることは無論である。

【0064】

本実施形態のハーモニックロック検出器110はハーモニックロック状態を検出するとハーモニックロック信号HDを「ロー」に活性化させて出力し、ハーモニックロック状態を検出できなかった場合はハーモニックロック信号を「ハイ」にして出力することを例示的に説明したが、本発明はこれに限定されず、ハーモニックロック信号HDを他のロジックレベルで出力することもできる。

【0065】

また、第1サンプラ112Aが5個のフリップフロップFF11〜FF15を用いて2分周信号REF_2をサンプリングし、第2サンプラ112Bが4個のフリップフロップFF21〜FF24を用いて第1乃至第4サンプリング信号Q11〜Q14をサンプリングする場合を例にあげて説明したが、フリップフロップの個数及び分周信号は適用する回路及び環境に沿って様々に変わることができる。

【0066】

図11は、正常ロック状態時のハーモニックロック検出器の動作タイミング図である。図11に示す「4」、「6」、「8」、「10」、「12」はハーモニックロック検出に用いられたクロック信号CK4、CK6、CK8、CK10及びCK12の立ち上がりエッジ(positive edge、rising edge)を意味する。

【0067】

図11を参照すると、基準クロックREFの毎周期内にクロック信号CK2、CK4、CK6、CK8、CK10及びCK12の全ての立ち上がりエッジが存在するのでハーモニックロック検出器110はハーモニックロック信号HDを「ハイ」にして出力する。これは遅延ロックループ600が正常動作状態であることを意味する。この場合、第1サンプラ112Aの第1乃至第5フリップフロップFF11〜FF15はクロック信号CK4、CK6、CK8、CK10及びCK12の間の遅延間隔と同じ遅延間隔を有する第1乃至第5出力信号Q11〜Q15を出力する。

【0068】

第2サンプラ112Bの第6乃至第9フリップフロップFF21〜FF24は第1乃至第4出力信号Q11〜Q14を第2乃至第5出力信号Q12〜Q15でそれぞれサンプリングする。第2乃至第5出力信号Q12〜Q15の立ち上がりエッジ地点で第1乃至第4出力信号Q11〜Q14がそれぞれ「ハイ」状態であるので第6乃至第9出力信号Q21〜Q24をすべて「ハイ」にして出力する。したがって、ANDゲート113はハーモニックロック信号HDを「ハイ」にして出力して正常なロック状態であることを知らせる。

【0069】

図12は、正常ロック状態を検出できる最大範囲を示すハーモニックロック検出器の動作タイミング図である。

【0070】

図12を参照すると、第1乃至第5フリップフロップFF11〜FF15のクロックCK4、CK6、CK8、CK10及びCK12の立ち上がりエッジのうち位相が最も遅い第12遅延クロックCK12の立ち上がりエッジ「12」が基準クロックREFの立ち上がりエッジと一致する地点に位置する。このような状態はハーモニックロック検出器110が正しいロック状態を検出できる最大範囲を示す。このような場合、全てのクロック信号CK4、CK6、CK8、CK10及びCK12の立ち上がりエッジが基準クロックREFの毎周期区間内に存在するのでハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ハイ」にして出力する。したがって、遅延クロックCK1〜CK14のうちクロック信号CK4、CK6、CK8、CK10及びCK12とは異なる位相を有する遅延クロックをサンプリングクロックとして使用する場合、ハーモニックロック検出器110が正常ロック状態を検出できる最大範囲は変更され得る。

【0071】

図13は、正常ロック状態を検出できる最大範囲から離れた場合のハーモニックロック検出器の動作タイミング図である。

【0072】

図13を参照すると、クロック信号CK4、CK6、CK8、CK10及びCK12の立ち上がりエッジのうち位相が最も遅い第12遅延クロックCK12の立ち上がりエッジ「12」は基準クロックREFの1周期から離れることに比べ、第2遅延クロックCK2から第10遅延クロックCK10の立ち上がりエッジ「10」までは基準クロックREFの1周期内に属することがわかる。

【0073】

基準クロックREFの毎周期内にクロックCK4、CK6、CK8、CK10及びCK12の全ての立ち上がりエッジが存在しないのでハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ロー」に活性化させて出力する。これはハーモニックロックが生じたことを意味する。ハーモニックロック信号HDが「ロー」に活性化されて出力されると、遅延ロックループ600の位相検出器200はハーモニックロックを除去できるように電圧制御遅延ライン500の遅延時間を減らす方向に動作する。

【0074】

これをより具体的に説明する。上記のようにハーモニックロックが生じた場合、第1サンプラ112Aの第5フリップフロップFF15は第12遅延クロックCK12の立ち上がりエッジ地点で2分周信号REF_2の論理レベルをサンプリングして第5出力信号Q15を出力する。

【0075】

第2サンプラ112Bの第6乃至第9フリップフロップFF21〜FF24は第1乃至第4出力信号Q11〜Q14を第2乃至第5出力信号Q12〜Q15でそれぞれサンプリングする。第2乃至第4出力信号Q12〜Q14の立ち上がりエッジ地点で第1乃至第3出力信号Q11〜Q13がそれぞれ「ハイ」状態であるので第6乃至第8フリップフロップFF21〜FF23は第6乃至第8出力信号Q21〜Q23を「ハイ」にして出力する。一方、第5出力信号Q15の立ち上がりエッジ地点で第4出力信号Q14が「ロー」状態であるので第9フリップフロップFF24は第9出力信号Q24を「ロー」にして出力する。したがって、ハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ロー」にして出力してハーモニックロックが生じたことを知らせる。

【0076】

図14及び図15は、電圧制御遅延ラインで出力されるフィードバッククロックFEBの遅延時間がそれぞれ基準クロックの2周期及び3周期の間にある場合のハーモニックロック検出器110の動作タイミング図である。

【0077】

図14を参照すると、フィードバッククロックFEBの遅延時間が基準クロックREFの2周期の間にある場合、基準クロックREFの1周期範囲から離れて最初に迎える信号である第8遅延クロックCK8によって第2サンプラ112Bの第7フリップフロップFF22で「ロー」の信号が出力される。これにより、ハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ロー」にして出力してハーモニックロック状態が生じたことを知らせる。

【0078】

図15を参照すると、フィードバッククロックFEBの遅延時間が基準クロックREFの3周期の間にある場合、基準クロックREFの1周期範囲から始めて離れて最初に迎える信号である第6遅延クロックCK6によって第2サンプラ112Bの第6フリップフロップFF21で「ロー」の信号Q21が出力される。これにより、ハーモニックロック検出器110のANDゲート113はハーモニックロック信号HDを「ロー」にして出力してハーモニックロック状態が生じたことを知らせる。

【0079】

図16は、フィードバッククロックFEBの遅延時間が基準クロックの1周期より小さい場合のハーモニックロック検出器の動作タイミング図である。

【0080】

図16を参照すると、全ての遅延クロックCK1〜CK14の立ち上がりエッジが基準クロックREFの1周期内に存在するのでハーモニックロック検出器110は正常ロック状態であると判断してハーモニックロック信号HDを「ハイ」にして出力する。

【0081】

ところが、仮に全ての遅延クロックCK1〜CK14の立ち上がりエッジが基準クロックREFの1周期内に存在し、さらにフィードバッククロックFEBの遅延時間も基準クロックREFの1周期より小さいとしても、位相検出器200が誤った位相差信号、例えばアップ信号UPを生成してしまうと、遅延ロックループ600が電圧制御遅延ライン500の遅延時間を減らす方向に動作するようになるので、スタックロック状態が生じ得る。

【0082】

以下、スタックロックの発生に対して説明する。図17は、図9に示すスタックロック検出器の一実施形態による具現例を示す回路図である。

【0083】

図17を参照すると、スタックロック検出器120は中間遅延クロックCK5の立ち上がりエッジを基準にして予め設定された幅を有する立ち上がりエッジ検出信号RST_CKを生成する立ち上がりエッジ検出部121、アップ信号UPと立ち上がりエッジ検出信号RST_CKをAND演算する第2ANDゲートAD12、ダウン信号DOWNと立ち上がりエッジ検出信号RST_CKをAND演算する第3ANDゲートAD13及び第2ANDゲートAD12の出力と第3ANDゲートAD13の出力とをOR演算する第1ORゲートOR11を含む。

【0084】

立ち上がりエッジ検出部121は中間遅延クロックCK5の位相を反転させる第1インバータI11、第1インバータI11の出力を遅延させる第1遅延器DL11及び第1遅延器DL11の出力D_CK5_Bと中間遅延クロックCK5をAND演算して立ち上がりエッジ検出信号RST_CKとして出力する第1ANDゲートAD11を含む。予め設定された幅は第1遅延器DL11により決定されることができる。本実施形態では中間遅延クロックCK5が第5遅延クロックCK5である場合を例に挙げて説明したが、これに限定されず第1遅延クロックCK1より遅延時間が大きく第14遅延クロックCK14より遅延時間が小さい他の遅延クロックCK2〜CK4、CK6〜CK13のいずれかを使用しても同じ効果を得ることができる。

【0085】

図18は、図8に示す位相検出器のブロック図である。

【0086】

図18を参照すると、位相検出器200は第1フリップフロップFF1、第2フリップフロップFF2、アップ信号出力部211、ダウン信号出力部212及びリセット制御部213を含む。

【0087】

第1フリップフロップFF1のデータ入力端子Dには電源電圧VDDが、クロック端子CKには基準クロックREFが連結され、出力信号としてはアップ信号UPが出力端子Qで生成される。第2フリップフロップFF2のデータ入力端子Dには電源電圧VDDが、クロック端子CKにはフィードバッククロックFEBが連結され、ダウン信号DOWNは出力端子Qで生成される。基準クロックREFの位相がフィードバッククロックFEBの位相より先行している場合は第1フリップフロップFF1からアップ信号UPが出力され、フィードバッククロックFEBの位相が基準クロックREFの位相より先行している場合は第2フリップフロップFF2からダウン信号DOWNが出力される。

【0088】

アップ信号出力部211の第1スイッチTG1は第1フリップフロップFF1の出力端子Qとアップ信号UP出力端子の間に位置しハーモニックロック信号対HD、HD_Bに応じてアップ信号UPの出力を断続する。アップ信号出力部211の第2スイッチTG2は電源電圧VDDとアップ信号出力端子の間に位置しハーモニックロック信号対HD_B、HDに応じて電源電圧VDDの出力を断続する。第1スイッチTG1と第2スイッチTG2はハーモニックロック信号対HD、HD_Bに応じて相補的に動作することが好ましい。

【0089】

ダウン信号出力部212の第3スイッチTG3は第2フリップフロップFF2の出力端子Qとダウン信号出力端子の間に位置しハーモニックロック信号対HD、HD_Bに応じてダウン信号DOWNの出力を断続する。第4スイッチTG4はグラウンドGNDとダウン信号出力端子の間に位置しハーモニックロック信号対HD_B、HDに応じてグラウンドGNDとダウン信号出力パッドの連結を断続する。第3スイッチTG3と第4スイッチTG4はハーモニックロック信号対HD、HD_Bに応じて相補的に動作することが好ましい。

【0090】

リセット制御部213は第1フリップフロップFF1及び第2フリップフロップFF2の出力端子Qから出力される出力信号をAND演算するANDゲートAD1及びスタックロック信号RST_CONSTとANDゲートAD1の出力をOR演算するORゲートOR1を含む。

【0091】

電圧制御遅延ライン500の遅延時間が正常ロック状態を検出できる最大範囲内に存在する時、誤ロック防止回路100のハーモニックロック検出器110は位相検出器200にハーモニックロック信号HDを「ハイ」にして供給する。したがって、電源電圧VDDはアップ信号出力部211の第2スイッチTG2によってアップ信号UPに出力されないように遮断され、接地電源GNDはダウン信号出力部212の第4スイッチTG4によって遮断されてダウン信号DOWNに出力されない。第1フリップフロップFF1で出力されるアップ信号UPはアップ信号出力部211の第1スイッチTG1を介してチャージポンプ300側に出力され、第2フリップフロップFF2で出力されるダウン信号DOWNはダウン信号出力部212の第3スイッチTG3を介してチャージポンプ300側に出力される。

【0092】

ハーモニックロック信号HDが「ロー」に活性化されて位相検出器200に供給されると、基準クロックREFの遅延時間が基準クロックREFの1周期を超えたかハーモニックロックが生じた状態であることを意味するので位相検出器200は遅延時間を減らすために制御電圧Vctrlのレベルを上げなければならない。このために、アップ信号出力部211は電源電圧VDDを第2スイッチTG2を介してアップ信号UPで出力し、ダウン信号出力部212は接地電源GNDを第4スイッチTG4を介してダウン信号DOWNに出力する。これにより、電圧制御遅延ライン500で基準クロックREFの遅延時間が迅速に減ってハーモニックロック状態を防止できるようになる。

【0093】

一方、電圧制御遅延ライン500の遅延時間が誤ロック検出器100のハーモニックロック検出器110が正常ロック状態を検出できる最大範囲内に存在する時、誤ロック防止回路100内のハーモニックロック検出器110は位相検出器200に活性化されたリセット信号RST_CONTを供給しない。これにより、位相検出器200の第1及び第2フリップフロップFF1、FF2はリセット制御部213のアップ信号UPとダウン信号DOWNの演算結果による出力信号によってのみリセットされる。しかし、誤ロック防止回路100のハーモニックロック検出器110が位相検出器200にスタックロック信号RST_CONTを供給すると、リセット制御部213を介して第1及び第2フリップフロップFF1、FF2がリセットされ、程なく位相検出器200全体がリセットされる。

【0094】

図19は、電圧制御遅延ラインの遅延時間が基準クロックの0.5周期より小さい時、基準クロックとフィードバッククロックを正しく比較する場合の位相検出器及びスタックロック検出器の動作タイミング図である。

【0095】

図19を参照すると、基準クロックREFのN番目の立ち上がりエッジ位相よりフィードバッククロックFEBのN−1番目の立ち上がりエッジ位相が先行しているので、位相検出器200は位相差に該当する区間の間ダウン信号DOWNを「ハイ」に活性化させて出力し、ダウン信号DOWNが「ロー」に遷移された立ち下がりエッジに同期された瞬間的パルスをアップ信号UP(図示せず)に出力する。ここで位相差は正常ロック状態のために増加させるべき遅延量を示す。

【0096】

本実施形態は制御電圧Vctrlが増加するほど電圧制御遅延ライン500の遅延時間が減少するように設計された場合であるので正常信号(Normal signal)はダウン信号DOWNになる。アップ信号UPはダウン信号DOWNが「ハイ」から「ロー」になる時、非常に短い時間の間「ロー」から「ハイ」になり再び「ロー」となる。この時、ダウン信号DOWNが「ハイ」から「ロー」になる時間とアップ信号UPが「ハイ」から「ロー」になる時間は一致する。アップ信号UPの「ハイ」区間は位相検出器200のフリップフロップをリセットさせるために必要な非常に短い時間である。

【0097】

ハーモニックロック検出器110はサンプリングクロックCK1〜CK14のすべてが基準クロックREFの1周期内にあるのでハーモニックロック信号HDを「ハイ」にして出力してハーモニックロック状態ではないことを知らせる。スタックロック検出器120の立ち上がりエッジ検出部121は中間遅延信号CK5と、中間遅延信号CK5を反転させて遅延させた信号D_CK5_BとをAND演算して立ち上がりエッジ検出信号RST_CKパルスを生成する。立ち上がりエッジ検出信号RST_CKは電圧制御遅延ライン500によって遅延された時間内に生成される。

【0098】

スタックロック検出器120のORゲートOR1は立ち上がりエッジ検出信号RST_CKとダウン信号DOWNが同時に「ハイ」の区間が発生するとスタックロック信号RST_CONTを「ハイ」に活性化させる。本実施形態では、ダウン信号DOWNと立ち上がりエッジ検出信号RST_CKの「ハイ」区間が重複しないのでスタックロック信号RST_CONTは「ロー」状態を維持する。この場合、ダウン信号DOWN及び基準クロックREFの立ち上がりエッジで第1フリップフロップFF1が瞬間的に発生するアップ信号UPのAND演算によって位相検出器200はリセットされる。

【0099】

図20は、電圧制御遅延ラインの遅延時間が基準クロックの0.5周期より小さい時、基準クロックとフィードバッククロックを誤って比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【0100】

図20を参照すると、位相検出器200が初期値の誤りなどの何らかの理由によって基準クロックREFのN−1番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとを比較するようになると、基準クロックREFのN−1番目の立ち上がりエッジの位相がフィードバッククロックFEBの位相より先行しているので位相検出器200は電圧制御遅延ライン500によって遅延された遅延時間を減少させなければならない位相差であると判断する。

【0101】

したがって、位相検出器200は非正常アップ信号(Abnormal UP)を生成して制御電圧Vctrlを増加させ、遅延ロックループは制御電圧Vctrlに応じて基準クロックREFのN−1番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとの間の位相差を減らす方向に動作するようになる。非正常アップ信号が「ハイ」である区間は位相検出器200が減少させなければならない位相差であると認識する遅延時間である。非正常ダウン信号(Abnormal DOWN)は遅延時間が経過した後フィードバッククロックFEBの立ち上がりエッジによって生成される信号である。

【0102】

ここで、非正常アップ信号とは誤ロック状態でのアップUP信号を意味し、正常なロック状態であれば発生すべきではない信号状態をいう。非正常ダウン信号も同様であり、以下ですべて同じ意味に使われる。

【0103】

もし、従来の遅延ロックループのように、本実施形態によるスタックロック検出器120が存在しない場合、位相検出器200は基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN番目の立ち上がりエッジとを再び比較するようになり、遅延ロックループ600は継続的に電圧制御遅延ライン500の遅延時間を減らす方向に動作するようになってスタックロック状態から抜け出すことができなくなる。

【0104】

しかし、本発明の一実施形態によるスタックロック検出器120を備えた場合、スタックロック検出器120の立ち上がりエッジ検出部121は電圧制御遅延ライン500によって遅延された遅延時間区間内に立ち上がりエッジ検出信号RST_CKを生成する。スタックロック検出器120はAND演算を介して非正常アップ信号と立ち上がりエッジ検出信号RST_CKの「ハイ」が重複する区間で活性化されるスタックロック信号RST_CONTを出力する。スタックロック信号RST_CONTはリセット制御部213のORゲートOR1を介して位相検出器200の第1フリップフロップFF1と第2フリップフロップFF2をリセットさせ、非正常アップ信号が正常アップ信号に訂正されることができるようにする。

【0105】

その後、スタックロック信号RST_CONTによってリセットされた位相検出器200はフィードバッククロックFEBのN−1番目の立ち上がりエッジと基準クロックREFのN番目の立ち上がりエッジとを比較するようになるので、遅延ロックループ600が電圧制御遅延ライン500の遅延時間を増加させる方向に動作するようにする訂正された正常ダウン信号(Corrected DOWN)と訂正された正常アップ信号(Corrected UP)を生成して正常なロック状態に戻る。

【0106】

したがって、本実施形態による遅延ロックループ600は位相検出器200が何らかの理由によって基準クロックのN−1番目の立ち上がりエッジとフィードバッククロックのN−1番目の立ち上がりエッジとを比較して誤ったアップ信号を生成しても、スタックロック検出器120で生成されたリセット信号RST_CONTによって位相検出器200がリセットされて基準クロックのN番目の立ち上がりエッジとフィードバッククロックのN−1番目の立ち上がりエッジとを正しく比較することができる。そして、遅延ロックループ600でスタックロック状態が生じることを防止できるようになり、基準クロックREFを1周期だけ遅延させてその基準クロックREFとフィードバッククロックFEBを同期化させることができるようになる。

【0107】

図21は、正常ロック状態を判断できる最大範囲内で、基準クロックとフィードバッククロックを正しく比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【0108】

図21を参照すると、基準クロックREFのN番目の立ち上がりエッジの位相がフィードバッククロックFEBN−1番目の立ち上がりエッジの位相より先行しているので、位相検出器200はアップ信号UPを生成して制御電圧Vctrlによって電圧制御遅延ライン500の遅延が減少する方向に動作する。アップ信号UPの「ハイ」区間は電圧制御遅延ライン500が減少させるべき遅延量に対応する。スタックロック検出器120の立ち上がりエッジ検出部121は電圧制御遅延ライン500によって遅延された遅延時間区間内に立ち上がりエッジ検出信号RST_CKを生成する。

【0109】

ハーモニックロック検出器110が正常ロック状態であると判断できる最大範囲内で、位相検出器200が基準クロックREFとフィードバッククロックFEBとを正しく比較判断すると、立ち上がりエッジ検出信号RST_CKとアップ信号UPの「ハイ」が重複する区間が存在しないのでスタックロック検出器120はスタックロック信号RST_CONTを活性化させない。

【0110】

したがって、位相検出器200はスタックロック信号RST_CONTによってリセットされず基準クロックREFとフィードバッククロックFEBの位相差を減らす方向に正常動作するようになる。

【0111】

図22は、正常ロック状態を判断できる最大範囲内で、基準クロックとフィードバッククロックを誤って比較する場合の位相検出器とスタックロック検出器の動作タイミング図である。

【0112】

図22を参照すると、基準クロックREFがフィードバッククロックFEBより基準クロックREFのN番目の立ち上がりエッジからフィードバッククロックFEBのN−1番目の立ち上がりエッジまでの間の区間だけ先行しているので、基準クロックREFとフィードバッククロックFEBの同期を合わせるためにはフィードバッククロックFEBの遅延を減少させなければならないことがわかる。

【0113】

ところが、位相検出器200が初期値の誤りなどの何らかの理由によって基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−2番目の立ち上がりエッジとを比較するようになると、フィードバッククロックFEBが基準クロックREFよりフィードバッククロックFEBのN−2番目の立ち上がりエッジから基準クロックREFの立ち上がりエッジまでの間の区間だけ先行しているので、位相検出器200は基準クロックREFとフィードバッククロックFEBの同期を合わせるためにフィードバッククロックFEBの遅延を増加させるべきであると判断するようになり非正常ダウン信号を生成するようになる。

【0114】

本実施形態によるスタックロック検出器120が存在しない従来の遅延ロックループでは、位相検出器200は引続き基準クロックのN+1番目の立ち上がりエッジとフィードバッククロックのN−1番目の立ち上がりエッジとを比較した後、引き続き基準クロックのN+2番目の立ち上がりエッジとフィードバッククロックのN番目の立ち上がりエッジとを比較するようになるので遅延ロックループ500はスタックロック状態から抜け出すことができなくなる。

【0115】

本発明の一実施形態によるスタックロック検出器120を備えた場合、スタックロック検出器120の立ち上がりエッジ検出部121は電圧制御遅延ライン500によって遅延された遅延時間区間内に立ち上がりエッジ検出信号RST_CKを生成する。スタックロック検出器120は立ち上がりエッジ検出信号RST_CKと非正常ダウン信号をAND演算して非正常ダウン信号と立ち上がりエッジ検出信号RST_CKの「ハイ」が重複する区間で活性化されるスタックロック信号RST_CONTを出力する。スタックロック信号RST_CONTはリセット制御部213のORゲートOR1を介して位相検出器200の第1フリップフロップFF1と第2フリップフロップFF2をリセットさせ、非正常ダウン信号を正常ダウン信号に訂正する。

【0116】

その後、スタックロック信号RST_CONTによってリセットされた位相検出器200はフィードバッククロックFEBのN−1番目の立ち上がりエッジと基準クロックREFのN番目の立ち上がりエッジとを比較するようになるので、遅延ロックループ600が電圧制御遅延ライン500の遅延時間を減少させる方向に動作するようにする正常ダウン信号を生成する。

【0117】

したがって、上記のように位相検出器200が基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−2番目の立ち上がりエッジとを誤って比較判断する場合にもスタックロック状態が生じることを防止できるようになり、基準クロックREFを1周期だけ遅延させてその基準クロックREFとフィードバッククロックFEBを同期化させることができるようになる。

【0118】

本発明の実施形態による遅延ロックループ600は次の2つの状態のうちいずれかの状態になることができる。

【0119】

第一、誤ロック防止回路100がハーモニックロック信号HDとスタックロック信号RST_CONTをすべて「ハイ」にして出力すると、位相検出器200は図20のように基準クロックREFのN−1番目の立ち上がりエッジと前記フィードバッククロックFEBのN−1番目の立ち上がりエッジの位相を比較する場合、及び図22のように基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−2番目の立ち上がりエッジの位相を比較する場合にもすべてスタックロック信号RST_CONTによってリセットされ得る。位相検出器200がスタックロック信号RST_CONTによってリセットされたので、その後は基準クロックREFのN番目の立ち上がりエッジとフィードバッククロックFEBのN−1番目の立ち上がりエッジとを正常に比較できるようになる。すなわち、基準クロックREFとフィードバッククロックFEBの位相を正しく比較して遅延ロックループ600が正常にロック状態になることができる。

【0120】

第二、誤ロック防止回路100がハーモニックロック信号HDを「ハイ」にして出力し、スタックロック信号RST_CONTを引き続き「ロー」にして出力する場合、基準クロックREFとフィードバッククロックFEBの位相を正しく比較している状態であるので位相検出器200の動作によって遅延ロックループ600は正常にロック状態になることができる。

【0121】

図23は、図8に示す位相検出器の状態図である。

【0122】

図23を参照すると、本実施形態による位相検出器200はハーモニックロック信号HDが「0」(ロジック「ロー」)であれば遅延ロックループ600がいかなる状態にあってもアップ信号UPは「1」(ロジック「ハイ」)で、ダウン信号DOWNは「0」になるロジックを含む。したがって、本実施形態による固定遅延ループ600はハーモニックロック状態で基準クロックREFとフィードバッククロックFEBの位相を同期させるために電圧制御遅延ライン500の遅延を減少させる方向に動作できるようになる。

【0123】

ハーモニックロック信号HDが「1」で、基準クロックREFとフィードバッククロックFEBの位相を比較して基準クロックREFが先行していると、アップ信号UPは「1」で、ダウン信号は「0」になる。ハーモニックロック信号HDが「1」で、基準クロックREFとフィードバッククロックFEBの位相を比較して基準クロックREFが遅れていると、アップ信号UPは「0」で、ダウン信号は「1」になる。ハーモニックロック信号HDが「1」で、基準クロックREFとフィードバッククロックFEBの位相を比較して互いに同じであると判明すると、アップ信号UPは「0」で、ダウン信号も「0」になる。

【0124】

アップ信号UPは「1」で、ダウン信号は「0」であるか、アップ信号UPは「0」で、ダウン信号は「1」である状態で、リセット信号RST_CONTが「1」になると、これは位相検出器200が基準クロックREFとフィードバッククロックFEBの位相を誤って比較したことを意味する。本実施形態による位相検出器200は何らかの理由によって基準クロックREFとフィードバッククロックFEBとを誤って比較してスタックロック状態に陥り得る状態になるとスタックロック信号RST_CONTによって訂正され得るロジックを含む。

【0125】

したがって、アップ信号UPは「1」で、ダウン信号は「0」である状態でリセット信号RST_CONTが「1」になると、アップ信号UPは「0」、ダウン信号は「1」の状態に訂正され、アップ信号UPは「0」で、ダウン信号は「1」である状態でリセット信号RST_CONTが「1」になると、アップ信号UPは「1」、ダウン信号は「0」の状態に訂正され、基準クロックREFとフィードバッククロックFEBの位相を同期させることができるようになる。

【0126】

ロック状態はアップ信号UPとダウン信号DOWNがすべて「0」である状態でハーモニックロック信号HDが「1」で基準クロックREFとフィードバッククロックFEBの位相差が「0」に維持される状態である。

【0127】

本発明の実施形態による誤ロック防止回路100が適用される遅延ロックループ600で電圧制御遅延ライン500の遅延範囲VCDL delayは0<VCDL delay<2*T*Nの範囲を有する。ここで、「N」は前記制御遅延ライン500の遅延素子DL1〜DLnの個数を意味する。したがって、図8のように前記制御遅延ライン500が14個の遅延素子を用いる場合、制御遅延ライン500の遅延範囲は0<VCDL delay<28*Tの範囲を有する。

【0128】

また、本発明の実施形態による誤ロック防止回路100のハーモニックロック検出器110とスタックロック検出器120は電圧制御遅延ライン500で生成された第1乃至第14クロックCK1〜CK14の立ち上がりエッジを使用してハーモニックロック及びスタックロック状態を検出するので、固定遅延ループ600は基準クロックのデューティ比に影響されず動作できる利点を有する。

【0129】

本実施形態で電圧制御遅延ライン500は制御電圧Vctrlが電源電圧VDDの時に最小遅延を有し、ダウン信号DOWNによって制御電圧Vctrlが次第に低くなると遅延時間が増加する構造を例示して説明したが、本発明はこれに限定されない。例えば、電圧制御遅延ライン500は制御電圧Vctrlが接地電圧VSSの時に最小遅延を有し、アップ信号UPによって制御電圧Vctrlが次第に高くなると遅延時間が増加する構造を有し得る。電圧制御遅延ライン500の制御電圧Vctrlが接地電圧VSSの時に最小遅延を有する場合の構成及び動作は電圧制御遅延ライン500が制御電圧Vctrlが電源電圧VDDの時に最小遅延を有する上記した説明から当業者が容易に理解できるものであるので詳細な説明は省略する。

【0130】

本実施形態で電圧制御遅延ライン500は14個の遅延素子を有し、遅延素子に対応して14個の遅延クロックを含む場合を例示して説明したが、本発明はこれに限定されず、適用されるシステムによって異なる個数の遅延素子を有し得る。

【0131】

以上、本発明の好ましい実施形態に対して詳細に説明したが、本発明の権利範囲はこれに限定されず下記の特許請求の範囲で定義する本発明の基本概念に基づいて様々な実施形態に具現されることができ、このような実施形態も本発明の権利範囲に属するものである。

【符号の説明】

【0132】

100:誤ロック防止回路

110:ハーモニックロック検出器

111:2分周器

112A:第1サンプラ

112B:第2サンプラ

113:ANDゲート

120:スタックロック検出器

200:位相検出器

300:チャージポンプ

400:低域フィルタ

500:電圧制御遅延ライン

600:遅延ロックループ

【特許請求の範囲】

【請求項1】

基準クロック信号;

前記基準クロック信号から遅延された複数個の遅延クロック信号;及び

前記複数個の遅延クロック信号のうち少なくとも一部が前記基準クロック信号の1周期内から離れたことを検出する検出器;を備え、

前記検出器は前記基準クロック信号の1周期以内に前記複数個の遅延クロック信号の遷移エッジ(transition edge)のうち1つ以上が存在しない時、誤ロックが生じたことを知らせることを特徴とする誤ロック防止回路。

【請求項2】

前記検出器は、

前記基準クロック信号を分周する分周器;

前記複数個の遅延クロック信号のうち一部又は全部を用いて前記分周器の出力信号をサンプリングする第1サンプラ;

前記第1サンプラの出力信号を再度サンプリングする第2サンプラ;

前記第2サンプラの出力を論理演算する論理部;

を含むことを特徴とする請求項1に記載の誤ロック防止回路。

【請求項3】

前記第1サンプラ及び前記第2サンプラは、

それぞれ複数個のフリップフロップを含むことを特徴とする請求項2に記載の誤ロック防止回路。

【請求項4】

基準クロックと前記基準クロックから所定時間遅延されたフィードバッククロックとを同期させる遅延ロックループにおいて、

前記基準クロックを分周した後、複数個の遅延クロックを用いて前記分周されたクロックを複数回サンプリングし、前記サンプリング結果を論理演算してハーモニックロック信号を生成するハーモニックロック検出器を含む誤ロック防止回路;

前記ハーモニックロック信号が活性化された状態で入力される時に前記基準クロックとフィードバッククロックの位相差が減るようにアップ信号とダウン信号を生成し、スタックロック信号が活性化された状態で入力される時にリセットされて前記基準クロックと前記フィードバッククロックの位相差を検出する位相検出器;

前記アップ信号又はダウン信号に応じて電流をソース(source)するか電流をシンク(sink)するチャージポンプ(charge pump);

前記電流に応じた制御電圧を発生させる低域通過フィルタ;及び

前記制御電圧の変化に沿って各遅延時間間隔が増えるか減る複数個の遅延クロックを発生する電圧制御遅延ライン;を備えることを特徴とする誤ロック防止回路を利用した遅延ロックループ。

【請求項5】

前記位相検出器は前記基準クロックが前記フィードバッククロックより1周期以上位相が先行していると前記遅延時間間隔を減少させる信号を発生し、1周期以下位相が遅れていると前記遅延時間間隔を増加させる信号を発生することを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項6】

誤ロック防止回路は前記複数個の遅延クロックのうち1つを遅延及び論理演算して立ち上がりエッジ検出信号を生成し前記立ち上がりエッジ検出信号をアップ信号又はダウン信号と論理演算してスタックロック信号を生成するスタックロック検出器をさらに含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延固定ループ。

【請求項7】

前記誤ロック防止回路は、

前記複数個の遅延クロックを用いて前記基準クロックに基づいた分周クロックをサンプリングし論理演算を行う第1誤ロック検出器;及び

前記検出された位相差信号及び前記複数個の遅延クロックのうち一部を用いて他の論理演算を行う第2誤ロック検出器;

を含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項8】

前記誤ロック防止回路は前記フィードバッククロックの前記遅延時間が前記基準クロックの1周期を超えたことを検出することを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項9】

前記誤ロック防止回路は、

前記基準クロック信号を分周する分周器;

前記複数個の遅延クロック信号のうち一部又は全部を用いて前記分周器の出力信号をサンプリングする第1サンプラ;

前記第1サンプラの出力信号を再度サンプリングする第2サンプラ;及び

前記第2サンプラの出力を論理演算する論理部;

を含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項10】

前記位相検出器は前記ハーモニックロックが検出されるとそこから抜け出すまで前記フィードバッククロックの遅延を持続的に減少させることを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項11】

前記位相検出器は、

前記基準クロックを入力とする第1フリップフロップ;

前記フィードバッククロックを入力とする第2フリップフロップ;

アップ信号を出力するアップ信号出力部;

ダウン信号を出力するダウン信号出力部;

前記第1フリップフロップ及び前記第2フリップフロップのリセット端子に連結されたリセット制御部;

を含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項12】

前記アップ信号出力部は固定電圧に連結された第1経路及び前記第1フリップフロップの出力に連結された第2経路のうち1つの経路を選択し、

前記ダウン信号出力部は他の固定電圧に連結された第3経路及び前記第2フリップフロップの出力に連結された第4経路のうち1つの経路を選択することを特徴とする請求項11に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項13】

前記アップ信号出力部は前記ハーモニックロック状態の時は前記第1経路を選択し、前記ハーモニックロック状態ではない時には前記第2経路を選択することを特徴とする請求項12に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項14】

前記ダウン信号出力部は前記ハーモニックロック状態の時は前記第3経路を選択し、前記ハーモニックロック状態ではない時には前記第4経路を選択することを特徴とする請求項12に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項15】

前記誤ロック防止回路は、

前記検出された位相差信号及び前記複数個の遅延クロックのうち少なくとも1つを選択しその選択されたクロックを用いて論理演算を行い、その結果としてハーモニックロックが生じたことを知らせる特定信号を生成する誤ロック検出器を含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項16】

前記誤ロック検出器は前記特定信号によって前記位相検出器をリセットすることを特徴とする請求項15に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項17】

前記特定信号は、

前記選択されたクロックと前記選択されたクロックから所定時間遅延されたクロックを用いて生成されたパルス信号に基づいた信号であることを特徴とする請求項15に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項18】

前記パルス信号は、

前記選択されたクロック、前記遅延されたクロック、前記遅延されたクロックのうち選択されたクロックのうち1つ以上の変化エッジ(transition edge)を検出することによって生成されたことを特徴とする請求項17に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項19】

誤ロック防止方法において、

(a)基準クロック信号から遅延された複数の遅延クロック信号を発生するステップ;

(b)前記基準クロック信号から分周されたクロック信号を発生するステップ;

(c)前記遅延クロック信号の少なくとも一部を用いて前記分周されたクロック信号をサンプリングして論理演算するステップ;

(d)前記複数の遅延クロック信号の前記遅延のうち少なくとも一部が前記基準クロック信号から予め決められた時間遅延以上である時にのみ前記論理演算の結果によって前記複数の遅延クロック信号の前記遅延を減らすようにするステップ;を備えることを特徴とする誤ロック防止方法。

【請求項20】

前記予め決められた時間遅延は、前記基準クロック信号の1周期に該当する時間であるか、前記基準クロック信号の1周期より2以上の整数倍の時間であることを特徴とする請求項19に記載の誤ロック防止方法。

【請求項21】

誤ロック防止方法において、

(a)基準クロック信号から遅延された複数の遅延クロック信号を発生するステップ;

(b)前記複数の遅延クロック信号のうち1つを選択し、それと前記基準クロック信号の位相差を比較するステップ;

(c)前記複数の遅延クロック信号のうち他の1つを選択して遷移エッジ(transition edge)を検出するステップ;

(d)前記検出結果と前記位相差比較結果を論理演算するステップ;

(e)前記論理演算の結果によって前記位相差比較をリセット(reret)するステップ;を備えることを特徴とする誤ロック防止方法。

【請求項22】

前記遷移エッジの検出結果は前記基準クロック信号の周期より短いパルス信号であることを特徴とする請求項21に記載の誤ロック防止方法。

【請求項23】

前記短いパルス信号は前記(c)ステップで選択されたクロック信号及び前記(c)ステップで選択されたクロック信号から遅延された信号を互いに論理演算して発生した信号であることを特徴とする請求項22に記載の誤ロック防止方法。

【請求項1】

基準クロック信号;

前記基準クロック信号から遅延された複数個の遅延クロック信号;及び

前記複数個の遅延クロック信号のうち少なくとも一部が前記基準クロック信号の1周期内から離れたことを検出する検出器;を備え、

前記検出器は前記基準クロック信号の1周期以内に前記複数個の遅延クロック信号の遷移エッジ(transition edge)のうち1つ以上が存在しない時、誤ロックが生じたことを知らせることを特徴とする誤ロック防止回路。

【請求項2】

前記検出器は、

前記基準クロック信号を分周する分周器;

前記複数個の遅延クロック信号のうち一部又は全部を用いて前記分周器の出力信号をサンプリングする第1サンプラ;

前記第1サンプラの出力信号を再度サンプリングする第2サンプラ;

前記第2サンプラの出力を論理演算する論理部;

を含むことを特徴とする請求項1に記載の誤ロック防止回路。

【請求項3】

前記第1サンプラ及び前記第2サンプラは、

それぞれ複数個のフリップフロップを含むことを特徴とする請求項2に記載の誤ロック防止回路。

【請求項4】

基準クロックと前記基準クロックから所定時間遅延されたフィードバッククロックとを同期させる遅延ロックループにおいて、

前記基準クロックを分周した後、複数個の遅延クロックを用いて前記分周されたクロックを複数回サンプリングし、前記サンプリング結果を論理演算してハーモニックロック信号を生成するハーモニックロック検出器を含む誤ロック防止回路;

前記ハーモニックロック信号が活性化された状態で入力される時に前記基準クロックとフィードバッククロックの位相差が減るようにアップ信号とダウン信号を生成し、スタックロック信号が活性化された状態で入力される時にリセットされて前記基準クロックと前記フィードバッククロックの位相差を検出する位相検出器;

前記アップ信号又はダウン信号に応じて電流をソース(source)するか電流をシンク(sink)するチャージポンプ(charge pump);

前記電流に応じた制御電圧を発生させる低域通過フィルタ;及び

前記制御電圧の変化に沿って各遅延時間間隔が増えるか減る複数個の遅延クロックを発生する電圧制御遅延ライン;を備えることを特徴とする誤ロック防止回路を利用した遅延ロックループ。

【請求項5】

前記位相検出器は前記基準クロックが前記フィードバッククロックより1周期以上位相が先行していると前記遅延時間間隔を減少させる信号を発生し、1周期以下位相が遅れていると前記遅延時間間隔を増加させる信号を発生することを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項6】

誤ロック防止回路は前記複数個の遅延クロックのうち1つを遅延及び論理演算して立ち上がりエッジ検出信号を生成し前記立ち上がりエッジ検出信号をアップ信号又はダウン信号と論理演算してスタックロック信号を生成するスタックロック検出器をさらに含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延固定ループ。

【請求項7】

前記誤ロック防止回路は、

前記複数個の遅延クロックを用いて前記基準クロックに基づいた分周クロックをサンプリングし論理演算を行う第1誤ロック検出器;及び

前記検出された位相差信号及び前記複数個の遅延クロックのうち一部を用いて他の論理演算を行う第2誤ロック検出器;

を含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項8】

前記誤ロック防止回路は前記フィードバッククロックの前記遅延時間が前記基準クロックの1周期を超えたことを検出することを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項9】

前記誤ロック防止回路は、

前記基準クロック信号を分周する分周器;

前記複数個の遅延クロック信号のうち一部又は全部を用いて前記分周器の出力信号をサンプリングする第1サンプラ;

前記第1サンプラの出力信号を再度サンプリングする第2サンプラ;及び

前記第2サンプラの出力を論理演算する論理部;

を含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項10】

前記位相検出器は前記ハーモニックロックが検出されるとそこから抜け出すまで前記フィードバッククロックの遅延を持続的に減少させることを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項11】

前記位相検出器は、

前記基準クロックを入力とする第1フリップフロップ;

前記フィードバッククロックを入力とする第2フリップフロップ;

アップ信号を出力するアップ信号出力部;

ダウン信号を出力するダウン信号出力部;

前記第1フリップフロップ及び前記第2フリップフロップのリセット端子に連結されたリセット制御部;

を含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項12】

前記アップ信号出力部は固定電圧に連結された第1経路及び前記第1フリップフロップの出力に連結された第2経路のうち1つの経路を選択し、

前記ダウン信号出力部は他の固定電圧に連結された第3経路及び前記第2フリップフロップの出力に連結された第4経路のうち1つの経路を選択することを特徴とする請求項11に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項13】

前記アップ信号出力部は前記ハーモニックロック状態の時は前記第1経路を選択し、前記ハーモニックロック状態ではない時には前記第2経路を選択することを特徴とする請求項12に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項14】

前記ダウン信号出力部は前記ハーモニックロック状態の時は前記第3経路を選択し、前記ハーモニックロック状態ではない時には前記第4経路を選択することを特徴とする請求項12に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項15】

前記誤ロック防止回路は、

前記検出された位相差信号及び前記複数個の遅延クロックのうち少なくとも1つを選択しその選択されたクロックを用いて論理演算を行い、その結果としてハーモニックロックが生じたことを知らせる特定信号を生成する誤ロック検出器を含むことを特徴とする請求項4に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項16】

前記誤ロック検出器は前記特定信号によって前記位相検出器をリセットすることを特徴とする請求項15に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項17】

前記特定信号は、

前記選択されたクロックと前記選択されたクロックから所定時間遅延されたクロックを用いて生成されたパルス信号に基づいた信号であることを特徴とする請求項15に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項18】

前記パルス信号は、

前記選択されたクロック、前記遅延されたクロック、前記遅延されたクロックのうち選択されたクロックのうち1つ以上の変化エッジ(transition edge)を検出することによって生成されたことを特徴とする請求項17に記載の誤ロック防止回路を利用した遅延ロックループ。

【請求項19】

誤ロック防止方法において、

(a)基準クロック信号から遅延された複数の遅延クロック信号を発生するステップ;

(b)前記基準クロック信号から分周されたクロック信号を発生するステップ;

(c)前記遅延クロック信号の少なくとも一部を用いて前記分周されたクロック信号をサンプリングして論理演算するステップ;

(d)前記複数の遅延クロック信号の前記遅延のうち少なくとも一部が前記基準クロック信号から予め決められた時間遅延以上である時にのみ前記論理演算の結果によって前記複数の遅延クロック信号の前記遅延を減らすようにするステップ;を備えることを特徴とする誤ロック防止方法。

【請求項20】

前記予め決められた時間遅延は、前記基準クロック信号の1周期に該当する時間であるか、前記基準クロック信号の1周期より2以上の整数倍の時間であることを特徴とする請求項19に記載の誤ロック防止方法。

【請求項21】

誤ロック防止方法において、

(a)基準クロック信号から遅延された複数の遅延クロック信号を発生するステップ;

(b)前記複数の遅延クロック信号のうち1つを選択し、それと前記基準クロック信号の位相差を比較するステップ;

(c)前記複数の遅延クロック信号のうち他の1つを選択して遷移エッジ(transition edge)を検出するステップ;

(d)前記検出結果と前記位相差比較結果を論理演算するステップ;

(e)前記論理演算の結果によって前記位相差比較をリセット(reret)するステップ;を備えることを特徴とする誤ロック防止方法。

【請求項22】

前記遷移エッジの検出結果は前記基準クロック信号の周期より短いパルス信号であることを特徴とする請求項21に記載の誤ロック防止方法。

【請求項23】

前記短いパルス信号は前記(c)ステップで選択されたクロック信号及び前記(c)ステップで選択されたクロック信号から遅延された信号を互いに論理演算して発生した信号であることを特徴とする請求項22に記載の誤ロック防止方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2012−253762(P2012−253762A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2012−123193(P2012−123193)

【出願日】平成24年5月30日(2012.5.30)

【出願人】(508038091)シリコン・ワークス・カンパニー・リミテッド (46)

【氏名又は名称原語表記】Silicon Works Co., LTD.

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成24年5月30日(2012.5.30)

【出願人】(508038091)シリコン・ワークス・カンパニー・リミテッド (46)

【氏名又は名称原語表記】Silicon Works Co., LTD.

【Fターム(参考)】

[ Back to top ]