誤書き込み防止回路および半導体装置

【課題】 書き込み時間の増加を抑制しつつ、保護対象のモジュールに対する誤書き込みを防止する。

【解決手段】 誤書き込み防止回路は、バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードを生成する比較コード生成部と、バスに接続された保護対象のモジュールに書き込まれるデータに対応する期待値と比較コードとを比較する比較部と、比較部の比較結果に基づいて、モジュールに対する書き込みを許可するか否かを決定する書き込み制御部とを有している。

【解決手段】 誤書き込み防止回路は、バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードを生成する比較コード生成部と、バスに接続された保護対象のモジュールに書き込まれるデータに対応する期待値と比較コードとを比較する比較部と、比較部の比較結果に基づいて、モジュールに対する書き込みを許可するか否かを決定する書き込み制御部とを有している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、誤書き込み防止回路および半導体装置に関する。

【背景技術】

【0002】

マイクロコントローラ等の半導体装置では、保護対象のモジュール(例えば、レジスタ)に対する誤書き込みを防止するための対策が施されている。この種の半導体装置は、例えば、保護対象のモジュールにライトデータを書き込む際に、所定のシーケンスを実施することにより、誤書き込みを防止する。例えば、“00”、“01”、“10”、“11”、“ライトデータ”の順に保護対象のモジュールにアクセスするシーケンスが実施されたときのみ、ライトデータが保護対象のモジュールに書き込まれる。この場合、ライトデータを書き込む前に、4回(“00”、“01”、“10”、“11”)の書き込み動作(所定のシーケンス)が実施される。一般的に、所定のシーケンスで実施される書き込み動作等の回数の増加に伴い、保護対象のモジュールのセキュリティは、向上する。

【0003】

また、保護対象のレジスタ毎に設定されたマスターキーコードを用いて誤書き込みを防止するマイクロコントローラが提案されている(例えば、特許文献1)。この種のマイクロコントローラは、例えば、マスターキーコードを記憶する記憶部を有し、マスターキーコードと一致する入力キーコードを受けたときに、保護対象のレジスタに対する書き込みを許可する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−204387号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ライトデータを書き込む前に所定のシーケンスを実施する構成では、保護対象のモジュールにライトデータを書き込む際に、所定のシーケンスを実施する時間を別途設ける必要がある。例えば、上述したシーケンスでは、保護対象のモジュールへの1回の書き込みに対して、4回の書き込みをするための余計な時間が必要である。このため、保護対象のモジュールに対する書き込み時間は増加する。

【0006】

本発明の目的は、書き込み時間の増加を抑制しつつ、保護対象のモジュールに対する誤書き込みを防止することである。

【課題を解決するための手段】

【0007】

本発明の一形態では、誤書き込み防止回路は、バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードを生成する比較コード生成部と、バスに接続された保護対象のモジュールに書き込まれるデータに対応する期待値と比較コードとを比較する比較部と、比較部の比較結果に基づいて、モジュールに対する書き込みを許可するか否かを決定する書き込み制御部とを有している。

【発明の効果】

【0008】

書き込み時間の増加を抑制しつつ、保護対象のモジュールに対する誤書き込みを防止できる。

【図面の簡単な説明】

【0009】

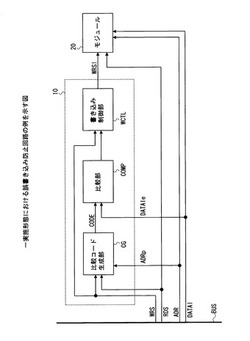

【図1】一実施形態における誤書き込み防止回路の例を示している。

【図2】図1に示した保護対象のモジュールにライトデータを書き込む際のデータ構成の一例を示している。

【図3】図1に示した誤書き込み防止回路が搭載される半導体装置の一例を示している。

【図4】別の実施形態における誤書き込み防止回路の一例を示している。

【図5】図4に示した誤書き込み防止回路の動作の一例を示している。

【図6】別の実施形態における誤書き込み防止回路の一例を示している。

【図7】図6に示した誤書き込み防止回路の動作の一例を示している。

【図8】別の実施形態における誤書き込み防止回路の一例を示している。

【図9】図8に示した誤書き込み防止回路の動作の一例を示している。

【図10】別の実施形態における誤書き込み防止回路の一例を示している。

【図11】別の実施形態における誤書き込み防止回路の一例を示している。

【図12】別の実施形態における半導体装置の一例を示している。

【図13】図12に示した半導体装置に搭載される誤書き込み防止回路の一例を示している。

【発明を実施するための形態】

【0010】

以下、実施形態を図面を用いて説明する。

【0011】

図1は、一実施形態における誤書き込み防止回路10の例を示している。誤書き込み防止回路10は、例えば、保護対象のモジュール20に対する書き込みを制御する。保護対象のモジュール20は、例えば、バスBUSに接続されたレジスタであり、I/O設定等の重要な情報を記憶する。なお、保護対象のモジュール20は、レジスタに限定されない。例えば、保護対象のモジュール20は、レジスタ以外のメモリでもよい。誤書き込み防止回路10はおよびモジュール20は、半導体装置の少なくとも一部を構成する。

【0012】

誤書き込み防止回路10は、例えば、バスBUSに接続された比較コード生成部CGと、バスBUSに接続された比較部COMPと、書き込み制御部WCTLとを有している。バスBUSには、例えば、データDATAI、アドレスADR、ライトストローブ信号WRSおよびリードストローブ信号RDS等が出力される。なお、データDATAIは、書き込み動作時にバスBUSに出力されるデータである。読み出し動作時には、例えば、図3に示すように、データDATAO(以下、リードデータとも称する)がバスBUSに出力される。

【0013】

比較コード生成部CGは、例えば、アドレスADRp、ライトストローブ信号WRSおよびリードストローブ信号RDSを受け、比較コードCODEを比較部COMPに出力する。なお、アドレスADRpは、書き込み動作時および読み出し動作時のいずれかにバスBUSに出力されるアドレスADRの一部(例えば、下位4ビット)である。

【0014】

例えば、比較コード生成部CGは、ライトストローブ信号WRSに基づく書き込みタイミングおよびリードストローブ信号RDSに基づく読み出しタイミングに同期して、バスBUSに出力されたアドレスADRp(アドレスADRの一部)の値を取得する。そして、比較コード生成部CGは、例えば、取得したアドレスADRpの値を用いて比較コードCODEを生成する。

【0015】

このように、比較コード生成部CGは、保護対象のモジュール20に対する書き込みが実施される前に、バスBUS上の情報(例えば、バスBUSに出力されたアドレスADRpの値)を用いて比較コードCODEを生成する。したがって、この実施形態では、保護対象のモジュール20内に固定の比較コードを設けなくともよい。このため、誤書き込み防止回路10は、誤書き込み対策の無い既存のモジュールに対しても、誤書き込みを防止できる。

【0016】

さらに、バスBUS上の情報を用いて比較コードCODEが生成されるため、比較コードCODEは、固定されない。このため、この実施形態では、期待値DATAIeと固定された比較コードCODEとを比較する構成に比べて、保護対象のモジュール20のセキュリティを向上できる。

【0017】

なお、比較コード生成部CGは、互いに異なるタイミングで取得した複数のアドレスADRpの値を用いて比較コードCODEを生成してもよいし、1つのアドレスADRpの値を用いて比較コードCODEを生成してもよい。例えば、互いに異なるタイミングで取得した複数のアドレスADRpの値を用いて比較コードCODEを生成したときには、比較コードCODEに時系列の要素が含まれるため、保護対象のモジュール20のセキュリティは、向上する。

【0018】

比較部COMPは、保護対象のモジュール20に書き込まれるライトデータ(例えば、図2に示すライトデータDATAIw)に対応する期待値DATAIeと比較コードCODEとを比較する。例えば、期待値DATAIeと比較コードCODEとの比較は、特別なシーケンス(ライトデータを書き込む前の比較用の書き込み動作等)のための時間を別途設けることなく、常に実施される。そして、比較部COMPは、比較結果を書き込み制御部WCTLに通知する。例えば、比較部COMPの出力信号(比較結果)は、期待値DATAIeと比較コードCODEとが一致しているとき、アサートされる。

【0019】

書き込み制御部WCTLは、ライトストローブ信号WRSおよび比較部COMPの比較結果を受け、モジュール20用のライトストローブ信号WRSIをモジュール20に出力する。例えば、書き込み制御部WCTLは、期待値DATAIeと比較コードCODEとが一致しているとき、ライトストローブ信号WRSのアサートに応答して、ライトストローブ信号WRSIをアサートする。これにより、モジュール20に対する書き込みは、許可される。

【0020】

また、例えば、書き込み制御部WCTLは、期待値DATAIeと比較コードCODEとが不一致のとき、ライトストローブ信号WRSの状態に拘わらず、ライトストローブ信号WRSIをネゲートする。これにより、モジュール20に対する書き込みは、禁止される。すなわち、書き込み制御部WCTLは、比較部COMPの比較結果に基づいて、モジュール20に対する書き込みを許可するか否かを決定する。

【0021】

なお、誤書き込み防止回路10の構成は、この例に限定されない。例えば、誤書き込み防止回路10は、期待値DATAIeと比較コードCODEとの比較を実施するか否かをCPU30等により制御されてもよい。この場合、期待値DATAIeと比較コードCODEとの比較が許可されている期間、期待値DATAIeと比較コードCODEとの比較が常に実施される。

【0022】

また、例えば、比較コード生成部CGは、バスBUSに出力されたデータ(データDATAIや図3に示すデータDATAO)の一部の値を取得し、取得した値を用いて比較コードCODEを生成してもよい。あるいは、比較コード生成部CGは、バスBUSに出力されたアドレスADRおよびデータのそれぞれの一部の値を取得し、取得した値を用いて比較コードCODEを生成してもよい。すなわち、比較コード生成部CGは、バスBUSに出力されたアドレスADRおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードCODEを生成する。

【0023】

図2は、図1に示した保護対象のモジュール20にライトデータを書き込む際のデータ構成の一例を示している。なお、図2は、バスBUSのデータバスのバス幅が32ビットで、モジュール20のデータバス幅が16ビットのときのデータDATAIの一例を示している。

【0024】

例えば、データDATAIは、下位16ビット(0ビット−15ビット)がモジュール20に書き込まれるライトデータDATAIwに割り当てられ、上位16ビット(16ビット−31ビット)が期待値DATAIeに割り当てられる。この場合、保護対象のモジュール20への1回の書き込みに対して、データDATAIが1回出力されればよい。期待値DATAIeとライトデータDATAIwとが一緒に出力されるため、書き込み時間の増加が抑制される。例えば、データDATAIの下位16ビット(ライトデータDATAIw)は、データDATAIの上位16ビット(期待値DATAIe)が比較コードCODEと一致したとき、モジュール20に書き込まれる。なお、モジュール20では、例えば、データDATAIの上位16ビット(期待値DATAIe)は破棄される。

【0025】

ここで、モジュール20のデータバス幅(例えば、32ビット)がバスBUSのデータバスのバス幅と一致しているときには、保護対象のモジュール20への1回の書き込みに対して、データDATAIが2回出力される。この場合、16ビットの期待値DATAIeおよび16ビットのライトデータDATAIwを含むデータDATAIが2回出力されてもよいし、16ビットの期待値DATAIeを含むデータDATAIと32ビットのライトデータDATAIwを含むデータDATAIとが順次出力されてもよい。

【0026】

すなわち、モジュール20のデータバス幅がバスBUSのデータバスのバス幅と一致している構成では、2回の書き込み動作により、モジュール20にライトデータIDATAIwを書き込むことができる。したがって、モジュール20のデータバス幅がバスBUSのデータバスのバス幅と一致している構成においても、例えば、モジュール20にライトデータIDATAIwを書き込む前に複数回の書き込み動作(所定のシーケンス)を実施する構成に比べて、書き込み時間を短くできる。すなわち、モジュール20のデータバス幅がバスBUSのデータバスのバス幅と一致している構成においても、書き込み時間の増加を抑制しつつ、保護対象のモジュール20に対する誤書き込みを防止できる。

【0027】

なお、データDATAIに対する期待値DATAIeの割り当ては、この例に限定されない。例えば、期待値DATAIeのデータ幅は、保護対象のモジュール20のセキュリティレベルやバスBUS構成等に応じて決定される。

【0028】

図3は、図1に示した誤書き込み防止回路10が搭載される半導体装置100の一例を示している。半導体装置100は、例えば、誤書き込み防止回路10、保護対象のモジュール20、CPU30、保護対象以外のモジュール40、42および選択部50を有している。誤書き込み防止回路10、モジュール20、40、42、CPU30および選択部50は、バスBUSに接続されている。なお、半導体装置100の最小構成は、誤書き込み防止回路10および保護対象のモジュール20である。

【0029】

誤書き込み防止回路10は、例えば、データDATAIに含まれる期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRSおよびリードストローブ信号RDSを、バスBUSを介して受け、ライトストローブ信号WRSIをモジュール20に出力する。例えば、誤書き込み防止回路10は、保護対象のモジュール20に対する書き込みが実施される前に、ジュール20、40、42に対する書き込み動作や読み出し動作が実施される度に、アドレスADRpを取得する。そして、誤書き込み防止回路10は、例えば、互いに異なるタイミングで取得した複数のアドレスADRpの値を用いて比較コードCODEを生成する。

【0030】

モジュール20は、例えば、データバス幅が16ビットのレジスタであり、アドレスADRをデコードするアドレスデコーダADECを有している。なお、アドレスデコーダADECは、モジュール20の外部に設けられてもよい。モジュール20は、例えば、データDATAI、アドレスADRおよびリードストローブ信号RDSを、バスBUSを介して受ける。さらに、モジュール20は、ライトストローブ信号WRSIを誤書き込み防止回路10から受ける。

【0031】

例えば、書き込み動作時には、ライトストローブ信号WRSIおよびアドレスADRに基づいて、データDATAI(より詳細には、図2に示したライトデータDATAIw)がモジュール20に書き込まれる。また、読み出し動作時には、リードストローブ信号RDSおよびアドレスADRに基づいて、モジュール20からデータDATAOが出力される。

【0032】

CPU30は、例えば、半導体装置100の動作を制御する。例えば、CPU30は、モジュール20、40、42に対する書き込み動作や読み出し動作を制御する。なお、CPU30は、誤書き込み防止回路10の動作を制御してもよい。例えば、CPU30は、期待値DATAIeと比較コードCODEとの比較を実施するか否かを制御してもよい。すなわち、誤書き込み防止回路10は、期待値DATAIeと比較コードCODEとの比較を実施するか否かをCPU30等により制御されてもよい。

【0033】

モジュール40、42は、例えば、データバス幅が32ビットのレジスタである。例えば、ジュール40、42は、データDATAI、アドレスADR、ライトストローブ信号WRSおよびリードストローブ信号RDSを、バスBUSを介して受ける。また、例えば、モジュール40、42は、データDATAOを、選択部50を介してバスBUSに出力する。

【0034】

例えば、書き込み動作時には、ライトストローブ信号WRSおよびアドレスADRに基づいて、データDATAIがモジュール40、42に書き込まれる。また、読み出し動作時には、リードストローブ信号RDSおよびアドレスADRに基づいて、モジュール40、42からデータDATAOが出力される。

【0035】

選択部50は、モジュール20、40、42からデータDATAOを受け、有効なデータDATAOをバスBUSに出力する。例えば、選択部50からバスBUSに出力されるデータDATAOは、リードストローブ信号RDSおよびアドレスADRに基づいてモジュール20、40、42のいずれかから読み出されたデータDATAOである。

【0036】

以上、この実施形態では、誤書き込み防止回路10は、比較コードCODEと期待値DATAIeとの比較結果に基づいて、保護対象のモジュール20に対する書き込みを許可するか否かを決定する。また、この実施形態では、例えば、特別なシーケンス動作の書き込み時間を設けることなく、比較コードCODEと期待値DATAIeとの比較が実施される。したがって、この実施形態では、特別なシーケンス動作の書き込み時間等の余計な時間を省くことができ、書き込み時間の増加を抑制できる。この結果、この実施形態では、書き込み時間の増加を抑制しつつ、保護対象のモジュール20に対する誤書き込みを防止できる。また、この実施形態では、比較コードCODEが可変であるため、比較コードCODEを変更する頻度を調整することにより、システム上でのセキュリティレベルを調整することができる。

【0037】

図4は、別の実施形態における誤書き込み防止回路11の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路11では、図1に示した誤書き込み防止回路10に比較制御部CCTLが追加され、比較コード生成部CGおよび書き込み制御部WCTLの代わりに比較コード生成部CG2および書き込み制御部WCTL2がそれぞれ設けられている。誤書き込み防止回路11のその他の構成は、上述した実施形態と同じである。また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路11が設けられることを除いて、上述した実施形態と同じである。例えば、半導体装置の最小構成は、誤書き込み防止回路11および保護対象のモジュール20である。

【0038】

誤書き込み防止回路11は、例えば、比較コード生成部CG2、比較部COMP、書き込み制御部WCTL2および比較制御部CCTLを有している。例えば、誤書き込み防止回路11は、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTSおよびクロックCLKを受け、ライトストローブ信号WRSIを出力する。比較制御信号CNTSは、例えば、比較コード生成部CG2および書き込み制御部WCTL2に対する比較許可信号CENをアサートするための信号であり、CPUから出力される。

【0039】

比較制御部CCTLは、例えば、比較制御信号CNTSおよびライトストローブ信号WRSIを受け、比較許可信号CENを比較コード生成部CG2のAND回路AND1および書き込み制御部WCTL2のAND回路AND2に出力する。例えば、比較制御部CCTLは、CPUから受ける比較制御信号CNTSに応答して、比較許可信号CENをアサートし、書き込み制御部WCTL2から受けるライトストローブ信号WRSIに応答して、比較許可信号CENをネゲートする。これにより、比較制御部CCTLは、比較コード生成部CG2および書き込み制御部WCTL2の動作を制御する。

【0040】

比較コード生成部CG2は、例えば、アドレスADRp、ライトストローブ信号WRS、リードストローブ信号RDS、比較許可信号CENおよびクロックCLKを受け、比較コードCODEを比較部COMPに出力する。例えば、比較コード生成部CG2は、OR回路OR1、AND回路AND1、フリップフロップ回路FF1、FF2、FF3、FF4およびマルチプレクサMUX1を有している。

【0041】

OR回路OR1は、ライトストローブ信号WRSおよびリードストローブ信号RDSを受け、ライトストローブ信号WRSとリードストローブ信号RDSとの論理和結果をAND回路AND1に出力する。AND回路AND1は、OR回路OR1の出力信号と比較許可信号CENとの論理積結果を、各フリップフロップ回路FF(FF1−FF4)のイネーブル端子ENに出力する。すなわち、各フリップフロップ回路FFのイネーブル端子ENが受けるイネーブル信号は、ライトストローブ信号WRSおよびリードストローブ信号RDSのいずれかと比較許可信号CENとがアサートされているときに、アサートされる。

【0042】

各フリップフロップ回路FFは、例えば、イネーブル端子ENで受けるイネーブル信号がアサートされているとき、端子CKで受けるクロックCLKが立ち上がる度に、入力端子Dで受けた信号を取り込み、保持する。例えば、フリップフロップ回路FF1、FF2、FF3の出力端子Qは、フリップフロップ回路FF2、FF3、FF4の入力端子Dにそれぞれ接続されている。すなわち、フリップフロップ回路FF1−FF4は、クロックCLKに同期して動作するシフトレジスタとして機能する。

【0043】

例えば、フリップフロップ回路FF1は、クロックCLKが立ち上がる度に、バスBUSに出力されているアドレスADRの一部(アドレスADRp)の値を取り込み、保持する。また、フリップフロップ回路FF2、FF3、FF4は、クロックCLKが立ち上がる度に、フリップフロップ回路FF1、FF2、FF3にそれぞれ保持されているアドレスADRpの値を取り込み、保持する。なお、フリップフロップ回路FF4に保持されているアドレスADRpの値は、例えば、クロックCLKが立ち上がる度に、破棄される。

【0044】

すなわち、各フリップフロップ回路FFが保持しているアドレスADRpの値は、例えば、クロックCLKが立ち上がる度に、更新される。なお、任意のモジュールに対する読み出し動作および書き込み動作のいずれも実施されないアイドルサイクルでは、ライトストローブ信号WRSおよびリードストローブ信号RDSのいずれもネゲートされているため、各フリップフロップ回路FFのイネーブル信号は、ネゲートされる。したがって、アイドルサイクルでは、フリップフロップ回路FF1−FF4がそれぞれ保持しているアドレスADRpの値(信号CODEa、CODEb、CODEc、CODEd)は、維持される。

【0045】

また、各フリップフロップ回路FF(FF1−FF4)の出力端子Qは、マルチプレクサMUX1の入力部に接続される。すなわち、フリップフロップ回路FF1−FF4がそれぞれ保持しているアドレスADRpの値(信号CODEa、CODEb、CODEc、CODEd)は、マルチプレクサMUX1に入力される。

【0046】

マルチプレクサMUX1は、例えば、並列直列変換回路として動作し、フリップフロップ回路FF1−FF4から受けた4つの信号CODEa、CODEb、CODEc、CODEdを1つの比較コードCODEとして比較部COMPに出力する。例えば、マルチプレクサMUX1は、アドレスADRpのビット幅が4ビットのとき、信号CODEa、CODEb、CODEc、CODEdを、比較コードCODEの0ビット−3ビット、4ビット−7ビット、8ビット−11ビット、12ビット−15ビットにそれぞれ割り当てる。

【0047】

すなわち、比較コードCODEは、互いに異なるタイミングで取得した4つのアドレスADRpの値を用いて生成される。例えば、比較コードCODEを構成する信号CODEa、CODEb、CODEc、CODEdでは、信号CODEaは、最後に取得したアドレスADRpの値であり、信号CODEbは、3番目に取得したアドレスADRpの値であり、信号CODEcは、2番目に取得したアドレスADRpの値であり、信号CODEdは、最初に取得したアドレスADRpの値である。このように、比較コードCODEは、時系列の要素を含む。

【0048】

比較部COMPは、期待値DATAIeと比較コードCODEとを比較し、比較結果を書き込み制御部WCTLに通知する。このように、この実施形態では、時系列の要素を含む比較コードCODEと期待値DATAIeとを比較するため、時系列の要素を含まない比較コードCODEを用いうる構成に比べて、保護対象のモジュール20のセキュリティを向上できる。

【0049】

なお、この実施形態では、例えば、書き込み動作や読み出し動作が実施される度にアドレスADRpが順次取得されるため、時系列の要素を含む比較コードCODEを生成するための時間を別途設けなくともよい。したがって、この実施形態では、書き込み時間の増加を抑制しつつ、保護対象のモジュール20のセキュリティを向上できる。すなわち、この実施形態では、書き込み時間の増加を抑制しつつ、保護対象のモジュール20に対する誤書き込みを防止できる。

【0050】

書き込み制御部WCTL2は、例えば、ライトストローブ信号WRS、比較許可信号CENおよび比較部COMPの比較結果を受け、ライトストローブ信号WRSIを比較制御部CCTLおよび保護対象のモジュール20に出力する。比較部COMPの出力信号(比較結果)は、例えば、期待値DATAIeと比較コードCODEとが一致しているとき、アサートされる。

【0051】

例えば、書き込み制御部WCTL2は、ライトストローブ信号WRS、比較許可信号CENおよび比較部COMPの比較結果を受けるAND回路AND2を有している。AND回路AND2は、ライトストローブ信号WRS、比較許可信号CENおよび比較部COMPの出力信号(比較結果)の論理積結果(ライトストローブ信号WRSI)を、比較制御部CCTLおよび保護対象のモジュール20に出力する。

【0052】

したがって、書き込み制御部WCTL2は、比較許可信号CENがアサートされているとき、比較部COMPの比較結果に基づいて、モジュール20に対する書き込みを許可するか否かを決定する。すなわち、比較許可信号CENがアサートされているときの書き込み制御部WCTL2の動作は、上述した実施形態の書き込み制御部WCTLと同じである。

【0053】

例えば、書き込み制御部WCTL2は、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、期待値DATAIeと比較コードCODEとが一致しているとき、ライトストローブ信号WRSIをアサートする。これにより、モジュール20に対する書き込みは、許可される。また、例えば、書き込み制御部WCTL2は、期待値DATAIeと比較コードCODEとが不一致のとき、ライトストローブ信号WRSおよび比較許可信号CENの状態に拘わらず、ライトストローブ信号WRSIをネゲートする。これにより、モジュール20に対する書き込みは、禁止される。

【0054】

なお、書き込み制御部WCTL2は、例えば、比較許可信号CENがネゲートされているときには、比較部COMPの比較結果およびライトストローブ信号WRSの状態に拘わらず、ライトストローブ信号WRSIをネゲートする。すなわち、書き込み制御部WCTL2は、比較許可信号CENがネゲートされているときには、モジュール20に対する書き込みを禁止する。このように、この実施形態では、比較許可信号CENをネゲートすることにより、モジュール20に対する書き込みを禁止できるため、モジュール20のセキュリティをさらに向上できる。

【0055】

なお、誤書き込み防止回路11の構成は、この例に限定されない。例えば、誤書き込み防止回路11は、比較制御部CCTLが省かれてもよい。また、例えば、シフトレジスタを構成するフリップフロップ回路FFの数は、2つでもよいし、3つでもよい。あるいは、シフトレジスタを構成するフリップフロップ回路FFの数は、5つ以上でもよい。

【0056】

図5は、図4に示した誤書き込み防止回路11の動作の一例を示している。なお、図5は、保護対象のモジュール20とは別の2つのモジュール(例えば、図3に示したモジュール40、42)に対するアクセスが実施された後に、モジュール20に対する書き込み動作が実施されるときの誤書き込み防止回路11の動作の一例を示している。図5では、モジュール20とは別の2つのモジュールを、図3に示したモジュール40およびモジュール42として説明する。例えば、図5に示した動作では、モジュール40に対する書き込み動作および読み出し動作、アイドルサイクル、モジュール42に対する書き込み動作および読み出し動作、モジュール20に対する書き込み動作が順番に実施される。

【0057】

また、図5の例では、比較コード生成部CG2により取り込まれるアドレスADRpのビット幅は4ビットであり、比較コードCODEおよび期待値DATAIeのビット幅は16ビットであり、バスBUSのデータバス幅は32ビットである。図中の“i”、“j”、“k”、“l”、“m”、“n”、“x”は、4ビットで示される任意の値を示している。なお、この動作の説明においては、図中の“x”は、特に意味のない値である。また、図中の“4321”は、モジュール20に書き込まれる16ビットのライトデータを示している。

【0058】

先ず、CPUの制御信号(図4に示した比較制御信号CNTS)に応答して、比較許可信号CENがアサートされる。これにより、比較コードCODEは、例えば、読み出し動作および書き込み動作のいずれかが実施される度に、更新される。

【0059】

期間T1では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール40内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール40に対する書き込み動作が実施される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“i”である。したがって、期間T2において、比較コードCODEは、“xxxi”に更新される。

【0060】

期間T2では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール40内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール40に対する読み出し動作が実施される。なお、バスBUSに出力されたアドレス(読み出し対象のアドレス)の下位4ビット(アドレスADRp)は、“j”である。したがって、期間T3において、比較コードCODEは、“xxij”に更新される。

【0061】

期間T3では、ライトストローブ信号WRSおよびリードストローブ信号RDSがネゲートされ、任意のアドレスがバスBUSに出力される。すなわち、期間T3は、アイドルサイクルである。なお、バスBUSに出力されたアドレスの下位4ビット(アドレスADRp)は、“k”である。期間T3がアイドルサイクルであるため、期間T4において、比較コードCODEは、更新されない。すなわち、比較コードCODEは、“xxij”に維持される。

【0062】

期間T4では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール42内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール42に対する書き込み動作が実施される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“l”である。したがって、期間T5において、比較コードCODEは、“xijl”に更新される。

【0063】

期間T5では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール42内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール42に対する読み出し動作が実施される。なお、バスBUSに出力されたアドレス(読み出し対象のアドレス)の下位4ビット(アドレスADRp)は、“m”である。したがって、期間T6において、比較コードCODEは、“ijlm”に更新される。これにより、保護対象のモジュール20に対する書き込み動作時に参照される比較コードCODEが生成される。

【0064】

この例では、比較コードCODEは、期間T1、T2、T4、T5のアドレス(モジュール20に対する書き込み動作の前に実施された4回のアクセスのアドレス)の情報を含んでいる。すなわち、比較コードCODEは、互いに異なるタイミングで取得した複数のアドレスADRpの値を用いて生成され、時系列の要素を含む。

【0065】

期間T6では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、データDATAIおよびモジュール20内の領域を示すアドレスがバスBUSに出力される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“n”である。また、バスBUSに出力されたDATAIは、モジュール20に対する書き込みを実施するためのデータである。例えば、データDATAIの上位16ビット(期待値DATAIe)は、“ijlm”であり、データDATAIの下位16ビット(ライトデータDATAIw)は、“4321”である。

【0066】

このように、期間T6では、データDATAIの上位16ビット(期待値DATAIe)および比較コードCODEは、共に“ijlm”であり、互いに一致している。すなわち、期間T6では、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、期待値DATAIeと比較コードCODEとが一致している。このため、ライトストローブ信号WRSIがアサートされる。なお、期間T1−T5以外では、期待値DATAIeと比較コードCODEとが不一致のため、ライトストローブ信号WRSIはネゲートされている。

【0067】

ライトストローブ信号WRSIがアサートされたため、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“4321”)がモジュール20に書き込まれる。このように、この実施形態では、保護対象のモジュール20に対する書き込み動作が実施される前に、比較コードCODEに用いられるアドレスADRp(“i”、“j”、“l”、“m”)が取得される。そして、例えば、期待値DATAIeと比較コードCODEとが不一致のときには、ライトストローブ信号WRSIがネゲートされるため、モジュール20に対する書き込みは、禁止される。これにより、この実施形態では、モジュール20に対する誤書き込みを防止できる。

【0068】

ここで、例えば、モジュール20を使用する正規のプログラマは、モジュール20に対する書き込み動作の前に実施されるアクセスを認識している。したがって、プログラマは、モジュール20にライトデータを書き込む際の期待値DATAIeとして、“ijlm”をデータDATAIの上位16ビットに設定できる。換言すれば、不正な使用者は、モジュール20にライトデータを書き込む際の期待値DATAIeとして、“ijlm”をデータDATAIの上位16ビットに設定することが困難である。

【0069】

したがって、この実施形態では、モジュール20のデータが不正に書き換えられることを防止できる。また、この実施形態では、時系列の要素が比較コードCODEに含まれるため、比較コードCODEと期待値DATAIeとが誤動作等により偶然一致することを低減できる。したがって、この実施形態では、保護対象のモジュール20のセキュリティを向上できる。

【0070】

期間T7では、ライトストローブ信号WRSおよびリードストローブ信号RDSがネゲートされる。また、ライトストローブ信号WRSIが期間T6にアサートされたため、期間T7において、比較許可信号CENがネゲートされる。例えば、比較制御部CCTLは、ライトストローブ信号WRSIのアサートに応答して、比較許可信号CENをネゲートする。これにより、モジュール20に対する書き込み動作が終了する。なお、期間T7では、比較コードCODEは、“jlmn”に更新されている。そして、期間T8では、期間T7がアイドルサイクルであるため、比較コードCODEは、“jlmn”に維持される。

【0071】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、時系列の要素を含む比較コードCODEと期待値DATAIeとが一致したときに、保護対象のモジュール20に対する書き込みが許可される。これにより、この実施形態では、保護対象のモジュール20のセキュリティをさらに向上できる。また、この実施形態では、例えば、比較コードCODEに用いられるアドレスADRpは、モジュール40等に対する通常のアクセスが実施されたとき(期間T1、T2、T4、T5)、取得される。したがって、この実施形態では、比較コードCODEに時系列の要素を含めるための時間を別途設けなくともよい。

【0072】

すなわち、この実施形態では、モジュール20に対する誤書き込みを防止するために、特別なシーケンス(ライトデータを書き込む前の比較用の書き込み動作等)を実施するための時間を別途設けなくともよい。これにより、この実施形態では、書き込み時間の増加を抑制しつつ、モジュール20のセキュリティを向上できる。すなわち、この実施形態では、書き込み時間の増加を抑制しつつ、保護対象のモジュール20に対する誤書き込みを防止できる。

【0073】

図6は、別の実施形態における誤書き込み防止回路12の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路12は、図4に示した比較コード生成部CG2の代わりに、比較コード生成部CG4を有している。誤書き込み防止回路12のその他の構成は、図4および図5で説明した実施形態と同じである。また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路12が設けられることを除いて、図1−図3で説明した実施形態と同じである。例えば、半導体装置の最小構成は、誤書き込み防止回路12および保護対象のモジュール20である。

【0074】

誤書き込み防止回路12は、例えば、比較コード生成部CG4、比較部COMP、書き込み制御部WCTL2および比較制御部CCTLを有している。例えば、誤書き込み防止回路12は、データDATAIp、DATAOp、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTSおよびクロックCLKを受け、ライトストローブ信号WRSIを出力する。なお、データDATAIpは、書き込み動作時にバスBUSに出力されるデータDATAIの一部(例えば、下位4ビット)である。また、データDATAOpは、読み出し動作時にバスBUSに出力されるデータDATAOの一部(例えば、下位4ビット)である。

【0075】

比較コード生成部CG4は、例えば、データDATAIp、DATAOp、アドレスADRp、ライトストローブ信号WRS、リードストローブ信号RDS、比較許可信号CENおよびクロックCLKを受け、比較コードCODEを比較部COMPに出力する。例えば、比較コード生成部CG4は、データDATAIpの値およびアドレスADRpの値を書き込み動作時に取得し、データDATAOpの値およびアドレスADRpの値を読み出し動作時に取得する。そして、比較コード生成部CG4は、例えば、取得した値(アドレスADRp等の値)を用いて比較コードCODEを生成する。

【0076】

例えば、比較コード生成部CG4は、OR回路OR1、AND回路AND1、セレクタSEL、マルチプレクサMUX2、MUX3、フリップフロップ回路FF5、FF6を有している。

【0077】

OR回路OR1は、ライトストローブ信号WRSとリードストローブ信号RDSとの論理和結果をAND回路AND1に出力する。AND回路AND1は、OR回路OR1の出力信号と比較許可信号CENとの論理積結果を、フリップフロップ回路FF5、FF6のイネーブル端子ENに出力する。すなわち、フリップフロップ回路FF5、FF6のイネーブル端子ENが受けるイネーブル信号は、ライトストローブ信号WRSおよびリードストローブ信号RDSのいずれかと比較許可信号CENとがアサートされているときに、アサートされる。

【0078】

セレクタSELは、データDATAIp、DATAOpおよびライトストローブ信号WRSを受け、データDATAIp、DATAOpのいずれかをマルチプレクサMUX2に出力する。例えば、セレクタSELは、ライトストローブ信号WRSがアサートされているとき、データDATAIpをマルチプレクサMUX2に出力し、ライトストローブ信号WRSがネゲートされているとき、データDATAOpをマルチプレクサMUX2に出力する。

【0079】

なお、セレクタSELは、ライトストローブ信号WRSの代わりに、リードストローブ信号RDSを受けてもよい。すなわち、セレクタSELは、書き込み動作時に、データDATAIpをマルチプレクサMUX2に出力し、かつ、読み出し動作時に、データDATAOpをマルチプレクサMUX2に出力するように構成されればよい。

【0080】

マルチプレクサMUX2は、例えば、並列直列変換回路として動作し、2つの信号を1つの信号に変換して、フリップフロップ回路FF5の入力端子Dに出力する。例えば、データDATAIp、DATAOpおよびアドレスADRpのビット幅が4ビットのとき、マルチプレクサMUX2は、セレクタSELから受けた4ビットのデータ(データDATAIp、DATAOpのいずれか)とバスBUSに出力されているアドレスADRp(アドレスADRの一部)とを合わせた8ビットのデータを、フリップフロップ回路FF5の入力端子Dに出力する。

【0081】

フリップフロップ回路FF5、FF6は、例えば、イネーブル端子ENで受けるイネーブル信号がアサートされているとき、端子CKで受けるクロックCLKが立ち上がる度に、入力端子Dで受けた信号を取り込み、保持する。例えば、フリップフロップ回路FF5の出力端子Qは、フリップフロップ回路FF6の入力端子Dに接続されている。すなわち、フリップフロップ回路FF5、FF6は、クロックCLKに同期して動作するシフトレジスタとして機能する。

【0082】

例えば、フリップフロップ回路FF5は、クロックCLKが立ち上がる度に、マルチプレクサMUX2から受けた信号(データDATAIp、DATAOpのいずれかとアドレスADRp)の値を取り込み、保持する。また、フリップフロップ回路FF6は、クロックCLKが立ち上がる度に、フリップフロップ回路FF5に保持されている信号の値を取り込み、保持する。なお、フリップフロップ回路FF6に保持されている信号の値は、例えば、クロックCLKが立ち上がる度に、破棄される。

【0083】

すなわち、フリップフロップ回路FF5、FF6が保持している信号の値は、例えば、クロックCLKが立ち上がる度に、更新される。なお、アイドルサイクルでは、ライトストローブ信号WRSおよびリードストローブ信号RDSのいずれもネゲートされているため、各フリップフロップ回路FFのイネーブル信号は、ネゲートされる。したがって、アイドルサイクルでは、フリップフロップ回路FF5、FF6がそれぞれ保持している信号の値(信号CODEab、CODEcd)は、維持される。

【0084】

また、フリップフロップ回路FF5、FF6の出力端子Qは、マルチプレクサMUX3の入力部に接続される。すなわち、フリップフロップ回路FF5、FF6がそれぞれ保持している信号の値(信号CODEab、CODEcd)は、マルチプレクサMUX1に入力される。

【0085】

マルチプレクサMUX3は、例えば、並列直列変換回路として動作し、フリップフロップ回路FF5、FF6から受けた2つの信号CODEab、CODEcdを1つの比較コードCODEとして比較部COMPに出力する。例えば、マルチプレクサMUX3は、データDATAIp、DATAOpおよびアドレスADRpのビット幅が4ビットのとき、信号CODEab、CODEcdを、比較コードCODEの0ビット−7ビット、8ビット−15ビットにそれぞれ割り当てる。

【0086】

すなわち、比較コードCODEは、互いに異なるタイミングで取得した2つの信号CODEab、CODEcdを用いて生成され、時系列の要素を含む。また、信号CODEab、CODEcdは、アドレスADRの一部とデータ(データDATAI、DATAO)の一部とを含んでいる。このため、この実施形態では、例えば、アドレスADRpのみを用いて生成された比較コードCODEに比べて、比較コードCODEの不規則性を高くできる。これにより、保護対象のモジュール20のセキュリティは、向上する。

【0087】

比較部COMPは、期待値DATAIeと比較コードCODEとを比較し、比較結果を書き込み制御部WCTLに通知する。書き込み制御部WCTL2は、例えば、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、期待値DATAIeと比較コードCODEとが一致しているとき、ライトストローブ信号WRSIをアサートする。また、例えば、書き込み制御部WCTL2は、比較許可信号CENがネゲートされているときには、比較部COMPの比較結果およびライトストローブ信号WRSの状態に拘わらず、ライトストローブ信号WRSIをネゲートする。

【0088】

なお、誤書き込み防止回路12の構成は、この例に限定されない。例えば、誤書き込み防止回路12は、比較制御部CCTLが省かれてもよい。また、例えば、シフトレジスタを構成するフリップフロップ回路FFの数は、3つ以上でもよい。あるいは、比較コード生成部CG4は、例えば、アドレスADRpを用いずに、データの一部(例えば、データDATAIp、DATAOp)のみを用いて比較コードCODEを生成してもよい。

【0089】

図7は、図6に示した誤書き込み防止回路12の動作の一例を示している。なお、図6は、保護対象のモジュール20とは別の2つのモジュール(例えば、図3に示したモジュール40、42)に対するアクセスが実施された後に、モジュール20に対する書き込み動作が実施されるときの誤書き込み防止回路12の動作の一例を示している。図7では、モジュール20とは別の2つのモジュールを、図3に示したモジュール40およびモジュール42として説明する。例えば、図7に示した動作では、モジュール40に対する書き込み動作および読み出し動作、アイドルサイクル、モジュール42に対する書き込み動作および読み出し動作、モジュール20に対する書き込み動作が順番に実施される。

【0090】

また、図7の例では、比較コード生成部CG4により取り込まれるデータDATAIp、DATAOpおよびアドレスADRpのビット幅は4ビットであり、比較コードCODEおよび期待値DATAIeのビット幅は16ビットである。また、バスBUSのデータバス幅は32ビットである。図中の“a”、“b”、“c”、“d”、“i”、“j”、“k”、“l”、“m”、“n”、“x”は、4ビットで示される任意の値を示している。なお、この動作の説明においては、図中の“x”は、特に意味のない値である。また、図中の“4321”は、モジュール20に書き込まれる16ビットのライトデータを示している。

【0091】

先ず、CPUの制御信号(図6に示した比較制御信号CNTS)に応答して、比較許可信号CENがアサートされる。これにより、比較コードCODEは、例えば、読み出し動作および書き込み動作のいずれかが実施される度に、更新される。

【0092】

期間T1では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされる。また、データDATAIおよびモジュール40内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール40に対する書き込み動作が実施される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“i”である。また、バスBUSに出力されたデータDATAIの下位4ビット(図6に示したデータDATAIp)は、“a”である。

【0093】

したがって、期間T2において、比較コードCODEは、“xxia”に更新される。この例の比較コードCODEでは、データDATAIの一部(データDATAIp)は、アドレスADRpより下位のビットに割り当てられている。なお、アドレスADRpとデータDATAIpとが割り当てられるビットは、互いに逆でもよい。

【0094】

期間T2では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール40内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール40に対する読み出し動作が実施され、バスBUSにリードデータ(図6に示したデータDATAO)が出力される。

【0095】

なお、バスBUSに出力されたアドレス(読み出し対象のアドレス)の下位4ビット(アドレスADRp)は、“j”である。また、バスBUSに出力されたリードデータの下位4ビット(データDATAOp)は、“b”である。したがって、期間T3において、比較コードCODEは、“iajb”に更新される。

【0096】

期間T3では、ライトストローブ信号WRSおよびリードストローブ信号RDSがネゲートされる。すなわち、期間T3は、アイドルサイクルである。例えば、アイドルサイクルにバスBUSに出力されているアドレスの下位4ビット(アドレスADRp)は、“k”である。期間T3がアイドルサイクルであるため、期間T4において、比較コードCODEは、更新されない。すなわち、比較コードCODEは、“iajb”に維持される。

【0097】

期間T4では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされる。また、データDATAIおよびモジュール42内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール42に対する書き込み動作が実施される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“l”である。また、バスBUSに出力されたデータDATAIの下位4ビットは、“c”である。したがって、期間T5において、比較コードCODEは、“jblc”に更新される。

【0098】

期間T5では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール42内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール42に対する読み出し動作が実施され、バスBUSにリードデータが出力される。

【0099】

なお、バスBUSに出力されたアドレス(読み出し対象のアドレス)の下位4ビット(アドレスADRp)は、“m”である。また、バスBUSに出力されたリードデータの下位4ビット(データDATAOp)は、“d”である。したがって、期間T6において、比較コードCODEは、“lcmd”に更新される。これにより、保護対象のモジュール20に対する書き込み動作時に参照される比較コードCODEが生成される。

【0100】

この例では、比較コードCODEは、期間T4のバスBUS上のアドレスADRpおよびデータDATAIの一部(データDATAIp)と期間T5のバスBUS上のアドレスADRpおよびデータDATAOpとを含んでいる。すなわち、比較コードCODEは、互いに異なるタイミングで取得したバスBUS上の情報を用いて生成され、時系列の要素を含む。なお、この例では、期間T1、T2のバスBUS上の情報は、オーバーフローにより破棄され、期待値DATAIeとの比較対象から外れる。したがって、比較許可信号CENは、例えば、期間T4の直前にアサートされるように制御されてもよい。

【0101】

期間T6では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、データDATAIおよびモジュール20内の領域を示すアドレスがバスBUSに出力される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“n”である。また、バスBUSに出力されたDATAIは、モジュール20に対する書き込みを実施するためのデータである。例えば、データDATAIの上位16ビット(期待値DATAIe)は、“lcmd”であり、データDATAIの下位16ビット(ライトデータDATAIw)は、“4321”である。

【0102】

データDATAIの上位16ビット(期待値DATAIe)および比較コードCODEは、共に“lcmd”であり、互いに一致している。すなわち、期間T6では、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、期待値DATAIeと比較コードCODEとが一致している。このため、ライトストローブ信号WRSIがアサートされる。なお、期間T1−T5では、期待値DATAIeと比較コードCODEとが不一致のため、ライトストローブ信号WRSIはネゲートされている。

【0103】

ライトストローブ信号WRSIがアサートされたため、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“4321”)がモジュール20に書き込まれる。なお、例えば、期待値DATAIeと比較コードCODEとが不一致のときには、ライトストローブ信号WRSIがネゲートされるため、モジュール20に対する書き込みは、禁止される。これにより、この実施形態では、モジュール20に対する誤書き込みを防止できる。

【0104】

ここで、例えば、モジュール20を使用する正規のプログラマは、モジュール20に対する書き込み動作の前に実施されるアクセスを認識している。したがって、プログラマは、モジュール20にライトデータを書き込む際の期待値DATAIeとして、“lcmd”をデータDATAIの上位16ビットに設定できる。

【0105】

期間T7では、ライトストローブ信号WRSおよびリードストローブ信号RDSがネゲートされる。また、ライトストローブ信号WRSIが期間T6にアサートされたため、期間T7において、比較許可信号CENがネゲートされる。これにより、モジュール20に対する書き込み動作が終了する。なお、期間T7では、比較コードCODEは、“mdn1”に更新されている。そして、期間T8では、期間T7がアイドルサイクルであるため、比較コードCODEは、“mdn1”に維持される。

【0106】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、比較コードCODEは、アドレスADRの一部とデータ(データDATAI、DATAOの少なくとも一方)の一部とを含んでいる。これにより、比較コードCODEの不規則性が高くなる。このため、この実施形態では、保護対象のモジュール20のセキュリティをさらに向上できる。

【0107】

図8は、別の実施形態における誤書き込み防止回路13の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路13では、図4に示した誤書き込み防止回路11にカウンタ部CTが追加され、書き込み制御部WCTL2の代わりに書き込み制御部WCTL4が設けられている。誤書き込み防止回路13のその他の構成は、図4および図5で説明した実施形態と同じである。また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路13が設けられることを除いて、図1−図3で説明した実施形態と同じである。例えば、半導体装置の最小構成は、誤書き込み防止回路13および保護対象のモジュール20である。

【0108】

誤書き込み防止回路13は、例えば、保護対象のモジュール20に対する書き込みを比較部COMPの比較結果に基づいて許可したとき、予め設定された回数の書き込みがモジュール20に対して実施されるまで、モジュール20に対する書き込みを許可する。例えば、誤書き込み防止回路13は、カウンタ部CT、比較コード生成部CG2、比較部COMP、書き込み制御部WCTL4および比較制御部CCTLを有している。

【0109】

そして、誤書き込み防止回路13は、例えば、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTS、書き込み回数信号WNUM、アドレスデコード信号DECおよびクロックCLKを受け、ライトストローブ信号WRSIを出力する。書き込み回数信号WNUMは、例えば、モジュール20に対する書き込み回数を設定するための信号であり、CPUから出力される。また、アドレスデコード信号DECは、例えば、アドレスADRのデコード結果を示す信号であり、アドレスデコーダ(例えば、図3に示したアドレスデコーダADEC)から出力される。例えば、アドレスデコード信号DECは、モジュール20内の領域を示すアドレスがバスBUSに出力されたとき、アサートされる。

【0110】

カウンタ部CTは、例えば、クロックCLK、書き込み回数信号WNUMおよびライトストローブ信号WRSIを受け、書き込み許可信号WENを書き込み制御部WCTL4に出力する。例えば、カウンタ部CTは、回数比較部NCOMP、カウント制御部CTCNおよびクロックカウンタCCTを有している。

【0111】

回数比較部NCOMPは、例えば、CPUから受けた書き込み回数信号WNUMに基づいて、モジュール20に対する書き込み回数を設定する。そして、回数比較部NCOMPは、書き込み回数信号WNUMに基づく設定回数とクロックカウンタCCTのカウント値CTNUMとを比較し、比較結果をカウント制御部CTCNに通知する。例えば、設定回数は、期待値DATAIeと比較コードCODEとの比較結果に拘わらず実施されるモジュール20への書き込み回数である。この場合、設定回数に1を加算した回数の書き込みがモジュール20に対して実施される。

【0112】

カウント制御部CTCNは、書き込み制御部WCTL4からのライトストローブ信号WRSIおよび回数比較部NCOMPの比較結果を受け、書き込み許可信号WENをクロックカウンタCCTおよび書き込み制御部WCTL4に出力する。例えば、カウント制御部CTCNは、ライトストローブ信号WRSIに応答して、書き込み許可信号WENをアサートする。そして、カウント制御部CTCNは、設定回数とクロックカウンタCCTのカウント値CTNUMとの一致を示す比較結果に応答して、書き込み許可信号WENをネゲートする。

【0113】

クロックカウンタCCTは、例えば、モジュール20に対して実施された書き込み回数を、設定回数に一致するまでカウントする。例えば、クロックカウンタCCTは、書き込み許可信号WENおよびライトストローブ信号WRSIがアサートされているとき、クロックCLKに同期して、カウントアップする。そして、クロックカウンタCCTは、例えば、設定回数とクロックカウンタCCTのカウント値CTNUMとの一致を示す比較結果に応答して、カウント値CTNUMをリセットする。例えば、クロックカウンタCCTは、書き込み許可信号WENがネゲートされたとき、カウント値CTNUMをリセットする。

【0114】

書き込み制御部WCTL4は、比較部COMPの比較結果、比較許可信号CEN、書き込み許可信号WEN、ライトストローブ信号WRSおよびアドレスデコード信号DECを受け、ライトストローブ信号WRSIを保護対象のモジュール20に出力する。例えば、書き込み制御部WCTL4は、AND回路AND3、OR回路OR2およびAND回路AND4を有している。

【0115】

AND回路AND3は、比較許可信号CENおよび比較部COMPの比較結果を受ける。そして、AND回路AND3は、比較許可信号CENおよび比較部COMPの出力信号(比較結果)の論理積結果を、OR回路OR2に出力する。なお、比較部COMPの出力信号(比較結果)は、例えば、期待値DATAIeと比較コードCODEとが一致しているとき、アサートされる。

【0116】

OR回路OR2は、書き込み許可信号WENおよびAND回路AND3の出力信号を受ける。そして、OR回路OR2は、書き込み許可信号WENおよびAND回路AND3の出力信号の論理和結果を、AND回路AND4に出力する。

【0117】

AND回路AND4は、ライトストローブ信号WRS、アドレスデコード信号DECおよびOR回路OR2の出力信号を受ける。そして、AND回路AND4は、ライトストローブ信号WRS、アドレスデコード信号DECおよびOR回路OR2の出力信号の論理積結果(ライトストローブ信号WRSI)を、比較制御部CCTL、カウンタ部CTおよび保護対象のモジュール20に出力する。

【0118】

このように、書き込み制御部WCTL4は、例えば、比較許可信号CEN、ライトストローブ信号WRSおよびアドレスデコード信号DECがアサートされ、かつ、書き込み許可信号WENがネゲートされているとき、比較部COMPの比較結果に基づいて、モジュール20に対する書き込みを許可するか否かを決定する。

【0119】

また、例えば、書き込み制御部WCTL4は、書き込み許可信号WEN、ライトストローブ信号WRSおよびアドレスデコード信号DECがアサートされているとき、比較部COMPの比較結果および比較許可信号CENの状態に拘わらず、ライトストローブ信号WRSIをアサートする。これにより、モジュール20に対する書き込みは、比較部COMPの比較結果に基づいて許可されてから、書き込み回数信号WNUMに基づく設定回数とクロックカウンタCCTのカウント値CTNUMとが一致するまで許可される。

【0120】

なお、誤書き込み防止回路13の構成は、この例に限定されない。例えば、誤書き込み防止回路13は、比較制御部CCTLが省かれてもよい。また、誤書き込み防止回路13は、例えば、比較コード生成部CG2の代わりに、比較コード生成部CG4を有してもよい。

【0121】

図9は、図8に示した誤書き込み防止回路13の動作の一例を示している。なお、図9は、保護対象のモジュール20とは別の2つのモジュール(例えば、図3に示したモジュール40、42)に対するアクセスが実施された後に、モジュール20に対する書き込み動作が実施されるときの誤書き込み防止回路13の動作の一例を示している。図9に示した動作では、モジュール20に対する書き込み動作の前に実施される2つのモジュールに対するアクセス(例えば、モジュール40、42に対するアクセス)は、図5と同じである。なお、図9に示した動作では、書き込み回数信号WNUMに基づく設定回数は、2回である。

【0122】

また、図9の例では、アドレスADRpのビット幅は4ビットであり、比較コードCODEおよび期待値DATAIeのビット幅は16ビットであり、バスBUSのデータバス幅は32ビットである。図中の“i”、“j”、“k”、“l”、“m”、“n”、“x”の意味は、図5と同じである。また、図中の“4321”、“8765”および“cba9”は、モジュール20に書き込まれる16ビットのライトデータを示している。

【0123】

期間T1−期間T6までの誤書き込み防止回路13の動作は、図5に示した期間T1−T6と同じである。なお、期間T1−期間T6では、書き込み許可信号WENがネゲートされ、カウント値CTNUMが0に維持されている。

【0124】

例えば、期間T6では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、データDATAIおよびモジュール20内の領域を示すアドレスがバスBUSに出力される。モジュール20内の領域を示すアドレスがバスBUSに出力されたため、アドレスデコード信号DECがアサートされる。

【0125】

ライトストローブ信号WRSIは、データDATAIの上位16ビット(期待値DATAIe)と比較コードCODEとが一致し、かつ、ライトストローブ信号WRSおよびアドレスデコード信号DECがアサートされているため、アサートされる。これにより、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“4321”)がモジュール20に書き込まれる。

【0126】

期間T7では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール20以外の領域を示すアドレスがバスBUSに出力される。モジュール20以外の領域を示すアドレスがバスBUSに出力されたため、アドレスデコード信号DECがネゲートされる。アドレスデコード信号DECがネゲートされるため、ライトストローブ信号WRSIは、書き込み許可信号WENおよびライトストローブ信号WRSの状態に拘わらず、ネゲートされる。これにより、モジュール20に対する書き込みが禁止される。

【0127】

また、ライトストローブ信号WRSIが期間T6にアサートされたため、期間T7において、比較許可信号CENおよび書き込み許可信号WENがそれぞれネゲートおよびアサートされ、クロックカウンタCCTのカウント動作が開始される。なお、カウント値CTNUMは、ライトストローブ信号WRSIがネゲートされているため、更新されない。また、比較コードCODEは、期間T6の書き込み動作に応答して、“jlmn”に更新されている。そして、期間T8以降では、比較コードCODEは、比較許可信号CENがネゲートされているため、“jlmn”に維持される。

【0128】

期間T8では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール20内の領域を示すアドレスがバスBUSに出力される。このため、アドレスデコード信号DECがアサートされる。ライトストローブ信号WRS、書き込み許可信号WENおよびアドレスデコード信号DECがアサートされるため、ライトストローブ信号WRSIは、比較部COMPの比較結果に拘わらず、アサートされる。これにより、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“8765”)がモジュール20に書き込まれる。

【0129】

なお、書き込み許可信号WENは、カウント値CTNUMが設定回数(2回)に到達していないため、アサート状態に維持される。書き込み許可信号WENおよびライトストローブ信号WRSIがアサートされているため、カウント値CTNUMは、期間T9において、“0”から“1”に更新される。すなわち、カウント値CTNUMは、比較部COMPの比較結果に基づく最初の書き込みがモジュール20に対して実施された後、モジュール20に対する書き込み動作が実施される度に、カウントアップする。

【0130】

期間T9では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール20以外の領域を示すアドレスがバスBUSに出力される。このため、アドレスデコード信号DECがネゲートされる。これにより、ライトストローブ信号WRSIがネゲートされる。この結果、モジュール20に対する書き込みが禁止される。このため、カウント値CTNUMは、更新されない。したがって、書き込み許可信号WENは、アサート状態に維持される。

【0131】

期間T10では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール20内の領域を示すアドレスがバスBUSに出力される。このため、アドレスデコード信号DECがアサートされる。ライトストローブ信号WRS、書き込み許可信号WENおよびアドレスデコード信号DECがアサートされるため、ライトストローブ信号WRSIは、比較部COMPの比較結果に拘わらず、アサートされる。これにより、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“cba9”)がモジュール20に書き込まれる。

【0132】

なお、書き込み許可信号WENは、カウント値CTNUMが設定回数(2回)に到達していないため、アサートされている。書き込み許可信号WENおよびライトストローブ信号WRSIがアサートされているため、カウント値CTNUMは、期間T11において、“1”から“2”に更新される。なお、カウント値CTNUMは、“2”に更新されることにより、設定回数(2回)と一致するため、“0”にリセットされる。このため、図9では、期間T11のカウント値CTNUMを“0”と記載している。

【0133】

期間T11では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール20内の領域を示すアドレスがバスBUSに出力される。このため、アドレスデコード信号DECがアサートされる。なお、書き込み許可信号WENは、カウント値CTNUMが設定回数(2回)に到達したため、ネゲートされる。

【0134】

書き込み許可信号WENがネゲートされるため、ライトストローブ信号WRSIは、ライトストローブ信号WRSおよびアドレスデコード信号DECの状態に拘わらず、ネゲートされる。これにより、モジュール20に対する書き込みが禁止される。これにより、モジュール20に対する書き込み動作が終了する。

【0135】

なお、誤書き込み防止回路13の動作は、この例に限定されない。例えば、誤書き込み防止回路13は、比較部COMPの比較結果に基づく最初の書き込みを含むモジュール20に対する書き込み回数が設定回数(図9の例では、2回)に到達したとき、モジュール20に対する書き込み動作を終了してもよい。

【0136】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、誤書き込み防止回路13は、保護対象のモジュール20に対する書き込みを比較部COMPの比較結果に基づいて許可したとき、予め設定された回数の書き込みがモジュール20に対して実施されるまで、モジュール20に対する書き込みを許可する。これにより、この実施形態では、例えば、モジュール20に対する連続する書き込み(バースト書き込み等)に容易に対応できる。また、この実施形態では、例えば、バースト書き込みのうちの最初の書き込みに対してのみ比較コード生成部CG2を動作させればよいため、比較コード生成部CG2の消費電力を低減できる。

【0137】

図10は、別の実施形態における誤書き込み防止回路14の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路14では、図4に示した比較制御部CCTLの代わりに比較制御部CCTL2が設けられている。誤書き込み防止回路14のその他の構成は、図4および図5で説明した実施形態と同じである。なお、誤書き込み防止回路14は、CPU30を有してもよい。

【0138】

また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路14が設けられることを除いて、図1−図3で説明した実施形態と同じである。なお、この実施形態の半導体装置の最小構成は、例えば、誤書き込み防止回路14、保護対象のモジュール20およびCPU30である。

【0139】

誤書き込み防止回路14は、例えば、比較コード生成部CG2、比較部COMP、書き込み制御部WCTL2および比較制御部CCTL2を有している。例えば、誤書き込み防止回路14は、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTSおよびクロックCLKを受け、比較コードCODEおよびライトストローブ信号WRSIを出力する。

【0140】

比較制御部CCTL2は、例えば、比較制御信号CNTSおよびライトストローブ信号WRSIを受け、比較許可信号CENおよびコード生成信号CGEを出力する。例えば、比較制御部CCTL2は、比較コードCODEの生成開始を示すコード比較制御信号CNTSに応答して、コード生成信号CGEをアサートし、比較コードCODEの生成終了を示すコード比較制御信号CNTSに応答して、コード生成信号CGEをネゲートする。

【0141】

また、例えば、比較制御部CCTL2は、モジュール20に対する書き込みが実施されることを示す比較制御信号CNTSに応答して、比較許可信号CENをアサートする。そして、比較制御部CCTL2は、書き込み制御部WCTL2から受けるライトストローブ信号WRSIに応答して、比較許可信号CENをネゲートする。このように、比較制御部CCTL2は、比較コード生成部CG2および書き込み制御部WCTL2の動作を制御する。

【0142】

比較コード生成部CG2の動作は、比較許可信号CENの代わりにコード生成信号CGEを受けることを除いて、図4および図5で説明した実施形態と同じである。例えば、比較コード生成部CG2は、コード生成信号CGEがアサートされているとき、読み出し動作および書き込み動作のいずれかが実施される度に、比較コードCODEを更新する。すなわち、比較コードCODEは、コード生成信号CGEがネゲートされているとき、更新されない。

【0143】

また、比較コードCODEは、例えば、CPU30および比較部COMPに出力される。例えば、CPU30は、モジュール20に対する書き込みが実施されることを示す比較制御信号CNTSを誤書き込み防止回路14に出力する前に、誤書き込み防止回路14から受けた最新の比較コードCODEを、データDATAIの上位16ビット(期待値DATAIe)に設定する。これにより、モジュール20に対する書き込みが実施されるとき、期待値DATAIeと比較コードCODEとが一致する。

【0144】

なお、誤書き込み防止回路14の構成は、この例に限定されない。例えば、誤書き込み防止回路14は、比較コード生成部CG2の代わりに、比較コード生成部CG4を有してもよい。あるいは、誤書き込み防止回路14は、例えば、比較コード生成部CG2から取得した比較コードCODEをデータDATAIの上位16ビット(期待値DATAIe)に設定する処理部(CPU30の一部の機能)を有してもよい。

【0145】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、コード比較制御信号CNTSに基づくコード生成信号CGEを用いて、期待値DATAIeを簡易に生成できる。このため、この実施形態では、誤書き込み防止回路14等の使用勝手を向上できる。

【0146】

図11は、別の実施形態における誤書き込み防止回路15の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路15は、図4に示した書き込み制御部WCTL4および比較制御部CCTLの代わりに、書き込み制御部WCTL6および比較制御部CCTL4をそれぞれ有している。誤書き込み防止回路15のその他の構成は、図4および図5で説明した実施形態と同じである。また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路15が設けられることを除いて、図1−図3で説明した実施形態と同じである。例えば、半導体装置の最小構成は、誤書き込み防止回路15および保護対象のモジュール20である。

【0147】

誤書き込み防止回路15は、例えば、比較コード生成部CG2、比較部COMP、書き込み制御部WCTL6および比較制御部CCTL4を有している。例えば、誤書き込み防止回路15は、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTSおよびクロックCLKを受け、ライトストローブ信号WRSIを出力する。

【0148】

比較制御部CCTL4は、例えば、比較制御信号CNTSおよびライトストローブ信号WRSIを受け、比較許可信号CENおよび解除信号CANCを出力する。例えば、比較制御部CCTL4は、保護を無効にするコード比較制御信号CNTSに応答して、解除信号CANCをアサートし、保護を有効にするコード比較制御信号CNTSに応答して、解除信号CANCをネゲートする。

【0149】

また、例えば、比較制御部CCTL4は、比較コードCODEの更新等を許可することを示す比較制御信号CNTSに応答して、比較許可信号CENをアサートする。そして、比較制御部CCTL4は、書き込み制御部WCTL6から受けるライトストローブ信号WRSIに応答して、比較許可信号CENをネゲートする。このように、比較制御部CCTL4は、比較コード生成部CG2および書き込み制御部WCTL6の動作を制御する。なお、比較コード生成部CG2の動作は、図4および図5で説明した実施形態と同じである。

【0150】

書き込み制御部WCTL6は、比較部COMPの比較結果、比較許可信号CEN、解除信号CANCおよびライトストローブ信号WRSを受け、ライトストローブ信号WRSIを保護対象のモジュール20に出力する。例えば、書き込み制御部WCTL6は、AND回路AND3、OR回路OR2およびAND回路AND5を有している。

【0151】

AND回路AND3は、比較許可信号CENおよび比較部COMPの比較結果を受ける。そして、AND回路AND3は、比較許可信号CENおよび比較部COMPの出力信号(比較結果)の論理積結果を、OR回路OR2に出力する。なお、比較部COMPの出力信号(比較結果)は、例えば、期待値DATAIeと比較コードCODEとが一致しているとき、アサートされる。

【0152】

OR回路OR2は、解除信号CANCおよびAND回路AND3の出力信号を受ける。そして、OR回路OR2は、解除信号CANCおよびAND回路AND3の出力信号の論理和結果を、AND回路AND5に出力する。AND回路AND5は、ライトストローブ信号WRSおよびOR回路OR2の出力信号を受ける。そして、AND回路AND5は、ライトストローブ信号WRSおよびOR回路OR2の出力信号の論理積結果(ライトストローブ信号WRSI)を、比較制御部CCTL4および保護対象のモジュール20に出力する。

【0153】

このように、書き込み制御部WCTL6は、例えば、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、解除信号CANCがネゲートされているとき、比較部COMPの比較結果に基づいて、モジュール20に対する書き込みを許可するか否かを決定する。

【0154】

また、例えば、書き込み制御部WCTL6は、解除信号CANCおよびライトストローブ信号WRSがアサートされているとき、比較部COMPの比較結果および比較許可信号CENの状態に拘わらず、ライトストローブ信号WRSIをアサートする。すなわち、書き込み制御部WCTL6は、解除信号CANCがアサートされているとき、ライトストローブ信号WRSをライトストローブ信号WRSIとして出力する。これにより、この実施形態では、例えば、モジュール20に対する書き込みを保護しなくてよいとき、解除信号CANCをアサートすることにより、期待値DATAIeの設定を省くことができる。この結果、この実施形態では、誤書き込み防止回路15等の使用勝手を向上できる。

【0155】

なお、誤書き込み防止回路15の構成は、この例に限定されない。例えば、比較制御部CCTL4は、解除信号CANCをアサートしたとき、比較許可信号CENをネゲートしてもよい。この場合、例えば、モジュール20に対する書き込みを保護しなくてよいとき、誤書き込み防止回路15の消費電力を低減できる。また、例えば、誤書き込み防止回路15は、比較コード生成部CG2の代わりに、比較コード生成部CG4を有してもよい。

【0156】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、コード比較制御信号CNTSに基づく解除信号CANCを用いて、誤書き込み防止回路15に接続されたモジュール20に対する保護を有効にするか無効にするか設定できる。このため、この実施形態では、誤書き込み防止回路15等の使用勝手を向上できる。

【0157】

図12は、別の実施形態における半導体装置102の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の半導体装置102では、図2に示した誤書き込み防止回路10およびモジュール20の代わりに誤書き込み防止回路11およびモジュール22がそれぞれ設けられ、アドレスデコーダADECがモジュール22の外部に設けられている。半導体装置102のその他の構成は、図1−図3で説明した実施形態と同じである。なお、例えば、半導体装置の最小構成は、誤書き込み防止回路11、保護対象のモジュール22およびアドレスデコーダADECである。また、モジュール22の構成は、アドレスデコーダADECが外部に設けられていることを除いて、モジュール20と同じである。なお、モジュール22は、図3に示したライトストローブ信号WRSIの代わりにライトストローブ信号WRSを受ける。

【0158】

アドレスデコーダADECは、アドレスADRをバスBUSを介して受け、アドレスデコード信号DECを誤書き込み防止回路11に出力する。誤書き込み防止回路11は、アドレスデコード信号DECIをモジュール22に出力する。すなわち、誤書き込み防止回路11は、アドレスデコード信号DECIを用いて、モジュール22に対する書き込みの許可/禁止を制御する。例えば、アドレスデコード信号DECIおよびライトストローブ信号WRSがアサートされたとき、モジュール22に対する書き込みが実施される。

【0159】

なお、半導体装置102の構成は、この例に限定されない。例えば、半導体装置102は、誤書き込み防止回路11の代わりに、誤書き込み防止回路10、12−15のいずれかを有してもよい。この場合、誤書き込み防止回路10、12−15は、アドレスデコード信号DECを受け、アドレスデコード信号DECIを出力する。

【0160】

図13は、図12に示した半導体装置102に搭載される誤書き込み防止回路11の一例を示している。誤書き込み防止回路11の書き込み制御部WCTL2は、入力信号の一部の種類および出力信号の種類を除いて、図4に示した書き込み制御部WCTL2と同じである。例えば、書き込み制御部WCTL2は、ライトストローブ信号WRSの代わりにアドレスデコード信号DECを受け、ライトストローブ信号WRSIの代わりにアドレスデコード信号DECIを出力する。

【0161】

また、誤書き込み防止回路11の比較制御部CCTLは、ライトストローブ信号WRSIの代わりにアドレスデコード信号DECIを受けることを除いて、図4に示した比較制御部CCTLと同じである。誤書き込み防止回路11のその他の構成および動作は、図4および図5で説明した実施形態と同じである。

【0162】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0163】

以上の実施形態において説明した発明を整理して、付記として開示する。

(付記1)

バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードを生成する比較コード生成部と、

前記バスに接続された保護対象のモジュールに書き込まれるデータに対応する期待値と前記比較コードとを比較する比較部と、

前記比較部の比較結果に基づいて、前記モジュールに対する書き込みを許可するか否かを決定する書き込み制御部と

を備えていることを特徴とする誤書き込み防止回路。

(付記2)

前記比較コード生成部は、前記バスに出力されたアドレスおよびデータのそれぞれの一部の値を取得し、取得した値を用いて前記比較コードを生成すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記3)

前記比較コード生成部は、前記バスに出力されたアドレスの一部の値を取得し、取得した値を用いて前記比較コードを生成すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記4)

前記比較コード生成部は、前記バスに出力されたデータの一部の値を取得し、取得した値を用いて前記比較コードを生成すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記5)

前記モジュールに対して実施された書き込みの回数をカウントするカウンタ部を有し、

前記書き込み制御部は、前記モジュールに対する書き込みを前記比較結果に基づいて許可したとき、予め設定された回数の書き込みが前記モジュールに対して実施されるまで、前記モジュールに対する書き込みを許可すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記6)

前記比較コード生成部に保持されている前記比較コードを取得し、取得した前記比較コードを前記期待値として前記比較部に出力する処理部を有し、

前記比較コード生成部は、前記期待値生成部に前記比較コードを出力した後、少なくとも前記モジュールに対して書き込みが実施されるまで、前記比較コードを更新しないこと

を特徴とする付記1記載の誤書き込み防止回路。

(付記7)

前記比較部の前記比較結果を有効にするか無効にするかを設定する比較制御部を有し、

前記書き込み制御部は、前記比較結果が無効のとき、前記モジュールに対する書き込みを前記比較結果に拘わらず許可すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記8)

前記比較コード生成部は、前記バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を順次取得し、互いに異なるタイミングで取得した値を用いて前記比較コードを生成すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記9)

前記比較コードの更新を実施するか否かを設定する比較制御部を有し、

前記書き込み制御部は、前記比較コードの更新を実施しないとき、前記モジュールに対する書き込みを前記比較結果に拘わらず禁止すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記10)

バスに接続された保護対象のモジュールと、前記モジュールへの書き込みを制御する誤書き込み防止回路とを備え、

前記誤書き込み防止回路は、

前記バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードを生成する比較コード生成部と、

前記モジュールに書き込まれるデータに対応する期待値と前記比較コードとを比較する比較部と、

前記比較部の比較結果に基づいて、前記モジュールに対する書き込みを許可するか否かを決定する書き込み制御部とを備えていること

を特徴とする半導体装置。

(付記11)

前記比較コード生成部は、前記バスに出力されたアドレスおよびデータのそれぞれの一部の値を取得し、取得した値を用いて前記比較コードを生成すること

を特徴とする付記10記載の半導体装置。

(付記12)

前記比較コード生成部は、前記バスに出力されたアドレスの一部の値を取得し、取得した値を用いて前記比較コードを生成すること

を特徴とする付記10記載の半導体装置。

(付記13)

前記比較コード生成部は、前記バスに出力されたデータの一部の値を取得し、取得した値を用いて前記比較コードを生成すること

を特徴とする付記10記載の半導体装置。

(付記14)

前記誤書き込み防止回路は、前記モジュールに対して実施された書き込みの回数をカウントするカウンタ部を有し、

前記書き込み制御部は、前記モジュールに対する書き込みを前記比較結果に基づいて許可したとき、予め設定された回数の書き込みが前記モジュールに対して実施されるまで、前記モジュールに対する書き込みを許可すること

を特徴とする付記10記載の半導体装置。

(付記15)

前記誤書き込み防止回路は、前記比較コード生成部に保持されている前記比較コードを取得し、取得した前記比較コードを前記期待値として前記比較部に出力する処理部を有し、

前記比較コード生成部は、前記期待値生成部に前記比較コードを出力した後、少なくとも前記モジュールに対して書き込みが実施されるまで、前記比較コードを更新しないこと

を特徴とする付記10記載の半導体装置。

(付記16)

前記誤書き込み防止回路は、前記比較部の前記比較結果を有効にするか無効にするかを設定する比較制御部を有し、

前記書き込み制御部は、前記比較結果が無効のとき、前記モジュールに対する書き込みを前記比較結果に拘わらず許可すること

を特徴とする付記10記載の半導体装置。

(付記17)

前記比較コード生成部は、前記バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を順次取得し、互いに異なるタイミングで取得した値を用いて前記比較コードを生成すること

を特徴とする付記10記載の半導体装置。

(付記18)

前記誤書き込み防止回路は、前記比較コードの更新を実施するか否かを設定する比較制御部を有し、

前記書き込み制御部は、前記比較コードの更新を実施しないとき、前記モジュールに対する書き込みを前記比較結果に拘わらず禁止すること

を特徴とする付記10記載の半導体装置。

【0164】

以上の詳細な説明により、実施形態の特徴点および利点は明らかになるであろう。これは、特許請求の範囲がその精神および権利範囲を逸脱しない範囲で前述のような実施形態の特徴点および利点にまで及ぶことを意図するものである。また、当該技術分野において通常の知識を有する者であれば、あらゆる改良および変更に容易に想到できるはずであり、発明性を有する実施形態の範囲を前述したものに限定する意図はなく、実施形態に開示された範囲に含まれる適当な改良物および均等物に拠ることも可能である。

【符号の説明】

【0165】

10−15‥誤書き込み防止回路;20、22、40、42‥モジュール;30‥CPU;50‥選択部;100、102‥半導体装置;ADEC‥アドレスデコーダ;ADR‥アドレス;AND1−AND5‥AND回路;BUS‥バス;CCT‥クロックカウンタ;CCTL、CCTL2、CCTL4‥比較制御部;CG、CG2、CG4‥比較コード生成部;CODE‥比較コード;COMP‥比較部;CT‥カウンタ部;CTCN‥カウント制御部;DATAI、DATAO‥データ;DATAIe‥期待値;DATAIw‥ライトデータ;FF1−FF6‥フリップフロップ回路;MUX1−MUX3‥マルチプレクサ;NCOMP‥回数比較部;OR1、OR2‥OR回路;SEL‥セレクタ;WCTL、WCTL2、WCTL4、WCTL6‥書き込み制御部

【技術分野】

【0001】

本発明は、誤書き込み防止回路および半導体装置に関する。

【背景技術】

【0002】

マイクロコントローラ等の半導体装置では、保護対象のモジュール(例えば、レジスタ)に対する誤書き込みを防止するための対策が施されている。この種の半導体装置は、例えば、保護対象のモジュールにライトデータを書き込む際に、所定のシーケンスを実施することにより、誤書き込みを防止する。例えば、“00”、“01”、“10”、“11”、“ライトデータ”の順に保護対象のモジュールにアクセスするシーケンスが実施されたときのみ、ライトデータが保護対象のモジュールに書き込まれる。この場合、ライトデータを書き込む前に、4回(“00”、“01”、“10”、“11”)の書き込み動作(所定のシーケンス)が実施される。一般的に、所定のシーケンスで実施される書き込み動作等の回数の増加に伴い、保護対象のモジュールのセキュリティは、向上する。

【0003】

また、保護対象のレジスタ毎に設定されたマスターキーコードを用いて誤書き込みを防止するマイクロコントローラが提案されている(例えば、特許文献1)。この種のマイクロコントローラは、例えば、マスターキーコードを記憶する記憶部を有し、マスターキーコードと一致する入力キーコードを受けたときに、保護対象のレジスタに対する書き込みを許可する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−204387号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ライトデータを書き込む前に所定のシーケンスを実施する構成では、保護対象のモジュールにライトデータを書き込む際に、所定のシーケンスを実施する時間を別途設ける必要がある。例えば、上述したシーケンスでは、保護対象のモジュールへの1回の書き込みに対して、4回の書き込みをするための余計な時間が必要である。このため、保護対象のモジュールに対する書き込み時間は増加する。

【0006】

本発明の目的は、書き込み時間の増加を抑制しつつ、保護対象のモジュールに対する誤書き込みを防止することである。

【課題を解決するための手段】

【0007】

本発明の一形態では、誤書き込み防止回路は、バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードを生成する比較コード生成部と、バスに接続された保護対象のモジュールに書き込まれるデータに対応する期待値と比較コードとを比較する比較部と、比較部の比較結果に基づいて、モジュールに対する書き込みを許可するか否かを決定する書き込み制御部とを有している。

【発明の効果】

【0008】

書き込み時間の増加を抑制しつつ、保護対象のモジュールに対する誤書き込みを防止できる。

【図面の簡単な説明】

【0009】

【図1】一実施形態における誤書き込み防止回路の例を示している。

【図2】図1に示した保護対象のモジュールにライトデータを書き込む際のデータ構成の一例を示している。

【図3】図1に示した誤書き込み防止回路が搭載される半導体装置の一例を示している。

【図4】別の実施形態における誤書き込み防止回路の一例を示している。

【図5】図4に示した誤書き込み防止回路の動作の一例を示している。

【図6】別の実施形態における誤書き込み防止回路の一例を示している。

【図7】図6に示した誤書き込み防止回路の動作の一例を示している。

【図8】別の実施形態における誤書き込み防止回路の一例を示している。

【図9】図8に示した誤書き込み防止回路の動作の一例を示している。

【図10】別の実施形態における誤書き込み防止回路の一例を示している。

【図11】別の実施形態における誤書き込み防止回路の一例を示している。

【図12】別の実施形態における半導体装置の一例を示している。

【図13】図12に示した半導体装置に搭載される誤書き込み防止回路の一例を示している。

【発明を実施するための形態】

【0010】

以下、実施形態を図面を用いて説明する。

【0011】

図1は、一実施形態における誤書き込み防止回路10の例を示している。誤書き込み防止回路10は、例えば、保護対象のモジュール20に対する書き込みを制御する。保護対象のモジュール20は、例えば、バスBUSに接続されたレジスタであり、I/O設定等の重要な情報を記憶する。なお、保護対象のモジュール20は、レジスタに限定されない。例えば、保護対象のモジュール20は、レジスタ以外のメモリでもよい。誤書き込み防止回路10はおよびモジュール20は、半導体装置の少なくとも一部を構成する。

【0012】

誤書き込み防止回路10は、例えば、バスBUSに接続された比較コード生成部CGと、バスBUSに接続された比較部COMPと、書き込み制御部WCTLとを有している。バスBUSには、例えば、データDATAI、アドレスADR、ライトストローブ信号WRSおよびリードストローブ信号RDS等が出力される。なお、データDATAIは、書き込み動作時にバスBUSに出力されるデータである。読み出し動作時には、例えば、図3に示すように、データDATAO(以下、リードデータとも称する)がバスBUSに出力される。

【0013】

比較コード生成部CGは、例えば、アドレスADRp、ライトストローブ信号WRSおよびリードストローブ信号RDSを受け、比較コードCODEを比較部COMPに出力する。なお、アドレスADRpは、書き込み動作時および読み出し動作時のいずれかにバスBUSに出力されるアドレスADRの一部(例えば、下位4ビット)である。

【0014】

例えば、比較コード生成部CGは、ライトストローブ信号WRSに基づく書き込みタイミングおよびリードストローブ信号RDSに基づく読み出しタイミングに同期して、バスBUSに出力されたアドレスADRp(アドレスADRの一部)の値を取得する。そして、比較コード生成部CGは、例えば、取得したアドレスADRpの値を用いて比較コードCODEを生成する。

【0015】

このように、比較コード生成部CGは、保護対象のモジュール20に対する書き込みが実施される前に、バスBUS上の情報(例えば、バスBUSに出力されたアドレスADRpの値)を用いて比較コードCODEを生成する。したがって、この実施形態では、保護対象のモジュール20内に固定の比較コードを設けなくともよい。このため、誤書き込み防止回路10は、誤書き込み対策の無い既存のモジュールに対しても、誤書き込みを防止できる。

【0016】

さらに、バスBUS上の情報を用いて比較コードCODEが生成されるため、比較コードCODEは、固定されない。このため、この実施形態では、期待値DATAIeと固定された比較コードCODEとを比較する構成に比べて、保護対象のモジュール20のセキュリティを向上できる。

【0017】

なお、比較コード生成部CGは、互いに異なるタイミングで取得した複数のアドレスADRpの値を用いて比較コードCODEを生成してもよいし、1つのアドレスADRpの値を用いて比較コードCODEを生成してもよい。例えば、互いに異なるタイミングで取得した複数のアドレスADRpの値を用いて比較コードCODEを生成したときには、比較コードCODEに時系列の要素が含まれるため、保護対象のモジュール20のセキュリティは、向上する。

【0018】

比較部COMPは、保護対象のモジュール20に書き込まれるライトデータ(例えば、図2に示すライトデータDATAIw)に対応する期待値DATAIeと比較コードCODEとを比較する。例えば、期待値DATAIeと比較コードCODEとの比較は、特別なシーケンス(ライトデータを書き込む前の比較用の書き込み動作等)のための時間を別途設けることなく、常に実施される。そして、比較部COMPは、比較結果を書き込み制御部WCTLに通知する。例えば、比較部COMPの出力信号(比較結果)は、期待値DATAIeと比較コードCODEとが一致しているとき、アサートされる。

【0019】

書き込み制御部WCTLは、ライトストローブ信号WRSおよび比較部COMPの比較結果を受け、モジュール20用のライトストローブ信号WRSIをモジュール20に出力する。例えば、書き込み制御部WCTLは、期待値DATAIeと比較コードCODEとが一致しているとき、ライトストローブ信号WRSのアサートに応答して、ライトストローブ信号WRSIをアサートする。これにより、モジュール20に対する書き込みは、許可される。

【0020】

また、例えば、書き込み制御部WCTLは、期待値DATAIeと比較コードCODEとが不一致のとき、ライトストローブ信号WRSの状態に拘わらず、ライトストローブ信号WRSIをネゲートする。これにより、モジュール20に対する書き込みは、禁止される。すなわち、書き込み制御部WCTLは、比較部COMPの比較結果に基づいて、モジュール20に対する書き込みを許可するか否かを決定する。

【0021】

なお、誤書き込み防止回路10の構成は、この例に限定されない。例えば、誤書き込み防止回路10は、期待値DATAIeと比較コードCODEとの比較を実施するか否かをCPU30等により制御されてもよい。この場合、期待値DATAIeと比較コードCODEとの比較が許可されている期間、期待値DATAIeと比較コードCODEとの比較が常に実施される。

【0022】

また、例えば、比較コード生成部CGは、バスBUSに出力されたデータ(データDATAIや図3に示すデータDATAO)の一部の値を取得し、取得した値を用いて比較コードCODEを生成してもよい。あるいは、比較コード生成部CGは、バスBUSに出力されたアドレスADRおよびデータのそれぞれの一部の値を取得し、取得した値を用いて比較コードCODEを生成してもよい。すなわち、比較コード生成部CGは、バスBUSに出力されたアドレスADRおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードCODEを生成する。

【0023】

図2は、図1に示した保護対象のモジュール20にライトデータを書き込む際のデータ構成の一例を示している。なお、図2は、バスBUSのデータバスのバス幅が32ビットで、モジュール20のデータバス幅が16ビットのときのデータDATAIの一例を示している。

【0024】

例えば、データDATAIは、下位16ビット(0ビット−15ビット)がモジュール20に書き込まれるライトデータDATAIwに割り当てられ、上位16ビット(16ビット−31ビット)が期待値DATAIeに割り当てられる。この場合、保護対象のモジュール20への1回の書き込みに対して、データDATAIが1回出力されればよい。期待値DATAIeとライトデータDATAIwとが一緒に出力されるため、書き込み時間の増加が抑制される。例えば、データDATAIの下位16ビット(ライトデータDATAIw)は、データDATAIの上位16ビット(期待値DATAIe)が比較コードCODEと一致したとき、モジュール20に書き込まれる。なお、モジュール20では、例えば、データDATAIの上位16ビット(期待値DATAIe)は破棄される。

【0025】

ここで、モジュール20のデータバス幅(例えば、32ビット)がバスBUSのデータバスのバス幅と一致しているときには、保護対象のモジュール20への1回の書き込みに対して、データDATAIが2回出力される。この場合、16ビットの期待値DATAIeおよび16ビットのライトデータDATAIwを含むデータDATAIが2回出力されてもよいし、16ビットの期待値DATAIeを含むデータDATAIと32ビットのライトデータDATAIwを含むデータDATAIとが順次出力されてもよい。

【0026】

すなわち、モジュール20のデータバス幅がバスBUSのデータバスのバス幅と一致している構成では、2回の書き込み動作により、モジュール20にライトデータIDATAIwを書き込むことができる。したがって、モジュール20のデータバス幅がバスBUSのデータバスのバス幅と一致している構成においても、例えば、モジュール20にライトデータIDATAIwを書き込む前に複数回の書き込み動作(所定のシーケンス)を実施する構成に比べて、書き込み時間を短くできる。すなわち、モジュール20のデータバス幅がバスBUSのデータバスのバス幅と一致している構成においても、書き込み時間の増加を抑制しつつ、保護対象のモジュール20に対する誤書き込みを防止できる。

【0027】

なお、データDATAIに対する期待値DATAIeの割り当ては、この例に限定されない。例えば、期待値DATAIeのデータ幅は、保護対象のモジュール20のセキュリティレベルやバスBUS構成等に応じて決定される。

【0028】

図3は、図1に示した誤書き込み防止回路10が搭載される半導体装置100の一例を示している。半導体装置100は、例えば、誤書き込み防止回路10、保護対象のモジュール20、CPU30、保護対象以外のモジュール40、42および選択部50を有している。誤書き込み防止回路10、モジュール20、40、42、CPU30および選択部50は、バスBUSに接続されている。なお、半導体装置100の最小構成は、誤書き込み防止回路10および保護対象のモジュール20である。

【0029】

誤書き込み防止回路10は、例えば、データDATAIに含まれる期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRSおよびリードストローブ信号RDSを、バスBUSを介して受け、ライトストローブ信号WRSIをモジュール20に出力する。例えば、誤書き込み防止回路10は、保護対象のモジュール20に対する書き込みが実施される前に、ジュール20、40、42に対する書き込み動作や読み出し動作が実施される度に、アドレスADRpを取得する。そして、誤書き込み防止回路10は、例えば、互いに異なるタイミングで取得した複数のアドレスADRpの値を用いて比較コードCODEを生成する。

【0030】

モジュール20は、例えば、データバス幅が16ビットのレジスタであり、アドレスADRをデコードするアドレスデコーダADECを有している。なお、アドレスデコーダADECは、モジュール20の外部に設けられてもよい。モジュール20は、例えば、データDATAI、アドレスADRおよびリードストローブ信号RDSを、バスBUSを介して受ける。さらに、モジュール20は、ライトストローブ信号WRSIを誤書き込み防止回路10から受ける。

【0031】

例えば、書き込み動作時には、ライトストローブ信号WRSIおよびアドレスADRに基づいて、データDATAI(より詳細には、図2に示したライトデータDATAIw)がモジュール20に書き込まれる。また、読み出し動作時には、リードストローブ信号RDSおよびアドレスADRに基づいて、モジュール20からデータDATAOが出力される。

【0032】

CPU30は、例えば、半導体装置100の動作を制御する。例えば、CPU30は、モジュール20、40、42に対する書き込み動作や読み出し動作を制御する。なお、CPU30は、誤書き込み防止回路10の動作を制御してもよい。例えば、CPU30は、期待値DATAIeと比較コードCODEとの比較を実施するか否かを制御してもよい。すなわち、誤書き込み防止回路10は、期待値DATAIeと比較コードCODEとの比較を実施するか否かをCPU30等により制御されてもよい。

【0033】

モジュール40、42は、例えば、データバス幅が32ビットのレジスタである。例えば、ジュール40、42は、データDATAI、アドレスADR、ライトストローブ信号WRSおよびリードストローブ信号RDSを、バスBUSを介して受ける。また、例えば、モジュール40、42は、データDATAOを、選択部50を介してバスBUSに出力する。

【0034】

例えば、書き込み動作時には、ライトストローブ信号WRSおよびアドレスADRに基づいて、データDATAIがモジュール40、42に書き込まれる。また、読み出し動作時には、リードストローブ信号RDSおよびアドレスADRに基づいて、モジュール40、42からデータDATAOが出力される。

【0035】

選択部50は、モジュール20、40、42からデータDATAOを受け、有効なデータDATAOをバスBUSに出力する。例えば、選択部50からバスBUSに出力されるデータDATAOは、リードストローブ信号RDSおよびアドレスADRに基づいてモジュール20、40、42のいずれかから読み出されたデータDATAOである。

【0036】

以上、この実施形態では、誤書き込み防止回路10は、比較コードCODEと期待値DATAIeとの比較結果に基づいて、保護対象のモジュール20に対する書き込みを許可するか否かを決定する。また、この実施形態では、例えば、特別なシーケンス動作の書き込み時間を設けることなく、比較コードCODEと期待値DATAIeとの比較が実施される。したがって、この実施形態では、特別なシーケンス動作の書き込み時間等の余計な時間を省くことができ、書き込み時間の増加を抑制できる。この結果、この実施形態では、書き込み時間の増加を抑制しつつ、保護対象のモジュール20に対する誤書き込みを防止できる。また、この実施形態では、比較コードCODEが可変であるため、比較コードCODEを変更する頻度を調整することにより、システム上でのセキュリティレベルを調整することができる。

【0037】

図4は、別の実施形態における誤書き込み防止回路11の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路11では、図1に示した誤書き込み防止回路10に比較制御部CCTLが追加され、比較コード生成部CGおよび書き込み制御部WCTLの代わりに比較コード生成部CG2および書き込み制御部WCTL2がそれぞれ設けられている。誤書き込み防止回路11のその他の構成は、上述した実施形態と同じである。また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路11が設けられることを除いて、上述した実施形態と同じである。例えば、半導体装置の最小構成は、誤書き込み防止回路11および保護対象のモジュール20である。

【0038】

誤書き込み防止回路11は、例えば、比較コード生成部CG2、比較部COMP、書き込み制御部WCTL2および比較制御部CCTLを有している。例えば、誤書き込み防止回路11は、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTSおよびクロックCLKを受け、ライトストローブ信号WRSIを出力する。比較制御信号CNTSは、例えば、比較コード生成部CG2および書き込み制御部WCTL2に対する比較許可信号CENをアサートするための信号であり、CPUから出力される。

【0039】

比較制御部CCTLは、例えば、比較制御信号CNTSおよびライトストローブ信号WRSIを受け、比較許可信号CENを比較コード生成部CG2のAND回路AND1および書き込み制御部WCTL2のAND回路AND2に出力する。例えば、比較制御部CCTLは、CPUから受ける比較制御信号CNTSに応答して、比較許可信号CENをアサートし、書き込み制御部WCTL2から受けるライトストローブ信号WRSIに応答して、比較許可信号CENをネゲートする。これにより、比較制御部CCTLは、比較コード生成部CG2および書き込み制御部WCTL2の動作を制御する。

【0040】

比較コード生成部CG2は、例えば、アドレスADRp、ライトストローブ信号WRS、リードストローブ信号RDS、比較許可信号CENおよびクロックCLKを受け、比較コードCODEを比較部COMPに出力する。例えば、比較コード生成部CG2は、OR回路OR1、AND回路AND1、フリップフロップ回路FF1、FF2、FF3、FF4およびマルチプレクサMUX1を有している。

【0041】

OR回路OR1は、ライトストローブ信号WRSおよびリードストローブ信号RDSを受け、ライトストローブ信号WRSとリードストローブ信号RDSとの論理和結果をAND回路AND1に出力する。AND回路AND1は、OR回路OR1の出力信号と比較許可信号CENとの論理積結果を、各フリップフロップ回路FF(FF1−FF4)のイネーブル端子ENに出力する。すなわち、各フリップフロップ回路FFのイネーブル端子ENが受けるイネーブル信号は、ライトストローブ信号WRSおよびリードストローブ信号RDSのいずれかと比較許可信号CENとがアサートされているときに、アサートされる。

【0042】

各フリップフロップ回路FFは、例えば、イネーブル端子ENで受けるイネーブル信号がアサートされているとき、端子CKで受けるクロックCLKが立ち上がる度に、入力端子Dで受けた信号を取り込み、保持する。例えば、フリップフロップ回路FF1、FF2、FF3の出力端子Qは、フリップフロップ回路FF2、FF3、FF4の入力端子Dにそれぞれ接続されている。すなわち、フリップフロップ回路FF1−FF4は、クロックCLKに同期して動作するシフトレジスタとして機能する。

【0043】

例えば、フリップフロップ回路FF1は、クロックCLKが立ち上がる度に、バスBUSに出力されているアドレスADRの一部(アドレスADRp)の値を取り込み、保持する。また、フリップフロップ回路FF2、FF3、FF4は、クロックCLKが立ち上がる度に、フリップフロップ回路FF1、FF2、FF3にそれぞれ保持されているアドレスADRpの値を取り込み、保持する。なお、フリップフロップ回路FF4に保持されているアドレスADRpの値は、例えば、クロックCLKが立ち上がる度に、破棄される。

【0044】

すなわち、各フリップフロップ回路FFが保持しているアドレスADRpの値は、例えば、クロックCLKが立ち上がる度に、更新される。なお、任意のモジュールに対する読み出し動作および書き込み動作のいずれも実施されないアイドルサイクルでは、ライトストローブ信号WRSおよびリードストローブ信号RDSのいずれもネゲートされているため、各フリップフロップ回路FFのイネーブル信号は、ネゲートされる。したがって、アイドルサイクルでは、フリップフロップ回路FF1−FF4がそれぞれ保持しているアドレスADRpの値(信号CODEa、CODEb、CODEc、CODEd)は、維持される。

【0045】

また、各フリップフロップ回路FF(FF1−FF4)の出力端子Qは、マルチプレクサMUX1の入力部に接続される。すなわち、フリップフロップ回路FF1−FF4がそれぞれ保持しているアドレスADRpの値(信号CODEa、CODEb、CODEc、CODEd)は、マルチプレクサMUX1に入力される。

【0046】

マルチプレクサMUX1は、例えば、並列直列変換回路として動作し、フリップフロップ回路FF1−FF4から受けた4つの信号CODEa、CODEb、CODEc、CODEdを1つの比較コードCODEとして比較部COMPに出力する。例えば、マルチプレクサMUX1は、アドレスADRpのビット幅が4ビットのとき、信号CODEa、CODEb、CODEc、CODEdを、比較コードCODEの0ビット−3ビット、4ビット−7ビット、8ビット−11ビット、12ビット−15ビットにそれぞれ割り当てる。

【0047】

すなわち、比較コードCODEは、互いに異なるタイミングで取得した4つのアドレスADRpの値を用いて生成される。例えば、比較コードCODEを構成する信号CODEa、CODEb、CODEc、CODEdでは、信号CODEaは、最後に取得したアドレスADRpの値であり、信号CODEbは、3番目に取得したアドレスADRpの値であり、信号CODEcは、2番目に取得したアドレスADRpの値であり、信号CODEdは、最初に取得したアドレスADRpの値である。このように、比較コードCODEは、時系列の要素を含む。

【0048】

比較部COMPは、期待値DATAIeと比較コードCODEとを比較し、比較結果を書き込み制御部WCTLに通知する。このように、この実施形態では、時系列の要素を含む比較コードCODEと期待値DATAIeとを比較するため、時系列の要素を含まない比較コードCODEを用いうる構成に比べて、保護対象のモジュール20のセキュリティを向上できる。

【0049】

なお、この実施形態では、例えば、書き込み動作や読み出し動作が実施される度にアドレスADRpが順次取得されるため、時系列の要素を含む比較コードCODEを生成するための時間を別途設けなくともよい。したがって、この実施形態では、書き込み時間の増加を抑制しつつ、保護対象のモジュール20のセキュリティを向上できる。すなわち、この実施形態では、書き込み時間の増加を抑制しつつ、保護対象のモジュール20に対する誤書き込みを防止できる。

【0050】

書き込み制御部WCTL2は、例えば、ライトストローブ信号WRS、比較許可信号CENおよび比較部COMPの比較結果を受け、ライトストローブ信号WRSIを比較制御部CCTLおよび保護対象のモジュール20に出力する。比較部COMPの出力信号(比較結果)は、例えば、期待値DATAIeと比較コードCODEとが一致しているとき、アサートされる。

【0051】

例えば、書き込み制御部WCTL2は、ライトストローブ信号WRS、比較許可信号CENおよび比較部COMPの比較結果を受けるAND回路AND2を有している。AND回路AND2は、ライトストローブ信号WRS、比較許可信号CENおよび比較部COMPの出力信号(比較結果)の論理積結果(ライトストローブ信号WRSI)を、比較制御部CCTLおよび保護対象のモジュール20に出力する。

【0052】

したがって、書き込み制御部WCTL2は、比較許可信号CENがアサートされているとき、比較部COMPの比較結果に基づいて、モジュール20に対する書き込みを許可するか否かを決定する。すなわち、比較許可信号CENがアサートされているときの書き込み制御部WCTL2の動作は、上述した実施形態の書き込み制御部WCTLと同じである。

【0053】

例えば、書き込み制御部WCTL2は、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、期待値DATAIeと比較コードCODEとが一致しているとき、ライトストローブ信号WRSIをアサートする。これにより、モジュール20に対する書き込みは、許可される。また、例えば、書き込み制御部WCTL2は、期待値DATAIeと比較コードCODEとが不一致のとき、ライトストローブ信号WRSおよび比較許可信号CENの状態に拘わらず、ライトストローブ信号WRSIをネゲートする。これにより、モジュール20に対する書き込みは、禁止される。

【0054】

なお、書き込み制御部WCTL2は、例えば、比較許可信号CENがネゲートされているときには、比較部COMPの比較結果およびライトストローブ信号WRSの状態に拘わらず、ライトストローブ信号WRSIをネゲートする。すなわち、書き込み制御部WCTL2は、比較許可信号CENがネゲートされているときには、モジュール20に対する書き込みを禁止する。このように、この実施形態では、比較許可信号CENをネゲートすることにより、モジュール20に対する書き込みを禁止できるため、モジュール20のセキュリティをさらに向上できる。

【0055】

なお、誤書き込み防止回路11の構成は、この例に限定されない。例えば、誤書き込み防止回路11は、比較制御部CCTLが省かれてもよい。また、例えば、シフトレジスタを構成するフリップフロップ回路FFの数は、2つでもよいし、3つでもよい。あるいは、シフトレジスタを構成するフリップフロップ回路FFの数は、5つ以上でもよい。

【0056】

図5は、図4に示した誤書き込み防止回路11の動作の一例を示している。なお、図5は、保護対象のモジュール20とは別の2つのモジュール(例えば、図3に示したモジュール40、42)に対するアクセスが実施された後に、モジュール20に対する書き込み動作が実施されるときの誤書き込み防止回路11の動作の一例を示している。図5では、モジュール20とは別の2つのモジュールを、図3に示したモジュール40およびモジュール42として説明する。例えば、図5に示した動作では、モジュール40に対する書き込み動作および読み出し動作、アイドルサイクル、モジュール42に対する書き込み動作および読み出し動作、モジュール20に対する書き込み動作が順番に実施される。

【0057】

また、図5の例では、比較コード生成部CG2により取り込まれるアドレスADRpのビット幅は4ビットであり、比較コードCODEおよび期待値DATAIeのビット幅は16ビットであり、バスBUSのデータバス幅は32ビットである。図中の“i”、“j”、“k”、“l”、“m”、“n”、“x”は、4ビットで示される任意の値を示している。なお、この動作の説明においては、図中の“x”は、特に意味のない値である。また、図中の“4321”は、モジュール20に書き込まれる16ビットのライトデータを示している。

【0058】

先ず、CPUの制御信号(図4に示した比較制御信号CNTS)に応答して、比較許可信号CENがアサートされる。これにより、比較コードCODEは、例えば、読み出し動作および書き込み動作のいずれかが実施される度に、更新される。

【0059】

期間T1では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール40内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール40に対する書き込み動作が実施される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“i”である。したがって、期間T2において、比較コードCODEは、“xxxi”に更新される。

【0060】

期間T2では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール40内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール40に対する読み出し動作が実施される。なお、バスBUSに出力されたアドレス(読み出し対象のアドレス)の下位4ビット(アドレスADRp)は、“j”である。したがって、期間T3において、比較コードCODEは、“xxij”に更新される。

【0061】

期間T3では、ライトストローブ信号WRSおよびリードストローブ信号RDSがネゲートされ、任意のアドレスがバスBUSに出力される。すなわち、期間T3は、アイドルサイクルである。なお、バスBUSに出力されたアドレスの下位4ビット(アドレスADRp)は、“k”である。期間T3がアイドルサイクルであるため、期間T4において、比較コードCODEは、更新されない。すなわち、比較コードCODEは、“xxij”に維持される。

【0062】

期間T4では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール42内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール42に対する書き込み動作が実施される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“l”である。したがって、期間T5において、比較コードCODEは、“xijl”に更新される。

【0063】

期間T5では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール42内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール42に対する読み出し動作が実施される。なお、バスBUSに出力されたアドレス(読み出し対象のアドレス)の下位4ビット(アドレスADRp)は、“m”である。したがって、期間T6において、比較コードCODEは、“ijlm”に更新される。これにより、保護対象のモジュール20に対する書き込み動作時に参照される比較コードCODEが生成される。

【0064】

この例では、比較コードCODEは、期間T1、T2、T4、T5のアドレス(モジュール20に対する書き込み動作の前に実施された4回のアクセスのアドレス)の情報を含んでいる。すなわち、比較コードCODEは、互いに異なるタイミングで取得した複数のアドレスADRpの値を用いて生成され、時系列の要素を含む。

【0065】

期間T6では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、データDATAIおよびモジュール20内の領域を示すアドレスがバスBUSに出力される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“n”である。また、バスBUSに出力されたDATAIは、モジュール20に対する書き込みを実施するためのデータである。例えば、データDATAIの上位16ビット(期待値DATAIe)は、“ijlm”であり、データDATAIの下位16ビット(ライトデータDATAIw)は、“4321”である。

【0066】

このように、期間T6では、データDATAIの上位16ビット(期待値DATAIe)および比較コードCODEは、共に“ijlm”であり、互いに一致している。すなわち、期間T6では、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、期待値DATAIeと比較コードCODEとが一致している。このため、ライトストローブ信号WRSIがアサートされる。なお、期間T1−T5以外では、期待値DATAIeと比較コードCODEとが不一致のため、ライトストローブ信号WRSIはネゲートされている。

【0067】

ライトストローブ信号WRSIがアサートされたため、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“4321”)がモジュール20に書き込まれる。このように、この実施形態では、保護対象のモジュール20に対する書き込み動作が実施される前に、比較コードCODEに用いられるアドレスADRp(“i”、“j”、“l”、“m”)が取得される。そして、例えば、期待値DATAIeと比較コードCODEとが不一致のときには、ライトストローブ信号WRSIがネゲートされるため、モジュール20に対する書き込みは、禁止される。これにより、この実施形態では、モジュール20に対する誤書き込みを防止できる。

【0068】

ここで、例えば、モジュール20を使用する正規のプログラマは、モジュール20に対する書き込み動作の前に実施されるアクセスを認識している。したがって、プログラマは、モジュール20にライトデータを書き込む際の期待値DATAIeとして、“ijlm”をデータDATAIの上位16ビットに設定できる。換言すれば、不正な使用者は、モジュール20にライトデータを書き込む際の期待値DATAIeとして、“ijlm”をデータDATAIの上位16ビットに設定することが困難である。

【0069】

したがって、この実施形態では、モジュール20のデータが不正に書き換えられることを防止できる。また、この実施形態では、時系列の要素が比較コードCODEに含まれるため、比較コードCODEと期待値DATAIeとが誤動作等により偶然一致することを低減できる。したがって、この実施形態では、保護対象のモジュール20のセキュリティを向上できる。

【0070】

期間T7では、ライトストローブ信号WRSおよびリードストローブ信号RDSがネゲートされる。また、ライトストローブ信号WRSIが期間T6にアサートされたため、期間T7において、比較許可信号CENがネゲートされる。例えば、比較制御部CCTLは、ライトストローブ信号WRSIのアサートに応答して、比較許可信号CENをネゲートする。これにより、モジュール20に対する書き込み動作が終了する。なお、期間T7では、比較コードCODEは、“jlmn”に更新されている。そして、期間T8では、期間T7がアイドルサイクルであるため、比較コードCODEは、“jlmn”に維持される。

【0071】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、時系列の要素を含む比較コードCODEと期待値DATAIeとが一致したときに、保護対象のモジュール20に対する書き込みが許可される。これにより、この実施形態では、保護対象のモジュール20のセキュリティをさらに向上できる。また、この実施形態では、例えば、比較コードCODEに用いられるアドレスADRpは、モジュール40等に対する通常のアクセスが実施されたとき(期間T1、T2、T4、T5)、取得される。したがって、この実施形態では、比較コードCODEに時系列の要素を含めるための時間を別途設けなくともよい。

【0072】

すなわち、この実施形態では、モジュール20に対する誤書き込みを防止するために、特別なシーケンス(ライトデータを書き込む前の比較用の書き込み動作等)を実施するための時間を別途設けなくともよい。これにより、この実施形態では、書き込み時間の増加を抑制しつつ、モジュール20のセキュリティを向上できる。すなわち、この実施形態では、書き込み時間の増加を抑制しつつ、保護対象のモジュール20に対する誤書き込みを防止できる。

【0073】

図6は、別の実施形態における誤書き込み防止回路12の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路12は、図4に示した比較コード生成部CG2の代わりに、比較コード生成部CG4を有している。誤書き込み防止回路12のその他の構成は、図4および図5で説明した実施形態と同じである。また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路12が設けられることを除いて、図1−図3で説明した実施形態と同じである。例えば、半導体装置の最小構成は、誤書き込み防止回路12および保護対象のモジュール20である。

【0074】

誤書き込み防止回路12は、例えば、比較コード生成部CG4、比較部COMP、書き込み制御部WCTL2および比較制御部CCTLを有している。例えば、誤書き込み防止回路12は、データDATAIp、DATAOp、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTSおよびクロックCLKを受け、ライトストローブ信号WRSIを出力する。なお、データDATAIpは、書き込み動作時にバスBUSに出力されるデータDATAIの一部(例えば、下位4ビット)である。また、データDATAOpは、読み出し動作時にバスBUSに出力されるデータDATAOの一部(例えば、下位4ビット)である。

【0075】

比較コード生成部CG4は、例えば、データDATAIp、DATAOp、アドレスADRp、ライトストローブ信号WRS、リードストローブ信号RDS、比較許可信号CENおよびクロックCLKを受け、比較コードCODEを比較部COMPに出力する。例えば、比較コード生成部CG4は、データDATAIpの値およびアドレスADRpの値を書き込み動作時に取得し、データDATAOpの値およびアドレスADRpの値を読み出し動作時に取得する。そして、比較コード生成部CG4は、例えば、取得した値(アドレスADRp等の値)を用いて比較コードCODEを生成する。

【0076】

例えば、比較コード生成部CG4は、OR回路OR1、AND回路AND1、セレクタSEL、マルチプレクサMUX2、MUX3、フリップフロップ回路FF5、FF6を有している。

【0077】

OR回路OR1は、ライトストローブ信号WRSとリードストローブ信号RDSとの論理和結果をAND回路AND1に出力する。AND回路AND1は、OR回路OR1の出力信号と比較許可信号CENとの論理積結果を、フリップフロップ回路FF5、FF6のイネーブル端子ENに出力する。すなわち、フリップフロップ回路FF5、FF6のイネーブル端子ENが受けるイネーブル信号は、ライトストローブ信号WRSおよびリードストローブ信号RDSのいずれかと比較許可信号CENとがアサートされているときに、アサートされる。

【0078】

セレクタSELは、データDATAIp、DATAOpおよびライトストローブ信号WRSを受け、データDATAIp、DATAOpのいずれかをマルチプレクサMUX2に出力する。例えば、セレクタSELは、ライトストローブ信号WRSがアサートされているとき、データDATAIpをマルチプレクサMUX2に出力し、ライトストローブ信号WRSがネゲートされているとき、データDATAOpをマルチプレクサMUX2に出力する。

【0079】

なお、セレクタSELは、ライトストローブ信号WRSの代わりに、リードストローブ信号RDSを受けてもよい。すなわち、セレクタSELは、書き込み動作時に、データDATAIpをマルチプレクサMUX2に出力し、かつ、読み出し動作時に、データDATAOpをマルチプレクサMUX2に出力するように構成されればよい。

【0080】

マルチプレクサMUX2は、例えば、並列直列変換回路として動作し、2つの信号を1つの信号に変換して、フリップフロップ回路FF5の入力端子Dに出力する。例えば、データDATAIp、DATAOpおよびアドレスADRpのビット幅が4ビットのとき、マルチプレクサMUX2は、セレクタSELから受けた4ビットのデータ(データDATAIp、DATAOpのいずれか)とバスBUSに出力されているアドレスADRp(アドレスADRの一部)とを合わせた8ビットのデータを、フリップフロップ回路FF5の入力端子Dに出力する。

【0081】

フリップフロップ回路FF5、FF6は、例えば、イネーブル端子ENで受けるイネーブル信号がアサートされているとき、端子CKで受けるクロックCLKが立ち上がる度に、入力端子Dで受けた信号を取り込み、保持する。例えば、フリップフロップ回路FF5の出力端子Qは、フリップフロップ回路FF6の入力端子Dに接続されている。すなわち、フリップフロップ回路FF5、FF6は、クロックCLKに同期して動作するシフトレジスタとして機能する。

【0082】

例えば、フリップフロップ回路FF5は、クロックCLKが立ち上がる度に、マルチプレクサMUX2から受けた信号(データDATAIp、DATAOpのいずれかとアドレスADRp)の値を取り込み、保持する。また、フリップフロップ回路FF6は、クロックCLKが立ち上がる度に、フリップフロップ回路FF5に保持されている信号の値を取り込み、保持する。なお、フリップフロップ回路FF6に保持されている信号の値は、例えば、クロックCLKが立ち上がる度に、破棄される。

【0083】

すなわち、フリップフロップ回路FF5、FF6が保持している信号の値は、例えば、クロックCLKが立ち上がる度に、更新される。なお、アイドルサイクルでは、ライトストローブ信号WRSおよびリードストローブ信号RDSのいずれもネゲートされているため、各フリップフロップ回路FFのイネーブル信号は、ネゲートされる。したがって、アイドルサイクルでは、フリップフロップ回路FF5、FF6がそれぞれ保持している信号の値(信号CODEab、CODEcd)は、維持される。

【0084】

また、フリップフロップ回路FF5、FF6の出力端子Qは、マルチプレクサMUX3の入力部に接続される。すなわち、フリップフロップ回路FF5、FF6がそれぞれ保持している信号の値(信号CODEab、CODEcd)は、マルチプレクサMUX1に入力される。

【0085】

マルチプレクサMUX3は、例えば、並列直列変換回路として動作し、フリップフロップ回路FF5、FF6から受けた2つの信号CODEab、CODEcdを1つの比較コードCODEとして比較部COMPに出力する。例えば、マルチプレクサMUX3は、データDATAIp、DATAOpおよびアドレスADRpのビット幅が4ビットのとき、信号CODEab、CODEcdを、比較コードCODEの0ビット−7ビット、8ビット−15ビットにそれぞれ割り当てる。

【0086】

すなわち、比較コードCODEは、互いに異なるタイミングで取得した2つの信号CODEab、CODEcdを用いて生成され、時系列の要素を含む。また、信号CODEab、CODEcdは、アドレスADRの一部とデータ(データDATAI、DATAO)の一部とを含んでいる。このため、この実施形態では、例えば、アドレスADRpのみを用いて生成された比較コードCODEに比べて、比較コードCODEの不規則性を高くできる。これにより、保護対象のモジュール20のセキュリティは、向上する。

【0087】

比較部COMPは、期待値DATAIeと比較コードCODEとを比較し、比較結果を書き込み制御部WCTLに通知する。書き込み制御部WCTL2は、例えば、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、期待値DATAIeと比較コードCODEとが一致しているとき、ライトストローブ信号WRSIをアサートする。また、例えば、書き込み制御部WCTL2は、比較許可信号CENがネゲートされているときには、比較部COMPの比較結果およびライトストローブ信号WRSの状態に拘わらず、ライトストローブ信号WRSIをネゲートする。

【0088】

なお、誤書き込み防止回路12の構成は、この例に限定されない。例えば、誤書き込み防止回路12は、比較制御部CCTLが省かれてもよい。また、例えば、シフトレジスタを構成するフリップフロップ回路FFの数は、3つ以上でもよい。あるいは、比較コード生成部CG4は、例えば、アドレスADRpを用いずに、データの一部(例えば、データDATAIp、DATAOp)のみを用いて比較コードCODEを生成してもよい。

【0089】

図7は、図6に示した誤書き込み防止回路12の動作の一例を示している。なお、図6は、保護対象のモジュール20とは別の2つのモジュール(例えば、図3に示したモジュール40、42)に対するアクセスが実施された後に、モジュール20に対する書き込み動作が実施されるときの誤書き込み防止回路12の動作の一例を示している。図7では、モジュール20とは別の2つのモジュールを、図3に示したモジュール40およびモジュール42として説明する。例えば、図7に示した動作では、モジュール40に対する書き込み動作および読み出し動作、アイドルサイクル、モジュール42に対する書き込み動作および読み出し動作、モジュール20に対する書き込み動作が順番に実施される。

【0090】

また、図7の例では、比較コード生成部CG4により取り込まれるデータDATAIp、DATAOpおよびアドレスADRpのビット幅は4ビットであり、比較コードCODEおよび期待値DATAIeのビット幅は16ビットである。また、バスBUSのデータバス幅は32ビットである。図中の“a”、“b”、“c”、“d”、“i”、“j”、“k”、“l”、“m”、“n”、“x”は、4ビットで示される任意の値を示している。なお、この動作の説明においては、図中の“x”は、特に意味のない値である。また、図中の“4321”は、モジュール20に書き込まれる16ビットのライトデータを示している。

【0091】

先ず、CPUの制御信号(図6に示した比較制御信号CNTS)に応答して、比較許可信号CENがアサートされる。これにより、比較コードCODEは、例えば、読み出し動作および書き込み動作のいずれかが実施される度に、更新される。

【0092】

期間T1では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされる。また、データDATAIおよびモジュール40内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール40に対する書き込み動作が実施される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“i”である。また、バスBUSに出力されたデータDATAIの下位4ビット(図6に示したデータDATAIp)は、“a”である。

【0093】

したがって、期間T2において、比較コードCODEは、“xxia”に更新される。この例の比較コードCODEでは、データDATAIの一部(データDATAIp)は、アドレスADRpより下位のビットに割り当てられている。なお、アドレスADRpとデータDATAIpとが割り当てられるビットは、互いに逆でもよい。

【0094】

期間T2では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール40内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール40に対する読み出し動作が実施され、バスBUSにリードデータ(図6に示したデータDATAO)が出力される。

【0095】

なお、バスBUSに出力されたアドレス(読み出し対象のアドレス)の下位4ビット(アドレスADRp)は、“j”である。また、バスBUSに出力されたリードデータの下位4ビット(データDATAOp)は、“b”である。したがって、期間T3において、比較コードCODEは、“iajb”に更新される。

【0096】

期間T3では、ライトストローブ信号WRSおよびリードストローブ信号RDSがネゲートされる。すなわち、期間T3は、アイドルサイクルである。例えば、アイドルサイクルにバスBUSに出力されているアドレスの下位4ビット(アドレスADRp)は、“k”である。期間T3がアイドルサイクルであるため、期間T4において、比較コードCODEは、更新されない。すなわち、比較コードCODEは、“iajb”に維持される。

【0097】

期間T4では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされる。また、データDATAIおよびモジュール42内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール42に対する書き込み動作が実施される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“l”である。また、バスBUSに出力されたデータDATAIの下位4ビットは、“c”である。したがって、期間T5において、比較コードCODEは、“jblc”に更新される。

【0098】

期間T5では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール42内の領域を示すアドレスがバスBUSに出力される。これにより、モジュール42に対する読み出し動作が実施され、バスBUSにリードデータが出力される。

【0099】

なお、バスBUSに出力されたアドレス(読み出し対象のアドレス)の下位4ビット(アドレスADRp)は、“m”である。また、バスBUSに出力されたリードデータの下位4ビット(データDATAOp)は、“d”である。したがって、期間T6において、比較コードCODEは、“lcmd”に更新される。これにより、保護対象のモジュール20に対する書き込み動作時に参照される比較コードCODEが生成される。

【0100】

この例では、比較コードCODEは、期間T4のバスBUS上のアドレスADRpおよびデータDATAIの一部(データDATAIp)と期間T5のバスBUS上のアドレスADRpおよびデータDATAOpとを含んでいる。すなわち、比較コードCODEは、互いに異なるタイミングで取得したバスBUS上の情報を用いて生成され、時系列の要素を含む。なお、この例では、期間T1、T2のバスBUS上の情報は、オーバーフローにより破棄され、期待値DATAIeとの比較対象から外れる。したがって、比較許可信号CENは、例えば、期間T4の直前にアサートされるように制御されてもよい。

【0101】

期間T6では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、データDATAIおよびモジュール20内の領域を示すアドレスがバスBUSに出力される。なお、バスBUSに出力されたアドレス(書き込み対象のアドレス)の下位4ビット(アドレスADRp)は、“n”である。また、バスBUSに出力されたDATAIは、モジュール20に対する書き込みを実施するためのデータである。例えば、データDATAIの上位16ビット(期待値DATAIe)は、“lcmd”であり、データDATAIの下位16ビット(ライトデータDATAIw)は、“4321”である。

【0102】

データDATAIの上位16ビット(期待値DATAIe)および比較コードCODEは、共に“lcmd”であり、互いに一致している。すなわち、期間T6では、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、期待値DATAIeと比較コードCODEとが一致している。このため、ライトストローブ信号WRSIがアサートされる。なお、期間T1−T5では、期待値DATAIeと比較コードCODEとが不一致のため、ライトストローブ信号WRSIはネゲートされている。

【0103】

ライトストローブ信号WRSIがアサートされたため、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“4321”)がモジュール20に書き込まれる。なお、例えば、期待値DATAIeと比較コードCODEとが不一致のときには、ライトストローブ信号WRSIがネゲートされるため、モジュール20に対する書き込みは、禁止される。これにより、この実施形態では、モジュール20に対する誤書き込みを防止できる。

【0104】

ここで、例えば、モジュール20を使用する正規のプログラマは、モジュール20に対する書き込み動作の前に実施されるアクセスを認識している。したがって、プログラマは、モジュール20にライトデータを書き込む際の期待値DATAIeとして、“lcmd”をデータDATAIの上位16ビットに設定できる。

【0105】

期間T7では、ライトストローブ信号WRSおよびリードストローブ信号RDSがネゲートされる。また、ライトストローブ信号WRSIが期間T6にアサートされたため、期間T7において、比較許可信号CENがネゲートされる。これにより、モジュール20に対する書き込み動作が終了する。なお、期間T7では、比較コードCODEは、“mdn1”に更新されている。そして、期間T8では、期間T7がアイドルサイクルであるため、比較コードCODEは、“mdn1”に維持される。

【0106】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、比較コードCODEは、アドレスADRの一部とデータ(データDATAI、DATAOの少なくとも一方)の一部とを含んでいる。これにより、比較コードCODEの不規則性が高くなる。このため、この実施形態では、保護対象のモジュール20のセキュリティをさらに向上できる。

【0107】

図8は、別の実施形態における誤書き込み防止回路13の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路13では、図4に示した誤書き込み防止回路11にカウンタ部CTが追加され、書き込み制御部WCTL2の代わりに書き込み制御部WCTL4が設けられている。誤書き込み防止回路13のその他の構成は、図4および図5で説明した実施形態と同じである。また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路13が設けられることを除いて、図1−図3で説明した実施形態と同じである。例えば、半導体装置の最小構成は、誤書き込み防止回路13および保護対象のモジュール20である。

【0108】

誤書き込み防止回路13は、例えば、保護対象のモジュール20に対する書き込みを比較部COMPの比較結果に基づいて許可したとき、予め設定された回数の書き込みがモジュール20に対して実施されるまで、モジュール20に対する書き込みを許可する。例えば、誤書き込み防止回路13は、カウンタ部CT、比較コード生成部CG2、比較部COMP、書き込み制御部WCTL4および比較制御部CCTLを有している。

【0109】

そして、誤書き込み防止回路13は、例えば、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTS、書き込み回数信号WNUM、アドレスデコード信号DECおよびクロックCLKを受け、ライトストローブ信号WRSIを出力する。書き込み回数信号WNUMは、例えば、モジュール20に対する書き込み回数を設定するための信号であり、CPUから出力される。また、アドレスデコード信号DECは、例えば、アドレスADRのデコード結果を示す信号であり、アドレスデコーダ(例えば、図3に示したアドレスデコーダADEC)から出力される。例えば、アドレスデコード信号DECは、モジュール20内の領域を示すアドレスがバスBUSに出力されたとき、アサートされる。

【0110】

カウンタ部CTは、例えば、クロックCLK、書き込み回数信号WNUMおよびライトストローブ信号WRSIを受け、書き込み許可信号WENを書き込み制御部WCTL4に出力する。例えば、カウンタ部CTは、回数比較部NCOMP、カウント制御部CTCNおよびクロックカウンタCCTを有している。

【0111】

回数比較部NCOMPは、例えば、CPUから受けた書き込み回数信号WNUMに基づいて、モジュール20に対する書き込み回数を設定する。そして、回数比較部NCOMPは、書き込み回数信号WNUMに基づく設定回数とクロックカウンタCCTのカウント値CTNUMとを比較し、比較結果をカウント制御部CTCNに通知する。例えば、設定回数は、期待値DATAIeと比較コードCODEとの比較結果に拘わらず実施されるモジュール20への書き込み回数である。この場合、設定回数に1を加算した回数の書き込みがモジュール20に対して実施される。

【0112】

カウント制御部CTCNは、書き込み制御部WCTL4からのライトストローブ信号WRSIおよび回数比較部NCOMPの比較結果を受け、書き込み許可信号WENをクロックカウンタCCTおよび書き込み制御部WCTL4に出力する。例えば、カウント制御部CTCNは、ライトストローブ信号WRSIに応答して、書き込み許可信号WENをアサートする。そして、カウント制御部CTCNは、設定回数とクロックカウンタCCTのカウント値CTNUMとの一致を示す比較結果に応答して、書き込み許可信号WENをネゲートする。

【0113】

クロックカウンタCCTは、例えば、モジュール20に対して実施された書き込み回数を、設定回数に一致するまでカウントする。例えば、クロックカウンタCCTは、書き込み許可信号WENおよびライトストローブ信号WRSIがアサートされているとき、クロックCLKに同期して、カウントアップする。そして、クロックカウンタCCTは、例えば、設定回数とクロックカウンタCCTのカウント値CTNUMとの一致を示す比較結果に応答して、カウント値CTNUMをリセットする。例えば、クロックカウンタCCTは、書き込み許可信号WENがネゲートされたとき、カウント値CTNUMをリセットする。

【0114】

書き込み制御部WCTL4は、比較部COMPの比較結果、比較許可信号CEN、書き込み許可信号WEN、ライトストローブ信号WRSおよびアドレスデコード信号DECを受け、ライトストローブ信号WRSIを保護対象のモジュール20に出力する。例えば、書き込み制御部WCTL4は、AND回路AND3、OR回路OR2およびAND回路AND4を有している。

【0115】

AND回路AND3は、比較許可信号CENおよび比較部COMPの比較結果を受ける。そして、AND回路AND3は、比較許可信号CENおよび比較部COMPの出力信号(比較結果)の論理積結果を、OR回路OR2に出力する。なお、比較部COMPの出力信号(比較結果)は、例えば、期待値DATAIeと比較コードCODEとが一致しているとき、アサートされる。

【0116】

OR回路OR2は、書き込み許可信号WENおよびAND回路AND3の出力信号を受ける。そして、OR回路OR2は、書き込み許可信号WENおよびAND回路AND3の出力信号の論理和結果を、AND回路AND4に出力する。

【0117】

AND回路AND4は、ライトストローブ信号WRS、アドレスデコード信号DECおよびOR回路OR2の出力信号を受ける。そして、AND回路AND4は、ライトストローブ信号WRS、アドレスデコード信号DECおよびOR回路OR2の出力信号の論理積結果(ライトストローブ信号WRSI)を、比較制御部CCTL、カウンタ部CTおよび保護対象のモジュール20に出力する。

【0118】

このように、書き込み制御部WCTL4は、例えば、比較許可信号CEN、ライトストローブ信号WRSおよびアドレスデコード信号DECがアサートされ、かつ、書き込み許可信号WENがネゲートされているとき、比較部COMPの比較結果に基づいて、モジュール20に対する書き込みを許可するか否かを決定する。

【0119】

また、例えば、書き込み制御部WCTL4は、書き込み許可信号WEN、ライトストローブ信号WRSおよびアドレスデコード信号DECがアサートされているとき、比較部COMPの比較結果および比較許可信号CENの状態に拘わらず、ライトストローブ信号WRSIをアサートする。これにより、モジュール20に対する書き込みは、比較部COMPの比較結果に基づいて許可されてから、書き込み回数信号WNUMに基づく設定回数とクロックカウンタCCTのカウント値CTNUMとが一致するまで許可される。

【0120】

なお、誤書き込み防止回路13の構成は、この例に限定されない。例えば、誤書き込み防止回路13は、比較制御部CCTLが省かれてもよい。また、誤書き込み防止回路13は、例えば、比較コード生成部CG2の代わりに、比較コード生成部CG4を有してもよい。

【0121】

図9は、図8に示した誤書き込み防止回路13の動作の一例を示している。なお、図9は、保護対象のモジュール20とは別の2つのモジュール(例えば、図3に示したモジュール40、42)に対するアクセスが実施された後に、モジュール20に対する書き込み動作が実施されるときの誤書き込み防止回路13の動作の一例を示している。図9に示した動作では、モジュール20に対する書き込み動作の前に実施される2つのモジュールに対するアクセス(例えば、モジュール40、42に対するアクセス)は、図5と同じである。なお、図9に示した動作では、書き込み回数信号WNUMに基づく設定回数は、2回である。

【0122】

また、図9の例では、アドレスADRpのビット幅は4ビットであり、比較コードCODEおよび期待値DATAIeのビット幅は16ビットであり、バスBUSのデータバス幅は32ビットである。図中の“i”、“j”、“k”、“l”、“m”、“n”、“x”の意味は、図5と同じである。また、図中の“4321”、“8765”および“cba9”は、モジュール20に書き込まれる16ビットのライトデータを示している。

【0123】

期間T1−期間T6までの誤書き込み防止回路13の動作は、図5に示した期間T1−T6と同じである。なお、期間T1−期間T6では、書き込み許可信号WENがネゲートされ、カウント値CTNUMが0に維持されている。

【0124】

例えば、期間T6では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、データDATAIおよびモジュール20内の領域を示すアドレスがバスBUSに出力される。モジュール20内の領域を示すアドレスがバスBUSに出力されたため、アドレスデコード信号DECがアサートされる。

【0125】

ライトストローブ信号WRSIは、データDATAIの上位16ビット(期待値DATAIe)と比較コードCODEとが一致し、かつ、ライトストローブ信号WRSおよびアドレスデコード信号DECがアサートされているため、アサートされる。これにより、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“4321”)がモジュール20に書き込まれる。

【0126】

期間T7では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール20以外の領域を示すアドレスがバスBUSに出力される。モジュール20以外の領域を示すアドレスがバスBUSに出力されたため、アドレスデコード信号DECがネゲートされる。アドレスデコード信号DECがネゲートされるため、ライトストローブ信号WRSIは、書き込み許可信号WENおよびライトストローブ信号WRSの状態に拘わらず、ネゲートされる。これにより、モジュール20に対する書き込みが禁止される。

【0127】

また、ライトストローブ信号WRSIが期間T6にアサートされたため、期間T7において、比較許可信号CENおよび書き込み許可信号WENがそれぞれネゲートおよびアサートされ、クロックカウンタCCTのカウント動作が開始される。なお、カウント値CTNUMは、ライトストローブ信号WRSIがネゲートされているため、更新されない。また、比較コードCODEは、期間T6の書き込み動作に応答して、“jlmn”に更新されている。そして、期間T8以降では、比較コードCODEは、比較許可信号CENがネゲートされているため、“jlmn”に維持される。

【0128】

期間T8では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール20内の領域を示すアドレスがバスBUSに出力される。このため、アドレスデコード信号DECがアサートされる。ライトストローブ信号WRS、書き込み許可信号WENおよびアドレスデコード信号DECがアサートされるため、ライトストローブ信号WRSIは、比較部COMPの比較結果に拘わらず、アサートされる。これにより、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“8765”)がモジュール20に書き込まれる。

【0129】

なお、書き込み許可信号WENは、カウント値CTNUMが設定回数(2回)に到達していないため、アサート状態に維持される。書き込み許可信号WENおよびライトストローブ信号WRSIがアサートされているため、カウント値CTNUMは、期間T9において、“0”から“1”に更新される。すなわち、カウント値CTNUMは、比較部COMPの比較結果に基づく最初の書き込みがモジュール20に対して実施された後、モジュール20に対する書き込み動作が実施される度に、カウントアップする。

【0130】

期間T9では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれネゲートおよびアサートされ、モジュール20以外の領域を示すアドレスがバスBUSに出力される。このため、アドレスデコード信号DECがネゲートされる。これにより、ライトストローブ信号WRSIがネゲートされる。この結果、モジュール20に対する書き込みが禁止される。このため、カウント値CTNUMは、更新されない。したがって、書き込み許可信号WENは、アサート状態に維持される。

【0131】

期間T10では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール20内の領域を示すアドレスがバスBUSに出力される。このため、アドレスデコード信号DECがアサートされる。ライトストローブ信号WRS、書き込み許可信号WENおよびアドレスデコード信号DECがアサートされるため、ライトストローブ信号WRSIは、比較部COMPの比較結果に拘わらず、アサートされる。これにより、モジュール20に対する書き込みが許可される。例えば、ライトデータ(“cba9”)がモジュール20に書き込まれる。

【0132】

なお、書き込み許可信号WENは、カウント値CTNUMが設定回数(2回)に到達していないため、アサートされている。書き込み許可信号WENおよびライトストローブ信号WRSIがアサートされているため、カウント値CTNUMは、期間T11において、“1”から“2”に更新される。なお、カウント値CTNUMは、“2”に更新されることにより、設定回数(2回)と一致するため、“0”にリセットされる。このため、図9では、期間T11のカウント値CTNUMを“0”と記載している。

【0133】

期間T11では、ライトストローブ信号WRSおよびリードストローブ信号RDSがそれぞれアサートおよびネゲートされ、モジュール20内の領域を示すアドレスがバスBUSに出力される。このため、アドレスデコード信号DECがアサートされる。なお、書き込み許可信号WENは、カウント値CTNUMが設定回数(2回)に到達したため、ネゲートされる。

【0134】

書き込み許可信号WENがネゲートされるため、ライトストローブ信号WRSIは、ライトストローブ信号WRSおよびアドレスデコード信号DECの状態に拘わらず、ネゲートされる。これにより、モジュール20に対する書き込みが禁止される。これにより、モジュール20に対する書き込み動作が終了する。

【0135】

なお、誤書き込み防止回路13の動作は、この例に限定されない。例えば、誤書き込み防止回路13は、比較部COMPの比較結果に基づく最初の書き込みを含むモジュール20に対する書き込み回数が設定回数(図9の例では、2回)に到達したとき、モジュール20に対する書き込み動作を終了してもよい。

【0136】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、誤書き込み防止回路13は、保護対象のモジュール20に対する書き込みを比較部COMPの比較結果に基づいて許可したとき、予め設定された回数の書き込みがモジュール20に対して実施されるまで、モジュール20に対する書き込みを許可する。これにより、この実施形態では、例えば、モジュール20に対する連続する書き込み(バースト書き込み等)に容易に対応できる。また、この実施形態では、例えば、バースト書き込みのうちの最初の書き込みに対してのみ比較コード生成部CG2を動作させればよいため、比較コード生成部CG2の消費電力を低減できる。

【0137】

図10は、別の実施形態における誤書き込み防止回路14の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路14では、図4に示した比較制御部CCTLの代わりに比較制御部CCTL2が設けられている。誤書き込み防止回路14のその他の構成は、図4および図5で説明した実施形態と同じである。なお、誤書き込み防止回路14は、CPU30を有してもよい。

【0138】

また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路14が設けられることを除いて、図1−図3で説明した実施形態と同じである。なお、この実施形態の半導体装置の最小構成は、例えば、誤書き込み防止回路14、保護対象のモジュール20およびCPU30である。

【0139】

誤書き込み防止回路14は、例えば、比較コード生成部CG2、比較部COMP、書き込み制御部WCTL2および比較制御部CCTL2を有している。例えば、誤書き込み防止回路14は、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTSおよびクロックCLKを受け、比較コードCODEおよびライトストローブ信号WRSIを出力する。

【0140】

比較制御部CCTL2は、例えば、比較制御信号CNTSおよびライトストローブ信号WRSIを受け、比較許可信号CENおよびコード生成信号CGEを出力する。例えば、比較制御部CCTL2は、比較コードCODEの生成開始を示すコード比較制御信号CNTSに応答して、コード生成信号CGEをアサートし、比較コードCODEの生成終了を示すコード比較制御信号CNTSに応答して、コード生成信号CGEをネゲートする。

【0141】

また、例えば、比較制御部CCTL2は、モジュール20に対する書き込みが実施されることを示す比較制御信号CNTSに応答して、比較許可信号CENをアサートする。そして、比較制御部CCTL2は、書き込み制御部WCTL2から受けるライトストローブ信号WRSIに応答して、比較許可信号CENをネゲートする。このように、比較制御部CCTL2は、比較コード生成部CG2および書き込み制御部WCTL2の動作を制御する。

【0142】

比較コード生成部CG2の動作は、比較許可信号CENの代わりにコード生成信号CGEを受けることを除いて、図4および図5で説明した実施形態と同じである。例えば、比較コード生成部CG2は、コード生成信号CGEがアサートされているとき、読み出し動作および書き込み動作のいずれかが実施される度に、比較コードCODEを更新する。すなわち、比較コードCODEは、コード生成信号CGEがネゲートされているとき、更新されない。

【0143】

また、比較コードCODEは、例えば、CPU30および比較部COMPに出力される。例えば、CPU30は、モジュール20に対する書き込みが実施されることを示す比較制御信号CNTSを誤書き込み防止回路14に出力する前に、誤書き込み防止回路14から受けた最新の比較コードCODEを、データDATAIの上位16ビット(期待値DATAIe)に設定する。これにより、モジュール20に対する書き込みが実施されるとき、期待値DATAIeと比較コードCODEとが一致する。

【0144】

なお、誤書き込み防止回路14の構成は、この例に限定されない。例えば、誤書き込み防止回路14は、比較コード生成部CG2の代わりに、比較コード生成部CG4を有してもよい。あるいは、誤書き込み防止回路14は、例えば、比較コード生成部CG2から取得した比較コードCODEをデータDATAIの上位16ビット(期待値DATAIe)に設定する処理部(CPU30の一部の機能)を有してもよい。

【0145】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、コード比較制御信号CNTSに基づくコード生成信号CGEを用いて、期待値DATAIeを簡易に生成できる。このため、この実施形態では、誤書き込み防止回路14等の使用勝手を向上できる。

【0146】

図11は、別の実施形態における誤書き込み防止回路15の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の誤書き込み防止回路15は、図4に示した書き込み制御部WCTL4および比較制御部CCTLの代わりに、書き込み制御部WCTL6および比較制御部CCTL4をそれぞれ有している。誤書き込み防止回路15のその他の構成は、図4および図5で説明した実施形態と同じである。また、この実施形態の半導体装置は、誤書き込み防止回路10の代わりに誤書き込み防止回路15が設けられることを除いて、図1−図3で説明した実施形態と同じである。例えば、半導体装置の最小構成は、誤書き込み防止回路15および保護対象のモジュール20である。

【0147】

誤書き込み防止回路15は、例えば、比較コード生成部CG2、比較部COMP、書き込み制御部WCTL6および比較制御部CCTL4を有している。例えば、誤書き込み防止回路15は、期待値DATAIe、アドレスADRp(アドレスADRの一部)、ライトストローブ信号WRS、リードストローブ信号RDS、比較制御信号CNTSおよびクロックCLKを受け、ライトストローブ信号WRSIを出力する。

【0148】

比較制御部CCTL4は、例えば、比較制御信号CNTSおよびライトストローブ信号WRSIを受け、比較許可信号CENおよび解除信号CANCを出力する。例えば、比較制御部CCTL4は、保護を無効にするコード比較制御信号CNTSに応答して、解除信号CANCをアサートし、保護を有効にするコード比較制御信号CNTSに応答して、解除信号CANCをネゲートする。

【0149】

また、例えば、比較制御部CCTL4は、比較コードCODEの更新等を許可することを示す比較制御信号CNTSに応答して、比較許可信号CENをアサートする。そして、比較制御部CCTL4は、書き込み制御部WCTL6から受けるライトストローブ信号WRSIに応答して、比較許可信号CENをネゲートする。このように、比較制御部CCTL4は、比較コード生成部CG2および書き込み制御部WCTL6の動作を制御する。なお、比較コード生成部CG2の動作は、図4および図5で説明した実施形態と同じである。

【0150】

書き込み制御部WCTL6は、比較部COMPの比較結果、比較許可信号CEN、解除信号CANCおよびライトストローブ信号WRSを受け、ライトストローブ信号WRSIを保護対象のモジュール20に出力する。例えば、書き込み制御部WCTL6は、AND回路AND3、OR回路OR2およびAND回路AND5を有している。

【0151】

AND回路AND3は、比較許可信号CENおよび比較部COMPの比較結果を受ける。そして、AND回路AND3は、比較許可信号CENおよび比較部COMPの出力信号(比較結果)の論理積結果を、OR回路OR2に出力する。なお、比較部COMPの出力信号(比較結果)は、例えば、期待値DATAIeと比較コードCODEとが一致しているとき、アサートされる。

【0152】

OR回路OR2は、解除信号CANCおよびAND回路AND3の出力信号を受ける。そして、OR回路OR2は、解除信号CANCおよびAND回路AND3の出力信号の論理和結果を、AND回路AND5に出力する。AND回路AND5は、ライトストローブ信号WRSおよびOR回路OR2の出力信号を受ける。そして、AND回路AND5は、ライトストローブ信号WRSおよびOR回路OR2の出力信号の論理積結果(ライトストローブ信号WRSI)を、比較制御部CCTL4および保護対象のモジュール20に出力する。

【0153】

このように、書き込み制御部WCTL6は、例えば、比較許可信号CENおよびライトストローブ信号WRSがアサートされ、かつ、解除信号CANCがネゲートされているとき、比較部COMPの比較結果に基づいて、モジュール20に対する書き込みを許可するか否かを決定する。

【0154】

また、例えば、書き込み制御部WCTL6は、解除信号CANCおよびライトストローブ信号WRSがアサートされているとき、比較部COMPの比較結果および比較許可信号CENの状態に拘わらず、ライトストローブ信号WRSIをアサートする。すなわち、書き込み制御部WCTL6は、解除信号CANCがアサートされているとき、ライトストローブ信号WRSをライトストローブ信号WRSIとして出力する。これにより、この実施形態では、例えば、モジュール20に対する書き込みを保護しなくてよいとき、解除信号CANCをアサートすることにより、期待値DATAIeの設定を省くことができる。この結果、この実施形態では、誤書き込み防止回路15等の使用勝手を向上できる。

【0155】

なお、誤書き込み防止回路15の構成は、この例に限定されない。例えば、比較制御部CCTL4は、解除信号CANCをアサートしたとき、比較許可信号CENをネゲートしてもよい。この場合、例えば、モジュール20に対する書き込みを保護しなくてよいとき、誤書き込み防止回路15の消費電力を低減できる。また、例えば、誤書き込み防止回路15は、比較コード生成部CG2の代わりに、比較コード生成部CG4を有してもよい。

【0156】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。また、この実施形態では、コード比較制御信号CNTSに基づく解除信号CANCを用いて、誤書き込み防止回路15に接続されたモジュール20に対する保護を有効にするか無効にするか設定できる。このため、この実施形態では、誤書き込み防止回路15等の使用勝手を向上できる。

【0157】

図12は、別の実施形態における半導体装置102の一例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態の半導体装置102では、図2に示した誤書き込み防止回路10およびモジュール20の代わりに誤書き込み防止回路11およびモジュール22がそれぞれ設けられ、アドレスデコーダADECがモジュール22の外部に設けられている。半導体装置102のその他の構成は、図1−図3で説明した実施形態と同じである。なお、例えば、半導体装置の最小構成は、誤書き込み防止回路11、保護対象のモジュール22およびアドレスデコーダADECである。また、モジュール22の構成は、アドレスデコーダADECが外部に設けられていることを除いて、モジュール20と同じである。なお、モジュール22は、図3に示したライトストローブ信号WRSIの代わりにライトストローブ信号WRSを受ける。

【0158】

アドレスデコーダADECは、アドレスADRをバスBUSを介して受け、アドレスデコード信号DECを誤書き込み防止回路11に出力する。誤書き込み防止回路11は、アドレスデコード信号DECIをモジュール22に出力する。すなわち、誤書き込み防止回路11は、アドレスデコード信号DECIを用いて、モジュール22に対する書き込みの許可/禁止を制御する。例えば、アドレスデコード信号DECIおよびライトストローブ信号WRSがアサートされたとき、モジュール22に対する書き込みが実施される。

【0159】

なお、半導体装置102の構成は、この例に限定されない。例えば、半導体装置102は、誤書き込み防止回路11の代わりに、誤書き込み防止回路10、12−15のいずれかを有してもよい。この場合、誤書き込み防止回路10、12−15は、アドレスデコード信号DECを受け、アドレスデコード信号DECIを出力する。

【0160】

図13は、図12に示した半導体装置102に搭載される誤書き込み防止回路11の一例を示している。誤書き込み防止回路11の書き込み制御部WCTL2は、入力信号の一部の種類および出力信号の種類を除いて、図4に示した書き込み制御部WCTL2と同じである。例えば、書き込み制御部WCTL2は、ライトストローブ信号WRSの代わりにアドレスデコード信号DECを受け、ライトストローブ信号WRSIの代わりにアドレスデコード信号DECIを出力する。

【0161】

また、誤書き込み防止回路11の比較制御部CCTLは、ライトストローブ信号WRSIの代わりにアドレスデコード信号DECIを受けることを除いて、図4に示した比較制御部CCTLと同じである。誤書き込み防止回路11のその他の構成および動作は、図4および図5で説明した実施形態と同じである。

【0162】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0163】

以上の実施形態において説明した発明を整理して、付記として開示する。

(付記1)

バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードを生成する比較コード生成部と、

前記バスに接続された保護対象のモジュールに書き込まれるデータに対応する期待値と前記比較コードとを比較する比較部と、

前記比較部の比較結果に基づいて、前記モジュールに対する書き込みを許可するか否かを決定する書き込み制御部と

を備えていることを特徴とする誤書き込み防止回路。

(付記2)

前記比較コード生成部は、前記バスに出力されたアドレスおよびデータのそれぞれの一部の値を取得し、取得した値を用いて前記比較コードを生成すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記3)

前記比較コード生成部は、前記バスに出力されたアドレスの一部の値を取得し、取得した値を用いて前記比較コードを生成すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記4)

前記比較コード生成部は、前記バスに出力されたデータの一部の値を取得し、取得した値を用いて前記比較コードを生成すること

を特徴とする付記1記載の誤書き込み防止回路。

(付記5)

前記モジュールに対して実施された書き込みの回数をカウントするカウンタ部を有し、