論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

Notice: Undefined index: DEJ in /mnt/www/gzt_disp.php on line 298

【特許請求の範囲】

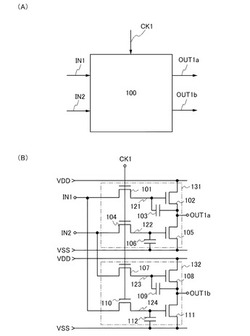

【請求項1】

入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された前記第1の信号乃至前記第3の信号に応じて電圧状態が設定された第4の信号を出力する第1の論理回路と、

入力信号として、前記第1の信号、前記第2の信号、及び前記第3の信号が入力され、入力された前記第1の信号乃至前記第3の信号に応じて電圧状態が設定された第5の信号を出力する第2の論理回路と、を有し、

前記第1の論理回路は、第1のトランジスタ乃至第4のトランジスタ、並びに第1の容量素子を有し、

前記第1のトランジスタのゲートには前記第3の信号が入力され、前記第1のトランジスタのソース及びドレインの一方には前記第1の信号が入力され、

前記第2のトランジスタのゲートは前記第1のトランジスタのソース及びドレインの他方に電気的に接続され、前記第2のトランジスタのソース及びドレインの一方に高電源電圧が与えられ、前記第2のトランジスタのソース及びドレインの他方の電圧が前記第4の信号の電圧となり、

前記第3のトランジスタのゲートには前記第3の信号が入力され、前記第3のトランジスタのソース及びドレインの一方には前記第2の信号が入力され、

前記第4のトランジスタのゲートは前記第3のトランジスタのソース及びドレインの他方に電気的に接続され、前記第4のトランジスタのソース及びドレインの一方は前記第2のトランジスタのソース及びドレインの他方に電気的に接続され、前記第4のトランジスタのソース及びドレインの他方は低電源電圧が入力され、

前記第1の容量素子の第1の電極は前記第4のトランジスタのゲートに電気的に接続され、前記第1の容量素子の第2の電極に前記低電源電圧が入力され、

前記第2の論理回路は、第5のトランジスタ乃至第8のトランジスタ、並びに第2の容量素子を有し、

前記第5のトランジスタのゲートには前記第3の信号が入力され、前記第5のトランジスタのソース及びドレインの一方には前記第2の信号が入力され、

前記第6のトランジスタのゲートは前記第5のトランジスタのソース及びドレインの他方に電気的に接続され、前記第6のトランジスタのソース及びドレインの一方に高電源電圧が与えられ、前記第6のトランジスタのソース及びドレインの他方の電圧が前記第5の信号の電圧となり、

前記第7のトランジスタのゲートには前記第3の信号が入力され、前記第7のトランジスタのソース及びドレインの一方には前記第1の信号が入力され、

前記第8のトランジスタのゲートは前記第7のトランジスタのソース及びドレインの他方に電気的に接続され、前記第8のトランジスタのソース及びドレインの一方は前記第6のトランジスタのソース及びドレインの他方に電気的に接続され、前記第8のトランジスタのソース及びドレインの他方は前記低電源電圧が入力され、

前記第2の容量素子の第1の電極は前記第8のトランジスタのゲートに電気的に接続され、前記第2の容量素子の第2の電極に前記低電源電圧が入力され、

前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれは、チャネル形成層としての機能を有する酸化物半導体層を含み、

前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれは、ソース−ゲート間電圧が−10V、ソース−ドレイン間電圧が1Vのときに、チャネル幅1μmあたりのオフ電流が1×10−13A以下である論理回路。

【請求項2】

請求項1において、前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれにおける、チャネル幅1μmあたりのオフ電流は、1×10−17A以下である論理回路。

【請求項3】

請求項1又は請求項2において、前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれにおける、前記酸化物半導体層のキャリア濃度は、1×1014/cm3以下である論理回路。

【請求項4】

入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された前記第1の信号乃至前記第3の信号に応じて電圧状態が設定された第4の信号を出力する第1の論理回路と、

入力信号として、前記第1の信号、前記第2の信号、及び前記第3の信号が入力され、入力された前記第1の信号乃至前記第3の信号に応じて電圧状態が設定された第5の信号を出力する第2の論理回路と、を有し、

前記第1の論理回路は、第1のトランジスタ乃至第4のトランジスタ、並びに第1の容量素子を有し、

前記第1のトランジスタのゲートには前記第3の信号が入力され、前記第1のトランジスタのソース及びドレインの一方には前記第1の信号が入力され、

前記第2のトランジスタのゲートは前記第1のトランジスタのソース及びドレインの他方に電気的に接続され、前記第2のトランジスタのソース及びドレインの一方に高電源電圧が与えられ、前記第2のトランジスタのソース及びドレインの他方の電圧が前記第4の信号の電圧となり、

前記第3のトランジスタのゲートには前記第3の信号が入力され、前記第3のトランジスタのソース及びドレインの一方には前記第2の信号が入力され、

前記第4のトランジスタのゲートは前記第3のトランジスタのソース及びドレインの他方に電気的に接続され、前記第4のトランジスタのソース及びドレインの一方は前記第2のトランジスタのソース及びドレインの他方に電気的に接続され、前記第4のトランジスタのソース及びドレインの他方は低電源電圧が入力され、

前記第1の容量素子の第1の電極は前記第4のトランジスタのゲートに電気的に接続され、前記第1の容量素子の第2の電極に前記低電源電圧が入力され、

前記第2の論理回路は、第5のトランジスタ乃至第8のトランジスタ、並びに第2の容量素子を有し、

前記第5のトランジスタのゲートには前記第3の信号が入力され、前記第5のトランジスタのソース及びドレインの一方には前記第2の信号が入力され、

前記第6のトランジスタのゲートは前記第5のトランジスタのソース及びドレインの他方に電気的に接続され、前記第6のトランジスタのソース及びドレインの一方に高電源電圧が与えられ、前記第6のトランジスタのソース及びドレインの他方の電圧が前記第5の信号の電圧となり、

前記第7のトランジスタのゲートには前記第3の信号が入力され、前記第7のトランジスタのソース及びドレインの一方には前記第1の信号が入力され、

前記第8のトランジスタのゲートは前記第7のトランジスタのソース及びドレインの他方に電気的に接続され、前記第8のトランジスタのソース及びドレインの一方は前記第6のトランジスタのソース及びドレインの他方に電気的に接続され、前記第8のトランジスタのソース及びドレインの他方は前記低電源電圧が入力され、

前記第2の容量素子の第1の電極は前記第8のトランジスタのゲートに電気的に接続され、前記第2の容量素子の第2の電極に前記低電源電圧が入力され、

前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれは、キャリア濃度が1×1014/cm3以下である酸化物半導体層を有する論理回路。

【請求項5】

請求項1乃至請求項4のいずれか一項に記載の論理回路を含むシフトレジスタを備えた駆動回路と、前記駆動回路により表示状態が制御される画素を含む画素部と、を有する半導体装置。

【請求項1】

入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された前記第1の信号乃至前記第3の信号に応じて電圧状態が設定された第4の信号を出力する第1の論理回路と、

入力信号として、前記第1の信号、前記第2の信号、及び前記第3の信号が入力され、入力された前記第1の信号乃至前記第3の信号に応じて電圧状態が設定された第5の信号を出力する第2の論理回路と、を有し、

前記第1の論理回路は、第1のトランジスタ乃至第4のトランジスタ、並びに第1の容量素子を有し、

前記第1のトランジスタのゲートには前記第3の信号が入力され、前記第1のトランジスタのソース及びドレインの一方には前記第1の信号が入力され、

前記第2のトランジスタのゲートは前記第1のトランジスタのソース及びドレインの他方に電気的に接続され、前記第2のトランジスタのソース及びドレインの一方に高電源電圧が与えられ、前記第2のトランジスタのソース及びドレインの他方の電圧が前記第4の信号の電圧となり、

前記第3のトランジスタのゲートには前記第3の信号が入力され、前記第3のトランジスタのソース及びドレインの一方には前記第2の信号が入力され、

前記第4のトランジスタのゲートは前記第3のトランジスタのソース及びドレインの他方に電気的に接続され、前記第4のトランジスタのソース及びドレインの一方は前記第2のトランジスタのソース及びドレインの他方に電気的に接続され、前記第4のトランジスタのソース及びドレインの他方は低電源電圧が入力され、

前記第1の容量素子の第1の電極は前記第4のトランジスタのゲートに電気的に接続され、前記第1の容量素子の第2の電極に前記低電源電圧が入力され、

前記第2の論理回路は、第5のトランジスタ乃至第8のトランジスタ、並びに第2の容量素子を有し、

前記第5のトランジスタのゲートには前記第3の信号が入力され、前記第5のトランジスタのソース及びドレインの一方には前記第2の信号が入力され、

前記第6のトランジスタのゲートは前記第5のトランジスタのソース及びドレインの他方に電気的に接続され、前記第6のトランジスタのソース及びドレインの一方に高電源電圧が与えられ、前記第6のトランジスタのソース及びドレインの他方の電圧が前記第5の信号の電圧となり、

前記第7のトランジスタのゲートには前記第3の信号が入力され、前記第7のトランジスタのソース及びドレインの一方には前記第1の信号が入力され、

前記第8のトランジスタのゲートは前記第7のトランジスタのソース及びドレインの他方に電気的に接続され、前記第8のトランジスタのソース及びドレインの一方は前記第6のトランジスタのソース及びドレインの他方に電気的に接続され、前記第8のトランジスタのソース及びドレインの他方は前記低電源電圧が入力され、

前記第2の容量素子の第1の電極は前記第8のトランジスタのゲートに電気的に接続され、前記第2の容量素子の第2の電極に前記低電源電圧が入力され、

前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれは、チャネル形成層としての機能を有する酸化物半導体層を含み、

前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれは、ソース−ゲート間電圧が−10V、ソース−ドレイン間電圧が1Vのときに、チャネル幅1μmあたりのオフ電流が1×10−13A以下である論理回路。

【請求項2】

請求項1において、前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれにおける、チャネル幅1μmあたりのオフ電流は、1×10−17A以下である論理回路。

【請求項3】

請求項1又は請求項2において、前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれにおける、前記酸化物半導体層のキャリア濃度は、1×1014/cm3以下である論理回路。

【請求項4】

入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された前記第1の信号乃至前記第3の信号に応じて電圧状態が設定された第4の信号を出力する第1の論理回路と、

入力信号として、前記第1の信号、前記第2の信号、及び前記第3の信号が入力され、入力された前記第1の信号乃至前記第3の信号に応じて電圧状態が設定された第5の信号を出力する第2の論理回路と、を有し、

前記第1の論理回路は、第1のトランジスタ乃至第4のトランジスタ、並びに第1の容量素子を有し、

前記第1のトランジスタのゲートには前記第3の信号が入力され、前記第1のトランジスタのソース及びドレインの一方には前記第1の信号が入力され、

前記第2のトランジスタのゲートは前記第1のトランジスタのソース及びドレインの他方に電気的に接続され、前記第2のトランジスタのソース及びドレインの一方に高電源電圧が与えられ、前記第2のトランジスタのソース及びドレインの他方の電圧が前記第4の信号の電圧となり、

前記第3のトランジスタのゲートには前記第3の信号が入力され、前記第3のトランジスタのソース及びドレインの一方には前記第2の信号が入力され、

前記第4のトランジスタのゲートは前記第3のトランジスタのソース及びドレインの他方に電気的に接続され、前記第4のトランジスタのソース及びドレインの一方は前記第2のトランジスタのソース及びドレインの他方に電気的に接続され、前記第4のトランジスタのソース及びドレインの他方は低電源電圧が入力され、

前記第1の容量素子の第1の電極は前記第4のトランジスタのゲートに電気的に接続され、前記第1の容量素子の第2の電極に前記低電源電圧が入力され、

前記第2の論理回路は、第5のトランジスタ乃至第8のトランジスタ、並びに第2の容量素子を有し、

前記第5のトランジスタのゲートには前記第3の信号が入力され、前記第5のトランジスタのソース及びドレインの一方には前記第2の信号が入力され、

前記第6のトランジスタのゲートは前記第5のトランジスタのソース及びドレインの他方に電気的に接続され、前記第6のトランジスタのソース及びドレインの一方に高電源電圧が与えられ、前記第6のトランジスタのソース及びドレインの他方の電圧が前記第5の信号の電圧となり、

前記第7のトランジスタのゲートには前記第3の信号が入力され、前記第7のトランジスタのソース及びドレインの一方には前記第1の信号が入力され、

前記第8のトランジスタのゲートは前記第7のトランジスタのソース及びドレインの他方に電気的に接続され、前記第8のトランジスタのソース及びドレインの一方は前記第6のトランジスタのソース及びドレインの他方に電気的に接続され、前記第8のトランジスタのソース及びドレインの他方は前記低電源電圧が入力され、

前記第2の容量素子の第1の電極は前記第8のトランジスタのゲートに電気的に接続され、前記第2の容量素子の第2の電極に前記低電源電圧が入力され、

前記第1のトランジスタ乃至前記第8のトランジスタのそれぞれは、キャリア濃度が1×1014/cm3以下である酸化物半導体層を有する論理回路。

【請求項5】

請求項1乃至請求項4のいずれか一項に記載の論理回路を含むシフトレジスタを備えた駆動回路と、前記駆動回路により表示状態が制御される画素を含む画素部と、を有する半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図30】

【図31】

【図29】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図30】

【図31】

【図29】

【公開番号】特開2013−62809(P2013−62809A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2012−220094(P2012−220094)

【出願日】平成24年10月2日(2012.10.2)

【分割の表示】特願2010−229460(P2010−229460)の分割

【原出願日】平成22年10月12日(2010.10.12)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成24年10月2日(2012.10.2)

【分割の表示】特願2010−229460(P2010−229460)の分割

【原出願日】平成22年10月12日(2010.10.12)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]