論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路に関する。

【背景技術】

【0002】

ロジックLSI(Large Scale Integration)等の論理回路を含む半導体集積回路では、故障検出率を向上するために、テスト回路である観測点や制御点が論理回路中に挿入される。観測点は、所定のノードの信号値を観測するために論理回路中に挿入され、制御点は、所定のノードに信号値を与えるために論理回路中に挿入される。例えば、観測点または制御点を挿入するときの故障検出率をそれぞれ求め、単位面積当たりの故障検出率の向上効果が高いテスト回路を論理回路内に挿入する手法が提案されている(例えば、特許文献1参照。)。

【0003】

また、論理回路中の全てのフリップフロップをスキャンフリップフロップに置き換えるフルスキャン設計において、テストパターン数が所定値を超える回路ブロックに観測点や制御点を挿入する手法が提案されている(例えば、特許文献2参照。)。マクロとユーザロジックとの間の遅延故障を検出するために、マクロの入力端子に接続された制御点にトグル動作する機能を追加する手法が提案されている(例えば、特許文献3参照。)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−84427号公報

【特許文献2】特開2001−312529号公報

【特許文献3】特開2009−205414号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

論理ゲートの一方の入力にユーザロジックの出力が接続され、論理ゲートの他方の入力に制御点を介して別のユーザロジックの出力が接続される場合、一方の入力を含む信号パスの遅延故障と、他方の入力を含む信号パスの遅延故障とを、1つの制御点を用いて検出できない。具体的には、一方の入力を含む信号パスの遅延故障を検出するために、出力論理を固定する機能を有する制御点を設ける場合、制御点から互いに異なる論理を連続して出力できないため、他方の入力を含む信号パスの遅延故障を検出できない。また、他方の入力を含む信号パスの遅延故障を検出するために、出力論理を順に変化する機能を有する制御点を設ける場合、制御点から同じ論理を連続して出力できないため、一方の入力を含む信号パスの遅延故障を検出できない。

【0006】

本発明の目的は、論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出できる論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路を提供することである。

【課題を解決するための手段】

【0007】

本発明の論理回路の故障検出方法の一形態では、データ入力およびスキャン入力を有する複数の第1スキャンフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、少なくとも1つの第1スキャンフリップフロップを含み、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有し、制御点は、第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する論理回路の故障検出方法であって、スキャン入力を有効にし、第1および第2スキャンフリップフロップをシフトレジスタとして動作させるスキャンシフト期間に、第1スキャンフリップフロップの1つおよび第2スキャンフリップフロップに同じ論理を設定し、第1入力に直列に接続される一対の第1スキャンフリップフロップに互いに異なる論理を設定し、データ入力を有効にするキャプチャ期間に、第1および第2スキャンフリップフロップに2つのクロックパルスを供給し、第3ユーザロジックの第1スキャンフリップフロップに保持される論理が変化しないときに第1入力を含む信号パスの遅延故障を検出することを特徴とする。

【0008】

本発明の論理回路のテスト回路挿入方法の一形態では、複数のフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力および第2ユーザロジックの出力に接続される第2入力を有する第1論理ゲートと、第1論理ゲートの出力に接続され、少なくとも1つのフリップフロップを含む第3ユーザロジックとを有する論理回路のテスト回路挿入方法であって、フリップフロップをデータ入力およびスキャン入力を各々有する第1スキャンフリップフロップに置き換える処理と、データ入力およびスキャン入力を有する第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第2入力に接続された第2論理ゲートとを有する制御点を、第2ユーザロジックと第1論理ゲートとの間に挿入する処理と、第2スキャンフリップフロップのデータ入力に第1スキャンフリップフロップの1つのデータ出力を接続する処理とを含むことを特徴とする。

【0009】

本発明の論理回路のテスト回路挿入装置の一形態では、複数のフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力および第2ユーザロジックの出力に接続される第2入力を有する第1論理ゲートと、第1論理ゲートの出力に接続され、少なくとも1つのフリップフロップを含む第3ユーザロジックとを有する論理回路のテスト回路挿入装置であって、フリップフロップをデータ入力およびスキャン入力を各々有する第1スキャンフリップフロップに置き換える処理と、データ入力およびスキャン入力を有する第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第2入力に接続された第2論理ゲートとを有する制御点を、第2ユーザロジックと第1論理ゲートとの間に挿入する処理と、第2スキャンフリップフロップのデータ入力に第1スキャンフリップフロップの1つのデータ出力を接続する処理とを実施することを特徴とする。

【0010】

本発明の半導体集積回路の一形態では、データ入力およびスキャン入力を有する複数の第1スキャンフリップフロップをそれぞれ含む第1ユーザロジックと、第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、少なくとも1つの第1スキャンフリップフロップを含み、第1論理ゲートの出力に接続された第3ユーザロジックと、第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力およびテストモードを示すテストモード端子に接続されたマスク回路と、一対の入力がマスク回路の出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する制御点とを備え、マスク回路は、テストモード中に、第2スキャンフリップフロップからの出力信号を第2論理ゲートに伝達し、テストモードを除く期間に、出力信号の第2論理ゲートへの伝達をマスクするとともに、第2ユーザロジックからの出力信号を第2論理ゲートを介して第1論理ゲートに伝達するための論理値を第2論理ゲートに出力することを特徴とする。

【発明の効果】

【0011】

第1論理ゲートの第1入力を含む信号パスの遅延故障と、第1論理ゲートの第2入力を含む信号パスの遅延故障とを、1つの制御点により検出できる。

【図面の簡単な説明】

【0012】

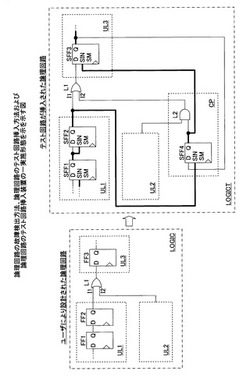

【図1】論理回路の故障検出方法、論理回路のテスト回路挿入方法および論理回路のテスト回路挿入装置の一実施形態を示している。

【図2】図1に示したテスト回路が挿入された論理回路の故障検出方法の例を示している。

【図3】論理回路の故障検出方法、論理回路のテスト回路挿入方法および論理回路のテスト回路挿入装置の別の実施形態および半導体集積回路の一実施形態を示している。

【図4】図3に示した論理回路にテスト回路を挿入する前の論理回路の例を示している。

【図5】図4に示した論理回路から図3に示した論理回路を生成するテスト回路挿入装置の例を示している。

【図6】図5に示したテスト回路挿入装置の動作の例を示している。

【図7】図3に示した論理回路を有する半導体集積回路をテストするテストシステムの例を示している。

【図8】図3に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図9】図3に示した論理回路の遅延故障を検出するためのテストの別の例を示している。

【図10】論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。

【図11】図10に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図12】図10に示した論理回路の遅延故障を検出するためのテストの別の例を示している。

【図13】論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。

【図14】図13に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図15】図13に示した論理回路の遅延故障を検出するためのテストの別の例を示している。

【図16】論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。

【図17】図16に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図18】図16に示した論理回路の遅延故障を検出するためのテストの別の例を示している。

【図19】論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。

【図20】19に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図21】図19に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。

【発明を実施するための形態】

【0013】

以下、図面を用いて実施形態を説明する。図中、信号が伝達される信号線には、信号名と同じ符号を使用する。

【0014】

図1は、論理回路の故障検出方法、論理回路のテスト回路挿入方法および論理回路のテスト回路挿入装置の一実施形態を示している。図1の左側は、ユーザにより設計された論理回路LOGICの例を示している。図1の右側は、論理回路LOGICにテスト回路を挿入することで生成された論理回路LOGICTの例を示している。

【0015】

論理回路LOGICは、ユーザロジックUL1、UL2、UL3および論理ゲートL1を有している。ユーザロジックUL1は、複数のフリップフロップFF(FF1、FF2)を含んでいる。ユーザロジックUL3は、少なくとも1つのフリップフロップFF3を含んでいる。フリップフロップFF1−FF5は、”>”印で示すクロック入力で共通のクロックを受けて動作する。なお、図が複雑になることを避けるため、クロック配線は省略している。

【0016】

ユーザロジックUL1、UL2の出力は、論理ゲートL1の入力I1、I2にそれぞれ接続されている。論理ゲートL1の出力は、ユーザロジックUL3の入力に接続されている。なお、論理ゲートL1は、オアゲートに限定されず、アンドゲート、ノアゲート、ナンドゲート等でもよい。

【0017】

例えば、フリップフロップFF1のデータ出力Qは、フリップフロップFF2のデータ入力Dに接続されている。フリップフロップFF2のデータ出力Qは、論理ゲートL1の入力I1に接続されている。すなわち、フリップフロップFF1、FF2は、直列に接続されている。なお、フリップフロップFF1のデータ出力Qは、組み合わせ回路を介してフリップフロップFF2のデータ入力Dに接続されてもよい。フリップフロップFF2のデータ出力Qは、組み合わせ回路を介して入力I1に接続されてもよい。論理ゲートL1の出力は、フリップフロップFF3のデータ入力Dに接続されている。なお、論理ゲートL1の出力は、組み合わせ回路を介してフリップフロップFF3のデータ入力Dに接続されてもよい。

【0018】

この例では、ユーザロジックUL2の出力(すなわち、論理ゲートL1の入力I2)は、論理1になりやすいとする。このため、入力ノードI1を含む信号パスの縮退故障や遅延故障を検出するため、あるいは、入力ノードI2を含む信号パスの縮退故障や遅延故障を検出するために、図1の右側に示すようにテスト回路が挿入される。

【0019】

論理回路LOGICTは、フリップフロップFFから置き換えられたスキャンフリップフロップSFF(SFF1、SFF2、SFF3)と、ユーザロジックUL2の出力と論理ゲートL1の入力I2との間に挿入された制御点CPとを有している。制御点CPは、論理ゲートL1の入力I2の論理値を制御するためのテスト回路の一例であり、スキャンフリップフロップSFF4および論理ゲートL2を有している。

【0020】

各スキャンフリップフロップSFF1−SFF4は、データ入力Dの他にスキャン入力SINおよびスキャンモード入力SMを有している。なお、図が複雑になることを避けるため、スキャンモード入力SMに接続される配線は省略している。スキャンフリップフロップSFF1−SFF4は、スキャンモード入力SMで第1論理(例えば、論理0)を受けているキャプチャ期間に、データ入力Dで受ける論理をクロックに同期してラッチし、ラッチした論理をデータ出力Qから出力する。

【0021】

スキャンフリップフロップSFF1−SFF4は、スキャンモード入力SMで第2論理(例えば、論理1)を受けているスキャンシフト期間に、スキャン入力SINで受ける論理をクロックに同期してラッチし、ラッチした論理をデータ出力Qから出力する。なお、各スキャンフリップフロップSFF1−SFF4は、データ入力Dまたはスキャン入力SINのいずれかを選択するマルチプレクサを、各フリップフロップFF1−FF4のデータ入力Dに接続することにより形成されてもよい。

【0022】

論理回路LOGICTに太線で示した信号線は、スキャンシフト期間にスキャンフリップフロップSFF1−SFF4に伝達される信号の経路を示している。各スキャンフリップフロップSFFのスキャン入力SINは、別のスキャンフリップフロップSFFのデータ出力Qに接続される。太い信号線により、スキャンフリップフロップSFF1−SFF4は、スキャンシフト期間にシフトレジスタとして動作する。なお、スキャンシフト期間中の信号の伝達経路は、スキャンフリップフロップSFF1−SFF4の順でなくてもよい。テストの容易性を向上させるために、上述のように通常のフリップフロップFFをシフトレジスタとして動作可能なスキャンフリップフロップSFFに置き換えることをスキャン設計と称する。

【0023】

この例では、ユーザロジックUL2の出力が論理1になりやすいため、論理ゲートL2としてアンドゲートが使用される。例えば、ユーザロジックUL2の出力が論理0になりやすいとき、論理ゲートL2としてオアゲートが使用される。なお、論理ゲートL2として、アンドゲートの代わりにナンドゲートが使用されてもよく、オアゲートの代わりにノアゲートが使用されてもよい。例えば、論理回路LOGICにおいて、ユーザロジックUL2と論理ゲートL1の入力I2との間にインバータ等の反転論理が配置されている場合、論理回路LOGICTにおいて、ユーザロジックUL2と反転論理の間に、ナンドゲートまたはノアゲートが配置される。

【0024】

制御点CPは、ユーザロジックUL2の出力が論理1に設定されているときに、論理ゲートL1の入力I2を論理0に設定可能にするために設けられる。この種の制御点CPは、”0制御点”と称される。一方、ユーザロジックUL2の出力が論理0になりやすいときに挿入されるオアゲートを含む制御点は、”1制御点”と称される。制御点CPの挿入により、入力ノードI2の論理をスキャンフリップフロップSFF4により任意に設定でき、故障検出率を向上できる。

【0025】

スキャンフリップフロップSFF1−SFF4のスキャンモード入力SMには、共通のスキャンモード入力信号SMが供給される。スキャンフリップフロップSFF1−SFF4に”>”印で示すクロック入力には、共通のクロックが供給される。なお、図が複雑になることを避けるため、スキャンモード信号SMの信号線およびクロック配線の記載は省略している。

【0026】

制御点CPに形成されるスキャンフリップフロップSFF4のデータ入力Dは、制御点CP以外に形成されるスキャンフリップフロップSFF1−SFF3のいずれかのデータ出力Qに接続される。この例では、スキャンフリップフロップSFF4のデータ入力Dは、スキャンフリップフロップSFF3のデータ出力Qに接続されている。

【0027】

例えば、ユーザにより設計された論理回路LOGICへのテスト回路の挿入は、ワークステーション等のコンピュータシステムがテスト回路挿入プログラムを実行することにより実施される。換言すれば、テスト回路挿入プログラムの実行により、論理回路LOGICにテスト回路を挿入するコンピュータシステムは、テスト回路挿入装置として機能する。そして、テスト回路挿入装置の動作により、論理回路LOGICにテスト回路を挿入するテスト回路挿入方法が実施される。

【0028】

テスト回路挿入装置は、テスト回路挿入プログラムを実行することにより、以下に示す少なくとも3つの処理1−処理3を実施し、論理回路LOGICにテスト回路を挿入して論理回路LOGICTを生成する。なお、テスト回路挿入装置は、処理1、処理2をこの順で実施してもよく、逆順で実施してもよい。また、テスト回路挿入装置は、処理1、処理2を同時に実施してもよい。

(処理1)論理回路LOGICのフリップフロップFF1−FF3を、シフトレジスタとして機能させるために、データ入力Dおよびスキャン入力SINを各々有するスキャンフリップフロップSFF1−SFF3に置き換える。

(処理2)テストを容易化するために制御点CPの挿入が必要なノードと、挿入する制御点CPの論理を求める。この例では、制御点CPは、ユーザロジックUL2と論理ゲートL1との間に挿入され、データ入力Dおよびスキャン入力SINを有するスキャンフリップフロップSFF4と、論理ゲートL2とを有する。論理ゲートL2は、一対の入力がスキャンフリップフロップSFF4のデータ出力QおよびユーザロジックUL2の出力にそれぞれ接続される。

(処理3)スキャンフリップフロップSFF4のデータ入力Dに、制御点CP以外に形成されるスキャンフリップフロップSFF1−SFF3のデータ出力Qを接続する。この例では、スキャンフリップフロップSFF4のデータ入力Dは、スキャンフリップフロップSFF3のデータ出力Qに接続される。

【0029】

図2は、図1に示したテスト回路が挿入された論理回路LOGICTの故障検出方法の例を示している。例えば、図2に示す故障検出方法は、論理回路LOGICTを含む半導体集積回路の製造工程内のテスト工程において、LSI(large Scale Integration)テスタ等のテスト装置を用いて、良品と不良品とを識別するために実施される。スキャンフリップフロップSFF1、SFF2、SFF3、SFF4の中に括弧で示した論理値は、スキャン入力SINを有効にし、スキャンフリップフロップSFF1−SFF4をシフトレジスタとして動作させるスキャンシフト期間中に設定される論理値を示している。

【0030】

図2の左側は、論理ゲートL1の入力ノードI1を含む信号パス(スキャンフリップフロップSFF2のデータ出力Q以降の信号パス)の遅延故障を検出するための方法を示している。図2の右側は、論理ゲートL1の入力ノードI2を含む信号パス(論理ゲートL2の出力以降の信号パス)の遅延故障を検出するための方法を示している。

【0031】

なお、X印を付けた符号F1、F2は、遅延故障の存在を示している。但し、X印は、遅延故障F1、F2が発生している位置を示しているとは限らない。例えば、遅延故障F1は、スキャンフリップフロップSFF2のデータ出力QからスキャンフリップフロップSFF3のデータ入力Dまでの信号パスのいずれかに局所的に発生する。あるいは、遅延故障F1は、スキャンフリップフロップSFF2のデータ出力QからスキャンフリップフロップSFF3のデータ入力Dまでの信号パス上に分散して発生する。

【0032】

同様に、遅延故障F2は、論理ゲートL2の出力からスキャンフリップフロップSFF3のデータ入力Dまでの信号パスのいずれかに局所的に発生する。あるいは、遅延故障F2は、論理ゲートL2の出力からスキャンフリップフロップSFF3のデータ入力Dまでの信号パス上に分散して発生する。一般に、局所的に発生する遅延故障は遷移遅延故障と称され、分散して発生する遅延故障はパス遅延故障と称される。

【0033】

図の左側において、制御点CPに接続されない入力I1を含む信号パスの遅延故障を検出する場合、テスト装置は、スキャンシフト期間に移行するために、スキャンモード入力SMを第2論理に設定する。スキャンシフト期間では、各スキャンフリップフロップSFF1−SFF4は、クロックに同期してスキャン入力SINで受ける論理をラッチし、ラッチした論理をデータ出力Qから出力する。

【0034】

テスト装置は、スキャンシフト期間にスキャンフリップフロップSFF1−SFF4をシフト動作し、論理1、論理0、論理0、論理0を、スキャンフリップフロップSFF1、SFF2、SFF3、SFF4にそれぞれ設定する。すなわち、テスト装置は、入力I1に直列に接続される一対のスキャンフリップフロップSFF1、SFF2に互いに異なる論理を設定し、スキャンフリップフロップSFF3、SFF4に同じ論理を設定する。

【0035】

ここで、スキャンフリップフロップSFF1、SFF2は、論理0、論理1にそれぞれ設定されてもよい。スキャンフリップフロップSFF3、SFF4に設定される論理0は、ユーザロジックUL2から出力される論理に依存せず、論理ゲートL1の入力I2を論理0に固定するために必要である。入力I2を論理0に固定することにより、スキャンフリップフロップSFF2、SFF1に設定された論理0、論理1を論理ゲートL1の出力に順に伝達できる。

【0036】

次に、テスト装置は、スキャンシフト期間からキャプチャ期間に移行するために、スキャンモード入力SMを第1論理に設定する。キャプチャ期間では、各スキャンフリップフロップSFF1−SFF4は、クロックに同期してデータ入力Dで受ける論理を順にラッチし、ラッチした論理をデータ出力Qから出力する。テスト装置は、キャプチャ期間に2つのクロックパルスを発生する。論理ゲートL1の入力I1は、最初のクロックパルスにより論理0から論理1に変化する。

【0037】

遅延故障F1のない論理回路では、スキャンフリップフロップSFF3は、最初のクロックパルスに同期してスキャンフリップフロップSFF2に初期設定された論理0をラッチし、2番目のクロックパルスに同期してスキャンフリップフロップSFF1に初期設定された論理1をラッチする。

【0038】

一方、遅延故障F1のある論理回路では、スキャンフリップフロップSFF2のデータ出力Qの論理0から論理1への遷移は、スキャンフリップフロップSFF3に遅れて伝わる。このため、スキャンフリップフロップSFF3は、2番目のクロックパルスに同期してスキャンフリップフロップSFF1に初期設定された論理1をラッチできず、スキャンフリップフロップSFF2に初期設定された論理0を再びラッチする。

【0039】

この後、テスト装置は、キャプチャ期間からスキャンシフト期間に移行し、スキャンフリップフロップSFF3に保持されている論理を読み出す。そして、テスト装置は、スキャンフリップフロップSFF3に論理1が保持されているときに、遅延故障F1が存在しないことを検出し、スキャンフリップフロップSFF3に論理0が保持されているときに、遅延故障F1が存在することを検出する。すなわち、スキャンフリップフロップSFF3に保持される論理が、2番目のクロックパルスの前後で変化しないときに、入力I1を含む信号パスの遅延故障F1が検出される。

【0040】

一方、図の右側において、制御点CPに接続される入力I2を含む信号パスの遅延故障F2を検出する場合、テスト装置は、スキャンシフト期間に、論理0、論理0、論理1、論理0を、スキャンフリップフロップSFF1、SFF2、SFF3、SFF4にそれぞれ設定する。すなわち、テスト装置は、入力I1に直列に接続される一対のスキャンフリップフロップSFF1、SFF2に同じ論理を設定し、スキャンフリップフロップSFF3、SFF4に互いに異なる論理を設定する。

【0041】

ここで、スキャンフリップフロップSFF3、SFF4は、論理0、論理1にそれぞれ設定されてもよい。スキャンフリップフロップSFF1、SFF2に設定される論理0は、スキャンフリップフロップSFF4、SFF3に設定された論理0、論理1を論理ゲートL1の出力に順に伝達するために必要である。

【0042】

次に、テスト装置は、キャプチャ期間に、論理ゲートL1の入力I2を論理0から論理1に変化し、論理ゲートL1の出力値をスキャンフリップフロップSFF3にラッチするために、2つのクロックパルスを発生する。図2の左側の動作と同様に、遅延故障F2のない論理回路では、スキャンフリップフロップSFF3は、2番目のクロックパルスに同期してスキャンフリップフロップSFF1に初期設定された論理1をラッチする。一方、遅延故障F2のある論理回路では、スキャンフリップフロップSFF3は、2番目のクロックパルスに同期してスキャンフリップフロップSFF1に初期設定された論理1をラッチできず、スキャンフリップフロップSFF2に初期設定された論理0を再びラッチする。

【0043】

この後、テスト装置は、図2の左側の動作と同様に、キャプチャ期間にスキャンフリップフロップSFF3に保持されている論理を読み出す。そして、テスト装置は、スキャンフリップフロップSFF3に論理1が保持されているときに、遅延故障F2が存在しないことを検出し、スキャンフリップフロップSFF3に論理0が保持されているときに、遅延故障F2が存在することを検出する。すなわち、スキャンフリップフロップSFF3に保持される論理が、2番目のクロックパルスの前後で変化しないときに、入力I2を含む信号パスの遅延故障F2が検出される。

【0044】

なお、図2の左側の故障検出方法の実施により、遅延故障F1だけでなく、入力I1を含む信号パスの縮退故障を検出できる。図2の右側の故障検出方法の実施により、遅延故障F2だけでなく、入力I2を含む信号パスの縮退故障を検出できる。また、スキャンフリップフロップSFF1−SFF4への論理値の設定および遅延故障F1、F2の検出は、テスト装置に用いずに、論理回路LOGICTを含む半導体集積回路に搭載されるBIST(Built-In Self Test)回路等により実施されてもよい。

【0045】

以上、この実施形態では、検出する遅延故障F1、F2の位置に応じて、キャプチャ期間に制御点CPの出力の論理を固定し、あるいは論理を変化させることができる。これにより、論理ゲートL1の入力I1の論理変化を後段の論理に伝達でき、あるいは論理ゲートL1の入力I2の論理変化を後段の論理に伝達できる。この結果、論理ゲートL1の入力I1を含む信号パスの遅延故障F1と、論理ゲートL1の入力I2を含む信号パスの遅延故障F2とを、1つの制御点CPにより検出できる。すなわち、遅延故障F1、F2を1つの制御点CPにより検出できる論理回路の故障検出方法、テスト回路挿入方法およびテスト回路挿入装置を提供できる。

【0046】

図3は、論理回路の故障検出方法、論理回路のテスト回路挿入方法および論理回路のテスト回路挿入装置の別の実施形態および半導体集積回路の一実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。図3は、テスト回路の一例である制御点CPが挿入された論理回路LOGICTを示している。テスト回路を挿入前の論理回路LOGICは、図4に示す。

【0047】

この実施形態では、論理回路LOGICTは、ユーザロジックUL1、UL2、UL3、オアゲートOR1および制御点CPを有している。ユーザロジックUL1の出力は、オアゲートOR1の入力I1に接続されている。ユーザロジックUL2の出力は、制御点CPを介してオアゲートOR1の入力I2に接続されている。オアゲートOR1の出力は、ユーザロジックUL3に接続されている。

【0048】

なお、オアゲートOR1は、アンドゲート、ノアゲート、ナンドゲート等でもよい。アンドゲートおよびナンドゲートの場合、入力I2を論理1に固定し、入力I1の論理を変化させることで、入力I1を含む信号パスの遅延故障F1を検出できる。また、入力I1を論理1に固定し、入力I2の論理を変化させることで、入力I2を含む信号パスの遅延故障F2を検出できる。ノアゲートの場合、オアゲートOR1と同様に、入力I2を論理0に固定し、入力I1の論理を変化させることで、入力I1を含む信号パスの遅延故障F1を検出できる。また、入力I1を論理0に固定し、入力I2の論理を変化させることで、入力I2を含む信号パスの遅延故障F2を検出できる。遅延故障の検出方法については、図8および図9で説明する。

【0049】

例えば、ユーザロジックUL1は、複数のスキャンフリップフロップSFF(SFFa、SFFb)を含んでいる。スキャンフリップフロップSFFaのデータ出力Qは、ノードNDaを介してスキャンフリップフロップSFFbのデータ入力Dおよびスキャン入力SINに接続されている。スキャンフリップフロップSFFbのデータ出力Qは、ノードNDbを介してオアゲートOR1の入力I1およびスキャンフリップフロップSFFcのスキャン入力SINに接続されている。なお、スキャンフリップフロップSFFbのデータ出力Qは、組み合わせ回路を介して入力I1に接続されてもよい。

【0050】

例えば、ユーザロジックUL2は、複数のスキャンフリップフロップSFF(SFFc、SFFc)および組み合わせ回路等の回路CC1を含んでいる。この例では、回路CC1の出力(すなわち、ノードNDe)は、論理1になりやすいとする。換言すれば、ユーザロジックUL2の動作中に、ノードNDeが論理1になる確率は、ノードNDeが論理0になる確率よりも十分に高い。このため、ノードNDeが論理1のときにオアゲートOR1の入力I2を任意の論理に設定可能にするために、制御点CPが挿入されている。

【0051】

スキャンフリップフロップSFFcのデータ出力Qは、ノードNDcを介してスキャンフリップフロップSFFdのデータ入力Dおよびスキャン入力SINに接続されている。スキャンフリップフロップSFFdのデータ出力Qは、スキャンフリップフロップSFFfのスキャン入力SINに接続され、回路CC1を介してノードNDeに接続されている。

【0052】

例えば、ユーザロジックUL3は、組み合わせ回路等の回路CC2および少なくとも1つのスキャンフリップフロップSFFeを有している。回路CC2の入力は、ノードNDhを介してオアゲートOR1の出力に接続されている。例えば、回路CC2は、ノードNDhの論理を反転してノードNDiに出力する。スキャンフリップフロップSFFeのデータ入力Dは、ノードNDiを介して回路CC2の出力に接続されている。スキャンフリップフロップSFFeのスキャン入力SINは、スキャンフリップフロップSFFfのデータ出力Qに接続されている。スキャンフリップフロップSFFeのデータ出力Qは、ノードSOUTおよびスキャンフリップフロップSFFfのデータ入力Dに接続されている。

【0053】

制御点CPは、テスト回路の一例であり、スキャンフリップフロップSFFf、ナンドゲートNAND1およびアンドゲートAND1を有している。スキャンフリップフロップSFFfのデータ出力Qは、ナンドゲートNAND1の一方の入力およびスキャンフリップフロップSFFeのスキャン入力SINに接続されている。ナンドゲートNAND1の他方の入力は、テストモード信号を受けるテストモード端子TMに接続されている。ナンドゲートNAND1の出力は、ノードNDfを介してアンドゲートAND1の一方の入力に接続されている。アンドゲートAND1の他方の入力は、ノードNDeを介して回路CC1の出力に接続されている。アンドゲートAND1の出力は、ノードNDgを介してオアゲートOR1の入力I2に接続されている。

【0054】

この例では、テストモード端子TMは、遅延故障を検出するためのテストモード中に論理1に設定され、論理回路LOGICTがユーザシステムの一部として動作するシステムモード中に論理0に設定される。テストモード端子TMの論理1により、ナンドゲートNAND1の信号伝達機能は有効になり、ナンドゲートNAND1は、スキャンフリップフロップSFFfの出力Qの論理を反転してアンドゲートAND1に出力する。一方、テストモード端子TMの論理0により、ナンドゲートNAND1の信号伝達機能は無効になり、ナンドゲートNAND1の出力であるノードNDfは論理1に固定される。

【0055】

これにより、システムモード中(TM=論理0)に、データ入力Dで受ける論理に応じて動作するスキャンフリップフロップSFFfのデータ出力Qの論理がアンドゲートAND1に伝達されることを防止でき、ユーザロジックUL3等の誤動作を防止できる。ナンドゲートNAND1がノードNDfに論理1を出力することで、回路CC1の出力であるノードNDeの論理は、アンドゲートAND1を介してオアゲートOR1に伝達される。このように、スキャンフリップフロップSFFfをテストモード信号TMにより制御されるナンドゲートNAND1を介してアンドゲートAND1に接続することで、システムモード中のスキャンフリップフロップSFFfの動作による誤動作を防止できる。

【0056】

図1と同様に、太線で示した信号線は、スキャンシフト期間にスキャンフリップフロップSFFa、SFFb、SFFc、SFFd、SFFf、SFFeに伝達される信号の経路を示している。X印を付けた符号F1、F2は、遅延故障の存在を示している。但し、遅延故障F1、F2は、確率的に同時に発生しないものとして扱われる。また、図2で説明したように、X印は、遅延故障F1、F2が発生している位置を示しているとは限らない。

【0057】

なお、各スキャンフリップフロップSFFa−SFFfは、データ入力またはスキャン入力のいずれかを選択するマルチプレクサを、フリップフロップのデータ入力に接続することにより形成されてもよい。

【0058】

図4は、図3に示した論理回路LOGICTにテスト回路を挿入する前の論理回路LOGICの例を示している。論理回路LOGICは、ユーザにより設計された回路である。論理回路LOGICは、図3のスキャンフリップフロップSFFa、SFFb、SFFc、SFFd、SFFeの代わりにフリップフロップFFa、FFb、FFc、FFd、FFeが配置されている。論理回路LOGICは、制御点CPを含まない。このため、論理回路LOGICでは、ユーザロジックUL2の出力は、オアゲートOR1の入力I2に直接接続されている。

【0059】

図5は、図4に示した論理回路LOGICから図3に示した論理回路LOGICTを生成するテスト回路挿入装置CADの例を示している。例えば、テスト回路挿入装置CADは、ワークステーション等のコンピュータシステムにより実現される。

【0060】

テスト回路挿入装置CADは、図3に示した制御点CP等のテスト回路を挿入するテスト回路挿入プログラム等を記憶するメモリ装置MEMと、テスト回路挿入プログラムを実行するプロセッサCPUとを有している。メモリ装置MEMは、例えば、半導体メモリ装置やハードディスクドライブ装置である。テスト回路挿入装置CADは、ディスプレイDISP、キーボードやマウス等の入力デバイスINPUT、ディスクドライブ装置DRVおよび入出力デバイスINOUTを有している。

【0061】

ディスプレイDISPは、入力デバイスINPUTおよびディスクドライブ装置DRVから入力された情報や、テスト回路挿入プログラムにより生成された論理回路LOGICTの論理図やネットリスト等を表示する。ディスクドライブ装置DRVには、テスト回路挿入プログラムあるいは図4に示した論理回路LOGICのネットリストが記録されたCD−ROM、DVD等の記録媒体がセットされる。テスト回路挿入プログラムやネットリストは、ディスクドライブ装置DRVを介してメモリ装置MEMにダウンロードされる。

【0062】

そして、プロセッサCPUがテスト回路挿入プログラムを実行することにより、テスト回路挿入方法が実施され、図4の論理回路LOGICから図3の論理回路LOGICT(ネットリスト)が生成される。生成されたネットリストは、メモリ装置MEMからメモリカード等のシリコンディスク、磁気テープ装置、あるいはハードディスクドライブ装置等の入出力デバイスINOUTに書き込まれる。

【0063】

なお、ディスクドライブ装置DRVの代わりに、入出力デバイスINOUTを用いて、テスト回路挿入プログラムやネットリストをメモリ装置MEMに転送してもよい。あるいは、テスト回路挿入プログラムやネットリストは、ネットワークを介してメモリ装置MEMに入出力されてもよい。

【0064】

図6は、図5に示したテスト回路挿入装置CADの動作の例を示している。図6は、テスト回路挿入方法のフローを示しており、テスト回路挿入装置CADがテスト回路挿入プログラムを実行することにより実現される。

【0065】

先ず、ステップS10において、テスト回路挿入装置CADは、ユーザにより設計された論理回路LOGICのネットリストを解析し、制御点CPの挿入が必要なノードと、挿入する制御点CPの論理を求める。テスト回路挿入装置CADは、必要に応じて、観測点の挿入が必要な挿入するノードと、挿入する観測点の論理を求める。観測点は、テスト回路の一種であり、遅延故障を検出するための論理値を得るために挿入が必要なスキャンフリップフロップ等である。求めた制御点CPの情報および観測点の情報は、挿入されるテスト回路の情報としてメモリ装置MEM等に書き込まれる。

【0066】

次に、ステップS20において、テスト回路挿入装置CADは、求めた制御点CPの情報に基づいて、制御点CPのスキャンフリップフロップSFF(例えば、図3のSFFf)のデータ入力Dに接続するスキャンフリップフロップSFFを選択する。例えば、ステップS20では、制御点CPの下流側(出力側)が順に探索され、制御点CPからの論理段数が最も少ないスキャンフリップフロップSFFが選択される。あるいは、制御点CPの上流側(入力側)が順に探索され、制御点CPからの論理段数が最も少ないスキャンフリップフロップSFFが選択される。これにより、制御点CPのスキャンフリップフロップSFFのデータ入力Dは、制御点CP以外に形成されるスキャンフリップフロップSFFのいずれかのデータ出力Qに接続される。選択されたスキャンフリップフロップSFFの情報は、メモリ装置MEM等に書き込まれる。

【0067】

次に、ステップS30において、テスト回路挿入装置CADは、論理回路LOGICのネットリストを用いて、ネットリスト上のフリップフロップFFをスキャンフリップフロップSFFに置き換える。次に、テスト回路挿入装置CADは、制御点CPの情報を用いて、ネットリスト上に制御点CPを挿入する。また、テスト回路挿入装置CADは、ステップS20で選択したスキャンフリップフロップSFFの情報を用いて、挿入した制御点CPのスキャンフリップフロップSFF(図3のSFFf)のデータ入力Dに、選択したスキャンフリップフロップSFFのデータ出力Qを接続する。そして、図3に示した論理回路LOGICT(ネットリスト)が生成される。

【0068】

テスト回路挿入装置CADは、必要に応じて、観測点の情報に基づいて、ネットリスト上に観測点を挿入する。テスト回路挿入装置CADは、テスト回路が挿入された論理回路LOGICTのネットリストを生成する。そして、生成されたネットリストを用いて、トランジスタ等の素子の配置および素子間の配線を実施するプログラムが実行され、半導体集積回路LSIを製造するためのフォトマスクのデータが生成される。素子の配置、配線およびフォトマスクのデータ生成は、テスト回路挿入装置CADが別のプログラムを実行することで実施されてもよく、大型計算機等を用いて実施されてもよい。

【0069】

この後、フォトマスクのデータを用いてフォトマスクが製作され、フォトマスクを用いて半導体製造工程が実施され、図3に示した論理回路LOGICTを有する半導体集積回路LSIが製造される。製造された半導体集積回路LSIは、図7に示すテストシステムTSYSによりテストされ、遅延故障の有無が検出される。

【0070】

図7は、図3に示した論理回路LOGICTを有する半導体集積回路LSIをテストするテストシステムTSYSの例を示している。なお、後述する実施形態においても、図7と同じテストシステムTSYSが使用される。テストシステムTSYSは、半導体集積回路LSIの製造工程におけるテスト工程で使用される。

【0071】

まず、半導体製造工程により半導体ウエハWAF上に複数の半導体集積回路LSIが形成される。半導体集積回路LSIは、ウエハWAFから切り出される前にテスタTEST等のテスト装置によりテストされる。テストシステムTSYSによる半導体集積回路LSIのテストにより、論理回路LOGICTの故障検出方法が実現される。すなわち、テスタTESTは、論理回路LOGICTの故障検出装置として動作する。

【0072】

半導体集積回路LSIは、例えば、プローブカードのプローブPRBを介してテスタTESTに接続される。図7では、1つの半導体集積回路LSIがテスタTESTに接続されているが、複数の半導体集積回路LSIをテスタTESTに一度に接続してもよい。テスタTESTに一度に接続する半導体集積回路LSIの数は、テスタTESTの端子数と半導体集積回路LSIの端子数に依存する。

【0073】

例えば、テスタTESTは、論理回路LOGICTの遅延故障を検出するための故障検出プログラムを実行し、クロックCLK、テストモード信号TM、スキャンモード入力信号SMおよびスキャン入力信号SINを半導体集積回路LSIに出力する。そして、テスタTESTは、論理回路LOGICT内の所定のスキャンフリップフロップSFF(例えば、図3のSFFe)に保持されている論理をスキャンアウト端子SOUTを介して読み出し、遅延故障の有無を検出する。遅延故障が検出された半導体集積回路LSIは、不良品として扱われる。なお、テスタTESTは、パッケージングされた半導体集積回路LSIをテストするために使用されてもよい。

【0074】

図8は、図3に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図8の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図3に示した遅延故障F1を検出するために実施される。換言すれば、図8は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。

【0075】

図8および以降の波形図において、1番目から6番目のクロックサイクルおよび9番目のクロックサイクルは、スキャンモード入力SMが論理1に設定されるスキャンシフト期間を示している。7番目および8番目のクロックサイクルは、スキャンモード入力SMが論理0に設定されるキャプチャ期間を示している。7番目のクロックサイクルの長さは、遅延故障F1またはF2を判断する信号パスの遅延時間に合わせて設定される。換言すれば、信号パスの遅延時間が7番目のクロックサイクルの長さより長いときに、遅延故障F1またはF2の発生が検出される。ここで、7番目のクロックサイクルの長さは、7番目のクロックCLKの立ち上がりエッジから8番目のクロックCLKの立ち上がりエッジまでの期間である。また、スキャンフリップフロップSFFfから出力される論理(遷移エッジ)をオアゲートOR1に伝達するために、テストモード端子TMはテストモード中に論理1に設定される。7番目から9番目のクロックサイクルにおいて、破線で示した波形は、遅延故障が存在するときの動作を示している。

【0076】

この例では、スキャンフリップフロップSFFe、SFFf、SFFd、SFFc、Sffb、Sffaに所望の論理を設定するために、1番目から6番目のクロックサイクルにおいてスキャン入力SINに論理1、論理1、論理0、論理0、論理0、論理1が順に供給される。スキャン入力SINの波形上に示したスキャンフリップフロップ名は、6番目のクロックサイクルで設定される論理との対応を示している。キャプチャ期間の直前の6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFeは、論理0、論理1、論理1、論理1にそれぞれ設定される。

【0077】

すなわち、6番目のクロックサイクルにおいて、オアゲートOR1の入力I1にデータ入力D経由で直列に接続されるスキャンフリップフロップSFFb、SFFaは、互いに異なる論理を保持する。これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFbに保持される論理を論理0から論理1に変化でき、オアゲートOR1の入力I1を論理0から論理1に変化できる。

【0078】

また、6番目のクロックサイクルにおいて、ナンドゲートNAND1およびアンドゲートAND1を介し、かつデータ入力D経由でオアゲートOR1の入力I2に直列に接続されるスキャンフリップフロップSFFf、SFFeは、互いに同じ論理を保持する。これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFfに保持される論理を、1クロックサイクル前にスキャンフリップフロップSFFeに保持されている論理を用いて論理1に維持できる。したがって、スキャンフリップフロップSFFfの出力ノードに接続されるオアゲートOR1の入力I2を論理0に維持できる。なお、スキャンフリップフロップSFFfに保持されている論理は、ナンドゲートNAND1により反転されて、ノードNDfおよびオアゲートOR1の入力I2に伝達される。

【0079】

遅延故障F1が存在しないとき、スキャンフリップフロップSFFbの論理変化は、オアゲートOR1の入力I1、オアゲートOR1の出力ノードNDhに直ちに伝達される。回路CC2は、出力ノードNDhの論理0から論理1への変化に応答して、出力ノードNDiを論理1から論理0に直ちに変化する。このため、スキャンフリップフロップSFFeは、キャプチャ期間の8番目のクロックサイクルにおいて、論理0をラッチし、ラッチした論理0をスキャンアウト端子SOUTに出力する。そして、スキャンシフト期間の9番目のクロックサイクルにおいて、図7に示したテスタTESTは、スキャンアウト端子SOUTの論理0を読み込むことにより、遅延故障F1が存在しないことを検出する。

【0080】

なお、実際の回路では、スキャンフリップフロップSFFeの出力は、複数のスキャンフリップフロップを介してスキャンアウト端子SOUTに接続されることが多い。この場合、スキャンアウト端子SOUTは、例えば、シフトレジスタを構成する最終のスキャンフリップフロップの出力Qに接続され、遅延故障F1の有無は、9番目のクロックサイクルより後のクロックサイクルで判定される。

【0081】

一方、遅延故障F1が存在するとき、スキャンフリップフロップSFFbの論理変化は、破線で示すように、オアゲートOR1の入力I1、オアゲートOR1の出力ノードNDhあるいは回路CC2の出力ノードNDiに遅れて伝達される。信号の遅延により、キャプチャ期間の8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeがノードNDiの論理0をラッチできないとき、スキャンアウト端子SOUTは論理1に維持される。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理1を読み込むことにより、遅延故障F1が存在することを検出する。

【0082】

図9は、図3に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図9の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図3に示した遅延故障F2を検出するために実施される。換言すれば、図9は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8と同じ動作については、詳細な説明は省略する。

【0083】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理0、論理1、論理0、論理0、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFeは、論理0、論理0、論理1、論理0にそれぞれ設定される。すなわち、6番目のクロックサイクルにおいて、オアゲートOR1の入力I1に直列に接続されるスキャンフリップフロップSFFb、SFFaは、互いに同じ論理を保持する。ナンドゲートNAND1およびアンドゲートAND1を介してオアゲートOR1の入力I2に直列に接続されるスキャンフリップフロップSFFf、SFFeは、互いに異なる論理を保持する。

【0084】

これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFfに保持される論理を、1クロックサイクル前にスキャンフリップフロップSFFeに保持されている論理を用いて、論理1から論理0に変更できる。スキャンフリップフロップSFFeに保持されている論理は、ナンドゲートNAND1により反転される。すなわち、7番目のクロックサイクルにおいて、オアゲートOR1の入力I1を論理0に維持した状態で、オアゲートOR1の入力I2を論理0から論理1に変化できる。

【0085】

遅延故障F2が存在しないとき、スキャンフリップフロップSFFfの論理変化は、オアゲートOR1の入力I2および出力ノードNDhに直ちに伝達される。図8と同様に、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて論理0をラッチし、テスタTESTは、9番目のクロックサイクルにおいてスキャンアウト端子SOUTの論理0を読み込む。これにより、遅延故障F2が存在しないことが検出される。

【0086】

一方、遅延故障F2が存在するとき、破線で示すように、スキャンフリップフロップSFFfの論理変化は、オアゲートOR1の入力I1、オアゲートOR1の出力ノードNDhあるいは回路CC2の出力ノードNDiに遅れて伝達される。そして、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeがノードNDiの論理0をラッチできないとき、スキャンアウト端子SOUTは論理1に維持される。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理1を読み込むことにより、遅延故障F2が存在することを検出する。

【0087】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。さらに、論理ゲートL1の入力I1を含む信号パスの遅延故障F1と、論理ゲートL1の入力I2を含む信号パスの遅延故障F2とを、1つの制御点CPにより検出できる半導体集積回路LSIを提供できる。また、スキャンフリップフロップSFFfのデータ出力Qを、テストモード信号TMにより制御されるナンドゲートNAND1を介してアンド回路AND1に接続することで、システムモード中にスキャンフリップフロップSFFfのデータ出力Qの論理がアンドゲートAND1に伝達されることを防止できる。この結果、論理回路LOGICTが誤動作することを防止できる。

【0088】

図10は、論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。

【0089】

この実施形態の論理回路LOGICTは、図3の回路CC1の代わりに回路CC3を有している。また、制御点CPは、図3に示したナンドゲートNAND1の代わりにアンドゲートAND2を有し、図3に示したアンドゲートAND1の代わりにオアゲートOR2を有している。論理回路LOGICTのその他の構成は、図3と同様である。図10の論理回路LOGICは、図5に示したテスト回路挿入装置CADがテスト回路挿入プログラムを実行し、図6に示した処理を実施することにより生成される。

【0090】

この実施形態では、回路CC3の出力(すなわち、ノードNDe)は、論理0になりやすいとする。換言すれば、ユーザロジックUL2の動作中に、ノードNDeが論理0になる確率は、ノードNDeが論理1になる確率よりも十分に高い。このため、オアゲートOR1の入力I2を任意の論理に設定可能にし、故障検出率を向上するために、図3と異なる制御点CPが挿入されている。制御点CPのオアゲートOR2は、回路CC3の出力が論理0に設定されているときに、オアゲートL1の入力I2を論理1に設定可能にするために設けられる。

【0091】

テストモード中(TM=論理1)、アンドゲートAND2の信号伝達機能は有効になり、アンドゲートAND2は、スキャンフリップフロップSFFfの出力Qの論理をオアゲートOR2に出力する。一方、システムモード中(TM=論理0)、アンドゲートAND2の信号伝達機能は無効になり、アンドゲートAND2の出力であるノードNDfは論理0固定される。これにより、システムモード中に、データ入力Dで受ける論理に応じて動作するスキャンフリップフロップSFFfのデータ出力Qの論理がオアゲートOR2に伝達されることを防止でき、ユーザロジックUL3等の誤動作を防止できる。アンドゲートAND2がノードNDfに論理0を出力することで、回路CC3の出力であるノードNDeの論理は、オアゲートOR2を介してオアゲートOR1に伝達される。このように、スキャンフリップフロップSFFfをテストモード信号TMにより制御されるアンドゲートAND2を介してオアゲートOR2に接続することで、システムモード中のスキャンフリップフロップSFFfの動作による誤動作を防止できる。

【0092】

図11は、図10に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図11の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図10に示した遅延故障F1を検出するために実施される。換言すれば、図11は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8と同じ動作については、詳細な説明は省略する。

【0093】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理0、論理0、論理0、論理0、論理0、論理1が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFeは、論理0、論理1、論理0、論理0にそれぞれ設定される。すなわち、6番目のクロックサイクルにおいて、オアゲートOR1の入力I1に直列に接続されるスキャンフリップフロップSFFb、SFFaは、互いに異なる論理を保持する。これにより、図8と同様に、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFbに保持される論理を論理0から論理1に変化でき、オアゲートOR1の入力I1を論理0から論理1に変化できる。

【0094】

6番目のクロックサイクルにおいて、アンドゲートAND2およびオアゲートOR2を介してオアゲートOR1の入力I2に直列に接続されるスキャンフリップフロップSFFf、SFFeは、互いに同じ論理を保持する。これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFfに保持される論理を、1クロックサイクル前にスキャンフリップフロップSFFeに保持されている論理を用いて論理0に維持できる。ここで、図10の制御点CPは、ナンドゲートNAND1(図3)の代わりにアンドゲートAND2を有しているため、制御点CPを”0制御点”として動作させるために、スキャンフリップフロップSFFf、SFFeは、論理0を設定される。制御点CPにより、スキャンフリップフロップSFFfの出力ノードに接続されるオアゲートOR1の入力I2を論理0に維持できる。

【0095】

遅延故障F1が存在しないとき、図8と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiの論理変化として直ちに現れる。スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチし、ラッチした論理0をスキャンアウト端子SOUTに出力する。図7に示したテスタTESTは、スキャンアウト端子SOUTの論理0を読み込むことにより、遅延故障F1が存在しないことを検出する。

【0096】

一方、遅延故障F1が存在するとき、図8と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiに遅れて伝達される。8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeがノードNDiの論理0をラッチできないとき、スキャンアウト端子SOUTは論理1に維持される。図7に示したテスタTESTは、スキャンアウト端子SOUTの論理1を読み込むことにより、遅延故障F1が存在することを検出する。

【0097】

図12は、図10に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図12の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図10に示した遅延故障F2を検出するために実施される。換言すれば、図12は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8および図9と同じ動作については、詳細な説明は省略する。

【0098】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理0、論理0、論理0、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFeは、論理0、論理0、論理0、論理1にそれぞれ設定される。すなわち、6番目のクロックサイクルにおいて、オアゲートOR1の入力I1に直列に接続されるスキャンフリップフロップSFFb、SFFaは、互いに同じ論理を保持する。アンドゲートAND2およびオアゲートOR2を介してオアゲートOR1の入力I2に直列に接続されるスキャンフリップフロップSFFf、SFFeは、互いに異なる論理を保持する。

【0099】

これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFfに保持される論理を、1クロックサイクル前にスキャンフリップフロップSFFeに保持されている論理を用いて、論理0から論理1に変更できる。すなわち、7番目のクロックサイクルにおいて、オアゲートOR1の入力I1を論理0に維持した状態で、オアゲートOR1の入力I2を論理0から論理1に変化できる。

【0100】

遅延故障F2が存在しないとき、スキャンフリップフロップSFFfの論理変化は、オアゲートOR1の入力I2およびノードNDh、NDiに直ちに伝達される。スキャンフリップフロップSFFeは、図9と同様に、8番目のクロックサイクルにおいて論理0をラッチし、テスタTESTは、9番目のクロックサイクルにおいてスキャンアウト端子SOUTの論理0を読み込む。これにより、遅延故障F2が存在しないことが検出される。

【0101】

一方、遅延故障F2が存在するとき、スキャンフリップフロップSFFfの論理変化は、オアゲートOR1の入力ノードI2、オアゲートOR1の出力ノードNDhあるいは回路CC2の出力ノードNDiに遅れて伝達される。そして、図9と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeがノードNDiの論理0をラッチできないとき、スキャンアウト端子SOUTは論理1に維持される。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理1を読み込むことにより、遅延故障F2が存在することを検出する。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0102】

図13は、論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。

【0103】

この実施形態の論理回路LOGICTでは、制御点CPのスキャンフリップフロップSFFfのデータ入力Dは、図3に示したスキャンフリップフロップSFFeのデータ出力Qではなく、スキャンフリップフロップSFFdのデータ出力Qに接続されている。論理回路LOGICTのその他の構成は、図3と同様である。図13の論理回路LOGICは、図5に示したテスト回路挿入装置CADがテスト回路挿入プログラムを実行し、図6に示した処理を実施することにより生成される。

【0104】

図14は、図13に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図14の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図13に示した遅延故障F1を検出するために実施される。換言すれば、図14は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8と同じ動作については、詳細な説明は省略する。

【0105】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理1、論理1、論理1、論理0、論理1が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFdは、論理0、論理1、論理1、論理1にそれぞれ設定される。そして、遅延故障F1が存在しないとき、図8と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F1が存在するとき、図8と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F1の有無を検出する。

【0106】

図15は、図13に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図15の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図13に示した遅延故障F2を検出するために実施される。換言すれば、図15は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8および図9と同じ動作については、詳細な説明は省略する。

【0107】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理1、論理0、論理0、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFdは、論理0、論理0、論理1、論理0にそれぞれ設定される。そして、遅延故障F2が存在しないとき、図9と同様に、スキャンフリップフロップSFFfの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F2が存在するとき、図9と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F2の有無を検出する。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0108】

図16は、論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。

【0109】

この実施形態の論理回路LOGICTでは、制御点CPのスキャンフリップフロップSFFfのデータ入力Dは、図10に示したスキャンフリップフロップSFFeのデータ出力Qではなく、スキャンフリップフロップSFFdのデータ出力Qに接続されている。論理回路LOGICTのその他の構成は、図10と同様である。図16の論理回路LOGICは、図5に示したテスト回路挿入装置CADがテスト回路挿入プログラムを実行し、図6に示した処理を実施することにより生成される。

【0110】

図17は、図16に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図17の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図16に示した遅延故障F1を検出するために実施される。換言すれば、図17は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8および図11と同じ動作については、詳細な説明は省略する。

【0111】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理0、論理0、論理0、論理0、論理0、論理1が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFdは、論理0、論理1、論理0、論理0にそれぞれ設定される。そして、遅延故障F1が存在しないとき、図11と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F1が存在するとき、図11と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F1の有無を検出する。

【0112】

図18は、図16に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図18の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図16に示した遅延故障F2を検出するために実施される。換言すれば、図15は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8、図9および図12と同じ動作については、詳細な説明は省略する。

【0113】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理0、論理0、論理1、論理1、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFdは、論理0、論理0、論理0、論理1にそれぞれ設定される。そして、遅延故障F2が存在しないとき、図12と同様に、スキャンフリップフロップSFFfの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F2が存在するとき、図12と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F2の有無を検出する。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0114】

図19は、論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。

【0115】

この実施形態の論理回路LOGICTでは、制御点CPのスキャンフリップフロップSFFfのデータ入力Dは、図3に示したスキャンフリップフロップSFFeのデータ出力Qではなく、スキャンフリップフロップSFFcのデータ出力Qに接続されている。論理回路LOGICTのその他の構成は、図3と同様である。図19の論理回路LOGICは、図5に示したテスト回路挿入装置CADがテスト回路挿入プログラムを実行し、図6に示した処理を実施することにより生成される。

【0116】

図20は、図19に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図20の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図19に示した遅延故障F1を検出するために実施される。換言すれば、図20は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8および図14と同じ動作については、詳細な説明は省略する。

【0117】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理1、論理1、論理1、論理0、論理1が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFcは、論理0、論理1、論理1、論理1にそれぞれ設定される。そして、遅延故障F1が存在しないとき、図14と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F1が存在するとき、図14と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F1の有無を検出する。

【0118】

図21は、図19に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図21の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図19に示した遅延故障F2を検出するために実施される。換言すれば、図21は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8、図9および図15と同じ動作については、詳細な説明は省略する。

【0119】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理1、論理0、論理0、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFcは、論理0、論理0、論理1、論理0にそれぞれ設定される。そして、遅延故障F2が存在しないとき、図15と同様に、スキャンフリップフロップSFFfの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F2が存在するとき、図15と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F2の有無を検出する。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0120】

以上の詳細な説明により、実施形態の特徴点および利点は明らかになるであろう。これは、特許請求の範囲がその精神および権利範囲を逸脱しない範囲で前述のような実施形態の特徴点および利点にまで及ぶことを意図するものである。また、当該技術分野において通常の知識を有する者であれば、あらゆる改良および変更に容易に想到できるはずであり、発明性を有する実施形態の範囲を前述したものに限定する意図はなく、実施形態に開示された範囲に含まれる適当な改良物および均等物に拠ることも可能である。

【符号の説明】

【0121】

CAD‥テスト回路挿入装置;CC1、CC2‥回路;CP‥制御点;CPU‥プロセッサ;DISP‥ディスプレイ;DRV‥ディスクドライブ装置;FF1−FF4、FFa−FFf‥フリップフロップ;INOUT‥入出力デバイス;INPUT‥入力デバイス;L1、L2‥論理ゲート;LSI‥半導体集積回路;LOGIC、LOGICT‥論理回路;MEM‥メモリ装置;PRB‥プローブ;SFF1−SFF4、SFFa−SFFf‥スキャンフリップフロップ;SIN‥スキャン入力;SM‥スキャンモード入力;TEST‥テスタ;TSYS‥テストシステム;UL1、UL2、UL3‥ユーザロジック;WAF‥半導体ウエハ

【技術分野】

【0001】

本発明は、論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路に関する。

【背景技術】

【0002】

ロジックLSI(Large Scale Integration)等の論理回路を含む半導体集積回路では、故障検出率を向上するために、テスト回路である観測点や制御点が論理回路中に挿入される。観測点は、所定のノードの信号値を観測するために論理回路中に挿入され、制御点は、所定のノードに信号値を与えるために論理回路中に挿入される。例えば、観測点または制御点を挿入するときの故障検出率をそれぞれ求め、単位面積当たりの故障検出率の向上効果が高いテスト回路を論理回路内に挿入する手法が提案されている(例えば、特許文献1参照。)。

【0003】

また、論理回路中の全てのフリップフロップをスキャンフリップフロップに置き換えるフルスキャン設計において、テストパターン数が所定値を超える回路ブロックに観測点や制御点を挿入する手法が提案されている(例えば、特許文献2参照。)。マクロとユーザロジックとの間の遅延故障を検出するために、マクロの入力端子に接続された制御点にトグル動作する機能を追加する手法が提案されている(例えば、特許文献3参照。)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−84427号公報

【特許文献2】特開2001−312529号公報

【特許文献3】特開2009−205414号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

論理ゲートの一方の入力にユーザロジックの出力が接続され、論理ゲートの他方の入力に制御点を介して別のユーザロジックの出力が接続される場合、一方の入力を含む信号パスの遅延故障と、他方の入力を含む信号パスの遅延故障とを、1つの制御点を用いて検出できない。具体的には、一方の入力を含む信号パスの遅延故障を検出するために、出力論理を固定する機能を有する制御点を設ける場合、制御点から互いに異なる論理を連続して出力できないため、他方の入力を含む信号パスの遅延故障を検出できない。また、他方の入力を含む信号パスの遅延故障を検出するために、出力論理を順に変化する機能を有する制御点を設ける場合、制御点から同じ論理を連続して出力できないため、一方の入力を含む信号パスの遅延故障を検出できない。

【0006】

本発明の目的は、論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出できる論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路を提供することである。

【課題を解決するための手段】

【0007】

本発明の論理回路の故障検出方法の一形態では、データ入力およびスキャン入力を有する複数の第1スキャンフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、少なくとも1つの第1スキャンフリップフロップを含み、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有し、制御点は、第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する論理回路の故障検出方法であって、スキャン入力を有効にし、第1および第2スキャンフリップフロップをシフトレジスタとして動作させるスキャンシフト期間に、第1スキャンフリップフロップの1つおよび第2スキャンフリップフロップに同じ論理を設定し、第1入力に直列に接続される一対の第1スキャンフリップフロップに互いに異なる論理を設定し、データ入力を有効にするキャプチャ期間に、第1および第2スキャンフリップフロップに2つのクロックパルスを供給し、第3ユーザロジックの第1スキャンフリップフロップに保持される論理が変化しないときに第1入力を含む信号パスの遅延故障を検出することを特徴とする。

【0008】

本発明の論理回路のテスト回路挿入方法の一形態では、複数のフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力および第2ユーザロジックの出力に接続される第2入力を有する第1論理ゲートと、第1論理ゲートの出力に接続され、少なくとも1つのフリップフロップを含む第3ユーザロジックとを有する論理回路のテスト回路挿入方法であって、フリップフロップをデータ入力およびスキャン入力を各々有する第1スキャンフリップフロップに置き換える処理と、データ入力およびスキャン入力を有する第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第2入力に接続された第2論理ゲートとを有する制御点を、第2ユーザロジックと第1論理ゲートとの間に挿入する処理と、第2スキャンフリップフロップのデータ入力に第1スキャンフリップフロップの1つのデータ出力を接続する処理とを含むことを特徴とする。

【0009】

本発明の論理回路のテスト回路挿入装置の一形態では、複数のフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力および第2ユーザロジックの出力に接続される第2入力を有する第1論理ゲートと、第1論理ゲートの出力に接続され、少なくとも1つのフリップフロップを含む第3ユーザロジックとを有する論理回路のテスト回路挿入装置であって、フリップフロップをデータ入力およびスキャン入力を各々有する第1スキャンフリップフロップに置き換える処理と、データ入力およびスキャン入力を有する第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第2入力に接続された第2論理ゲートとを有する制御点を、第2ユーザロジックと第1論理ゲートとの間に挿入する処理と、第2スキャンフリップフロップのデータ入力に第1スキャンフリップフロップの1つのデータ出力を接続する処理とを実施することを特徴とする。

【0010】

本発明の半導体集積回路の一形態では、データ入力およびスキャン入力を有する複数の第1スキャンフリップフロップをそれぞれ含む第1ユーザロジックと、第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、少なくとも1つの第1スキャンフリップフロップを含み、第1論理ゲートの出力に接続された第3ユーザロジックと、第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力およびテストモードを示すテストモード端子に接続されたマスク回路と、一対の入力がマスク回路の出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する制御点とを備え、マスク回路は、テストモード中に、第2スキャンフリップフロップからの出力信号を第2論理ゲートに伝達し、テストモードを除く期間に、出力信号の第2論理ゲートへの伝達をマスクするとともに、第2ユーザロジックからの出力信号を第2論理ゲートを介して第1論理ゲートに伝達するための論理値を第2論理ゲートに出力することを特徴とする。

【発明の効果】

【0011】

第1論理ゲートの第1入力を含む信号パスの遅延故障と、第1論理ゲートの第2入力を含む信号パスの遅延故障とを、1つの制御点により検出できる。

【図面の簡単な説明】

【0012】

【図1】論理回路の故障検出方法、論理回路のテスト回路挿入方法および論理回路のテスト回路挿入装置の一実施形態を示している。

【図2】図1に示したテスト回路が挿入された論理回路の故障検出方法の例を示している。

【図3】論理回路の故障検出方法、論理回路のテスト回路挿入方法および論理回路のテスト回路挿入装置の別の実施形態および半導体集積回路の一実施形態を示している。

【図4】図3に示した論理回路にテスト回路を挿入する前の論理回路の例を示している。

【図5】図4に示した論理回路から図3に示した論理回路を生成するテスト回路挿入装置の例を示している。

【図6】図5に示したテスト回路挿入装置の動作の例を示している。

【図7】図3に示した論理回路を有する半導体集積回路をテストするテストシステムの例を示している。

【図8】図3に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図9】図3に示した論理回路の遅延故障を検出するためのテストの別の例を示している。

【図10】論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。

【図11】図10に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図12】図10に示した論理回路の遅延故障を検出するためのテストの別の例を示している。

【図13】論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。

【図14】図13に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図15】図13に示した論理回路の遅延故障を検出するためのテストの別の例を示している。

【図16】論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。

【図17】図16に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図18】図16に示した論理回路の遅延故障を検出するためのテストの別の例を示している。

【図19】論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。

【図20】19に示した論理回路の遅延故障を検出するためのテストの例を示している。

【図21】図19に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。

【発明を実施するための形態】

【0013】

以下、図面を用いて実施形態を説明する。図中、信号が伝達される信号線には、信号名と同じ符号を使用する。

【0014】

図1は、論理回路の故障検出方法、論理回路のテスト回路挿入方法および論理回路のテスト回路挿入装置の一実施形態を示している。図1の左側は、ユーザにより設計された論理回路LOGICの例を示している。図1の右側は、論理回路LOGICにテスト回路を挿入することで生成された論理回路LOGICTの例を示している。

【0015】

論理回路LOGICは、ユーザロジックUL1、UL2、UL3および論理ゲートL1を有している。ユーザロジックUL1は、複数のフリップフロップFF(FF1、FF2)を含んでいる。ユーザロジックUL3は、少なくとも1つのフリップフロップFF3を含んでいる。フリップフロップFF1−FF5は、”>”印で示すクロック入力で共通のクロックを受けて動作する。なお、図が複雑になることを避けるため、クロック配線は省略している。

【0016】

ユーザロジックUL1、UL2の出力は、論理ゲートL1の入力I1、I2にそれぞれ接続されている。論理ゲートL1の出力は、ユーザロジックUL3の入力に接続されている。なお、論理ゲートL1は、オアゲートに限定されず、アンドゲート、ノアゲート、ナンドゲート等でもよい。

【0017】

例えば、フリップフロップFF1のデータ出力Qは、フリップフロップFF2のデータ入力Dに接続されている。フリップフロップFF2のデータ出力Qは、論理ゲートL1の入力I1に接続されている。すなわち、フリップフロップFF1、FF2は、直列に接続されている。なお、フリップフロップFF1のデータ出力Qは、組み合わせ回路を介してフリップフロップFF2のデータ入力Dに接続されてもよい。フリップフロップFF2のデータ出力Qは、組み合わせ回路を介して入力I1に接続されてもよい。論理ゲートL1の出力は、フリップフロップFF3のデータ入力Dに接続されている。なお、論理ゲートL1の出力は、組み合わせ回路を介してフリップフロップFF3のデータ入力Dに接続されてもよい。

【0018】

この例では、ユーザロジックUL2の出力(すなわち、論理ゲートL1の入力I2)は、論理1になりやすいとする。このため、入力ノードI1を含む信号パスの縮退故障や遅延故障を検出するため、あるいは、入力ノードI2を含む信号パスの縮退故障や遅延故障を検出するために、図1の右側に示すようにテスト回路が挿入される。

【0019】

論理回路LOGICTは、フリップフロップFFから置き換えられたスキャンフリップフロップSFF(SFF1、SFF2、SFF3)と、ユーザロジックUL2の出力と論理ゲートL1の入力I2との間に挿入された制御点CPとを有している。制御点CPは、論理ゲートL1の入力I2の論理値を制御するためのテスト回路の一例であり、スキャンフリップフロップSFF4および論理ゲートL2を有している。

【0020】

各スキャンフリップフロップSFF1−SFF4は、データ入力Dの他にスキャン入力SINおよびスキャンモード入力SMを有している。なお、図が複雑になることを避けるため、スキャンモード入力SMに接続される配線は省略している。スキャンフリップフロップSFF1−SFF4は、スキャンモード入力SMで第1論理(例えば、論理0)を受けているキャプチャ期間に、データ入力Dで受ける論理をクロックに同期してラッチし、ラッチした論理をデータ出力Qから出力する。

【0021】

スキャンフリップフロップSFF1−SFF4は、スキャンモード入力SMで第2論理(例えば、論理1)を受けているスキャンシフト期間に、スキャン入力SINで受ける論理をクロックに同期してラッチし、ラッチした論理をデータ出力Qから出力する。なお、各スキャンフリップフロップSFF1−SFF4は、データ入力Dまたはスキャン入力SINのいずれかを選択するマルチプレクサを、各フリップフロップFF1−FF4のデータ入力Dに接続することにより形成されてもよい。

【0022】

論理回路LOGICTに太線で示した信号線は、スキャンシフト期間にスキャンフリップフロップSFF1−SFF4に伝達される信号の経路を示している。各スキャンフリップフロップSFFのスキャン入力SINは、別のスキャンフリップフロップSFFのデータ出力Qに接続される。太い信号線により、スキャンフリップフロップSFF1−SFF4は、スキャンシフト期間にシフトレジスタとして動作する。なお、スキャンシフト期間中の信号の伝達経路は、スキャンフリップフロップSFF1−SFF4の順でなくてもよい。テストの容易性を向上させるために、上述のように通常のフリップフロップFFをシフトレジスタとして動作可能なスキャンフリップフロップSFFに置き換えることをスキャン設計と称する。

【0023】

この例では、ユーザロジックUL2の出力が論理1になりやすいため、論理ゲートL2としてアンドゲートが使用される。例えば、ユーザロジックUL2の出力が論理0になりやすいとき、論理ゲートL2としてオアゲートが使用される。なお、論理ゲートL2として、アンドゲートの代わりにナンドゲートが使用されてもよく、オアゲートの代わりにノアゲートが使用されてもよい。例えば、論理回路LOGICにおいて、ユーザロジックUL2と論理ゲートL1の入力I2との間にインバータ等の反転論理が配置されている場合、論理回路LOGICTにおいて、ユーザロジックUL2と反転論理の間に、ナンドゲートまたはノアゲートが配置される。

【0024】

制御点CPは、ユーザロジックUL2の出力が論理1に設定されているときに、論理ゲートL1の入力I2を論理0に設定可能にするために設けられる。この種の制御点CPは、”0制御点”と称される。一方、ユーザロジックUL2の出力が論理0になりやすいときに挿入されるオアゲートを含む制御点は、”1制御点”と称される。制御点CPの挿入により、入力ノードI2の論理をスキャンフリップフロップSFF4により任意に設定でき、故障検出率を向上できる。

【0025】

スキャンフリップフロップSFF1−SFF4のスキャンモード入力SMには、共通のスキャンモード入力信号SMが供給される。スキャンフリップフロップSFF1−SFF4に”>”印で示すクロック入力には、共通のクロックが供給される。なお、図が複雑になることを避けるため、スキャンモード信号SMの信号線およびクロック配線の記載は省略している。

【0026】

制御点CPに形成されるスキャンフリップフロップSFF4のデータ入力Dは、制御点CP以外に形成されるスキャンフリップフロップSFF1−SFF3のいずれかのデータ出力Qに接続される。この例では、スキャンフリップフロップSFF4のデータ入力Dは、スキャンフリップフロップSFF3のデータ出力Qに接続されている。

【0027】

例えば、ユーザにより設計された論理回路LOGICへのテスト回路の挿入は、ワークステーション等のコンピュータシステムがテスト回路挿入プログラムを実行することにより実施される。換言すれば、テスト回路挿入プログラムの実行により、論理回路LOGICにテスト回路を挿入するコンピュータシステムは、テスト回路挿入装置として機能する。そして、テスト回路挿入装置の動作により、論理回路LOGICにテスト回路を挿入するテスト回路挿入方法が実施される。

【0028】

テスト回路挿入装置は、テスト回路挿入プログラムを実行することにより、以下に示す少なくとも3つの処理1−処理3を実施し、論理回路LOGICにテスト回路を挿入して論理回路LOGICTを生成する。なお、テスト回路挿入装置は、処理1、処理2をこの順で実施してもよく、逆順で実施してもよい。また、テスト回路挿入装置は、処理1、処理2を同時に実施してもよい。

(処理1)論理回路LOGICのフリップフロップFF1−FF3を、シフトレジスタとして機能させるために、データ入力Dおよびスキャン入力SINを各々有するスキャンフリップフロップSFF1−SFF3に置き換える。

(処理2)テストを容易化するために制御点CPの挿入が必要なノードと、挿入する制御点CPの論理を求める。この例では、制御点CPは、ユーザロジックUL2と論理ゲートL1との間に挿入され、データ入力Dおよびスキャン入力SINを有するスキャンフリップフロップSFF4と、論理ゲートL2とを有する。論理ゲートL2は、一対の入力がスキャンフリップフロップSFF4のデータ出力QおよびユーザロジックUL2の出力にそれぞれ接続される。

(処理3)スキャンフリップフロップSFF4のデータ入力Dに、制御点CP以外に形成されるスキャンフリップフロップSFF1−SFF3のデータ出力Qを接続する。この例では、スキャンフリップフロップSFF4のデータ入力Dは、スキャンフリップフロップSFF3のデータ出力Qに接続される。

【0029】

図2は、図1に示したテスト回路が挿入された論理回路LOGICTの故障検出方法の例を示している。例えば、図2に示す故障検出方法は、論理回路LOGICTを含む半導体集積回路の製造工程内のテスト工程において、LSI(large Scale Integration)テスタ等のテスト装置を用いて、良品と不良品とを識別するために実施される。スキャンフリップフロップSFF1、SFF2、SFF3、SFF4の中に括弧で示した論理値は、スキャン入力SINを有効にし、スキャンフリップフロップSFF1−SFF4をシフトレジスタとして動作させるスキャンシフト期間中に設定される論理値を示している。

【0030】

図2の左側は、論理ゲートL1の入力ノードI1を含む信号パス(スキャンフリップフロップSFF2のデータ出力Q以降の信号パス)の遅延故障を検出するための方法を示している。図2の右側は、論理ゲートL1の入力ノードI2を含む信号パス(論理ゲートL2の出力以降の信号パス)の遅延故障を検出するための方法を示している。

【0031】

なお、X印を付けた符号F1、F2は、遅延故障の存在を示している。但し、X印は、遅延故障F1、F2が発生している位置を示しているとは限らない。例えば、遅延故障F1は、スキャンフリップフロップSFF2のデータ出力QからスキャンフリップフロップSFF3のデータ入力Dまでの信号パスのいずれかに局所的に発生する。あるいは、遅延故障F1は、スキャンフリップフロップSFF2のデータ出力QからスキャンフリップフロップSFF3のデータ入力Dまでの信号パス上に分散して発生する。

【0032】

同様に、遅延故障F2は、論理ゲートL2の出力からスキャンフリップフロップSFF3のデータ入力Dまでの信号パスのいずれかに局所的に発生する。あるいは、遅延故障F2は、論理ゲートL2の出力からスキャンフリップフロップSFF3のデータ入力Dまでの信号パス上に分散して発生する。一般に、局所的に発生する遅延故障は遷移遅延故障と称され、分散して発生する遅延故障はパス遅延故障と称される。

【0033】

図の左側において、制御点CPに接続されない入力I1を含む信号パスの遅延故障を検出する場合、テスト装置は、スキャンシフト期間に移行するために、スキャンモード入力SMを第2論理に設定する。スキャンシフト期間では、各スキャンフリップフロップSFF1−SFF4は、クロックに同期してスキャン入力SINで受ける論理をラッチし、ラッチした論理をデータ出力Qから出力する。

【0034】

テスト装置は、スキャンシフト期間にスキャンフリップフロップSFF1−SFF4をシフト動作し、論理1、論理0、論理0、論理0を、スキャンフリップフロップSFF1、SFF2、SFF3、SFF4にそれぞれ設定する。すなわち、テスト装置は、入力I1に直列に接続される一対のスキャンフリップフロップSFF1、SFF2に互いに異なる論理を設定し、スキャンフリップフロップSFF3、SFF4に同じ論理を設定する。

【0035】

ここで、スキャンフリップフロップSFF1、SFF2は、論理0、論理1にそれぞれ設定されてもよい。スキャンフリップフロップSFF3、SFF4に設定される論理0は、ユーザロジックUL2から出力される論理に依存せず、論理ゲートL1の入力I2を論理0に固定するために必要である。入力I2を論理0に固定することにより、スキャンフリップフロップSFF2、SFF1に設定された論理0、論理1を論理ゲートL1の出力に順に伝達できる。

【0036】

次に、テスト装置は、スキャンシフト期間からキャプチャ期間に移行するために、スキャンモード入力SMを第1論理に設定する。キャプチャ期間では、各スキャンフリップフロップSFF1−SFF4は、クロックに同期してデータ入力Dで受ける論理を順にラッチし、ラッチした論理をデータ出力Qから出力する。テスト装置は、キャプチャ期間に2つのクロックパルスを発生する。論理ゲートL1の入力I1は、最初のクロックパルスにより論理0から論理1に変化する。

【0037】

遅延故障F1のない論理回路では、スキャンフリップフロップSFF3は、最初のクロックパルスに同期してスキャンフリップフロップSFF2に初期設定された論理0をラッチし、2番目のクロックパルスに同期してスキャンフリップフロップSFF1に初期設定された論理1をラッチする。

【0038】

一方、遅延故障F1のある論理回路では、スキャンフリップフロップSFF2のデータ出力Qの論理0から論理1への遷移は、スキャンフリップフロップSFF3に遅れて伝わる。このため、スキャンフリップフロップSFF3は、2番目のクロックパルスに同期してスキャンフリップフロップSFF1に初期設定された論理1をラッチできず、スキャンフリップフロップSFF2に初期設定された論理0を再びラッチする。

【0039】

この後、テスト装置は、キャプチャ期間からスキャンシフト期間に移行し、スキャンフリップフロップSFF3に保持されている論理を読み出す。そして、テスト装置は、スキャンフリップフロップSFF3に論理1が保持されているときに、遅延故障F1が存在しないことを検出し、スキャンフリップフロップSFF3に論理0が保持されているときに、遅延故障F1が存在することを検出する。すなわち、スキャンフリップフロップSFF3に保持される論理が、2番目のクロックパルスの前後で変化しないときに、入力I1を含む信号パスの遅延故障F1が検出される。

【0040】

一方、図の右側において、制御点CPに接続される入力I2を含む信号パスの遅延故障F2を検出する場合、テスト装置は、スキャンシフト期間に、論理0、論理0、論理1、論理0を、スキャンフリップフロップSFF1、SFF2、SFF3、SFF4にそれぞれ設定する。すなわち、テスト装置は、入力I1に直列に接続される一対のスキャンフリップフロップSFF1、SFF2に同じ論理を設定し、スキャンフリップフロップSFF3、SFF4に互いに異なる論理を設定する。

【0041】

ここで、スキャンフリップフロップSFF3、SFF4は、論理0、論理1にそれぞれ設定されてもよい。スキャンフリップフロップSFF1、SFF2に設定される論理0は、スキャンフリップフロップSFF4、SFF3に設定された論理0、論理1を論理ゲートL1の出力に順に伝達するために必要である。

【0042】

次に、テスト装置は、キャプチャ期間に、論理ゲートL1の入力I2を論理0から論理1に変化し、論理ゲートL1の出力値をスキャンフリップフロップSFF3にラッチするために、2つのクロックパルスを発生する。図2の左側の動作と同様に、遅延故障F2のない論理回路では、スキャンフリップフロップSFF3は、2番目のクロックパルスに同期してスキャンフリップフロップSFF1に初期設定された論理1をラッチする。一方、遅延故障F2のある論理回路では、スキャンフリップフロップSFF3は、2番目のクロックパルスに同期してスキャンフリップフロップSFF1に初期設定された論理1をラッチできず、スキャンフリップフロップSFF2に初期設定された論理0を再びラッチする。

【0043】

この後、テスト装置は、図2の左側の動作と同様に、キャプチャ期間にスキャンフリップフロップSFF3に保持されている論理を読み出す。そして、テスト装置は、スキャンフリップフロップSFF3に論理1が保持されているときに、遅延故障F2が存在しないことを検出し、スキャンフリップフロップSFF3に論理0が保持されているときに、遅延故障F2が存在することを検出する。すなわち、スキャンフリップフロップSFF3に保持される論理が、2番目のクロックパルスの前後で変化しないときに、入力I2を含む信号パスの遅延故障F2が検出される。

【0044】

なお、図2の左側の故障検出方法の実施により、遅延故障F1だけでなく、入力I1を含む信号パスの縮退故障を検出できる。図2の右側の故障検出方法の実施により、遅延故障F2だけでなく、入力I2を含む信号パスの縮退故障を検出できる。また、スキャンフリップフロップSFF1−SFF4への論理値の設定および遅延故障F1、F2の検出は、テスト装置に用いずに、論理回路LOGICTを含む半導体集積回路に搭載されるBIST(Built-In Self Test)回路等により実施されてもよい。

【0045】

以上、この実施形態では、検出する遅延故障F1、F2の位置に応じて、キャプチャ期間に制御点CPの出力の論理を固定し、あるいは論理を変化させることができる。これにより、論理ゲートL1の入力I1の論理変化を後段の論理に伝達でき、あるいは論理ゲートL1の入力I2の論理変化を後段の論理に伝達できる。この結果、論理ゲートL1の入力I1を含む信号パスの遅延故障F1と、論理ゲートL1の入力I2を含む信号パスの遅延故障F2とを、1つの制御点CPにより検出できる。すなわち、遅延故障F1、F2を1つの制御点CPにより検出できる論理回路の故障検出方法、テスト回路挿入方法およびテスト回路挿入装置を提供できる。

【0046】

図3は、論理回路の故障検出方法、論理回路のテスト回路挿入方法および論理回路のテスト回路挿入装置の別の実施形態および半導体集積回路の一実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。図3は、テスト回路の一例である制御点CPが挿入された論理回路LOGICTを示している。テスト回路を挿入前の論理回路LOGICは、図4に示す。

【0047】

この実施形態では、論理回路LOGICTは、ユーザロジックUL1、UL2、UL3、オアゲートOR1および制御点CPを有している。ユーザロジックUL1の出力は、オアゲートOR1の入力I1に接続されている。ユーザロジックUL2の出力は、制御点CPを介してオアゲートOR1の入力I2に接続されている。オアゲートOR1の出力は、ユーザロジックUL3に接続されている。

【0048】

なお、オアゲートOR1は、アンドゲート、ノアゲート、ナンドゲート等でもよい。アンドゲートおよびナンドゲートの場合、入力I2を論理1に固定し、入力I1の論理を変化させることで、入力I1を含む信号パスの遅延故障F1を検出できる。また、入力I1を論理1に固定し、入力I2の論理を変化させることで、入力I2を含む信号パスの遅延故障F2を検出できる。ノアゲートの場合、オアゲートOR1と同様に、入力I2を論理0に固定し、入力I1の論理を変化させることで、入力I1を含む信号パスの遅延故障F1を検出できる。また、入力I1を論理0に固定し、入力I2の論理を変化させることで、入力I2を含む信号パスの遅延故障F2を検出できる。遅延故障の検出方法については、図8および図9で説明する。

【0049】

例えば、ユーザロジックUL1は、複数のスキャンフリップフロップSFF(SFFa、SFFb)を含んでいる。スキャンフリップフロップSFFaのデータ出力Qは、ノードNDaを介してスキャンフリップフロップSFFbのデータ入力Dおよびスキャン入力SINに接続されている。スキャンフリップフロップSFFbのデータ出力Qは、ノードNDbを介してオアゲートOR1の入力I1およびスキャンフリップフロップSFFcのスキャン入力SINに接続されている。なお、スキャンフリップフロップSFFbのデータ出力Qは、組み合わせ回路を介して入力I1に接続されてもよい。

【0050】

例えば、ユーザロジックUL2は、複数のスキャンフリップフロップSFF(SFFc、SFFc)および組み合わせ回路等の回路CC1を含んでいる。この例では、回路CC1の出力(すなわち、ノードNDe)は、論理1になりやすいとする。換言すれば、ユーザロジックUL2の動作中に、ノードNDeが論理1になる確率は、ノードNDeが論理0になる確率よりも十分に高い。このため、ノードNDeが論理1のときにオアゲートOR1の入力I2を任意の論理に設定可能にするために、制御点CPが挿入されている。

【0051】

スキャンフリップフロップSFFcのデータ出力Qは、ノードNDcを介してスキャンフリップフロップSFFdのデータ入力Dおよびスキャン入力SINに接続されている。スキャンフリップフロップSFFdのデータ出力Qは、スキャンフリップフロップSFFfのスキャン入力SINに接続され、回路CC1を介してノードNDeに接続されている。

【0052】

例えば、ユーザロジックUL3は、組み合わせ回路等の回路CC2および少なくとも1つのスキャンフリップフロップSFFeを有している。回路CC2の入力は、ノードNDhを介してオアゲートOR1の出力に接続されている。例えば、回路CC2は、ノードNDhの論理を反転してノードNDiに出力する。スキャンフリップフロップSFFeのデータ入力Dは、ノードNDiを介して回路CC2の出力に接続されている。スキャンフリップフロップSFFeのスキャン入力SINは、スキャンフリップフロップSFFfのデータ出力Qに接続されている。スキャンフリップフロップSFFeのデータ出力Qは、ノードSOUTおよびスキャンフリップフロップSFFfのデータ入力Dに接続されている。

【0053】

制御点CPは、テスト回路の一例であり、スキャンフリップフロップSFFf、ナンドゲートNAND1およびアンドゲートAND1を有している。スキャンフリップフロップSFFfのデータ出力Qは、ナンドゲートNAND1の一方の入力およびスキャンフリップフロップSFFeのスキャン入力SINに接続されている。ナンドゲートNAND1の他方の入力は、テストモード信号を受けるテストモード端子TMに接続されている。ナンドゲートNAND1の出力は、ノードNDfを介してアンドゲートAND1の一方の入力に接続されている。アンドゲートAND1の他方の入力は、ノードNDeを介して回路CC1の出力に接続されている。アンドゲートAND1の出力は、ノードNDgを介してオアゲートOR1の入力I2に接続されている。

【0054】

この例では、テストモード端子TMは、遅延故障を検出するためのテストモード中に論理1に設定され、論理回路LOGICTがユーザシステムの一部として動作するシステムモード中に論理0に設定される。テストモード端子TMの論理1により、ナンドゲートNAND1の信号伝達機能は有効になり、ナンドゲートNAND1は、スキャンフリップフロップSFFfの出力Qの論理を反転してアンドゲートAND1に出力する。一方、テストモード端子TMの論理0により、ナンドゲートNAND1の信号伝達機能は無効になり、ナンドゲートNAND1の出力であるノードNDfは論理1に固定される。

【0055】

これにより、システムモード中(TM=論理0)に、データ入力Dで受ける論理に応じて動作するスキャンフリップフロップSFFfのデータ出力Qの論理がアンドゲートAND1に伝達されることを防止でき、ユーザロジックUL3等の誤動作を防止できる。ナンドゲートNAND1がノードNDfに論理1を出力することで、回路CC1の出力であるノードNDeの論理は、アンドゲートAND1を介してオアゲートOR1に伝達される。このように、スキャンフリップフロップSFFfをテストモード信号TMにより制御されるナンドゲートNAND1を介してアンドゲートAND1に接続することで、システムモード中のスキャンフリップフロップSFFfの動作による誤動作を防止できる。

【0056】

図1と同様に、太線で示した信号線は、スキャンシフト期間にスキャンフリップフロップSFFa、SFFb、SFFc、SFFd、SFFf、SFFeに伝達される信号の経路を示している。X印を付けた符号F1、F2は、遅延故障の存在を示している。但し、遅延故障F1、F2は、確率的に同時に発生しないものとして扱われる。また、図2で説明したように、X印は、遅延故障F1、F2が発生している位置を示しているとは限らない。

【0057】

なお、各スキャンフリップフロップSFFa−SFFfは、データ入力またはスキャン入力のいずれかを選択するマルチプレクサを、フリップフロップのデータ入力に接続することにより形成されてもよい。

【0058】

図4は、図3に示した論理回路LOGICTにテスト回路を挿入する前の論理回路LOGICの例を示している。論理回路LOGICは、ユーザにより設計された回路である。論理回路LOGICは、図3のスキャンフリップフロップSFFa、SFFb、SFFc、SFFd、SFFeの代わりにフリップフロップFFa、FFb、FFc、FFd、FFeが配置されている。論理回路LOGICは、制御点CPを含まない。このため、論理回路LOGICでは、ユーザロジックUL2の出力は、オアゲートOR1の入力I2に直接接続されている。

【0059】

図5は、図4に示した論理回路LOGICから図3に示した論理回路LOGICTを生成するテスト回路挿入装置CADの例を示している。例えば、テスト回路挿入装置CADは、ワークステーション等のコンピュータシステムにより実現される。

【0060】

テスト回路挿入装置CADは、図3に示した制御点CP等のテスト回路を挿入するテスト回路挿入プログラム等を記憶するメモリ装置MEMと、テスト回路挿入プログラムを実行するプロセッサCPUとを有している。メモリ装置MEMは、例えば、半導体メモリ装置やハードディスクドライブ装置である。テスト回路挿入装置CADは、ディスプレイDISP、キーボードやマウス等の入力デバイスINPUT、ディスクドライブ装置DRVおよび入出力デバイスINOUTを有している。

【0061】

ディスプレイDISPは、入力デバイスINPUTおよびディスクドライブ装置DRVから入力された情報や、テスト回路挿入プログラムにより生成された論理回路LOGICTの論理図やネットリスト等を表示する。ディスクドライブ装置DRVには、テスト回路挿入プログラムあるいは図4に示した論理回路LOGICのネットリストが記録されたCD−ROM、DVD等の記録媒体がセットされる。テスト回路挿入プログラムやネットリストは、ディスクドライブ装置DRVを介してメモリ装置MEMにダウンロードされる。

【0062】

そして、プロセッサCPUがテスト回路挿入プログラムを実行することにより、テスト回路挿入方法が実施され、図4の論理回路LOGICから図3の論理回路LOGICT(ネットリスト)が生成される。生成されたネットリストは、メモリ装置MEMからメモリカード等のシリコンディスク、磁気テープ装置、あるいはハードディスクドライブ装置等の入出力デバイスINOUTに書き込まれる。

【0063】

なお、ディスクドライブ装置DRVの代わりに、入出力デバイスINOUTを用いて、テスト回路挿入プログラムやネットリストをメモリ装置MEMに転送してもよい。あるいは、テスト回路挿入プログラムやネットリストは、ネットワークを介してメモリ装置MEMに入出力されてもよい。

【0064】

図6は、図5に示したテスト回路挿入装置CADの動作の例を示している。図6は、テスト回路挿入方法のフローを示しており、テスト回路挿入装置CADがテスト回路挿入プログラムを実行することにより実現される。

【0065】

先ず、ステップS10において、テスト回路挿入装置CADは、ユーザにより設計された論理回路LOGICのネットリストを解析し、制御点CPの挿入が必要なノードと、挿入する制御点CPの論理を求める。テスト回路挿入装置CADは、必要に応じて、観測点の挿入が必要な挿入するノードと、挿入する観測点の論理を求める。観測点は、テスト回路の一種であり、遅延故障を検出するための論理値を得るために挿入が必要なスキャンフリップフロップ等である。求めた制御点CPの情報および観測点の情報は、挿入されるテスト回路の情報としてメモリ装置MEM等に書き込まれる。

【0066】

次に、ステップS20において、テスト回路挿入装置CADは、求めた制御点CPの情報に基づいて、制御点CPのスキャンフリップフロップSFF(例えば、図3のSFFf)のデータ入力Dに接続するスキャンフリップフロップSFFを選択する。例えば、ステップS20では、制御点CPの下流側(出力側)が順に探索され、制御点CPからの論理段数が最も少ないスキャンフリップフロップSFFが選択される。あるいは、制御点CPの上流側(入力側)が順に探索され、制御点CPからの論理段数が最も少ないスキャンフリップフロップSFFが選択される。これにより、制御点CPのスキャンフリップフロップSFFのデータ入力Dは、制御点CP以外に形成されるスキャンフリップフロップSFFのいずれかのデータ出力Qに接続される。選択されたスキャンフリップフロップSFFの情報は、メモリ装置MEM等に書き込まれる。

【0067】

次に、ステップS30において、テスト回路挿入装置CADは、論理回路LOGICのネットリストを用いて、ネットリスト上のフリップフロップFFをスキャンフリップフロップSFFに置き換える。次に、テスト回路挿入装置CADは、制御点CPの情報を用いて、ネットリスト上に制御点CPを挿入する。また、テスト回路挿入装置CADは、ステップS20で選択したスキャンフリップフロップSFFの情報を用いて、挿入した制御点CPのスキャンフリップフロップSFF(図3のSFFf)のデータ入力Dに、選択したスキャンフリップフロップSFFのデータ出力Qを接続する。そして、図3に示した論理回路LOGICT(ネットリスト)が生成される。

【0068】

テスト回路挿入装置CADは、必要に応じて、観測点の情報に基づいて、ネットリスト上に観測点を挿入する。テスト回路挿入装置CADは、テスト回路が挿入された論理回路LOGICTのネットリストを生成する。そして、生成されたネットリストを用いて、トランジスタ等の素子の配置および素子間の配線を実施するプログラムが実行され、半導体集積回路LSIを製造するためのフォトマスクのデータが生成される。素子の配置、配線およびフォトマスクのデータ生成は、テスト回路挿入装置CADが別のプログラムを実行することで実施されてもよく、大型計算機等を用いて実施されてもよい。

【0069】

この後、フォトマスクのデータを用いてフォトマスクが製作され、フォトマスクを用いて半導体製造工程が実施され、図3に示した論理回路LOGICTを有する半導体集積回路LSIが製造される。製造された半導体集積回路LSIは、図7に示すテストシステムTSYSによりテストされ、遅延故障の有無が検出される。

【0070】

図7は、図3に示した論理回路LOGICTを有する半導体集積回路LSIをテストするテストシステムTSYSの例を示している。なお、後述する実施形態においても、図7と同じテストシステムTSYSが使用される。テストシステムTSYSは、半導体集積回路LSIの製造工程におけるテスト工程で使用される。

【0071】

まず、半導体製造工程により半導体ウエハWAF上に複数の半導体集積回路LSIが形成される。半導体集積回路LSIは、ウエハWAFから切り出される前にテスタTEST等のテスト装置によりテストされる。テストシステムTSYSによる半導体集積回路LSIのテストにより、論理回路LOGICTの故障検出方法が実現される。すなわち、テスタTESTは、論理回路LOGICTの故障検出装置として動作する。

【0072】

半導体集積回路LSIは、例えば、プローブカードのプローブPRBを介してテスタTESTに接続される。図7では、1つの半導体集積回路LSIがテスタTESTに接続されているが、複数の半導体集積回路LSIをテスタTESTに一度に接続してもよい。テスタTESTに一度に接続する半導体集積回路LSIの数は、テスタTESTの端子数と半導体集積回路LSIの端子数に依存する。

【0073】

例えば、テスタTESTは、論理回路LOGICTの遅延故障を検出するための故障検出プログラムを実行し、クロックCLK、テストモード信号TM、スキャンモード入力信号SMおよびスキャン入力信号SINを半導体集積回路LSIに出力する。そして、テスタTESTは、論理回路LOGICT内の所定のスキャンフリップフロップSFF(例えば、図3のSFFe)に保持されている論理をスキャンアウト端子SOUTを介して読み出し、遅延故障の有無を検出する。遅延故障が検出された半導体集積回路LSIは、不良品として扱われる。なお、テスタTESTは、パッケージングされた半導体集積回路LSIをテストするために使用されてもよい。

【0074】

図8は、図3に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図8の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図3に示した遅延故障F1を検出するために実施される。換言すれば、図8は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。

【0075】

図8および以降の波形図において、1番目から6番目のクロックサイクルおよび9番目のクロックサイクルは、スキャンモード入力SMが論理1に設定されるスキャンシフト期間を示している。7番目および8番目のクロックサイクルは、スキャンモード入力SMが論理0に設定されるキャプチャ期間を示している。7番目のクロックサイクルの長さは、遅延故障F1またはF2を判断する信号パスの遅延時間に合わせて設定される。換言すれば、信号パスの遅延時間が7番目のクロックサイクルの長さより長いときに、遅延故障F1またはF2の発生が検出される。ここで、7番目のクロックサイクルの長さは、7番目のクロックCLKの立ち上がりエッジから8番目のクロックCLKの立ち上がりエッジまでの期間である。また、スキャンフリップフロップSFFfから出力される論理(遷移エッジ)をオアゲートOR1に伝達するために、テストモード端子TMはテストモード中に論理1に設定される。7番目から9番目のクロックサイクルにおいて、破線で示した波形は、遅延故障が存在するときの動作を示している。

【0076】

この例では、スキャンフリップフロップSFFe、SFFf、SFFd、SFFc、Sffb、Sffaに所望の論理を設定するために、1番目から6番目のクロックサイクルにおいてスキャン入力SINに論理1、論理1、論理0、論理0、論理0、論理1が順に供給される。スキャン入力SINの波形上に示したスキャンフリップフロップ名は、6番目のクロックサイクルで設定される論理との対応を示している。キャプチャ期間の直前の6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFeは、論理0、論理1、論理1、論理1にそれぞれ設定される。

【0077】

すなわち、6番目のクロックサイクルにおいて、オアゲートOR1の入力I1にデータ入力D経由で直列に接続されるスキャンフリップフロップSFFb、SFFaは、互いに異なる論理を保持する。これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFbに保持される論理を論理0から論理1に変化でき、オアゲートOR1の入力I1を論理0から論理1に変化できる。

【0078】

また、6番目のクロックサイクルにおいて、ナンドゲートNAND1およびアンドゲートAND1を介し、かつデータ入力D経由でオアゲートOR1の入力I2に直列に接続されるスキャンフリップフロップSFFf、SFFeは、互いに同じ論理を保持する。これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFfに保持される論理を、1クロックサイクル前にスキャンフリップフロップSFFeに保持されている論理を用いて論理1に維持できる。したがって、スキャンフリップフロップSFFfの出力ノードに接続されるオアゲートOR1の入力I2を論理0に維持できる。なお、スキャンフリップフロップSFFfに保持されている論理は、ナンドゲートNAND1により反転されて、ノードNDfおよびオアゲートOR1の入力I2に伝達される。

【0079】

遅延故障F1が存在しないとき、スキャンフリップフロップSFFbの論理変化は、オアゲートOR1の入力I1、オアゲートOR1の出力ノードNDhに直ちに伝達される。回路CC2は、出力ノードNDhの論理0から論理1への変化に応答して、出力ノードNDiを論理1から論理0に直ちに変化する。このため、スキャンフリップフロップSFFeは、キャプチャ期間の8番目のクロックサイクルにおいて、論理0をラッチし、ラッチした論理0をスキャンアウト端子SOUTに出力する。そして、スキャンシフト期間の9番目のクロックサイクルにおいて、図7に示したテスタTESTは、スキャンアウト端子SOUTの論理0を読み込むことにより、遅延故障F1が存在しないことを検出する。

【0080】

なお、実際の回路では、スキャンフリップフロップSFFeの出力は、複数のスキャンフリップフロップを介してスキャンアウト端子SOUTに接続されることが多い。この場合、スキャンアウト端子SOUTは、例えば、シフトレジスタを構成する最終のスキャンフリップフロップの出力Qに接続され、遅延故障F1の有無は、9番目のクロックサイクルより後のクロックサイクルで判定される。

【0081】

一方、遅延故障F1が存在するとき、スキャンフリップフロップSFFbの論理変化は、破線で示すように、オアゲートOR1の入力I1、オアゲートOR1の出力ノードNDhあるいは回路CC2の出力ノードNDiに遅れて伝達される。信号の遅延により、キャプチャ期間の8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeがノードNDiの論理0をラッチできないとき、スキャンアウト端子SOUTは論理1に維持される。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理1を読み込むことにより、遅延故障F1が存在することを検出する。

【0082】

図9は、図3に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図9の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図3に示した遅延故障F2を検出するために実施される。換言すれば、図9は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8と同じ動作については、詳細な説明は省略する。

【0083】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理0、論理1、論理0、論理0、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFeは、論理0、論理0、論理1、論理0にそれぞれ設定される。すなわち、6番目のクロックサイクルにおいて、オアゲートOR1の入力I1に直列に接続されるスキャンフリップフロップSFFb、SFFaは、互いに同じ論理を保持する。ナンドゲートNAND1およびアンドゲートAND1を介してオアゲートOR1の入力I2に直列に接続されるスキャンフリップフロップSFFf、SFFeは、互いに異なる論理を保持する。

【0084】

これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFfに保持される論理を、1クロックサイクル前にスキャンフリップフロップSFFeに保持されている論理を用いて、論理1から論理0に変更できる。スキャンフリップフロップSFFeに保持されている論理は、ナンドゲートNAND1により反転される。すなわち、7番目のクロックサイクルにおいて、オアゲートOR1の入力I1を論理0に維持した状態で、オアゲートOR1の入力I2を論理0から論理1に変化できる。

【0085】

遅延故障F2が存在しないとき、スキャンフリップフロップSFFfの論理変化は、オアゲートOR1の入力I2および出力ノードNDhに直ちに伝達される。図8と同様に、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて論理0をラッチし、テスタTESTは、9番目のクロックサイクルにおいてスキャンアウト端子SOUTの論理0を読み込む。これにより、遅延故障F2が存在しないことが検出される。

【0086】

一方、遅延故障F2が存在するとき、破線で示すように、スキャンフリップフロップSFFfの論理変化は、オアゲートOR1の入力I1、オアゲートOR1の出力ノードNDhあるいは回路CC2の出力ノードNDiに遅れて伝達される。そして、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeがノードNDiの論理0をラッチできないとき、スキャンアウト端子SOUTは論理1に維持される。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理1を読み込むことにより、遅延故障F2が存在することを検出する。

【0087】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。さらに、論理ゲートL1の入力I1を含む信号パスの遅延故障F1と、論理ゲートL1の入力I2を含む信号パスの遅延故障F2とを、1つの制御点CPにより検出できる半導体集積回路LSIを提供できる。また、スキャンフリップフロップSFFfのデータ出力Qを、テストモード信号TMにより制御されるナンドゲートNAND1を介してアンド回路AND1に接続することで、システムモード中にスキャンフリップフロップSFFfのデータ出力Qの論理がアンドゲートAND1に伝達されることを防止できる。この結果、論理回路LOGICTが誤動作することを防止できる。

【0088】

図10は、論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。

【0089】

この実施形態の論理回路LOGICTは、図3の回路CC1の代わりに回路CC3を有している。また、制御点CPは、図3に示したナンドゲートNAND1の代わりにアンドゲートAND2を有し、図3に示したアンドゲートAND1の代わりにオアゲートOR2を有している。論理回路LOGICTのその他の構成は、図3と同様である。図10の論理回路LOGICは、図5に示したテスト回路挿入装置CADがテスト回路挿入プログラムを実行し、図6に示した処理を実施することにより生成される。

【0090】

この実施形態では、回路CC3の出力(すなわち、ノードNDe)は、論理0になりやすいとする。換言すれば、ユーザロジックUL2の動作中に、ノードNDeが論理0になる確率は、ノードNDeが論理1になる確率よりも十分に高い。このため、オアゲートOR1の入力I2を任意の論理に設定可能にし、故障検出率を向上するために、図3と異なる制御点CPが挿入されている。制御点CPのオアゲートOR2は、回路CC3の出力が論理0に設定されているときに、オアゲートL1の入力I2を論理1に設定可能にするために設けられる。

【0091】

テストモード中(TM=論理1)、アンドゲートAND2の信号伝達機能は有効になり、アンドゲートAND2は、スキャンフリップフロップSFFfの出力Qの論理をオアゲートOR2に出力する。一方、システムモード中(TM=論理0)、アンドゲートAND2の信号伝達機能は無効になり、アンドゲートAND2の出力であるノードNDfは論理0固定される。これにより、システムモード中に、データ入力Dで受ける論理に応じて動作するスキャンフリップフロップSFFfのデータ出力Qの論理がオアゲートOR2に伝達されることを防止でき、ユーザロジックUL3等の誤動作を防止できる。アンドゲートAND2がノードNDfに論理0を出力することで、回路CC3の出力であるノードNDeの論理は、オアゲートOR2を介してオアゲートOR1に伝達される。このように、スキャンフリップフロップSFFfをテストモード信号TMにより制御されるアンドゲートAND2を介してオアゲートOR2に接続することで、システムモード中のスキャンフリップフロップSFFfの動作による誤動作を防止できる。

【0092】

図11は、図10に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図11の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図10に示した遅延故障F1を検出するために実施される。換言すれば、図11は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8と同じ動作については、詳細な説明は省略する。

【0093】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理0、論理0、論理0、論理0、論理0、論理1が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFeは、論理0、論理1、論理0、論理0にそれぞれ設定される。すなわち、6番目のクロックサイクルにおいて、オアゲートOR1の入力I1に直列に接続されるスキャンフリップフロップSFFb、SFFaは、互いに異なる論理を保持する。これにより、図8と同様に、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFbに保持される論理を論理0から論理1に変化でき、オアゲートOR1の入力I1を論理0から論理1に変化できる。

【0094】

6番目のクロックサイクルにおいて、アンドゲートAND2およびオアゲートOR2を介してオアゲートOR1の入力I2に直列に接続されるスキャンフリップフロップSFFf、SFFeは、互いに同じ論理を保持する。これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFfに保持される論理を、1クロックサイクル前にスキャンフリップフロップSFFeに保持されている論理を用いて論理0に維持できる。ここで、図10の制御点CPは、ナンドゲートNAND1(図3)の代わりにアンドゲートAND2を有しているため、制御点CPを”0制御点”として動作させるために、スキャンフリップフロップSFFf、SFFeは、論理0を設定される。制御点CPにより、スキャンフリップフロップSFFfの出力ノードに接続されるオアゲートOR1の入力I2を論理0に維持できる。

【0095】

遅延故障F1が存在しないとき、図8と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiの論理変化として直ちに現れる。スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチし、ラッチした論理0をスキャンアウト端子SOUTに出力する。図7に示したテスタTESTは、スキャンアウト端子SOUTの論理0を読み込むことにより、遅延故障F1が存在しないことを検出する。

【0096】

一方、遅延故障F1が存在するとき、図8と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiに遅れて伝達される。8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeがノードNDiの論理0をラッチできないとき、スキャンアウト端子SOUTは論理1に維持される。図7に示したテスタTESTは、スキャンアウト端子SOUTの論理1を読み込むことにより、遅延故障F1が存在することを検出する。

【0097】

図12は、図10に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図12の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図10に示した遅延故障F2を検出するために実施される。換言すれば、図12は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8および図9と同じ動作については、詳細な説明は省略する。

【0098】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理0、論理0、論理0、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFeは、論理0、論理0、論理0、論理1にそれぞれ設定される。すなわち、6番目のクロックサイクルにおいて、オアゲートOR1の入力I1に直列に接続されるスキャンフリップフロップSFFb、SFFaは、互いに同じ論理を保持する。アンドゲートAND2およびオアゲートOR2を介してオアゲートOR1の入力I2に直列に接続されるスキャンフリップフロップSFFf、SFFeは、互いに異なる論理を保持する。

【0099】

これにより、キャプチャ期間の7番目のクロックサイクルにおいて、スキャンフリップフロップSFFfに保持される論理を、1クロックサイクル前にスキャンフリップフロップSFFeに保持されている論理を用いて、論理0から論理1に変更できる。すなわち、7番目のクロックサイクルにおいて、オアゲートOR1の入力I1を論理0に維持した状態で、オアゲートOR1の入力I2を論理0から論理1に変化できる。

【0100】

遅延故障F2が存在しないとき、スキャンフリップフロップSFFfの論理変化は、オアゲートOR1の入力I2およびノードNDh、NDiに直ちに伝達される。スキャンフリップフロップSFFeは、図9と同様に、8番目のクロックサイクルにおいて論理0をラッチし、テスタTESTは、9番目のクロックサイクルにおいてスキャンアウト端子SOUTの論理0を読み込む。これにより、遅延故障F2が存在しないことが検出される。

【0101】

一方、遅延故障F2が存在するとき、スキャンフリップフロップSFFfの論理変化は、オアゲートOR1の入力ノードI2、オアゲートOR1の出力ノードNDhあるいは回路CC2の出力ノードNDiに遅れて伝達される。そして、図9と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeがノードNDiの論理0をラッチできないとき、スキャンアウト端子SOUTは論理1に維持される。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理1を読み込むことにより、遅延故障F2が存在することを検出する。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0102】

図13は、論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。

【0103】

この実施形態の論理回路LOGICTでは、制御点CPのスキャンフリップフロップSFFfのデータ入力Dは、図3に示したスキャンフリップフロップSFFeのデータ出力Qではなく、スキャンフリップフロップSFFdのデータ出力Qに接続されている。論理回路LOGICTのその他の構成は、図3と同様である。図13の論理回路LOGICは、図5に示したテスト回路挿入装置CADがテスト回路挿入プログラムを実行し、図6に示した処理を実施することにより生成される。

【0104】

図14は、図13に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図14の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図13に示した遅延故障F1を検出するために実施される。換言すれば、図14は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8と同じ動作については、詳細な説明は省略する。

【0105】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理1、論理1、論理1、論理0、論理1が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFdは、論理0、論理1、論理1、論理1にそれぞれ設定される。そして、遅延故障F1が存在しないとき、図8と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F1が存在するとき、図8と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F1の有無を検出する。

【0106】

図15は、図13に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図15の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図13に示した遅延故障F2を検出するために実施される。換言すれば、図15は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8および図9と同じ動作については、詳細な説明は省略する。

【0107】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理1、論理0、論理0、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFdは、論理0、論理0、論理1、論理0にそれぞれ設定される。そして、遅延故障F2が存在しないとき、図9と同様に、スキャンフリップフロップSFFfの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F2が存在するとき、図9と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F2の有無を検出する。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0108】

図16は、論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。

【0109】

この実施形態の論理回路LOGICTでは、制御点CPのスキャンフリップフロップSFFfのデータ入力Dは、図10に示したスキャンフリップフロップSFFeのデータ出力Qではなく、スキャンフリップフロップSFFdのデータ出力Qに接続されている。論理回路LOGICTのその他の構成は、図10と同様である。図16の論理回路LOGICは、図5に示したテスト回路挿入装置CADがテスト回路挿入プログラムを実行し、図6に示した処理を実施することにより生成される。

【0110】

図17は、図16に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図17の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図16に示した遅延故障F1を検出するために実施される。換言すれば、図17は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8および図11と同じ動作については、詳細な説明は省略する。

【0111】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理0、論理0、論理0、論理0、論理0、論理1が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFdは、論理0、論理1、論理0、論理0にそれぞれ設定される。そして、遅延故障F1が存在しないとき、図11と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F1が存在するとき、図11と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F1の有無を検出する。

【0112】

図18は、図16に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図18の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図16に示した遅延故障F2を検出するために実施される。換言すれば、図15は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8、図9および図12と同じ動作については、詳細な説明は省略する。

【0113】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理0、論理0、論理1、論理1、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFdは、論理0、論理0、論理0、論理1にそれぞれ設定される。そして、遅延故障F2が存在しないとき、図12と同様に、スキャンフリップフロップSFFfの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F2が存在するとき、図12と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F2の有無を検出する。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0114】

図19は、論理回路の故障検出方法、論理回路のテスト回路挿入方法、論理回路のテスト回路挿入装置および半導体集積回路の別の実施形態を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。

【0115】

この実施形態の論理回路LOGICTでは、制御点CPのスキャンフリップフロップSFFfのデータ入力Dは、図3に示したスキャンフリップフロップSFFeのデータ出力Qではなく、スキャンフリップフロップSFFcのデータ出力Qに接続されている。論理回路LOGICTのその他の構成は、図3と同様である。図19の論理回路LOGICは、図5に示したテスト回路挿入装置CADがテスト回路挿入プログラムを実行し、図6に示した処理を実施することにより生成される。

【0116】

図20は、図19に示した論理回路LOGICTの遅延故障を検出するためのテストの例を示している。図20の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図19に示した遅延故障F1を検出するために実施される。換言すれば、図20は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8および図14と同じ動作については、詳細な説明は省略する。

【0117】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理1、論理1、論理1、論理0、論理1が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFcは、論理0、論理1、論理1、論理1にそれぞれ設定される。そして、遅延故障F1が存在しないとき、図14と同様に、スキャンフリップフロップSFFbの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F1が存在するとき、図14と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F1の有無を検出する。

【0118】

図21は、図19に示した論理回路LOGICTの遅延故障を検出するためのテストの別の例を示している。図21の動作は、図7に示したテスタTESTが故障検出プログラムを実行することで実現され、図19に示した遅延故障F2を検出するために実施される。換言すれば、図21は、論理回路LOGICTの遅延故障の故障検出方法を示し、半導体集積回路LSIの製造方法を示している。図8、図9および図15と同じ動作については、詳細な説明は省略する。

【0119】

この例では、1番目から6番目のクロックサイクルにスキャン入力SINに論理1、論理1、論理0、論理0、論理0、論理0が順に供給される。6番目のクロックサイクルにおいて、スキャンフリップフロップSFFb、SFFa、SFFf、SFFcは、論理0、論理0、論理1、論理0にそれぞれ設定される。そして、遅延故障F2が存在しないとき、図15と同様に、スキャンフリップフロップSFFfの論理変化は、出力ノードNDiの論理変化として直ちに現れ、スキャンフリップフロップSFFeは、8番目のクロックサイクルにおいて、論理0をラッチする。遅延故障F2が存在するとき、図15と同様に、8番目のクロックサイクルにおいて、スキャンフリップフロップSFFeは、ノードNDiの論理0をラッチできない。図7に示したテスタTESTは、スキャンシフト期間の9番目のクロックサイクルにおいて、スキャンアウト端子SOUTの論理を読み込むことにより、遅延故障F2の有無を検出する。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

【0120】

以上の詳細な説明により、実施形態の特徴点および利点は明らかになるであろう。これは、特許請求の範囲がその精神および権利範囲を逸脱しない範囲で前述のような実施形態の特徴点および利点にまで及ぶことを意図するものである。また、当該技術分野において通常の知識を有する者であれば、あらゆる改良および変更に容易に想到できるはずであり、発明性を有する実施形態の範囲を前述したものに限定する意図はなく、実施形態に開示された範囲に含まれる適当な改良物および均等物に拠ることも可能である。

【符号の説明】

【0121】

CAD‥テスト回路挿入装置;CC1、CC2‥回路;CP‥制御点;CPU‥プロセッサ;DISP‥ディスプレイ;DRV‥ディスクドライブ装置;FF1−FF4、FFa−FFf‥フリップフロップ;INOUT‥入出力デバイス;INPUT‥入力デバイス;L1、L2‥論理ゲート;LSI‥半導体集積回路;LOGIC、LOGICT‥論理回路;MEM‥メモリ装置;PRB‥プローブ;SFF1−SFF4、SFFa−SFFf‥スキャンフリップフロップ;SIN‥スキャン入力;SM‥スキャンモード入力;TEST‥テスタ;TSYS‥テストシステム;UL1、UL2、UL3‥ユーザロジック;WAF‥半導体ウエハ

【特許請求の範囲】

【請求項1】

データ入力およびスキャン入力を有する複数の第1スキャンフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、前記第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、少なくとも1つの第1スキャンフリップフロップを含み、前記第1論理ゲートの出力に接続された第3ユーザロジックと、前記第2ユーザロジックと前記第1論理ゲートとの間に挿入された制御点とを有し、前記制御点は、前記第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が前記第2スキャンフリップフロップのデータ出力および前記第2ユーザロジックの出力にそれぞれ接続され、出力が前記第1論理ゲートの第2入力に接続された第2論理ゲートとを有する論理回路の故障検出方法であって、

前記スキャン入力を有効にし、前記第1および第2スキャンフリップフロップをシフトレジスタとして動作させるスキャンシフト期間に、前記第1スキャンフリップフロップの前記1つおよび前記第2スキャンフリップフロップに同じ論理を設定し、前記第1入力に直列に接続される一対の前記第1スキャンフリップフロップに互いに異なる論理を設定し、

前記データ入力を有効にするキャプチャ期間に、前記第1および第2スキャンフリップフロップに2つのクロックパルスを供給し、前記第3ユーザロジックの前記第1スキャンフリップフロップに保持される論理が変化しないときに前記第1入力を含む信号パスの遅延故障を検出すること

を特徴とする論理回路の故障検出方法。

【請求項2】

前記スキャンシフト期間に前記第1スキャンフリップフロップの前記1つおよび前記第2スキャンフリップフロップに互いに異なる論理を設定し、前記一対の第1スキャンフリップフロップに同じ論理を設定し、前記キャプチャ期間に、前記第1および第2スキャンフリップフロップに2つのクロックパルスを供給し、前記第3ユーザロジックの前記第1スキャンフリップフロップに保持される論理が変化しないときに前記第2入力を含む信号パスの遅延故障を検出すること

を特徴とする請求項1に記載の論理回路の故障検出方法。

【請求項3】

前記制御点は、前記第2スキャンフリップフロップのデータ出力と前記第2論理ゲートとの間に配置され、前記テストモード中に、前記第2スキャンフリップフロップからの出力信号を前記第2論理ゲートに伝達し、前記テストモードを除く期間に、前記出力信号の前記第2論理ゲートへの伝達をマスクするとともに、前記第2ユーザロジックからの出力信号を前記第2論理ゲートを介して前記第1論理ゲートに伝達するための論理値を前記第2論理ゲートに出力するマスク回路を備え、

前記スキャンシフト期間および前記キャプチャ期間の動作を、前記テストモード中に実施すること

を特徴とする請求項1または請求項2に記載の論理回路の故障検出方法。

【請求項4】

複数のフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、前記第1ユーザロジックの出力に接続される第1入力および第2ユーザロジックの出力に接続される第2入力を有する第1論理ゲートと、前記第1論理ゲートの出力に接続され、少なくとも1つのフリップフロップを含む第3ユーザロジックとを有する論理回路のテスト回路挿入方法であって、

前記フリップフロップをデータ入力およびスキャン入力を各々有する第1スキャンフリップフロップに置き換える処理と、

データ入力およびスキャン入力を有する第2スキャンフリップフロップと、一対の入力が前記第2スキャンフリップフロップのデータ出力および前記第2ユーザロジックの出力にそれぞれ接続され、出力が前記第2入力に接続された第2論理ゲートとを有する制御点を、前記第2ユーザロジックと前記第1論理ゲートとの間に挿入する処理と、

前記第2スキャンフリップフロップのデータ入力に前記第1スキャンフリップフロップの1つのデータ出力を接続する処理と

を含むことを特徴とする論理回路のテスト回路挿入方法。

【請求項5】

テストモード中に、前記第2スキャンフリップフロップからの出力信号を前記第2論理ゲートに伝達し、前記テストモードを除く期間に、前記出力信号の前記第2論理ゲートへの伝達をマスクするとともに、前記第2ユーザロジックからの出力信号を前記第2論理ゲートを介して前記第1論理ゲートに伝達するための論理値を前記第2論理ゲートに出力するマスク回路を、前記第2スキャンフリップフロップのデータ出力と前記第2論理ゲートとの間に配置する処理を含むこと

を特徴とする請求項4に記載の論理回路のテスト回路挿入方法。

【請求項6】

複数のフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、前記第1ユーザロジックの出力に接続される第1入力および第2ユーザロジックの出力に接続される第2入力を有する第1論理ゲートと、前記第1論理ゲートの出力に接続され、少なくとも1つのフリップフロップを含む第3ユーザロジックとを有する論理回路のテスト回路挿入装置であって、

前記フリップフロップをデータ入力およびスキャン入力を各々有する第1スキャンフリップフロップに置き換える処理と、

データ入力およびスキャン入力を有する第2スキャンフリップフロップと、一対の入力が前記第2スキャンフリップフロップのデータ出力および前記第2ユーザロジックの出力にそれぞれ接続され、出力が前記第2入力に接続された第2論理ゲートとを有する制御点を、前記第2ユーザロジックと前記第1論理ゲートとの間に挿入する処理と、

前記第2スキャンフリップフロップのデータ入力に前記第1スキャンフリップフロップの1つのデータ出力を接続する処理と

を実施することを特徴とする論理回路のテスト回路挿入装置。

【請求項7】

テストモード中に、前記第2スキャンフリップフロップからの出力信号を前記第2論理ゲートに伝達し、前記テストモードを除く期間に、前記出力信号の前記第2論理ゲートへの伝達をマスクし、前記第2ユーザロジックからの出力信号を前記第2論理ゲートを介して前記第1論理ゲートに伝達するための論理値を前記第2論理ゲートに出力するマスク回路を、前記第2スキャンフリップフロップのデータ出力と前記第2論理ゲートとの間に配置する処理を実施すること

を特徴とする請求項6に記載の論理回路のテスト回路挿入装置。

【請求項8】

データ入力およびスキャン入力を有する複数の第1スキャンフリップフロップを含む第1ユーザロジックと、

第2ユーザロジックと、

前記第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、

少なくとも1つの第1スキャンフリップフロップを含み、前記第1論理ゲートの出力に接続された第3ユーザロジックと、

前記第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が前記第2スキャンフリップフロップのデータ出力およびテストモードを示すテストモード端子に接続されたマスク回路と、一対の入力が前記マスク回路の出力および前記第2ユーザロジックの出力にそれぞれ接続され、出力が前記第1論理ゲートの第2入力に接続された第2論理ゲートとを有する制御点と

を備え、

前記マスク回路は、前記テストモード中に、前記第2スキャンフリップフロップからの出力信号を前記第2論理ゲートに伝達し、前記テストモードを除く期間に、前記出力信号の前記第2論理ゲートへの伝達をマスクするとともに、前記第2ユーザロジックからの出力信号を前記第2論理ゲートを介して前記第1論理ゲートに伝達するための論理値を前記第2論理ゲートに出力すること

を特徴とする半導体集積回路。

【請求項1】

データ入力およびスキャン入力を有する複数の第1スキャンフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、前記第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、少なくとも1つの第1スキャンフリップフロップを含み、前記第1論理ゲートの出力に接続された第3ユーザロジックと、前記第2ユーザロジックと前記第1論理ゲートとの間に挿入された制御点とを有し、前記制御点は、前記第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が前記第2スキャンフリップフロップのデータ出力および前記第2ユーザロジックの出力にそれぞれ接続され、出力が前記第1論理ゲートの第2入力に接続された第2論理ゲートとを有する論理回路の故障検出方法であって、

前記スキャン入力を有効にし、前記第1および第2スキャンフリップフロップをシフトレジスタとして動作させるスキャンシフト期間に、前記第1スキャンフリップフロップの前記1つおよび前記第2スキャンフリップフロップに同じ論理を設定し、前記第1入力に直列に接続される一対の前記第1スキャンフリップフロップに互いに異なる論理を設定し、

前記データ入力を有効にするキャプチャ期間に、前記第1および第2スキャンフリップフロップに2つのクロックパルスを供給し、前記第3ユーザロジックの前記第1スキャンフリップフロップに保持される論理が変化しないときに前記第1入力を含む信号パスの遅延故障を検出すること

を特徴とする論理回路の故障検出方法。

【請求項2】

前記スキャンシフト期間に前記第1スキャンフリップフロップの前記1つおよび前記第2スキャンフリップフロップに互いに異なる論理を設定し、前記一対の第1スキャンフリップフロップに同じ論理を設定し、前記キャプチャ期間に、前記第1および第2スキャンフリップフロップに2つのクロックパルスを供給し、前記第3ユーザロジックの前記第1スキャンフリップフロップに保持される論理が変化しないときに前記第2入力を含む信号パスの遅延故障を検出すること

を特徴とする請求項1に記載の論理回路の故障検出方法。

【請求項3】

前記制御点は、前記第2スキャンフリップフロップのデータ出力と前記第2論理ゲートとの間に配置され、前記テストモード中に、前記第2スキャンフリップフロップからの出力信号を前記第2論理ゲートに伝達し、前記テストモードを除く期間に、前記出力信号の前記第2論理ゲートへの伝達をマスクするとともに、前記第2ユーザロジックからの出力信号を前記第2論理ゲートを介して前記第1論理ゲートに伝達するための論理値を前記第2論理ゲートに出力するマスク回路を備え、

前記スキャンシフト期間および前記キャプチャ期間の動作を、前記テストモード中に実施すること

を特徴とする請求項1または請求項2に記載の論理回路の故障検出方法。

【請求項4】

複数のフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、前記第1ユーザロジックの出力に接続される第1入力および第2ユーザロジックの出力に接続される第2入力を有する第1論理ゲートと、前記第1論理ゲートの出力に接続され、少なくとも1つのフリップフロップを含む第3ユーザロジックとを有する論理回路のテスト回路挿入方法であって、

前記フリップフロップをデータ入力およびスキャン入力を各々有する第1スキャンフリップフロップに置き換える処理と、

データ入力およびスキャン入力を有する第2スキャンフリップフロップと、一対の入力が前記第2スキャンフリップフロップのデータ出力および前記第2ユーザロジックの出力にそれぞれ接続され、出力が前記第2入力に接続された第2論理ゲートとを有する制御点を、前記第2ユーザロジックと前記第1論理ゲートとの間に挿入する処理と、

前記第2スキャンフリップフロップのデータ入力に前記第1スキャンフリップフロップの1つのデータ出力を接続する処理と

を含むことを特徴とする論理回路のテスト回路挿入方法。

【請求項5】

テストモード中に、前記第2スキャンフリップフロップからの出力信号を前記第2論理ゲートに伝達し、前記テストモードを除く期間に、前記出力信号の前記第2論理ゲートへの伝達をマスクするとともに、前記第2ユーザロジックからの出力信号を前記第2論理ゲートを介して前記第1論理ゲートに伝達するための論理値を前記第2論理ゲートに出力するマスク回路を、前記第2スキャンフリップフロップのデータ出力と前記第2論理ゲートとの間に配置する処理を含むこと

を特徴とする請求項4に記載の論理回路のテスト回路挿入方法。

【請求項6】

複数のフリップフロップを含む第1ユーザロジックと、第2ユーザロジックと、前記第1ユーザロジックの出力に接続される第1入力および第2ユーザロジックの出力に接続される第2入力を有する第1論理ゲートと、前記第1論理ゲートの出力に接続され、少なくとも1つのフリップフロップを含む第3ユーザロジックとを有する論理回路のテスト回路挿入装置であって、

前記フリップフロップをデータ入力およびスキャン入力を各々有する第1スキャンフリップフロップに置き換える処理と、

データ入力およびスキャン入力を有する第2スキャンフリップフロップと、一対の入力が前記第2スキャンフリップフロップのデータ出力および前記第2ユーザロジックの出力にそれぞれ接続され、出力が前記第2入力に接続された第2論理ゲートとを有する制御点を、前記第2ユーザロジックと前記第1論理ゲートとの間に挿入する処理と、

前記第2スキャンフリップフロップのデータ入力に前記第1スキャンフリップフロップの1つのデータ出力を接続する処理と

を実施することを特徴とする論理回路のテスト回路挿入装置。

【請求項7】

テストモード中に、前記第2スキャンフリップフロップからの出力信号を前記第2論理ゲートに伝達し、前記テストモードを除く期間に、前記出力信号の前記第2論理ゲートへの伝達をマスクし、前記第2ユーザロジックからの出力信号を前記第2論理ゲートを介して前記第1論理ゲートに伝達するための論理値を前記第2論理ゲートに出力するマスク回路を、前記第2スキャンフリップフロップのデータ出力と前記第2論理ゲートとの間に配置する処理を実施すること

を特徴とする請求項6に記載の論理回路のテスト回路挿入装置。

【請求項8】

データ入力およびスキャン入力を有する複数の第1スキャンフリップフロップを含む第1ユーザロジックと、

第2ユーザロジックと、

前記第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、

少なくとも1つの第1スキャンフリップフロップを含み、前記第1論理ゲートの出力に接続された第3ユーザロジックと、

前記第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が前記第2スキャンフリップフロップのデータ出力およびテストモードを示すテストモード端子に接続されたマスク回路と、一対の入力が前記マスク回路の出力および前記第2ユーザロジックの出力にそれぞれ接続され、出力が前記第1論理ゲートの第2入力に接続された第2論理ゲートとを有する制御点と

を備え、

前記マスク回路は、前記テストモード中に、前記第2スキャンフリップフロップからの出力信号を前記第2論理ゲートに伝達し、前記テストモードを除く期間に、前記出力信号の前記第2論理ゲートへの伝達をマスクするとともに、前記第2ユーザロジックからの出力信号を前記第2論理ゲートを介して前記第1論理ゲートに伝達するための論理値を前記第2論理ゲートに出力すること

を特徴とする半導体集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2013−92382(P2013−92382A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−232707(P2011−232707)

【出願日】平成23年10月24日(2011.10.24)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月24日(2011.10.24)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]