論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力電圧のレベルに応じた電圧を生成する論理回路に関する。

【背景技術】

【0002】

従来から、論理演算を行う電気回路として論理回路が広く用いられている。この論理回路の代表例としては、P型のFETとN型のFETとを組み合わせて構成されたCMOS(Complementary Metal Oxide Semiconductor)論理ゲートが知られている(例えば、下記非特許文献1参照)。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】A.ヘイ、R.アレン 編、原康夫、中山健、松田和典 訳 「ファインマン計算機科学」岩波書店発行、1999年

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来のCMOS構造では、P型FETとN型FETとが組み合わされており、2種のチャネル材料によって構成される必要があるため、製造プロセスが複雑化する傾向があった。また、P型FETとN型FETとでは一般に電流密度が異なるために等しい電流が得られるように素子サイズを変えてレイアウトする必要があるために、設計やレイアウトが複雑になる傾向にもあった。さらに、P型FETとN型FETとが共存しているので、ラッチアップ現象や、電流値を均一にするために一方の素子面積を大きくすることによる素子容量の増大に起因した回路動作速度の制限等が懸念され、論理回路全体での安定動作に限界が生じていた。加えて、従来型のP型FET或いはN型FETのみで構成する論理ゲートは、常時回路に電流が流れるために消費電力が大きくなる傾向にもあった。

【0005】

そこで、本発明は、かかる課題に鑑みて為されたものであり、安定した高速動作を低消費電力で実現しつつ、製造工程及び設計工程も簡素化することが可能な論理回路を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するため、本発明の論理回路は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2の電界効果トランジスタを備える論理回路であって、第1及び第2の電界効果トランジスタのうちの少なくとも1つは、ゲート端子が接続されるゲート電極膜と、半導体材料からなるチャネル層と、ゲート電極膜とチャネル層との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層と、を有する。

【0007】

このような論理回路によれば、論理回路を構成する2つの電界効果トランジスタのうちの少なくとも1つはゲート電極膜とチャネル層との間に電荷を蓄積及び放出する電荷蓄積構造を備えているので、入力信号に対してスイッチング動作が逆である2つの電界効果トランジスタを、P型及びN型のトランジスタのどちらでも実現することができる。その結果、P型FET又はN型FETのみで回路を構成できるので、論理回路全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。さらに、電荷蓄積構造を備える電界効果トランジスタを採用することで消費電力を低減することもできる。

【0008】

ここで、電荷蓄積層においては、電荷蓄積構造が、チャネル層或いはゲート電極膜との間で電荷を蓄積及び放出可能に構成されている、ことが好適である。さらに、電荷蓄積層においては、電荷蓄積構造が、チャネル層或いはゲート電極膜側に片寄って配置されている、ことが好適である。さらに、電荷蓄積層においては、電荷蓄積構造が、電荷に対する特性が異なる2層によって挟まれて配置されている、ことが好適である。かかる構成を採れば、P型FET及びN型FETのいずれを使用した場合でも、入力信号に対するスイッチング動作を任意に設定することができる。

【0009】

また、第1及び第2の電界効果トランジスタはN型トランジスタである、ことが好適である。この場合、N型FETのみで回路を構成できるので、論理回路全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。さらには、移動度の高いキャリアを用いることで、更なる高速動作を実現することができる。

【0010】

また、第1及び第2の電界効果トランジスタはP型トランジスタである、ことも好適である。この場合、P型FETのみで回路を構成できるので、論理回路全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。

【0011】

また、バイアス電源、グラウンド、及びゲート端子の少なくとも1つには、雑音源が接続されている、ことも好適である。かかる雑音源を備えれば、意図的に雑音を導入することで、出力振幅が十分大きくでき消費電力を低減できる。

【0012】

電荷蓄積構造は、電荷蓄積層中における導電材料層によって構成されている、ことが好適である。また、電荷蓄積構造は、電荷蓄積層中における欠陥によって生成されていてもよいし、電荷蓄積層中における組成比のずれによって生成されていてもよいし、電荷蓄積層中における微小材料によって生成されていてもよいし、電荷蓄積層中における不純物原子或いは不純物分子によって構成されていてもよい。

【発明の効果】

【0013】

本発明による論理回路によれば、安定した高速動作を低消費電力で実現しつつ、製造工程及び設計プロセスも簡素化することができる。

【図面の簡単な説明】

【0014】

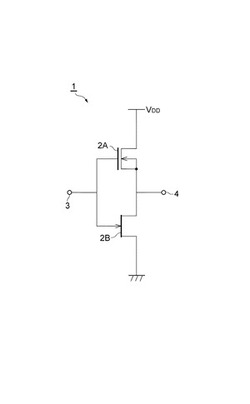

【図1】本発明の好適な一実施形態にかかる論理回路1の回路図である。

【図2】図1のFET2Bのゲート電圧VGに対するドレイン電流IDSの特性を示すグラフである。

【図3】図1のFET2Aの構造を示す半導体基板の垂直方向に沿った断面図である。

【図4】図3の電荷蓄積層16の構造を示す半導体基板の垂直方向に沿った断面図である。

【図5】図3の電荷蓄積層16の別の構造を示す半導体基板の垂直方向に沿った断面図である。

【図6】図3の電荷蓄積層16の別の構造を示す半導体基板の垂直方向に沿った断面図である。

【図7】図3の電荷蓄積層16の別の構造を示す半導体基板の垂直方向に沿った断面図である。

【図8】図1のFET2Aのゲート電圧VGに対するドレイン電流IDSの特性を示すグラフである。

【図9】本発明の実施形態にかかる論理回路1の動作を説明するための回路図である。

【図10】図1の論理回路1における入力電圧及び出力電圧のタイミングチャートである。

【図11】図1の論理回路1における入力電圧及び出力電圧のタイミングチャートである。

【図12】本発明の変形例にかかる論理回路101の回路図である。

【図13】図12のFET2Cに含まれる電荷蓄積層116の構造を示す半導体基板の垂直方向に沿った断面図である。

【図14】本発明の変形例にかかる論理回路201の回路図である。

【図15】本発明の変形例にかかる論理回路301の回路図である。

【発明を実施するための形態】

【0015】

以下、図面を参照しつつ本発明の論理回路の好適な実施形態について詳細に説明する。なお、図面の説明においては同一又は相当部分には同一符号を付し、重複する説明を省略する。

【0016】

図1は、本発明の好適な一実施形態にかかる論理回路1の回路図である。同図に示す論理回路1は、入力電圧のレベルに応じた2種類の出力電圧を生成するためのアナログ回路であり、2つの電界効果トランジスタ(FET:Field Effect Transistor)2A,2Bが、バイアス電圧源とグラウンドとの間で直列に接続されて構成されている。すなわち、FET2Aのドレイン端子(電流端子)がバイアス電圧源に接続され、FET2Aのソース端子(電流端子)がFET2Bのドレイン端子に接続され、FET2Bのソース端子はグラウンドに接続されている。さらに、FET2A及びFET2Bのゲート端子(制御端子)が共通に入力端子3に接続されると共に、FET2Aのソース端子及びFET2Bのドレイン端子は共通に出力端子4に接続されている。この入力端子3からFET2A及びFET2Bのゲート端子に入力電圧が印加され、出力端子4から出力電圧が出力される。

【0017】

FET2Bは、N型(Nチャンネル)トランジスタであり、具体的には、チャネル材料としてGaAs等を含むMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)、MESFET(MetalSemiconductor Field Effect Transistor)、及びHEMT(High Electron MobilityTransistor)等のキャリアとして電子を利用するFETである。このFET2Bは、入力端子3からゲート端子にハイレベルの入力電圧が与えられるとオンになり、入力端子3からゲート端子にローレベルの入力電圧が与えられるとオフになる特性を有する。図2には、FET2Bにおいて、ドレイン−ソース間の電圧を0.1Vに設定した際のゲート電圧VGに対するドレイン−ソース間電流であるドレイン電流IDSの特性の一例を示している。このように、入力電圧として0.5Vのハイレベルの電圧を印加するとドレイン電流IDSが流れ、FET2Bがオン状態となる。一方で、入力電圧として0Vのローレベルの電圧を印加するとドレイン電流IDSはほとんど流れず、FET2Bがオフ状態となる。

【0018】

FET2Aは、ゲート端子が接続されるゲート電極膜と電子走行層であるチャネル層との間に電荷蓄積層を含み、この電荷蓄積層において電荷を蓄積及び放出可能に構成されたN型FETである。図3は、FET2Aの構造を示す半導体基板の垂直方向に沿った断面図である。同図に示すように、FET2Aは、GaAs基板10上に、下部障壁層11、チャネル層12、スペーサ層13、局所ドーピング層14、上部障壁層15、電荷蓄積層16、及びゲート電極膜17がこの順で積層されて構成されている。

【0019】

下部障壁層11は、例えば、アンドープの半導体材料であるAlGaAsによって膜厚100nmで形成されており、FET2Aのサブスレッショルド特性を高める機能を有する。チャネル層12は、電子が走行する領域である電子走行層であり、例えば、アンドープの半導体材料であるGaAsによって膜厚20nmで形成されている。スペーサ層13は、例えば、アンドープのAlGaAsによって膜厚12nmで形成されており、局所ドーピング層14にドープしたSiのチャネルへの拡散を抑え、移動度を高めるための層である。局所ドーピング層14は、SiでデルタドープされたAlGaAs層であり、チャネルにキャリアを発生させるための層である。上部障壁層15は、アンドープのAlGaAsによって膜厚50nmで形成されており、ゲート容量の誘電体層としての役割、ゲートリーク電流を抑える役割を有する。

【0020】

図4を参照しながら、チャネル層12とゲート電極膜17との間に配置された電荷蓄積層16の構造の一例について詳述する。電荷蓄積層16は、2層のワイドギャップ層18a,18bの間に、金属薄膜、ポリシリコン膜、狭バンドギャップ半導体膜等の導電材料によって電荷蓄積構造を構成する電荷トラップ層(導電材料層)19を挟んだような構造を有する。このワイドギャップ層18a,18bは、Siチャネルの場合はSiO2、Al2O3、SiN、SiNO、SiON等、GaAs系化合物半導体チャネルの場合はAlAs等の絶縁材料によって形成される。なお、電荷トラップ層19は、ワイドギャップ層18bの膜厚がワイドギャップ層18aの膜厚よりも厚く形成されることによって、ゲート電極膜17からチャネル層12に片寄って配置されている。このように、電荷トラップ層19を配置することで、電荷蓄積層16では、ゲート電圧に応じてチャネル層12と電荷トラップ層19との間で電子を移動させることにより、電荷をチャネル層12との間で充電(蓄積)及び放電(放出)させることができる。

【0021】

また、電荷蓄積層16としては、図5に示すように、1層のワイドギャップ層中に欠陥や原子組成比(ストイキオメトリ)のずれを複数あるいは単数形成させることによって電荷蓄積構造である電荷トラップ20を点在させた構造を採用してもよい。この場合も、複数又は単数の電荷トラップ20はゲート電極膜17からチャネル層12に片寄って配置される。例えば、このような欠陥の製法の一例としては、化学気相堆積法によって水素を含む原料ガスを用いSiNを成膜する方法が挙げられる。この方法によれば、膜中にSi−HやN−H結合が不可避的に含有され、この水素が脱離することでSiやNの未結合手が生成され、この未結合手が電荷トラップとして機能する。

【0022】

また、電荷蓄積層16としては、図6に示すように、必ずしも電荷蓄積構造がゲート電極膜17からチャネル層12に片寄って配置される構造には限定されず、キャリアをトンネルさせる確率であるキャリア遷移率が異なる2層のワイドギャップ層21a,21bの間に電荷トラップ層19が挟まれたような構造が採用されてもよい。例えば、キャリア遷移率の小さいワイドギャップ層21b、及びキャリア遷移率の大きいワイドギャップ層21aの材料の組み合わせとして、SiO2とSiN、Al2O3とSiN、SiO2とSiON、AlAsとAlGaAsの組み合わせが挙げられる。このようなワイドギャップ層21a,21bとしては、キャリアを熱的励起、電界放出させる際のキャリア生成率の異なる材料を採用してもよい。この場合、チャネル層12側のワイドギャップ層21aのキャリア遷移率或いはキャリア生成率が、ゲート電極膜17側のワイドギャップ層21bのキャリア遷移率或いはキャリア生成率よりも大きくなるように設定される。

【0023】

さらに、電荷蓄積層16としては、図7に示すように、1層のワイドギャップ層中に半導体材料等の微小材料を複数形成させることによって電荷蓄積構造である電荷トラップ22を点在させた構造を採用してもよい。このような微小材料による電荷トラップの生成方法としては、Si系の場合は、高周波プラズマCVD法によりSiドットを形成し、その後SiO2を堆積する方法や、GaAs系の場合は、結晶成長法によってGaAsやAlGaAs上にInAsを僅かに成長させて結晶格子定数の違いによりInAsを凝集させてドットを形成し、それに引き続いてGaAs或いはAlGaAsを障壁層として成長させる方法が挙げられる。さらに、1層のワイドギャップ層中に不純物原子や不純物分子をドープすることによって電荷蓄積構造である電荷トラップ22を点在させた構造を採用してもよい。この場合も、複数の電荷トラップ22は、ゲート電極膜17からチャネル層12に片寄って配置される。

【0024】

図8には、上述した構造を有するFET2Aにおいて、ドレイン−ソース間の電圧を0.1Vに設定した際のゲート電圧VGに対するドレイン電流IDSの特性の一例を示している。このように、FET2Aは、電荷蓄積可能なゲート構造を有することで伝達特性としてヒステリシスを描く双安定系を実現している。詳細には、入力電圧としてローレベルの電圧が与えられると、電荷蓄積層16に充電されている電荷がチャネル層12に向けて放電されて伝達特性が第1の系S1に切り替えられる。この状態で入力電圧としてローレベルの所定電圧(例えば、0V)が印加されると、ドレイン電流IDSが流れ、FET2Aがオン状態となる。一方で、入力電圧としてハイレベルの電圧が与えられると、チャネル層12から電荷蓄積層16に電荷が充電されて伝達特性が第2の系S2に切り替えられる。この状態で入力電圧としてハイレベルの所定電圧(例えば、0.5V)が印加されると、ドレイン電流IDSが小さくなり、FET2Aがオフ状態となる。この結果から、FET2Aは、N型FETであるが、ゲート入力電圧に対するスイッチング動作に関しては従来のP型FETと同様な動作を実現する。

【0025】

次に、図9及び図10を参照しながら、FET2A,2Bによって構成される論理回路1の動作について説明する。図9(a)には、入力端子3にハイレベルの電圧が入力された場合の状態を示している。この場合は、FET2Aの電荷蓄積層16に電荷(電子)が蓄積されることによりFET2Aがオフ状態に切り替えられると同時に、FET2Bはオン状態に切り替えられる。その結果、出力端子4にはグラウンド電位“0V”が出力される。図9(b)には、入力端子3にローレベルの電圧が入力された場合の状態を示している。この場合は、FET2Aの電荷蓄積層16から電荷(電子)が放出されることによりFET2Aがオン状態に切り替えられると同時に、FET2Bはオフ状態に切り替えられる。その結果、出力端子4にはバイアス電圧源の電位VDDが出力される。

【0026】

また、図10には、バイアス電圧VDDを0.5Vに設定した際の論理回路1における入力電圧及び出力電圧のタイミングチャートを示している。入力電圧VINとして、ローレベルが0Vで、ハイレベルが0.5Vのパルス信号を入力した場合、入力信号と同期した出力レベルを有するパルス状の出力電圧VOUTが生成される。ただし、雑音を含まない入力電圧の場合はFET2Aの伝達特性の系が完全に切り替えられないために、出力電圧VOUTのローレベルが下がりきらずに出力振幅が大きくとれないことになる。これに対して、雑音成分を含む入力電圧VINの場合には、FET2Aのヒステリシス特性を利用した確率共鳴現象が発生し、雑音が電荷蓄積層16における電荷充放電の緩和を抑制するために、出力電圧VOUTのローレベルが0V近くまで下がる結果、十分に出力振幅を大きくできる。このことから、論理回路1で利用する入力電圧としては雑音を含むパルス電圧であることが好ましいことがわかる。このような雑音は、入力端子3、及びFET2A,2Bのゲート端子に雑音源を接続することによって意図的に付加されてもよいし、電源や抵抗素子等により自然発生した雑音が利用されてもよい。このような雑音源としては、SiN膜を絶縁ゲートに挿入したSi MOSFET等が利用できる。また、このような雑音源は、バイアス電圧源(すなわち、FET2Aのドレイン端子側)又はグラウンド(すなわち、FET2Bのソース端子側)に接続されてもよい。これによっても、FET2Aのヒステリシス特性を利用した確率共鳴現象を発生させることができる。

【0027】

以上説明した論理回路1によれば、論理回路1を構成する2つのFET2A,2BのうちのFET2Aは、ゲート電極膜17とチャネル層12との間に電荷を蓄積及び放出する電荷蓄積層16を備えているので、入力信号に対してスイッチング動作が逆である2つのFETを、N型のトランジスタのみで実現することができる。その結果、ラッチアップ現象等の懸念が無くなり論理回路1全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。さらに、電荷蓄積構造を備えるFETを採用することで消費電力を低減することもできる。また、FET2A,2Bは共にN型トランジスタであるので、移動度の高いキャリアを用いることで、更なる高速動作を実現することができる。

【0028】

ここで、電荷蓄積層16においては、電荷蓄積構造がチャネル層12側に片寄って配置されているので、N型のFET2Bに対して入力信号に対するスイッチング動作を逆に設定することができる。

【0029】

さらに、論理回路1では、入力電圧として雑音を含むパルス電圧を利用しているので、入力に雑音を含むことで出力電圧VOUTの出力振幅を大きくとることができ、更なる低消費電力化及び安定動作を実現することができる。

【0030】

なお、論理回路1では、図11に示すような入力電圧VINを利用することも可能である。すなわち、入力信号としてパルス電圧の立ち上がりタイミング及び立ち下がりタイミングにプリパルスが付加された信号を利用した場合は、プリパルスが発生したタイミングでFET2Aの伝達特性の系を完全に切り替えることができるので、出力電圧VOUTのレベルを0VとVDDとの間で切り替えることが可能になる。このようなプリパルスを入力電圧に付加する方法としては、配線間の容量結合や配線の自己インダクタンスによって変位電流を引き起こす方法が選択できる。ただし、電荷蓄積層16における電荷蓄積効果にはリテンションタイムと呼ばれる有限の電荷保持時間が存在するため、電荷の充電/放電後に徐々に電荷が放電/充電されてヒステリシスが小さくなり、出力電圧VOUTの波形に歪が発生する傾向にある。これに対して、図10に示すように、入力電圧に雑音が付加された場合は、電荷蓄積層16における電荷の蓄積状態及び消去状態に対して雑音誘起安定(Noise-Induced Stabilization)現象が引き起こされて波形の歪が生じにくいため、より好ましい。

【0031】

なお、本発明は、前述した実施形態に限定されるものではない。

【0032】

例えば、論理回路に含まれる2つのFETの両方が電荷蓄積層を有するものであってもよい。図12には、本発明の変形例に係る論理回路101の構成を示している。論理回路101の論理回路1との相違点は、FET2Bに替えてFET2Cを備える点である。このFET2Cは、基本構造はFET2Aとほぼ同一であり、電荷蓄積層が電荷をゲート電極膜17との間で充電及び放電させる機能を有する点が異なる。図13には、FET2Cの電荷蓄積層116の構造を示している。電荷蓄積層116において、電荷トラップ層19は、ゲート電極膜17側のワイドギャップ層118bの膜厚がチャネル層12側のワイドギャップ層118aの膜厚よりも薄く形成されることによって、チャネル層12からゲート電極膜17に片寄って配置されている。このように、電荷トラップ層19を配置することで、電荷蓄積層116では、ゲート電圧に応じてゲート電極膜17と電荷トラップ層19との間で電子を移動させることにより、電荷をゲートとの間で充電(蓄積)及び放電(放出)させることができる。この場合、電荷蓄積層116としては、図5〜7に示した電荷蓄積構造と同様な構造であってもよい。このような論理回路101によっても、2つのFET2A、2Bが入力電圧に対して逆のスイッチング動作を行うように構成され、論理回路を実現できる。

【0033】

また、図14に示すように、2つのP型のFETによって論理回路を構成してもよい。同図に示す論理回路201は、バイアス電圧源とグラウンドとの間にFET2DとFET2Eとが直列に接続されて構成される。FET2Dは、P型(Pチャンネル)のMOSFET、MESFET、及びHEMT等のキャリアとしてイオンを利用するFETである。また、FET2Eは、電荷蓄積層においてチャネル層との間で電荷を蓄積及び放出可能に構成されたP型FETであり、基本構造はFET2Aと同様である。このような論理回路101によっても、2つのFET2D、2Eが入力電圧に対して逆のスイッチング動作を行うように構成され、論理回路を実現できる。また、2つのFETが共にP型のトランジスタであるので、ラッチアップ現象等の懸念が無くなり論理回路1全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。さらに、電荷蓄積構造を備えるFETを採用することで消費電力を低減することもできる。

【0034】

さらに、図15に示すように、2つのP型のFETによって論理回路を構成してもよい。論理回路301の論理回路201との相違点は、FET2Dに替えてFET2Fを備える点である。このFET2Fは、基本構造はFET2Dとほぼ同一であり、電荷蓄積層が電荷をゲート電極膜との間で充電及び放電させる機能を有する点が異なる。この場合、電荷蓄積層としては、図13、及び図5〜7に示した電荷蓄積構造と同様な構造であってもよい。このような論理回路301によっても、2つのFET2F、2Eが入力電圧に対して逆のスイッチング動作を行うように構成され、論理回路を実現できる。

【符号の説明】

【0035】

1,101,201,301…論理回路、2A,2B,2C,2D,2E,2F…FET、3…入力端子、4…出力端子、12…チャネル層、16,116…電荷蓄積層、17…ゲート電極膜、19…電荷トラップ層(電荷蓄積構造、導電材料層)、20、22…電荷トラップ(電荷蓄積構造)。

【技術分野】

【0001】

本発明は、入力電圧のレベルに応じた電圧を生成する論理回路に関する。

【背景技術】

【0002】

従来から、論理演算を行う電気回路として論理回路が広く用いられている。この論理回路の代表例としては、P型のFETとN型のFETとを組み合わせて構成されたCMOS(Complementary Metal Oxide Semiconductor)論理ゲートが知られている(例えば、下記非特許文献1参照)。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】A.ヘイ、R.アレン 編、原康夫、中山健、松田和典 訳 「ファインマン計算機科学」岩波書店発行、1999年

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来のCMOS構造では、P型FETとN型FETとが組み合わされており、2種のチャネル材料によって構成される必要があるため、製造プロセスが複雑化する傾向があった。また、P型FETとN型FETとでは一般に電流密度が異なるために等しい電流が得られるように素子サイズを変えてレイアウトする必要があるために、設計やレイアウトが複雑になる傾向にもあった。さらに、P型FETとN型FETとが共存しているので、ラッチアップ現象や、電流値を均一にするために一方の素子面積を大きくすることによる素子容量の増大に起因した回路動作速度の制限等が懸念され、論理回路全体での安定動作に限界が生じていた。加えて、従来型のP型FET或いはN型FETのみで構成する論理ゲートは、常時回路に電流が流れるために消費電力が大きくなる傾向にもあった。

【0005】

そこで、本発明は、かかる課題に鑑みて為されたものであり、安定した高速動作を低消費電力で実現しつつ、製造工程及び設計工程も簡素化することが可能な論理回路を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するため、本発明の論理回路は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2の電界効果トランジスタを備える論理回路であって、第1及び第2の電界効果トランジスタのうちの少なくとも1つは、ゲート端子が接続されるゲート電極膜と、半導体材料からなるチャネル層と、ゲート電極膜とチャネル層との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層と、を有する。

【0007】

このような論理回路によれば、論理回路を構成する2つの電界効果トランジスタのうちの少なくとも1つはゲート電極膜とチャネル層との間に電荷を蓄積及び放出する電荷蓄積構造を備えているので、入力信号に対してスイッチング動作が逆である2つの電界効果トランジスタを、P型及びN型のトランジスタのどちらでも実現することができる。その結果、P型FET又はN型FETのみで回路を構成できるので、論理回路全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。さらに、電荷蓄積構造を備える電界効果トランジスタを採用することで消費電力を低減することもできる。

【0008】

ここで、電荷蓄積層においては、電荷蓄積構造が、チャネル層或いはゲート電極膜との間で電荷を蓄積及び放出可能に構成されている、ことが好適である。さらに、電荷蓄積層においては、電荷蓄積構造が、チャネル層或いはゲート電極膜側に片寄って配置されている、ことが好適である。さらに、電荷蓄積層においては、電荷蓄積構造が、電荷に対する特性が異なる2層によって挟まれて配置されている、ことが好適である。かかる構成を採れば、P型FET及びN型FETのいずれを使用した場合でも、入力信号に対するスイッチング動作を任意に設定することができる。

【0009】

また、第1及び第2の電界効果トランジスタはN型トランジスタである、ことが好適である。この場合、N型FETのみで回路を構成できるので、論理回路全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。さらには、移動度の高いキャリアを用いることで、更なる高速動作を実現することができる。

【0010】

また、第1及び第2の電界効果トランジスタはP型トランジスタである、ことも好適である。この場合、P型FETのみで回路を構成できるので、論理回路全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。

【0011】

また、バイアス電源、グラウンド、及びゲート端子の少なくとも1つには、雑音源が接続されている、ことも好適である。かかる雑音源を備えれば、意図的に雑音を導入することで、出力振幅が十分大きくでき消費電力を低減できる。

【0012】

電荷蓄積構造は、電荷蓄積層中における導電材料層によって構成されている、ことが好適である。また、電荷蓄積構造は、電荷蓄積層中における欠陥によって生成されていてもよいし、電荷蓄積層中における組成比のずれによって生成されていてもよいし、電荷蓄積層中における微小材料によって生成されていてもよいし、電荷蓄積層中における不純物原子或いは不純物分子によって構成されていてもよい。

【発明の効果】

【0013】

本発明による論理回路によれば、安定した高速動作を低消費電力で実現しつつ、製造工程及び設計プロセスも簡素化することができる。

【図面の簡単な説明】

【0014】

【図1】本発明の好適な一実施形態にかかる論理回路1の回路図である。

【図2】図1のFET2Bのゲート電圧VGに対するドレイン電流IDSの特性を示すグラフである。

【図3】図1のFET2Aの構造を示す半導体基板の垂直方向に沿った断面図である。

【図4】図3の電荷蓄積層16の構造を示す半導体基板の垂直方向に沿った断面図である。

【図5】図3の電荷蓄積層16の別の構造を示す半導体基板の垂直方向に沿った断面図である。

【図6】図3の電荷蓄積層16の別の構造を示す半導体基板の垂直方向に沿った断面図である。

【図7】図3の電荷蓄積層16の別の構造を示す半導体基板の垂直方向に沿った断面図である。

【図8】図1のFET2Aのゲート電圧VGに対するドレイン電流IDSの特性を示すグラフである。

【図9】本発明の実施形態にかかる論理回路1の動作を説明するための回路図である。

【図10】図1の論理回路1における入力電圧及び出力電圧のタイミングチャートである。

【図11】図1の論理回路1における入力電圧及び出力電圧のタイミングチャートである。

【図12】本発明の変形例にかかる論理回路101の回路図である。

【図13】図12のFET2Cに含まれる電荷蓄積層116の構造を示す半導体基板の垂直方向に沿った断面図である。

【図14】本発明の変形例にかかる論理回路201の回路図である。

【図15】本発明の変形例にかかる論理回路301の回路図である。

【発明を実施するための形態】

【0015】

以下、図面を参照しつつ本発明の論理回路の好適な実施形態について詳細に説明する。なお、図面の説明においては同一又は相当部分には同一符号を付し、重複する説明を省略する。

【0016】

図1は、本発明の好適な一実施形態にかかる論理回路1の回路図である。同図に示す論理回路1は、入力電圧のレベルに応じた2種類の出力電圧を生成するためのアナログ回路であり、2つの電界効果トランジスタ(FET:Field Effect Transistor)2A,2Bが、バイアス電圧源とグラウンドとの間で直列に接続されて構成されている。すなわち、FET2Aのドレイン端子(電流端子)がバイアス電圧源に接続され、FET2Aのソース端子(電流端子)がFET2Bのドレイン端子に接続され、FET2Bのソース端子はグラウンドに接続されている。さらに、FET2A及びFET2Bのゲート端子(制御端子)が共通に入力端子3に接続されると共に、FET2Aのソース端子及びFET2Bのドレイン端子は共通に出力端子4に接続されている。この入力端子3からFET2A及びFET2Bのゲート端子に入力電圧が印加され、出力端子4から出力電圧が出力される。

【0017】

FET2Bは、N型(Nチャンネル)トランジスタであり、具体的には、チャネル材料としてGaAs等を含むMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)、MESFET(MetalSemiconductor Field Effect Transistor)、及びHEMT(High Electron MobilityTransistor)等のキャリアとして電子を利用するFETである。このFET2Bは、入力端子3からゲート端子にハイレベルの入力電圧が与えられるとオンになり、入力端子3からゲート端子にローレベルの入力電圧が与えられるとオフになる特性を有する。図2には、FET2Bにおいて、ドレイン−ソース間の電圧を0.1Vに設定した際のゲート電圧VGに対するドレイン−ソース間電流であるドレイン電流IDSの特性の一例を示している。このように、入力電圧として0.5Vのハイレベルの電圧を印加するとドレイン電流IDSが流れ、FET2Bがオン状態となる。一方で、入力電圧として0Vのローレベルの電圧を印加するとドレイン電流IDSはほとんど流れず、FET2Bがオフ状態となる。

【0018】

FET2Aは、ゲート端子が接続されるゲート電極膜と電子走行層であるチャネル層との間に電荷蓄積層を含み、この電荷蓄積層において電荷を蓄積及び放出可能に構成されたN型FETである。図3は、FET2Aの構造を示す半導体基板の垂直方向に沿った断面図である。同図に示すように、FET2Aは、GaAs基板10上に、下部障壁層11、チャネル層12、スペーサ層13、局所ドーピング層14、上部障壁層15、電荷蓄積層16、及びゲート電極膜17がこの順で積層されて構成されている。

【0019】

下部障壁層11は、例えば、アンドープの半導体材料であるAlGaAsによって膜厚100nmで形成されており、FET2Aのサブスレッショルド特性を高める機能を有する。チャネル層12は、電子が走行する領域である電子走行層であり、例えば、アンドープの半導体材料であるGaAsによって膜厚20nmで形成されている。スペーサ層13は、例えば、アンドープのAlGaAsによって膜厚12nmで形成されており、局所ドーピング層14にドープしたSiのチャネルへの拡散を抑え、移動度を高めるための層である。局所ドーピング層14は、SiでデルタドープされたAlGaAs層であり、チャネルにキャリアを発生させるための層である。上部障壁層15は、アンドープのAlGaAsによって膜厚50nmで形成されており、ゲート容量の誘電体層としての役割、ゲートリーク電流を抑える役割を有する。

【0020】

図4を参照しながら、チャネル層12とゲート電極膜17との間に配置された電荷蓄積層16の構造の一例について詳述する。電荷蓄積層16は、2層のワイドギャップ層18a,18bの間に、金属薄膜、ポリシリコン膜、狭バンドギャップ半導体膜等の導電材料によって電荷蓄積構造を構成する電荷トラップ層(導電材料層)19を挟んだような構造を有する。このワイドギャップ層18a,18bは、Siチャネルの場合はSiO2、Al2O3、SiN、SiNO、SiON等、GaAs系化合物半導体チャネルの場合はAlAs等の絶縁材料によって形成される。なお、電荷トラップ層19は、ワイドギャップ層18bの膜厚がワイドギャップ層18aの膜厚よりも厚く形成されることによって、ゲート電極膜17からチャネル層12に片寄って配置されている。このように、電荷トラップ層19を配置することで、電荷蓄積層16では、ゲート電圧に応じてチャネル層12と電荷トラップ層19との間で電子を移動させることにより、電荷をチャネル層12との間で充電(蓄積)及び放電(放出)させることができる。

【0021】

また、電荷蓄積層16としては、図5に示すように、1層のワイドギャップ層中に欠陥や原子組成比(ストイキオメトリ)のずれを複数あるいは単数形成させることによって電荷蓄積構造である電荷トラップ20を点在させた構造を採用してもよい。この場合も、複数又は単数の電荷トラップ20はゲート電極膜17からチャネル層12に片寄って配置される。例えば、このような欠陥の製法の一例としては、化学気相堆積法によって水素を含む原料ガスを用いSiNを成膜する方法が挙げられる。この方法によれば、膜中にSi−HやN−H結合が不可避的に含有され、この水素が脱離することでSiやNの未結合手が生成され、この未結合手が電荷トラップとして機能する。

【0022】

また、電荷蓄積層16としては、図6に示すように、必ずしも電荷蓄積構造がゲート電極膜17からチャネル層12に片寄って配置される構造には限定されず、キャリアをトンネルさせる確率であるキャリア遷移率が異なる2層のワイドギャップ層21a,21bの間に電荷トラップ層19が挟まれたような構造が採用されてもよい。例えば、キャリア遷移率の小さいワイドギャップ層21b、及びキャリア遷移率の大きいワイドギャップ層21aの材料の組み合わせとして、SiO2とSiN、Al2O3とSiN、SiO2とSiON、AlAsとAlGaAsの組み合わせが挙げられる。このようなワイドギャップ層21a,21bとしては、キャリアを熱的励起、電界放出させる際のキャリア生成率の異なる材料を採用してもよい。この場合、チャネル層12側のワイドギャップ層21aのキャリア遷移率或いはキャリア生成率が、ゲート電極膜17側のワイドギャップ層21bのキャリア遷移率或いはキャリア生成率よりも大きくなるように設定される。

【0023】

さらに、電荷蓄積層16としては、図7に示すように、1層のワイドギャップ層中に半導体材料等の微小材料を複数形成させることによって電荷蓄積構造である電荷トラップ22を点在させた構造を採用してもよい。このような微小材料による電荷トラップの生成方法としては、Si系の場合は、高周波プラズマCVD法によりSiドットを形成し、その後SiO2を堆積する方法や、GaAs系の場合は、結晶成長法によってGaAsやAlGaAs上にInAsを僅かに成長させて結晶格子定数の違いによりInAsを凝集させてドットを形成し、それに引き続いてGaAs或いはAlGaAsを障壁層として成長させる方法が挙げられる。さらに、1層のワイドギャップ層中に不純物原子や不純物分子をドープすることによって電荷蓄積構造である電荷トラップ22を点在させた構造を採用してもよい。この場合も、複数の電荷トラップ22は、ゲート電極膜17からチャネル層12に片寄って配置される。

【0024】

図8には、上述した構造を有するFET2Aにおいて、ドレイン−ソース間の電圧を0.1Vに設定した際のゲート電圧VGに対するドレイン電流IDSの特性の一例を示している。このように、FET2Aは、電荷蓄積可能なゲート構造を有することで伝達特性としてヒステリシスを描く双安定系を実現している。詳細には、入力電圧としてローレベルの電圧が与えられると、電荷蓄積層16に充電されている電荷がチャネル層12に向けて放電されて伝達特性が第1の系S1に切り替えられる。この状態で入力電圧としてローレベルの所定電圧(例えば、0V)が印加されると、ドレイン電流IDSが流れ、FET2Aがオン状態となる。一方で、入力電圧としてハイレベルの電圧が与えられると、チャネル層12から電荷蓄積層16に電荷が充電されて伝達特性が第2の系S2に切り替えられる。この状態で入力電圧としてハイレベルの所定電圧(例えば、0.5V)が印加されると、ドレイン電流IDSが小さくなり、FET2Aがオフ状態となる。この結果から、FET2Aは、N型FETであるが、ゲート入力電圧に対するスイッチング動作に関しては従来のP型FETと同様な動作を実現する。

【0025】

次に、図9及び図10を参照しながら、FET2A,2Bによって構成される論理回路1の動作について説明する。図9(a)には、入力端子3にハイレベルの電圧が入力された場合の状態を示している。この場合は、FET2Aの電荷蓄積層16に電荷(電子)が蓄積されることによりFET2Aがオフ状態に切り替えられると同時に、FET2Bはオン状態に切り替えられる。その結果、出力端子4にはグラウンド電位“0V”が出力される。図9(b)には、入力端子3にローレベルの電圧が入力された場合の状態を示している。この場合は、FET2Aの電荷蓄積層16から電荷(電子)が放出されることによりFET2Aがオン状態に切り替えられると同時に、FET2Bはオフ状態に切り替えられる。その結果、出力端子4にはバイアス電圧源の電位VDDが出力される。

【0026】

また、図10には、バイアス電圧VDDを0.5Vに設定した際の論理回路1における入力電圧及び出力電圧のタイミングチャートを示している。入力電圧VINとして、ローレベルが0Vで、ハイレベルが0.5Vのパルス信号を入力した場合、入力信号と同期した出力レベルを有するパルス状の出力電圧VOUTが生成される。ただし、雑音を含まない入力電圧の場合はFET2Aの伝達特性の系が完全に切り替えられないために、出力電圧VOUTのローレベルが下がりきらずに出力振幅が大きくとれないことになる。これに対して、雑音成分を含む入力電圧VINの場合には、FET2Aのヒステリシス特性を利用した確率共鳴現象が発生し、雑音が電荷蓄積層16における電荷充放電の緩和を抑制するために、出力電圧VOUTのローレベルが0V近くまで下がる結果、十分に出力振幅を大きくできる。このことから、論理回路1で利用する入力電圧としては雑音を含むパルス電圧であることが好ましいことがわかる。このような雑音は、入力端子3、及びFET2A,2Bのゲート端子に雑音源を接続することによって意図的に付加されてもよいし、電源や抵抗素子等により自然発生した雑音が利用されてもよい。このような雑音源としては、SiN膜を絶縁ゲートに挿入したSi MOSFET等が利用できる。また、このような雑音源は、バイアス電圧源(すなわち、FET2Aのドレイン端子側)又はグラウンド(すなわち、FET2Bのソース端子側)に接続されてもよい。これによっても、FET2Aのヒステリシス特性を利用した確率共鳴現象を発生させることができる。

【0027】

以上説明した論理回路1によれば、論理回路1を構成する2つのFET2A,2BのうちのFET2Aは、ゲート電極膜17とチャネル層12との間に電荷を蓄積及び放出する電荷蓄積層16を備えているので、入力信号に対してスイッチング動作が逆である2つのFETを、N型のトランジスタのみで実現することができる。その結果、ラッチアップ現象等の懸念が無くなり論理回路1全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。さらに、電荷蓄積構造を備えるFETを採用することで消費電力を低減することもできる。また、FET2A,2Bは共にN型トランジスタであるので、移動度の高いキャリアを用いることで、更なる高速動作を実現することができる。

【0028】

ここで、電荷蓄積層16においては、電荷蓄積構造がチャネル層12側に片寄って配置されているので、N型のFET2Bに対して入力信号に対するスイッチング動作を逆に設定することができる。

【0029】

さらに、論理回路1では、入力電圧として雑音を含むパルス電圧を利用しているので、入力に雑音を含むことで出力電圧VOUTの出力振幅を大きくとることができ、更なる低消費電力化及び安定動作を実現することができる。

【0030】

なお、論理回路1では、図11に示すような入力電圧VINを利用することも可能である。すなわち、入力信号としてパルス電圧の立ち上がりタイミング及び立ち下がりタイミングにプリパルスが付加された信号を利用した場合は、プリパルスが発生したタイミングでFET2Aの伝達特性の系を完全に切り替えることができるので、出力電圧VOUTのレベルを0VとVDDとの間で切り替えることが可能になる。このようなプリパルスを入力電圧に付加する方法としては、配線間の容量結合や配線の自己インダクタンスによって変位電流を引き起こす方法が選択できる。ただし、電荷蓄積層16における電荷蓄積効果にはリテンションタイムと呼ばれる有限の電荷保持時間が存在するため、電荷の充電/放電後に徐々に電荷が放電/充電されてヒステリシスが小さくなり、出力電圧VOUTの波形に歪が発生する傾向にある。これに対して、図10に示すように、入力電圧に雑音が付加された場合は、電荷蓄積層16における電荷の蓄積状態及び消去状態に対して雑音誘起安定(Noise-Induced Stabilization)現象が引き起こされて波形の歪が生じにくいため、より好ましい。

【0031】

なお、本発明は、前述した実施形態に限定されるものではない。

【0032】

例えば、論理回路に含まれる2つのFETの両方が電荷蓄積層を有するものであってもよい。図12には、本発明の変形例に係る論理回路101の構成を示している。論理回路101の論理回路1との相違点は、FET2Bに替えてFET2Cを備える点である。このFET2Cは、基本構造はFET2Aとほぼ同一であり、電荷蓄積層が電荷をゲート電極膜17との間で充電及び放電させる機能を有する点が異なる。図13には、FET2Cの電荷蓄積層116の構造を示している。電荷蓄積層116において、電荷トラップ層19は、ゲート電極膜17側のワイドギャップ層118bの膜厚がチャネル層12側のワイドギャップ層118aの膜厚よりも薄く形成されることによって、チャネル層12からゲート電極膜17に片寄って配置されている。このように、電荷トラップ層19を配置することで、電荷蓄積層116では、ゲート電圧に応じてゲート電極膜17と電荷トラップ層19との間で電子を移動させることにより、電荷をゲートとの間で充電(蓄積)及び放電(放出)させることができる。この場合、電荷蓄積層116としては、図5〜7に示した電荷蓄積構造と同様な構造であってもよい。このような論理回路101によっても、2つのFET2A、2Bが入力電圧に対して逆のスイッチング動作を行うように構成され、論理回路を実現できる。

【0033】

また、図14に示すように、2つのP型のFETによって論理回路を構成してもよい。同図に示す論理回路201は、バイアス電圧源とグラウンドとの間にFET2DとFET2Eとが直列に接続されて構成される。FET2Dは、P型(Pチャンネル)のMOSFET、MESFET、及びHEMT等のキャリアとしてイオンを利用するFETである。また、FET2Eは、電荷蓄積層においてチャネル層との間で電荷を蓄積及び放出可能に構成されたP型FETであり、基本構造はFET2Aと同様である。このような論理回路101によっても、2つのFET2D、2Eが入力電圧に対して逆のスイッチング動作を行うように構成され、論理回路を実現できる。また、2つのFETが共にP型のトランジスタであるので、ラッチアップ現象等の懸念が無くなり論理回路1全体での安定動作を可能にすると共に、製造プロセス及び設計プロセスも簡素化することができる。さらに、電荷蓄積構造を備えるFETを採用することで消費電力を低減することもできる。

【0034】

さらに、図15に示すように、2つのP型のFETによって論理回路を構成してもよい。論理回路301の論理回路201との相違点は、FET2Dに替えてFET2Fを備える点である。このFET2Fは、基本構造はFET2Dとほぼ同一であり、電荷蓄積層が電荷をゲート電極膜との間で充電及び放電させる機能を有する点が異なる。この場合、電荷蓄積層としては、図13、及び図5〜7に示した電荷蓄積構造と同様な構造であってもよい。このような論理回路301によっても、2つのFET2F、2Eが入力電圧に対して逆のスイッチング動作を行うように構成され、論理回路を実現できる。

【符号の説明】

【0035】

1,101,201,301…論理回路、2A,2B,2C,2D,2E,2F…FET、3…入力端子、4…出力端子、12…チャネル層、16,116…電荷蓄積層、17…ゲート電極膜、19…電荷トラップ層(電荷蓄積構造、導電材料層)、20、22…電荷トラップ(電荷蓄積構造)。

【特許請求の範囲】

【請求項1】

バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2の電界効果トランジスタを備える論理回路であって、

前記第1及び第2の電界効果トランジスタのうちの少なくとも1つは、

前記ゲート端子が接続されるゲート電極膜と、

半導体材料からなるチャネル層と、

前記ゲート電極膜と前記チャネル層との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層と、

を有する

ことを特徴とする論理回路。

【請求項2】

前記電荷蓄積層においては、

前記電荷蓄積構造が、前記チャネル層或いは前記ゲート電極膜との間で電荷を蓄積及び放出可能に構成されている、

ことを特徴とする請求項1記載の論理回路。

【請求項3】

前記電荷蓄積層においては、

前記電荷蓄積構造が、前記チャネル層或いは前記ゲート電極膜側に片寄って配置されている、

ことを特徴とする請求項2記載の論理回路。

【請求項4】

前記電荷蓄積層においては、

前記電荷蓄積構造が、電荷に対する特性が異なる2層によって挟まれて配置されている、

ことを特徴とする請求項2記載の論理回路。

【請求項5】

前記第1及び第2の電界効果トランジスタはN型トランジスタである、

ことを特徴とする請求項1〜4のいずれか1項に記載の論理回路。

【請求項6】

前記第1及び第2の電界効果トランジスタはP型トランジスタである、

ことを特徴とする請求項1〜4のいずれか1項に記載の論理回路。

【請求項7】

前記バイアス電源、前記グラウンド、及び前記ゲート端子の少なくとも1つには、雑音源が接続されている、

ことを特徴とする請求項1〜6のいずれか1項に記載の論理回路。

【請求項8】

前記電荷蓄積構造は、前記電荷蓄積層中における導電材料層によって構成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【請求項9】

前記電荷蓄積構造は、前記電荷蓄積層中における欠陥によって生成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【請求項10】

前記電荷蓄積構造は、前記電荷蓄積層中における組成比のずれによって生成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【請求項11】

前記電荷蓄積構造は、前記電荷蓄積層中における微小材料によって生成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【請求項12】

前記電荷蓄積構造は、前記電荷蓄積層中における不純物原子或いは不純物分子によって構成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【請求項1】

バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2の電界効果トランジスタを備える論理回路であって、

前記第1及び第2の電界効果トランジスタのうちの少なくとも1つは、

前記ゲート端子が接続されるゲート電極膜と、

半導体材料からなるチャネル層と、

前記ゲート電極膜と前記チャネル層との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層と、

を有する

ことを特徴とする論理回路。

【請求項2】

前記電荷蓄積層においては、

前記電荷蓄積構造が、前記チャネル層或いは前記ゲート電極膜との間で電荷を蓄積及び放出可能に構成されている、

ことを特徴とする請求項1記載の論理回路。

【請求項3】

前記電荷蓄積層においては、

前記電荷蓄積構造が、前記チャネル層或いは前記ゲート電極膜側に片寄って配置されている、

ことを特徴とする請求項2記載の論理回路。

【請求項4】

前記電荷蓄積層においては、

前記電荷蓄積構造が、電荷に対する特性が異なる2層によって挟まれて配置されている、

ことを特徴とする請求項2記載の論理回路。

【請求項5】

前記第1及び第2の電界効果トランジスタはN型トランジスタである、

ことを特徴とする請求項1〜4のいずれか1項に記載の論理回路。

【請求項6】

前記第1及び第2の電界効果トランジスタはP型トランジスタである、

ことを特徴とする請求項1〜4のいずれか1項に記載の論理回路。

【請求項7】

前記バイアス電源、前記グラウンド、及び前記ゲート端子の少なくとも1つには、雑音源が接続されている、

ことを特徴とする請求項1〜6のいずれか1項に記載の論理回路。

【請求項8】

前記電荷蓄積構造は、前記電荷蓄積層中における導電材料層によって構成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【請求項9】

前記電荷蓄積構造は、前記電荷蓄積層中における欠陥によって生成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【請求項10】

前記電荷蓄積構造は、前記電荷蓄積層中における組成比のずれによって生成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【請求項11】

前記電荷蓄積構造は、前記電荷蓄積層中における微小材料によって生成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【請求項12】

前記電荷蓄積構造は、前記電荷蓄積層中における不純物原子或いは不純物分子によって構成されている、

ことを特徴とする請求項1〜7のいずれか1項に記載の論理回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−89916(P2013−89916A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−232085(P2011−232085)

【出願日】平成23年10月21日(2011.10.21)

【出願人】(504173471)国立大学法人北海道大学 (971)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月21日(2011.10.21)

【出願人】(504173471)国立大学法人北海道大学 (971)

【Fターム(参考)】

[ Back to top ]