論理検証システム

【課題】シミュレーションに要する時間の短縮、及び出力情報の削減によるメモリ、ディスク等リソース使用量の低減が可能で、かつ、カバレッジ情報を効率よく抽出可能な論理検証システムを提供する。

【解決手段】 論理シミュレーションを実行する論理シミュレーション実行部と、前記カバレッジ情報を前記論理シミュレーション実行部から取得するカバレッジ情報取得部と、取得した前記カバレッジ情報を解析するカバレッジ情報解析部と、前記論理シミュレーション実行部の動作の制御を行う制御部とを備える。前記カバレッジ解析部は、一度テストされた論理素子に関するカバレッジ情報は抽出しない旨の指示を前記制御部に出し、前記制御部は、その指示に基づいて、前記論理シミュレーション実行部を制御して抽出しない対象の論理素子からのカバレッジ情報の抽出動作を中止させる。

【解決手段】 論理シミュレーションを実行する論理シミュレーション実行部と、前記カバレッジ情報を前記論理シミュレーション実行部から取得するカバレッジ情報取得部と、取得した前記カバレッジ情報を解析するカバレッジ情報解析部と、前記論理シミュレーション実行部の動作の制御を行う制御部とを備える。前記カバレッジ解析部は、一度テストされた論理素子に関するカバレッジ情報は抽出しない旨の指示を前記制御部に出し、前記制御部は、その指示に基づいて、前記論理シミュレーション実行部を制御して抽出しない対象の論理素子からのカバレッジ情報の抽出動作を中止させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、論理回路が正しく設計されていることを確認する論理シミュレーションにおいて、特にテストパターンが十分であるか否かの指標となるカバレッジ情報を抽出することを特徴とする論理検証システムに関する。

【背景技術】

【0002】

従来より、論理シミュレーションのテストパターンが十分であるか否かの指標として主に、機能カバレッジと、コードカバレッジとが使用されている。機能カバレッジとは、論理回路内部の機能をどれくらい網羅したかを表す指標であり、コードカバレッジとは、論理回路のソースコードを基準とし、内部のロジックをどれくらい網羅したかを表す指標である。

【0003】

コードカバレッジには、ソースコードの全てのステートメント(行)の実行を表すステートメントカバレッジ、ソースコード内の条件分岐の全ての条件が成立し、分岐が行われたかを表すコンディションカバレッジ、ソースコード内で使用される全ての変数の変化を表すトグルカバレッジ等の種類がある。

【0004】

コードカバレッジ情報を管理する設計検証システムとして、「設計検証システム、設計検証方法および設計検証プログラムを格納したコンピュータ読み取り可能な記録媒体」(特許文献1)が提案されている。

【0005】

特許文献1に記載された設計検証システムは、論理シミュレーション部と、論理シミュレーションにおいて実行されていない回路記述を抽出する未実行記述抽出部と、抽出された回路記述が実行される可能性が有るか否かを判別する判別手段と、テストベンチの入力パターンと同じか否かを判定するテストベンチを生成する禁止入力チェッカ生成部とを備えている。これにより、コードカバレッジ情報を効率よく管理できるとしている。

【特許文献1】特開2002−99584号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、従来の論理検証システムは、シミュレーションの対象となる論理回路にテストパターンを適用してシミュレーションを行い、論理回路を構成する論理素子の活性化状態、即ち、それぞれの論理素子を示す演算子の出力端子が0、1の両方になったかを検出して論理回路全体のカバレッジを算出していた。

【0007】

通常、一つのテストパターンで、論理回路を構成する全ての論理素子の出力端子を0、1両方に変化させることは困難であり、一般的には、複数のテストパターンを用いて論理回路の動作を検証している。

【0008】

この場合においては、それぞれのテストパターンで論理回路を構成する全ての論理素子の動作状態を監視する必要があり、シミュレーションに要する計算時間の増大、及び出力情報の増大による、メモリ、ディスク等のリソース使用量の増大という問題があった。

【0009】

本発明は、このような実情に鑑みてなされたものであり、シミュレーションに要する時間の短縮、及び出力情報の削減によるメモリ、ディスク等リソース使用量の低減が可能で、かつ、カバレッジ情報を効率よく抽出可能な論理検証システムを提供しようとするものである。

【課題を解決するための手段】

【0010】

本発明の課題は、下記の各発明によって解決することができる。

即ち、本発明の論理検証システムは、テストパターンを用いて論理回路のシミュレーションを実行し、前記テストパターンによって実際にテストされた、前記論理回路を構成する論理素子に関する情報であるカバレッジ情報を取得する論理検証システムであって、論理シミュレーションを実行する論理シミュレーション実行部と、前記カバレッジ情報を前記論理シミュレーション実行部から取得するカバレッジ情報取得部と、取得した前記カバレッジ情報を解析するカバレッジ情報解析部と、前記論理シミュレーション実行部の動作の制御を行う制御部と、を備え、前記カバレッジ解析部は、前記カバレッジ情報取得部が取得したカバレッジ情報を基にして、一度テストされた論理素子に関するカバレッジ情報は抽出しない旨の指示を前記制御部に出し、全ての前記論理素子がテストされたことを検出した場合は、シミュレーションの実行を中止する旨の指示を前記制御部に出し、前記制御部は、前記カバレッジ解析部から一度テストされた論理素子に関するカバレッジ情報は抽出しない旨の指示を受信したとき、前記論理シミュレーション実行部を制御して抽出しない対象の論理素子からのカバレッジ情報の抽出動作を中止させ、前記カバレッジ解析部からシミュレーションの実行を中止する旨の指示を受信したとき、前記論理シミュレーション実行部を制御してシミュレーションを中止させることを主要な特徴としている。

【0011】

これにより、既に活性化された、即ちテストされた論理素子についてはカバレッジ情報取得の動作を行わない指示を出すので、既にテストされた論理素子についてはカバレッジ情報の取得動作は行わない。よって、CPU負荷を軽減し、メモリ、記憶装置の使用量を減少させることができる。

【0012】

また、本発明の論理検証システムは、前記論理回路と、前記論理回路からカバレッジ情報を抽出するためのカバレッジ回路と、前記カバレッジ回路の動作を中止させるための抑止回路と、前記テストパターンとを用いて、前記論理シミュレーション実行部がシミュレーションを行い、前記カバレッジ回路は、前記論理回路を構成する各前記論理素子に接続され、前記抑止回路は、各前記カバレッジ回路に接続され、前記論理シミュレーション実行部が、シミュレーションを実行することにより、前記カバレッジ回路は、当該カバレッジ回路が接続されている論理素子のカバレッジ情報を抽出し、前記カバレッジ情報取得部は、前記カバレッジ回路が抽出した前記カバレッジ情報を取得し、前記制御部は、カバレッジ情報を抽出しない対象の論理素子に接続されたカバレッジ回路に接続された抑止回路に、カバレッジ回路の動作を中止させるための信号を送信し、前記抑止回路は、前記信号を受信することにより、カバレッジ回路の動作を中止させるための信号を、当該抑止回路に接続されたカバレッジ回路に送信し、前記カバレッジ回路は、前記抑止回路から前記信号を受信することにより、カバレッジ情報を抽出する動作を中止することを主要な特徴としている。

【0013】

これにより、シミュレーション対象の回路がどのように変わろうとも、それに応じたカバレッジ回路、抑止回路を付加すればよいので、論理検証システム自身のハードウエアやソフトウエアを変更する必要が無い。

【発明の効果】

【0014】

以上説明したように、本発明の論理検証システムによれば、既に活性化された、即ちテストされた論理素子についてはカバレッジ情報取得の動作を行わない指示を出すので、既にテストされた論理素子についてはカバレッジ情報の取得動作は行わない。よって、CPU負荷を軽減し、メモリ、記憶装置の使用量を減少させることができる。

【0015】

また、シミュレーション対象の回路がどのように変わろうとも、それに応じたカバレッジ回路、抑止回路を付加すればよいので、論理検証システム自身のハードウエアやソフトウエアを変更する必要が無い。

【発明を実施するための最良の形態】

【0016】

以下、添付図面を参照しながら、本発明の論理検証システムを実施するための最良の形態を詳細に説明する。

【0017】

<構成>

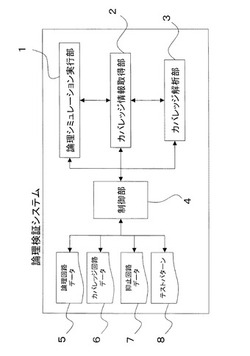

本発明の一実施形態に係る論理検証システムの構成について図を参照して説明する。図1は、本発明の一実施形態に係る論理検証システムの概略構成図である。

【0018】

図1に示すように、本発明の論理検証システムは、論理シミュレーション実行部1と、カバレッジ情報取得部2と、カバレッジ解析部3と、制御部4と、シミュレーション対象の論理回路データ5と、論理回路データに付加されるカバレッジ回路データ6と、カバレッジ回路データ6に付加される抑止回路データ7と、論理回路の動作を検証するためのテストパターン8と、から構成されている。

【0019】

ここで、論理回路データ5、カバレッジ回路データ6、抑止回路データ7は、現実の物理的な回路ではなく、回路をシミュレーションするために、回路をデータで表したものである。しかしながら、シミュレーション上では、物理的な回路と同等の動作を模擬するものなので、以下の説明においては、回路として説明する。よって、論理回路データ5、カバレッジ回路データ6、抑止回路データ7は、それぞれ、論理回路5、カバレッジ回路6、抑止回路7として説明する。

【0020】

論理シミュレーション実行部1は、シミュレーション対象の論理回路5と、この論理回路5に付加されたカバレッジ回路6、抑止回路7とに、テストパターン8を適用してシミュレーションを実行する。

【0021】

カバレッジ情報取得部2は、カバレッジ情報を論理シミュレーション実行部1から取得する。ここで、カバレッジ情報とは、論理回路5を構成する論理素子のうち、シミュレーション実行によって活性化された論理素子に関する情報のことである。即ち、テストパターン8によって実際にテストされた論理素子に関する情報のことである。ここで、活性化されたとは、テストによって動作されたという意味である。

尚、一度活性化された論理素子のカバレッジ情報を図示しないメモリに一時記憶しておくことができる。

【0022】

カバレッジ解析部3は、カバレッジ情報取得部2が取得したカバレッジ情報を基にして、一度活性化された論理素子に関するカバレッジ情報は抽出しない旨の指示を制御部4に出す。また、カバレッジ解析部3は、全ての論理素子が活性化されたことを検出した場合は、シミュレーションの実行を中止する指示を制御部4に出す。また、カバレッジ情報を外部の記憶装置、モニタ等に出力する。

【0023】

制御部4は、一度活性化された論理素子に関するカバレッジ情報は抽出しない旨の指示をカバレッジ解析部3から受信したとき、抽出しない対象となるカバレッジ回路6の動作を抑止する抑止回路7に抑止を指示する抑止指定信号を印加する。制御部4は、論理シミュレーション実行部1から、この抑止指定信号を抑止回路7に印加させることもできる。

【0024】

また、制御部4は、カバレッジ解析部3からシミュレーションの実行を中止する指示を受信したときは、論理シミュレーション実行部に指示して、論理シミュレーション実行部の動作を中止させる。

【0025】

次に一実施形態に係る各回路の構成について図2を参照して説明する。図2は、本発明の一実施形態に係る回路図である。

図2に示すように、シミュレーションの実行対象である論理回路5は、複数の論理素子21によって構成されており、各論理素子21には、それぞれカバレッジ回路6が接続されている。各カバレッジ回路6には、それぞれ抑止回路7が接続されている。カバレッジ回路6は、論理素子21の入力と出力に接続され、論理素子21に信号が入力され、論理素子21が信号を出力したことを検知すると、この回路は活性化されたとして、活性化されたことを示す信号であるカバレッジ抽出信号をCV1に出力する。また、抑止回路7からの信号を受信すると、カバレッジ回路6は、動作を中止し、CV1への信号出力も中止する。

【0026】

抑止回路7は、抑止指定信号が入力Y1に印加されると、出力Y2からカバレッジ回路に信号を送信する。これにより、カバレッジ回路6は上述したように動作を中止する。

また、抑止回路7は、2種類の抑止モード(抑止モード1、2)を指定するための入力M1とM2とを備えている。抑止モードとは、抑止回路7がカバレッジ回路6に動作中止のための信号を送信するための条件のことである。

【0027】

具体的に説明すると、入力M1に信号が入力されていると、カバレッジ回路6が1回でも活性化されたことを示す信号をCV1から出力すると、Y1に入力が無くても出力Y2からカバレッジ回路6の動作を中止させる信号を出力する(抑止モード1)。

【0028】

また、入力M2に信号が入力されていると、全ての抑止回路7において、Y1の入力がされているか、または、CV1から出力がされていればINTから信号を出力する(抑止モード2)。INTからの信号は割り込み信号であり、論理シミュレーション実行部は、このINTからの信号を受信するとシミュレーションの実行を中止する。

【0029】

上述のように、論理素子21、カバレッジ回路6、抑止回路7としてそれぞれ一つの回路で説明したが、実際には、シミュレーションの実行対象回路は、複数の論理素子21で構成され、カバレッジ回路6は、それぞれの論理素子21に接続され、抑止回路7は、それぞれのカバレッジ回路6に接続されている。

【0030】

また、図2においては、論理記号により回路図を表しているが、この論理記号で表された回路に限定されるものではなく、同様の機能を果たす回路であれば、どのような回路でも採用することが可能である。

【0031】

以上説明したように、論理素子一つ一つにカバレッジ回路6、抑止回路7を付加してカバレッジ情報の抽出、カバレッジ情報の抽出中止動作を行っているので、シミュレーション対象の回路がどのように変わろうとも、それに応じたカバレッジ回路、抑止回路を付加すればよく、論理検証システム自身のハードウエアやソフトウエアを変更する必要が無い。

【0032】

<動作>

次に、本発明の一実施形態に係る論理検証システムの動作について、図3を参照して説明する。図3は、本発明の一実施形態に係る論理検証システムのフロー図である。

制御部4は、論理回路5、カバレッジ回路6、抑止回路7、テストパターン8の各データを読み込む(S311)。読み込み元としては、外部の記憶装置から読み込むこともできるし、本願の論理検証システム自身が備える記憶装置から読み込むこともできる。

【0033】

制御部4は、読み込んだデータを論理シミュレーション実行部1に渡す(S312)。論理シミュレーション実行部1は、制御部より渡されたデータを基にして論理シミュレーションを実行する(S313)。

【0034】

論理シミュレーション実行部1は、論理シミュレーションの実行結果である、テスト結果のデータと、カバレッジ情報のデータとを出力する(S314)。

カバレッジ情報取得部2は、論理シミュレーション実行部からカバレッジ情報を読み込む(S315)。カバレッジ情報取得部2は、読み込んだカバレッジ情報をカバレッジ解析部3に渡す(S316)。

【0035】

カバレッジ解析部3は、カバレッジ情報取得部2から渡されたカバレッジ情報の解析を行う(S317)。カバレッジ解析部3は、活性化された論理素子21からのカバレッジ情報の抽出を中止するため、活性化された論理素子21に接続されたカバレッジ回路の動作を中止する指示を制御部に出す(S318)。

【0036】

制御部4は、カバレッジ解析部3から動作の中止を指示されたカバレッジ回路に接続された抑止回路に抑止指定信号を印加する(S319)。この抑止指定信号は、制御部4が直接抑止回路に印加する構成にすることもできるし、論理シミュレーション実行部1が抑止回路に抑止指定信号を印加する構成にすることもできる。

尚、既に論理シミュレーションを実行しているが、カバレッジ率が100%に達しなかった論理回路につき、後にテストパターンを追加して論理シミュレーションを実行する場合には、制御部4はS311において各データを読み込む際に、実行済みの論理シミュレーションにおけるカバレッジ情報を取得し、既に活性化された論理素子のからのカバレッジ情報の抽出を中止するよう抑止指定信号を印加するものとする。

【0037】

カバレッジ解析部3は、全ての論理素子21がテストされたか、即ち全ての論理素子21が活性化されたか判定を行い、全ての論理素子21がテストされた場合はS322を実行し、そうでない場合は、S321を実行する(S320)。

【0038】

カバレッジ解析部3において全ての論理素子21がテストされていないと判定された場合は、制御部4は、全テストパターンを実行したか判定を行い、全テストパターンを実行していない場合は、S311から実行を行い、全テストパターンを実行した場合は、S323を実行する(S321)。

【0039】

カバレッジ解析部3において全ての論理素子21がテストされたと判定された場合は、カバレッジ解析部3は、論理シミュレーションの実行中止の指示を制御部4に出す(S322)。制御部4は、論理シミュレーション実行部1が行っている論理シミュレーションの実行を中止させる(S323)。

【0040】

次にカバレッジ回路6、抑止回路7の動作について図を参照して説明する。図4は、抑止モード1のときの、カバレッジ回路と抑止回路のタイミングチャートである。図4における、CLK、IN1、IN2等の各符号は図2の同一の符号と対応するが、図2においては、信号ラインを示し、図4においては、信号を示す。即ち、例えば、CLKは、図2においては、クロック信号ラインを示すが、図4においては、クロック信号を示す。

【0041】

図2に示すように、CLKはクロック信号ラインであり、IN1、IN2は論理素子21への入力信号ラインである。OUT1は、論理素子21からの出力信号ラインである。

カバレッジ回路6は、クロック信号ラインCLK、入力信号ラインIN1、IN2が入力ラインに接続され、カバレッジ抽出信号ラインCV1が出力ラインに接続される。

【0042】

抑止回路7は、抑止モード1を指定する信号ラインM1、抑止モード2を指定する信号ラインM2、抑止指定信号ラインY1、カバレッジ抽出信号ラインCV1が入力ラインに接続され、カバレッジ回路6の動作を中止させる抑止指示を出す信号ラインY2、割り込み信号ラインINTが出力ラインと接続されている。

【0043】

次に、図4に示すように、抑止モード1を指定する信号M1が「1」、抑止モード2を指定する信号M2が「0」、抑止指定信号Y1が「0」で固定されているときの動作について説明する。

【0044】

クロック信号CLKは、周期的に「1」、「0」を繰り返す。ここでこれ以降、信号が「0」から「1」に変化することを、「立ち上がる」と表現し、信号が「1」から「0」に変化することを、「立ち下がる」と表現する。

【0045】

時刻T1において、IN1、IN2がともに立ち上がり、時刻T3においてIN1、IN2がともに立ち下がり、時刻T3において、OUT1が立ち上がり、時刻T5でOUT1が立ち下がったとき、CV1は、時刻T5で立ち上がる。

【0046】

ここで図2を参照すると、CV1が立ち上がることにより、抑止回路7のFが「1」に変化し、M1が「1」なので、Gも「1」となり、Y2も「1」となる。これにより、カバレッジ回路6のCLK2が「1」に固定されるので、カバレッジ回路6は動作を行わなくなる。図4にもどると、時刻T5以降は、IN1、IN2、OUT1が変化してもCV1は、「1」に固定されたままで変化しない。即ち、カバレッジ回路6は動作を停止している。

【0047】

続いて、抑止モード1を指定する信号M1が「0」の場合について図2と図5を参照して説明する。図5は、抑止モードが設定されていないときの、カバレッジ回路と抑止回路のタイミングチャートである。図2に示すように、M1が「0」ときは、Gは常に「0」となり、Y1が「1」でない限りは、Y2は「0」となる。これにより、CLK2は、「1」に固定されることはないので、カバレッジ回路6は動作を停止することはなく、図5に示すように、IN1、IN2、OUT1の変化に伴って、CV1も変化する。即ち、CV1は出力を続ける。

【0048】

次に、抑止モード1を指定する信号M1が「1」、抑止モード2を指定する信号M2が「1」、抑止指定信号Y1が「0」で固定されているとき、即ち抑止モード2のときの動作について説明する。図6は、抑止モード2のときの、カバレッジ回路と抑止回路のタイミングチャートである。この場合は、図2に示すように、M2が「1」であり、CV1が立ち上がるとFが「1」になるので、Hも「1」となる。よって、他の抑止回路の全てのH’が1になればINTが「1」となる。INTが「1」となることにより、この信号を受信した論理シミュレーション実行部1は、動作を中止する。ここで、図6を参照すると、CV1が立ち上がることにより、論理シミュレーション実行部1は動作を中止するので、IN1、IN2、OUT1も「0」で固定される。

【0049】

次にカバレッジ解析部3の動作の一例を図7を参照して説明する。図7は、カバレッジ解析部の動作の一例を示す図である。

この図において、論理回路5を構成する論理素子を、論理素子A、B、C、D、Eで表している。また、「1」は、その論理素子が活性化されたことを表し、「0」は、その論理素子がまだ活性化されていないことを表す。

【0050】

符号71で示すように、カバレッジ解析部3が有するデータベースにおいて、テストパターン実行前は、全ての論理素子が「0」として登録されている。テストパターン1の実行結果のカバレッジ情報72が、カバレッジ情報取得部2からカバレッジ解析部3に渡されたとき、カバレッジ解析部3は、渡された情報を基にして、データベース内容を更新する。更新した結果を符号73で示す。

【0051】

符号73で示すように、テストパターン1の実行によって活性化された論理素子A、Cについて、「1」と更新されている。カバレッジ解析部3は、「1」と更新された論理素子A、Cについてカバレッジ情報取得動作を中止する指示を制御部4に出す。

【0052】

テストパターン1の後に実施した、テストパターン2の実行結果のカバレッジ情報を符号74で示す。カバレッジ情報取得部2は、このカバレッジ情報をカバレッジ解析部3に送る。カバレッジ解析部3は、渡されたカバレッジ情報を基にして、データベース内容を更新する。更新された結果を符号75で示す。

【0053】

符号75で示すように、テストパターン2の実行によって活性化された論理素子Dについて、「1」と更新されている。カバレッジ解析部3は、「1」と更新された論理素子Dについてカバレッジ情報取得動作を中止する指示を制御部4に出す。

【0054】

テストパターン2の後に実行した、テストパターン3の実行結果のカバレッジ情報を符号76で示す。カバレッジ情報取得部2は、このカバレッジ情報をカバレッジ解析部3に送る。カバレッジ解析部3は、渡されたカバレッジ情報を基にして、データベース内容を更新する。更新された結果を符号77で示す。

【0055】

符号77で示すように、テストパターン3の実行によって活性化された論理素子B、Eについて、「1」と更新されている。カバレッジ解析部3は、「1」と更新された論理素子B、Eについてカバレッジ情報取得動作を中止する指示を制御部4に出す。

【0056】

このように、既に活性化された、即ちテストされた論理素子についてはカバレッジ情報取得の動作を行わない指示を出すので、既にテストされた論理素子についてはカバレッジ情報の取得動作は行わない。これにより、論理シミュレーション実行部1の負担が軽減し、CPU負荷や、メモリ、記憶装置の使用量を減少させることができる。

【0057】

以上、本発明の論理検証システムについて、具体的な実施の形態を示して説明したが、本発明はこれらに限定されるものではない。当業者であれば、本発明の要旨を逸脱しない範囲内において、上記実施形態における論理検証システムの構成及び機能に様々な変更・改良を加えることが可能である。

【産業上の利用可能性】

【0058】

本発明の論理検証システムは、コンピュータのCPU、メモリ、補助記憶装置等を含むハードウエア資源上に構築されたOS、アプリケーション等によって実現されるものであり、回路のシミュレーション、カバレッジ情報の抽出という情報処理が上記ハードウエア資源を用いて具体的に実現されるものであるから、自然法則を利用した技術的思想に該当するものであり、回路のシミュレーションが必要な、電子回路、半導体等の開発、設計、製造分野において利用することができるものである。

【図面の簡単な説明】

【0059】

【図1】本発明の一実施形態に係る論理検証システムの概略構成図である。

【図2】本発明の一実施形態に係る回路図である。

【図3】本発明の一実施形態に係る論理検証システムのフロー図である。

【図4】抑止モード1のときの、カバレッジ回路と抑止回路のタイミングチャートである。

【図5】抑止モードが設定されていないときの、カバレッジ回路と抑止回路のタイミングチャートである。

【図6】抑止モード2のときの、カバレッジ回路と抑止回路のタイミングチャートである。

【図7】カバレッジ解析部の動作の一例を示す図である。

【符号の説明】

【0060】

1 論理シミュレーション実行部

2 カバレッジ情報取得部

3 カバレッジ解析部

4 制御部

5 論理回路データ

6 カバレッジ回路データ

7 抑止回路データ

8 テストパターン

21 論理素子

【技術分野】

【0001】

本発明は、論理回路が正しく設計されていることを確認する論理シミュレーションにおいて、特にテストパターンが十分であるか否かの指標となるカバレッジ情報を抽出することを特徴とする論理検証システムに関する。

【背景技術】

【0002】

従来より、論理シミュレーションのテストパターンが十分であるか否かの指標として主に、機能カバレッジと、コードカバレッジとが使用されている。機能カバレッジとは、論理回路内部の機能をどれくらい網羅したかを表す指標であり、コードカバレッジとは、論理回路のソースコードを基準とし、内部のロジックをどれくらい網羅したかを表す指標である。

【0003】

コードカバレッジには、ソースコードの全てのステートメント(行)の実行を表すステートメントカバレッジ、ソースコード内の条件分岐の全ての条件が成立し、分岐が行われたかを表すコンディションカバレッジ、ソースコード内で使用される全ての変数の変化を表すトグルカバレッジ等の種類がある。

【0004】

コードカバレッジ情報を管理する設計検証システムとして、「設計検証システム、設計検証方法および設計検証プログラムを格納したコンピュータ読み取り可能な記録媒体」(特許文献1)が提案されている。

【0005】

特許文献1に記載された設計検証システムは、論理シミュレーション部と、論理シミュレーションにおいて実行されていない回路記述を抽出する未実行記述抽出部と、抽出された回路記述が実行される可能性が有るか否かを判別する判別手段と、テストベンチの入力パターンと同じか否かを判定するテストベンチを生成する禁止入力チェッカ生成部とを備えている。これにより、コードカバレッジ情報を効率よく管理できるとしている。

【特許文献1】特開2002−99584号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、従来の論理検証システムは、シミュレーションの対象となる論理回路にテストパターンを適用してシミュレーションを行い、論理回路を構成する論理素子の活性化状態、即ち、それぞれの論理素子を示す演算子の出力端子が0、1の両方になったかを検出して論理回路全体のカバレッジを算出していた。

【0007】

通常、一つのテストパターンで、論理回路を構成する全ての論理素子の出力端子を0、1両方に変化させることは困難であり、一般的には、複数のテストパターンを用いて論理回路の動作を検証している。

【0008】

この場合においては、それぞれのテストパターンで論理回路を構成する全ての論理素子の動作状態を監視する必要があり、シミュレーションに要する計算時間の増大、及び出力情報の増大による、メモリ、ディスク等のリソース使用量の増大という問題があった。

【0009】

本発明は、このような実情に鑑みてなされたものであり、シミュレーションに要する時間の短縮、及び出力情報の削減によるメモリ、ディスク等リソース使用量の低減が可能で、かつ、カバレッジ情報を効率よく抽出可能な論理検証システムを提供しようとするものである。

【課題を解決するための手段】

【0010】

本発明の課題は、下記の各発明によって解決することができる。

即ち、本発明の論理検証システムは、テストパターンを用いて論理回路のシミュレーションを実行し、前記テストパターンによって実際にテストされた、前記論理回路を構成する論理素子に関する情報であるカバレッジ情報を取得する論理検証システムであって、論理シミュレーションを実行する論理シミュレーション実行部と、前記カバレッジ情報を前記論理シミュレーション実行部から取得するカバレッジ情報取得部と、取得した前記カバレッジ情報を解析するカバレッジ情報解析部と、前記論理シミュレーション実行部の動作の制御を行う制御部と、を備え、前記カバレッジ解析部は、前記カバレッジ情報取得部が取得したカバレッジ情報を基にして、一度テストされた論理素子に関するカバレッジ情報は抽出しない旨の指示を前記制御部に出し、全ての前記論理素子がテストされたことを検出した場合は、シミュレーションの実行を中止する旨の指示を前記制御部に出し、前記制御部は、前記カバレッジ解析部から一度テストされた論理素子に関するカバレッジ情報は抽出しない旨の指示を受信したとき、前記論理シミュレーション実行部を制御して抽出しない対象の論理素子からのカバレッジ情報の抽出動作を中止させ、前記カバレッジ解析部からシミュレーションの実行を中止する旨の指示を受信したとき、前記論理シミュレーション実行部を制御してシミュレーションを中止させることを主要な特徴としている。

【0011】

これにより、既に活性化された、即ちテストされた論理素子についてはカバレッジ情報取得の動作を行わない指示を出すので、既にテストされた論理素子についてはカバレッジ情報の取得動作は行わない。よって、CPU負荷を軽減し、メモリ、記憶装置の使用量を減少させることができる。

【0012】

また、本発明の論理検証システムは、前記論理回路と、前記論理回路からカバレッジ情報を抽出するためのカバレッジ回路と、前記カバレッジ回路の動作を中止させるための抑止回路と、前記テストパターンとを用いて、前記論理シミュレーション実行部がシミュレーションを行い、前記カバレッジ回路は、前記論理回路を構成する各前記論理素子に接続され、前記抑止回路は、各前記カバレッジ回路に接続され、前記論理シミュレーション実行部が、シミュレーションを実行することにより、前記カバレッジ回路は、当該カバレッジ回路が接続されている論理素子のカバレッジ情報を抽出し、前記カバレッジ情報取得部は、前記カバレッジ回路が抽出した前記カバレッジ情報を取得し、前記制御部は、カバレッジ情報を抽出しない対象の論理素子に接続されたカバレッジ回路に接続された抑止回路に、カバレッジ回路の動作を中止させるための信号を送信し、前記抑止回路は、前記信号を受信することにより、カバレッジ回路の動作を中止させるための信号を、当該抑止回路に接続されたカバレッジ回路に送信し、前記カバレッジ回路は、前記抑止回路から前記信号を受信することにより、カバレッジ情報を抽出する動作を中止することを主要な特徴としている。

【0013】

これにより、シミュレーション対象の回路がどのように変わろうとも、それに応じたカバレッジ回路、抑止回路を付加すればよいので、論理検証システム自身のハードウエアやソフトウエアを変更する必要が無い。

【発明の効果】

【0014】

以上説明したように、本発明の論理検証システムによれば、既に活性化された、即ちテストされた論理素子についてはカバレッジ情報取得の動作を行わない指示を出すので、既にテストされた論理素子についてはカバレッジ情報の取得動作は行わない。よって、CPU負荷を軽減し、メモリ、記憶装置の使用量を減少させることができる。

【0015】

また、シミュレーション対象の回路がどのように変わろうとも、それに応じたカバレッジ回路、抑止回路を付加すればよいので、論理検証システム自身のハードウエアやソフトウエアを変更する必要が無い。

【発明を実施するための最良の形態】

【0016】

以下、添付図面を参照しながら、本発明の論理検証システムを実施するための最良の形態を詳細に説明する。

【0017】

<構成>

本発明の一実施形態に係る論理検証システムの構成について図を参照して説明する。図1は、本発明の一実施形態に係る論理検証システムの概略構成図である。

【0018】

図1に示すように、本発明の論理検証システムは、論理シミュレーション実行部1と、カバレッジ情報取得部2と、カバレッジ解析部3と、制御部4と、シミュレーション対象の論理回路データ5と、論理回路データに付加されるカバレッジ回路データ6と、カバレッジ回路データ6に付加される抑止回路データ7と、論理回路の動作を検証するためのテストパターン8と、から構成されている。

【0019】

ここで、論理回路データ5、カバレッジ回路データ6、抑止回路データ7は、現実の物理的な回路ではなく、回路をシミュレーションするために、回路をデータで表したものである。しかしながら、シミュレーション上では、物理的な回路と同等の動作を模擬するものなので、以下の説明においては、回路として説明する。よって、論理回路データ5、カバレッジ回路データ6、抑止回路データ7は、それぞれ、論理回路5、カバレッジ回路6、抑止回路7として説明する。

【0020】

論理シミュレーション実行部1は、シミュレーション対象の論理回路5と、この論理回路5に付加されたカバレッジ回路6、抑止回路7とに、テストパターン8を適用してシミュレーションを実行する。

【0021】

カバレッジ情報取得部2は、カバレッジ情報を論理シミュレーション実行部1から取得する。ここで、カバレッジ情報とは、論理回路5を構成する論理素子のうち、シミュレーション実行によって活性化された論理素子に関する情報のことである。即ち、テストパターン8によって実際にテストされた論理素子に関する情報のことである。ここで、活性化されたとは、テストによって動作されたという意味である。

尚、一度活性化された論理素子のカバレッジ情報を図示しないメモリに一時記憶しておくことができる。

【0022】

カバレッジ解析部3は、カバレッジ情報取得部2が取得したカバレッジ情報を基にして、一度活性化された論理素子に関するカバレッジ情報は抽出しない旨の指示を制御部4に出す。また、カバレッジ解析部3は、全ての論理素子が活性化されたことを検出した場合は、シミュレーションの実行を中止する指示を制御部4に出す。また、カバレッジ情報を外部の記憶装置、モニタ等に出力する。

【0023】

制御部4は、一度活性化された論理素子に関するカバレッジ情報は抽出しない旨の指示をカバレッジ解析部3から受信したとき、抽出しない対象となるカバレッジ回路6の動作を抑止する抑止回路7に抑止を指示する抑止指定信号を印加する。制御部4は、論理シミュレーション実行部1から、この抑止指定信号を抑止回路7に印加させることもできる。

【0024】

また、制御部4は、カバレッジ解析部3からシミュレーションの実行を中止する指示を受信したときは、論理シミュレーション実行部に指示して、論理シミュレーション実行部の動作を中止させる。

【0025】

次に一実施形態に係る各回路の構成について図2を参照して説明する。図2は、本発明の一実施形態に係る回路図である。

図2に示すように、シミュレーションの実行対象である論理回路5は、複数の論理素子21によって構成されており、各論理素子21には、それぞれカバレッジ回路6が接続されている。各カバレッジ回路6には、それぞれ抑止回路7が接続されている。カバレッジ回路6は、論理素子21の入力と出力に接続され、論理素子21に信号が入力され、論理素子21が信号を出力したことを検知すると、この回路は活性化されたとして、活性化されたことを示す信号であるカバレッジ抽出信号をCV1に出力する。また、抑止回路7からの信号を受信すると、カバレッジ回路6は、動作を中止し、CV1への信号出力も中止する。

【0026】

抑止回路7は、抑止指定信号が入力Y1に印加されると、出力Y2からカバレッジ回路に信号を送信する。これにより、カバレッジ回路6は上述したように動作を中止する。

また、抑止回路7は、2種類の抑止モード(抑止モード1、2)を指定するための入力M1とM2とを備えている。抑止モードとは、抑止回路7がカバレッジ回路6に動作中止のための信号を送信するための条件のことである。

【0027】

具体的に説明すると、入力M1に信号が入力されていると、カバレッジ回路6が1回でも活性化されたことを示す信号をCV1から出力すると、Y1に入力が無くても出力Y2からカバレッジ回路6の動作を中止させる信号を出力する(抑止モード1)。

【0028】

また、入力M2に信号が入力されていると、全ての抑止回路7において、Y1の入力がされているか、または、CV1から出力がされていればINTから信号を出力する(抑止モード2)。INTからの信号は割り込み信号であり、論理シミュレーション実行部は、このINTからの信号を受信するとシミュレーションの実行を中止する。

【0029】

上述のように、論理素子21、カバレッジ回路6、抑止回路7としてそれぞれ一つの回路で説明したが、実際には、シミュレーションの実行対象回路は、複数の論理素子21で構成され、カバレッジ回路6は、それぞれの論理素子21に接続され、抑止回路7は、それぞれのカバレッジ回路6に接続されている。

【0030】

また、図2においては、論理記号により回路図を表しているが、この論理記号で表された回路に限定されるものではなく、同様の機能を果たす回路であれば、どのような回路でも採用することが可能である。

【0031】

以上説明したように、論理素子一つ一つにカバレッジ回路6、抑止回路7を付加してカバレッジ情報の抽出、カバレッジ情報の抽出中止動作を行っているので、シミュレーション対象の回路がどのように変わろうとも、それに応じたカバレッジ回路、抑止回路を付加すればよく、論理検証システム自身のハードウエアやソフトウエアを変更する必要が無い。

【0032】

<動作>

次に、本発明の一実施形態に係る論理検証システムの動作について、図3を参照して説明する。図3は、本発明の一実施形態に係る論理検証システムのフロー図である。

制御部4は、論理回路5、カバレッジ回路6、抑止回路7、テストパターン8の各データを読み込む(S311)。読み込み元としては、外部の記憶装置から読み込むこともできるし、本願の論理検証システム自身が備える記憶装置から読み込むこともできる。

【0033】

制御部4は、読み込んだデータを論理シミュレーション実行部1に渡す(S312)。論理シミュレーション実行部1は、制御部より渡されたデータを基にして論理シミュレーションを実行する(S313)。

【0034】

論理シミュレーション実行部1は、論理シミュレーションの実行結果である、テスト結果のデータと、カバレッジ情報のデータとを出力する(S314)。

カバレッジ情報取得部2は、論理シミュレーション実行部からカバレッジ情報を読み込む(S315)。カバレッジ情報取得部2は、読み込んだカバレッジ情報をカバレッジ解析部3に渡す(S316)。

【0035】

カバレッジ解析部3は、カバレッジ情報取得部2から渡されたカバレッジ情報の解析を行う(S317)。カバレッジ解析部3は、活性化された論理素子21からのカバレッジ情報の抽出を中止するため、活性化された論理素子21に接続されたカバレッジ回路の動作を中止する指示を制御部に出す(S318)。

【0036】

制御部4は、カバレッジ解析部3から動作の中止を指示されたカバレッジ回路に接続された抑止回路に抑止指定信号を印加する(S319)。この抑止指定信号は、制御部4が直接抑止回路に印加する構成にすることもできるし、論理シミュレーション実行部1が抑止回路に抑止指定信号を印加する構成にすることもできる。

尚、既に論理シミュレーションを実行しているが、カバレッジ率が100%に達しなかった論理回路につき、後にテストパターンを追加して論理シミュレーションを実行する場合には、制御部4はS311において各データを読み込む際に、実行済みの論理シミュレーションにおけるカバレッジ情報を取得し、既に活性化された論理素子のからのカバレッジ情報の抽出を中止するよう抑止指定信号を印加するものとする。

【0037】

カバレッジ解析部3は、全ての論理素子21がテストされたか、即ち全ての論理素子21が活性化されたか判定を行い、全ての論理素子21がテストされた場合はS322を実行し、そうでない場合は、S321を実行する(S320)。

【0038】

カバレッジ解析部3において全ての論理素子21がテストされていないと判定された場合は、制御部4は、全テストパターンを実行したか判定を行い、全テストパターンを実行していない場合は、S311から実行を行い、全テストパターンを実行した場合は、S323を実行する(S321)。

【0039】

カバレッジ解析部3において全ての論理素子21がテストされたと判定された場合は、カバレッジ解析部3は、論理シミュレーションの実行中止の指示を制御部4に出す(S322)。制御部4は、論理シミュレーション実行部1が行っている論理シミュレーションの実行を中止させる(S323)。

【0040】

次にカバレッジ回路6、抑止回路7の動作について図を参照して説明する。図4は、抑止モード1のときの、カバレッジ回路と抑止回路のタイミングチャートである。図4における、CLK、IN1、IN2等の各符号は図2の同一の符号と対応するが、図2においては、信号ラインを示し、図4においては、信号を示す。即ち、例えば、CLKは、図2においては、クロック信号ラインを示すが、図4においては、クロック信号を示す。

【0041】

図2に示すように、CLKはクロック信号ラインであり、IN1、IN2は論理素子21への入力信号ラインである。OUT1は、論理素子21からの出力信号ラインである。

カバレッジ回路6は、クロック信号ラインCLK、入力信号ラインIN1、IN2が入力ラインに接続され、カバレッジ抽出信号ラインCV1が出力ラインに接続される。

【0042】

抑止回路7は、抑止モード1を指定する信号ラインM1、抑止モード2を指定する信号ラインM2、抑止指定信号ラインY1、カバレッジ抽出信号ラインCV1が入力ラインに接続され、カバレッジ回路6の動作を中止させる抑止指示を出す信号ラインY2、割り込み信号ラインINTが出力ラインと接続されている。

【0043】

次に、図4に示すように、抑止モード1を指定する信号M1が「1」、抑止モード2を指定する信号M2が「0」、抑止指定信号Y1が「0」で固定されているときの動作について説明する。

【0044】

クロック信号CLKは、周期的に「1」、「0」を繰り返す。ここでこれ以降、信号が「0」から「1」に変化することを、「立ち上がる」と表現し、信号が「1」から「0」に変化することを、「立ち下がる」と表現する。

【0045】

時刻T1において、IN1、IN2がともに立ち上がり、時刻T3においてIN1、IN2がともに立ち下がり、時刻T3において、OUT1が立ち上がり、時刻T5でOUT1が立ち下がったとき、CV1は、時刻T5で立ち上がる。

【0046】

ここで図2を参照すると、CV1が立ち上がることにより、抑止回路7のFが「1」に変化し、M1が「1」なので、Gも「1」となり、Y2も「1」となる。これにより、カバレッジ回路6のCLK2が「1」に固定されるので、カバレッジ回路6は動作を行わなくなる。図4にもどると、時刻T5以降は、IN1、IN2、OUT1が変化してもCV1は、「1」に固定されたままで変化しない。即ち、カバレッジ回路6は動作を停止している。

【0047】

続いて、抑止モード1を指定する信号M1が「0」の場合について図2と図5を参照して説明する。図5は、抑止モードが設定されていないときの、カバレッジ回路と抑止回路のタイミングチャートである。図2に示すように、M1が「0」ときは、Gは常に「0」となり、Y1が「1」でない限りは、Y2は「0」となる。これにより、CLK2は、「1」に固定されることはないので、カバレッジ回路6は動作を停止することはなく、図5に示すように、IN1、IN2、OUT1の変化に伴って、CV1も変化する。即ち、CV1は出力を続ける。

【0048】

次に、抑止モード1を指定する信号M1が「1」、抑止モード2を指定する信号M2が「1」、抑止指定信号Y1が「0」で固定されているとき、即ち抑止モード2のときの動作について説明する。図6は、抑止モード2のときの、カバレッジ回路と抑止回路のタイミングチャートである。この場合は、図2に示すように、M2が「1」であり、CV1が立ち上がるとFが「1」になるので、Hも「1」となる。よって、他の抑止回路の全てのH’が1になればINTが「1」となる。INTが「1」となることにより、この信号を受信した論理シミュレーション実行部1は、動作を中止する。ここで、図6を参照すると、CV1が立ち上がることにより、論理シミュレーション実行部1は動作を中止するので、IN1、IN2、OUT1も「0」で固定される。

【0049】

次にカバレッジ解析部3の動作の一例を図7を参照して説明する。図7は、カバレッジ解析部の動作の一例を示す図である。

この図において、論理回路5を構成する論理素子を、論理素子A、B、C、D、Eで表している。また、「1」は、その論理素子が活性化されたことを表し、「0」は、その論理素子がまだ活性化されていないことを表す。

【0050】

符号71で示すように、カバレッジ解析部3が有するデータベースにおいて、テストパターン実行前は、全ての論理素子が「0」として登録されている。テストパターン1の実行結果のカバレッジ情報72が、カバレッジ情報取得部2からカバレッジ解析部3に渡されたとき、カバレッジ解析部3は、渡された情報を基にして、データベース内容を更新する。更新した結果を符号73で示す。

【0051】

符号73で示すように、テストパターン1の実行によって活性化された論理素子A、Cについて、「1」と更新されている。カバレッジ解析部3は、「1」と更新された論理素子A、Cについてカバレッジ情報取得動作を中止する指示を制御部4に出す。

【0052】

テストパターン1の後に実施した、テストパターン2の実行結果のカバレッジ情報を符号74で示す。カバレッジ情報取得部2は、このカバレッジ情報をカバレッジ解析部3に送る。カバレッジ解析部3は、渡されたカバレッジ情報を基にして、データベース内容を更新する。更新された結果を符号75で示す。

【0053】

符号75で示すように、テストパターン2の実行によって活性化された論理素子Dについて、「1」と更新されている。カバレッジ解析部3は、「1」と更新された論理素子Dについてカバレッジ情報取得動作を中止する指示を制御部4に出す。

【0054】

テストパターン2の後に実行した、テストパターン3の実行結果のカバレッジ情報を符号76で示す。カバレッジ情報取得部2は、このカバレッジ情報をカバレッジ解析部3に送る。カバレッジ解析部3は、渡されたカバレッジ情報を基にして、データベース内容を更新する。更新された結果を符号77で示す。

【0055】

符号77で示すように、テストパターン3の実行によって活性化された論理素子B、Eについて、「1」と更新されている。カバレッジ解析部3は、「1」と更新された論理素子B、Eについてカバレッジ情報取得動作を中止する指示を制御部4に出す。

【0056】

このように、既に活性化された、即ちテストされた論理素子についてはカバレッジ情報取得の動作を行わない指示を出すので、既にテストされた論理素子についてはカバレッジ情報の取得動作は行わない。これにより、論理シミュレーション実行部1の負担が軽減し、CPU負荷や、メモリ、記憶装置の使用量を減少させることができる。

【0057】

以上、本発明の論理検証システムについて、具体的な実施の形態を示して説明したが、本発明はこれらに限定されるものではない。当業者であれば、本発明の要旨を逸脱しない範囲内において、上記実施形態における論理検証システムの構成及び機能に様々な変更・改良を加えることが可能である。

【産業上の利用可能性】

【0058】

本発明の論理検証システムは、コンピュータのCPU、メモリ、補助記憶装置等を含むハードウエア資源上に構築されたOS、アプリケーション等によって実現されるものであり、回路のシミュレーション、カバレッジ情報の抽出という情報処理が上記ハードウエア資源を用いて具体的に実現されるものであるから、自然法則を利用した技術的思想に該当するものであり、回路のシミュレーションが必要な、電子回路、半導体等の開発、設計、製造分野において利用することができるものである。

【図面の簡単な説明】

【0059】

【図1】本発明の一実施形態に係る論理検証システムの概略構成図である。

【図2】本発明の一実施形態に係る回路図である。

【図3】本発明の一実施形態に係る論理検証システムのフロー図である。

【図4】抑止モード1のときの、カバレッジ回路と抑止回路のタイミングチャートである。

【図5】抑止モードが設定されていないときの、カバレッジ回路と抑止回路のタイミングチャートである。

【図6】抑止モード2のときの、カバレッジ回路と抑止回路のタイミングチャートである。

【図7】カバレッジ解析部の動作の一例を示す図である。

【符号の説明】

【0060】

1 論理シミュレーション実行部

2 カバレッジ情報取得部

3 カバレッジ解析部

4 制御部

5 論理回路データ

6 カバレッジ回路データ

7 抑止回路データ

8 テストパターン

21 論理素子

【特許請求の範囲】

【請求項1】

テストパターンを用いて論理回路のシミュレーションを実行し、前記テストパターンによって実際にテストされた、前記論理回路を構成する論理素子に関する情報であるカバレッジ情報を取得する論理検証システムであって、

論理シミュレーションを実行する論理シミュレーション実行部と、前記カバレッジ情報を前記論理シミュレーション実行部から取得するカバレッジ情報取得部と、取得した前記カバレッジ情報を解析するカバレッジ情報解析部と、前記論理シミュレーション実行部の動作の制御を行う制御部と、

を備え、

前記カバレッジ解析部は、

前記カバレッジ情報取得部が取得したカバレッジ情報を基にして、一度テストされた論理素子に関するカバレッジ情報を抽出しない旨の指示を前記制御部に出し、

全ての前記論理素子がテストされたことを検出した場合は、シミュレーションの実行を中止する旨の指示を前記制御部に出し、

前記制御部は、

前記カバレッジ解析部から一度テストされた論理素子に関するカバレッジ情報を抽出しない旨の指示を受信したとき、前記論理シミュレーション実行部を制御して抽出しない対象の論理素子からのカバレッジ情報の抽出動作を中止させ、

前記カバレッジ解析部からシミュレーションの実行を中止する旨の指示を受信したとき、前記論理シミュレーション実行部を制御してシミュレーションを中止させること、

を特徴とする論理検証システム。

【請求項2】

請求項1に記載の論理検証システムであって、

前記論理回路と、前記論理回路からカバレッジ情報を抽出するためのカバレッジ回路と、前記カバレッジ回路の動作を中止させるための抑止回路と、前記テストパターンとを用いて、前記論理シミュレーション実行部がシミュレーションを行い、

前記カバレッジ回路は、前記論理回路を構成する各前記論理素子に接続され、

前記抑止回路は、各前記カバレッジ回路に接続され、

前記論理シミュレーション実行部が、シミュレーションを実行することにより、前記カバレッジ回路は、当該カバレッジ回路が接続されている論理素子のカバレッジ情報を抽出し、

前記カバレッジ情報取得部は、前記カバレッジ回路が抽出した前記カバレッジ情報を取得し、

前記制御部は、カバレッジ情報を抽出しない対象の論理素子に接続されたカバレッジ回路に接続された抑止回路に、カバレッジ回路の動作を中止させるための信号を送信し、

前記抑止回路は、前記信号を受信することにより、カバレッジ回路を動作を中止させるための信号を、当該抑止回路に接続されたカバレッジ回路に送信し、

前記カバレッジ回路は、前記抑止回路から前記信号を受信することにより、カバレッジ情報を抽出する動作を中止すること、

を特徴とする論理検証システム。

【請求項3】

コンピュータに、テストパターンを用いて論理回路のシミュレーションを実行させ、前記テストパターンによって実際にテストされた、前記論理回路を構成する論理素子に関する情報であるカバレッジ情報を取得させるための論理検証プログラムであって、

コンピュータを、論理シミュレーションを実行する論理シミュレーション実行手段と、前記カバレッジ情報を前記論理シミュレーション実行手段から取得するカバレッジ情報取得手段と、取得した前記カバレッジ情報を解析するカバレッジ情報解析手段と、前記論理シミュレーション実行手段の動作の制御を行う制御手段と、

して機能させ、

前記カバレッジ解析手段は、

前記カバレッジ情報取得手段が取得したカバレッジ情報を基にして、一度テストされた論理素子に関するカバレッジ情報を抽出しない旨の指示を前記制御手段に出すステップを実行し、

全ての前記論理素子がテストされたことを検出した場合は、シミュレーションの実行を中止する旨の指示を前記制御手段に出すステップを実行し、

前記制御手段は、

前記カバレッジ解析手段から一度テストされた論理素子に関するカバレッジ情報を抽出しない旨の指示を受信したとき、前記論理シミュレーション実行手段を制御して抽出しない対象の論理素子からのカバレッジ情報の抽出動作を中止させるステップを実行し、

前記カバレッジ解析手段からシミュレーションの実行を中止する旨の指示を受信したとき、前記論理シミュレーション実行手段を制御してシミュレーションを中止させるステップを実行すること、

を特徴とする論理検証プログラム。

【請求項4】

請求項3に記載の論理検証プログラムであって、

前記論理回路と、前記論理回路からカバレッジ情報を抽出するためのカバレッジ回路と、前記カバレッジ回路の動作を中止させるための抑止回路と、前記テストパターンとを用いて、前記論理シミュレーション実行手段がシミュレーションを行うステップを実行し、

前記カバレッジ回路は、前記論理回路を構成する各前記論理素子に接続され、

前記抑止回路は、各前記カバレッジ回路に接続され、

前記論理シミュレーション実行手段が、シミュレーションを実行することにより、前記カバレッジ回路は、当該カバレッジ回路が接続されている論理素子のカバレッジ情報を抽出し、

前記カバレッジ情報取得部は、前記カバレッジ回路が抽出した前記カバレッジ情報を取得し、

前記制御手段は、カバレッジ情報を抽出しない対象の論理素子に接続されたカバレッジ回路に接続された抑止回路に、カバレッジ回路の動作を中止させるための信号を送信するステップを実行し、

前記抑止回路は、前記信号を受信することにより、カバレッジ回路を動作を中止させるための信号を、当該抑止回路に接続されたカバレッジ回路に送信し、

前記カバレッジ回路は、前記抑止回路から前記信号を受信することにより、カバレッジ情報を抽出する動作を中止すること、

を特徴とする論理検証プログラム。

【請求項1】

テストパターンを用いて論理回路のシミュレーションを実行し、前記テストパターンによって実際にテストされた、前記論理回路を構成する論理素子に関する情報であるカバレッジ情報を取得する論理検証システムであって、

論理シミュレーションを実行する論理シミュレーション実行部と、前記カバレッジ情報を前記論理シミュレーション実行部から取得するカバレッジ情報取得部と、取得した前記カバレッジ情報を解析するカバレッジ情報解析部と、前記論理シミュレーション実行部の動作の制御を行う制御部と、

を備え、

前記カバレッジ解析部は、

前記カバレッジ情報取得部が取得したカバレッジ情報を基にして、一度テストされた論理素子に関するカバレッジ情報を抽出しない旨の指示を前記制御部に出し、

全ての前記論理素子がテストされたことを検出した場合は、シミュレーションの実行を中止する旨の指示を前記制御部に出し、

前記制御部は、

前記カバレッジ解析部から一度テストされた論理素子に関するカバレッジ情報を抽出しない旨の指示を受信したとき、前記論理シミュレーション実行部を制御して抽出しない対象の論理素子からのカバレッジ情報の抽出動作を中止させ、

前記カバレッジ解析部からシミュレーションの実行を中止する旨の指示を受信したとき、前記論理シミュレーション実行部を制御してシミュレーションを中止させること、

を特徴とする論理検証システム。

【請求項2】

請求項1に記載の論理検証システムであって、

前記論理回路と、前記論理回路からカバレッジ情報を抽出するためのカバレッジ回路と、前記カバレッジ回路の動作を中止させるための抑止回路と、前記テストパターンとを用いて、前記論理シミュレーション実行部がシミュレーションを行い、

前記カバレッジ回路は、前記論理回路を構成する各前記論理素子に接続され、

前記抑止回路は、各前記カバレッジ回路に接続され、

前記論理シミュレーション実行部が、シミュレーションを実行することにより、前記カバレッジ回路は、当該カバレッジ回路が接続されている論理素子のカバレッジ情報を抽出し、

前記カバレッジ情報取得部は、前記カバレッジ回路が抽出した前記カバレッジ情報を取得し、

前記制御部は、カバレッジ情報を抽出しない対象の論理素子に接続されたカバレッジ回路に接続された抑止回路に、カバレッジ回路の動作を中止させるための信号を送信し、

前記抑止回路は、前記信号を受信することにより、カバレッジ回路を動作を中止させるための信号を、当該抑止回路に接続されたカバレッジ回路に送信し、

前記カバレッジ回路は、前記抑止回路から前記信号を受信することにより、カバレッジ情報を抽出する動作を中止すること、

を特徴とする論理検証システム。

【請求項3】

コンピュータに、テストパターンを用いて論理回路のシミュレーションを実行させ、前記テストパターンによって実際にテストされた、前記論理回路を構成する論理素子に関する情報であるカバレッジ情報を取得させるための論理検証プログラムであって、

コンピュータを、論理シミュレーションを実行する論理シミュレーション実行手段と、前記カバレッジ情報を前記論理シミュレーション実行手段から取得するカバレッジ情報取得手段と、取得した前記カバレッジ情報を解析するカバレッジ情報解析手段と、前記論理シミュレーション実行手段の動作の制御を行う制御手段と、

して機能させ、

前記カバレッジ解析手段は、

前記カバレッジ情報取得手段が取得したカバレッジ情報を基にして、一度テストされた論理素子に関するカバレッジ情報を抽出しない旨の指示を前記制御手段に出すステップを実行し、

全ての前記論理素子がテストされたことを検出した場合は、シミュレーションの実行を中止する旨の指示を前記制御手段に出すステップを実行し、

前記制御手段は、

前記カバレッジ解析手段から一度テストされた論理素子に関するカバレッジ情報を抽出しない旨の指示を受信したとき、前記論理シミュレーション実行手段を制御して抽出しない対象の論理素子からのカバレッジ情報の抽出動作を中止させるステップを実行し、

前記カバレッジ解析手段からシミュレーションの実行を中止する旨の指示を受信したとき、前記論理シミュレーション実行手段を制御してシミュレーションを中止させるステップを実行すること、

を特徴とする論理検証プログラム。

【請求項4】

請求項3に記載の論理検証プログラムであって、

前記論理回路と、前記論理回路からカバレッジ情報を抽出するためのカバレッジ回路と、前記カバレッジ回路の動作を中止させるための抑止回路と、前記テストパターンとを用いて、前記論理シミュレーション実行手段がシミュレーションを行うステップを実行し、

前記カバレッジ回路は、前記論理回路を構成する各前記論理素子に接続され、

前記抑止回路は、各前記カバレッジ回路に接続され、

前記論理シミュレーション実行手段が、シミュレーションを実行することにより、前記カバレッジ回路は、当該カバレッジ回路が接続されている論理素子のカバレッジ情報を抽出し、

前記カバレッジ情報取得部は、前記カバレッジ回路が抽出した前記カバレッジ情報を取得し、

前記制御手段は、カバレッジ情報を抽出しない対象の論理素子に接続されたカバレッジ回路に接続された抑止回路に、カバレッジ回路の動作を中止させるための信号を送信するステップを実行し、

前記抑止回路は、前記信号を受信することにより、カバレッジ回路を動作を中止させるための信号を、当該抑止回路に接続されたカバレッジ回路に送信し、

前記カバレッジ回路は、前記抑止回路から前記信号を受信することにより、カバレッジ情報を抽出する動作を中止すること、

を特徴とする論理検証プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2009−223861(P2009−223861A)

【公開日】平成21年10月1日(2009.10.1)

【国際特許分類】

【出願番号】特願2008−70761(P2008−70761)

【出願日】平成20年3月19日(2008.3.19)

【出願人】(000233295)日立情報通信エンジニアリング株式会社 (195)

【Fターム(参考)】

【公開日】平成21年10月1日(2009.10.1)

【国際特許分類】

【出願日】平成20年3月19日(2008.3.19)

【出願人】(000233295)日立情報通信エンジニアリング株式会社 (195)

【Fターム(参考)】

[ Back to top ]