負荷回路の制御装置

【課題】並列に接続したMOSFETの発熱を均一化することが可能な負荷回路の制御装置を提供する。

【解決手段】電源と負荷とを接続する負荷回路に、2個のMOSFET(Q1),(Q2)を並列に配置する。そして、各MOSFET(Q1),(Q2)が交互にオン、オフとなるように制御する。その結果、各MOSFET(Q1),(Q2)のいずれか一方にのみ電流が流れることになるので、電流センサ12,22で検出されるオフセット誤差は、いずれか一方のオフセット誤差のみとなり、高精度な電流検出が可能となる。従って、負荷に流れる電流が過電流となった際に回路を遮断する制御を行う際に、高精度な遮断制御が可能となる。

【解決手段】電源と負荷とを接続する負荷回路に、2個のMOSFET(Q1),(Q2)を並列に配置する。そして、各MOSFET(Q1),(Q2)が交互にオン、オフとなるように制御する。その結果、各MOSFET(Q1),(Q2)のいずれか一方にのみ電流が流れることになるので、電流センサ12,22で検出されるオフセット誤差は、いずれか一方のオフセット誤差のみとなり、高精度な電流検出が可能となる。従って、負荷に流れる電流が過電流となった際に回路を遮断する制御を行う際に、高精度な遮断制御が可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の半導体スイッチを用いて、負荷回路のオン、オフを制御する制御装置に関する。

【背景技術】

【0002】

例えば、車両に搭載されるモータやランプ等の負荷は、バッテリとの間にFET等の半導体スイッチを設け、該FETのオン、オフを切り替えることにより、負荷の駆動、停止を制御する。また、負荷回路に大電流が流れる場合には、複数の半導体スイッチを並列に接続し、各半導体スイッチを同一の制御信号で制御することにより、負荷回路に流れる電流を分散させて1つの半導体スイッチに流れる電流を低減させ、ひいては発熱を抑制するる方式が提案されている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−310720号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した特許文献1に開示された従来例では、半導体スイッチを構成する各素子のばらつきにより、各半導体スイッチに流れる電流に偏りが発生し、特定の半導体スイッチの発熱量が大きくなるという問題が発生する。

【0005】

本発明は、このような従来の課題を解決するためになされたものであり、その目的とするところは、並列に接続した半導体スイッチの発熱を均一化することが可能な負荷回路の制御装置を提供することにある。

【課題を解決するための手段】

【0006】

上記目的を達成するため、本願請求項1に記載の発明は、電源(VB)と負荷(RL)とを接続する負荷回路に、複数の半導体スイッチ(MOSFETQ1,Q2)を並列に配置し、各半導体スイッチのオン、オフを切り替えることにより、前記負荷の駆動、停止を制御する負荷回路の制御装置において、前記各半導体スイッチにそれぞれ設けられ、各半導体スイッチに流れる電流を検出する電流検出手段(電流センサ12,22)と、駆動指令信号が入力された際に、前記各半導体スイッチ毎にそれぞれ異なるオン時間帯、及びオフ時間帯となるように各半導体スイッチに制御信号を出力する制御を行い、且つ、前記電流検出手段により検出される電流に基づいて、前記各半導体スイッチを遮断する制御を行う制御手段(制御部31)と、を有することを特徴とする。

【0007】

請求項2に記載の発明は、前記電流検出手段は、オペアンプを用いて前記半導体スイッチに流れる電流に比例した参照電流を発生させ、該参照電流に基づいて、前記半導体スイッチに流れる電流を検出することを特徴とする。

【0008】

請求項3に記載の発明は、前記制御手段は、前記各半導体スイッチのうちのいずれか一つがオンとなるように、各半導体スイッチのオン時間帯、及びオフ時間帯を設定することを特徴とする。

【0009】

請求項4に記載の発明は、前記制御手段は、前記各半導体スイッチに対して順次オン時間帯を設定すると共に、今回オンとする半導体スイッチのオン時間帯と、次回オンとする半導体スイッチのオン時間帯が若干重複するように、各半導体スイッチのオン時間帯、及びオフ時間帯を設定することを特徴とする。

【発明の効果】

【0010】

請求項1の発明では、負荷回路に複数の半導体スイッチの並列接続を配置し、各半導体のオン時間帯、及びオフ時間帯をそれぞれ設定するので、電流検出手段に存在するオフセット誤差による影響を軽減することができ、高精度な電流検出が可能となる。その結果、負荷回路に過電流が流れた場合には即時にこれを検出して負荷回路を遮断することが可能となる。

【0011】

請求項2の発明では、電流検出手段がオペアンプを備えており、オペアンプを用いて半導体スイッチに流れる電流に比例した参照電流を発生させ、この参照電流に基づいて半導体スイッチに流れる電流を検出するので、電流検出の精度を向上させることができる。

【0012】

請求項3の発明では、複数の半導体スイッチのうちいずれか一つがオンとなるように制御されるので、電流検出手段に存在するオフセット誤差による影響を低減でき、電流検出を高精度に行うことが可能となる。

【0013】

請求項4の発明では、今回オンとなる半導体スイッチがオフとなる前に、次回オンとなる半導体スイッチがオンとなるので、オンとする半導体スイッチが切り替わる際に、若干の重複時間が存在し、ノイズの発生を低減することが可能となる。

【図面の簡単な説明】

【0014】

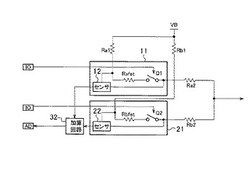

【図1】本発明の一実施形態に係る制御装置が設けられた負荷回路を示す説明図である。

【図2】本発明の一実施形態に係る負荷回路の制御装置の、各配線に存在する抵抗を等価的示した説明図であり、Q1,Q2が共にオフの状態を示す。

【図3】本発明の一実施形態に係る負荷回路の制御装置の、各配線に存在する抵抗を等価的示した説明図であり、Q1,Q2が共にオンの状態を示す。

【図4】本発明の一実施形態に係る負荷回路の制御装置の、各配線に存在する抵抗を等価的示した説明図であり、Q1がオフ、Q2がオンの状態を示す。

【図5】本発明の一実施形態に係る負荷回路の制御装置の、各配線に存在する抵抗を等価的示した説明図であり、Q1がオン、Q2がオフの状態を示す。

【図6】本発明の一実施形態に係る負荷回路の制御装置に設けられる電流センサの構成を示す回路図である。

【図7】本発明の一実施形態に係る負荷回路の制御装置の、各半導体スイッチ回路のオン時間帯、オフ時間帯を示すタイミングチャート図である。

【図8】本発明の一実施形態に係る負荷回路の制御装置の、各MOSFETの温度上昇を示す特性図である。

【図9】本発明の一実施形態に係る負荷回路の制御装置の、各半導体スイッチのオン時間、オフ時間を適切に設定した場合のオン時間帯、オフ時間帯、及び各MOSFETの温度変化を示すタイミングチャートである。

【図10】本発明の変形例に係る負荷回路の制御装置の、各MOSFETのオン時間帯、オフ時間帯を示すタイミングチャートである。

【発明を実施するための形態】

【0015】

以下、本発明の実施形態を図面に基づいて説明する。図1は、本発明の一実施形態に係る制御装置が接続された負荷回路示す回路図である。図1に示すように、本実施形態に係る制御装置100は、バッテリVBと負荷RLとの間に設置され、負荷RLのオン、オフを制御するものであり、互いに並列に接続された2つの半導体スイッチ回路11,21と、制御部31と、加算回路32を備えている。

【0016】

半導体スイッチ回路11は、一つの半導体チップで構成されており、MOSFET(Q1;半導体スイッチ)と、該MOSFET(Q1)に流れる電流を検出する電流センサ(電流検出手段)12を備えている。そして、MOSFET(Q1)のドレインは端子TB11を介してバッテリVBに接続され、ソースは端子TB12を介してモータやランプ等の負荷RLに接続されている。更に、MOSFET(Q1)のゲートは、端子TB13を介して制御部31に接続され(図ではTB13〜Q1間の接続線を省略)、電流センサ12は端子TB14を介して加算回路32に接続されている。

【0017】

半導体スイッチ回路21についても同様に、一つの半導体チップで構成されており、MOSFET(Q2)と、該MOSFET(Q2)に流れる電流を検出する電流センサ22を備えている。そして、MOSFET(Q2)のドレインは端子TB21を介してバッテリVBに接続され、ソースは端子T22を介して負荷RLに接続されている。更に、MOSFET(Q2)のゲートは、端子TB23を介して制御部31に接続され(図ではTB23〜Q2間の接続線を省略)、電流センサ22は端子TB14を介して加算回路32に接続されている。そして、加算回路32の出力端子は制御部31に接続されている。

【0018】

図2は、図1に示した制御装置100に存在する配線抵抗、及び半導体素子の抵抗を等価的に示す回路であり、バッテリVBと半導体スイッチ回路11とを接続する配線(図1のVB〜TB11間の配線)には抵抗Ra1が存在し、半導体スイッチ回路11と負荷RLとの間(図1のTB12〜RL間の配線)には抵抗Ra2が存在し、MOSFET(Q1)にはオン抵抗Rafetが存在する。同様に、バッテリVBと半導体スイッチ回路21とを接続する配線(図1のVB〜TB21間の配線)には抵抗Rb1が存在し、半導体スイッチ回路21と負荷RLとの間(図1のTB22〜RL間の配線)には抵抗Rb2が存在し、MOSFET(Q2)にはオン抵抗Rbfetが存在する。

【0019】

次に、電流センサ12,22、及び加算回路32の詳細な構成について、図6に示す回路図を参照して説明する。図6に示すように、MOSFET(Q1)は、メインFET(Q1a)とサブFET(Q1b)から成るマルチソースFETを構成しており、メインFET(Q1a)のソースは2系統に分岐され、一つ目の分岐線は図1に示した端子TB12を介して負荷RLに接続され、二つ目の分岐線はアンプAMP11の一方の入力端子に接続されている。また、サブFET(Q1b)のソースは2系統に分岐され、一つ目の分岐線はP型のMOSFET(Q11)のソースに接続され、二つ目の分岐線はアンプAMP11の他方の入力端子に接続されている。

【0020】

更に、アンプAMP11の出力端子は、MOSFET(Q11)のゲートに接続され、該MOSFET(Q11)のドレインはセンス抵抗Rsを介してグランドに接地されている。

【0021】

従って、アンプAMP11は、メインFET(Q1a)のソース電圧とサブFET(Q1b)のソース電圧が等しくなるように、MOSFET(Q11)のゲートに制御信号を出力するので、MOSFET(Q11)にはMOSFET(Q1)に流れる電流に比例した大きさの電流が流れることになる。

【0022】

MOSFET(Q2)についても同様に、メインFET(Q2a)とサブFET(Q2b)から成るマルチソースFETを構成しており、メインFET(Q2a)のソースはアンプAMP21の一方の入力端子に接続され、サブFET(Q2b)のソースはアンプAMP21の他方の入力端子に接続されている。

【0023】

更にアンプAMP21の出力端子は、P型のMOSFET(Q21)のゲートに接続され、該MOSFET(Q21)のソースはサブFET(Q2b)に接続され、ドレインはセンス抵抗Rsを介してグランドに接地されている。

【0024】

従って、アンプAMP21は、メインFET(Q2a)のソース電圧とサブFET(Q2b)のソース電圧が等しくなるように、MOSFET(Q21)のゲートに制御信号を出力するので、MOSFET(Q21)にはMOSFET(Q2)に流れる電流に比例した大きさの電流が流れることになる。

【0025】

また、各MOSFET(Q11),(Q21)に流れる電流(参照電流)を加算した電流がセンス抵抗Rsに流れるので、該センス抵抗Rsの両端電圧を測定することにより、負荷RLに流れる電流を測定することができる。即ち、電流センサ12,22(電流検出手段)は、オペアンプを用いてMOSFET(Q1,Q2;半導体スイッチ)に流れる電流に比例した参照電流を発生させ、該参照電流に基づいて、MOSFET(Q1,Q2)に流れる電流を検出する。また、センス抵抗Rsが、図1に示した加算回路32に相当する。

【0026】

更に、図1に示した制御部31は、MOSFET(Q1)に流れる電流Iaと、MOSFET(Q2)に流れる電流Ibを加算した電流Icに基づき、電流Icが予め設定した閾値を上回った場合には、各MOSFET(Q1),(Q2)をオフとして負荷回路を遮断し、回路全体を保護する制御を行う。或いは、電流Icに基づいて負荷回路の電線温度を推定し、推定温度が閾値を上回った場合には負荷回路を遮断して、回路全体を過熱から保護する制御を行う。

【0027】

そして、本実施形態では、各MOSFET(Q1),(Q2)のオン、オフを交互に切り替えることにより、各MOSFET(Q1),(Q2)のうちの一方をオン、他方をオフとして、各MOSFET(Q1),(Q2)に流れる電流の偏りを抑制する。以下、各MOSFET(Q1),(Q2)を同時にオンとして負荷RLを駆動する場合(従来の方式)と、各MOSFET(Q1),(Q2)を交互に切り替えて負荷RLを駆動する場合(本発明の方式)の双方における、電流の偏りについて説明する。

【0028】

[Q1,Q2を同時にオンとする場合]

初めに、2つの半導体スイッチ回路11,21を共にオンすることにより、負荷RLに流れる電流を、2つの半導体スイッチ回路11,21に分散する場合の動作について説明する。図2に示した等価回路によると、半導体スイッチ回路11を経由する回路の抵抗(これを、Raとする)は、次の(1)式で示すことができる。

【0029】

Ra=Ra1+Rafet+Ra2 …(1)

同様に、半導体スイッチ回路21を経由する回路の抵抗(これを、Rbとする)は、次の(2)式で示すことができる。

【0030】

Rb=Rb1+Rbfet+Rb2 …(2)

従って、図3に示すように、2つのMOSFET(Q1),(Q2)を共にオンとした場合には、半導体スイッチ回路11に電流Iaが流れ、半導体スイッチ回路21に電流Ibが流れることになり、電流Iaと電流Ibの比率「Ia/Ib」は、抵抗の逆比に等しいので「Ia/Ib=Rb/Ra」となる。

【0031】

この際、図6に示した電流センサ12,22では、仮にアンプAMP11,AMP21にオフセット誤差が存在しなければ、MOSFET(Q1)の両端電圧Vafetを、「Vafet=Rafet*Ia」として検出し、MOSFET(Q2)の両端電圧Vbfetを、「Vbfet=Rbfet*Ib」として検出することになる。しかし、実際にはアンプAMP11,AMP21にはオフセット誤差Vaoffset,Vboffsetが存在するので、各電圧Vafet,Vbfetを以下に示す(3)式、(4)式のように検出してしまう。

【0032】

Vafet=Rafet*Ia+Vaoffset …(3)

Vbfet=Rbfet*Ib+Vboffset …(4)

従って、電流Ia,Ibの測定値Iasens,Ibsensは、次の(5)式、(6)式として検出されることになる。

【0033】

Iasens=(Vafet/Rafet)=Ia+Vaoffset/Rafet …(5)

Ibsens=(Vbfet/Rbfet)=Ib+Vboffset/Rbfet …(6)

負荷RLに流れる電流をIcとすると、その測定値Icsensは(5)式と(6)式を加算するので、下記の(7)式として検出される。

【0034】

Icsens=Ic+Vaoffset/Rafet+Vboffset/Rbfet …(7)

(7)式から理解されるように、MOSFET(Q1),(Q2)を共にオンとして負荷RLに電流を流すと、本来測定しようとする電流Icに対して2つの電流センサ12,22のオフセット誤差の成分が加算されてしまう。更に(7)式より、抵抗Rafet、Rbfetが小さい程、その影響(Icに対する割合)が大きくなるので、MOSFET(Q1),(Q2)の発熱、即ち、ジュール熱「Rafet*Ia2+Rbfet*Ib2」を抑えるために抵抗Rafet、Rbfetを小さくすると、より誤差の影響を助長することになる。

【0035】

[Q1,Q2を交互にオンとする場合]

次に、MOSFET(Q1),(Q2)を交互にオンとして負荷RLに電流を供給する場合の動作について説明する。この場合には、図7に示すように、MOSFET(Q1)がオン時間帯のときに、MOSFET(Q2)をオフ時間帯とし、MOSFET(Q1)がオフ時間帯のときに、MOSFET(Q2)をオン時間帯とするように、各MOSFET(Q1),(Q2)を制御する。

【0036】

そして、負荷RLに流れる電流Icの測定値Icsensは、MOSFET(Q1)がオンのとき(図5参照)には下記の(8)式で示され、MOSFET(Q2)がオンのとき(図4参照)には、下記の(9)式で示されることになる。

【0037】

Icsens=Ic+Vaoffset/Rafet …(8)

Icsens=Ic+Vboffset/Rbfet …(9)

(8),(9)式より、MOSFET(Q1),(Q2)を交互に動作させる場合には、一方の電流センサの誤差のみが発生することとなる。

【0038】

このように、いずれか一方のMOSFETのみをオンとすることにより、アンプが有するオフセット誤差の影響を低減することができることが理解される。

【0039】

また、2つのMOSFET(Q1),(Q2)は、オン抵抗が同一であるとは限らないので、各MOSFET(Q1),(Q2)のオン時間帯、及びオフ時間帯を均一に設定すると、各MOSFETの発熱量に偏りが発生する場合があり、一方のMOSFETの温度上昇が大きくなるという問題が生じる。

【0040】

本実施形態では、MOSFETの温度の上昇し易さに応じて、オン時間帯、及びオフ時間帯を調整し、各MOSFET(Q1),(Q2)の温度が均一となるようにする。具体的には、温度が上昇し易いMOSFETについてはオン時間帯を短く設定し、反対に、温度が上昇し難いMOSFETについてはオン時間帯を長く設定する。

【0041】

温度が上昇し易いか否かの判断は、MOSFETの電気抵抗、熱抵抗の理論値を用いる方法、基板設計後にサンプルの実測値を取得し、この実測値に基づいて判断する方法、或いは、出荷前の検査時に各製品毎に温度上昇の度合いを測定する方法等を用いることができる。

【0042】

例えば、図8に示すように、一定時間の通電によりMOSFET(Q1)の温度がT1となり、MOSFET(Q2)の温度がT1よりも高いT2となる場合には、図9(a),(b)に示すように、MOSFET(Q1)のオン時間をt1とし、MOSFET(Q2)のオン時間をt2(<t1)とすることにより、各MOSFET(Q1),(Q2)の温度を均一化させる。具体的には、図9(c)に示すように、MOSFET(Q1)の温度は曲線p1に示すように上昇、下降を繰り返して変化し、MOSFET(Q2)の温度は曲線p2に示すように上昇、下降を繰り返して変化する。その結果、温度T1とT2の平均値に収束することになり、各MOSFET(Q1),(Q2)の温度を均一化することができる。

【0043】

このようにして、本実施形態に係る負荷回路の制御装置100では、2つのMOSFET(Q1),(Q2)を並列に配置し、いずれか一方をオンとするように制御するので、電流センサ12,22のアンプAMP11,AMP21にオフセット誤差が存在する場合であっても、このオフセット誤差の影響を低減することができ、高精度な電流検出が可能となる。従って、検出した電流値に基づいて半導体スイッチ回路11,21を遮断する制御を実行する場合には、高精度な遮断制御が可能となる。

【0044】

また、各MOSFET(Q1),(Q2)のオン抵抗にばらつきが存在する場合であっても、各MOSFET(Q1),(Q2)のオン時間帯、及びオフ時間帯を適宜設定することにより、全体の温度を均一化することが可能となる。

【0045】

[変形例の説明]

次に、上述した実施形態の変形例について説明する。上述した実施形態では、図7に示したように、一方のMOSFETがオンの時には他方のMOSFETがオフとなるように制御したが、変形例では図10(a),(b)に示すように、MOSFET(Q2)がオンからオフに切り替わるタイミングよりも、MOSFET(Q1)がオフからオンに切り替わるタイミングの方が若干時間Δtだけ早くなるように制御する。即ち、双方のMOSFETのオン時間帯に若干の重複時間を設けている。

【0046】

このような構成によれば、各MOSFETのオン、オフ切替時におけるノイズを低減することができる。

【0047】

以上、本発明の負荷回路の制御装置を図示の実施形態に基づいて説明したが、本発明はこれに限定されるものではなく、各部の構成は、同様の機能を有する任意の構成のものに置き換えることができる。

【0048】

例えば、上述した本実施形態では、2つの半導体スイッチ回路11,21を並列に接続し、各MOSFET(Q1),(Q2)を交互にオンとするように制御する例について説明したが、本発明はこれに限定されるものではなく、3個以上の半導体スイッチ回路を設け、各半導体スイッチ回路を順繰りにオンとすることで、上述と同様の効果を達成することが可能となる。

【産業上の利用可能性】

【0049】

本発明は、複数の半導体スイッチを用いて負荷を駆動する際の、電流の偏りを防止することに利用できる。

【符号の説明】

【0050】

11,21 半導体スイッチ回路

12,22 電流センサ

31 制御部

32 加算回路

100 制御装置

Q1,Q2 MOSFET

【技術分野】

【0001】

本発明は、複数の半導体スイッチを用いて、負荷回路のオン、オフを制御する制御装置に関する。

【背景技術】

【0002】

例えば、車両に搭載されるモータやランプ等の負荷は、バッテリとの間にFET等の半導体スイッチを設け、該FETのオン、オフを切り替えることにより、負荷の駆動、停止を制御する。また、負荷回路に大電流が流れる場合には、複数の半導体スイッチを並列に接続し、各半導体スイッチを同一の制御信号で制御することにより、負荷回路に流れる電流を分散させて1つの半導体スイッチに流れる電流を低減させ、ひいては発熱を抑制するる方式が提案されている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−310720号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した特許文献1に開示された従来例では、半導体スイッチを構成する各素子のばらつきにより、各半導体スイッチに流れる電流に偏りが発生し、特定の半導体スイッチの発熱量が大きくなるという問題が発生する。

【0005】

本発明は、このような従来の課題を解決するためになされたものであり、その目的とするところは、並列に接続した半導体スイッチの発熱を均一化することが可能な負荷回路の制御装置を提供することにある。

【課題を解決するための手段】

【0006】

上記目的を達成するため、本願請求項1に記載の発明は、電源(VB)と負荷(RL)とを接続する負荷回路に、複数の半導体スイッチ(MOSFETQ1,Q2)を並列に配置し、各半導体スイッチのオン、オフを切り替えることにより、前記負荷の駆動、停止を制御する負荷回路の制御装置において、前記各半導体スイッチにそれぞれ設けられ、各半導体スイッチに流れる電流を検出する電流検出手段(電流センサ12,22)と、駆動指令信号が入力された際に、前記各半導体スイッチ毎にそれぞれ異なるオン時間帯、及びオフ時間帯となるように各半導体スイッチに制御信号を出力する制御を行い、且つ、前記電流検出手段により検出される電流に基づいて、前記各半導体スイッチを遮断する制御を行う制御手段(制御部31)と、を有することを特徴とする。

【0007】

請求項2に記載の発明は、前記電流検出手段は、オペアンプを用いて前記半導体スイッチに流れる電流に比例した参照電流を発生させ、該参照電流に基づいて、前記半導体スイッチに流れる電流を検出することを特徴とする。

【0008】

請求項3に記載の発明は、前記制御手段は、前記各半導体スイッチのうちのいずれか一つがオンとなるように、各半導体スイッチのオン時間帯、及びオフ時間帯を設定することを特徴とする。

【0009】

請求項4に記載の発明は、前記制御手段は、前記各半導体スイッチに対して順次オン時間帯を設定すると共に、今回オンとする半導体スイッチのオン時間帯と、次回オンとする半導体スイッチのオン時間帯が若干重複するように、各半導体スイッチのオン時間帯、及びオフ時間帯を設定することを特徴とする。

【発明の効果】

【0010】

請求項1の発明では、負荷回路に複数の半導体スイッチの並列接続を配置し、各半導体のオン時間帯、及びオフ時間帯をそれぞれ設定するので、電流検出手段に存在するオフセット誤差による影響を軽減することができ、高精度な電流検出が可能となる。その結果、負荷回路に過電流が流れた場合には即時にこれを検出して負荷回路を遮断することが可能となる。

【0011】

請求項2の発明では、電流検出手段がオペアンプを備えており、オペアンプを用いて半導体スイッチに流れる電流に比例した参照電流を発生させ、この参照電流に基づいて半導体スイッチに流れる電流を検出するので、電流検出の精度を向上させることができる。

【0012】

請求項3の発明では、複数の半導体スイッチのうちいずれか一つがオンとなるように制御されるので、電流検出手段に存在するオフセット誤差による影響を低減でき、電流検出を高精度に行うことが可能となる。

【0013】

請求項4の発明では、今回オンとなる半導体スイッチがオフとなる前に、次回オンとなる半導体スイッチがオンとなるので、オンとする半導体スイッチが切り替わる際に、若干の重複時間が存在し、ノイズの発生を低減することが可能となる。

【図面の簡単な説明】

【0014】

【図1】本発明の一実施形態に係る制御装置が設けられた負荷回路を示す説明図である。

【図2】本発明の一実施形態に係る負荷回路の制御装置の、各配線に存在する抵抗を等価的示した説明図であり、Q1,Q2が共にオフの状態を示す。

【図3】本発明の一実施形態に係る負荷回路の制御装置の、各配線に存在する抵抗を等価的示した説明図であり、Q1,Q2が共にオンの状態を示す。

【図4】本発明の一実施形態に係る負荷回路の制御装置の、各配線に存在する抵抗を等価的示した説明図であり、Q1がオフ、Q2がオンの状態を示す。

【図5】本発明の一実施形態に係る負荷回路の制御装置の、各配線に存在する抵抗を等価的示した説明図であり、Q1がオン、Q2がオフの状態を示す。

【図6】本発明の一実施形態に係る負荷回路の制御装置に設けられる電流センサの構成を示す回路図である。

【図7】本発明の一実施形態に係る負荷回路の制御装置の、各半導体スイッチ回路のオン時間帯、オフ時間帯を示すタイミングチャート図である。

【図8】本発明の一実施形態に係る負荷回路の制御装置の、各MOSFETの温度上昇を示す特性図である。

【図9】本発明の一実施形態に係る負荷回路の制御装置の、各半導体スイッチのオン時間、オフ時間を適切に設定した場合のオン時間帯、オフ時間帯、及び各MOSFETの温度変化を示すタイミングチャートである。

【図10】本発明の変形例に係る負荷回路の制御装置の、各MOSFETのオン時間帯、オフ時間帯を示すタイミングチャートである。

【発明を実施するための形態】

【0015】

以下、本発明の実施形態を図面に基づいて説明する。図1は、本発明の一実施形態に係る制御装置が接続された負荷回路示す回路図である。図1に示すように、本実施形態に係る制御装置100は、バッテリVBと負荷RLとの間に設置され、負荷RLのオン、オフを制御するものであり、互いに並列に接続された2つの半導体スイッチ回路11,21と、制御部31と、加算回路32を備えている。

【0016】

半導体スイッチ回路11は、一つの半導体チップで構成されており、MOSFET(Q1;半導体スイッチ)と、該MOSFET(Q1)に流れる電流を検出する電流センサ(電流検出手段)12を備えている。そして、MOSFET(Q1)のドレインは端子TB11を介してバッテリVBに接続され、ソースは端子TB12を介してモータやランプ等の負荷RLに接続されている。更に、MOSFET(Q1)のゲートは、端子TB13を介して制御部31に接続され(図ではTB13〜Q1間の接続線を省略)、電流センサ12は端子TB14を介して加算回路32に接続されている。

【0017】

半導体スイッチ回路21についても同様に、一つの半導体チップで構成されており、MOSFET(Q2)と、該MOSFET(Q2)に流れる電流を検出する電流センサ22を備えている。そして、MOSFET(Q2)のドレインは端子TB21を介してバッテリVBに接続され、ソースは端子T22を介して負荷RLに接続されている。更に、MOSFET(Q2)のゲートは、端子TB23を介して制御部31に接続され(図ではTB23〜Q2間の接続線を省略)、電流センサ22は端子TB14を介して加算回路32に接続されている。そして、加算回路32の出力端子は制御部31に接続されている。

【0018】

図2は、図1に示した制御装置100に存在する配線抵抗、及び半導体素子の抵抗を等価的に示す回路であり、バッテリVBと半導体スイッチ回路11とを接続する配線(図1のVB〜TB11間の配線)には抵抗Ra1が存在し、半導体スイッチ回路11と負荷RLとの間(図1のTB12〜RL間の配線)には抵抗Ra2が存在し、MOSFET(Q1)にはオン抵抗Rafetが存在する。同様に、バッテリVBと半導体スイッチ回路21とを接続する配線(図1のVB〜TB21間の配線)には抵抗Rb1が存在し、半導体スイッチ回路21と負荷RLとの間(図1のTB22〜RL間の配線)には抵抗Rb2が存在し、MOSFET(Q2)にはオン抵抗Rbfetが存在する。

【0019】

次に、電流センサ12,22、及び加算回路32の詳細な構成について、図6に示す回路図を参照して説明する。図6に示すように、MOSFET(Q1)は、メインFET(Q1a)とサブFET(Q1b)から成るマルチソースFETを構成しており、メインFET(Q1a)のソースは2系統に分岐され、一つ目の分岐線は図1に示した端子TB12を介して負荷RLに接続され、二つ目の分岐線はアンプAMP11の一方の入力端子に接続されている。また、サブFET(Q1b)のソースは2系統に分岐され、一つ目の分岐線はP型のMOSFET(Q11)のソースに接続され、二つ目の分岐線はアンプAMP11の他方の入力端子に接続されている。

【0020】

更に、アンプAMP11の出力端子は、MOSFET(Q11)のゲートに接続され、該MOSFET(Q11)のドレインはセンス抵抗Rsを介してグランドに接地されている。

【0021】

従って、アンプAMP11は、メインFET(Q1a)のソース電圧とサブFET(Q1b)のソース電圧が等しくなるように、MOSFET(Q11)のゲートに制御信号を出力するので、MOSFET(Q11)にはMOSFET(Q1)に流れる電流に比例した大きさの電流が流れることになる。

【0022】

MOSFET(Q2)についても同様に、メインFET(Q2a)とサブFET(Q2b)から成るマルチソースFETを構成しており、メインFET(Q2a)のソースはアンプAMP21の一方の入力端子に接続され、サブFET(Q2b)のソースはアンプAMP21の他方の入力端子に接続されている。

【0023】

更にアンプAMP21の出力端子は、P型のMOSFET(Q21)のゲートに接続され、該MOSFET(Q21)のソースはサブFET(Q2b)に接続され、ドレインはセンス抵抗Rsを介してグランドに接地されている。

【0024】

従って、アンプAMP21は、メインFET(Q2a)のソース電圧とサブFET(Q2b)のソース電圧が等しくなるように、MOSFET(Q21)のゲートに制御信号を出力するので、MOSFET(Q21)にはMOSFET(Q2)に流れる電流に比例した大きさの電流が流れることになる。

【0025】

また、各MOSFET(Q11),(Q21)に流れる電流(参照電流)を加算した電流がセンス抵抗Rsに流れるので、該センス抵抗Rsの両端電圧を測定することにより、負荷RLに流れる電流を測定することができる。即ち、電流センサ12,22(電流検出手段)は、オペアンプを用いてMOSFET(Q1,Q2;半導体スイッチ)に流れる電流に比例した参照電流を発生させ、該参照電流に基づいて、MOSFET(Q1,Q2)に流れる電流を検出する。また、センス抵抗Rsが、図1に示した加算回路32に相当する。

【0026】

更に、図1に示した制御部31は、MOSFET(Q1)に流れる電流Iaと、MOSFET(Q2)に流れる電流Ibを加算した電流Icに基づき、電流Icが予め設定した閾値を上回った場合には、各MOSFET(Q1),(Q2)をオフとして負荷回路を遮断し、回路全体を保護する制御を行う。或いは、電流Icに基づいて負荷回路の電線温度を推定し、推定温度が閾値を上回った場合には負荷回路を遮断して、回路全体を過熱から保護する制御を行う。

【0027】

そして、本実施形態では、各MOSFET(Q1),(Q2)のオン、オフを交互に切り替えることにより、各MOSFET(Q1),(Q2)のうちの一方をオン、他方をオフとして、各MOSFET(Q1),(Q2)に流れる電流の偏りを抑制する。以下、各MOSFET(Q1),(Q2)を同時にオンとして負荷RLを駆動する場合(従来の方式)と、各MOSFET(Q1),(Q2)を交互に切り替えて負荷RLを駆動する場合(本発明の方式)の双方における、電流の偏りについて説明する。

【0028】

[Q1,Q2を同時にオンとする場合]

初めに、2つの半導体スイッチ回路11,21を共にオンすることにより、負荷RLに流れる電流を、2つの半導体スイッチ回路11,21に分散する場合の動作について説明する。図2に示した等価回路によると、半導体スイッチ回路11を経由する回路の抵抗(これを、Raとする)は、次の(1)式で示すことができる。

【0029】

Ra=Ra1+Rafet+Ra2 …(1)

同様に、半導体スイッチ回路21を経由する回路の抵抗(これを、Rbとする)は、次の(2)式で示すことができる。

【0030】

Rb=Rb1+Rbfet+Rb2 …(2)

従って、図3に示すように、2つのMOSFET(Q1),(Q2)を共にオンとした場合には、半導体スイッチ回路11に電流Iaが流れ、半導体スイッチ回路21に電流Ibが流れることになり、電流Iaと電流Ibの比率「Ia/Ib」は、抵抗の逆比に等しいので「Ia/Ib=Rb/Ra」となる。

【0031】

この際、図6に示した電流センサ12,22では、仮にアンプAMP11,AMP21にオフセット誤差が存在しなければ、MOSFET(Q1)の両端電圧Vafetを、「Vafet=Rafet*Ia」として検出し、MOSFET(Q2)の両端電圧Vbfetを、「Vbfet=Rbfet*Ib」として検出することになる。しかし、実際にはアンプAMP11,AMP21にはオフセット誤差Vaoffset,Vboffsetが存在するので、各電圧Vafet,Vbfetを以下に示す(3)式、(4)式のように検出してしまう。

【0032】

Vafet=Rafet*Ia+Vaoffset …(3)

Vbfet=Rbfet*Ib+Vboffset …(4)

従って、電流Ia,Ibの測定値Iasens,Ibsensは、次の(5)式、(6)式として検出されることになる。

【0033】

Iasens=(Vafet/Rafet)=Ia+Vaoffset/Rafet …(5)

Ibsens=(Vbfet/Rbfet)=Ib+Vboffset/Rbfet …(6)

負荷RLに流れる電流をIcとすると、その測定値Icsensは(5)式と(6)式を加算するので、下記の(7)式として検出される。

【0034】

Icsens=Ic+Vaoffset/Rafet+Vboffset/Rbfet …(7)

(7)式から理解されるように、MOSFET(Q1),(Q2)を共にオンとして負荷RLに電流を流すと、本来測定しようとする電流Icに対して2つの電流センサ12,22のオフセット誤差の成分が加算されてしまう。更に(7)式より、抵抗Rafet、Rbfetが小さい程、その影響(Icに対する割合)が大きくなるので、MOSFET(Q1),(Q2)の発熱、即ち、ジュール熱「Rafet*Ia2+Rbfet*Ib2」を抑えるために抵抗Rafet、Rbfetを小さくすると、より誤差の影響を助長することになる。

【0035】

[Q1,Q2を交互にオンとする場合]

次に、MOSFET(Q1),(Q2)を交互にオンとして負荷RLに電流を供給する場合の動作について説明する。この場合には、図7に示すように、MOSFET(Q1)がオン時間帯のときに、MOSFET(Q2)をオフ時間帯とし、MOSFET(Q1)がオフ時間帯のときに、MOSFET(Q2)をオン時間帯とするように、各MOSFET(Q1),(Q2)を制御する。

【0036】

そして、負荷RLに流れる電流Icの測定値Icsensは、MOSFET(Q1)がオンのとき(図5参照)には下記の(8)式で示され、MOSFET(Q2)がオンのとき(図4参照)には、下記の(9)式で示されることになる。

【0037】

Icsens=Ic+Vaoffset/Rafet …(8)

Icsens=Ic+Vboffset/Rbfet …(9)

(8),(9)式より、MOSFET(Q1),(Q2)を交互に動作させる場合には、一方の電流センサの誤差のみが発生することとなる。

【0038】

このように、いずれか一方のMOSFETのみをオンとすることにより、アンプが有するオフセット誤差の影響を低減することができることが理解される。

【0039】

また、2つのMOSFET(Q1),(Q2)は、オン抵抗が同一であるとは限らないので、各MOSFET(Q1),(Q2)のオン時間帯、及びオフ時間帯を均一に設定すると、各MOSFETの発熱量に偏りが発生する場合があり、一方のMOSFETの温度上昇が大きくなるという問題が生じる。

【0040】

本実施形態では、MOSFETの温度の上昇し易さに応じて、オン時間帯、及びオフ時間帯を調整し、各MOSFET(Q1),(Q2)の温度が均一となるようにする。具体的には、温度が上昇し易いMOSFETについてはオン時間帯を短く設定し、反対に、温度が上昇し難いMOSFETについてはオン時間帯を長く設定する。

【0041】

温度が上昇し易いか否かの判断は、MOSFETの電気抵抗、熱抵抗の理論値を用いる方法、基板設計後にサンプルの実測値を取得し、この実測値に基づいて判断する方法、或いは、出荷前の検査時に各製品毎に温度上昇の度合いを測定する方法等を用いることができる。

【0042】

例えば、図8に示すように、一定時間の通電によりMOSFET(Q1)の温度がT1となり、MOSFET(Q2)の温度がT1よりも高いT2となる場合には、図9(a),(b)に示すように、MOSFET(Q1)のオン時間をt1とし、MOSFET(Q2)のオン時間をt2(<t1)とすることにより、各MOSFET(Q1),(Q2)の温度を均一化させる。具体的には、図9(c)に示すように、MOSFET(Q1)の温度は曲線p1に示すように上昇、下降を繰り返して変化し、MOSFET(Q2)の温度は曲線p2に示すように上昇、下降を繰り返して変化する。その結果、温度T1とT2の平均値に収束することになり、各MOSFET(Q1),(Q2)の温度を均一化することができる。

【0043】

このようにして、本実施形態に係る負荷回路の制御装置100では、2つのMOSFET(Q1),(Q2)を並列に配置し、いずれか一方をオンとするように制御するので、電流センサ12,22のアンプAMP11,AMP21にオフセット誤差が存在する場合であっても、このオフセット誤差の影響を低減することができ、高精度な電流検出が可能となる。従って、検出した電流値に基づいて半導体スイッチ回路11,21を遮断する制御を実行する場合には、高精度な遮断制御が可能となる。

【0044】

また、各MOSFET(Q1),(Q2)のオン抵抗にばらつきが存在する場合であっても、各MOSFET(Q1),(Q2)のオン時間帯、及びオフ時間帯を適宜設定することにより、全体の温度を均一化することが可能となる。

【0045】

[変形例の説明]

次に、上述した実施形態の変形例について説明する。上述した実施形態では、図7に示したように、一方のMOSFETがオンの時には他方のMOSFETがオフとなるように制御したが、変形例では図10(a),(b)に示すように、MOSFET(Q2)がオンからオフに切り替わるタイミングよりも、MOSFET(Q1)がオフからオンに切り替わるタイミングの方が若干時間Δtだけ早くなるように制御する。即ち、双方のMOSFETのオン時間帯に若干の重複時間を設けている。

【0046】

このような構成によれば、各MOSFETのオン、オフ切替時におけるノイズを低減することができる。

【0047】

以上、本発明の負荷回路の制御装置を図示の実施形態に基づいて説明したが、本発明はこれに限定されるものではなく、各部の構成は、同様の機能を有する任意の構成のものに置き換えることができる。

【0048】

例えば、上述した本実施形態では、2つの半導体スイッチ回路11,21を並列に接続し、各MOSFET(Q1),(Q2)を交互にオンとするように制御する例について説明したが、本発明はこれに限定されるものではなく、3個以上の半導体スイッチ回路を設け、各半導体スイッチ回路を順繰りにオンとすることで、上述と同様の効果を達成することが可能となる。

【産業上の利用可能性】

【0049】

本発明は、複数の半導体スイッチを用いて負荷を駆動する際の、電流の偏りを防止することに利用できる。

【符号の説明】

【0050】

11,21 半導体スイッチ回路

12,22 電流センサ

31 制御部

32 加算回路

100 制御装置

Q1,Q2 MOSFET

【特許請求の範囲】

【請求項1】

電源と負荷とを接続する負荷回路に、複数の半導体スイッチを並列に配置し、各半導体スイッチのオン、オフを切り替えることにより、前記負荷の駆動、停止を制御する負荷回路の制御装置において、

前記各半導体スイッチにそれぞれ設けられ、各半導体スイッチに流れる電流を検出する電流検出手段と、

駆動指令信号が入力された際に、前記各半導体スイッチ毎にそれぞれ異なるオン時間帯、及びオフ時間帯となるように各半導体スイッチに制御信号を出力する制御を行い、且つ、前記電流検出手段により検出される電流に基づいて、前記各半導体スイッチを遮断する制御を行う制御手段と、

を有することを特徴とする負荷回路の制御装置。

【請求項2】

前記電流検出手段は、オペアンプを用いて前記半導体スイッチに流れる電流に比例した参照電流を発生させ、該参照電流に基づいて、前記半導体スイッチに流れる電流を検出することを特徴とする請求項1に記載の負荷回路の制御装置。

【請求項3】

前記制御手段は、前記各半導体スイッチのうちのいずれか一つがオンとなるように、各半導体スイッチのオン時間帯、及びオフ時間帯を設定することを特徴とする請求項1または請求項2のいずれかに記載の負荷回路の制御装置。

【請求項4】

前記制御手段は、前記各半導体スイッチに対して順次オン時間帯を設定すると共に、今回オンとする半導体スイッチのオン時間帯と、次回オンとする半導体スイッチのオン時間帯が若干重複するように、各半導体スイッチのオン時間帯、及びオフ時間帯を設定することを特徴とする請求項1または請求項2のいずれかに記載の負荷回路の制御装置。

【請求項1】

電源と負荷とを接続する負荷回路に、複数の半導体スイッチを並列に配置し、各半導体スイッチのオン、オフを切り替えることにより、前記負荷の駆動、停止を制御する負荷回路の制御装置において、

前記各半導体スイッチにそれぞれ設けられ、各半導体スイッチに流れる電流を検出する電流検出手段と、

駆動指令信号が入力された際に、前記各半導体スイッチ毎にそれぞれ異なるオン時間帯、及びオフ時間帯となるように各半導体スイッチに制御信号を出力する制御を行い、且つ、前記電流検出手段により検出される電流に基づいて、前記各半導体スイッチを遮断する制御を行う制御手段と、

を有することを特徴とする負荷回路の制御装置。

【請求項2】

前記電流検出手段は、オペアンプを用いて前記半導体スイッチに流れる電流に比例した参照電流を発生させ、該参照電流に基づいて、前記半導体スイッチに流れる電流を検出することを特徴とする請求項1に記載の負荷回路の制御装置。

【請求項3】

前記制御手段は、前記各半導体スイッチのうちのいずれか一つがオンとなるように、各半導体スイッチのオン時間帯、及びオフ時間帯を設定することを特徴とする請求項1または請求項2のいずれかに記載の負荷回路の制御装置。

【請求項4】

前記制御手段は、前記各半導体スイッチに対して順次オン時間帯を設定すると共に、今回オンとする半導体スイッチのオン時間帯と、次回オンとする半導体スイッチのオン時間帯が若干重複するように、各半導体スイッチのオン時間帯、及びオフ時間帯を設定することを特徴とする請求項1または請求項2のいずれかに記載の負荷回路の制御装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−55721(P2013−55721A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−190288(P2011−190288)

【出願日】平成23年9月1日(2011.9.1)

【出願人】(000006895)矢崎総業株式会社 (7,019)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月1日(2011.9.1)

【出願人】(000006895)矢崎総業株式会社 (7,019)

【Fターム(参考)】

[ Back to top ]