負荷駆動制御回路

【課題】 ブートストラップ回路およびチャージポンプ回路を併用した負荷駆動制御回路において、ブートストラップ回路から安定して電圧を出力させることができる負荷駆動制御回路を提供する。

【解決手段】 主電源B1から供給される電圧を制御することによって、負荷を駆動する負荷駆動制御回路であって、チャージポンプ回路40に接続された主電源B1または副電源B2からチャージポンプ回路40の昇圧用コンデンサ46への充電を行わせる一方、デューティ比が所定値よりも小さいときに、昇圧用コンデンサ46からブートストラップ回路30の電圧供給用コンデンサ側32に放電させ、電圧供給用コンデンサ32から制御電圧出力手段10への電圧の供給を補助させるように、チャージポンプ回路40を制御する。

【解決手段】 主電源B1から供給される電圧を制御することによって、負荷を駆動する負荷駆動制御回路であって、チャージポンプ回路40に接続された主電源B1または副電源B2からチャージポンプ回路40の昇圧用コンデンサ46への充電を行わせる一方、デューティ比が所定値よりも小さいときに、昇圧用コンデンサ46からブートストラップ回路30の電圧供給用コンデンサ側32に放電させ、電圧供給用コンデンサ32から制御電圧出力手段10への電圧の供給を補助させるように、チャージポンプ回路40を制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、負荷に供給する電圧を制御することによって負荷を駆動するための負荷駆動制御回路に関するものである。

【背景技術】

【0002】

従来の負荷駆動制御回路として、例えば特許文献1に開示されたものが知られている。この負荷駆動制御回路は、電動パワーステアリング装置に適用されており、直列に接続された2つのFET(Field Effect Trandistor:電界効果トランジスタ)で構成され、モータ電源に接続されたパワー回路と、2つのFETにそれぞれ対応するブースタ回路を備えている。また、この負荷駆動制御回路は、電源にそれぞれ接続されたブートストラップ回路およびチャージポンプ式電源回路を備えている。

【0003】

この負荷駆動制御回路では、ブースタ回路のトランジスタにPWM(Pulse Width Modulation:パルス幅変調)制御信号が供給されることにより、トランジスタがオン/オフされ、オンされたときに、ブートストラップ回路のコンデンサから出力された電圧が、ブースタ回路で増幅されてパワー回路のFETのゲートにゲート電圧として供給される。それにより、FETがオンされ、FETを流れるモータ電源からの電流が電動モータに供給されることによって、電動モータが駆動される。一方、トランジスタがオフされたときには、電源からコンデンサに充電が行われる。

【0004】

また、PWM制御信号のデューティが100%に近く、トランジスタがほぼオンされた状態に維持された場合は、コンデンサが十分に充電されず、FETをオンさせるためのゲート電圧を確保できないので、チャージポンプ式電源回路を駆動し、昇圧した電源電圧をトランジスタに供給することによって、FETをオンさせるために必要なゲート電圧を確保している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−311467号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、この負荷駆動制御回路では、電源から直接、ブートストラップ回路のコンデンサに充電するので、負荷駆動制御回路が作動するたびに電源電圧が低下するおそれがあり、その結果、FETにゲート電圧として供給される電圧の低下を招くおそれがある。その場合、チャージポンプ回路によって電圧の不足が補われるものの、電圧低下の発生からチャージポンプ回路により所要の電圧がパワー回路のFETに実際に供給されるまで、時間差が生じ、チャージポンプを使用した高デューティの出力を高速に出力することができない。また、PWM制御中は、ブートストラップ回路のコンデンサへの充電およびコンデンサからの放電が繰り返されるので、それに伴ってノイズが増大するおそれがある。また、例えばFETを流れる電流値に基づく保護機能が実装されている場合、電源電圧の低下に伴うFETのオン抵抗の増大により電流値が変動すると、これを保護機能が不具合であると誤検出するおそれがある。

【0007】

本発明は、以上のような課題を解決するためになされたものであり、ブートストラップ回路およびチャージポンプ回路を併用した負荷駆動制御回路において、ブートストラップ回路から安定して電圧を出力させることができる負荷駆動制御回路を提供することを目的としている。

【課題を解決するための手段】

【0008】

上記の目的を達成するために、特許請求の範囲に記載の請求項1の負荷駆動制御回路は、主電源から供給される電圧を制御することによって、負荷を駆動する負荷駆動制御回路であって、副電源と、前記負荷を駆動するためのパルス幅変調制御信号を生成する制御信号生成手段と、当該制御信号生成手段により生成されたパルス幅変調制御信号に基づいてオン/オフされることによって、制御電圧信号を出力するための制御電圧出力手段と、一方の電極が前記副電源側および前記制御電圧出力手段側に接続された電圧供給用コンデンサを有し、前記制御電圧出力手段がオン/オフされるのに応じて、前記副電源から前記電圧供給用コンデンサへの充電、および当該電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を行うことにより、当該制御電圧出力手段に制御電圧信号を出力させるブートストラップ回路と、前記主電源に接続され、前記制御電圧出力手段から出力された制御電圧信号に基づいてオン/オフされるのに応じて、前記主電源と前記負荷の間を導通させるスイッチ素子と、一方の電極が前記電圧供給用コンデンサ側に接続された昇圧用コンデンサを有し、前記主電源および前記副電源の少なくとも一方に接続されたチャージポンプ回路と、前記チャージポンプ回路に接続された前記主電源または前記副電源から前記昇圧用コンデンサへの充電を行わせる一方、前記パルス幅変調制御信号のデューティ比が所定値よりも小さいときに、前記昇圧用コンデンサから前記電圧供給用コンデンサ側に放電させ、当該電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を補助させるように、前記チャージポンプ回路を制御するチャージポンプ回路制御手段と、を備えていることを特徴とする。

【0009】

請求項2に係る発明は、請求項1に記載の負荷駆動制御回路において、前記チャージポンプ回路は、少なくとも、前記昇圧用コンデンサとして第1の昇圧用コンデンサを有する第1のチャージポンプ回路と、前記昇圧用コンデンサとして前記第1の昇圧用コンデンサよりも高耐圧の第2の昇圧用コンデンサを有する第2のチャージポンプ回路とで構成され、前記第1のチャージポンプ回路に接続された前記副電源または前記主電源の電圧を検出する電源電圧検出手段をさらに備え、前記チャージポンプ回路制御手段は、前記電源電圧検出手段によって検出された電圧と、前記第1および第2の昇圧用コンデンサの耐圧とに応じて、前記第1および第2のチャージポンプ回路を切り換えて駆動するように、前記チャージポンプ回路を制御することを特徴とする。

【0010】

請求項3に係る発明は、請求項2に記載の負荷駆動制御回路において、前記チャージポンプ回路制御手段は、前記デューティ比が前記所定値よりも小さいときに、第1の昇圧用コンデンサおよび第2の昇圧用コンデンサの少なくとも一方を、前記電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を補助させるように、前記チャージポンプ回路を制御することを特徴とする。

【0011】

請求項4に係る発明は、請求項2または3に記載の負荷駆動制御回路において、前記チャージポンプ回路の少なくとも一部はICチップに搭載され、前記第2の昇圧用コンデンサは、前記ICチップの外部に設けられていることを特徴とする。

【0012】

請求項5に係る発明は、請求項4に記載の負荷駆動制御回路において、前記第1の昇圧用コンデンサは、前記ICチップに搭載されていることを特徴とする。

【0013】

請求項6に係る発明は、請求項1ないし5のいずれか1項に記載の負荷駆動制御回路において、前記昇圧用コンデンサと前記電圧供給用コンデンサの間に設けられた逆流防止用スイッチをさらに備え、当該逆流防止用スイッチ素子は、前記デューティ比が前記所定値よりも小さいときにオンされることを特徴とする。

【発明の効果】

【0014】

請求項1の発明では、制御信号生成手段によって生成されたパルス幅変調制御信号に基づいて、制御電圧出力手段がオン/オフされるのに応じ、ブートストラップ回路の電圧供給用コンデンサに副電源側から充電された電荷が、制御電圧出力手段側に放電される。それにより、制御電圧出力手段に電圧が供給されることによって、パルス幅変調制御信号に応じた制御電圧信号が、制御電圧出力手段から出力される。

【0015】

また、チャージポンプ回路がチャージポンプ回路制御手段で制御されることによって、主電源および副電源の少なくとも一方に接続されたチャージポンプ回路の昇圧用コンデンサが充電される。また、パルス幅変調制御信号のデューティ比が所定値よりも小さいときには、昇圧用コンデンサに充電された電荷が電圧供給用コンデンサ側に放電され、その分、電圧供給用コンデンサから制御電圧出力手段への電圧の供給が補助される。

【0016】

スイッチ素子は、制御電圧出力手段から出力された制御電圧信号に基づいてオン/オフされ、それに応じて、主電源と負荷の間の導通が確保され、主電源から負荷に電圧が供給されることによって、負荷が駆動される。

【0017】

以上のように、電源電圧の低下などにより、ブートストラップ回路の電圧供給用コンデンサから供給される電圧が不足した場合でも、チャージポンプ回路の昇圧用コンデンサによる補助によって、制御電圧出力手段に供給される電圧を安定させることができ、その結果、負荷に供給される電圧を制御するスイッチ素子を安定して駆動することができる。また、あらかじめ充電された昇圧用コンデンサからの放電によって電圧供給用コンデンサの補助を行うので、電圧供給用コンデンサの電圧が低下した場合でも、制御電圧出力手段に供給される電圧を低下させることなく維持することができる。

【0018】

また、デューティ比が所定値よりも低く、電圧供給用コンデンサへの充電と放電が繰り返されるときに、充放電の反復に伴って発生するノイズを、チャージポンプ回路の昇圧用コンデンサによって低減でき、したがって、負荷駆動制御回路の安定した動作を確保することができる。また、その結果、電力の損失も低減されるので、熱の発生を抑制することができる。さらに、チャージポンプ回路の昇圧用コンデンサを、電圧維持やノイズ低減用のコンデンサとして使用するので、新たな搭載部品およびそのための搭載スペースを必要とすることなく、上記の効果を得ることができる。

【0019】

請求項2の発明では、電源電圧と、第1および第2の昇圧用コンデンサの耐圧に応じて、第1および第2のチャージポンプ回路が切り換えて駆動されるので、電源電圧の変化に応じて、耐圧が互いに異なる第1および第2の昇圧用コンデンサを、適切に切り換えて使用することができる。その結果、ノイズ低減などの効果を、電源電圧の変動にかかわらず得ることができる。

【0020】

請求項3の発明では、第1および第2の昇圧用コンデンサの少なくとも一方は、デューティ比が所定値よりも小さいときに、ブートストラップ回路の補助として使用される。PWM制御中は、スイッチ素子などのオン/オフが高速で実行されるので、そのような場合に、チャージポンプ回路のコンデンサをブートストラップ回路の補助として用いることにより、ノイズや損失の低減効果を確実に得ることができる。

【0021】

請求項4の発明では、ICチップの外部に第2の昇圧用コンデンサが設けられているので、第2の昇圧用コンデンサとして、より大容量のコンデンサを、ICチップに搭載するよりも低コストで用いることができ、それにより、ノイズや損失の低減などの効果を、より低コストで得ることができる。

【0022】

請求項5の発明では、第1の昇圧用コンデンサがICチップに搭載されているので、その分、配線のL成分を抑制することができる。

【0023】

請求項6の発明では、デューティ比が所定値よりも小さいとき、すなわち、ノイズの発生しやすいPWM制御の実行中には、逆流防止用のスイッチがオンされ、チャージポンプ側への電流の逆流が阻止される一方、昇圧用コンデンサからの放電を行うことができ、ノイズの損失をより確実に低減させることができる。

【図面の簡単な説明】

【0024】

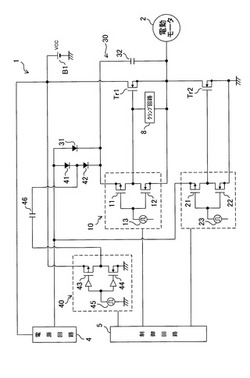

【図1】本発明の第1実施形態に係る負荷駆動制御回路、およびこれによって駆動される電動モータなどを示す回路図である。

【図2】本発明の第1実施形態に係る負荷駆動制御回路の第1の変形例、およびこれによって駆動される電動モータなどを示す回路図である。

【図3】本発明の第1実施形態に係る負荷駆動制御回路の第2の変形例、およびこれによって駆動される電動モータなどを示す回路図である。

【図4】本発明の第2実施形態に係る負荷駆動制御回路、およびこれによって駆動される電動モータなどを示す回路図である。

【図5】第1チャージポンプ回路を示す回路図である。

【図6】第1チャージポンプ回路の動作を説明するためのタイミングチャートである。

【図7】第2実施形態に係る負荷駆動制御回路の第1の変形例、およびこれによって駆動される電動モータなどを示す回路図である。

【図8】第2チャージポンプ回路およびその逆流防止用スイッチの動作を説明するためのタイミングチャートである。

【図9】第1チャージポンプ回路の変形例を示す回路図である。

【図10】第1チャージポンプ回路の変形例の第1の動作例を説明するためのタイミングチャートである。

【図11】第1チャージポンプ回路の変形例の第2の動作例を説明するためのタイミングチャートである。

【図12】第1チャージポンプ回路の変形例の第3の動作例を説明するためのタイミングチャートである。

【図13】第2実施形態に係る負荷駆動制御回路の第2の変形例、およびこれによって駆動される電動モータなどを示す回路図である。

【図14】逆流防止用スイッチの第1の動作例を説明するためのタイミングチャートである。

【図15】逆流防止用スイッチの第2の動作例を説明するためのタイミングチャートである。

【図16】逆流防止用スイッチの第3の動作例を説明するためのタイミングチャートである。

【図17】第1および第2チャージポンプ回路の動作の切換えを説明するためのタイミングチャートである。

【発明を実施するための形態】

【0025】

以下、本発明の第1実施形態に係る負荷駆動制御回路について、図面を参照しながら説明する。図1は、本発明を適用した負荷駆動制御回路1、およびこれによって駆動される電動モータ2(負荷)の回路図を示している。同図に示すように、この負荷駆動制御回路1は、ICチップ(図示せず)に搭載された複数の回路、およびICチップの外部に設けられた複数の回路や素子などで構成されており、電源回路4(電源電圧検出手段)、制御回路5(制御信号生成手段、チャージポンプ回路制御手段)、スイッチ素子Tr1、Tr2、駆動信号出力回路10(制御電圧出力手段)、ブートストラップ回路30およびチャージポンプ回路40を備えている。

【0026】

電源回路4はICチップに搭載されている。この電源回路4には主電源B1の正極が接続されおり、電源回路4は、この主電源B1から入力された電圧VCCに基づいて、制御回路5やチャージポンプ回路40などを作動させるための電圧を生成する。また、電源回路4は、主電源B1の電圧VCCを監視し、その監視結果に応じた制御信号を制御回路5に出力するように構成されている。

【0027】

駆動信号出力回路10は、電動モータ2を駆動するために、スイッチ素子Tr1、Tr2を後述するようにオン/オフするための駆動信号を出力するものであり、ICチップに搭載されている。この駆動信号出力回路10は、直列に接続されたFET11、12を有しており、FET11はPチャンネル型のMOSFETで、FET12はNチャンネル型のMOSFETでそれぞれ構成されている。FET11のドレインとFET12のドレインは互いに接続されており、両者11、12のゲートには信号源13(制御信号生成手段)が接続されている。この信号源13は、制御回路5で制御されることによって、PWM制御信号をFET11、12のゲートに供給する。

【0028】

また、駆動信号出力回路10は、Pチャンネル型のMOSFETで構成されたFET21と、Nチャンネル型のMOSFETで構成されたFET22と、信号源23(制御信号生成手段)をさらに有しており、これらは、上述したFET11、12および信号源13と同様に互いに接続されている。また、FET21のソースには電源回路4が接続され、FET22のソースは接地されている。

【0029】

スイッチ素子Tr1、Tr2は、ICチップの外部に設けられており、Nチャンネル型のMOSFETでいずれも構成されている。このスイッチ素子Tr1のドレインには、主電源B1の正極が接続され、ゲートには、前述した駆動信号出力回路10のFET11およびFET12が接続されている。具体的には、FET11のドレインとFET12のドレインの間の接続点に、接続されている。

【0030】

スイッチ素子Tr1のソースには、スイッチ素子Tr2のドレインが接続されている。これらの間の接続点には、FET12のソースおよび電動モータ2が接続されている。また、スイッチ素子Tr2のゲートには、FET21のドレインとFET22のドレインの間の接続点が接続され、ソースは接地されている。また、スイッチ素子Tr1のゲートとソースの間には、クランプ回路8が設けられている。

【0031】

ブートストラップ回路30は、ICチップに搭載されたダイオード31と、ICチップの外部に設けられた電圧供給用コンデンサ32を有している。コンデンサ32の一方の電極は、前述した駆動信号出力回路10のFET11のソースに接続され、他方の電極は、スイッチ素子Tr1、Tr2間の接続点よりも電動モータ2側に接続されている。また、ダイオード31は、電圧供給用コンデンサ32と電源回路4の間に設けられている。具体的には、ダイオード31のアノードは電源回路4に接続され、カソードは、コンデンサ32の一方の電極とFET11のソースの間の接続点に、接続されている。すなわち、電圧供給用コンデンサ32の一方の電極は、ダイオード31を介して、電源回路4にも接続されている。

【0032】

チャージポンプ回路40は、ICチップに搭載されたダイオード41、42、FET43、44、およびICチップの外部に設けられた大容量かつ高耐圧の昇圧用コンデンサ46(第2の昇圧用コンデンサ)などを有している。FET43およびFET44は、PチャンネルMOSFETおよびNチャネルMOSFETでそれぞれ構成されており、FET43のソースには主電源B1が接続され、FET44のソースは接地されている。また、両者43,44のゲートには、接地された信号源45が接続され、FET43,44のドレイン間の接続点には、昇圧用コンデンサ46の一方の電極が接続されている。

【0033】

ダイオード41,42は、ブートストラップ回路30のダイオード31に並列に設けられている。両者41,42は、互いに直列かつ、それぞれのアノードが電源回路4側に向くように、接続されている。また、昇圧用コンデンサ46の他方の電極は、ダイオード41,42の中間に接続されている。

【0034】

一方、制御回路5は、電動モータ2を駆動するために、信号源13,23および45を制御することによりPWM制御信号をそれぞれ生成し、生成したPWM制御信号を駆動信号出力回路10のFET11,12,21および22と、チャージポンプ回路40のFET43,44のそれぞれのゲートに入力する。

【0035】

次いで、上述した負荷駆動制御回路1の動作を説明する。この負荷駆動制御回路1では、制御回路5による制御によって、信号源13で生成されたPWM制御信号が、駆動信号出力回路10のFET11、12のそれぞれのゲートに入力される。その際、PWM制御信号がローレベル(以下、「Lo」という)のときには、FET11がオンされ、そのソース、ドレイン間の導通が確保される一方、FET12がオフになり、その結果、ブートストラップ回路30の電圧供給用コンデンサ32から放電されることにより供給された電圧が、スイッチ素子Tr1のゲートに制御電圧信号として出力される。

【0036】

その際、制御回路5による制御によって、ハイレベル(以下、「Hi」という)のPWM制御信号が、信号源23で生成され、FET21がオフされることによって、電源回路4からスイッチ素子Tr2への制御電圧信号の供給は行われない。したがって、スイッチ素子Tr2はオフの状態に維持される。

【0037】

一方、信号源13からのPWM制御信号がHiのときには、FET11がオフされることによって、スイッチ素子Tr1への制御電圧信号の供給が停止されるとともに、電源回路4から電圧供給用コンデンサ32に充電が行われる。その際、信号源23からはLoのPWM制御信号が出力されることにより、FET21がオンされる一方、FET22がオフされることによって、電源回路4とスイッチ素子Tr2の間の導通が確保されるので、スイッチ素子Tr2のゲートに電圧が制御電圧信号として供給される。それにより、スイッチ素子Tr2がオンされることにより、FET12のソースが接地される。

【0038】

以上のように、電圧供給用コンデンサ32からの電圧供給およびPWM制御信号に基づくFET11のオン/オフによって、スイッチ素子Tr1のゲートに制御電圧信号が供給され、スイッチ素子Tr1は、この制御電圧信号に基づいてオン/オフされる。それにより、制御電圧信号が供給されたときには、スイッチ素子Tr1がオンされることによって、そのソース、ドレイン間の導通が確保され、主電源B1からの電圧が、電動モータ2に供給される。一方、制御電圧信号が停止されたときには、スイッチ素子Tr1がオフされることによって、電動モータ2への電圧の供給が停止される。

【0039】

チャージポンプ回路40では、制御回路5による制御によって、信号源45で生成されたPWM制御信号が、FET43、44のそれぞれのゲートに入力される。その際、PWM制御信号がHiのときには、電源回路4からコンデンサ46に、ダイオード41を介して充電され、PWM信号がLoに切り換わることによって、主電源B1からコンデンサ46にFET43を介して電圧が供給されることによって、電源回路4から充電された電圧に主電源B1の電圧を加算した電圧が、ダイオード42を介して、前述したブートストラップ回路30の電圧供給用コンデンサ32側に供給される。

【0040】

その結果、電圧供給用コンデンサ32によるFET11への電圧の供給が補助される。すなわち、FET11への放電により電圧供給用コンデンサ32からの放電電圧が低下すると、電源回路4からの電圧供給とともに、昇圧用コンデンサ46から電圧供給用コンデンサ32に放電されることによって、電圧供給用コンデンサ32に電荷が十分、蓄積される。それにより、電圧供給用コンデンサ32からFET11に供給される電圧が維持され、その結果、スイッチ素子Tr1をオンするために入力される制御電圧信号の電圧が維持される。

【0041】

また、前述した駆動信号出力回路10の信号源13で生成されるPWM制御信号のデューティ比(以下、単に「デューティ比」という)が所定値(本実施形態においては「1」)以上のときには、電圧供給用コンデンサ32からFET11への電圧の供給が常時、行われ、電圧供給用コンデンサ32から供給される電圧が、スイッチ素子Tr1をオンさせるために必要な所要の電圧を確保できないおそれがあるので、これを補助するために、チャージポンプ回路40が常時、駆動される。一方、デューティ比が「1」未満のときには、チャージポンプ回路40は、スイッチ素子Tr1への制御電圧信号の電圧低下を招かないように、適宜、駆動される。

【0042】

以上のように、本実施形態の負荷駆動制御回路1によれば、主電源B1の電圧低下や高デューティ比での駆動により、ブートストラップ回路30の電圧供給用コンデンサ32から供給される電圧が不足した場合でも、チャージポンプ回路40の昇圧用コンデンサ46による補助によって、駆動信号出力回路10のFET11に供給される電圧を安定させることができ、その結果、電動モータ2に供給される電圧を制御するスイッチ素子Tr1を、安定して駆動することができる。また、あらかじめ充電された昇圧用コンデンサ46からの放電によって電圧供給用コンデンサ32の補助を行うので、電圧供給用コンデンサ32の電圧が低下した場合でも、FET11に供給される電圧を低下させることなく維持することができる。

【0043】

また、デューティ比が「1」未満で、電圧供給用コンデンサ32の充電と放電が繰り返されるときに、充放電の反復に伴って発生するノイズを、チャージポンプ回路40の昇圧用コンデンサ46からの電圧供給によって低減でき、したがって、負荷駆動制御回路1の安定した動作を確保することができる。また、その結果、スイッチ素子Tr1のオン抵抗の増大を回避でき、熱の発生に伴う電力の損失を低減することもできる。さらに、チャージポンプ回路40の昇圧用コンデンサ46を、電圧維持やノイズ低減用のコンデンサとして使用するので、新たな搭載部品およびそのための搭載スペースを必要とすることなく、上記の効果を得ることができる。

【0044】

また、ICチップの外部に昇圧用コンデンサ46が設けられているので、昇圧用コンデンサをICチップに搭載する場合と比較して、より大容量のコンデンサを昇圧用コンデンサとして、低コストで用いることができ、それにより、ノイズや電力損失の低減などの上述した効果を、低コストで得ることができる。

【0045】

次いで、上述した第1実施形態に係る負荷駆動制御回路の第1の変形例について、図2を参照しながら説明する。図2は、本変形例に係る負荷駆動制御回路1dおよびこれによって駆動される電動モータ2などを示す回路図である。

【0046】

この負荷駆動制御回路1dでは、前述した第1実施形態に係る負荷駆動制御回路1と比較して、電源回路4に代えて副電源B2が設けられており、この副電源B2の正極に、ブートストラップ回路30が接続されている。したがって、ブートストラップ回路30の電圧供給用コンデンサ32には、副電源B2から電圧が直接、供給される。また、クランプ回路8が省略されている。他の構成は、前述した第1実施形態と同様である。

【0047】

次いで、上述した第1実施形態に係る負荷駆動制御回路の第2の変形例について、図3を参照しながら説明する。図3は、本変形例に係る負荷駆動制御回路1eおよびこれによって駆動される電動モータ2などを示す回路図である。

【0048】

この負荷駆動制御回路1eでは、前述した第1実施形態に係る負荷駆動制御回路1と比較して、副電源B2が設けられており、この副電源B2の正極に、電源回路4が接続されている。また、ブートストラップ回路30およびチャージポンプ回路40の一部や電源回路4などは、前述した第1実施形態と同様に、ICチップ3に搭載されている。他の構成は、前述した第1実施形態と同様である。

【0049】

以上の構成の第1および第2変形例の負荷駆動制御回路1d、1eでも、電圧供給用コンデンサ32からFET11への電圧の供給を、チャージポンプ回路40によって補助するので、副電源B2や電源回路4などの電源にかかわらず、FET11への安定した電圧供給を確保することができる。

【0050】

次に、本発明の第2実施形態に係る負荷駆動制御回路について、図4〜図6を参照しながら説明する。図2は、第2実施形態に係る負荷駆動制御回路1aを示す回路図である。図5は、負荷駆動回路1aで用いられる第1チャージポンプ回路CP1を示す回路図である。図6は、第1チャージポンプ回路CP1の動作を説明するためのタイミングチャートである。本実施形態による負荷駆動制御回路1aは、前述した第1実施形態と比較して、2つのチャージポンプ回路を設けた点が、主に異なっている。以下、第1実施形態と共通する構成要素については同じ符号を付し、第1実施形態との差異を中心として説明する。

【0051】

この負荷駆動制御回路1aは、チャージポンプ回路40aとして、第1チャージポンプ回路CP1および第2チャージポンプ回路CP2を備えている。第2チャージポンプ回路CP2は、前述した第1実施形態のチャージポンプ回路40と全く同じ構成を有している。第1チャージポンプ回路CP1は、ICチップ3に搭載されており、基本回路51〜53、チャージポンプ駆動回路54〜56およびダイオード57を有している。

【0052】

基本回路51は、コンデンサ51aおよびダイオード51bを有している。コンデンサ51aの一方の電極は、ダイオード51bを介して主電源B1の正極に接続されており、他方の電極は、チャージポンプ駆動回路54に接続されている。また、ダイオード51bのカソードがコンデンサ51aに、アノードが主電源B1に接続されている。

【0053】

基本回路52は、基本回路51と同様に構成されており、コンデンサ52aおよびダイオード52bを有している。コンデンサ52aの一方の電極は、ダイオード52bを介して基本回路51のコンデンサ51aの一方の電極に接続されており、他方の電極はチャージポンプ駆動回路55に接続されている。また、ダイオード52bは、基本回路41のダイオード51bと同じ方向で配置されている。

【0054】

基本回路53もまた、基本回路52と同様に構成されており、コンデンサ53a(第1の昇圧用コンデンサ)およびダイオード53bを有し、隣接する基本回路52に対し、基本回路52と同様に接続されている。

【0055】

チャージポンプ駆動回路54〜56は、制御回路5から入力されるチャージポンプ駆動信号に基づいて、基本回路51〜53を駆動する回路である。チャージポンプ駆動回路54は、FET54aおよびFET54bを有しており、FET54aはPチャンネルチャンネルMOSFETで、FET54bはNチャンネルMOSFETでそれぞれ構成されている。また、FET54aのドレインと、FET54bのドレインが互いに接続されており、両者の間の接続点に、コンデンサ51aの他方の電極が接続されている。また、FET54aのソースには、電源回路4から電圧VCAが供給され、FET54bのソースは接地されている。また、FET54aおよびFET54bのゲートには、制御回路5が接続されており、両者54a,54bをオン/オフするためのチャージポンプ駆動信号NP1およびNN1が、制御回路5からそれぞれ供給される。

【0056】

チャージポンプ駆動回路55,56は、チャージポンプ駆動回路54と同様に構成されており、チャージポンプ駆動回路55のFET55a,55bには、チャージポンプ駆動信号NP2,NN2がそれぞれ供給され、チャージポンプ駆動回路56のFET56a,56bには、チャージポンプ駆動信号NP3,NN3がそれぞれ供給される。

【0057】

第1チャージポンプ回路CP1の出力は、前述したブートストラップ回路30の電圧供給用コンデンサ32と駆動信号出力回路10のFET11とを接続するラインに、ダイオード57を介して接続されている。このダイオード57のアノードは、基本回路53のコンデンサ53a側に、カソードは電圧供給用コンデンサ32側にそれぞれ接続されている。なお、このチャージポンプ回路CP1は、前述したようにICチップ3に搭載されているので、コンデンサ51a〜53aとして、チャージポンプ回路CP2の昇圧用コンデンサ46よりも低容量かつ低耐圧のものが採用されている。

【0058】

次いで、上述した第1チャージポンプ回路CP1の動作について説明する。図6に示すように、第1チャージポンプ回路CP1の駆動中、チャージポンプ駆動回路54、56の各FETにチャージポンプ駆動信号として、LoのPWM制御信号が入力され、チャージポンプ駆動回路55の各FETにHiのPWM信号が入力されている場合に、時刻t1において、FET54a、56aに対するPWM制御信号がHiに,FET55bに対するPWM制御信号がLoにそれぞれ切り換えられる。それにより、FET54a〜56aおよび54b〜56bがいずれもオフされる。

【0059】

時刻t1から若干の間隔をおいた時刻t2において、FET54b、56bに対するPWM制御信号がHiに切り換えられるとともに、FET55aに対するPWM制御信号がLoに切り換えられる。それにより、FET54b、56bがオンされることにより、コンデンサ51aに電圧VCCが充電されるとともに、コンデンサ52aに電圧VCAが供給され、コンデンサ52aにあらかじめ充電されていた電圧に、電圧VCAを加算した電圧が、ダイオード53bを介し、コンデンサ53aに充電される。

【0060】

次に、時刻t3において、FET54b、56bに対するPWM制御信号がLoに切り換えられるとともに、FET55aに対するPWM制御信号がHiに切り換えられると、FET54a〜56aおよび54b〜56bがいずれもオフされる。

【0061】

そして、時刻t3から若干の間隔をおいた時刻t4において、FET54a、56aに対するPWM制御信号がLoに切り換えられるとともに、FET55bに対するPWM制御信号がHiに切り換えられると、FET54a、55b、56aがオンされる。これにより、コンデンサ51aに電圧VCAが供給され、コンデンサ51aにあらかじめ充電されていた電圧に、電圧VCAを加算した電圧が、ダイオード52bを介し、コンデンサ52aに充電される。また、コンデンサ53aに電圧VCAがさらに供給されることにより、最終的に昇圧された電圧が、チャージポンプ回路CP1から出力される。

【0062】

以上のような動作が周期的に繰り返されるように、制御回路5は、チャージポンプ駆動回路54、56に対して同一周期で同位相のパルス信号を、チャージポンプ駆動回路55に対してほぼ逆位相のパルス信号を、チャージポンプ駆動信号としてそれぞれ出力する。チャージポンプ駆動回路54〜56は、チャージポンプ駆動信号に基づいて、コンデンサ51a〜53aの一方の電極を電源回路4に接続または接地する。これにより、コンデンサ51a〜53aの充放電が繰り返され、主電源B1の電圧VCCを、昇圧してコンデンサ53aから出力する。

【0063】

そして、時刻t5において、第1チャージポンプ回路CP1に入力される電圧VCAが、コンデンサ51a〜53aの耐圧に応じてあらかじめ設定された所定の電圧を上回ったことが検出されると、制御回路5は、第1チャージポンプ回路CP1の駆動を停止し、各チャージポンプ駆動信号をHiに固定する。これにより、コンデンサ51a〜53aが接地される。なお、この所定の電圧は、コンデンサ51a〜53aを保護するために、コンデンサ51a〜53aの耐圧よりも低い値に設定されている。

【0064】

以上のように、本実施形態の負荷駆動制御回路1aによれば、副電源B2の電圧VCと、第1チャージポンプ回路CP1のコンデンサ51a〜53aと、第2チャージポンプ回路CP2の昇圧用コンデンサ46の耐圧に応じて、第1および第2のチャージポンプ回路CP1、CP2が切り換えて駆動される。それにより、副電源B2の電圧VCの変化に応じて、耐圧が互いに異なるコンデンサ51a〜53cと第2の昇圧用コンデンサ46とを、適切に切り換えて使用することができる。その結果、ノイズ低減などの前述した効果を、副電源B2の電圧の変動にかかわらず得ることができる。

【0065】

また、第1チャージポンプ回路CP1のコンデンサ51a〜53aがICチップ3に搭載されているので、ICチップ3の外部に設けた場合と比較して、配線のL成分を抑制することができる。

【0066】

次いで、上述した第2実施形態に係る負荷駆動制御回路の第1の変形例について、図7および図8を参照しながら説明する。図7は、本変形例に係る負荷駆動制御回路1bおよびこれによって駆動される電動モータ2などを示す回路図である。図8は、本変形例における第2チャージポンプ回路CP2の逆流防止用スイッチの動作を説明するためのタイミングチャートである。

【0067】

この負荷駆動制御回路1bでは、第2チャージポンプ回路CP2のダイオード41に代えて、スイッチS1が設けられている。このスイッチS1は、PチャンネルMOSFETで構成されており、そのソースが電源回路4側に、ドレインがダイオード42「側にそれぞれ接続されている。また、そのゲートには制御回路5が接続されており、スイッチS1は、制御回路5から供給される駆動信号に基づいて、オン/オフされる。他の構成は、前述した第2実施形態の負荷駆動制御回路1aと同じである。

【0068】

図8に示すように、この負荷駆動制御回路1bでは、第2チャージポンプ回路CP2が駆動されているときには、スイッチS1への駆動信号の供給が行われず、スイッチS1はオフに維持される。時刻t11において、第2チャージポンプ回路CP2が停止され、第2チャージポンプ回路CP2でのPWM制御信号がHiに維持されると同時に、スイッチS1はオンされる。

【0069】

次いで、第2実施形態に係る負荷駆動制御回路の第2の変形例について、図9〜12を参照しながら説明する。図9は、第1チャージポンプ回路の変形例を示す回路図である。図10は、第1チャージポンプ回路の変形例の第1の動作例を説明するためのタイミングチャートである。図11は第1チャージポンプ回路の変形例の第2の動作例を説明するためのタイミングチャートである。図12は、第1チャージポンプ回路の変形例の第3の動作例を説明するためのタイミングチャートである。

【0070】

図9に示すように、本変形例の第1チャージポンプ回路CP1aでは、前述した第2実施形態の第1チャージポンプ回路CP1のダイオード51b〜53bに代えて、FET51c〜53cが設けられており、これらとコンデンサ51a〜53aによって、基本回路51d〜53dがそれぞれ構成されている。FET51c〜53cは、いずれもPチャンネルMOSFETで構成されており、各FETのドレインが第1チャージポンプ回路CP1aの出力側に、ソースが主電源B1側にそれぞれ接続されている。また、各FETのゲートは、制御回路5に接続されており、制御回路5から供給される駆動信号M1〜M3によって、FET51c〜53cのオン/オフがそれぞれ切り換えられる。

【0071】

次いで、この第1チャージポンプ回路CP1aの第1の動作例を説明する。図10に示すように、チャージポンプ駆動回路54〜56の動作は、前述した第2実施形態の第1チャージポンプ回路CP1と全く同じである。また、時刻t6において、前述したように電圧VCAが所定の電圧を上回り、第1チャージポンプ回路CP1aの駆動が停止がされるまで、FET51c〜53cは、オンに維持される。また、時刻t6において、第1チャージポンプ回路CP1aの駆動が停止されると、駆動信号M1〜M3によって、FET51c〜53cがいずれもオフに切り換えられる。

【0072】

次いで、第1チャージポンプ回路CP1aの第2の動作例を説明する。図11に示すように、チャージポンプ駆動回路54〜56の動作は、前述した第2実施形態と全く同じである。FET52cは、時刻t1において、駆動信号M2によってオフからオンに切り換えられる。それにより、コンデンサ51aからコンデンサ52aへの導通が確保されるとともに、電圧の供給が行われる。また、FET51c、53cは、時刻t2において、駆動信号M1、M3によってオンからオフに切り換えられ、時刻t3において、オンに切り換えられる。また、FET52cは、時刻t4において、オンからオフに切り換えられる。以上のようなFET51c〜53cの動作は、チャージポンプ駆動回路54〜55の動作に同期して行われる。そして、時刻t6において、第1チャージポンプ回路CP1aの駆動が停止されると、FET51c〜53cはいずれも、第1チャージポンプ回路CP1aの駆動が再開されるまで、オフに維持される。

【0073】

次いで、第1チャージポンプ回路CP1aの第3の動作例を説明する。図12に示すように、デューティ比が「1」で第1チャージポンプ回路CP1aが駆動されているときのチャージポンプ駆動回路54〜56およびFET51c〜53cの動作は、前述した第2の動作例と全く同じである。時刻t8において、デューティ比が「1」を下回ると、チャージポンプ駆動回路54〜56の各FETは、そのときのオン/オフの状態を、期間Tが経過するまで維持し、時刻t9において、いずれもオンに切り換えられる。一方、基本回路51d〜53dのFET51c〜53cは、時刻t8においていずれも一旦、オフされ、期間Tが経過した時刻t9において、いずれもオンに切り換えられる。

【0074】

次いで、第2実施形態に係る負荷駆動制御回路の第3の変形例について、図13〜図16を参照しながら説明する。図13は、第2実施形態に係る負荷駆動制御回路の第2の変形例、およびこれによって駆動される電動モータ2などを示す回路図である。図14は、逆流防止用スイッチの第1の動作例を説明するためのタイミングチャートである。図15は、逆流防止用スイッチの第2の動作例を説明するためのタイミングチャートである。図16は、逆流防止用スイッチの第3の動作例を説明するためのタイミングチャートである。

【0075】

本変形例の負荷駆動制御回路1cでは、ブートストラップ回路30のダイオード31に代えてスイッチS2が、第2チャージポンプ回路CP2のダイオード41,42に代えてスイッチS1,S3(逆流防止用スイッチ)が、第1チャージポンプ回路CP1のダイオード57に代えてスイッチS4(逆流防止用スイッチ)が、それぞれ設けられている。これらは、いずれもPチャンネルMOSFETで構成されており、スイッチS1〜S3のソースは電源回路4側に接続され、スイッチS4のソースは、第1チャージポンプ回路CP1のコンデンサ53a側に接続されている。また、スイッチS1〜S4のゲートは制御回路5に接続されており、制御回路5から供給される駆動信号によって、各FETのオン/オフが切り換えられる。

【0076】

次いで、本変形例におけるスイッチS1〜S4の第1の動作例について説明する。図14に示すように、ブートストラップ回路30のスイッチS2および第2チャージポンプ回路CP2のスイッチS1は、常時オフされている。一方、スイッチ素子Tr1に制御電圧信号が供給され、スイッチ素子Tr1がオンされているときには、第2チャージポンプ回路CP2のスイッチS3および第1チャージポンプ回路CP1のスイッチS4は、オフされており、時刻t22でスイッチ素子Tr1がオフされるのに先立つ時刻t21において、オンされる。そして、時刻t23でスイッチ素子Tr1がオンされると、その直後の時刻t24において、スイッチS3、S4は、オフされる。スイッチS1〜S4の以上のような動作は、制御電圧信号によりスイッチ素子Tr1がオン/オフされるのに同期して実行される。

【0077】

次いで、本変形例におけるスイッチS1〜S4の第2の動作例について説明する。図15に示すように、この動作例では、制御電圧信号に従い、スイッチ素子Tr1がオン/オフされるのにかかわらず、スイッチS1は、常時、オンに維持され、スイッチS2〜S3は、オフに維持される。

【0078】

次いで本変形例におけるスイッチS1〜S4の第3の動作例について説明する。図16に示すように、この動作例では、スイッチS1〜S4はいずれも、時刻t22においてスイッチ素子Tr1がオフされる直前の時刻t21において、オンされる。そして、時刻t23においてスイッチ素子Tr1がオフされた直後の時刻t24において、スイッチS1〜S4は、いずれもオフされる。スイッチ委S1〜S4の以上のような動作は、制御電圧信号によりスイッチ素子Tr1がオン/オフされるのに同期して実行される。

【0079】

次いで、第1および第2チャージポンプ回路CP1、CP2の切り換えについての動作例を説明する。図17に示すように、スイッチ素子Tr1に対するデューティ比が比較的、小さく、スイッチ素子Tr1のオン/オフが1回、行われる間にブートストラップ回路30の電圧供給用コンデンサ32から放出される電荷が、第1チャージポンプ回路CP1のコンデンサ53aの容量よりも少ないときには、制御回路5は、第1チャージポンプ回路CP1のみを駆動する。

【0080】

また、デューティ比がより大きく、スイッチ素子Tr1が一回、オン/オフがされる間にブートストラップ回路30の電圧供給用コンデンサ32から放出される電荷が、第1チャージポンプ回路CP1のコンデンサ53aの容量を上回るときには、制御回路5は、第1チャージポンプ回路CP1と同時に第2チャージポンプ回路CP2を駆動する。

【0081】

第1チャージポンプ回路CP1のスイッチS4は、時刻t32において、スイッチ素子Tr1がオンされる直前の時刻t31においてオンされ、時刻t33においてスイッチ素子Tr1がオフされた直後の時刻t34において、オフされる。

【0082】

このような動作が、制御電圧信号に同期して繰り返された後、時刻t35において、デューティ比がより大きな値に変更され、スイッチ素子Tr1の1回のオン時間が時刻t35以前よりも長くなると、制御回路5は、第2チャージポンプ回路CP2の駆動を開始させる。スイッチS4は、デューティ比が切り換わった後も、切り換わる前と同様に、スイッチ素子Tr1のオン/オフに同期してオン/オフされる。

【0083】

なお、上述した動作例では、より大きなデューティ比への切り換え後は、第1および第2チャージポンプ回路CP1,CP2の双方を駆動するように制御しているが、昇圧用コンデンサ53aの容量がより小さな第1チャージポンプ回路CP1を停止し、より大容量の昇圧用コンデンサ46を有する第2チャージポンプ回路CP2のみを駆動するようにしてもよい。

【0084】

なお、本発明は上記実施形態に限定されるものではなく、本発明の趣旨の範囲内で、細部の構成を適宜、変更することが可能である。

【符号の説明】

【0085】

1,1a〜1e 負荷駆動制御回路

2 電動モータ(負荷)

3 ICチップ

4 電源回路(電源電圧検出手段)

5 制御回路(制御信号生成手段、チャージポンプ回路制御手段)

10 駆動信号出力回路(制御電圧出力手段)

13 信号源(制御信号生成手段)

23 信号源(制御信号生成手段)

30 ブートストラップ回路

32 電圧供給用コンデンサ

40 チャージポンプ回路

40a チャージポンプ回路

46 昇圧用コンデンサ(第2の昇圧用コンデンサ)

53a コンデンサ(第1の昇圧用コンデンサ)

B1 主電源

B2 副電源

Tr1 スイッチ素子

Tr2 スイッチ素子

CP1 第1チャージポンプ回路

CP1a 第1チャージポンプ回路

CP2 第2チャージポンプ回路

S3 スイッチ(逆流防止用スイッチ)

S4 スイッチ(逆流防止用スイッチ)

【技術分野】

【0001】

本発明は、負荷に供給する電圧を制御することによって負荷を駆動するための負荷駆動制御回路に関するものである。

【背景技術】

【0002】

従来の負荷駆動制御回路として、例えば特許文献1に開示されたものが知られている。この負荷駆動制御回路は、電動パワーステアリング装置に適用されており、直列に接続された2つのFET(Field Effect Trandistor:電界効果トランジスタ)で構成され、モータ電源に接続されたパワー回路と、2つのFETにそれぞれ対応するブースタ回路を備えている。また、この負荷駆動制御回路は、電源にそれぞれ接続されたブートストラップ回路およびチャージポンプ式電源回路を備えている。

【0003】

この負荷駆動制御回路では、ブースタ回路のトランジスタにPWM(Pulse Width Modulation:パルス幅変調)制御信号が供給されることにより、トランジスタがオン/オフされ、オンされたときに、ブートストラップ回路のコンデンサから出力された電圧が、ブースタ回路で増幅されてパワー回路のFETのゲートにゲート電圧として供給される。それにより、FETがオンされ、FETを流れるモータ電源からの電流が電動モータに供給されることによって、電動モータが駆動される。一方、トランジスタがオフされたときには、電源からコンデンサに充電が行われる。

【0004】

また、PWM制御信号のデューティが100%に近く、トランジスタがほぼオンされた状態に維持された場合は、コンデンサが十分に充電されず、FETをオンさせるためのゲート電圧を確保できないので、チャージポンプ式電源回路を駆動し、昇圧した電源電圧をトランジスタに供給することによって、FETをオンさせるために必要なゲート電圧を確保している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−311467号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、この負荷駆動制御回路では、電源から直接、ブートストラップ回路のコンデンサに充電するので、負荷駆動制御回路が作動するたびに電源電圧が低下するおそれがあり、その結果、FETにゲート電圧として供給される電圧の低下を招くおそれがある。その場合、チャージポンプ回路によって電圧の不足が補われるものの、電圧低下の発生からチャージポンプ回路により所要の電圧がパワー回路のFETに実際に供給されるまで、時間差が生じ、チャージポンプを使用した高デューティの出力を高速に出力することができない。また、PWM制御中は、ブートストラップ回路のコンデンサへの充電およびコンデンサからの放電が繰り返されるので、それに伴ってノイズが増大するおそれがある。また、例えばFETを流れる電流値に基づく保護機能が実装されている場合、電源電圧の低下に伴うFETのオン抵抗の増大により電流値が変動すると、これを保護機能が不具合であると誤検出するおそれがある。

【0007】

本発明は、以上のような課題を解決するためになされたものであり、ブートストラップ回路およびチャージポンプ回路を併用した負荷駆動制御回路において、ブートストラップ回路から安定して電圧を出力させることができる負荷駆動制御回路を提供することを目的としている。

【課題を解決するための手段】

【0008】

上記の目的を達成するために、特許請求の範囲に記載の請求項1の負荷駆動制御回路は、主電源から供給される電圧を制御することによって、負荷を駆動する負荷駆動制御回路であって、副電源と、前記負荷を駆動するためのパルス幅変調制御信号を生成する制御信号生成手段と、当該制御信号生成手段により生成されたパルス幅変調制御信号に基づいてオン/オフされることによって、制御電圧信号を出力するための制御電圧出力手段と、一方の電極が前記副電源側および前記制御電圧出力手段側に接続された電圧供給用コンデンサを有し、前記制御電圧出力手段がオン/オフされるのに応じて、前記副電源から前記電圧供給用コンデンサへの充電、および当該電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を行うことにより、当該制御電圧出力手段に制御電圧信号を出力させるブートストラップ回路と、前記主電源に接続され、前記制御電圧出力手段から出力された制御電圧信号に基づいてオン/オフされるのに応じて、前記主電源と前記負荷の間を導通させるスイッチ素子と、一方の電極が前記電圧供給用コンデンサ側に接続された昇圧用コンデンサを有し、前記主電源および前記副電源の少なくとも一方に接続されたチャージポンプ回路と、前記チャージポンプ回路に接続された前記主電源または前記副電源から前記昇圧用コンデンサへの充電を行わせる一方、前記パルス幅変調制御信号のデューティ比が所定値よりも小さいときに、前記昇圧用コンデンサから前記電圧供給用コンデンサ側に放電させ、当該電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を補助させるように、前記チャージポンプ回路を制御するチャージポンプ回路制御手段と、を備えていることを特徴とする。

【0009】

請求項2に係る発明は、請求項1に記載の負荷駆動制御回路において、前記チャージポンプ回路は、少なくとも、前記昇圧用コンデンサとして第1の昇圧用コンデンサを有する第1のチャージポンプ回路と、前記昇圧用コンデンサとして前記第1の昇圧用コンデンサよりも高耐圧の第2の昇圧用コンデンサを有する第2のチャージポンプ回路とで構成され、前記第1のチャージポンプ回路に接続された前記副電源または前記主電源の電圧を検出する電源電圧検出手段をさらに備え、前記チャージポンプ回路制御手段は、前記電源電圧検出手段によって検出された電圧と、前記第1および第2の昇圧用コンデンサの耐圧とに応じて、前記第1および第2のチャージポンプ回路を切り換えて駆動するように、前記チャージポンプ回路を制御することを特徴とする。

【0010】

請求項3に係る発明は、請求項2に記載の負荷駆動制御回路において、前記チャージポンプ回路制御手段は、前記デューティ比が前記所定値よりも小さいときに、第1の昇圧用コンデンサおよび第2の昇圧用コンデンサの少なくとも一方を、前記電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を補助させるように、前記チャージポンプ回路を制御することを特徴とする。

【0011】

請求項4に係る発明は、請求項2または3に記載の負荷駆動制御回路において、前記チャージポンプ回路の少なくとも一部はICチップに搭載され、前記第2の昇圧用コンデンサは、前記ICチップの外部に設けられていることを特徴とする。

【0012】

請求項5に係る発明は、請求項4に記載の負荷駆動制御回路において、前記第1の昇圧用コンデンサは、前記ICチップに搭載されていることを特徴とする。

【0013】

請求項6に係る発明は、請求項1ないし5のいずれか1項に記載の負荷駆動制御回路において、前記昇圧用コンデンサと前記電圧供給用コンデンサの間に設けられた逆流防止用スイッチをさらに備え、当該逆流防止用スイッチ素子は、前記デューティ比が前記所定値よりも小さいときにオンされることを特徴とする。

【発明の効果】

【0014】

請求項1の発明では、制御信号生成手段によって生成されたパルス幅変調制御信号に基づいて、制御電圧出力手段がオン/オフされるのに応じ、ブートストラップ回路の電圧供給用コンデンサに副電源側から充電された電荷が、制御電圧出力手段側に放電される。それにより、制御電圧出力手段に電圧が供給されることによって、パルス幅変調制御信号に応じた制御電圧信号が、制御電圧出力手段から出力される。

【0015】

また、チャージポンプ回路がチャージポンプ回路制御手段で制御されることによって、主電源および副電源の少なくとも一方に接続されたチャージポンプ回路の昇圧用コンデンサが充電される。また、パルス幅変調制御信号のデューティ比が所定値よりも小さいときには、昇圧用コンデンサに充電された電荷が電圧供給用コンデンサ側に放電され、その分、電圧供給用コンデンサから制御電圧出力手段への電圧の供給が補助される。

【0016】

スイッチ素子は、制御電圧出力手段から出力された制御電圧信号に基づいてオン/オフされ、それに応じて、主電源と負荷の間の導通が確保され、主電源から負荷に電圧が供給されることによって、負荷が駆動される。

【0017】

以上のように、電源電圧の低下などにより、ブートストラップ回路の電圧供給用コンデンサから供給される電圧が不足した場合でも、チャージポンプ回路の昇圧用コンデンサによる補助によって、制御電圧出力手段に供給される電圧を安定させることができ、その結果、負荷に供給される電圧を制御するスイッチ素子を安定して駆動することができる。また、あらかじめ充電された昇圧用コンデンサからの放電によって電圧供給用コンデンサの補助を行うので、電圧供給用コンデンサの電圧が低下した場合でも、制御電圧出力手段に供給される電圧を低下させることなく維持することができる。

【0018】

また、デューティ比が所定値よりも低く、電圧供給用コンデンサへの充電と放電が繰り返されるときに、充放電の反復に伴って発生するノイズを、チャージポンプ回路の昇圧用コンデンサによって低減でき、したがって、負荷駆動制御回路の安定した動作を確保することができる。また、その結果、電力の損失も低減されるので、熱の発生を抑制することができる。さらに、チャージポンプ回路の昇圧用コンデンサを、電圧維持やノイズ低減用のコンデンサとして使用するので、新たな搭載部品およびそのための搭載スペースを必要とすることなく、上記の効果を得ることができる。

【0019】

請求項2の発明では、電源電圧と、第1および第2の昇圧用コンデンサの耐圧に応じて、第1および第2のチャージポンプ回路が切り換えて駆動されるので、電源電圧の変化に応じて、耐圧が互いに異なる第1および第2の昇圧用コンデンサを、適切に切り換えて使用することができる。その結果、ノイズ低減などの効果を、電源電圧の変動にかかわらず得ることができる。

【0020】

請求項3の発明では、第1および第2の昇圧用コンデンサの少なくとも一方は、デューティ比が所定値よりも小さいときに、ブートストラップ回路の補助として使用される。PWM制御中は、スイッチ素子などのオン/オフが高速で実行されるので、そのような場合に、チャージポンプ回路のコンデンサをブートストラップ回路の補助として用いることにより、ノイズや損失の低減効果を確実に得ることができる。

【0021】

請求項4の発明では、ICチップの外部に第2の昇圧用コンデンサが設けられているので、第2の昇圧用コンデンサとして、より大容量のコンデンサを、ICチップに搭載するよりも低コストで用いることができ、それにより、ノイズや損失の低減などの効果を、より低コストで得ることができる。

【0022】

請求項5の発明では、第1の昇圧用コンデンサがICチップに搭載されているので、その分、配線のL成分を抑制することができる。

【0023】

請求項6の発明では、デューティ比が所定値よりも小さいとき、すなわち、ノイズの発生しやすいPWM制御の実行中には、逆流防止用のスイッチがオンされ、チャージポンプ側への電流の逆流が阻止される一方、昇圧用コンデンサからの放電を行うことができ、ノイズの損失をより確実に低減させることができる。

【図面の簡単な説明】

【0024】

【図1】本発明の第1実施形態に係る負荷駆動制御回路、およびこれによって駆動される電動モータなどを示す回路図である。

【図2】本発明の第1実施形態に係る負荷駆動制御回路の第1の変形例、およびこれによって駆動される電動モータなどを示す回路図である。

【図3】本発明の第1実施形態に係る負荷駆動制御回路の第2の変形例、およびこれによって駆動される電動モータなどを示す回路図である。

【図4】本発明の第2実施形態に係る負荷駆動制御回路、およびこれによって駆動される電動モータなどを示す回路図である。

【図5】第1チャージポンプ回路を示す回路図である。

【図6】第1チャージポンプ回路の動作を説明するためのタイミングチャートである。

【図7】第2実施形態に係る負荷駆動制御回路の第1の変形例、およびこれによって駆動される電動モータなどを示す回路図である。

【図8】第2チャージポンプ回路およびその逆流防止用スイッチの動作を説明するためのタイミングチャートである。

【図9】第1チャージポンプ回路の変形例を示す回路図である。

【図10】第1チャージポンプ回路の変形例の第1の動作例を説明するためのタイミングチャートである。

【図11】第1チャージポンプ回路の変形例の第2の動作例を説明するためのタイミングチャートである。

【図12】第1チャージポンプ回路の変形例の第3の動作例を説明するためのタイミングチャートである。

【図13】第2実施形態に係る負荷駆動制御回路の第2の変形例、およびこれによって駆動される電動モータなどを示す回路図である。

【図14】逆流防止用スイッチの第1の動作例を説明するためのタイミングチャートである。

【図15】逆流防止用スイッチの第2の動作例を説明するためのタイミングチャートである。

【図16】逆流防止用スイッチの第3の動作例を説明するためのタイミングチャートである。

【図17】第1および第2チャージポンプ回路の動作の切換えを説明するためのタイミングチャートである。

【発明を実施するための形態】

【0025】

以下、本発明の第1実施形態に係る負荷駆動制御回路について、図面を参照しながら説明する。図1は、本発明を適用した負荷駆動制御回路1、およびこれによって駆動される電動モータ2(負荷)の回路図を示している。同図に示すように、この負荷駆動制御回路1は、ICチップ(図示せず)に搭載された複数の回路、およびICチップの外部に設けられた複数の回路や素子などで構成されており、電源回路4(電源電圧検出手段)、制御回路5(制御信号生成手段、チャージポンプ回路制御手段)、スイッチ素子Tr1、Tr2、駆動信号出力回路10(制御電圧出力手段)、ブートストラップ回路30およびチャージポンプ回路40を備えている。

【0026】

電源回路4はICチップに搭載されている。この電源回路4には主電源B1の正極が接続されおり、電源回路4は、この主電源B1から入力された電圧VCCに基づいて、制御回路5やチャージポンプ回路40などを作動させるための電圧を生成する。また、電源回路4は、主電源B1の電圧VCCを監視し、その監視結果に応じた制御信号を制御回路5に出力するように構成されている。

【0027】

駆動信号出力回路10は、電動モータ2を駆動するために、スイッチ素子Tr1、Tr2を後述するようにオン/オフするための駆動信号を出力するものであり、ICチップに搭載されている。この駆動信号出力回路10は、直列に接続されたFET11、12を有しており、FET11はPチャンネル型のMOSFETで、FET12はNチャンネル型のMOSFETでそれぞれ構成されている。FET11のドレインとFET12のドレインは互いに接続されており、両者11、12のゲートには信号源13(制御信号生成手段)が接続されている。この信号源13は、制御回路5で制御されることによって、PWM制御信号をFET11、12のゲートに供給する。

【0028】

また、駆動信号出力回路10は、Pチャンネル型のMOSFETで構成されたFET21と、Nチャンネル型のMOSFETで構成されたFET22と、信号源23(制御信号生成手段)をさらに有しており、これらは、上述したFET11、12および信号源13と同様に互いに接続されている。また、FET21のソースには電源回路4が接続され、FET22のソースは接地されている。

【0029】

スイッチ素子Tr1、Tr2は、ICチップの外部に設けられており、Nチャンネル型のMOSFETでいずれも構成されている。このスイッチ素子Tr1のドレインには、主電源B1の正極が接続され、ゲートには、前述した駆動信号出力回路10のFET11およびFET12が接続されている。具体的には、FET11のドレインとFET12のドレインの間の接続点に、接続されている。

【0030】

スイッチ素子Tr1のソースには、スイッチ素子Tr2のドレインが接続されている。これらの間の接続点には、FET12のソースおよび電動モータ2が接続されている。また、スイッチ素子Tr2のゲートには、FET21のドレインとFET22のドレインの間の接続点が接続され、ソースは接地されている。また、スイッチ素子Tr1のゲートとソースの間には、クランプ回路8が設けられている。

【0031】

ブートストラップ回路30は、ICチップに搭載されたダイオード31と、ICチップの外部に設けられた電圧供給用コンデンサ32を有している。コンデンサ32の一方の電極は、前述した駆動信号出力回路10のFET11のソースに接続され、他方の電極は、スイッチ素子Tr1、Tr2間の接続点よりも電動モータ2側に接続されている。また、ダイオード31は、電圧供給用コンデンサ32と電源回路4の間に設けられている。具体的には、ダイオード31のアノードは電源回路4に接続され、カソードは、コンデンサ32の一方の電極とFET11のソースの間の接続点に、接続されている。すなわち、電圧供給用コンデンサ32の一方の電極は、ダイオード31を介して、電源回路4にも接続されている。

【0032】

チャージポンプ回路40は、ICチップに搭載されたダイオード41、42、FET43、44、およびICチップの外部に設けられた大容量かつ高耐圧の昇圧用コンデンサ46(第2の昇圧用コンデンサ)などを有している。FET43およびFET44は、PチャンネルMOSFETおよびNチャネルMOSFETでそれぞれ構成されており、FET43のソースには主電源B1が接続され、FET44のソースは接地されている。また、両者43,44のゲートには、接地された信号源45が接続され、FET43,44のドレイン間の接続点には、昇圧用コンデンサ46の一方の電極が接続されている。

【0033】

ダイオード41,42は、ブートストラップ回路30のダイオード31に並列に設けられている。両者41,42は、互いに直列かつ、それぞれのアノードが電源回路4側に向くように、接続されている。また、昇圧用コンデンサ46の他方の電極は、ダイオード41,42の中間に接続されている。

【0034】

一方、制御回路5は、電動モータ2を駆動するために、信号源13,23および45を制御することによりPWM制御信号をそれぞれ生成し、生成したPWM制御信号を駆動信号出力回路10のFET11,12,21および22と、チャージポンプ回路40のFET43,44のそれぞれのゲートに入力する。

【0035】

次いで、上述した負荷駆動制御回路1の動作を説明する。この負荷駆動制御回路1では、制御回路5による制御によって、信号源13で生成されたPWM制御信号が、駆動信号出力回路10のFET11、12のそれぞれのゲートに入力される。その際、PWM制御信号がローレベル(以下、「Lo」という)のときには、FET11がオンされ、そのソース、ドレイン間の導通が確保される一方、FET12がオフになり、その結果、ブートストラップ回路30の電圧供給用コンデンサ32から放電されることにより供給された電圧が、スイッチ素子Tr1のゲートに制御電圧信号として出力される。

【0036】

その際、制御回路5による制御によって、ハイレベル(以下、「Hi」という)のPWM制御信号が、信号源23で生成され、FET21がオフされることによって、電源回路4からスイッチ素子Tr2への制御電圧信号の供給は行われない。したがって、スイッチ素子Tr2はオフの状態に維持される。

【0037】

一方、信号源13からのPWM制御信号がHiのときには、FET11がオフされることによって、スイッチ素子Tr1への制御電圧信号の供給が停止されるとともに、電源回路4から電圧供給用コンデンサ32に充電が行われる。その際、信号源23からはLoのPWM制御信号が出力されることにより、FET21がオンされる一方、FET22がオフされることによって、電源回路4とスイッチ素子Tr2の間の導通が確保されるので、スイッチ素子Tr2のゲートに電圧が制御電圧信号として供給される。それにより、スイッチ素子Tr2がオンされることにより、FET12のソースが接地される。

【0038】

以上のように、電圧供給用コンデンサ32からの電圧供給およびPWM制御信号に基づくFET11のオン/オフによって、スイッチ素子Tr1のゲートに制御電圧信号が供給され、スイッチ素子Tr1は、この制御電圧信号に基づいてオン/オフされる。それにより、制御電圧信号が供給されたときには、スイッチ素子Tr1がオンされることによって、そのソース、ドレイン間の導通が確保され、主電源B1からの電圧が、電動モータ2に供給される。一方、制御電圧信号が停止されたときには、スイッチ素子Tr1がオフされることによって、電動モータ2への電圧の供給が停止される。

【0039】

チャージポンプ回路40では、制御回路5による制御によって、信号源45で生成されたPWM制御信号が、FET43、44のそれぞれのゲートに入力される。その際、PWM制御信号がHiのときには、電源回路4からコンデンサ46に、ダイオード41を介して充電され、PWM信号がLoに切り換わることによって、主電源B1からコンデンサ46にFET43を介して電圧が供給されることによって、電源回路4から充電された電圧に主電源B1の電圧を加算した電圧が、ダイオード42を介して、前述したブートストラップ回路30の電圧供給用コンデンサ32側に供給される。

【0040】

その結果、電圧供給用コンデンサ32によるFET11への電圧の供給が補助される。すなわち、FET11への放電により電圧供給用コンデンサ32からの放電電圧が低下すると、電源回路4からの電圧供給とともに、昇圧用コンデンサ46から電圧供給用コンデンサ32に放電されることによって、電圧供給用コンデンサ32に電荷が十分、蓄積される。それにより、電圧供給用コンデンサ32からFET11に供給される電圧が維持され、その結果、スイッチ素子Tr1をオンするために入力される制御電圧信号の電圧が維持される。

【0041】

また、前述した駆動信号出力回路10の信号源13で生成されるPWM制御信号のデューティ比(以下、単に「デューティ比」という)が所定値(本実施形態においては「1」)以上のときには、電圧供給用コンデンサ32からFET11への電圧の供給が常時、行われ、電圧供給用コンデンサ32から供給される電圧が、スイッチ素子Tr1をオンさせるために必要な所要の電圧を確保できないおそれがあるので、これを補助するために、チャージポンプ回路40が常時、駆動される。一方、デューティ比が「1」未満のときには、チャージポンプ回路40は、スイッチ素子Tr1への制御電圧信号の電圧低下を招かないように、適宜、駆動される。

【0042】

以上のように、本実施形態の負荷駆動制御回路1によれば、主電源B1の電圧低下や高デューティ比での駆動により、ブートストラップ回路30の電圧供給用コンデンサ32から供給される電圧が不足した場合でも、チャージポンプ回路40の昇圧用コンデンサ46による補助によって、駆動信号出力回路10のFET11に供給される電圧を安定させることができ、その結果、電動モータ2に供給される電圧を制御するスイッチ素子Tr1を、安定して駆動することができる。また、あらかじめ充電された昇圧用コンデンサ46からの放電によって電圧供給用コンデンサ32の補助を行うので、電圧供給用コンデンサ32の電圧が低下した場合でも、FET11に供給される電圧を低下させることなく維持することができる。

【0043】

また、デューティ比が「1」未満で、電圧供給用コンデンサ32の充電と放電が繰り返されるときに、充放電の反復に伴って発生するノイズを、チャージポンプ回路40の昇圧用コンデンサ46からの電圧供給によって低減でき、したがって、負荷駆動制御回路1の安定した動作を確保することができる。また、その結果、スイッチ素子Tr1のオン抵抗の増大を回避でき、熱の発生に伴う電力の損失を低減することもできる。さらに、チャージポンプ回路40の昇圧用コンデンサ46を、電圧維持やノイズ低減用のコンデンサとして使用するので、新たな搭載部品およびそのための搭載スペースを必要とすることなく、上記の効果を得ることができる。

【0044】

また、ICチップの外部に昇圧用コンデンサ46が設けられているので、昇圧用コンデンサをICチップに搭載する場合と比較して、より大容量のコンデンサを昇圧用コンデンサとして、低コストで用いることができ、それにより、ノイズや電力損失の低減などの上述した効果を、低コストで得ることができる。

【0045】

次いで、上述した第1実施形態に係る負荷駆動制御回路の第1の変形例について、図2を参照しながら説明する。図2は、本変形例に係る負荷駆動制御回路1dおよびこれによって駆動される電動モータ2などを示す回路図である。

【0046】

この負荷駆動制御回路1dでは、前述した第1実施形態に係る負荷駆動制御回路1と比較して、電源回路4に代えて副電源B2が設けられており、この副電源B2の正極に、ブートストラップ回路30が接続されている。したがって、ブートストラップ回路30の電圧供給用コンデンサ32には、副電源B2から電圧が直接、供給される。また、クランプ回路8が省略されている。他の構成は、前述した第1実施形態と同様である。

【0047】

次いで、上述した第1実施形態に係る負荷駆動制御回路の第2の変形例について、図3を参照しながら説明する。図3は、本変形例に係る負荷駆動制御回路1eおよびこれによって駆動される電動モータ2などを示す回路図である。

【0048】

この負荷駆動制御回路1eでは、前述した第1実施形態に係る負荷駆動制御回路1と比較して、副電源B2が設けられており、この副電源B2の正極に、電源回路4が接続されている。また、ブートストラップ回路30およびチャージポンプ回路40の一部や電源回路4などは、前述した第1実施形態と同様に、ICチップ3に搭載されている。他の構成は、前述した第1実施形態と同様である。

【0049】

以上の構成の第1および第2変形例の負荷駆動制御回路1d、1eでも、電圧供給用コンデンサ32からFET11への電圧の供給を、チャージポンプ回路40によって補助するので、副電源B2や電源回路4などの電源にかかわらず、FET11への安定した電圧供給を確保することができる。

【0050】

次に、本発明の第2実施形態に係る負荷駆動制御回路について、図4〜図6を参照しながら説明する。図2は、第2実施形態に係る負荷駆動制御回路1aを示す回路図である。図5は、負荷駆動回路1aで用いられる第1チャージポンプ回路CP1を示す回路図である。図6は、第1チャージポンプ回路CP1の動作を説明するためのタイミングチャートである。本実施形態による負荷駆動制御回路1aは、前述した第1実施形態と比較して、2つのチャージポンプ回路を設けた点が、主に異なっている。以下、第1実施形態と共通する構成要素については同じ符号を付し、第1実施形態との差異を中心として説明する。

【0051】

この負荷駆動制御回路1aは、チャージポンプ回路40aとして、第1チャージポンプ回路CP1および第2チャージポンプ回路CP2を備えている。第2チャージポンプ回路CP2は、前述した第1実施形態のチャージポンプ回路40と全く同じ構成を有している。第1チャージポンプ回路CP1は、ICチップ3に搭載されており、基本回路51〜53、チャージポンプ駆動回路54〜56およびダイオード57を有している。

【0052】

基本回路51は、コンデンサ51aおよびダイオード51bを有している。コンデンサ51aの一方の電極は、ダイオード51bを介して主電源B1の正極に接続されており、他方の電極は、チャージポンプ駆動回路54に接続されている。また、ダイオード51bのカソードがコンデンサ51aに、アノードが主電源B1に接続されている。

【0053】

基本回路52は、基本回路51と同様に構成されており、コンデンサ52aおよびダイオード52bを有している。コンデンサ52aの一方の電極は、ダイオード52bを介して基本回路51のコンデンサ51aの一方の電極に接続されており、他方の電極はチャージポンプ駆動回路55に接続されている。また、ダイオード52bは、基本回路41のダイオード51bと同じ方向で配置されている。

【0054】

基本回路53もまた、基本回路52と同様に構成されており、コンデンサ53a(第1の昇圧用コンデンサ)およびダイオード53bを有し、隣接する基本回路52に対し、基本回路52と同様に接続されている。

【0055】

チャージポンプ駆動回路54〜56は、制御回路5から入力されるチャージポンプ駆動信号に基づいて、基本回路51〜53を駆動する回路である。チャージポンプ駆動回路54は、FET54aおよびFET54bを有しており、FET54aはPチャンネルチャンネルMOSFETで、FET54bはNチャンネルMOSFETでそれぞれ構成されている。また、FET54aのドレインと、FET54bのドレインが互いに接続されており、両者の間の接続点に、コンデンサ51aの他方の電極が接続されている。また、FET54aのソースには、電源回路4から電圧VCAが供給され、FET54bのソースは接地されている。また、FET54aおよびFET54bのゲートには、制御回路5が接続されており、両者54a,54bをオン/オフするためのチャージポンプ駆動信号NP1およびNN1が、制御回路5からそれぞれ供給される。

【0056】

チャージポンプ駆動回路55,56は、チャージポンプ駆動回路54と同様に構成されており、チャージポンプ駆動回路55のFET55a,55bには、チャージポンプ駆動信号NP2,NN2がそれぞれ供給され、チャージポンプ駆動回路56のFET56a,56bには、チャージポンプ駆動信号NP3,NN3がそれぞれ供給される。

【0057】

第1チャージポンプ回路CP1の出力は、前述したブートストラップ回路30の電圧供給用コンデンサ32と駆動信号出力回路10のFET11とを接続するラインに、ダイオード57を介して接続されている。このダイオード57のアノードは、基本回路53のコンデンサ53a側に、カソードは電圧供給用コンデンサ32側にそれぞれ接続されている。なお、このチャージポンプ回路CP1は、前述したようにICチップ3に搭載されているので、コンデンサ51a〜53aとして、チャージポンプ回路CP2の昇圧用コンデンサ46よりも低容量かつ低耐圧のものが採用されている。

【0058】

次いで、上述した第1チャージポンプ回路CP1の動作について説明する。図6に示すように、第1チャージポンプ回路CP1の駆動中、チャージポンプ駆動回路54、56の各FETにチャージポンプ駆動信号として、LoのPWM制御信号が入力され、チャージポンプ駆動回路55の各FETにHiのPWM信号が入力されている場合に、時刻t1において、FET54a、56aに対するPWM制御信号がHiに,FET55bに対するPWM制御信号がLoにそれぞれ切り換えられる。それにより、FET54a〜56aおよび54b〜56bがいずれもオフされる。

【0059】

時刻t1から若干の間隔をおいた時刻t2において、FET54b、56bに対するPWM制御信号がHiに切り換えられるとともに、FET55aに対するPWM制御信号がLoに切り換えられる。それにより、FET54b、56bがオンされることにより、コンデンサ51aに電圧VCCが充電されるとともに、コンデンサ52aに電圧VCAが供給され、コンデンサ52aにあらかじめ充電されていた電圧に、電圧VCAを加算した電圧が、ダイオード53bを介し、コンデンサ53aに充電される。

【0060】

次に、時刻t3において、FET54b、56bに対するPWM制御信号がLoに切り換えられるとともに、FET55aに対するPWM制御信号がHiに切り換えられると、FET54a〜56aおよび54b〜56bがいずれもオフされる。

【0061】

そして、時刻t3から若干の間隔をおいた時刻t4において、FET54a、56aに対するPWM制御信号がLoに切り換えられるとともに、FET55bに対するPWM制御信号がHiに切り換えられると、FET54a、55b、56aがオンされる。これにより、コンデンサ51aに電圧VCAが供給され、コンデンサ51aにあらかじめ充電されていた電圧に、電圧VCAを加算した電圧が、ダイオード52bを介し、コンデンサ52aに充電される。また、コンデンサ53aに電圧VCAがさらに供給されることにより、最終的に昇圧された電圧が、チャージポンプ回路CP1から出力される。

【0062】

以上のような動作が周期的に繰り返されるように、制御回路5は、チャージポンプ駆動回路54、56に対して同一周期で同位相のパルス信号を、チャージポンプ駆動回路55に対してほぼ逆位相のパルス信号を、チャージポンプ駆動信号としてそれぞれ出力する。チャージポンプ駆動回路54〜56は、チャージポンプ駆動信号に基づいて、コンデンサ51a〜53aの一方の電極を電源回路4に接続または接地する。これにより、コンデンサ51a〜53aの充放電が繰り返され、主電源B1の電圧VCCを、昇圧してコンデンサ53aから出力する。

【0063】

そして、時刻t5において、第1チャージポンプ回路CP1に入力される電圧VCAが、コンデンサ51a〜53aの耐圧に応じてあらかじめ設定された所定の電圧を上回ったことが検出されると、制御回路5は、第1チャージポンプ回路CP1の駆動を停止し、各チャージポンプ駆動信号をHiに固定する。これにより、コンデンサ51a〜53aが接地される。なお、この所定の電圧は、コンデンサ51a〜53aを保護するために、コンデンサ51a〜53aの耐圧よりも低い値に設定されている。

【0064】

以上のように、本実施形態の負荷駆動制御回路1aによれば、副電源B2の電圧VCと、第1チャージポンプ回路CP1のコンデンサ51a〜53aと、第2チャージポンプ回路CP2の昇圧用コンデンサ46の耐圧に応じて、第1および第2のチャージポンプ回路CP1、CP2が切り換えて駆動される。それにより、副電源B2の電圧VCの変化に応じて、耐圧が互いに異なるコンデンサ51a〜53cと第2の昇圧用コンデンサ46とを、適切に切り換えて使用することができる。その結果、ノイズ低減などの前述した効果を、副電源B2の電圧の変動にかかわらず得ることができる。

【0065】

また、第1チャージポンプ回路CP1のコンデンサ51a〜53aがICチップ3に搭載されているので、ICチップ3の外部に設けた場合と比較して、配線のL成分を抑制することができる。

【0066】

次いで、上述した第2実施形態に係る負荷駆動制御回路の第1の変形例について、図7および図8を参照しながら説明する。図7は、本変形例に係る負荷駆動制御回路1bおよびこれによって駆動される電動モータ2などを示す回路図である。図8は、本変形例における第2チャージポンプ回路CP2の逆流防止用スイッチの動作を説明するためのタイミングチャートである。

【0067】

この負荷駆動制御回路1bでは、第2チャージポンプ回路CP2のダイオード41に代えて、スイッチS1が設けられている。このスイッチS1は、PチャンネルMOSFETで構成されており、そのソースが電源回路4側に、ドレインがダイオード42「側にそれぞれ接続されている。また、そのゲートには制御回路5が接続されており、スイッチS1は、制御回路5から供給される駆動信号に基づいて、オン/オフされる。他の構成は、前述した第2実施形態の負荷駆動制御回路1aと同じである。

【0068】

図8に示すように、この負荷駆動制御回路1bでは、第2チャージポンプ回路CP2が駆動されているときには、スイッチS1への駆動信号の供給が行われず、スイッチS1はオフに維持される。時刻t11において、第2チャージポンプ回路CP2が停止され、第2チャージポンプ回路CP2でのPWM制御信号がHiに維持されると同時に、スイッチS1はオンされる。

【0069】

次いで、第2実施形態に係る負荷駆動制御回路の第2の変形例について、図9〜12を参照しながら説明する。図9は、第1チャージポンプ回路の変形例を示す回路図である。図10は、第1チャージポンプ回路の変形例の第1の動作例を説明するためのタイミングチャートである。図11は第1チャージポンプ回路の変形例の第2の動作例を説明するためのタイミングチャートである。図12は、第1チャージポンプ回路の変形例の第3の動作例を説明するためのタイミングチャートである。

【0070】

図9に示すように、本変形例の第1チャージポンプ回路CP1aでは、前述した第2実施形態の第1チャージポンプ回路CP1のダイオード51b〜53bに代えて、FET51c〜53cが設けられており、これらとコンデンサ51a〜53aによって、基本回路51d〜53dがそれぞれ構成されている。FET51c〜53cは、いずれもPチャンネルMOSFETで構成されており、各FETのドレインが第1チャージポンプ回路CP1aの出力側に、ソースが主電源B1側にそれぞれ接続されている。また、各FETのゲートは、制御回路5に接続されており、制御回路5から供給される駆動信号M1〜M3によって、FET51c〜53cのオン/オフがそれぞれ切り換えられる。

【0071】

次いで、この第1チャージポンプ回路CP1aの第1の動作例を説明する。図10に示すように、チャージポンプ駆動回路54〜56の動作は、前述した第2実施形態の第1チャージポンプ回路CP1と全く同じである。また、時刻t6において、前述したように電圧VCAが所定の電圧を上回り、第1チャージポンプ回路CP1aの駆動が停止がされるまで、FET51c〜53cは、オンに維持される。また、時刻t6において、第1チャージポンプ回路CP1aの駆動が停止されると、駆動信号M1〜M3によって、FET51c〜53cがいずれもオフに切り換えられる。

【0072】

次いで、第1チャージポンプ回路CP1aの第2の動作例を説明する。図11に示すように、チャージポンプ駆動回路54〜56の動作は、前述した第2実施形態と全く同じである。FET52cは、時刻t1において、駆動信号M2によってオフからオンに切り換えられる。それにより、コンデンサ51aからコンデンサ52aへの導通が確保されるとともに、電圧の供給が行われる。また、FET51c、53cは、時刻t2において、駆動信号M1、M3によってオンからオフに切り換えられ、時刻t3において、オンに切り換えられる。また、FET52cは、時刻t4において、オンからオフに切り換えられる。以上のようなFET51c〜53cの動作は、チャージポンプ駆動回路54〜55の動作に同期して行われる。そして、時刻t6において、第1チャージポンプ回路CP1aの駆動が停止されると、FET51c〜53cはいずれも、第1チャージポンプ回路CP1aの駆動が再開されるまで、オフに維持される。

【0073】

次いで、第1チャージポンプ回路CP1aの第3の動作例を説明する。図12に示すように、デューティ比が「1」で第1チャージポンプ回路CP1aが駆動されているときのチャージポンプ駆動回路54〜56およびFET51c〜53cの動作は、前述した第2の動作例と全く同じである。時刻t8において、デューティ比が「1」を下回ると、チャージポンプ駆動回路54〜56の各FETは、そのときのオン/オフの状態を、期間Tが経過するまで維持し、時刻t9において、いずれもオンに切り換えられる。一方、基本回路51d〜53dのFET51c〜53cは、時刻t8においていずれも一旦、オフされ、期間Tが経過した時刻t9において、いずれもオンに切り換えられる。

【0074】

次いで、第2実施形態に係る負荷駆動制御回路の第3の変形例について、図13〜図16を参照しながら説明する。図13は、第2実施形態に係る負荷駆動制御回路の第2の変形例、およびこれによって駆動される電動モータ2などを示す回路図である。図14は、逆流防止用スイッチの第1の動作例を説明するためのタイミングチャートである。図15は、逆流防止用スイッチの第2の動作例を説明するためのタイミングチャートである。図16は、逆流防止用スイッチの第3の動作例を説明するためのタイミングチャートである。

【0075】

本変形例の負荷駆動制御回路1cでは、ブートストラップ回路30のダイオード31に代えてスイッチS2が、第2チャージポンプ回路CP2のダイオード41,42に代えてスイッチS1,S3(逆流防止用スイッチ)が、第1チャージポンプ回路CP1のダイオード57に代えてスイッチS4(逆流防止用スイッチ)が、それぞれ設けられている。これらは、いずれもPチャンネルMOSFETで構成されており、スイッチS1〜S3のソースは電源回路4側に接続され、スイッチS4のソースは、第1チャージポンプ回路CP1のコンデンサ53a側に接続されている。また、スイッチS1〜S4のゲートは制御回路5に接続されており、制御回路5から供給される駆動信号によって、各FETのオン/オフが切り換えられる。

【0076】

次いで、本変形例におけるスイッチS1〜S4の第1の動作例について説明する。図14に示すように、ブートストラップ回路30のスイッチS2および第2チャージポンプ回路CP2のスイッチS1は、常時オフされている。一方、スイッチ素子Tr1に制御電圧信号が供給され、スイッチ素子Tr1がオンされているときには、第2チャージポンプ回路CP2のスイッチS3および第1チャージポンプ回路CP1のスイッチS4は、オフされており、時刻t22でスイッチ素子Tr1がオフされるのに先立つ時刻t21において、オンされる。そして、時刻t23でスイッチ素子Tr1がオンされると、その直後の時刻t24において、スイッチS3、S4は、オフされる。スイッチS1〜S4の以上のような動作は、制御電圧信号によりスイッチ素子Tr1がオン/オフされるのに同期して実行される。

【0077】

次いで、本変形例におけるスイッチS1〜S4の第2の動作例について説明する。図15に示すように、この動作例では、制御電圧信号に従い、スイッチ素子Tr1がオン/オフされるのにかかわらず、スイッチS1は、常時、オンに維持され、スイッチS2〜S3は、オフに維持される。

【0078】

次いで本変形例におけるスイッチS1〜S4の第3の動作例について説明する。図16に示すように、この動作例では、スイッチS1〜S4はいずれも、時刻t22においてスイッチ素子Tr1がオフされる直前の時刻t21において、オンされる。そして、時刻t23においてスイッチ素子Tr1がオフされた直後の時刻t24において、スイッチS1〜S4は、いずれもオフされる。スイッチ委S1〜S4の以上のような動作は、制御電圧信号によりスイッチ素子Tr1がオン/オフされるのに同期して実行される。

【0079】

次いで、第1および第2チャージポンプ回路CP1、CP2の切り換えについての動作例を説明する。図17に示すように、スイッチ素子Tr1に対するデューティ比が比較的、小さく、スイッチ素子Tr1のオン/オフが1回、行われる間にブートストラップ回路30の電圧供給用コンデンサ32から放出される電荷が、第1チャージポンプ回路CP1のコンデンサ53aの容量よりも少ないときには、制御回路5は、第1チャージポンプ回路CP1のみを駆動する。

【0080】

また、デューティ比がより大きく、スイッチ素子Tr1が一回、オン/オフがされる間にブートストラップ回路30の電圧供給用コンデンサ32から放出される電荷が、第1チャージポンプ回路CP1のコンデンサ53aの容量を上回るときには、制御回路5は、第1チャージポンプ回路CP1と同時に第2チャージポンプ回路CP2を駆動する。

【0081】

第1チャージポンプ回路CP1のスイッチS4は、時刻t32において、スイッチ素子Tr1がオンされる直前の時刻t31においてオンされ、時刻t33においてスイッチ素子Tr1がオフされた直後の時刻t34において、オフされる。

【0082】

このような動作が、制御電圧信号に同期して繰り返された後、時刻t35において、デューティ比がより大きな値に変更され、スイッチ素子Tr1の1回のオン時間が時刻t35以前よりも長くなると、制御回路5は、第2チャージポンプ回路CP2の駆動を開始させる。スイッチS4は、デューティ比が切り換わった後も、切り換わる前と同様に、スイッチ素子Tr1のオン/オフに同期してオン/オフされる。

【0083】

なお、上述した動作例では、より大きなデューティ比への切り換え後は、第1および第2チャージポンプ回路CP1,CP2の双方を駆動するように制御しているが、昇圧用コンデンサ53aの容量がより小さな第1チャージポンプ回路CP1を停止し、より大容量の昇圧用コンデンサ46を有する第2チャージポンプ回路CP2のみを駆動するようにしてもよい。

【0084】

なお、本発明は上記実施形態に限定されるものではなく、本発明の趣旨の範囲内で、細部の構成を適宜、変更することが可能である。

【符号の説明】

【0085】

1,1a〜1e 負荷駆動制御回路

2 電動モータ(負荷)

3 ICチップ

4 電源回路(電源電圧検出手段)

5 制御回路(制御信号生成手段、チャージポンプ回路制御手段)

10 駆動信号出力回路(制御電圧出力手段)

13 信号源(制御信号生成手段)

23 信号源(制御信号生成手段)

30 ブートストラップ回路

32 電圧供給用コンデンサ

40 チャージポンプ回路

40a チャージポンプ回路

46 昇圧用コンデンサ(第2の昇圧用コンデンサ)

53a コンデンサ(第1の昇圧用コンデンサ)

B1 主電源

B2 副電源

Tr1 スイッチ素子

Tr2 スイッチ素子

CP1 第1チャージポンプ回路

CP1a 第1チャージポンプ回路

CP2 第2チャージポンプ回路

S3 スイッチ(逆流防止用スイッチ)

S4 スイッチ(逆流防止用スイッチ)

【特許請求の範囲】

【請求項1】

主電源から供給される電圧を制御することによって、負荷を駆動する負荷駆動制御回路であって、

副電源と、

前記負荷を駆動するためのパルス幅変調制御信号を生成する制御信号生成手段と、

当該制御信号生成手段により生成されたパルス幅変調制御信号に基づいてオン/オフされることによって、制御電圧信号を出力するための制御電圧出力手段と、

一方の電極が前記副電源側および前記制御電圧出力手段側に接続された電圧供給用コンデンサを有し、前記制御電圧出力手段がオン/オフされるのに応じて、前記副電源から前記電圧供給用コンデンサへの充電、および当該電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を行うことにより、当該制御電圧出力手段に制御電圧信号を出力させるブートストラップ回路と、

前記主電源に接続され、前記制御電圧出力手段から出力された制御電圧信号に基づいてオン/オフされるのに応じて、前記主電源と前記負荷の間を導通させるスイッチ素子と、

一方の電極が前記電圧供給用コンデンサ側に接続された昇圧用コンデンサを有し、前記主電源および前記副電源の少なくとも一方に接続されたチャージポンプ回路と、

前記チャージポンプ回路に接続された前記主電源または前記副電源から前記昇圧用コンデンサへの充電を行わせる一方、前記パルス幅変調制御信号のデューティ比が所定値よりも小さいときに、前記昇圧用コンデンサから前記電圧供給用コンデンサ側に放電させ、当該電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を補助させるように、前記チャージポンプ回路を制御するチャージポンプ回路制御手段と、

を備えていることを特徴とする負荷駆動制御回路。

【請求項2】

前記チャージポンプ回路は、少なくとも、前記昇圧用コンデンサとして第1の昇圧用コンデンサを有する第1のチャージポンプ回路と、前記昇圧用コンデンサとして前記第1の昇圧用コンデンサよりも高耐圧の第2の昇圧用コンデンサを有する第2のチャージポンプ回路とで構成され、

前記第1のチャージポンプ回路に接続された前記副電源または前記主電源の電圧を検出する電源電圧検出手段をさらに備え、

前記チャージポンプ回路制御手段は、前記電源電圧検出手段によって検出された電圧と、前記第1および第2の昇圧用コンデンサの耐圧とに応じて、前記第1および第2のチャージポンプ回路を切り換えて駆動するように、前記チャージポンプ回路を制御することを特徴とする請求項1に記載の負荷駆動制御回路。

【請求項3】

前記チャージポンプ回路制御手段は、前記デューティ比が前記所定値よりも小さいときに、第1の昇圧用コンデンサおよび第2の昇圧用コンデンサの少なくとも一方を、前記電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を補助させるように、前記チャージポンプ回路を制御することを特徴とする請求項2に記載の負荷駆動制御回路。

【請求項4】

前記チャージポンプ回路の少なくとも一部はICチップに搭載され、

前記第2の昇圧用コンデンサは、前記ICチップの外部に設けられていることを特徴とする請求項2または3に記載の負荷駆動制御回路。

【請求項5】

前記第1の昇圧用コンデンサは、前記ICチップに搭載されていることを特徴とする請求項4に記載の負荷駆動制御回路。

【請求項6】

前記昇圧用コンデンサと前記電圧供給用コンデンサの間に設けられた逆流防止用スイッチをさらに備え、

当該逆流防止用スイッチ素子は、前記デューティ比が前記所定値よりも小さいときにオンされることを特徴とする請求項1ないし5のいずれか1項に記載の負荷駆動制御回路。

【請求項1】

主電源から供給される電圧を制御することによって、負荷を駆動する負荷駆動制御回路であって、

副電源と、

前記負荷を駆動するためのパルス幅変調制御信号を生成する制御信号生成手段と、

当該制御信号生成手段により生成されたパルス幅変調制御信号に基づいてオン/オフされることによって、制御電圧信号を出力するための制御電圧出力手段と、

一方の電極が前記副電源側および前記制御電圧出力手段側に接続された電圧供給用コンデンサを有し、前記制御電圧出力手段がオン/オフされるのに応じて、前記副電源から前記電圧供給用コンデンサへの充電、および当該電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を行うことにより、当該制御電圧出力手段に制御電圧信号を出力させるブートストラップ回路と、

前記主電源に接続され、前記制御電圧出力手段から出力された制御電圧信号に基づいてオン/オフされるのに応じて、前記主電源と前記負荷の間を導通させるスイッチ素子と、

一方の電極が前記電圧供給用コンデンサ側に接続された昇圧用コンデンサを有し、前記主電源および前記副電源の少なくとも一方に接続されたチャージポンプ回路と、

前記チャージポンプ回路に接続された前記主電源または前記副電源から前記昇圧用コンデンサへの充電を行わせる一方、前記パルス幅変調制御信号のデューティ比が所定値よりも小さいときに、前記昇圧用コンデンサから前記電圧供給用コンデンサ側に放電させ、当該電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を補助させるように、前記チャージポンプ回路を制御するチャージポンプ回路制御手段と、

を備えていることを特徴とする負荷駆動制御回路。

【請求項2】

前記チャージポンプ回路は、少なくとも、前記昇圧用コンデンサとして第1の昇圧用コンデンサを有する第1のチャージポンプ回路と、前記昇圧用コンデンサとして前記第1の昇圧用コンデンサよりも高耐圧の第2の昇圧用コンデンサを有する第2のチャージポンプ回路とで構成され、

前記第1のチャージポンプ回路に接続された前記副電源または前記主電源の電圧を検出する電源電圧検出手段をさらに備え、

前記チャージポンプ回路制御手段は、前記電源電圧検出手段によって検出された電圧と、前記第1および第2の昇圧用コンデンサの耐圧とに応じて、前記第1および第2のチャージポンプ回路を切り換えて駆動するように、前記チャージポンプ回路を制御することを特徴とする請求項1に記載の負荷駆動制御回路。

【請求項3】

前記チャージポンプ回路制御手段は、前記デューティ比が前記所定値よりも小さいときに、第1の昇圧用コンデンサおよび第2の昇圧用コンデンサの少なくとも一方を、前記電圧供給用コンデンサから前記制御電圧出力手段への電圧の供給を補助させるように、前記チャージポンプ回路を制御することを特徴とする請求項2に記載の負荷駆動制御回路。

【請求項4】

前記チャージポンプ回路の少なくとも一部はICチップに搭載され、

前記第2の昇圧用コンデンサは、前記ICチップの外部に設けられていることを特徴とする請求項2または3に記載の負荷駆動制御回路。

【請求項5】

前記第1の昇圧用コンデンサは、前記ICチップに搭載されていることを特徴とする請求項4に記載の負荷駆動制御回路。

【請求項6】

前記昇圧用コンデンサと前記電圧供給用コンデンサの間に設けられた逆流防止用スイッチをさらに備え、

当該逆流防止用スイッチ素子は、前記デューティ比が前記所定値よりも小さいときにオンされることを特徴とする請求項1ないし5のいずれか1項に記載の負荷駆動制御回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2012−182884(P2012−182884A)

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願番号】特願2011−42791(P2011−42791)

【出願日】平成23年2月28日(2011.2.28)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願日】平成23年2月28日(2011.2.28)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]