負荷駆動回路およびそれを用いた点火装置

【課題】トランジスタのベースの電位が不安定になることで、寄生動作により保護回路が誤作動することを防止する。

【解決手段】保護回路7を逆トランジスタ方式で構成すると共に、各トランジスタ10〜12のベースをコレクタに接続することで、ベースの電位がコレクタの電位に固定できるようにする。これにより、従来のようにベースを開放した場合と比べて、ベースの電位を安定させられ、寄生ベースに対してノイズ的に電位が印加されても、寄生動作によりトランジスタがONしてしまう等の誤動作を防止することが可能となる。また、ベースの電位を安定させられることにより、サージ電流が発生したときに確実に保護回路7のトランジスタ10〜12をONさせられるため、保護回路7にてサージ電流を吸収してGNDに流れさせることが可能となる。

【解決手段】保護回路7を逆トランジスタ方式で構成すると共に、各トランジスタ10〜12のベースをコレクタに接続することで、ベースの電位がコレクタの電位に固定できるようにする。これにより、従来のようにベースを開放した場合と比べて、ベースの電位を安定させられ、寄生ベースに対してノイズ的に電位が印加されても、寄生動作によりトランジスタがONしてしまう等の誤動作を防止することが可能となる。また、ベースの電位を安定させられることにより、サージ電流が発生したときに確実に保護回路7のトランジスタ10〜12をONさせられるため、保護回路7にてサージ電流を吸収してGNDに流れさせることが可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体スイッチ素子のオンオフ制御を行う制御回路とそれをサージ電流などから保護するための保護回路とが備えられた負荷駆動回路に関し、特に、内燃機関における点火装置に適用すると好適である。

【背景技術】

【0002】

自動車に搭載される電子部品には、信頼性とサージ電流等の厳しい環境に耐えられる耐性の両方が要求される。このため、従来、内燃機関における点火装置において、同一の基板上に制御回路と保護回路を設けたものがある。

【0003】

例えば、特許文献1では、基板上に制御回路と保護回路を備えた半導体基板であって、保護回路として、同じ配線長さ、同じ配線幅を持ち、同じ配線抵抗で並列に接続された複数の保護素子を有し、さらに、ベースが開放したnpnトランジスタを含むものが開示されている。

【0004】

図8は、従来の保護回路100を示した回路図である。この図に示されるように、ベースが開放されたnpnトランジスタ101により保護回路100が構成されている。エミッタ側を高電位、コレクタ側を低電位とする逆トランジスタ方式が採用されており、ベースは開放された状態とされている。このような回路構成では、npnトランジスタ101の逆方向(エミッタ−ベース間)電圧が耐圧(例えば24V)以上になるとnpnトランジスタ101がブレークダウンするため、サージ電流をGNDに逃がせるようになっている。

【特許文献1】特開2004−335979号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献1に記載された保護回路では、サージ保護用のnpnトランジスタ101のベースが開放されているため、npnトランジスタ101のベースの電位が不安定となり、ベースに対してノイズ的に電位が印加されると、寄生動作によりnpnトランジスタ101がONしてしまう等、誤動作する恐れがあった。

【0006】

また、ベースを開放する構造であるため、電流増幅率(Hfe)を低くしなければならず、電流増幅率を低くするために、エミッタ層の不純物濃度をベース拡散層の不純物濃度に比べて低くする必要があり、サージ電流保護用のnpnトランジスタ101の動作抵抗が高くなって、サージ電流を吸収し難かった。

【0007】

本発明は上記点に鑑みて、トランジスタのベースの電位が不安定になることで、寄生動作により保護回路が誤作動することを防止することを第1の目的とする。

【0008】

また、サージ電流保護用のnpnトランジスタの動作抵抗が高くなることにより、サージ電流を吸収し難くなることを防止することを第2の目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するため、本発明では、保護回路(7)を、入力端子(3a)と接地端子(3b)間に配置すると共に、入力端子(3a)側をエミッタ、接地端子(3b)をコレクタとする単数もしくは複数のトランジスタ(10〜12)により構成された逆トランジスタ方式とし、該トランジスタ(10〜12)のベースをコレクタに電気的に接続することで、ベースをコレクタと同電位とすることを第1の特徴としている。

【0010】

このように、トランジスタ(10〜12)のベースをコレクタに電気的に接続することで、ベースをコレクタと同電位としている。このため、従来のようにベースを開放した場合と比べて、ベースの電位を安定させられ、寄生ベースに対してノイズ的に電位が印加されても、寄生動作によりトランジスタ(10〜12)がONしてしまう等の誤動作を防止することが可能となる。また、ベースの電位を安定させられることにより、サージ電流が発生したときに確実に保護回路(7)のトランジスタ(10〜12)をONさせられるため、保護回路(7)にてサージ電流を吸収してGNDに流れさせることが可能となる。

【0011】

このような構成の負荷駆動回路では、例えば、トランジスタ(10〜12)は、基板(13)上に形成された、コレクタを構成する第1導電型のコレクタ層(14)と、コレクタ層(14)内において一方を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、ベースを構成する第2導電型の複数のベース層(16)と、複数のベース層(16)内に対してそれぞれ形成され、該ベース層(16)の長手方向と同方向を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、エミッタを構成する第1導電型の複数のエミッタ層(17)と、を備えた構成とされる。

【0012】

この場合、複数のエミッタ層(17)それぞれに接続される複数のエミッタパターン配線(18)と、複数のベース層(16)それぞれに接続される複数のベースパターン配線(19)と、コレクタ層(14)のうち複数のベース層(16)に隣接する部分に接続される複数のコレクタパターン配線(20)と、複数のエミッタパターン配線(18)を連結する第1共通配線(21)と、複数のベースパターン配線(19)および複数のコレクタパターン配線(20)を連結する第2共通配線(22)とを有した構造によりトランジスタ(10〜12)を構成することができる。そして、第1共通配線(21)と第2共通配線(22)を、複数のベース層(16)および複数のエミッタ層(17)の長手方向の両端において、複数のベース層(16)および複数のエミッタ層(17)を挟んで対称的に配置すると共に、複数のベースパターン配線(19)および複数のコレクタパターン配線(20)を、複数のベース層(16)もしくは該複数のベース層(16)に隣接するコレクタ層(14)の長手方向に沿って延設して第1共通配線(21)に接続することで、複数のベースパターン配線(19)および複数のコレクタパターン配線(20)を第1共通配線(21)から櫛歯状に突き出したレイアウトとし、さらに、複数のエミッタパターン配線(18)を、複数のエミッタ層(17)の長手方向に沿って延設して第2共通配線(22)に接続することで、複数のエミッタパターン配線(18)が第2共通配線(22)から櫛歯状に突き出したレイアウトにすると好ましい。

【0013】

このようなレイアウトとすれば、トランジスタ(10〜12)がONしたときには、コレクタパターン配線(20)からコレクタ層(14)やエミッタ層(17)を通じてエミッタパターン配線(18)に流れる電流経路が素子のどの場所を通じた場合であっても均一な長さとなる。このため、保護回路(7)の全体が均一な配線抵抗となるようにできる。

【0014】

また、本発明は、保護回路(7)を、入力端子(3a)と接地端子(3b)間に配置されたトランジスタ(30)と、入力端子(3a)と接地端子(3b)間において直列接続されたツェナーダイオード(31)および抵抗(32)を有するドライブ回路と、を備えた構成とし、トランジスタ(30)のベースをツェナーダイオード(31)と抵抗(32)との接続点(P1)に接続することを第2の特徴としている。

【0015】

このような構成においては、サージ電流が発生したときに、ダイオード(31)の耐圧を超えるため、ダイオード(31)および抵抗(32)の間に電流が流れ、抵抗(32)での電圧ドロップによりトランジスタ(30)のベース−コレクタ間に電位差が発生する。これにより、トランジスタ(30)にベース電流が流れ込み、トランジスタ(30)がONする。したがって、トランジスタ(30)のコレクタ電流としてサージ電流を流せるため、保護回路(7)にてサージ電流を吸収してGNDに流させることが可能となる。また、このような構成とされた場合、従来のようにベースを開放した場合と比べて、電流増幅率Hfeを高くすることが可能となる。すなわち、エミッタ層(37)の不純物濃度をベース層(36)の不純物濃度に比べて低くしなくても良いため、トランジスタ(30)の動作抵抗を低くすることが可能となり、よりサージ電流を吸収し易くすることができる。

【0016】

このような構成の負荷駆動回路においても、トランジスタ(30)を上記第1の特徴と同様の構成とすることができる。

【0017】

この場合、第1共通配線(41)と第2共通配線(42)を、複数のベース層(36)および複数のエミッタ層(37)の長手方向の両端において、複数のベース層(36)および複数のエミッタ層(37)を挟んで対称的に配置すると共に、複数のコレクタパターン配線(40)を、複数のベース層(36)に隣接するコレクタ層(34)の長手方向に沿って延設して第1共通配線(41)に接続することで、複数のコレクタパターン配線(40)を第1共通配線(41)から櫛歯状に突き出したレイアウトとし、複数のエミッタパターン配線(38)を、複数のエミッタ層(37)の長手方向に沿って延設して第2共通配線(42)に接続することで、複数のエミッタパターン配線(38)が第2共通配線(42)から櫛歯状に突き出したレイアウトとする。そして、ベースパターン配線(39)を、エミッタパターン配線(38)および第1共通配線(41)とコレクタパターン配線(40)および第2共通配線(42)の間の隙間を縫って配置すると好ましい。

【0018】

このようなレイアウトとすれば、トランジスタ(30)がONしたときには、コレクタパターン配線(40)からコレクタ層(34)やエミッタ層(37)を通じてエミッタパターン配線(38)に流れる電流経路が素子のどの場所を通じた場合であっても均一な長さとなる。これにより、保護回路(7)の全体が均一な配線抵抗となるようにできる。

【0019】

以上のような負荷駆動回路は、例えば、点火コイル(4)を負荷として、該点火コイル(4)に流すコイル電流を制御するための点火装置に適用すると好ましい。

【0020】

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示すものである。

【発明を実施するための最良の形態】

【0021】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、図中、同一符号を付してある。

【0022】

(第1実施形態)

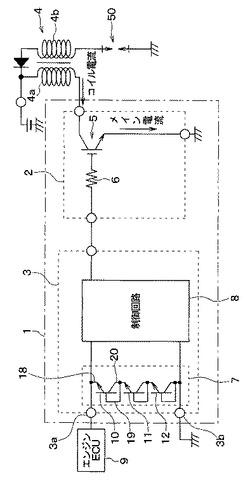

以下、本発明の一実施形態が適用された負荷駆動回路としての点火装置について説明する。図1に、本実施形態における点火装置1の回路構成図を示し、この図に基づいて説明する。

【0023】

点火装置1は、車両の内燃機関におけるプラグ50の点火に用いられる。図1に示されるように、点火装置1には、スイッチ部を構成するスイッチIC2と制御回路部を構成する制御回路IC3とが備えられている。これらスイッチIC2と制御回路IC3とは例えば別々のチップで構成されている。

【0024】

スイッチIC2は、点火コイル4の1次巻線4aへの通電のスイッチング制御を行うためのものである。このスイッチIC2には、IGBT5と抵抗6が備えられている。

【0025】

IGBT5は、点火コイル4の1次巻線4aへの通電のスイッチング制御を行うために用いられる。具体的には、IGBT5のコレクタ端子は、負荷となる点火コイル4の1次巻線4aが接続され、エミッタ端子は、GNDが接続されている。そして、制御回路IC3からIGBT5のゲートに対して制御信号となるゲート電圧が抵抗6を介して入力されることで、IGBT5のオンオフ制御が行える構成とされている。なお、抵抗6は、IGBT5のゲートに対してゲート電圧を印加するための入力抵抗である。

【0026】

一方、制御回路IC3は、保護回路7と制御回路8とが備えられ、入力端子3aを通じてエンジンECU9から送られてくる点火信号をスイッチIC2におけるIGBT5の制御信号として伝える役割を果たす。具体的には、保護回路7は、入力端子3aとGND端子3bとの間に配置され、この保護回路7にて、サージ電流などから制御回路8を保護する。そして、制御回路8にて、例えば点火コイル4の1次巻線4aに流されるコイル電流やスイッチIC2の温度等に基づいてIGBT5の制御信号を調整している。

【0027】

本実施形態では、保護回路7には、エミッタ側を高電位、コレクタ側を低電位とする逆トランジスタ方式が採用されており、本実施形態では、複数のトランジスタ10〜12を直列接続して保護回路7を構成している。各トランジスタ10〜12のベース−コレクタ間が電気的に接続されており、ベースの電位がコレクタの電位に固定されるようになっている。

【0028】

図2は、制御回路IC3中の保護回路7を構成するトランジスタ10の構造およびトランジスタ10の各部とパターン配線との接続状態などを模式的に示した断面図である。また、図3は、トランジスタ10の構造およびレイアウトを示した斜視透過図である。図2は、図3におけるA−A断面に相当している。なお、ここではトランジスタ10を例に挙げているが、トランジスタ11、12も同様の構造とされる。これら各トランジスタ10〜12は、同じ半導体基板上に形成されることになるが、周知の素子分離構造により、互いに電気的に分離された構造にできる。

【0029】

図2に示すように、例えばシリコン基板からなるp型の半導体基板13の表面にn+型コレクタ層14が成膜されており、このn+型コレクタ層14の表層部の所定領域にn-型ウェル層15が形成されている。n-型ウェル層15は、図3に示すように、複数個がストライプ状(短冊状)に並べられた構成とされている。すなわち、複数個のn-型ウェル層15が半導体基板13の一方向に並べて配列されており、その配列方向に対して各n-型ウェル層15の長手方向が垂直とされた構成とされている。そして、各n-型ウェル層15の幅、すなわちの上記配列方向の長さ(幅)や深さが等しくされていると共に、各n-型ウェル層15の長手方向の長さも等しくされている。このため、各n-型ウェル層15の長手方向の両端位置が揃った形状となっている。

【0030】

また、各n-型ウェル層15の内部には、n-型ウェル層15よりも接合深さが浅くされたp+型ベース層16が形成されている。図2の断面において、各p+型ベース層16の長さ(幅)は均一とされており、かつ、基板表面における各p+型ベース層16の終端位置から各n-型ウェル層15の終端位置までの距離が等しくなるように、各p+型ベース層16は各n-型ウェル層15の中心線に沿って形成されている。そして、各p+型ベース層16の長手方向の長さは各n-型ウェル層15の長手方向の長さと一致させられており、各p+型ベース層16の長手方向の両端位置が各n-型ウェル層15の長手方向の両端位置と一致したレイアウトとなっている。

【0031】

同様に、各p+型ベース層16の内部には、p+型ベース層16よりも接合深さが浅くされたn+型エミッタ層17が形成されている。図2の断面において、n+型エミッタ層17の長さ(幅)は均一とされており、かつ、基板表面における各n+型エミッタ層17の終端位置から各p+型ベース層16の終端位置までの距離が等しくなるように、各n+型エミッタ層17は各p+型ベース層16の中心線に沿って形成されている。そして、各n+型エミッタ層17の長手方向の長さは各p+型ベース層16の長手方向の長さと一致させられており、各n+型エミッタ層17の長手方向の両端位置が各p+型ベース層16の長手方向の両端位置と一致したレイアウトとなっている。

【0032】

このように構成されたトランジスタ10では、n+型エミッタ層17がエミッタパターン配線18や後述する共通配線部21を通じて入力端子3aへ接続され、p+型ベース層16およびn+型コレクタ層14がベースパターン配線19やコレクタパターン配線20および後述する共通配線部22を通じてトランジスタ11のn+型エミッタ層側に接続される。また、図2、図3ではトランジスタ11、12については図示していないが、図1の回路図から分かるように、トランジスタ11のp+型ベース層およびn+型コレクタ層は共にベースパターン配線およびコレクタパターン配線を介してトランジスタ12のn+型エミッタ層と接続され、トランジスタ12のp+型ベース層およびn+型コレクタ層は共にベースパターン配線およびコレクタパターン配線を介してGND端子3bに接続される。すなわち、各トランジスタ10のp+型ベース層16をn+型コレクタ層14とが同電位となるようにしている。

【0033】

具体的には、図3に示すように、エミッタパターン配線18は、図示しない層間絶縁膜に形成されたコンタクトホールを通じて各n+型エミッタ層17の表面と接触させられており、各n+型エミッタ層17の長手方向に沿って延設されていると共に、各n+型エミッタ層17の一方の端部よりも外側まで至ってから共通配線部21を通じて接続されている。すなわち、エミッタパターン配線18は、共通配線部21から櫛歯状に突き出した形状とされている。そして、各櫛歯を構成するエミッタパターン配線18の線幅はすべて均一とされている。

【0034】

一方、ベースパターン配線19およびコレクタパターン配線20も、図示しない層間絶縁膜に形成されたコンタクトホールを通じて、各p+型ベース層16の表面もしくは各p+型ベース層16に隣接する各n+型コレクタ層14と接触させられいる。ベースパターン配線19およびコレクタパターン配線20は、各p+型ベース層16もしくは各p+型ベース層16に隣接する各n+型コレクタ層14の長手方向に沿って延設されていると共に、各p+型ベース層16の他方(エミッタパターン配線18における共通配線部21とは反対側)の端部よりも外側まで至ってから共通配線部22を通じて接続されている。すなわち、ベースパターン配線19およびコレクタパターン配線20は、共通配線部22から櫛歯状に突き出した形状とされている。そして、各櫛歯を構成するベースパターン配線19やコレクタパターン配線20の線幅はすべて均一とされている。

【0035】

そして、エミッタパターン配線18とコレクタパターン配線20の間にベースパターン配線19が挟まれるように、各パターン配線18〜20が対向配置されたレイアウトとされている。さらに、エミッタパターン配線18やコレクタパターン配線20がそれぞれ接続される各共通配線部21、22もn+型コレクタ層14やn+型エミッタ層17を挟んで対称的なレイアウトとされている。

【0036】

このような構成により点火装置1が構成されている。このような点火装置1では、エンジンECU9からの点火信号が制御回路IC3を介してスイッチIC2に伝えられることでIGBT5をオンオフ制御するという作動を行う。そして、このような点火装置1に対して、さらに、スイッチIC2に備えられたIGBT5のコレクタ端子に点火コイル4の1次巻線4aが接続されると共に、点火コイル4の2次巻線4bがプラグ50に接続されるため、IGBT5をオンオフ制御することにより、点火装置1によるプラグ50の放電タイミングの制御が行えるようになっている。

【0037】

以上のように構成された点火装置1では、保護回路7を逆トランジスタ方式で構成すると共に、各トランジスタ10〜12のベースをコレクタに接続することで、ベースの電位がコレクタの電位に固定できるようにしている。このため、従来のようにベースを開放した場合と比べて、ベースの電位を安定させられ、寄生ベースに対してノイズ的に電位が印加されても、寄生動作によりトランジスタがONしてしまう等の誤動作を防止することが可能となる。また、ベースの電位を安定させられることにより、サージ電流が発生したときに確実に保護回路7のトランジスタ10〜12をONさせられるため、保護回路7にてサージ電流を吸収してGNDに流れさせることが可能となる。

【0038】

また、本実施形態では、n+型コレクタ層14内において、p+型ベース層16およびn+型エミッタ層17をストライプ状に配置している。そして、エミッタパターン配線18やコレクタパターン配線20も対向配置させていると共に、これらがそれぞれ接続される各共通配線部21、22もn+型コレクタ層14やn+型エミッタ層17を挟んで対称的に配置されている。このため、図4に示す電流経路(図中矢印参照)を示した模式図から分かるように、トランジスタ10〜12がONしたときには、コレクタパターン配線20からn+型コレクタ層14やn+型エミッタ層17を通じてエミッタパターン配線18に流れる電流経路が素子のどの場所を通じた場合であっても均一な長さとなる。このため、保護回路7の全体が均一な配線抵抗となるようにできる。

【0039】

さらに、本実施形態では、トランジスタ10がONしたときに、n+型コレクタ層14やn+型エミッタ層17が対抗配置された領域にしかサージ電流が流れない。つまり、特に電界集中が生じ易いp+型ベース層16やn+型エミッタ層17の両端にはサージ電流が流れない。このため、電界集中による素子破壊からの保護が可能となる。

【0040】

(第2実施形態)

本発明の第2実施形態について説明する。本実施形態の点火装置1は、第1実施形態に対して制御回路IC3内の保護回路7の構成を変更したものであり、その他に関しては第1実施形態と同様であるため、異なる部分についてのみ説明する。

【0041】

図5は、本実施形態における点火装置1の回路構成図である。この図に示すように、保護回路7は、npnトランジスタ30と複数のツェナーダイオード31および抵抗32とを有した構成とされている。npnトランジスタ30は、コレクタが入力端子3aに接続され、エミッタがGND端子3bに接続された構成とされている。複数のツェナーダイオード31および抵抗32は、npnトランジスタ30を駆動するためのドライブ回路を構成するものであり、入力端子3aとGND端子3bとの間において直列接続されており、複数のツェナーダイオード31と抵抗32との間の接続点P1がnpnトランジスタ30のベースに接続された構成とされている。

【0042】

図6は、制御回路IC3中の保護回路7を構成するトランジスタ30の構造およびトランジスタ30の各部とパターン配線との接続状態などを模式的に示した断面図である。また、図7は、トランジスタ30の構造およびレイアウトを示した斜視透過図である。図6は、図7におけるB−B断面に相当している。

【0043】

図6に示すように、トランジスタ30の断面構成の素子部を構成する部分、すなわち半導体基板33、n+型コレクタ層34、n-型ウェル層35、p+型ベース層36、n+型エミッタ層37に関しては、図2に示したトランジスタ10の素子部を構成する半導体基板13、n+型コレクタ層14、n-型ウェル層15、p+型ベース層16、n+型エミッタ層17の断面構成と同様である。ただし、図6に示すように、トランジスタ30では、n+型エミッタ層37がエミッタパターン配線38を通じてGND端子3bへ接続され、p+型ベース層36がベースパターン配線39を通じて接続点P1に接続され、n+型コレクタ層34がコレクタパターン配線40を通じて入力端子3aに接続される。

【0044】

具体的には、図7に示すように、エミッタパターン配線38は、第1実施形態におけるエミッタパターン配線18と同様のレイアウトとされており、各n+型エミッタ層37の長手方向に沿って延設され、各n+型エミッタ層37の一方の端部よりも外側まで至ってから共通配線部41を通じて接続されている。

【0045】

一方、コレクタパターン配線40も、第1実施形態におけるコレクタパターン配線20と同様のレイアウトとされており、各p+型ベース層36に隣接する各n+型コレクタ層34の長手方向に沿って延設され、各p+型ベース層16の他方(エミッタパターン配線38における共通配線部41とは反対側)の端部よりも外側まで至ってから共通配線部42を通じて接続されている。

【0046】

ただし、ベースパターン配線39に関しては、各p+型ベース層16の長手方向に沿って延設されているが、エミッタパターン配線38や共通配線41およびコレクタパターン配線40や共通配線42の間を縫って連結されたレイアウトとされている。これにより、エミッタパターン配線38とコレクタパターン配線40の間にベースパターン配線39が挟まれた状態で、エミッタパターン配線38とコレクタパターン配線40が対向配置されたレイアウトとされている。

【0047】

以上のように構成された点火装置1では、保護回路7をnpnトランジスタ30、ツェナーダイオード31および抵抗32にて構成している。このような構成においては、サージ電流が発生したときに、ツェナーダイオード31の耐圧を超えるため、ツェナーダイオード31および抵抗32の間に電流が流れ、抵抗32での電圧ドロップによりnpnトランジスタ30のベース−コレクタ間に電位差が発生する。これにより、npnトランジスタ30にベース電流が流れ込み、npnトランジスタ30がONする。したがって、npnトランジスタ30のコレクタ電流としてサージ電流を流せるため、保護回路7にてサージ電流を吸収してGNDに流させることが可能となる。

【0048】

また、このような構成とされた場合、従来のようにベースを開放した場合と比べて、電流増幅率Hfeを高くすることが可能となる。すなわち、n+型エミッタ層37の不純物濃度をp+型ベース層36の不純物濃度に比べて低くしなくても良いため、npnトランジスタ30の動作抵抗を低くすることが可能となり、よりサージ電流を吸収し易くすることができる。

【0049】

さらに、本実施形態では、n+型コレクタ層34内において、p+型ベース層36およびn+型エミッタ層37をストライプ状に配置している。そして、エミッタパターン配線38やコレクタパターン配線40も対向配置させていると共に、これらがそれぞれ接続される各共通配線部41、42もn+型コレクタ層34やn+型エミッタ層37を挟んで対称的に配置されている。このため、第1実施形態と同様に、npnトランジスタ30がONしたときには、コレクタパターン配線40からn+型コレクタ層34やn+型エミッタ層37を通じてエミッタパターン配線38に流れる電流経路が素子のどの場所を通じた場合であっても均一な長さとなる。これにより、保護回路7の全体が均一な配線抵抗となるようにできる。

【0050】

(他の実施形態)

上記第1、第2実施形態では、スイッチ部や制御回路部を構成するものとしてスイッチIC2や制御回路IC3を別々のチップで構成した例を挙げたが、必ずしも別々のチップとしなくても良い。

【0051】

上記第1実施形態や第2実施形態において、図1、図4では、トランジスタ10〜12やツェナーダイオード31の数の一例を図示しているが、これらは単なる一例であり、保護回路7として要求される耐圧などに応じて適宜変更可能である。また、トランジスタ10〜12やnpnトランジスタ30の断面構造の一例を示したが、必ずしもこのような断面構造としなければならない訳ではない。

【0052】

なお、上記各実施形態では、トランジスタ10〜12やnpnトランジスタ30を例に挙げて説明したが、各不純物層の導電型を逆転させても構わない。

【図面の簡単な説明】

【0053】

【図1】本発明の第1実施形態にかかる点火装置の回路構成図である。

【図2】制御回路IC中の保護回路を構成するトランジスタの構造およびトランジスタの各部とパターン配線との接続状態などを模式的に示した断面図である。

【図3】トランジスタの構造およびレイアウトを示した斜視透過図である。

【図4】トランジスタがONしたときの電流経路を示した模式図である。

【図5】本発明の第2実施形態にかかる点火装置の回路構成図である。

【図6】制御回路IC中の保護回路を構成するトランジスタの構造およびトランジスタの各部とパターン配線との接続状態などを模式的に示した断面図である。

【図7】トランジスタの構造およびレイアウトを示した斜視透過図である。

【図8】従来のベースが開放されたnpnトランジスタによる保護回路を示した図である。

【符号の説明】

【0054】

1…点火装置、2…スイッチIC、3…制御回路IC、3a…入力端子、3b…GND端子、4…点火コイル、6…抵抗、7…保護回路、8…制御回路、10〜12…トランジスタ、13、33…半導体基板、14、34…n+型コレクタ層、15、35…n-型ウェル層、16、36…p+型ベース層、17、37…n+型エミッタ層、18、38…エミッタパターン配線、19、29…ベースパターン配線、20、40…コレクタパターン配線、21、22、41、42…共通配線部、30…トランジスタ、31…ツェナーダイオード、32…抵抗。

【技術分野】

【0001】

本発明は、半導体スイッチ素子のオンオフ制御を行う制御回路とそれをサージ電流などから保護するための保護回路とが備えられた負荷駆動回路に関し、特に、内燃機関における点火装置に適用すると好適である。

【背景技術】

【0002】

自動車に搭載される電子部品には、信頼性とサージ電流等の厳しい環境に耐えられる耐性の両方が要求される。このため、従来、内燃機関における点火装置において、同一の基板上に制御回路と保護回路を設けたものがある。

【0003】

例えば、特許文献1では、基板上に制御回路と保護回路を備えた半導体基板であって、保護回路として、同じ配線長さ、同じ配線幅を持ち、同じ配線抵抗で並列に接続された複数の保護素子を有し、さらに、ベースが開放したnpnトランジスタを含むものが開示されている。

【0004】

図8は、従来の保護回路100を示した回路図である。この図に示されるように、ベースが開放されたnpnトランジスタ101により保護回路100が構成されている。エミッタ側を高電位、コレクタ側を低電位とする逆トランジスタ方式が採用されており、ベースは開放された状態とされている。このような回路構成では、npnトランジスタ101の逆方向(エミッタ−ベース間)電圧が耐圧(例えば24V)以上になるとnpnトランジスタ101がブレークダウンするため、サージ電流をGNDに逃がせるようになっている。

【特許文献1】特開2004−335979号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献1に記載された保護回路では、サージ保護用のnpnトランジスタ101のベースが開放されているため、npnトランジスタ101のベースの電位が不安定となり、ベースに対してノイズ的に電位が印加されると、寄生動作によりnpnトランジスタ101がONしてしまう等、誤動作する恐れがあった。

【0006】

また、ベースを開放する構造であるため、電流増幅率(Hfe)を低くしなければならず、電流増幅率を低くするために、エミッタ層の不純物濃度をベース拡散層の不純物濃度に比べて低くする必要があり、サージ電流保護用のnpnトランジスタ101の動作抵抗が高くなって、サージ電流を吸収し難かった。

【0007】

本発明は上記点に鑑みて、トランジスタのベースの電位が不安定になることで、寄生動作により保護回路が誤作動することを防止することを第1の目的とする。

【0008】

また、サージ電流保護用のnpnトランジスタの動作抵抗が高くなることにより、サージ電流を吸収し難くなることを防止することを第2の目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するため、本発明では、保護回路(7)を、入力端子(3a)と接地端子(3b)間に配置すると共に、入力端子(3a)側をエミッタ、接地端子(3b)をコレクタとする単数もしくは複数のトランジスタ(10〜12)により構成された逆トランジスタ方式とし、該トランジスタ(10〜12)のベースをコレクタに電気的に接続することで、ベースをコレクタと同電位とすることを第1の特徴としている。

【0010】

このように、トランジスタ(10〜12)のベースをコレクタに電気的に接続することで、ベースをコレクタと同電位としている。このため、従来のようにベースを開放した場合と比べて、ベースの電位を安定させられ、寄生ベースに対してノイズ的に電位が印加されても、寄生動作によりトランジスタ(10〜12)がONしてしまう等の誤動作を防止することが可能となる。また、ベースの電位を安定させられることにより、サージ電流が発生したときに確実に保護回路(7)のトランジスタ(10〜12)をONさせられるため、保護回路(7)にてサージ電流を吸収してGNDに流れさせることが可能となる。

【0011】

このような構成の負荷駆動回路では、例えば、トランジスタ(10〜12)は、基板(13)上に形成された、コレクタを構成する第1導電型のコレクタ層(14)と、コレクタ層(14)内において一方を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、ベースを構成する第2導電型の複数のベース層(16)と、複数のベース層(16)内に対してそれぞれ形成され、該ベース層(16)の長手方向と同方向を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、エミッタを構成する第1導電型の複数のエミッタ層(17)と、を備えた構成とされる。

【0012】

この場合、複数のエミッタ層(17)それぞれに接続される複数のエミッタパターン配線(18)と、複数のベース層(16)それぞれに接続される複数のベースパターン配線(19)と、コレクタ層(14)のうち複数のベース層(16)に隣接する部分に接続される複数のコレクタパターン配線(20)と、複数のエミッタパターン配線(18)を連結する第1共通配線(21)と、複数のベースパターン配線(19)および複数のコレクタパターン配線(20)を連結する第2共通配線(22)とを有した構造によりトランジスタ(10〜12)を構成することができる。そして、第1共通配線(21)と第2共通配線(22)を、複数のベース層(16)および複数のエミッタ層(17)の長手方向の両端において、複数のベース層(16)および複数のエミッタ層(17)を挟んで対称的に配置すると共に、複数のベースパターン配線(19)および複数のコレクタパターン配線(20)を、複数のベース層(16)もしくは該複数のベース層(16)に隣接するコレクタ層(14)の長手方向に沿って延設して第1共通配線(21)に接続することで、複数のベースパターン配線(19)および複数のコレクタパターン配線(20)を第1共通配線(21)から櫛歯状に突き出したレイアウトとし、さらに、複数のエミッタパターン配線(18)を、複数のエミッタ層(17)の長手方向に沿って延設して第2共通配線(22)に接続することで、複数のエミッタパターン配線(18)が第2共通配線(22)から櫛歯状に突き出したレイアウトにすると好ましい。

【0013】

このようなレイアウトとすれば、トランジスタ(10〜12)がONしたときには、コレクタパターン配線(20)からコレクタ層(14)やエミッタ層(17)を通じてエミッタパターン配線(18)に流れる電流経路が素子のどの場所を通じた場合であっても均一な長さとなる。このため、保護回路(7)の全体が均一な配線抵抗となるようにできる。

【0014】

また、本発明は、保護回路(7)を、入力端子(3a)と接地端子(3b)間に配置されたトランジスタ(30)と、入力端子(3a)と接地端子(3b)間において直列接続されたツェナーダイオード(31)および抵抗(32)を有するドライブ回路と、を備えた構成とし、トランジスタ(30)のベースをツェナーダイオード(31)と抵抗(32)との接続点(P1)に接続することを第2の特徴としている。

【0015】

このような構成においては、サージ電流が発生したときに、ダイオード(31)の耐圧を超えるため、ダイオード(31)および抵抗(32)の間に電流が流れ、抵抗(32)での電圧ドロップによりトランジスタ(30)のベース−コレクタ間に電位差が発生する。これにより、トランジスタ(30)にベース電流が流れ込み、トランジスタ(30)がONする。したがって、トランジスタ(30)のコレクタ電流としてサージ電流を流せるため、保護回路(7)にてサージ電流を吸収してGNDに流させることが可能となる。また、このような構成とされた場合、従来のようにベースを開放した場合と比べて、電流増幅率Hfeを高くすることが可能となる。すなわち、エミッタ層(37)の不純物濃度をベース層(36)の不純物濃度に比べて低くしなくても良いため、トランジスタ(30)の動作抵抗を低くすることが可能となり、よりサージ電流を吸収し易くすることができる。

【0016】

このような構成の負荷駆動回路においても、トランジスタ(30)を上記第1の特徴と同様の構成とすることができる。

【0017】

この場合、第1共通配線(41)と第2共通配線(42)を、複数のベース層(36)および複数のエミッタ層(37)の長手方向の両端において、複数のベース層(36)および複数のエミッタ層(37)を挟んで対称的に配置すると共に、複数のコレクタパターン配線(40)を、複数のベース層(36)に隣接するコレクタ層(34)の長手方向に沿って延設して第1共通配線(41)に接続することで、複数のコレクタパターン配線(40)を第1共通配線(41)から櫛歯状に突き出したレイアウトとし、複数のエミッタパターン配線(38)を、複数のエミッタ層(37)の長手方向に沿って延設して第2共通配線(42)に接続することで、複数のエミッタパターン配線(38)が第2共通配線(42)から櫛歯状に突き出したレイアウトとする。そして、ベースパターン配線(39)を、エミッタパターン配線(38)および第1共通配線(41)とコレクタパターン配線(40)および第2共通配線(42)の間の隙間を縫って配置すると好ましい。

【0018】

このようなレイアウトとすれば、トランジスタ(30)がONしたときには、コレクタパターン配線(40)からコレクタ層(34)やエミッタ層(37)を通じてエミッタパターン配線(38)に流れる電流経路が素子のどの場所を通じた場合であっても均一な長さとなる。これにより、保護回路(7)の全体が均一な配線抵抗となるようにできる。

【0019】

以上のような負荷駆動回路は、例えば、点火コイル(4)を負荷として、該点火コイル(4)に流すコイル電流を制御するための点火装置に適用すると好ましい。

【0020】

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示すものである。

【発明を実施するための最良の形態】

【0021】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、図中、同一符号を付してある。

【0022】

(第1実施形態)

以下、本発明の一実施形態が適用された負荷駆動回路としての点火装置について説明する。図1に、本実施形態における点火装置1の回路構成図を示し、この図に基づいて説明する。

【0023】

点火装置1は、車両の内燃機関におけるプラグ50の点火に用いられる。図1に示されるように、点火装置1には、スイッチ部を構成するスイッチIC2と制御回路部を構成する制御回路IC3とが備えられている。これらスイッチIC2と制御回路IC3とは例えば別々のチップで構成されている。

【0024】

スイッチIC2は、点火コイル4の1次巻線4aへの通電のスイッチング制御を行うためのものである。このスイッチIC2には、IGBT5と抵抗6が備えられている。

【0025】

IGBT5は、点火コイル4の1次巻線4aへの通電のスイッチング制御を行うために用いられる。具体的には、IGBT5のコレクタ端子は、負荷となる点火コイル4の1次巻線4aが接続され、エミッタ端子は、GNDが接続されている。そして、制御回路IC3からIGBT5のゲートに対して制御信号となるゲート電圧が抵抗6を介して入力されることで、IGBT5のオンオフ制御が行える構成とされている。なお、抵抗6は、IGBT5のゲートに対してゲート電圧を印加するための入力抵抗である。

【0026】

一方、制御回路IC3は、保護回路7と制御回路8とが備えられ、入力端子3aを通じてエンジンECU9から送られてくる点火信号をスイッチIC2におけるIGBT5の制御信号として伝える役割を果たす。具体的には、保護回路7は、入力端子3aとGND端子3bとの間に配置され、この保護回路7にて、サージ電流などから制御回路8を保護する。そして、制御回路8にて、例えば点火コイル4の1次巻線4aに流されるコイル電流やスイッチIC2の温度等に基づいてIGBT5の制御信号を調整している。

【0027】

本実施形態では、保護回路7には、エミッタ側を高電位、コレクタ側を低電位とする逆トランジスタ方式が採用されており、本実施形態では、複数のトランジスタ10〜12を直列接続して保護回路7を構成している。各トランジスタ10〜12のベース−コレクタ間が電気的に接続されており、ベースの電位がコレクタの電位に固定されるようになっている。

【0028】

図2は、制御回路IC3中の保護回路7を構成するトランジスタ10の構造およびトランジスタ10の各部とパターン配線との接続状態などを模式的に示した断面図である。また、図3は、トランジスタ10の構造およびレイアウトを示した斜視透過図である。図2は、図3におけるA−A断面に相当している。なお、ここではトランジスタ10を例に挙げているが、トランジスタ11、12も同様の構造とされる。これら各トランジスタ10〜12は、同じ半導体基板上に形成されることになるが、周知の素子分離構造により、互いに電気的に分離された構造にできる。

【0029】

図2に示すように、例えばシリコン基板からなるp型の半導体基板13の表面にn+型コレクタ層14が成膜されており、このn+型コレクタ層14の表層部の所定領域にn-型ウェル層15が形成されている。n-型ウェル層15は、図3に示すように、複数個がストライプ状(短冊状)に並べられた構成とされている。すなわち、複数個のn-型ウェル層15が半導体基板13の一方向に並べて配列されており、その配列方向に対して各n-型ウェル層15の長手方向が垂直とされた構成とされている。そして、各n-型ウェル層15の幅、すなわちの上記配列方向の長さ(幅)や深さが等しくされていると共に、各n-型ウェル層15の長手方向の長さも等しくされている。このため、各n-型ウェル層15の長手方向の両端位置が揃った形状となっている。

【0030】

また、各n-型ウェル層15の内部には、n-型ウェル層15よりも接合深さが浅くされたp+型ベース層16が形成されている。図2の断面において、各p+型ベース層16の長さ(幅)は均一とされており、かつ、基板表面における各p+型ベース層16の終端位置から各n-型ウェル層15の終端位置までの距離が等しくなるように、各p+型ベース層16は各n-型ウェル層15の中心線に沿って形成されている。そして、各p+型ベース層16の長手方向の長さは各n-型ウェル層15の長手方向の長さと一致させられており、各p+型ベース層16の長手方向の両端位置が各n-型ウェル層15の長手方向の両端位置と一致したレイアウトとなっている。

【0031】

同様に、各p+型ベース層16の内部には、p+型ベース層16よりも接合深さが浅くされたn+型エミッタ層17が形成されている。図2の断面において、n+型エミッタ層17の長さ(幅)は均一とされており、かつ、基板表面における各n+型エミッタ層17の終端位置から各p+型ベース層16の終端位置までの距離が等しくなるように、各n+型エミッタ層17は各p+型ベース層16の中心線に沿って形成されている。そして、各n+型エミッタ層17の長手方向の長さは各p+型ベース層16の長手方向の長さと一致させられており、各n+型エミッタ層17の長手方向の両端位置が各p+型ベース層16の長手方向の両端位置と一致したレイアウトとなっている。

【0032】

このように構成されたトランジスタ10では、n+型エミッタ層17がエミッタパターン配線18や後述する共通配線部21を通じて入力端子3aへ接続され、p+型ベース層16およびn+型コレクタ層14がベースパターン配線19やコレクタパターン配線20および後述する共通配線部22を通じてトランジスタ11のn+型エミッタ層側に接続される。また、図2、図3ではトランジスタ11、12については図示していないが、図1の回路図から分かるように、トランジスタ11のp+型ベース層およびn+型コレクタ層は共にベースパターン配線およびコレクタパターン配線を介してトランジスタ12のn+型エミッタ層と接続され、トランジスタ12のp+型ベース層およびn+型コレクタ層は共にベースパターン配線およびコレクタパターン配線を介してGND端子3bに接続される。すなわち、各トランジスタ10のp+型ベース層16をn+型コレクタ層14とが同電位となるようにしている。

【0033】

具体的には、図3に示すように、エミッタパターン配線18は、図示しない層間絶縁膜に形成されたコンタクトホールを通じて各n+型エミッタ層17の表面と接触させられており、各n+型エミッタ層17の長手方向に沿って延設されていると共に、各n+型エミッタ層17の一方の端部よりも外側まで至ってから共通配線部21を通じて接続されている。すなわち、エミッタパターン配線18は、共通配線部21から櫛歯状に突き出した形状とされている。そして、各櫛歯を構成するエミッタパターン配線18の線幅はすべて均一とされている。

【0034】

一方、ベースパターン配線19およびコレクタパターン配線20も、図示しない層間絶縁膜に形成されたコンタクトホールを通じて、各p+型ベース層16の表面もしくは各p+型ベース層16に隣接する各n+型コレクタ層14と接触させられいる。ベースパターン配線19およびコレクタパターン配線20は、各p+型ベース層16もしくは各p+型ベース層16に隣接する各n+型コレクタ層14の長手方向に沿って延設されていると共に、各p+型ベース層16の他方(エミッタパターン配線18における共通配線部21とは反対側)の端部よりも外側まで至ってから共通配線部22を通じて接続されている。すなわち、ベースパターン配線19およびコレクタパターン配線20は、共通配線部22から櫛歯状に突き出した形状とされている。そして、各櫛歯を構成するベースパターン配線19やコレクタパターン配線20の線幅はすべて均一とされている。

【0035】

そして、エミッタパターン配線18とコレクタパターン配線20の間にベースパターン配線19が挟まれるように、各パターン配線18〜20が対向配置されたレイアウトとされている。さらに、エミッタパターン配線18やコレクタパターン配線20がそれぞれ接続される各共通配線部21、22もn+型コレクタ層14やn+型エミッタ層17を挟んで対称的なレイアウトとされている。

【0036】

このような構成により点火装置1が構成されている。このような点火装置1では、エンジンECU9からの点火信号が制御回路IC3を介してスイッチIC2に伝えられることでIGBT5をオンオフ制御するという作動を行う。そして、このような点火装置1に対して、さらに、スイッチIC2に備えられたIGBT5のコレクタ端子に点火コイル4の1次巻線4aが接続されると共に、点火コイル4の2次巻線4bがプラグ50に接続されるため、IGBT5をオンオフ制御することにより、点火装置1によるプラグ50の放電タイミングの制御が行えるようになっている。

【0037】

以上のように構成された点火装置1では、保護回路7を逆トランジスタ方式で構成すると共に、各トランジスタ10〜12のベースをコレクタに接続することで、ベースの電位がコレクタの電位に固定できるようにしている。このため、従来のようにベースを開放した場合と比べて、ベースの電位を安定させられ、寄生ベースに対してノイズ的に電位が印加されても、寄生動作によりトランジスタがONしてしまう等の誤動作を防止することが可能となる。また、ベースの電位を安定させられることにより、サージ電流が発生したときに確実に保護回路7のトランジスタ10〜12をONさせられるため、保護回路7にてサージ電流を吸収してGNDに流れさせることが可能となる。

【0038】

また、本実施形態では、n+型コレクタ層14内において、p+型ベース層16およびn+型エミッタ層17をストライプ状に配置している。そして、エミッタパターン配線18やコレクタパターン配線20も対向配置させていると共に、これらがそれぞれ接続される各共通配線部21、22もn+型コレクタ層14やn+型エミッタ層17を挟んで対称的に配置されている。このため、図4に示す電流経路(図中矢印参照)を示した模式図から分かるように、トランジスタ10〜12がONしたときには、コレクタパターン配線20からn+型コレクタ層14やn+型エミッタ層17を通じてエミッタパターン配線18に流れる電流経路が素子のどの場所を通じた場合であっても均一な長さとなる。このため、保護回路7の全体が均一な配線抵抗となるようにできる。

【0039】

さらに、本実施形態では、トランジスタ10がONしたときに、n+型コレクタ層14やn+型エミッタ層17が対抗配置された領域にしかサージ電流が流れない。つまり、特に電界集中が生じ易いp+型ベース層16やn+型エミッタ層17の両端にはサージ電流が流れない。このため、電界集中による素子破壊からの保護が可能となる。

【0040】

(第2実施形態)

本発明の第2実施形態について説明する。本実施形態の点火装置1は、第1実施形態に対して制御回路IC3内の保護回路7の構成を変更したものであり、その他に関しては第1実施形態と同様であるため、異なる部分についてのみ説明する。

【0041】

図5は、本実施形態における点火装置1の回路構成図である。この図に示すように、保護回路7は、npnトランジスタ30と複数のツェナーダイオード31および抵抗32とを有した構成とされている。npnトランジスタ30は、コレクタが入力端子3aに接続され、エミッタがGND端子3bに接続された構成とされている。複数のツェナーダイオード31および抵抗32は、npnトランジスタ30を駆動するためのドライブ回路を構成するものであり、入力端子3aとGND端子3bとの間において直列接続されており、複数のツェナーダイオード31と抵抗32との間の接続点P1がnpnトランジスタ30のベースに接続された構成とされている。

【0042】

図6は、制御回路IC3中の保護回路7を構成するトランジスタ30の構造およびトランジスタ30の各部とパターン配線との接続状態などを模式的に示した断面図である。また、図7は、トランジスタ30の構造およびレイアウトを示した斜視透過図である。図6は、図7におけるB−B断面に相当している。

【0043】

図6に示すように、トランジスタ30の断面構成の素子部を構成する部分、すなわち半導体基板33、n+型コレクタ層34、n-型ウェル層35、p+型ベース層36、n+型エミッタ層37に関しては、図2に示したトランジスタ10の素子部を構成する半導体基板13、n+型コレクタ層14、n-型ウェル層15、p+型ベース層16、n+型エミッタ層17の断面構成と同様である。ただし、図6に示すように、トランジスタ30では、n+型エミッタ層37がエミッタパターン配線38を通じてGND端子3bへ接続され、p+型ベース層36がベースパターン配線39を通じて接続点P1に接続され、n+型コレクタ層34がコレクタパターン配線40を通じて入力端子3aに接続される。

【0044】

具体的には、図7に示すように、エミッタパターン配線38は、第1実施形態におけるエミッタパターン配線18と同様のレイアウトとされており、各n+型エミッタ層37の長手方向に沿って延設され、各n+型エミッタ層37の一方の端部よりも外側まで至ってから共通配線部41を通じて接続されている。

【0045】

一方、コレクタパターン配線40も、第1実施形態におけるコレクタパターン配線20と同様のレイアウトとされており、各p+型ベース層36に隣接する各n+型コレクタ層34の長手方向に沿って延設され、各p+型ベース層16の他方(エミッタパターン配線38における共通配線部41とは反対側)の端部よりも外側まで至ってから共通配線部42を通じて接続されている。

【0046】

ただし、ベースパターン配線39に関しては、各p+型ベース層16の長手方向に沿って延設されているが、エミッタパターン配線38や共通配線41およびコレクタパターン配線40や共通配線42の間を縫って連結されたレイアウトとされている。これにより、エミッタパターン配線38とコレクタパターン配線40の間にベースパターン配線39が挟まれた状態で、エミッタパターン配線38とコレクタパターン配線40が対向配置されたレイアウトとされている。

【0047】

以上のように構成された点火装置1では、保護回路7をnpnトランジスタ30、ツェナーダイオード31および抵抗32にて構成している。このような構成においては、サージ電流が発生したときに、ツェナーダイオード31の耐圧を超えるため、ツェナーダイオード31および抵抗32の間に電流が流れ、抵抗32での電圧ドロップによりnpnトランジスタ30のベース−コレクタ間に電位差が発生する。これにより、npnトランジスタ30にベース電流が流れ込み、npnトランジスタ30がONする。したがって、npnトランジスタ30のコレクタ電流としてサージ電流を流せるため、保護回路7にてサージ電流を吸収してGNDに流させることが可能となる。

【0048】

また、このような構成とされた場合、従来のようにベースを開放した場合と比べて、電流増幅率Hfeを高くすることが可能となる。すなわち、n+型エミッタ層37の不純物濃度をp+型ベース層36の不純物濃度に比べて低くしなくても良いため、npnトランジスタ30の動作抵抗を低くすることが可能となり、よりサージ電流を吸収し易くすることができる。

【0049】

さらに、本実施形態では、n+型コレクタ層34内において、p+型ベース層36およびn+型エミッタ層37をストライプ状に配置している。そして、エミッタパターン配線38やコレクタパターン配線40も対向配置させていると共に、これらがそれぞれ接続される各共通配線部41、42もn+型コレクタ層34やn+型エミッタ層37を挟んで対称的に配置されている。このため、第1実施形態と同様に、npnトランジスタ30がONしたときには、コレクタパターン配線40からn+型コレクタ層34やn+型エミッタ層37を通じてエミッタパターン配線38に流れる電流経路が素子のどの場所を通じた場合であっても均一な長さとなる。これにより、保護回路7の全体が均一な配線抵抗となるようにできる。

【0050】

(他の実施形態)

上記第1、第2実施形態では、スイッチ部や制御回路部を構成するものとしてスイッチIC2や制御回路IC3を別々のチップで構成した例を挙げたが、必ずしも別々のチップとしなくても良い。

【0051】

上記第1実施形態や第2実施形態において、図1、図4では、トランジスタ10〜12やツェナーダイオード31の数の一例を図示しているが、これらは単なる一例であり、保護回路7として要求される耐圧などに応じて適宜変更可能である。また、トランジスタ10〜12やnpnトランジスタ30の断面構造の一例を示したが、必ずしもこのような断面構造としなければならない訳ではない。

【0052】

なお、上記各実施形態では、トランジスタ10〜12やnpnトランジスタ30を例に挙げて説明したが、各不純物層の導電型を逆転させても構わない。

【図面の簡単な説明】

【0053】

【図1】本発明の第1実施形態にかかる点火装置の回路構成図である。

【図2】制御回路IC中の保護回路を構成するトランジスタの構造およびトランジスタの各部とパターン配線との接続状態などを模式的に示した断面図である。

【図3】トランジスタの構造およびレイアウトを示した斜視透過図である。

【図4】トランジスタがONしたときの電流経路を示した模式図である。

【図5】本発明の第2実施形態にかかる点火装置の回路構成図である。

【図6】制御回路IC中の保護回路を構成するトランジスタの構造およびトランジスタの各部とパターン配線との接続状態などを模式的に示した断面図である。

【図7】トランジスタの構造およびレイアウトを示した斜視透過図である。

【図8】従来のベースが開放されたnpnトランジスタによる保護回路を示した図である。

【符号の説明】

【0054】

1…点火装置、2…スイッチIC、3…制御回路IC、3a…入力端子、3b…GND端子、4…点火コイル、6…抵抗、7…保護回路、8…制御回路、10〜12…トランジスタ、13、33…半導体基板、14、34…n+型コレクタ層、15、35…n-型ウェル層、16、36…p+型ベース層、17、37…n+型エミッタ層、18、38…エミッタパターン配線、19、29…ベースパターン配線、20、40…コレクタパターン配線、21、22、41、42…共通配線部、30…トランジスタ、31…ツェナーダイオード、32…抵抗。

【特許請求の範囲】

【請求項1】

負荷(4)に流される電流を制御するための負荷駆動回路であって、

前記電流の制御を行う半導体スイッチング素子(5)が形成されたスイッチ部(2)と、

入力端子(3a)および接地端子(3b)を有し、前記入力端子(3a)から入力される駆動信号に基づいて前記半導体スイッチング素子(5)を駆動するための制御信号を出力する制御回路(8)と、前記制御回路(8)をサージ電流から保護するための保護回路(7)と、を備えた制御回路部(3)と、を備え、

前記保護回路(7)は、前記入力端子(3a)と前記接地端子(3b)間に配置され、前記入力端子(3a)側をエミッタ、前記接地端子(3b)をコレクタとする単数もしくは複数のトランジスタ(10〜12)により構成された逆トランジスタ方式とされており、該トランジスタ(10〜12)はベースが前記コレクタに電気的に接続され、前記ベースが前記コレクタと同電位とされていることを特徴とする負荷駆動回路。

【請求項2】

前記トランジスタ(10〜12)は、

基板(13)上に形成された、前記コレクタを構成する第1導電型のコレクタ層(14)と、

前記コレクタ層(14)内において一方を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、前記ベースを構成する第2導電型の複数のベース層(16)と、

前記複数のベース層(16)内にそれぞれ形成され、該ベース層(16)の長手方向と同方向を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、前記エミッタを構成する第1導電型の複数のエミッタ層(17)と、を備えて構成されていることを特徴とする請求項1に記載の負荷駆動回路。

【請求項3】

前記トランジスタ(10〜12)は、

前記複数のエミッタ層(17)それぞれに接続される複数のエミッタパターン配線(18)と、

前記複数のベース層(16)それぞれに接続される複数のベースパターン配線(19)と、

前記コレクタ層(14)のうち前記複数のベース層(16)に隣接する部分に接続される複数のコレクタパターン配線(20)と、

前記複数のエミッタパターン配線(18)を連結する第1共通配線(21)と、

前記複数のベースパターン配線(19)および前記複数のコレクタパターン配線(20)を連結する第2共通配線(22)とを有し、

前記第1共通配線(21)と前記第2共通配線(22)は、前記複数のベース層(16)および前記複数のエミッタ層(17)の長手方向の両端において、前記複数のベース層(16)および前記複数のエミッタ層(17)を挟んで対称的に配置され、

前記複数のベースパターン配線(19)および前記複数のコレクタパターン配線(20)は、前記複数のベース層(16)もしくは該複数のベース層(16)に隣接する前記コレクタ層(14)の長手方向に沿って延設されて前記第1共通配線(21)に接続されることで、前記複数のベースパターン配線(19)および前記複数のコレクタパターン配線(20)が前記第1共通配線(21)から櫛歯状に突き出したレイアウトとされ、

前記複数のエミッタパターン配線(18)は、前記複数のエミッタ層(17)の長手方向に沿って延設されて前記第2共通配線(22)に接続されることで、前記複数のエミッタパターン配線(18)が前記第2共通配線(22)から櫛歯状に突き出したレイアウトとされていることを特徴とする請求項2に記載の負荷駆動回路。

【請求項4】

負荷(4)に流される電流を制御するための負荷駆動回路であって、

前記電流の制御を行う半導体スイッチング素子(5)が形成されたスイッチ部(2)と、

入力端子(3a)および接地端子(3b)を有し、前記入力端子(3a)から入力される駆動信号に基づいて前記半導体スイッチング素子(5)を駆動するための制御信号を出力する制御回路(8)と、前記制御回路(8)をサージ電流から保護するための保護回路(7)と、を備えた制御回路部(3)と、を備え、

前記保護回路(7)は、前記入力端子(3a)と前記接地端子(3b)間に配置されたトランジスタ(30)と、前記入力端子(3a)と前記接地端子(3b)間において直列接続されたツェナーダイオード(31)および抵抗(32)を有するドライブ回路と、を備えて構成され、前記トランジスタ(30)のベースが前記ツェナーダイオード(31)と前記抵抗(32)との接続点(P1)に接続されていることを特徴とする負荷駆動回路。

【請求項5】

前記トランジスタ(30)は、

基板(33)上に形成された、前記コレクタを構成する第1導電型のコレクタ層(34)と、

前記コレクタ層(34)内において一方を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、前記ベースを構成する第2導電型の複数のベース層(36)と、

前記複数のベース層(36)内に対してそれぞれ形成され、該ベース層(36)の長手方向と同方向を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、前記エミッタを構成する第1導電型の複数のエミッタ層(37)と、を備えて構成されていることを特徴とする請求項4に記載の負荷駆動回路。

【請求項6】

前記トランジスタ(30)は、

前記複数のエミッタ層(37)それぞれに接続される複数のエミッタパターン配線(38)と、

前記複数のベース層(36)それぞれに接続される複数のベースパターン配線(39)と、

前記コレクタ層(34)のうち前記複数のベース層(36)に隣接する部分に接続される複数のコレクタパターン配線(40)と、

前記複数のエミッタパターン配線(38)を連結する第1共通配線(41)と、

前記複数のコレクタパターン配線(40)を連結する第2共通配線(42)とを有し、

前記第1共通配線(41)と前記第2共通配線(42)は、前記複数のベース層(36)および前記複数のエミッタ層(37)の長手方向の両端において、前記複数のベース層(36)および前記複数のエミッタ層(37)を挟んで対称的に配置され、

前記複数のコレクタパターン配線(40)は、前記複数のベース層(36)に隣接する前記コレクタ層(34)の長手方向に沿って延設されて前記第1共通配線(41)に接続されることで、前記複数のコレクタパターン配線(40)が前記第1共通配線(41)から櫛歯状に突き出したレイアウトとされ、

前記複数のエミッタパターン配線(38)は、前記複数のエミッタ層(37)の長手方向に沿って延設されて前記第2共通配線(42)に接続されることで、前記複数のエミッタパターン配線(38)が前記第2共通配線(42)から櫛歯状に突き出したレイアウトとされており、

前記ベースパターン配線(39)は、前記エミッタパターン配線(38)および前記第1共通配線(41)と前記コレクタパターン配線(40)および前記第2共通配線(42)の間の隙間を縫って配置されていることを特徴とする請求項5に記載の負荷駆動回路。

【請求項7】

点火コイル(4)を前記負荷として、請求項1ないし6に記載の負荷駆動回路を前記該点火コイル(4)に流すコイル電流を制御するために適用したことを特徴とする点火装置。

【請求項1】

負荷(4)に流される電流を制御するための負荷駆動回路であって、

前記電流の制御を行う半導体スイッチング素子(5)が形成されたスイッチ部(2)と、

入力端子(3a)および接地端子(3b)を有し、前記入力端子(3a)から入力される駆動信号に基づいて前記半導体スイッチング素子(5)を駆動するための制御信号を出力する制御回路(8)と、前記制御回路(8)をサージ電流から保護するための保護回路(7)と、を備えた制御回路部(3)と、を備え、

前記保護回路(7)は、前記入力端子(3a)と前記接地端子(3b)間に配置され、前記入力端子(3a)側をエミッタ、前記接地端子(3b)をコレクタとする単数もしくは複数のトランジスタ(10〜12)により構成された逆トランジスタ方式とされており、該トランジスタ(10〜12)はベースが前記コレクタに電気的に接続され、前記ベースが前記コレクタと同電位とされていることを特徴とする負荷駆動回路。

【請求項2】

前記トランジスタ(10〜12)は、

基板(13)上に形成された、前記コレクタを構成する第1導電型のコレクタ層(14)と、

前記コレクタ層(14)内において一方を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、前記ベースを構成する第2導電型の複数のベース層(16)と、

前記複数のベース層(16)内にそれぞれ形成され、該ベース層(16)の長手方向と同方向を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、前記エミッタを構成する第1導電型の複数のエミッタ層(17)と、を備えて構成されていることを特徴とする請求項1に記載の負荷駆動回路。

【請求項3】

前記トランジスタ(10〜12)は、

前記複数のエミッタ層(17)それぞれに接続される複数のエミッタパターン配線(18)と、

前記複数のベース層(16)それぞれに接続される複数のベースパターン配線(19)と、

前記コレクタ層(14)のうち前記複数のベース層(16)に隣接する部分に接続される複数のコレクタパターン配線(20)と、

前記複数のエミッタパターン配線(18)を連結する第1共通配線(21)と、

前記複数のベースパターン配線(19)および前記複数のコレクタパターン配線(20)を連結する第2共通配線(22)とを有し、

前記第1共通配線(21)と前記第2共通配線(22)は、前記複数のベース層(16)および前記複数のエミッタ層(17)の長手方向の両端において、前記複数のベース層(16)および前記複数のエミッタ層(17)を挟んで対称的に配置され、

前記複数のベースパターン配線(19)および前記複数のコレクタパターン配線(20)は、前記複数のベース層(16)もしくは該複数のベース層(16)に隣接する前記コレクタ層(14)の長手方向に沿って延設されて前記第1共通配線(21)に接続されることで、前記複数のベースパターン配線(19)および前記複数のコレクタパターン配線(20)が前記第1共通配線(21)から櫛歯状に突き出したレイアウトとされ、

前記複数のエミッタパターン配線(18)は、前記複数のエミッタ層(17)の長手方向に沿って延設されて前記第2共通配線(22)に接続されることで、前記複数のエミッタパターン配線(18)が前記第2共通配線(22)から櫛歯状に突き出したレイアウトとされていることを特徴とする請求項2に記載の負荷駆動回路。

【請求項4】

負荷(4)に流される電流を制御するための負荷駆動回路であって、

前記電流の制御を行う半導体スイッチング素子(5)が形成されたスイッチ部(2)と、

入力端子(3a)および接地端子(3b)を有し、前記入力端子(3a)から入力される駆動信号に基づいて前記半導体スイッチング素子(5)を駆動するための制御信号を出力する制御回路(8)と、前記制御回路(8)をサージ電流から保護するための保護回路(7)と、を備えた制御回路部(3)と、を備え、

前記保護回路(7)は、前記入力端子(3a)と前記接地端子(3b)間に配置されたトランジスタ(30)と、前記入力端子(3a)と前記接地端子(3b)間において直列接続されたツェナーダイオード(31)および抵抗(32)を有するドライブ回路と、を備えて構成され、前記トランジスタ(30)のベースが前記ツェナーダイオード(31)と前記抵抗(32)との接続点(P1)に接続されていることを特徴とする負荷駆動回路。

【請求項5】

前記トランジスタ(30)は、

基板(33)上に形成された、前記コレクタを構成する第1導電型のコレクタ層(34)と、

前記コレクタ層(34)内において一方を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、前記ベースを構成する第2導電型の複数のベース層(36)と、

前記複数のベース層(36)内に対してそれぞれ形成され、該ベース層(36)の長手方向と同方向を長手方向とし、該長手方向と垂直な方向を配列方向としてストライプ状に形成された、前記エミッタを構成する第1導電型の複数のエミッタ層(37)と、を備えて構成されていることを特徴とする請求項4に記載の負荷駆動回路。

【請求項6】

前記トランジスタ(30)は、

前記複数のエミッタ層(37)それぞれに接続される複数のエミッタパターン配線(38)と、

前記複数のベース層(36)それぞれに接続される複数のベースパターン配線(39)と、

前記コレクタ層(34)のうち前記複数のベース層(36)に隣接する部分に接続される複数のコレクタパターン配線(40)と、

前記複数のエミッタパターン配線(38)を連結する第1共通配線(41)と、

前記複数のコレクタパターン配線(40)を連結する第2共通配線(42)とを有し、

前記第1共通配線(41)と前記第2共通配線(42)は、前記複数のベース層(36)および前記複数のエミッタ層(37)の長手方向の両端において、前記複数のベース層(36)および前記複数のエミッタ層(37)を挟んで対称的に配置され、

前記複数のコレクタパターン配線(40)は、前記複数のベース層(36)に隣接する前記コレクタ層(34)の長手方向に沿って延設されて前記第1共通配線(41)に接続されることで、前記複数のコレクタパターン配線(40)が前記第1共通配線(41)から櫛歯状に突き出したレイアウトとされ、

前記複数のエミッタパターン配線(38)は、前記複数のエミッタ層(37)の長手方向に沿って延設されて前記第2共通配線(42)に接続されることで、前記複数のエミッタパターン配線(38)が前記第2共通配線(42)から櫛歯状に突き出したレイアウトとされており、

前記ベースパターン配線(39)は、前記エミッタパターン配線(38)および前記第1共通配線(41)と前記コレクタパターン配線(40)および前記第2共通配線(42)の間の隙間を縫って配置されていることを特徴とする請求項5に記載の負荷駆動回路。

【請求項7】

点火コイル(4)を前記負荷として、請求項1ないし6に記載の負荷駆動回路を前記該点火コイル(4)に流すコイル電流を制御するために適用したことを特徴とする点火装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2008−160283(P2008−160283A)

【公開日】平成20年7月10日(2008.7.10)

【国際特許分類】

【出願番号】特願2006−344347(P2006−344347)

【出願日】平成18年12月21日(2006.12.21)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成20年7月10日(2008.7.10)

【国際特許分類】

【出願日】平成18年12月21日(2006.12.21)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]