負荷駆動回路

【課題】ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能な負荷駆動回路を提供する。

【解決手段】電源3と負荷1との間に接続されたハイサイドスイッチとしてパワーMOSFET2を用いた負荷駆動回路10であって、パワーMOSFET のゲート電圧Vgと電源3の電源電圧Vpとを比較する比較回路11と、パワーMOSFET2のターンオフ動作においてパワーMOSFET2のゲート端子から電荷を放電させる遮断回路12とを具備し、遮断回路12によってパワーMOSFET2のゲート端子から電荷を放電させる放電速度は、ゲート電圧Vgが電源電圧Vpより高い場合の放電速度よりも、ゲート電圧Vgが電源電圧Vpより低い場合の放電速度が遅くなるように設定されている。

【解決手段】電源3と負荷1との間に接続されたハイサイドスイッチとしてパワーMOSFET2を用いた負荷駆動回路10であって、パワーMOSFET のゲート電圧Vgと電源3の電源電圧Vpとを比較する比較回路11と、パワーMOSFET2のターンオフ動作においてパワーMOSFET2のゲート端子から電荷を放電させる遮断回路12とを具備し、遮断回路12によってパワーMOSFET2のゲート端子から電荷を放電させる放電速度は、ゲート電圧Vgが電源電圧Vpより高い場合の放電速度よりも、ゲート電圧Vgが電源電圧Vpより低い場合の放電速度が遅くなるように設定されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、負荷を駆動制御する負荷駆動回路に関し、特にNチャネル型のパワーMOSFETのオン/オフを制御することで負荷を駆動制御する負荷駆動回路に関する。

【背景技術】

【0002】

Nチャネル型のパワーMOSFET(以下、パワーNMOSと称す)は、Pチャネル型のパワーMOSFETに比べて、ON抵抗が低いと共に、大電流を流すことが可能である。従って、ゲート電圧を電源電圧以上に昇圧する必要があるにもかかわらず、電源側で負荷を駆動するハイサイドスイッチとしてもパワーNMOSが用いられている。

【0003】

図5に、ランプやソレノイド等の負荷1を駆動するためのハイサイドスイッチとしてパワーNMOS2を用いた従来の負荷駆動回路例を示し、図6には、図5の各部の信号波形及び動作波形を示す。

NMOS2のドレイン端子に電源3が接続され、パワーNMOS2のソース端子が負荷1を介して接地端子に接続されている。また、パワーNMOS2のゲート端子は昇圧回路4の出力端子に接続され、パワーNMOS2のゲート端子と昇圧回路4の出力端子との接続点にNMOS5のドレイン端子が接続されている。さらに、NMOS5のソース端子は電流源6を介して接地端子に接続され、NMOS5のゲート端子は駆動回路7の出力端子に接続されている。

【0004】

昇圧回路4の入力端子と駆動回路7の入力端子には、パワーNMOS2のオン/オフを制御する駆動信号Vinが入力される。駆動信号は、high又はLowの2レベル間を変化する矩形波である。駆動信号Vinがhighになると昇圧回路4によってパワーNMOS2のゲート電圧Vgがドレイン端子に印加される電源3の電源電圧より高い電圧になるまで充電される。これにより、パワーNMOS2がターンオンされ、導通状態(オン状態)となり、負荷1に電流が流れる。昇圧回路4がパワーNMOS2をターンオンさせる駆動回路として機能する。

【0005】

一方、駆動回路7は、駆動信号Vinを反転させた信号を出力するインバータ等の回路であり、駆動信号VinがLowになると駆動回路7によってNMOS5が導通状態となる。NMOS5が導通状態となると、電流源6によってパワーNMOS2のゲート端子から電荷が放電される。これにより、ゲート電圧Vgが下げられ、パワーNMOS2がターンオフされ、遮断状態(オフ状態)となる。NMOS5、電流源6及び駆動回路7が遮断回路8として機能する。

【0006】

従来の負荷駆動回路におけるパワーNMOS2のターンオフ動作について図6を参照して更に詳細に説明する。

図6(a)に示すように、時刻t1において駆動信号VinがLowになると、NMOS5が導通状態となって、電流源6によってパワーNMOS2のゲート端子から電荷を引き抜かれるため、図6(b)に示すように、時刻t1〜t3にかけてパワーNMOS2のゲート電圧Vgは減少する。ゲート電圧VgがパワーNMOS2の閾値電圧Vth近傍まで減少すると、パワーNMOS2はターンオフされるため、図6(c)の時刻t2に示すように、負荷1に接続されているソース端子の電圧(以下、出力電圧と称す)Voutも低下してゆく。一般的に、駆動信号がHighからLowに変化してから、出力電圧Voutが低下を開始するまでの時間がオフ時間Toff、出力電圧Voutが低下し始めてから立下り切るまでの時間が立下り時間Tfとそれぞれ呼ばれており、オフ時間Toffは応答性の観点から短い方が好ましく、一方、立下り時間Tfはノイズ(dV/dt)の観点から必ずしも最短とする必要はなく、ノイズとターンオフ損失との兼ね合いで決定される。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平06−291631号公報

【特許文献2】特開2003−284318号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上述の従来技術では、パワーNMOS2のゲート端子から引き抜く電荷量、すなわちパワーNMOS2のゲート端子から放電させる電荷量は電流源1に依存されて一定であるため、オフ時間Toff及び立下り時間Tfは、電流源1によって一義的に決定されてしまい、オフ時間Toffと立下り時間Tfとを個別に調整することができないという問題があった。

【0009】

なお、ローサイドスイッチとして絶縁ゲート型バイポーラトランジスタを用いた負荷駆動回路においては、絶縁ゲート型バイポーラトランジスタのコレクタ電圧やゲート電圧を基準電圧と比較し、当該比較結果に応じてゲート端子から放電させる電荷量を変化させることで、オフ時間Toffと立下り時間Tfとを個別に調整する技術が提案されている(例えば、特許文献1、2参照)。

【0010】

しかしながら、特許文献1、2の負荷駆動回路では、コレクタ電圧やゲート電圧と比較する基準電圧を生成するための基準電圧生成回路を設ける必要があり、回路構成が複雑になってしまう。

【0011】

本発明の目的は、上記問題点に鑑みて従来技術の上記問題を解決し、ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能な負荷駆動回路を提供することにある。

【課題を解決するための手段】

【0012】

本発明の負荷駆動回路は、電源と負荷との間に接続されたハイサイドスイッチとしてNチャネル型のパワーMOSFETを用いた負荷駆動回路であって、前記パワーMOSFETのゲート電圧と前記電源の電源電圧とを比較する比較回路と、前記パワーMOSFETのターンオフ動作において前記パワーMOSFETのゲート端子から電荷を放電させる遮断回路とを具備し、前記パワーMOSFETのゲート端子から電荷を放電させる放電速度は、前記ゲート電圧が前記電源電圧より高い場合と比較して、前記ゲート電圧が前記電源電圧より低い場合を遅く切り換えることを特徴とする。

また、本発明の負荷駆動回路において、前記遮断回路は、第1の抵抗と第2の抵抗とを具備し、前記ゲート電圧が前記電源電圧より高い場合には、前記第1の抵抗及び前記第2の抵抗を介して前記パワーMOSFETのゲート端子から電荷を放電させ、前記ゲート電圧が前記電源電圧より低い場合には、前記第2の抵抗のみを介して前記パワーMOSFETのゲート端子から電荷を放電させることを特徴とする。

また、本発明の負荷駆動回路において、前記比較回路は、一方端が前記パワーMOSFETのゲート端子と接続された抵抗と、当該抵抗の他方端とアノードが接続され、カソードが前記電源に接続されたダイオードと、前記抵抗と前記ダイオードとの接続点がゲート端子に、前記パワーMOSFETのゲート端子がソース端子にそれぞれ接続されたPチャネル型のMOSFETからなるスイッチ素子とを具備し、前記比較回路の前記スイッチ素子によって前記第1の抵抗を流れる電流路を開閉させることを特徴とする。

また、本発明の負荷駆動回路において、前記遮断回路は、第1の電流源と第2の電流源とを具備し、前記ゲート電圧が前記電源電圧より高い場合には、前記第1の電流源及び前記第2の電流源を用いて前記パワーMOSFETのゲート端子から電荷を放電させ、前記ゲート電圧が前記電源電圧より低い場合には、前記第2の電流源のみを用いて前記パワーMOSFETのゲート端子から電荷を放電させることを特徴とする。

【発明の効果】

【0013】

本発明によれば、遮断回路によってパワーMOSFETのゲート端子から電荷を放電させる放電速度を、ゲート電圧が電源電圧より高い場合の放電速度よりも、ゲート電圧が電源電圧より低い場合の放電速度を遅く切り換えることにより、ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能になるという効果を奏する。

【図面の簡単な説明】

【0014】

【図1】本発明による第1実施形態の負荷駆動回路の概略構成を示したブロック図である。

【図2】図1の各部の信号波形及び動作波形を示す波形図である。

【図3】図1に示す比較回路及び遮断回路の具体的な回路構成を示す回路構成図である。

【図4】本発明による第2実施形態の負荷駆動回路の概略構成を示したブロック図である。

【図5】従来の負荷駆動回路の概略構成を示したブロック図である。

【図6】図5の各部の信号波形及び動作波形を示す波形図である。

【発明を実施するための形態】

【0015】

(第1実施形態)

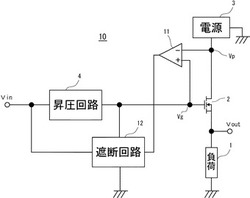

図1に、ランプやソレノイド等の負荷1を駆動するためのハイサイドスイッチとしてNチャネル型のパワーMOSFET(以下、パワーNMOSと称す)2を用いた第1実施形態の負荷駆動回路10の概略構成例を示す。

第1実施形態の負荷駆動回路10は、負荷1を駆動するためのハイサイドスイッチとしてパワーNMOS2と、電力を供給する電源3と、駆動信号Vinを昇圧させる昇圧回路4と、電源3の電源電圧VpとパワーNMOS2のゲート電圧Vgとを比較する比較器11と、ターンオフ動作に際し、パワーNMOS2のゲート端子から電荷を放電させてパワーNMOS2を遮断させる遮断回路12とからなる。

【0016】

パワーNMOS2のドレイン端子に電源3が接続され、パワーNMOS2のソース端子が負荷1を介して接地端子に接続されている。また、パワーNMOS2のゲート端子は昇圧回路4の出力端子に接続され、昇圧回路4の入力端子には、パワーNMOS2のオン/オフを制御する駆動信号Vinが入力される。駆動信号は、high又はLowの2レベル間を変化する矩形波である。駆動信号Vinがhighになると昇圧回路4によってパワーNMOS2のゲート電圧Vgがドレイン端子に印加される電源3の電源電圧Vpより高い電圧になるまで充電される。これにより、パワーNMOS2がターンオンされ、導通状態(オン状態)となり、負荷1に電流が流れる。昇圧回路4がパワーNMOS2をターンオンさせる駆動回路として機能する。

【0017】

比較器11の反転入力端子は電源3とパワーNMOS2のドレイン端子との接続点に接続されていると共に、比較器11の非反転入力端子はパワーNMOS2のゲート端子と昇圧回路4の出力端子との接続点に接続されている。また、比較器11の出力端子は遮断回路12に接続され、電源3の電源電圧VpとパワーNMOS2のゲート電圧Vgとを比較した比較結果が遮断回路12に出力される。

【0018】

遮断回路12には、パワーNMOS2のオン/オフを制御する駆動信号Vinが入力され、駆動信号VinがLowになると、パワーNMOS2のゲート端子から電荷を放電させることで、パワーNMOS2をターンオフさせる。ここで遮断回路12は、比較機11の比較結果に応じて、パワーNMOS2のゲート端子から電荷を放電させる放電電荷量を切り換える。すなわち放電電荷量を大から小へと2段階に切り換えることで放電速度を変化させる。これにより、パワーNMOS2のターンオフ動作におけるパワーNMOS2のゲート電圧Vgは、電源3の電源電圧Vpになるまで急激に減少した後に、緩やかに減少されることになり、オフ時間Toffと立下り時間Tfの最適化が可能になる。

【0019】

第1実施形態の負荷駆動回路10におけるパワーNMOS2のターンオフ動作について図2を参照して更に詳細に説明する。

図2(a)に示すように、時刻t1に駆動信号VinがLowになると、遮断回路12によってパワーNMOS2のゲート端子から電荷が引き抜かれるため、図2(b)に示すように、パワーNMOS2のゲート電圧Vgは減少する。ここで、パワーNMOS2のゲート端子から電荷を放電させる放電電荷量は、時刻t1〜t2の期間にかけてパワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpよりも高い時には大きく、時刻t2〜t3の期間にかけて電源3の電源電圧Vpよりも低くなった時には小さくなるように、遮断回路12によって2段階に切り換えられる。このため、パワーNMOS2のゲート電圧Vgは、電源電圧Vpに達するまで急激に減少した後、緩やかに減少することになる。

このように、パワーNMOS2のゲート電圧Vgの放電電荷量を切り換えることにより、駆動信号VinがHighからLowに変化してから、出力電圧Voutが低下を開始するまでの時間であるオフ時間Toffを短くすることができる。

【0020】

次に、図2(c)の時刻t3で示すように、ゲート電圧VgがパワーNMOS2の閾値電圧Vth近傍まで下がると、パワーNMOS2は遮断される。負荷1に接続されているソース端子の電圧(以下、出力電圧と称す)Voutは、時刻t2〜t3に示すように、パワーNMOS2のゲート電圧Vgに応じて減少する。パワーNMOS2のゲート電圧Vgが電源電圧Vpよりも小さくなると、遮断回路12によりパワーNMOS2のゲート端子から電荷を放電させる放電電荷量が小さく切り換えられるため、ゲート電圧Vgの減少は緩やかになり、出力電圧Voutの変化も緩やかになる。

このように、パワーNMOS2のゲート端子から電荷を放電させる放電電荷量を切り換えることで、出力電圧Voutが低下し始めてから下がり切るまでの立下り時間Tfを変えることなく、駆動信号がLOWに変化してから出力電圧Voutが低下するまでのオフ時間Toffのみ短くすることが可能になる。

【0021】

図3に、比較回路11及び遮断回路12の具体的な回路構成を示す

図3を参照すると、比較回路11は、Pチャネル型のMOSFET(以下、PMOSと称す)13と、抵抗14と、ダイオード15で構成されている。

【0022】

比較回路11の回路構成は、PMOS13のソース端子がパワーNMOS2のゲート端子に接続され、PMOS13のゲート端子とパワーNMOS2のゲート端子との間に抵抗14が接続されている。また、PMOS13のゲート端子と抵抗14の接続点がダイオード15のアノードに接続され、ダイオード15のカソードがパワーNMOS2のドレイン端子と電源3との接続点に接続されている。

【0023】

パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpよりも高い場合には、ダイオード15が順方向となるので、パワーNMOS2のゲート端子から抵抗14、ダイオード15を通って電流が流れる。従って、PMOS13のゲート電圧Vgは、ソース電圧に対してマイナスになって、PMOS13は導通状態となる。一方、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vp以下の場合には、ダイオード15が逆方向となるので、抵抗14に電流が流れることなく、PMOS13のゲート電圧Vgとソース電圧とは同電位となり、PMOS13は遮断状態となる。

【0024】

遮断回路12は、NMOS5と、駆動回路7と、第1の抵抗16と、第2の抵抗17で構成されている。

NMOS5のドレイン端子とNMOS13のドレイン端子とが第1の抵抗16を介して接続されていると共に、NMOS5のドレイン端子とパワーNMOS2のゲート端子とが第2の抵抗17を介して接続されている。また、NMOS5のソース端子は接地端子と接続され、ゲート端子は駆動回路7の出力端子に接続されている。

【0025】

駆動回路7は、駆動信号Vinを反転させた信号を出力するインバータ等の回路であり、駆動信号VinがLowになると駆動回路7によってNMOS5が導通状態となる。NMOS5が導通状態となると、第1の抵抗16と第2の抵抗17を通って電流が流れ、パワーNMOS2のゲート端子から電荷が引き抜かれることになる。このとき、パワーNMOS2のゲート電圧Vgが減少する速度、すなわちパワーNMOS2のゲート端子から電荷を放電させる放電速度は第1の抵抗16と第2の抵抗17の大きさ(第1の抵抗16と第2の抵抗17の合成抵抗値)で決められる。なお、駆動信号VinがHighからLowになった直後は、PMOS13のゲート電圧Vgはソース電圧に対してマイナスであり、PMOS13は導通状態となっているため、パワーNMOS2のゲート端子から第1の抵抗16を通って電流が流れることになる。

【0026】

パワーNMOS2のゲート端子から電荷が引き抜かれ、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vp以下になると、PMOS13のゲート電圧Vgとソース電圧とは同電位となるため、PMOS13は遮断状態となる。これにより、パワーNMOS2のゲート端子からの電荷の放電は第2の抵抗17からの放電のみに切り換わる。従って、

パワーNMOS2のゲート端子からの電荷の放電速度は、第1の抵抗16と第2の抵抗17の合成抵抗値から第2の抵抗17の抵抗値による放電に切り換わり遅く変化する。

【0027】

このように、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpになるまでは、パワーNMOS2のゲート電圧Vgが減少する速度が第1の抵抗16と第2の抵抗17の合成抵抗値で決められ、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpになった以降は、パワーNMOS2のゲート電圧Vgが減少する速度が第2の抵抗17の抵抗値で決められる。従って、第1の抵抗16と第2の抵抗17の抵抗値を調節することで、オフ時間Toffと立下り時間Tfを最適化することが可能になる。なお、第1の抵抗16と第2の抵抗17の合成抵抗値は、第2の抵抗17のみの抵抗値よりも小さいため、オフ時間Toffは短く、一方、立下り時間Tfは相対的に遅くする、又は従来の時間を保持することができる。

【0028】

(第2実施形態)

図4に、ランプやソレノイド等の負荷1を駆動するためのハイサイドスイッチとしてパワーNMOS2を用いた第2実施形態の負荷駆動回路20の概略構成例を示す。

第2実施形態の負荷駆動回路20では、第1実施形態の負荷駆動回路10の遮断回路12の構成を変更した遮断回路12aが採用されている。

【0029】

遮断回路12aは、NMOS5、5aと、電流源6、6aと、駆動回路7、7aとで構成されている。NMOS5のドレイン端子はパワーNMOS2のゲート端子と昇圧回路4の出力端子との接続点に接続され、NMOS5のソース端子は電流源6を介して接地端子に接続され、NMOS5のゲート端子は駆動回路7の出力端子に接続されている。また、NMOS5aのドレイン端子はパワーNMOS2のゲート端子と昇圧回路4の出力端子との接続点に接続され、NMOS5aのソース端子は電流源6aを介して接地端子に接続され、NMOS5aのゲート端子は駆動回路7aの出力端子に接続されている。さらに、駆動回路7、7aには、駆動信号Vinが入力されると共に、駆動回路7aは比較器11の出力端子と接続されている。

【0030】

駆動回路7は、駆動信号Vinを反転させた信号を出力するインバータ等の回路であり、駆動信号VinがLowになると駆動回路7によってNMOS5が導通状態となる。また、駆動回路7aは、駆動信号Vinを反転させた信号を出力するインバータ等の回路と、比較器11の出力と駆動信号Vinを反転させた信号との論理和をとるAND回路とで構成され、駆動信号VinがLowになり、且つ比較器11の出力がHigh、すなわちパワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpよりも高い場合にNMOS5aが導通状態となる。

【0031】

これにより、駆動信号VinがLowになり、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpになるまでは、電流源6と電流源6aとによってパワーNMOS2のゲート端子から電荷が放電され、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpになった以降は、電流源6のみによってパワーNMOS2のゲート端子から電荷が放電される。従って、電流源6と電流源6aを調節することで、オフ時間Toffと立下り時間Tfを最適化することが可能になる。なお、電流源6と電流源6aとで放電させる電荷量は、電流源6のみで放電させる電荷量よりも少ないため、オフ時間Toffは短く、一方、立下り時間Tfは遅くすることができる。

【0032】

以上、本発明を具体的な実施形態で説明したが、上記実施形態は一例であって、本発明の趣旨を逸脱しない範囲で変更して実施できることは言うまでも無い。

【符号の説明】

【0033】

1・・・負荷

2・・・Nチャネル型のパワーMOSFET(パワーNMOS)

3・・・電源

4・・・昇圧回路

5、5a・・・Nチャネル型のMOSFET(NMOS)

6、6a・・・電流源

7、7a・・・駆動回路

10、20・・・負荷駆動回路

11・・・比較器

8、12、12a・・・遮断回路

13・・・Pチャネル型のMOSFET(PMOS)

14・・・抵抗

15・・・ダイオード

16・・・第1の抵抗

17・・・第2の抵抗

Tf・・・立下り時間

Toff・・・オフ時間

【技術分野】

【0001】

本発明は、負荷を駆動制御する負荷駆動回路に関し、特にNチャネル型のパワーMOSFETのオン/オフを制御することで負荷を駆動制御する負荷駆動回路に関する。

【背景技術】

【0002】

Nチャネル型のパワーMOSFET(以下、パワーNMOSと称す)は、Pチャネル型のパワーMOSFETに比べて、ON抵抗が低いと共に、大電流を流すことが可能である。従って、ゲート電圧を電源電圧以上に昇圧する必要があるにもかかわらず、電源側で負荷を駆動するハイサイドスイッチとしてもパワーNMOSが用いられている。

【0003】

図5に、ランプやソレノイド等の負荷1を駆動するためのハイサイドスイッチとしてパワーNMOS2を用いた従来の負荷駆動回路例を示し、図6には、図5の各部の信号波形及び動作波形を示す。

NMOS2のドレイン端子に電源3が接続され、パワーNMOS2のソース端子が負荷1を介して接地端子に接続されている。また、パワーNMOS2のゲート端子は昇圧回路4の出力端子に接続され、パワーNMOS2のゲート端子と昇圧回路4の出力端子との接続点にNMOS5のドレイン端子が接続されている。さらに、NMOS5のソース端子は電流源6を介して接地端子に接続され、NMOS5のゲート端子は駆動回路7の出力端子に接続されている。

【0004】

昇圧回路4の入力端子と駆動回路7の入力端子には、パワーNMOS2のオン/オフを制御する駆動信号Vinが入力される。駆動信号は、high又はLowの2レベル間を変化する矩形波である。駆動信号Vinがhighになると昇圧回路4によってパワーNMOS2のゲート電圧Vgがドレイン端子に印加される電源3の電源電圧より高い電圧になるまで充電される。これにより、パワーNMOS2がターンオンされ、導通状態(オン状態)となり、負荷1に電流が流れる。昇圧回路4がパワーNMOS2をターンオンさせる駆動回路として機能する。

【0005】

一方、駆動回路7は、駆動信号Vinを反転させた信号を出力するインバータ等の回路であり、駆動信号VinがLowになると駆動回路7によってNMOS5が導通状態となる。NMOS5が導通状態となると、電流源6によってパワーNMOS2のゲート端子から電荷が放電される。これにより、ゲート電圧Vgが下げられ、パワーNMOS2がターンオフされ、遮断状態(オフ状態)となる。NMOS5、電流源6及び駆動回路7が遮断回路8として機能する。

【0006】

従来の負荷駆動回路におけるパワーNMOS2のターンオフ動作について図6を参照して更に詳細に説明する。

図6(a)に示すように、時刻t1において駆動信号VinがLowになると、NMOS5が導通状態となって、電流源6によってパワーNMOS2のゲート端子から電荷を引き抜かれるため、図6(b)に示すように、時刻t1〜t3にかけてパワーNMOS2のゲート電圧Vgは減少する。ゲート電圧VgがパワーNMOS2の閾値電圧Vth近傍まで減少すると、パワーNMOS2はターンオフされるため、図6(c)の時刻t2に示すように、負荷1に接続されているソース端子の電圧(以下、出力電圧と称す)Voutも低下してゆく。一般的に、駆動信号がHighからLowに変化してから、出力電圧Voutが低下を開始するまでの時間がオフ時間Toff、出力電圧Voutが低下し始めてから立下り切るまでの時間が立下り時間Tfとそれぞれ呼ばれており、オフ時間Toffは応答性の観点から短い方が好ましく、一方、立下り時間Tfはノイズ(dV/dt)の観点から必ずしも最短とする必要はなく、ノイズとターンオフ損失との兼ね合いで決定される。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平06−291631号公報

【特許文献2】特開2003−284318号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上述の従来技術では、パワーNMOS2のゲート端子から引き抜く電荷量、すなわちパワーNMOS2のゲート端子から放電させる電荷量は電流源1に依存されて一定であるため、オフ時間Toff及び立下り時間Tfは、電流源1によって一義的に決定されてしまい、オフ時間Toffと立下り時間Tfとを個別に調整することができないという問題があった。

【0009】

なお、ローサイドスイッチとして絶縁ゲート型バイポーラトランジスタを用いた負荷駆動回路においては、絶縁ゲート型バイポーラトランジスタのコレクタ電圧やゲート電圧を基準電圧と比較し、当該比較結果に応じてゲート端子から放電させる電荷量を変化させることで、オフ時間Toffと立下り時間Tfとを個別に調整する技術が提案されている(例えば、特許文献1、2参照)。

【0010】

しかしながら、特許文献1、2の負荷駆動回路では、コレクタ電圧やゲート電圧と比較する基準電圧を生成するための基準電圧生成回路を設ける必要があり、回路構成が複雑になってしまう。

【0011】

本発明の目的は、上記問題点に鑑みて従来技術の上記問題を解決し、ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能な負荷駆動回路を提供することにある。

【課題を解決するための手段】

【0012】

本発明の負荷駆動回路は、電源と負荷との間に接続されたハイサイドスイッチとしてNチャネル型のパワーMOSFETを用いた負荷駆動回路であって、前記パワーMOSFETのゲート電圧と前記電源の電源電圧とを比較する比較回路と、前記パワーMOSFETのターンオフ動作において前記パワーMOSFETのゲート端子から電荷を放電させる遮断回路とを具備し、前記パワーMOSFETのゲート端子から電荷を放電させる放電速度は、前記ゲート電圧が前記電源電圧より高い場合と比較して、前記ゲート電圧が前記電源電圧より低い場合を遅く切り換えることを特徴とする。

また、本発明の負荷駆動回路において、前記遮断回路は、第1の抵抗と第2の抵抗とを具備し、前記ゲート電圧が前記電源電圧より高い場合には、前記第1の抵抗及び前記第2の抵抗を介して前記パワーMOSFETのゲート端子から電荷を放電させ、前記ゲート電圧が前記電源電圧より低い場合には、前記第2の抵抗のみを介して前記パワーMOSFETのゲート端子から電荷を放電させることを特徴とする。

また、本発明の負荷駆動回路において、前記比較回路は、一方端が前記パワーMOSFETのゲート端子と接続された抵抗と、当該抵抗の他方端とアノードが接続され、カソードが前記電源に接続されたダイオードと、前記抵抗と前記ダイオードとの接続点がゲート端子に、前記パワーMOSFETのゲート端子がソース端子にそれぞれ接続されたPチャネル型のMOSFETからなるスイッチ素子とを具備し、前記比較回路の前記スイッチ素子によって前記第1の抵抗を流れる電流路を開閉させることを特徴とする。

また、本発明の負荷駆動回路において、前記遮断回路は、第1の電流源と第2の電流源とを具備し、前記ゲート電圧が前記電源電圧より高い場合には、前記第1の電流源及び前記第2の電流源を用いて前記パワーMOSFETのゲート端子から電荷を放電させ、前記ゲート電圧が前記電源電圧より低い場合には、前記第2の電流源のみを用いて前記パワーMOSFETのゲート端子から電荷を放電させることを特徴とする。

【発明の効果】

【0013】

本発明によれば、遮断回路によってパワーMOSFETのゲート端子から電荷を放電させる放電速度を、ゲート電圧が電源電圧より高い場合の放電速度よりも、ゲート電圧が電源電圧より低い場合の放電速度を遅く切り換えることにより、ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能になるという効果を奏する。

【図面の簡単な説明】

【0014】

【図1】本発明による第1実施形態の負荷駆動回路の概略構成を示したブロック図である。

【図2】図1の各部の信号波形及び動作波形を示す波形図である。

【図3】図1に示す比較回路及び遮断回路の具体的な回路構成を示す回路構成図である。

【図4】本発明による第2実施形態の負荷駆動回路の概略構成を示したブロック図である。

【図5】従来の負荷駆動回路の概略構成を示したブロック図である。

【図6】図5の各部の信号波形及び動作波形を示す波形図である。

【発明を実施するための形態】

【0015】

(第1実施形態)

図1に、ランプやソレノイド等の負荷1を駆動するためのハイサイドスイッチとしてNチャネル型のパワーMOSFET(以下、パワーNMOSと称す)2を用いた第1実施形態の負荷駆動回路10の概略構成例を示す。

第1実施形態の負荷駆動回路10は、負荷1を駆動するためのハイサイドスイッチとしてパワーNMOS2と、電力を供給する電源3と、駆動信号Vinを昇圧させる昇圧回路4と、電源3の電源電圧VpとパワーNMOS2のゲート電圧Vgとを比較する比較器11と、ターンオフ動作に際し、パワーNMOS2のゲート端子から電荷を放電させてパワーNMOS2を遮断させる遮断回路12とからなる。

【0016】

パワーNMOS2のドレイン端子に電源3が接続され、パワーNMOS2のソース端子が負荷1を介して接地端子に接続されている。また、パワーNMOS2のゲート端子は昇圧回路4の出力端子に接続され、昇圧回路4の入力端子には、パワーNMOS2のオン/オフを制御する駆動信号Vinが入力される。駆動信号は、high又はLowの2レベル間を変化する矩形波である。駆動信号Vinがhighになると昇圧回路4によってパワーNMOS2のゲート電圧Vgがドレイン端子に印加される電源3の電源電圧Vpより高い電圧になるまで充電される。これにより、パワーNMOS2がターンオンされ、導通状態(オン状態)となり、負荷1に電流が流れる。昇圧回路4がパワーNMOS2をターンオンさせる駆動回路として機能する。

【0017】

比較器11の反転入力端子は電源3とパワーNMOS2のドレイン端子との接続点に接続されていると共に、比較器11の非反転入力端子はパワーNMOS2のゲート端子と昇圧回路4の出力端子との接続点に接続されている。また、比較器11の出力端子は遮断回路12に接続され、電源3の電源電圧VpとパワーNMOS2のゲート電圧Vgとを比較した比較結果が遮断回路12に出力される。

【0018】

遮断回路12には、パワーNMOS2のオン/オフを制御する駆動信号Vinが入力され、駆動信号VinがLowになると、パワーNMOS2のゲート端子から電荷を放電させることで、パワーNMOS2をターンオフさせる。ここで遮断回路12は、比較機11の比較結果に応じて、パワーNMOS2のゲート端子から電荷を放電させる放電電荷量を切り換える。すなわち放電電荷量を大から小へと2段階に切り換えることで放電速度を変化させる。これにより、パワーNMOS2のターンオフ動作におけるパワーNMOS2のゲート電圧Vgは、電源3の電源電圧Vpになるまで急激に減少した後に、緩やかに減少されることになり、オフ時間Toffと立下り時間Tfの最適化が可能になる。

【0019】

第1実施形態の負荷駆動回路10におけるパワーNMOS2のターンオフ動作について図2を参照して更に詳細に説明する。

図2(a)に示すように、時刻t1に駆動信号VinがLowになると、遮断回路12によってパワーNMOS2のゲート端子から電荷が引き抜かれるため、図2(b)に示すように、パワーNMOS2のゲート電圧Vgは減少する。ここで、パワーNMOS2のゲート端子から電荷を放電させる放電電荷量は、時刻t1〜t2の期間にかけてパワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpよりも高い時には大きく、時刻t2〜t3の期間にかけて電源3の電源電圧Vpよりも低くなった時には小さくなるように、遮断回路12によって2段階に切り換えられる。このため、パワーNMOS2のゲート電圧Vgは、電源電圧Vpに達するまで急激に減少した後、緩やかに減少することになる。

このように、パワーNMOS2のゲート電圧Vgの放電電荷量を切り換えることにより、駆動信号VinがHighからLowに変化してから、出力電圧Voutが低下を開始するまでの時間であるオフ時間Toffを短くすることができる。

【0020】

次に、図2(c)の時刻t3で示すように、ゲート電圧VgがパワーNMOS2の閾値電圧Vth近傍まで下がると、パワーNMOS2は遮断される。負荷1に接続されているソース端子の電圧(以下、出力電圧と称す)Voutは、時刻t2〜t3に示すように、パワーNMOS2のゲート電圧Vgに応じて減少する。パワーNMOS2のゲート電圧Vgが電源電圧Vpよりも小さくなると、遮断回路12によりパワーNMOS2のゲート端子から電荷を放電させる放電電荷量が小さく切り換えられるため、ゲート電圧Vgの減少は緩やかになり、出力電圧Voutの変化も緩やかになる。

このように、パワーNMOS2のゲート端子から電荷を放電させる放電電荷量を切り換えることで、出力電圧Voutが低下し始めてから下がり切るまでの立下り時間Tfを変えることなく、駆動信号がLOWに変化してから出力電圧Voutが低下するまでのオフ時間Toffのみ短くすることが可能になる。

【0021】

図3に、比較回路11及び遮断回路12の具体的な回路構成を示す

図3を参照すると、比較回路11は、Pチャネル型のMOSFET(以下、PMOSと称す)13と、抵抗14と、ダイオード15で構成されている。

【0022】

比較回路11の回路構成は、PMOS13のソース端子がパワーNMOS2のゲート端子に接続され、PMOS13のゲート端子とパワーNMOS2のゲート端子との間に抵抗14が接続されている。また、PMOS13のゲート端子と抵抗14の接続点がダイオード15のアノードに接続され、ダイオード15のカソードがパワーNMOS2のドレイン端子と電源3との接続点に接続されている。

【0023】

パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpよりも高い場合には、ダイオード15が順方向となるので、パワーNMOS2のゲート端子から抵抗14、ダイオード15を通って電流が流れる。従って、PMOS13のゲート電圧Vgは、ソース電圧に対してマイナスになって、PMOS13は導通状態となる。一方、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vp以下の場合には、ダイオード15が逆方向となるので、抵抗14に電流が流れることなく、PMOS13のゲート電圧Vgとソース電圧とは同電位となり、PMOS13は遮断状態となる。

【0024】

遮断回路12は、NMOS5と、駆動回路7と、第1の抵抗16と、第2の抵抗17で構成されている。

NMOS5のドレイン端子とNMOS13のドレイン端子とが第1の抵抗16を介して接続されていると共に、NMOS5のドレイン端子とパワーNMOS2のゲート端子とが第2の抵抗17を介して接続されている。また、NMOS5のソース端子は接地端子と接続され、ゲート端子は駆動回路7の出力端子に接続されている。

【0025】

駆動回路7は、駆動信号Vinを反転させた信号を出力するインバータ等の回路であり、駆動信号VinがLowになると駆動回路7によってNMOS5が導通状態となる。NMOS5が導通状態となると、第1の抵抗16と第2の抵抗17を通って電流が流れ、パワーNMOS2のゲート端子から電荷が引き抜かれることになる。このとき、パワーNMOS2のゲート電圧Vgが減少する速度、すなわちパワーNMOS2のゲート端子から電荷を放電させる放電速度は第1の抵抗16と第2の抵抗17の大きさ(第1の抵抗16と第2の抵抗17の合成抵抗値)で決められる。なお、駆動信号VinがHighからLowになった直後は、PMOS13のゲート電圧Vgはソース電圧に対してマイナスであり、PMOS13は導通状態となっているため、パワーNMOS2のゲート端子から第1の抵抗16を通って電流が流れることになる。

【0026】

パワーNMOS2のゲート端子から電荷が引き抜かれ、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vp以下になると、PMOS13のゲート電圧Vgとソース電圧とは同電位となるため、PMOS13は遮断状態となる。これにより、パワーNMOS2のゲート端子からの電荷の放電は第2の抵抗17からの放電のみに切り換わる。従って、

パワーNMOS2のゲート端子からの電荷の放電速度は、第1の抵抗16と第2の抵抗17の合成抵抗値から第2の抵抗17の抵抗値による放電に切り換わり遅く変化する。

【0027】

このように、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpになるまでは、パワーNMOS2のゲート電圧Vgが減少する速度が第1の抵抗16と第2の抵抗17の合成抵抗値で決められ、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpになった以降は、パワーNMOS2のゲート電圧Vgが減少する速度が第2の抵抗17の抵抗値で決められる。従って、第1の抵抗16と第2の抵抗17の抵抗値を調節することで、オフ時間Toffと立下り時間Tfを最適化することが可能になる。なお、第1の抵抗16と第2の抵抗17の合成抵抗値は、第2の抵抗17のみの抵抗値よりも小さいため、オフ時間Toffは短く、一方、立下り時間Tfは相対的に遅くする、又は従来の時間を保持することができる。

【0028】

(第2実施形態)

図4に、ランプやソレノイド等の負荷1を駆動するためのハイサイドスイッチとしてパワーNMOS2を用いた第2実施形態の負荷駆動回路20の概略構成例を示す。

第2実施形態の負荷駆動回路20では、第1実施形態の負荷駆動回路10の遮断回路12の構成を変更した遮断回路12aが採用されている。

【0029】

遮断回路12aは、NMOS5、5aと、電流源6、6aと、駆動回路7、7aとで構成されている。NMOS5のドレイン端子はパワーNMOS2のゲート端子と昇圧回路4の出力端子との接続点に接続され、NMOS5のソース端子は電流源6を介して接地端子に接続され、NMOS5のゲート端子は駆動回路7の出力端子に接続されている。また、NMOS5aのドレイン端子はパワーNMOS2のゲート端子と昇圧回路4の出力端子との接続点に接続され、NMOS5aのソース端子は電流源6aを介して接地端子に接続され、NMOS5aのゲート端子は駆動回路7aの出力端子に接続されている。さらに、駆動回路7、7aには、駆動信号Vinが入力されると共に、駆動回路7aは比較器11の出力端子と接続されている。

【0030】

駆動回路7は、駆動信号Vinを反転させた信号を出力するインバータ等の回路であり、駆動信号VinがLowになると駆動回路7によってNMOS5が導通状態となる。また、駆動回路7aは、駆動信号Vinを反転させた信号を出力するインバータ等の回路と、比較器11の出力と駆動信号Vinを反転させた信号との論理和をとるAND回路とで構成され、駆動信号VinがLowになり、且つ比較器11の出力がHigh、すなわちパワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpよりも高い場合にNMOS5aが導通状態となる。

【0031】

これにより、駆動信号VinがLowになり、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpになるまでは、電流源6と電流源6aとによってパワーNMOS2のゲート端子から電荷が放電され、パワーNMOS2のゲート電圧Vgが電源3の電源電圧Vpになった以降は、電流源6のみによってパワーNMOS2のゲート端子から電荷が放電される。従って、電流源6と電流源6aを調節することで、オフ時間Toffと立下り時間Tfを最適化することが可能になる。なお、電流源6と電流源6aとで放電させる電荷量は、電流源6のみで放電させる電荷量よりも少ないため、オフ時間Toffは短く、一方、立下り時間Tfは遅くすることができる。

【0032】

以上、本発明を具体的な実施形態で説明したが、上記実施形態は一例であって、本発明の趣旨を逸脱しない範囲で変更して実施できることは言うまでも無い。

【符号の説明】

【0033】

1・・・負荷

2・・・Nチャネル型のパワーMOSFET(パワーNMOS)

3・・・電源

4・・・昇圧回路

5、5a・・・Nチャネル型のMOSFET(NMOS)

6、6a・・・電流源

7、7a・・・駆動回路

10、20・・・負荷駆動回路

11・・・比較器

8、12、12a・・・遮断回路

13・・・Pチャネル型のMOSFET(PMOS)

14・・・抵抗

15・・・ダイオード

16・・・第1の抵抗

17・・・第2の抵抗

Tf・・・立下り時間

Toff・・・オフ時間

【特許請求の範囲】

【請求項1】

電源と負荷との間に接続されたハイサイドスイッチとしてNチャネル型のパワーMOSFETを用いた負荷駆動回路であって、

前記パワーMOSFETのゲート電圧と前記電源の電源電圧とを比較する比較回路と、

前記パワーMOSFETのターンオフ動作において前記パワーMOSFETのゲート端子から電荷を放電させる遮断回路とを具備し、

前記パワーMOSFETのゲート端子から電荷を放電させる放電速度は、前記ゲート電圧が前記電源電圧より高い場合と比較して、前記ゲート電圧が前記電源電圧より低い場合を遅く切り換えることを特徴とする負荷駆動回路。

【請求項2】

前記遮断回路は、第1の抵抗と第2の抵抗とを具備し、前記ゲート電圧が前記電源電圧より高い場合には、前記第1の抵抗及び前記第2の抵抗を介して前記パワーMOSFETのゲート端子から電荷を放電させ、前記ゲート電圧が前記電源電圧より低い場合には、前記第2の抵抗のみを介して前記パワーMOSFETのゲート端子から電荷を放電させることを特徴とする請求項1記載の負荷駆動回路。

【請求項3】

前記比較回路は、一方端が前記パワーMOSFETのゲート端子と接続された抵抗と、

当該抵抗の他方端とアノードが接続され、カソードが前記電源に接続されたダイオードと、

前記抵抗と前記ダイオードとの接続点がゲート端子に、前記パワーMOSFETのゲート端子がソース端子にそれぞれ接続されたPチャネル型のMOSFETからなるスイッチ素子とを具備し、

前記比較回路の前記スイッチ素子によって前記第1の抵抗を流れる電流路を開閉させることを特徴とする請求項1又は2記載の負荷駆動回路。

【請求項4】

前記遮断回路は、第1の電流源と第2の電流源とを具備し、前記ゲート電圧が前記電源電圧より高い場合には、前記第1の電流源及び前記第2の電流源を用いて前記パワーMOSFETのゲート端子から電荷を放電させ、前記ゲート電圧が前記電源電圧より低い場合には、前記第2の電流源のみを用いて前記パワーMOSFETのゲート端子から電荷を放電させることを特徴とする請求項1記載の負荷駆動回路。

【請求項1】

電源と負荷との間に接続されたハイサイドスイッチとしてNチャネル型のパワーMOSFETを用いた負荷駆動回路であって、

前記パワーMOSFETのゲート電圧と前記電源の電源電圧とを比較する比較回路と、

前記パワーMOSFETのターンオフ動作において前記パワーMOSFETのゲート端子から電荷を放電させる遮断回路とを具備し、

前記パワーMOSFETのゲート端子から電荷を放電させる放電速度は、前記ゲート電圧が前記電源電圧より高い場合と比較して、前記ゲート電圧が前記電源電圧より低い場合を遅く切り換えることを特徴とする負荷駆動回路。

【請求項2】

前記遮断回路は、第1の抵抗と第2の抵抗とを具備し、前記ゲート電圧が前記電源電圧より高い場合には、前記第1の抵抗及び前記第2の抵抗を介して前記パワーMOSFETのゲート端子から電荷を放電させ、前記ゲート電圧が前記電源電圧より低い場合には、前記第2の抵抗のみを介して前記パワーMOSFETのゲート端子から電荷を放電させることを特徴とする請求項1記載の負荷駆動回路。

【請求項3】

前記比較回路は、一方端が前記パワーMOSFETのゲート端子と接続された抵抗と、

当該抵抗の他方端とアノードが接続され、カソードが前記電源に接続されたダイオードと、

前記抵抗と前記ダイオードとの接続点がゲート端子に、前記パワーMOSFETのゲート端子がソース端子にそれぞれ接続されたPチャネル型のMOSFETからなるスイッチ素子とを具備し、

前記比較回路の前記スイッチ素子によって前記第1の抵抗を流れる電流路を開閉させることを特徴とする請求項1又は2記載の負荷駆動回路。

【請求項4】

前記遮断回路は、第1の電流源と第2の電流源とを具備し、前記ゲート電圧が前記電源電圧より高い場合には、前記第1の電流源及び前記第2の電流源を用いて前記パワーMOSFETのゲート端子から電荷を放電させ、前記ゲート電圧が前記電源電圧より低い場合には、前記第2の電流源のみを用いて前記パワーMOSFETのゲート端子から電荷を放電させることを特徴とする請求項1記載の負荷駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−109916(P2012−109916A)

【公開日】平成24年6月7日(2012.6.7)

【国際特許分類】

【出願番号】特願2010−259033(P2010−259033)

【出願日】平成22年11月19日(2010.11.19)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

【公開日】平成24年6月7日(2012.6.7)

【国際特許分類】

【出願日】平成22年11月19日(2010.11.19)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

[ Back to top ]