負荷駆動装置、画像形成装置、負荷駆動方法およびプログラム

【課題】共振を利用し、容量性負荷の両端に逆位相の電圧パルスを印加可能として消費電力を低減する。

【解決手段】外部容量53と、コイルL1〜L3と、負荷容量52と外部容量53とコイルL1とを接続して第3電極から外部容量53に電荷を放電し、外部容量53への放電完了後に負荷容量51と負荷容量52とコイルL3とを接続して端子1−Aから端子2−Aに電荷を放電し、端子2−Aへの放電完了後に負荷容量51と外部容量53とコイルL1とを接続して外部容量53から端子1−Bに電荷を放電することにより、逆位相のパルス電圧を印加するSW駆動部と、を備える。

【解決手段】外部容量53と、コイルL1〜L3と、負荷容量52と外部容量53とコイルL1とを接続して第3電極から外部容量53に電荷を放電し、外部容量53への放電完了後に負荷容量51と負荷容量52とコイルL3とを接続して端子1−Aから端子2−Aに電荷を放電し、端子2−Aへの放電完了後に負荷容量51と外部容量53とコイルL1とを接続して外部容量53から端子1−Bに電荷を放電することにより、逆位相のパルス電圧を印加するSW駆動部と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、負荷駆動装置、画像形成装置、負荷駆動方法およびプログラムに関する。

【背景技術】

【0002】

画像形成装置でトナーをクラウド化させて現像する方式として、現像ローラの芯金と表面電極に逆位相のパルスを印加する方式が存在する。この方式では、現像ローラの芯金と表面電極は容量性負荷を形成する。

【0003】

このような容量性負荷の両端へのパルスの印加は、プラズマディスプレイなどの分野でも実施されている。容量性負荷を充放電する負荷駆動装置では、消費電力が大きいことが問題となっており、消費電力低減のためにLC共振でエネルギーを遷移させる技術が既に知られている。例えば、特許文献1では、消費電力を低減する目的で、容量性負荷(プラズマディスプレイ表示セル)の両端子に交互に電圧パルスを印加する駆動方式で、容量性負荷を2つのブロックに分割し各ブロックの電圧位相をずらすことで、共振を利用して各ブロックの容量性負荷間で電荷を充放電する技術が提案されている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1の方法では、一方の容量性負荷に電圧が印加されている間、他方の容量性負荷の両端子が等電位である。すなわち、容量性負荷の両端に逆位相の電圧パルスを印加できない。一方、クラウド現像は、容量性負荷の両端に逆位相の電圧パルスを印加することでトナーをクラウド化させるので、特許文献1などの従来の方法を適用できない。

【0005】

本発明は、上記に鑑みてなされたものであって、共振を利用し、かつ、容量性負荷の両端に逆位相の電圧パルスを印加可能とすることにより、消費電力を低減できる負荷駆動装置、画像形成装置、負荷駆動方法およびプログラムを提供することを目的とする。

【課題を解決するための手段】

【0006】

上述した課題を解決し、目的を達成するために、本発明は、第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加する負荷駆動装置であって、容量と、少なくとも1つのコイルと、前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電し、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電し、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電することにより、逆位相の前記パルス電圧を印加する駆動部と、を備えることを特徴とする。

【0007】

また、本発明は、第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加し、容量と少なくとも1つのコイルとを備える負荷駆動装置で実行される負荷駆動方法であって、前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電する第1放電ステップと、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電する第2放電ステップと、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電する第3放電ステップと、を含むことを特徴とする。

【0008】

また、本発明は、第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加し、容量と少なくとも1つのコイルとを備える負荷駆動装置を、前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電し、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電し、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電することにより、逆位相の前記パルス電圧を印加する駆動部、として機能させるためのプログラムである。

【0009】

本発明によれば、共振を利用し、かつ、容量性負荷の両端に逆位相の電圧パルスを印加可能とすることにより、消費電力を低減できるという効果を奏する。

【図面の簡単な説明】

【0010】

【図1】図1は、クラウド現像を行う現像装置を含む画像形成装置の構成例を示すブロック図である。

【図2】図2は、クラウドパルスについて説明する図である。

【図3】図3は、第1の実施形態にかかる負荷駆動装置の構成例を示すブロック図である。

【図4】図4は、ブリッジ回路を説明するための図である。

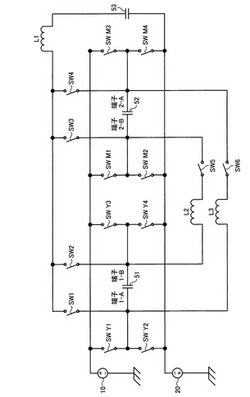

【図5】図5は、ブリッジ回路の全体を含む、負荷駆動装置の詳細な構成例を示す図である。

【図6】図6は、2つの容量性負荷を駆動する場合の負荷駆動装置の動作例を示すタイムチャートである。

【図7】図7は、変形例1の負荷駆動装置の構成例を示すブロック図である。

【図8】図8は、変形例2の負荷駆動装置の構成例を示すブロック図である。

【図9】図9は、逆電流防止用ダイオードを有する変形例3の負荷駆動装置の構成例を示す図である。

【図10】図10は、現像装置の構成例について説明するための図である。

【図11】図11は、トナー担持体の構成例について説明する図である。

【図12】図12は、トナー担持体の他の構成例について説明する図である。

【図13】図13は、カラー画像を形成する画像形成装置のトナー担持体の構成例について説明する図である。

【図14】図14は、第2の実施形態の負荷駆動装置の詳細な構成例を示す図である。

【図15】図15は、ダイオードが備えられていない場合の負荷駆動装置の動作を説明するための図である。

【図16】図16は、ダイオードが備えられていない場合の負荷駆動装置の動作を説明するための図である。

【図17】図17は、ダイオードが備えられていない場合の負荷駆動装置の動作を説明するための図である。

【図18】図18は、図14のような負荷駆動装置の動作を説明するための図である。

【図19】図19は、図14のような負荷駆動装置の動作を説明するための図である。

【図20】図20は、図14のような負荷駆動装置の動作を説明するための図である。

【図21】図21は、変形例4の負荷駆動装置の構成例を示す図である。

【図22】図22は、変形例5の負荷駆動装置の構成例を示す図である。

【図23】図23は、第1および第2の実施形態にかかる画像形成装置のハードウェア構成を示すブロック図である。

【発明を実施するための形態】

【0011】

以下に添付図面を参照して、この発明にかかる負荷駆動装置、画像形成装置、負荷駆動方法およびプログラムの一実施形態を詳細に説明する。

【0012】

(第1の実施形態)

画像形成装置の現像装置として、トナーをクラウド化して現像する方式の現像装置が知られている。例えば、現像ローラの表面に、現像ローラの回転方向と直交する方向に長く延びて所定の間隔で配設された複数の電極を有し、隣接する電極相互の間、または絶縁層を介して設けた下層の導体基材と電極との間に、逆位相のクラウドパルスを印加することでトナーをクラウド化し、現像ローラが回転移動することでトナーの搬送を行い、感光体にトナーを現像する現像装置が存在する。このような現像装置は、電極と電極との間に絶縁層を介するため容量性負荷を形成する。

【0013】

図1は、このような現像装置を含む画像形成装置の構成例を示すブロック図である。画像形成装置は、制御基板2と、負荷駆動装置3と、クラウド現像を行う現像装置4とを備えている。

【0014】

制御基板2は、画像形成装置の全体を制御し、CPU1を備えている。CPU1は、図示しないROM(Read Only Memory)などのメモリに記憶されたプログラムを読み出して負荷駆動装置3を制御する。

【0015】

現像装置4にクラウドパルスを印加する高圧電源である負荷駆動装置3は、制御基板2から発信される周波数制御信号、Vpp制御信号、およびVmin制御信号によりクラウドパルスを発生する。各信号の制御対象は以下の通りである。

周波数制御信号:クラウドパルスの周波数

Vpp制御信号:クラウドパルスの波高値

Vmin制御信号:クラウドパルスの最低値

【0016】

図2は、クラウドパルスについて説明する図である。図2に示すように、クラウドパルスは、波高値がVppであり、最低値がVminである。クラウドパルスの周波数、Vpp、およびVminは、温湿度環境や画像濃度に応じて最適なクラウドパルスとなるように制御される。以降、説明の簡略化のためクラウドパルスの状態を、波高値をHとし、最低値をLとして説明する。

【0017】

図3は、負荷駆動装置3の構成例を示すブロック図である。負荷駆動装置3は、SW駆動部30と、ブリッジ回路50と、Vpp電源10と、Vmin電源20と、出力部40とを備えている。

【0018】

Vpp電源10は、図2に示すVppの電圧値を出力する電源である。Vmin電源20は、図2に示すVminの電圧値を出力する電源である。パルスの下限値または上限値が接地電位でよい場合、Vmin電源20は不要である。

【0019】

SW駆動部30は、ブリッジ回路50に含まれる各スイッチ(後述)を制御する。これにより、最低値がVminであり、波高値がVppであるクラウドパルスが、ブリッジ回路50から出力部40を介して現像装置4に出力される。スイッチとしては、例えば高耐圧FET(Field Effect Transistor)を用いる。SW駆動部30は、各FETを所定のタイミングでオンおよびオフにする。

【0020】

図4は、ブリッジ回路50を説明するための図である。なお、図4は、説明のためにブリッジ回路50の一部のみを記載している。ブリッジ回路50の全体構成については図5で後述する。

【0021】

ブリッジ回路50は、スイッチとしてSW Y1〜SW Y4と、を含んでいる。なお、負荷容量51は、容量性負荷を形成する図1の現像装置4に相当する。SW Y1〜SW Y4は、図3のSW駆動部30により所定のタイミングでオンおよびオフされる。SW Y1、SW Y4がオン、SW Y3、SW Y2がオフのとき、負荷容量51の左側の端子がHとなり、右側の端子がLになる。SW Y1、SW Y4がオフ、SW Y3、SW Y2がオンのとき、負荷容量51の左側の端子がLとなり、右側の端子がHになる。

【0022】

例えば図1で説明したクラウド現像を行う現像装置4の場合、画像形成装置のステーション数分の容量性負荷(現像装置4)にクラウドパルスを印加する必要がある。画像形成装置のステーションがカラーの4色(Y、M、C、K)に対応する4つの場合、容量性負荷(現像装置4)の数は4つとなる。以下では、2つの容量性負荷(現像装置4)を備える場合を例に説明する。

【0023】

図5は、ブリッジ回路50の全体を含む、負荷駆動装置3の詳細な構成例を示す図である。図5に示すように、負荷駆動装置3は、図3に示すVpp電源10、Vmin電源20のほかに、外部容量53と、コイル(インダクタ)L1〜L3とを備えている。外部容量53は、電荷充電のために、負荷容量51および52とは別に設けた容量である。なお、負荷容量51および52は、2つの容量性負荷(現像装置4)に相当する。

【0024】

負荷容量51は、スイッチ(SW Y1、SW Y3)を介してVpp電源10に接続され、スイッチ(SW Y2、SW Y4)を介してVmin電源20に接続される。負荷容量52は、スイッチ(SW M1、SW M3)を介してVpp電源10に接続され、スイッチ(SW M2、SW M4)を介してVmin電源20に接続される。

【0025】

負荷容量51の端子1−A、1−B、および、負荷容量52の端子2−A、2−Bは、スイッチ(SW1、SW2、SW3、SW4)と、コイルL1を介して外部容量53に接続される。端子1−Aは、端子2−Aとスイッチ(SW6)とコイルL3を介して接続される。端子1−Bは、端子2−Bとスイッチ(SW5)とコイルL2を介して接続される。

【0026】

図5の各スイッチ(SW1〜SW6、SW Y1〜SW Y4、SW M1〜SW M4)は、SW駆動部30でオンおよびオフが制御される。

【0027】

図6は、2つの容量性負荷を駆動する場合の負荷駆動装置3の動作例を示すタイムチャートである。図6の「1−A」、「1−B」、「2−A」、および「2−B」は、それぞれ端子1−A、端子1−B、端子2−A、および端子2−Bの電位を表す。また、「C」は、外部容量53の電位を表す。Hのときの電位が図2のVmin+Vppであり、Lのときの電位がVminである。SW Y1〜SW Y4、SW M1〜SW M4、およびSW1〜SW6は、Hがスイッチオンを表し、Lがスイッチオフを表す。

【0028】

以下、図5の構成の負荷駆動装置3の動作を、図6のタイムチャートに従って説明する。

【0029】

(期間a)SW Y1、SW Y4、SW M1、SW M4がオンの状態で、1−AがH、1−BがL、2−AがL、2−BがHである。

(期間b)SW M1をオフにする。この期間はSW M1とSW3が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間c)SW3をオンにする。負荷容量52とコイルL1、外部容量53との間でLC共振が発生し、電荷が端子2−Bから外部容量53に移動する。電荷が全て移動後、SW3をオフにする。

(期間d)SW3をオフにする。この期間はSW3とSW M2が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間e)SW Y1をオフ、SW M2をオン、SW M4をオフにする。この期間はSW Y1とSW6が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間f)SW6をオンにする。負荷容量51とコイルL3、負荷容量52との間でLC共振が発生し、電荷が端子1−Aから端子2−Aに移動する。電荷が全て移動後SW3をオフにする。

(期間g)SW6をオフにする。この期間はSW6とSW M3が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間h)SW Y2をオン、SW Y4をオフ、SW M3をオンにする。この期間はSW Y4とSW2が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。またSW M3をオンにすることで、充電経路中の電力ロスにより端子2−Aの電圧がVmin+Vppに達しない場合でも、Vmin+Vppとすることができる。

(期間i)SW2をオンにする。負荷容量51とコイルL1、外部容量53との間でLC共振が発生し、電荷が外部容量53から端子1−Bに移動する。電荷が全て移動後SW2をオフにする。

(期間j)SW2をオフにする。この期間はSW2とSW Y3が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間k)SW Y3をオンにする。この期間は1−AがL、1−BがH、2−AがH、2−BがLとなっており、期間aと逆のパルス状態となる。

(期間l)SW M3をオフにする。この期間は1μsほどの時間でよい。

(期間m)SW4をオンにする。負荷容量52とコイルL1、外部容量53との間でLC共振が発生し、電荷が端子2−Aから外部容量53に移動する。電荷が全て移動後SW5をオフにする。

(期間n)SW4をオフにする。この期間はSW4とSW M4が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間o)SW Y3をオフ、SW M2をオフ、SW M4をオンにする。この期間はSW Y3とSW5が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間p)SW5をオンにする。負荷容量51とコイルL2、負荷容量52との間でLC共振が発生し、電荷が端子1−Bから端子2−Bに移動する。電荷が全て移動後SW5をオフにする。

(期間q)SW5をオフにする。この期間はSW5とSW M1が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間r)SW Y2をオフ、SW Y4をオン、SW M1をオンにする。この期間はSW Y2とSW1が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間s)SW1をオンにする。負荷容量51とコイルL1、外部容量53との間でLC共振が発生し、電荷が外部容量53から端子1−Aに移動する。電荷が全て移動後SW1をオフにする。

(期間t)SW1をオフにする。この期間はSW1とSW Y1が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

【0030】

次にSW Y1をオンにすることで期間aの状態に戻る。そして、期間a〜期間tを繰り返すことで、負荷容量51および負荷容量52の両端子に逆位相のパルス波形を印加することができる。

【0031】

このように、本実施形態の負荷駆動装置3では、端子1−A、端子1−B、端子2−A、端子2−Bを端子毎のスイッチと共通のコイルとで外部容量53に接続し、端子1−Aと端子2−Aをコイルとスイッチで接続し、端子1−Bと端子2−Bをコイルとスイッチで接続することにより、端子2−Aから外部容量53へ放電終了後、端子1−Bから端子2−Bへ放電し、放電終了後、外部容量53から端子1−Aに放電することができる。これにより、共振を利用した低消費電力化を実現できる。また、上記のようにスイッチを制御することにより、容量性負荷の両端に逆位相の電圧パルスを印加できる。

【0032】

(変形例1)

図7は、変形例1の負荷駆動装置3−2の構成例を示すブロック図である。負荷駆動装置3−2は、SW駆動部30−2と、ブリッジ回路50と、Vpp電源10と、Vmin電源20と、出力部40と、端子電圧検出回路60とを備えている。負荷駆動装置3−2は、端子電圧検出回路60を備えること、および、SW駆動部30−2の機能が、図3の負荷駆動装置3と異なっている。

【0033】

端子電圧検出回路60は、負荷容量51、負荷容量52、および、外部容量53の端子電圧を検出する回路である。

【0034】

充放電用のスイッチSW1〜SW6は、充放電が完全に終了した瞬間にオフにするのが最も電力効率がよい。そこで、変形例1の負荷駆動装置3−2は、各負荷容量の端子の電圧を検知する端子電圧検出回路60をさらに備え、端子電圧が所定の電圧になったときに、端子電圧検出回路60からSW駆動部30−2に充放電終了信号を発信する。所定の電圧とは例えばVmin+Vpp、またはVminである。

【0035】

SW駆動部30−2は、充放電終了信号を受信したときに、スイッチSW1〜SW6をオフにする。これにより、電力効率を向上させることができる。

【0036】

(変形例2)

図8は、変形例2の負荷駆動装置3−3の構成例を示すブロック図である。負荷駆動装置3−3は、SW駆動部30−3と、ブリッジ回路50と、Vpp電源10と、Vmin電源20と、出力部40と、充電電流検出回路70とを備えている。負荷駆動装置3−3は、充電電流検出回路70を備えること、および、SW駆動部30−3の機能が、図3の負荷駆動装置3と異なっている。

【0037】

充電電流検出回路70は、充放電用コイル(コイルL1〜L3)へ流れる電流を検出する回路である。

【0038】

充放電用コイルへ流れる電流は時間に対して正弦波となり、電流が略0となる時が充放電終了である。そのため充放電用コイルへ流れる電流を検知する充電電流検出回路70をさらに備え、電流が0になるときに、充電電流検出回路70からSW駆動部30−3に充放電終了信号を発信する。

【0039】

SW駆動部30−3は、充放電終了信号を受信したときに、スイッチSW1〜SW6をオフにする。これにより、電力効率を向上させることができる。

【0040】

(変形例3)

各スイッチのオンおよびオフは、SW駆動部30によって制御され、そのタイミングはSW駆動部30の定数によって決まる。回路定数にはバラツキが生じるため、スイッチのオンおよびオフのタイミングは狙いのタイミングからずれる可能性がある。

【0041】

例えば期間cにSW3をオンして2−Bから外部容量53に放電する場合、SW3をオフにするタイミングが遅れ、放電終了後もSW3がオンしたままの状態とすると、共振により放電とは逆方向、すなわち、外部容量53から2−Bに電流が流れる。スイッチには主にFETが用いられるため、逆方向に電流を流すと破壊等の不具合が発生する。またSW3をオフにするタイミングが早くなり、放電終了前にSW3をオフにするとコイルL1に逆起電圧が発生し、FETが破壊される。

【0042】

そこで、変形例3では、FETへの逆電流を防止するダイオードをさらに備える構成とする。図9は、逆電流防止用ダイオードを有する変形例3の負荷駆動装置の構成例を示す図である。図9に示すように、変形例3の負荷駆動装置は、逆電流防止用のダイオード901〜906を備えている。

【0043】

このような構成により、FETへの逆電流による破壊を防ぐことができる。また、逆電流が発生しないので、充放電に必要な時間より十分に長い時間、SW1〜SW6をオンにすることができ、放電終了前にスイッチをオフにすることによる逆起電圧の発生、および、FETの破壊を防止することができる。

【0044】

次に、画像形成装置の現像装置4の構成例について説明する。図10は、現像装置4の構成例について説明するための図である。図10に示すように、現像装置4は、現像剤であるトナーを担持するトナー担持体101と、例えば有機感光体(OPC)などの感光体102とを備えている。

【0045】

負荷駆動装置3がクラウドパルスをトナー担持体101に印加することで、トナーをクラウド状態にし、感光体102にトナーを現像させることができる。

【0046】

図11は、トナー担持体101の構成例について説明する図である。トナー担持体101は、その表面に、トナーの搬送方向と直交する方向に長く延びて所定の間隔で配設された複数の電極1101を有する。絶縁層1103を介して設けた下層の電極である導体基材1102と電極1101との間に逆位相のクラウドパルスを印加することでトナーをクラウド化することができる。下層の導体基材1102と電極1101とが容量性負荷を形成する。

【0047】

図12は、トナー担持体101の他の構成例について説明する図である。なお、図12(a)はトナー担持体101を展開した状態で示す模式的平面説明図、図12(b)は同じく模式的断面説明図である。

【0048】

この例は、トナー担持体101表面に複数の電極を設け、1本おきの2組を共通にした2相用電極を備え、180[°]位相の異なる2相パルス(図2参照)を印加して、隣接電極同士で吸引と反発を繰り返す2相電界を形成するトナー担持体101の例である。

【0049】

このトナー担持体101は、絶縁性基材101Aの表面上に複数の電極111としてA相用電極111Aと、B相用電極111Bとを設け、その上に表面保護層101Bを設けたものである。櫛歯状の電極111A、111Bは、トナーの搬送方向と直交する方向に微細なピッチに並行に設け、両サイドには共通のバスライン111Aa、111Baで2相パルス発生回路である負荷駆動装置3にそれぞれ接続されている。

【0050】

電極111A、111Bに印加するパルス電圧は、周波数が0.5[kHz]〜7[kHz]、DC電圧をバイアスに含むパルス電圧であるが、その波高値は±60〜±300[V]等、電極幅、電極間隔に応じたパルス電圧を印加する。この2相電界の場合は、隣接同士の電界方向の切り替わりに応じてトナーの反発飛翔と吸引飛翔を繰り返し、トナーは相互の電極間を往復移動する。そして、トナー担持体101全体は、トナーを搬送する方向に回転移動するものである。

【0051】

このように、トナー担持体101表面のトナーを飛翔させてクラウド化する手段が、トナー担持体101表面にトナーの搬送方向と直交する方向に長く延びて所定の間隔で配設された複数の電極を有し、各電極に印加する電圧は隣接電極相互の間でトナーを吸引する方向と反発する方向を交互に繰り返す関係の電圧を印加し、トナー担持体101が回転移動することでトナーの搬送とクラウド化を行う構成とする。これにより、トナー担持体101表面のトナーの搬送に関して、トナーの帯電品質に左右されない安定なトナーの搬送が可能となり、装置全体としても信頼性の高い画像形成装置を実現できる。

【0052】

図13は、カラー画像を形成する画像形成装置のトナー担持体の構成例について説明する図である。

【0053】

カラー画像を形成する画像形成装置で、複数の現像装置を有する場合、2つの現像装置に対して1つの負荷駆動装置3を有する構成にすると、電力や基板配置スペース、コストの観点で最も効率が良い。図13では、カラー画像の4色(Y、M、C、K)のうち、YおよびMにそれぞれ対応する現像装置4Yおよび4Mが負荷駆動装置3aで駆動され、CおよびKにそれぞれ対応する現像装置4Cおよび4Kが負荷駆動装置3bで駆動される例が示されている。

【0054】

なお、クラウド現像では、図2のVminが画像濃度に影響し、Vppがトナーのクラウド性能に影響する。したがってVminとVppとを独立に制御するように構成してもよい。これにより、クラウド性能に影響なく画像濃度の調整が可能となる。また、画像濃度に影響なくクラウド量を調整することが可能となる。なお、VminとVppの独立の制御は、例えば、制御基板2が、Vpp制御信号およびVmin制御信号を独立に出力可能とすることにより実現できる。

【0055】

(第2の実施形態)

複数の現像ローラを用いる場合は、クラウド現像の性能を最適化するためには、各現像ローラに印加する電圧を個別に設定できることが望ましい。しかし、第1の実施形態では、2つの容量性負荷(負荷容量51および負荷容量52)の電圧パルス波高値は共通の値であるVppにしか設定できない。そこで、第2の実施形態では、ダイオードを用いることで、容量性負荷毎に個別の波高値の電圧パルスを印加可能とする。

【0056】

図14は、第2の実施形態の負荷駆動装置3−4の詳細な構成例を示す図である。図14に示すように、負荷駆動装置3−4は、図5のVpp電源10の代わりに、2つの電源であるVpp1電源10−1およびVpp2電源10−2を備えている。また、負荷駆動装置3−4は、ダイオードDY1、DY2、DM1、およびDM2をさらに備えている。

【0057】

Vpp1電源10−1は、Vpp1の電圧値を出力する電源である。Vpp2電源10−2は、Vpp2の電圧値を出力する電源である。

【0058】

負荷容量51は、スイッチ(SW Y1、SW Y3)を介してVpp1電源10−1に接続され、スイッチ(SW Y2、SW Y4)を介してVmin電源20に接続される。また、負荷容量51は、端子側をアノード、電源側をカソードとしてダイオードDY1およびダイオードDY2に接続される。

【0059】

負荷容量52は、スイッチ(SW M1、SW M3)を介してVpp2電源10−2に接続され、スイッチ(SW M2、SW M4)を介してVmin電源20に接続される。また、負荷容量52は、端子側をアノード、電源側をカソードとしてダイオードDM1およびダイオードDM2に接続される。

【0060】

以下、図14の構成の負荷駆動装置の動作を、図6のタイムチャートに従って説明する。なお、図6のタイムチャート自体は、第1の実施形態と変わらない。以下では、本タイムチャートの各期間のうち、端子の電位が変化する期間の当該電位の変化について説明する。

【0061】

(期間f)期間fでは、Vpp1>Vpp2の場合はダイオードDM2が導通し、端子2−Aの電位はVpp2に固定される。Vpp1<Vpp2の場合は端子2−Aの電位はVpp1になる。

(期間h)期間hでは、Vpp1<Vpp2の場合はSW M3をONすることで、端子2−Aの電位がVpp2になる。

(期間i)期間iでは、Vpp1>Vpp2の場合は端子1−Bの電位はVpp2になる。Vpp1<Vpp2の場合はダイオードDY2が導通し、端子1−Bの電位はVpp1に固定される。

(期間k)期間kでは、Vpp1>Vpp2の場合はSW Y3をONすることで、端子1−Bの電位がVpp1になる。

(期間p)期間pでは、Vpp1>Vpp2の場合はダイオードDM1が導通し、端子2−Bの電位はVpp2に固定される。Vpp1<Vpp2の場合は端子1−Bの電位はVpp1になる。

(期間r)期間rでは、Vpp1<Vpp2の場合はSW M1をONすることで、端子2−Bの電位がVpp2になる。

(期間s)期間sでは、Vpp1>Vpp2の場合は端子1−Aの電位はVpp2になる。Vpp1<Vpp2の場合はダイオードDY1が導通し、端子1−Aの電位はVpp1に固定される。

【0062】

期間tの後、SW Y1をONすることで期間aの状態に戻る。Vpp1>Vpp2の場合はSW Y1をONすることで、端子1−Bの電位がVpp1になる。

【0063】

次に、ダイオードの効果について図15〜図20を用いて説明する。図15〜図17は、ダイオードが備えられていない場合の負荷駆動装置の動作を説明するための図である。すなわち、図15〜図17は、図14のような負荷駆動装置からダイオードDY1、DY2、DM1、およびDM2を除いた負荷駆動装置の一例を示している。

【0064】

ダイオードが存在しない場合、共振により端子1−Aに対して充電する前は、図15のように、外部容量53の電位がVpp2となり、端子1−A、1−B、2−Aの電位がVminとなり、端子2−Bの電位がVpp2となる。

【0065】

SW1をONにすることにより共振が発生し、外部容量53から端子1−Aに対してVpp2の充電が開始される(図16)。充電終了後は、図17のように、外部容量53の電位がVminとなり、端子1−B、2−Aの電位がVminとなり、端子1−A、2−Bの電位がVpp2になる。このように、ダイオードが存在しない場合は、端子1−Aを所望の電位であるVpp1に充電することができない。

【0066】

図18〜図20は、ダイオードが備えられている図14のような負荷駆動装置3−4の動作を説明するための図である。

【0067】

図14のようにダイオードが存在する構成では、Vpp1<Vpp2の場合、外部容量53から端子1−AにVpp2が充電されるとき、ダイオードDY1が導通する。そのため端子1−Aの電位はVpp1に固定される(図18)。

【0068】

充電終了後は、図19のように、外部容量53の電位がVminとなり、端子1−B、2−Aの電位がVminとなり、端子1−Aの電位がVpp1となり、端子2−Bの電位がVpp2になる。このようにダイオードが存在する場合は、端子1−Aを所望の電位Vpp1に充電することができる。

【0069】

Vpp1>Vpp2の場合、図17と同様に端子1−AはVpp2となり、所望の電位Vpp1より小さくなる。この後、SW Y1をONすることにより、図20のようにVpp1電源から端子1−Aに充電される。このため、端子1−Aは所望の電位Vpp1になる。

【0070】

以上のように、本実施形態によれば、複数の負荷容量それぞれに対して、所望のパルス電圧波高値を印加することができる。例えばVpp1>Vpp2の時に、負荷容量52には所望の電位Vpp2以上の電荷が充電されるが、ダイオードが存在するため負荷容量52の電位はVpp2以上にはならない。負荷容量51にはVpp2が共振により充電されるため所望の電位Vpp1より低い電圧となる。しかし、充電終了後、Vpp1が負荷容量51に接続され、負荷容量51の電位はVpp1となる。このように、パルス電圧波高値を個別に制御することができる。

【0071】

(変形例4)

第2の実施形態では、Vpp1電源10−1およびVpp2電源10−2の電圧値の大小関係は任意に設定できる。一方、Vpp1電源10−1およびVpp2電源10−2の電圧値の大小関係が固定の場合、ダイオードは、電圧値が低い電源に接続される一方の負荷容量にのみ接続すればよい。例えばVpp1<Vpp2の時、ダイオードDY1およびダイオードDY2のみを備えればよい。図21は、このように構成した変形例4の負荷駆動装置の構成例を示す図である。図21に示すような構成により、部品削減およびコスト削減を実現できる。

【0072】

(変形例5)

変形例5では、変形例3と同様に、第2の実施形態の負荷駆動装置3−4(図14)が、FETへの逆電流を防止するダイオードをさらに備える構成とする。図22は、逆電流防止用ダイオードを有する変形例5の負荷駆動装置の構成例を示す図である。図22に示すように、変形例5の負荷駆動装置は、逆電流防止用のダイオード901〜906を備えている。このような構成により、変形例3と同様に、FETへの逆電流による破壊の防止等の効果が得られる。

【0073】

図23は、第1および第2の実施形態にかかる画像形成装置のハードウェア構成を示すブロック図である。本図に示すように、この画像形成装置は、コントローラ210とエンジン部(Engine)260とをPCI(Peripheral Component Interface)バスで接続した構成となる。コントローラ210は、画像形成装置全体の制御と描画、通信、図示しない操作部からの入力を制御するコントローラであり、例えば制御基板2に相当する。エンジン部260は、PCIバスに接続可能なプリンタエンジンなどであり、たとえば白黒プロッタ、1ドラムカラープロッタ、4ドラムカラープロッタ、スキャナまたはファックスユニットなどである。なお、このエンジン部260には、プロッタなどのいわゆるエンジン部分に加えて、誤差拡散やガンマ変換などの画像処理部分が含まれる。

【0074】

コントローラ210は、CPU211と、ノースブリッジ(NB)213と、システムメモリ(MEM−P)212と、サウスブリッジ(SB)214と、ローカルメモリ(MEM−C)217と、ASIC(Application Specific Integrated Circuit)216と、ハードディスクドライブ(HDD)218とを有し、ノースブリッジ(NB)213とASIC216との間をAGP(Accelerated Graphics Port)バス215で接続した構成となる。また、MEM−P212は、ROM(Read Only Memory)212aと、RAM(Random Access Memory)212bと、をさらに有する。

【0075】

CPU211は、画像形成装置の全体制御をおこなうものであり、NB213、MEM−P212およびSB214からなるチップセットを有し、このチップセットを介して他の機器と接続される。

【0076】

NB213は、CPU211とMEM−P212、SB214、AGPバス215とを接続するためのブリッジであり、MEM−P212に対する読み書きなどを制御するメモリコントローラと、PCIマスタおよびAGPターゲットとを有する。

【0077】

MEM−P212は、プログラムやデータの格納用メモリ、プログラムやデータの展開用メモリ、プリンタの描画用メモリなどとして用いるシステムメモリであり、ROM212aとRAM212bとからなる。ROM212aは、プログラムやデータの格納用メモリとして用いる読み出し専用のメモリであり、RAM212bは、プログラムやデータの展開用メモリ、プリンタの描画用メモリなどとして用いる書き込みおよび読み出し可能なメモリである。

【0078】

SB214は、NB213とPCIデバイス、周辺デバイスとを接続するためのブリッジである。このSB214は、PCIバスを介してNB213と接続されており、このPCIバスには、ネットワークインターフェース(I/F)部なども接続される。

【0079】

ASIC216は、画像処理用のハードウェア要素を有する画像処理用途向けのIC(Integrated Circuit)であり、AGPバス215、PCIバス、HDD218およびMEM−C217をそれぞれ接続するブリッジの役割を有する。このASIC216は、PCIターゲットおよびAGPマスタと、ASIC216の中核をなすアービタ(ARB)と、MEM−C217を制御するメモリコントローラと、ハードウェアロジックなどにより画像データの回転などをおこなう複数のDMAC(Direct Memory Access Controller)と、エンジン部260との間でPCIバスを介したデータ転送をおこなうPCIユニットとからなる。このASIC216には、PCIバスを介してFCU(Facsimile Control Unit)230、USB(Universal Serial Bus)240、IEEE1394(the Institute of Electrical and Electronics Engineers 1394)インターフェース250が接続される。操作表示部220はASIC216に直接接続されている。

【0080】

MEM−C217は、コピー用画像バッファ、符号バッファとして用いるローカルメモリであり、HDD218は、画像データの蓄積、プログラムの蓄積、フォントデータの蓄積、フォームの蓄積を行うためのストレージである。

【0081】

AGPバス215は、グラフィック処理を高速化するために提案されたグラフィックスアクセラレーターカード用のバスインターフェースであり、MEM−P212に高スループットで直接アクセスすることにより、グラフィックスアクセラレーターカードを高速にするものである。

【0082】

なお、第1および第2の実施形態の負荷駆動装置で実行されるプログラムは、ROM等に予め組み込まれて提供される。

【0083】

第1および第2の実施形態の負荷駆動装置で実行されるプログラムは、インストール可能な形式又は実行可能な形式のファイルでCD−ROM、フレキシブルディスク(FD)、CD−R、DVD(Digital Versatile Disk)等のコンピュータで読み取り可能な記録媒体に記録してコンピュータ・プログラム・プロダクトとして提供するように構成してもよい。

【0084】

さらに、第1および第2の実施形態の負荷駆動装置で実行されるプログラムを、インターネット等のネットワークに接続されたコンピュータ上に格納し、ネットワーク経由でダウンロードさせることにより提供するように構成しても良い。また、第1および第2の実施形態の負荷駆動装置で実行されるプログラムをインターネット等のネットワーク経由で提供または配布するように構成しても良い。

【0085】

第1および第2の実施形態の負荷駆動装置で実行されるプログラムは、上述した各部(SW駆動部)を含むモジュール構成となっており、実際のハードウェアとしてはCPU(プロセッサ)が上記ROMからプログラムを読み出して実行することにより上記各部が主記憶装置上にロードされ上記各部が主記憶装置上に生成されるようになっている。

【0086】

なお、画像形成装置としては、コピー機能、プリンタ機能、スキャナ機能およびファクシミリ機能のうち少なくとも2つの機能を有する複合機のほかに、複写機、プリンタ、スキャナ装置、ファクシミリ装置等の画像形成装置であればいずれにも適用することができる。

【符号の説明】

【0087】

1 CPU

2 制御基板

3 負荷駆動装置

4 現像装置

10 Vpp電源

20 Vmin電源

30 SW駆動部

40 出力部

50 ブリッジ回路

51、52 負荷容量

53 外部容量

L1、L2、L3 コイル

60 端子電圧検出回路

70 充電電流検出回路

【先行技術文献】

【特許文献】

【0088】

【特許文献1】特開平11−338418号公報

【技術分野】

【0001】

本発明は、負荷駆動装置、画像形成装置、負荷駆動方法およびプログラムに関する。

【背景技術】

【0002】

画像形成装置でトナーをクラウド化させて現像する方式として、現像ローラの芯金と表面電極に逆位相のパルスを印加する方式が存在する。この方式では、現像ローラの芯金と表面電極は容量性負荷を形成する。

【0003】

このような容量性負荷の両端へのパルスの印加は、プラズマディスプレイなどの分野でも実施されている。容量性負荷を充放電する負荷駆動装置では、消費電力が大きいことが問題となっており、消費電力低減のためにLC共振でエネルギーを遷移させる技術が既に知られている。例えば、特許文献1では、消費電力を低減する目的で、容量性負荷(プラズマディスプレイ表示セル)の両端子に交互に電圧パルスを印加する駆動方式で、容量性負荷を2つのブロックに分割し各ブロックの電圧位相をずらすことで、共振を利用して各ブロックの容量性負荷間で電荷を充放電する技術が提案されている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1の方法では、一方の容量性負荷に電圧が印加されている間、他方の容量性負荷の両端子が等電位である。すなわち、容量性負荷の両端に逆位相の電圧パルスを印加できない。一方、クラウド現像は、容量性負荷の両端に逆位相の電圧パルスを印加することでトナーをクラウド化させるので、特許文献1などの従来の方法を適用できない。

【0005】

本発明は、上記に鑑みてなされたものであって、共振を利用し、かつ、容量性負荷の両端に逆位相の電圧パルスを印加可能とすることにより、消費電力を低減できる負荷駆動装置、画像形成装置、負荷駆動方法およびプログラムを提供することを目的とする。

【課題を解決するための手段】

【0006】

上述した課題を解決し、目的を達成するために、本発明は、第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加する負荷駆動装置であって、容量と、少なくとも1つのコイルと、前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電し、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電し、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電することにより、逆位相の前記パルス電圧を印加する駆動部と、を備えることを特徴とする。

【0007】

また、本発明は、第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加し、容量と少なくとも1つのコイルとを備える負荷駆動装置で実行される負荷駆動方法であって、前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電する第1放電ステップと、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電する第2放電ステップと、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電する第3放電ステップと、を含むことを特徴とする。

【0008】

また、本発明は、第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加し、容量と少なくとも1つのコイルとを備える負荷駆動装置を、前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電し、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電し、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電することにより、逆位相の前記パルス電圧を印加する駆動部、として機能させるためのプログラムである。

【0009】

本発明によれば、共振を利用し、かつ、容量性負荷の両端に逆位相の電圧パルスを印加可能とすることにより、消費電力を低減できるという効果を奏する。

【図面の簡単な説明】

【0010】

【図1】図1は、クラウド現像を行う現像装置を含む画像形成装置の構成例を示すブロック図である。

【図2】図2は、クラウドパルスについて説明する図である。

【図3】図3は、第1の実施形態にかかる負荷駆動装置の構成例を示すブロック図である。

【図4】図4は、ブリッジ回路を説明するための図である。

【図5】図5は、ブリッジ回路の全体を含む、負荷駆動装置の詳細な構成例を示す図である。

【図6】図6は、2つの容量性負荷を駆動する場合の負荷駆動装置の動作例を示すタイムチャートである。

【図7】図7は、変形例1の負荷駆動装置の構成例を示すブロック図である。

【図8】図8は、変形例2の負荷駆動装置の構成例を示すブロック図である。

【図9】図9は、逆電流防止用ダイオードを有する変形例3の負荷駆動装置の構成例を示す図である。

【図10】図10は、現像装置の構成例について説明するための図である。

【図11】図11は、トナー担持体の構成例について説明する図である。

【図12】図12は、トナー担持体の他の構成例について説明する図である。

【図13】図13は、カラー画像を形成する画像形成装置のトナー担持体の構成例について説明する図である。

【図14】図14は、第2の実施形態の負荷駆動装置の詳細な構成例を示す図である。

【図15】図15は、ダイオードが備えられていない場合の負荷駆動装置の動作を説明するための図である。

【図16】図16は、ダイオードが備えられていない場合の負荷駆動装置の動作を説明するための図である。

【図17】図17は、ダイオードが備えられていない場合の負荷駆動装置の動作を説明するための図である。

【図18】図18は、図14のような負荷駆動装置の動作を説明するための図である。

【図19】図19は、図14のような負荷駆動装置の動作を説明するための図である。

【図20】図20は、図14のような負荷駆動装置の動作を説明するための図である。

【図21】図21は、変形例4の負荷駆動装置の構成例を示す図である。

【図22】図22は、変形例5の負荷駆動装置の構成例を示す図である。

【図23】図23は、第1および第2の実施形態にかかる画像形成装置のハードウェア構成を示すブロック図である。

【発明を実施するための形態】

【0011】

以下に添付図面を参照して、この発明にかかる負荷駆動装置、画像形成装置、負荷駆動方法およびプログラムの一実施形態を詳細に説明する。

【0012】

(第1の実施形態)

画像形成装置の現像装置として、トナーをクラウド化して現像する方式の現像装置が知られている。例えば、現像ローラの表面に、現像ローラの回転方向と直交する方向に長く延びて所定の間隔で配設された複数の電極を有し、隣接する電極相互の間、または絶縁層を介して設けた下層の導体基材と電極との間に、逆位相のクラウドパルスを印加することでトナーをクラウド化し、現像ローラが回転移動することでトナーの搬送を行い、感光体にトナーを現像する現像装置が存在する。このような現像装置は、電極と電極との間に絶縁層を介するため容量性負荷を形成する。

【0013】

図1は、このような現像装置を含む画像形成装置の構成例を示すブロック図である。画像形成装置は、制御基板2と、負荷駆動装置3と、クラウド現像を行う現像装置4とを備えている。

【0014】

制御基板2は、画像形成装置の全体を制御し、CPU1を備えている。CPU1は、図示しないROM(Read Only Memory)などのメモリに記憶されたプログラムを読み出して負荷駆動装置3を制御する。

【0015】

現像装置4にクラウドパルスを印加する高圧電源である負荷駆動装置3は、制御基板2から発信される周波数制御信号、Vpp制御信号、およびVmin制御信号によりクラウドパルスを発生する。各信号の制御対象は以下の通りである。

周波数制御信号:クラウドパルスの周波数

Vpp制御信号:クラウドパルスの波高値

Vmin制御信号:クラウドパルスの最低値

【0016】

図2は、クラウドパルスについて説明する図である。図2に示すように、クラウドパルスは、波高値がVppであり、最低値がVminである。クラウドパルスの周波数、Vpp、およびVminは、温湿度環境や画像濃度に応じて最適なクラウドパルスとなるように制御される。以降、説明の簡略化のためクラウドパルスの状態を、波高値をHとし、最低値をLとして説明する。

【0017】

図3は、負荷駆動装置3の構成例を示すブロック図である。負荷駆動装置3は、SW駆動部30と、ブリッジ回路50と、Vpp電源10と、Vmin電源20と、出力部40とを備えている。

【0018】

Vpp電源10は、図2に示すVppの電圧値を出力する電源である。Vmin電源20は、図2に示すVminの電圧値を出力する電源である。パルスの下限値または上限値が接地電位でよい場合、Vmin電源20は不要である。

【0019】

SW駆動部30は、ブリッジ回路50に含まれる各スイッチ(後述)を制御する。これにより、最低値がVminであり、波高値がVppであるクラウドパルスが、ブリッジ回路50から出力部40を介して現像装置4に出力される。スイッチとしては、例えば高耐圧FET(Field Effect Transistor)を用いる。SW駆動部30は、各FETを所定のタイミングでオンおよびオフにする。

【0020】

図4は、ブリッジ回路50を説明するための図である。なお、図4は、説明のためにブリッジ回路50の一部のみを記載している。ブリッジ回路50の全体構成については図5で後述する。

【0021】

ブリッジ回路50は、スイッチとしてSW Y1〜SW Y4と、を含んでいる。なお、負荷容量51は、容量性負荷を形成する図1の現像装置4に相当する。SW Y1〜SW Y4は、図3のSW駆動部30により所定のタイミングでオンおよびオフされる。SW Y1、SW Y4がオン、SW Y3、SW Y2がオフのとき、負荷容量51の左側の端子がHとなり、右側の端子がLになる。SW Y1、SW Y4がオフ、SW Y3、SW Y2がオンのとき、負荷容量51の左側の端子がLとなり、右側の端子がHになる。

【0022】

例えば図1で説明したクラウド現像を行う現像装置4の場合、画像形成装置のステーション数分の容量性負荷(現像装置4)にクラウドパルスを印加する必要がある。画像形成装置のステーションがカラーの4色(Y、M、C、K)に対応する4つの場合、容量性負荷(現像装置4)の数は4つとなる。以下では、2つの容量性負荷(現像装置4)を備える場合を例に説明する。

【0023】

図5は、ブリッジ回路50の全体を含む、負荷駆動装置3の詳細な構成例を示す図である。図5に示すように、負荷駆動装置3は、図3に示すVpp電源10、Vmin電源20のほかに、外部容量53と、コイル(インダクタ)L1〜L3とを備えている。外部容量53は、電荷充電のために、負荷容量51および52とは別に設けた容量である。なお、負荷容量51および52は、2つの容量性負荷(現像装置4)に相当する。

【0024】

負荷容量51は、スイッチ(SW Y1、SW Y3)を介してVpp電源10に接続され、スイッチ(SW Y2、SW Y4)を介してVmin電源20に接続される。負荷容量52は、スイッチ(SW M1、SW M3)を介してVpp電源10に接続され、スイッチ(SW M2、SW M4)を介してVmin電源20に接続される。

【0025】

負荷容量51の端子1−A、1−B、および、負荷容量52の端子2−A、2−Bは、スイッチ(SW1、SW2、SW3、SW4)と、コイルL1を介して外部容量53に接続される。端子1−Aは、端子2−Aとスイッチ(SW6)とコイルL3を介して接続される。端子1−Bは、端子2−Bとスイッチ(SW5)とコイルL2を介して接続される。

【0026】

図5の各スイッチ(SW1〜SW6、SW Y1〜SW Y4、SW M1〜SW M4)は、SW駆動部30でオンおよびオフが制御される。

【0027】

図6は、2つの容量性負荷を駆動する場合の負荷駆動装置3の動作例を示すタイムチャートである。図6の「1−A」、「1−B」、「2−A」、および「2−B」は、それぞれ端子1−A、端子1−B、端子2−A、および端子2−Bの電位を表す。また、「C」は、外部容量53の電位を表す。Hのときの電位が図2のVmin+Vppであり、Lのときの電位がVminである。SW Y1〜SW Y4、SW M1〜SW M4、およびSW1〜SW6は、Hがスイッチオンを表し、Lがスイッチオフを表す。

【0028】

以下、図5の構成の負荷駆動装置3の動作を、図6のタイムチャートに従って説明する。

【0029】

(期間a)SW Y1、SW Y4、SW M1、SW M4がオンの状態で、1−AがH、1−BがL、2−AがL、2−BがHである。

(期間b)SW M1をオフにする。この期間はSW M1とSW3が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間c)SW3をオンにする。負荷容量52とコイルL1、外部容量53との間でLC共振が発生し、電荷が端子2−Bから外部容量53に移動する。電荷が全て移動後、SW3をオフにする。

(期間d)SW3をオフにする。この期間はSW3とSW M2が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間e)SW Y1をオフ、SW M2をオン、SW M4をオフにする。この期間はSW Y1とSW6が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間f)SW6をオンにする。負荷容量51とコイルL3、負荷容量52との間でLC共振が発生し、電荷が端子1−Aから端子2−Aに移動する。電荷が全て移動後SW3をオフにする。

(期間g)SW6をオフにする。この期間はSW6とSW M3が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間h)SW Y2をオン、SW Y4をオフ、SW M3をオンにする。この期間はSW Y4とSW2が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。またSW M3をオンにすることで、充電経路中の電力ロスにより端子2−Aの電圧がVmin+Vppに達しない場合でも、Vmin+Vppとすることができる。

(期間i)SW2をオンにする。負荷容量51とコイルL1、外部容量53との間でLC共振が発生し、電荷が外部容量53から端子1−Bに移動する。電荷が全て移動後SW2をオフにする。

(期間j)SW2をオフにする。この期間はSW2とSW Y3が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間k)SW Y3をオンにする。この期間は1−AがL、1−BがH、2−AがH、2−BがLとなっており、期間aと逆のパルス状態となる。

(期間l)SW M3をオフにする。この期間は1μsほどの時間でよい。

(期間m)SW4をオンにする。負荷容量52とコイルL1、外部容量53との間でLC共振が発生し、電荷が端子2−Aから外部容量53に移動する。電荷が全て移動後SW5をオフにする。

(期間n)SW4をオフにする。この期間はSW4とSW M4が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間o)SW Y3をオフ、SW M2をオフ、SW M4をオンにする。この期間はSW Y3とSW5が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間p)SW5をオンにする。負荷容量51とコイルL2、負荷容量52との間でLC共振が発生し、電荷が端子1−Bから端子2−Bに移動する。電荷が全て移動後SW5をオフにする。

(期間q)SW5をオフにする。この期間はSW5とSW M1が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間r)SW Y2をオフ、SW Y4をオン、SW M1をオンにする。この期間はSW Y2とSW1が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

(期間s)SW1をオンにする。負荷容量51とコイルL1、外部容量53との間でLC共振が発生し、電荷が外部容量53から端子1−Aに移動する。電荷が全て移動後SW1をオフにする。

(期間t)SW1をオフにする。この期間はSW1とSW Y1が同時にオンになるのを防ぐための期間であり、1μsほどの時間でよい。

【0030】

次にSW Y1をオンにすることで期間aの状態に戻る。そして、期間a〜期間tを繰り返すことで、負荷容量51および負荷容量52の両端子に逆位相のパルス波形を印加することができる。

【0031】

このように、本実施形態の負荷駆動装置3では、端子1−A、端子1−B、端子2−A、端子2−Bを端子毎のスイッチと共通のコイルとで外部容量53に接続し、端子1−Aと端子2−Aをコイルとスイッチで接続し、端子1−Bと端子2−Bをコイルとスイッチで接続することにより、端子2−Aから外部容量53へ放電終了後、端子1−Bから端子2−Bへ放電し、放電終了後、外部容量53から端子1−Aに放電することができる。これにより、共振を利用した低消費電力化を実現できる。また、上記のようにスイッチを制御することにより、容量性負荷の両端に逆位相の電圧パルスを印加できる。

【0032】

(変形例1)

図7は、変形例1の負荷駆動装置3−2の構成例を示すブロック図である。負荷駆動装置3−2は、SW駆動部30−2と、ブリッジ回路50と、Vpp電源10と、Vmin電源20と、出力部40と、端子電圧検出回路60とを備えている。負荷駆動装置3−2は、端子電圧検出回路60を備えること、および、SW駆動部30−2の機能が、図3の負荷駆動装置3と異なっている。

【0033】

端子電圧検出回路60は、負荷容量51、負荷容量52、および、外部容量53の端子電圧を検出する回路である。

【0034】

充放電用のスイッチSW1〜SW6は、充放電が完全に終了した瞬間にオフにするのが最も電力効率がよい。そこで、変形例1の負荷駆動装置3−2は、各負荷容量の端子の電圧を検知する端子電圧検出回路60をさらに備え、端子電圧が所定の電圧になったときに、端子電圧検出回路60からSW駆動部30−2に充放電終了信号を発信する。所定の電圧とは例えばVmin+Vpp、またはVminである。

【0035】

SW駆動部30−2は、充放電終了信号を受信したときに、スイッチSW1〜SW6をオフにする。これにより、電力効率を向上させることができる。

【0036】

(変形例2)

図8は、変形例2の負荷駆動装置3−3の構成例を示すブロック図である。負荷駆動装置3−3は、SW駆動部30−3と、ブリッジ回路50と、Vpp電源10と、Vmin電源20と、出力部40と、充電電流検出回路70とを備えている。負荷駆動装置3−3は、充電電流検出回路70を備えること、および、SW駆動部30−3の機能が、図3の負荷駆動装置3と異なっている。

【0037】

充電電流検出回路70は、充放電用コイル(コイルL1〜L3)へ流れる電流を検出する回路である。

【0038】

充放電用コイルへ流れる電流は時間に対して正弦波となり、電流が略0となる時が充放電終了である。そのため充放電用コイルへ流れる電流を検知する充電電流検出回路70をさらに備え、電流が0になるときに、充電電流検出回路70からSW駆動部30−3に充放電終了信号を発信する。

【0039】

SW駆動部30−3は、充放電終了信号を受信したときに、スイッチSW1〜SW6をオフにする。これにより、電力効率を向上させることができる。

【0040】

(変形例3)

各スイッチのオンおよびオフは、SW駆動部30によって制御され、そのタイミングはSW駆動部30の定数によって決まる。回路定数にはバラツキが生じるため、スイッチのオンおよびオフのタイミングは狙いのタイミングからずれる可能性がある。

【0041】

例えば期間cにSW3をオンして2−Bから外部容量53に放電する場合、SW3をオフにするタイミングが遅れ、放電終了後もSW3がオンしたままの状態とすると、共振により放電とは逆方向、すなわち、外部容量53から2−Bに電流が流れる。スイッチには主にFETが用いられるため、逆方向に電流を流すと破壊等の不具合が発生する。またSW3をオフにするタイミングが早くなり、放電終了前にSW3をオフにするとコイルL1に逆起電圧が発生し、FETが破壊される。

【0042】

そこで、変形例3では、FETへの逆電流を防止するダイオードをさらに備える構成とする。図9は、逆電流防止用ダイオードを有する変形例3の負荷駆動装置の構成例を示す図である。図9に示すように、変形例3の負荷駆動装置は、逆電流防止用のダイオード901〜906を備えている。

【0043】

このような構成により、FETへの逆電流による破壊を防ぐことができる。また、逆電流が発生しないので、充放電に必要な時間より十分に長い時間、SW1〜SW6をオンにすることができ、放電終了前にスイッチをオフにすることによる逆起電圧の発生、および、FETの破壊を防止することができる。

【0044】

次に、画像形成装置の現像装置4の構成例について説明する。図10は、現像装置4の構成例について説明するための図である。図10に示すように、現像装置4は、現像剤であるトナーを担持するトナー担持体101と、例えば有機感光体(OPC)などの感光体102とを備えている。

【0045】

負荷駆動装置3がクラウドパルスをトナー担持体101に印加することで、トナーをクラウド状態にし、感光体102にトナーを現像させることができる。

【0046】

図11は、トナー担持体101の構成例について説明する図である。トナー担持体101は、その表面に、トナーの搬送方向と直交する方向に長く延びて所定の間隔で配設された複数の電極1101を有する。絶縁層1103を介して設けた下層の電極である導体基材1102と電極1101との間に逆位相のクラウドパルスを印加することでトナーをクラウド化することができる。下層の導体基材1102と電極1101とが容量性負荷を形成する。

【0047】

図12は、トナー担持体101の他の構成例について説明する図である。なお、図12(a)はトナー担持体101を展開した状態で示す模式的平面説明図、図12(b)は同じく模式的断面説明図である。

【0048】

この例は、トナー担持体101表面に複数の電極を設け、1本おきの2組を共通にした2相用電極を備え、180[°]位相の異なる2相パルス(図2参照)を印加して、隣接電極同士で吸引と反発を繰り返す2相電界を形成するトナー担持体101の例である。

【0049】

このトナー担持体101は、絶縁性基材101Aの表面上に複数の電極111としてA相用電極111Aと、B相用電極111Bとを設け、その上に表面保護層101Bを設けたものである。櫛歯状の電極111A、111Bは、トナーの搬送方向と直交する方向に微細なピッチに並行に設け、両サイドには共通のバスライン111Aa、111Baで2相パルス発生回路である負荷駆動装置3にそれぞれ接続されている。

【0050】

電極111A、111Bに印加するパルス電圧は、周波数が0.5[kHz]〜7[kHz]、DC電圧をバイアスに含むパルス電圧であるが、その波高値は±60〜±300[V]等、電極幅、電極間隔に応じたパルス電圧を印加する。この2相電界の場合は、隣接同士の電界方向の切り替わりに応じてトナーの反発飛翔と吸引飛翔を繰り返し、トナーは相互の電極間を往復移動する。そして、トナー担持体101全体は、トナーを搬送する方向に回転移動するものである。

【0051】

このように、トナー担持体101表面のトナーを飛翔させてクラウド化する手段が、トナー担持体101表面にトナーの搬送方向と直交する方向に長く延びて所定の間隔で配設された複数の電極を有し、各電極に印加する電圧は隣接電極相互の間でトナーを吸引する方向と反発する方向を交互に繰り返す関係の電圧を印加し、トナー担持体101が回転移動することでトナーの搬送とクラウド化を行う構成とする。これにより、トナー担持体101表面のトナーの搬送に関して、トナーの帯電品質に左右されない安定なトナーの搬送が可能となり、装置全体としても信頼性の高い画像形成装置を実現できる。

【0052】

図13は、カラー画像を形成する画像形成装置のトナー担持体の構成例について説明する図である。

【0053】

カラー画像を形成する画像形成装置で、複数の現像装置を有する場合、2つの現像装置に対して1つの負荷駆動装置3を有する構成にすると、電力や基板配置スペース、コストの観点で最も効率が良い。図13では、カラー画像の4色(Y、M、C、K)のうち、YおよびMにそれぞれ対応する現像装置4Yおよび4Mが負荷駆動装置3aで駆動され、CおよびKにそれぞれ対応する現像装置4Cおよび4Kが負荷駆動装置3bで駆動される例が示されている。

【0054】

なお、クラウド現像では、図2のVminが画像濃度に影響し、Vppがトナーのクラウド性能に影響する。したがってVminとVppとを独立に制御するように構成してもよい。これにより、クラウド性能に影響なく画像濃度の調整が可能となる。また、画像濃度に影響なくクラウド量を調整することが可能となる。なお、VminとVppの独立の制御は、例えば、制御基板2が、Vpp制御信号およびVmin制御信号を独立に出力可能とすることにより実現できる。

【0055】

(第2の実施形態)

複数の現像ローラを用いる場合は、クラウド現像の性能を最適化するためには、各現像ローラに印加する電圧を個別に設定できることが望ましい。しかし、第1の実施形態では、2つの容量性負荷(負荷容量51および負荷容量52)の電圧パルス波高値は共通の値であるVppにしか設定できない。そこで、第2の実施形態では、ダイオードを用いることで、容量性負荷毎に個別の波高値の電圧パルスを印加可能とする。

【0056】

図14は、第2の実施形態の負荷駆動装置3−4の詳細な構成例を示す図である。図14に示すように、負荷駆動装置3−4は、図5のVpp電源10の代わりに、2つの電源であるVpp1電源10−1およびVpp2電源10−2を備えている。また、負荷駆動装置3−4は、ダイオードDY1、DY2、DM1、およびDM2をさらに備えている。

【0057】

Vpp1電源10−1は、Vpp1の電圧値を出力する電源である。Vpp2電源10−2は、Vpp2の電圧値を出力する電源である。

【0058】

負荷容量51は、スイッチ(SW Y1、SW Y3)を介してVpp1電源10−1に接続され、スイッチ(SW Y2、SW Y4)を介してVmin電源20に接続される。また、負荷容量51は、端子側をアノード、電源側をカソードとしてダイオードDY1およびダイオードDY2に接続される。

【0059】

負荷容量52は、スイッチ(SW M1、SW M3)を介してVpp2電源10−2に接続され、スイッチ(SW M2、SW M4)を介してVmin電源20に接続される。また、負荷容量52は、端子側をアノード、電源側をカソードとしてダイオードDM1およびダイオードDM2に接続される。

【0060】

以下、図14の構成の負荷駆動装置の動作を、図6のタイムチャートに従って説明する。なお、図6のタイムチャート自体は、第1の実施形態と変わらない。以下では、本タイムチャートの各期間のうち、端子の電位が変化する期間の当該電位の変化について説明する。

【0061】

(期間f)期間fでは、Vpp1>Vpp2の場合はダイオードDM2が導通し、端子2−Aの電位はVpp2に固定される。Vpp1<Vpp2の場合は端子2−Aの電位はVpp1になる。

(期間h)期間hでは、Vpp1<Vpp2の場合はSW M3をONすることで、端子2−Aの電位がVpp2になる。

(期間i)期間iでは、Vpp1>Vpp2の場合は端子1−Bの電位はVpp2になる。Vpp1<Vpp2の場合はダイオードDY2が導通し、端子1−Bの電位はVpp1に固定される。

(期間k)期間kでは、Vpp1>Vpp2の場合はSW Y3をONすることで、端子1−Bの電位がVpp1になる。

(期間p)期間pでは、Vpp1>Vpp2の場合はダイオードDM1が導通し、端子2−Bの電位はVpp2に固定される。Vpp1<Vpp2の場合は端子1−Bの電位はVpp1になる。

(期間r)期間rでは、Vpp1<Vpp2の場合はSW M1をONすることで、端子2−Bの電位がVpp2になる。

(期間s)期間sでは、Vpp1>Vpp2の場合は端子1−Aの電位はVpp2になる。Vpp1<Vpp2の場合はダイオードDY1が導通し、端子1−Aの電位はVpp1に固定される。

【0062】

期間tの後、SW Y1をONすることで期間aの状態に戻る。Vpp1>Vpp2の場合はSW Y1をONすることで、端子1−Bの電位がVpp1になる。

【0063】

次に、ダイオードの効果について図15〜図20を用いて説明する。図15〜図17は、ダイオードが備えられていない場合の負荷駆動装置の動作を説明するための図である。すなわち、図15〜図17は、図14のような負荷駆動装置からダイオードDY1、DY2、DM1、およびDM2を除いた負荷駆動装置の一例を示している。

【0064】

ダイオードが存在しない場合、共振により端子1−Aに対して充電する前は、図15のように、外部容量53の電位がVpp2となり、端子1−A、1−B、2−Aの電位がVminとなり、端子2−Bの電位がVpp2となる。

【0065】

SW1をONにすることにより共振が発生し、外部容量53から端子1−Aに対してVpp2の充電が開始される(図16)。充電終了後は、図17のように、外部容量53の電位がVminとなり、端子1−B、2−Aの電位がVminとなり、端子1−A、2−Bの電位がVpp2になる。このように、ダイオードが存在しない場合は、端子1−Aを所望の電位であるVpp1に充電することができない。

【0066】

図18〜図20は、ダイオードが備えられている図14のような負荷駆動装置3−4の動作を説明するための図である。

【0067】

図14のようにダイオードが存在する構成では、Vpp1<Vpp2の場合、外部容量53から端子1−AにVpp2が充電されるとき、ダイオードDY1が導通する。そのため端子1−Aの電位はVpp1に固定される(図18)。

【0068】

充電終了後は、図19のように、外部容量53の電位がVminとなり、端子1−B、2−Aの電位がVminとなり、端子1−Aの電位がVpp1となり、端子2−Bの電位がVpp2になる。このようにダイオードが存在する場合は、端子1−Aを所望の電位Vpp1に充電することができる。

【0069】

Vpp1>Vpp2の場合、図17と同様に端子1−AはVpp2となり、所望の電位Vpp1より小さくなる。この後、SW Y1をONすることにより、図20のようにVpp1電源から端子1−Aに充電される。このため、端子1−Aは所望の電位Vpp1になる。

【0070】

以上のように、本実施形態によれば、複数の負荷容量それぞれに対して、所望のパルス電圧波高値を印加することができる。例えばVpp1>Vpp2の時に、負荷容量52には所望の電位Vpp2以上の電荷が充電されるが、ダイオードが存在するため負荷容量52の電位はVpp2以上にはならない。負荷容量51にはVpp2が共振により充電されるため所望の電位Vpp1より低い電圧となる。しかし、充電終了後、Vpp1が負荷容量51に接続され、負荷容量51の電位はVpp1となる。このように、パルス電圧波高値を個別に制御することができる。

【0071】

(変形例4)

第2の実施形態では、Vpp1電源10−1およびVpp2電源10−2の電圧値の大小関係は任意に設定できる。一方、Vpp1電源10−1およびVpp2電源10−2の電圧値の大小関係が固定の場合、ダイオードは、電圧値が低い電源に接続される一方の負荷容量にのみ接続すればよい。例えばVpp1<Vpp2の時、ダイオードDY1およびダイオードDY2のみを備えればよい。図21は、このように構成した変形例4の負荷駆動装置の構成例を示す図である。図21に示すような構成により、部品削減およびコスト削減を実現できる。

【0072】

(変形例5)

変形例5では、変形例3と同様に、第2の実施形態の負荷駆動装置3−4(図14)が、FETへの逆電流を防止するダイオードをさらに備える構成とする。図22は、逆電流防止用ダイオードを有する変形例5の負荷駆動装置の構成例を示す図である。図22に示すように、変形例5の負荷駆動装置は、逆電流防止用のダイオード901〜906を備えている。このような構成により、変形例3と同様に、FETへの逆電流による破壊の防止等の効果が得られる。

【0073】

図23は、第1および第2の実施形態にかかる画像形成装置のハードウェア構成を示すブロック図である。本図に示すように、この画像形成装置は、コントローラ210とエンジン部(Engine)260とをPCI(Peripheral Component Interface)バスで接続した構成となる。コントローラ210は、画像形成装置全体の制御と描画、通信、図示しない操作部からの入力を制御するコントローラであり、例えば制御基板2に相当する。エンジン部260は、PCIバスに接続可能なプリンタエンジンなどであり、たとえば白黒プロッタ、1ドラムカラープロッタ、4ドラムカラープロッタ、スキャナまたはファックスユニットなどである。なお、このエンジン部260には、プロッタなどのいわゆるエンジン部分に加えて、誤差拡散やガンマ変換などの画像処理部分が含まれる。

【0074】

コントローラ210は、CPU211と、ノースブリッジ(NB)213と、システムメモリ(MEM−P)212と、サウスブリッジ(SB)214と、ローカルメモリ(MEM−C)217と、ASIC(Application Specific Integrated Circuit)216と、ハードディスクドライブ(HDD)218とを有し、ノースブリッジ(NB)213とASIC216との間をAGP(Accelerated Graphics Port)バス215で接続した構成となる。また、MEM−P212は、ROM(Read Only Memory)212aと、RAM(Random Access Memory)212bと、をさらに有する。

【0075】

CPU211は、画像形成装置の全体制御をおこなうものであり、NB213、MEM−P212およびSB214からなるチップセットを有し、このチップセットを介して他の機器と接続される。

【0076】

NB213は、CPU211とMEM−P212、SB214、AGPバス215とを接続するためのブリッジであり、MEM−P212に対する読み書きなどを制御するメモリコントローラと、PCIマスタおよびAGPターゲットとを有する。

【0077】

MEM−P212は、プログラムやデータの格納用メモリ、プログラムやデータの展開用メモリ、プリンタの描画用メモリなどとして用いるシステムメモリであり、ROM212aとRAM212bとからなる。ROM212aは、プログラムやデータの格納用メモリとして用いる読み出し専用のメモリであり、RAM212bは、プログラムやデータの展開用メモリ、プリンタの描画用メモリなどとして用いる書き込みおよび読み出し可能なメモリである。

【0078】

SB214は、NB213とPCIデバイス、周辺デバイスとを接続するためのブリッジである。このSB214は、PCIバスを介してNB213と接続されており、このPCIバスには、ネットワークインターフェース(I/F)部なども接続される。

【0079】

ASIC216は、画像処理用のハードウェア要素を有する画像処理用途向けのIC(Integrated Circuit)であり、AGPバス215、PCIバス、HDD218およびMEM−C217をそれぞれ接続するブリッジの役割を有する。このASIC216は、PCIターゲットおよびAGPマスタと、ASIC216の中核をなすアービタ(ARB)と、MEM−C217を制御するメモリコントローラと、ハードウェアロジックなどにより画像データの回転などをおこなう複数のDMAC(Direct Memory Access Controller)と、エンジン部260との間でPCIバスを介したデータ転送をおこなうPCIユニットとからなる。このASIC216には、PCIバスを介してFCU(Facsimile Control Unit)230、USB(Universal Serial Bus)240、IEEE1394(the Institute of Electrical and Electronics Engineers 1394)インターフェース250が接続される。操作表示部220はASIC216に直接接続されている。

【0080】

MEM−C217は、コピー用画像バッファ、符号バッファとして用いるローカルメモリであり、HDD218は、画像データの蓄積、プログラムの蓄積、フォントデータの蓄積、フォームの蓄積を行うためのストレージである。

【0081】

AGPバス215は、グラフィック処理を高速化するために提案されたグラフィックスアクセラレーターカード用のバスインターフェースであり、MEM−P212に高スループットで直接アクセスすることにより、グラフィックスアクセラレーターカードを高速にするものである。

【0082】

なお、第1および第2の実施形態の負荷駆動装置で実行されるプログラムは、ROM等に予め組み込まれて提供される。

【0083】

第1および第2の実施形態の負荷駆動装置で実行されるプログラムは、インストール可能な形式又は実行可能な形式のファイルでCD−ROM、フレキシブルディスク(FD)、CD−R、DVD(Digital Versatile Disk)等のコンピュータで読み取り可能な記録媒体に記録してコンピュータ・プログラム・プロダクトとして提供するように構成してもよい。

【0084】

さらに、第1および第2の実施形態の負荷駆動装置で実行されるプログラムを、インターネット等のネットワークに接続されたコンピュータ上に格納し、ネットワーク経由でダウンロードさせることにより提供するように構成しても良い。また、第1および第2の実施形態の負荷駆動装置で実行されるプログラムをインターネット等のネットワーク経由で提供または配布するように構成しても良い。

【0085】

第1および第2の実施形態の負荷駆動装置で実行されるプログラムは、上述した各部(SW駆動部)を含むモジュール構成となっており、実際のハードウェアとしてはCPU(プロセッサ)が上記ROMからプログラムを読み出して実行することにより上記各部が主記憶装置上にロードされ上記各部が主記憶装置上に生成されるようになっている。

【0086】

なお、画像形成装置としては、コピー機能、プリンタ機能、スキャナ機能およびファクシミリ機能のうち少なくとも2つの機能を有する複合機のほかに、複写機、プリンタ、スキャナ装置、ファクシミリ装置等の画像形成装置であればいずれにも適用することができる。

【符号の説明】

【0087】

1 CPU

2 制御基板

3 負荷駆動装置

4 現像装置

10 Vpp電源

20 Vmin電源

30 SW駆動部

40 出力部

50 ブリッジ回路

51、52 負荷容量

53 外部容量

L1、L2、L3 コイル

60 端子電圧検出回路

70 充電電流検出回路

【先行技術文献】

【特許文献】

【0088】

【特許文献1】特開平11−338418号公報

【特許請求の範囲】

【請求項1】

第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加する負荷駆動装置であって、

容量と、

少なくとも1つのコイルと、

前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電し、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電し、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電することにより、逆位相の前記パルス電圧を印加する駆動部と、

を備えることを特徴とする負荷駆動装置。

【請求項2】

前記第1容量性負荷に第1電圧値を出力する第1電源と、

前記第2容量性負荷に第2電圧値を出力する第2電源と、

前記第1電極側にアノードが接続され前記第1電源側にカソードが接続され第1ダイオードと、

前記第2電極側にアノードが接続され前記第1電源側にカソードが接続された第2ダイオードと、をさらに備えること、

を特徴とする請求項1に記載の負荷駆動装置。

【請求項3】

前記第3電極側にアノードが接続され前記第2電源側にカソードが接続され第3ダイオードと、

前記第4電極側にアノードが接続され前記第2電源側にカソードが接続された第4ダイオードと、をさらに備えること、

を特徴とする請求項2に記載の負荷駆動装置。

【請求項4】

前記第1容量性負荷、前記第2容量性負荷、および、前記容量の電圧を検出する電圧検出部をさらに備え、

前記駆動部は、検出された電圧が予め定められた規定電圧値に達したときに放電が完了したと判定すること、

を特徴とする請求項1に記載の負荷駆動装置。

【請求項5】

前記コイルの電流を検出する電流検出部をさらに備え、

前記駆動部は、検出された電流が予め定められた規定電流値に達したときに放電が完了したと判定すること、

を特徴とする請求項1に記載の負荷駆動装置。

【請求項6】

前記容量側にアノードが接続され前記第1容量性負荷側にカソードが接続されたダイオード、前記第2容量性負荷側にアノードが接続され前記容量側にカソードが接続されたダイオード、および、前記第1容量性負荷側にアノードが接続され前記第2容量性負荷側にカソードが接続されたダイオード、の少なくとも1つをさらに備えること、

を特徴とする請求項1に記載の負荷駆動装置。

【請求項7】

請求項1〜6のいずれか1つに記載の負荷駆動装置と、

現像剤を担持する現像剤担持体である前記第1容量性負荷および前記第2容量性負荷と、

前記負荷駆動装置が前記現像剤担持体に印加したパルス電圧によってクラウド化された前記現像剤により、像担持体に形成された潜像を現像する現像装置と、

を備えることを特徴とする画像形成装置。

【請求項8】

前記第1電極は、前記第1容量性負荷である前記現像剤担持体の表面に設けられ、

前記第2電極は、前記第1電極より下層に絶縁層を介して設けられ、

前記第3電極は、前記第2容量性負荷である前記現像剤担持体の表面に設けられ、

前記第4電極は、前記第3電極より下層に絶縁層を介して設けられること、

を特徴とする請求項7に記載の画像形成装置。

【請求項9】

前記第1電極および前記第2電極は、前記第1容量性負荷である前記現像剤担持体の表面に設けられ、

前記第3電極および前記第4電極は、前記第2容量性負荷である前記現像剤担持体の表面に設けられること、

を特徴とする請求項7に記載の画像形成装置。

【請求項10】

前記駆動部は、指定された最低値の前記パルス電圧を印加すること、

を特徴とする請求項7に記載の画像形成装置。

【請求項11】

前記駆動部は、指定された波高値の前記パルス電圧を印加すること、

を特徴とする請求項7に記載の画像形成装置。

【請求項12】

第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加し、容量と少なくとも1つのコイルとを備える負荷駆動装置で実行される負荷駆動方法であって、

前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電する第1放電ステップと、

前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電する第2放電ステップと、

前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電する第3放電ステップと、

を含むことを特徴とする負荷駆動方法。

【請求項13】

第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加し、容量と少なくとも1つのコイルとを備える負荷駆動装置を、

前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電し、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電し、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電することにより、逆位相の前記パルス電圧を印加する駆動部、

として機能させるためのプログラム。

【請求項1】

第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加する負荷駆動装置であって、

容量と、

少なくとも1つのコイルと、

前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電し、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電し、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電することにより、逆位相の前記パルス電圧を印加する駆動部と、

を備えることを特徴とする負荷駆動装置。

【請求項2】

前記第1容量性負荷に第1電圧値を出力する第1電源と、

前記第2容量性負荷に第2電圧値を出力する第2電源と、

前記第1電極側にアノードが接続され前記第1電源側にカソードが接続され第1ダイオードと、

前記第2電極側にアノードが接続され前記第1電源側にカソードが接続された第2ダイオードと、をさらに備えること、

を特徴とする請求項1に記載の負荷駆動装置。

【請求項3】

前記第3電極側にアノードが接続され前記第2電源側にカソードが接続され第3ダイオードと、

前記第4電極側にアノードが接続され前記第2電源側にカソードが接続された第4ダイオードと、をさらに備えること、

を特徴とする請求項2に記載の負荷駆動装置。

【請求項4】

前記第1容量性負荷、前記第2容量性負荷、および、前記容量の電圧を検出する電圧検出部をさらに備え、

前記駆動部は、検出された電圧が予め定められた規定電圧値に達したときに放電が完了したと判定すること、

を特徴とする請求項1に記載の負荷駆動装置。

【請求項5】

前記コイルの電流を検出する電流検出部をさらに備え、

前記駆動部は、検出された電流が予め定められた規定電流値に達したときに放電が完了したと判定すること、

を特徴とする請求項1に記載の負荷駆動装置。

【請求項6】

前記容量側にアノードが接続され前記第1容量性負荷側にカソードが接続されたダイオード、前記第2容量性負荷側にアノードが接続され前記容量側にカソードが接続されたダイオード、および、前記第1容量性負荷側にアノードが接続され前記第2容量性負荷側にカソードが接続されたダイオード、の少なくとも1つをさらに備えること、

を特徴とする請求項1に記載の負荷駆動装置。

【請求項7】

請求項1〜6のいずれか1つに記載の負荷駆動装置と、

現像剤を担持する現像剤担持体である前記第1容量性負荷および前記第2容量性負荷と、

前記負荷駆動装置が前記現像剤担持体に印加したパルス電圧によってクラウド化された前記現像剤により、像担持体に形成された潜像を現像する現像装置と、

を備えることを特徴とする画像形成装置。

【請求項8】

前記第1電極は、前記第1容量性負荷である前記現像剤担持体の表面に設けられ、

前記第2電極は、前記第1電極より下層に絶縁層を介して設けられ、

前記第3電極は、前記第2容量性負荷である前記現像剤担持体の表面に設けられ、

前記第4電極は、前記第3電極より下層に絶縁層を介して設けられること、

を特徴とする請求項7に記載の画像形成装置。

【請求項9】

前記第1電極および前記第2電極は、前記第1容量性負荷である前記現像剤担持体の表面に設けられ、

前記第3電極および前記第4電極は、前記第2容量性負荷である前記現像剤担持体の表面に設けられること、

を特徴とする請求項7に記載の画像形成装置。

【請求項10】

前記駆動部は、指定された最低値の前記パルス電圧を印加すること、

を特徴とする請求項7に記載の画像形成装置。

【請求項11】

前記駆動部は、指定された波高値の前記パルス電圧を印加すること、

を特徴とする請求項7に記載の画像形成装置。

【請求項12】

第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加し、容量と少なくとも1つのコイルとを備える負荷駆動装置で実行される負荷駆動方法であって、

前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電する第1放電ステップと、

前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電する第2放電ステップと、

前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電する第3放電ステップと、

を含むことを特徴とする負荷駆動方法。

【請求項13】

第1電極および第2電極で構成される第1容量性負荷と、第3電極および第4電極で構成される第2容量性負荷とにパルス電圧を印加し、容量と少なくとも1つのコイルとを備える負荷駆動装置を、

前記第2容量性負荷と前記容量と前記コイルとを接続して前記第3電極から前記容量に電荷を放電し、前記容量への放電完了後に前記第1容量性負荷と前記第2容量性負荷と前記コイルとを接続して前記第1電極から前記第4電極に電荷を放電し、前記第4電極への放電完了後に前記第1容量性負荷と前記容量と前記コイルとを接続して前記容量から前記第2電極に電荷を放電することにより、逆位相の前記パルス電圧を印加する駆動部、

として機能させるためのプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2012−44648(P2012−44648A)

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願番号】特願2011−143544(P2011−143544)

【出願日】平成23年6月28日(2011.6.28)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願日】平成23年6月28日(2011.6.28)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]