負荷駆動装置及び負荷駆動制御装置

【課題】パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能な負荷駆動装置、及び該負荷駆動装置を備える負荷駆動制御装置を提供する。

【解決手段】電源ラインBL側と接地電位との間に直列に接続されたコンデンサC1及び抵抗R1からなる微分器が電源ラインBLの電圧の立ち上がりを微分した微分電圧に基づいて、入力端子221,231を電源ラインBLに夫々プルアップする抵抗R4,R14の入力端子221,231側と接地電位との間にダイオードD3,D13を介して接続されたFETQ1が、少なくとも入力端子221,231に入出力ポート35,36より負荷L1,L2を駆動するための信号を与えられるまで導通する。

【解決手段】電源ラインBL側と接地電位との間に直列に接続されたコンデンサC1及び抵抗R1からなる微分器が電源ラインBLの電圧の立ち上がりを微分した微分電圧に基づいて、入力端子221,231を電源ラインBLに夫々プルアップする抵抗R4,R14の入力端子221,231側と接地電位との間にダイオードD3,D13を介して接続されたFETQ1が、少なくとも入力端子221,231に入出力ポート35,36より負荷L1,L2を駆動するための信号を与えられるまで導通する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路リセットの場合に負荷を駆動するための信号が絶たれる負荷駆動装置、及び該負荷駆動装置を備える負荷駆動制御装置に関する。

【背景技術】

【0002】

近年、マイクロコンピュータの利用が盛んになり、電気機器における様々な入出力制御が、ハードウエア及び組み込みソフトウエアの組み合わせによって実現されている。例えば、マイクロコンピュータが出力した信号に基づいて負荷への電源供給を制御することにより、負荷を駆動するようなことが普通に行われている。

【0003】

ところで、過渡的な状態であるパワーオンリセットの場合、及び異常が検出された状態であるウオッチドッグタイマによるリセットの場合には、ハードウエア及びソフトウエアの両面から考慮すべきことが多い。特にマイクロコンピュータの入出力ポートのようにリセット時に出力インピーダンスがハイインピーダンスとなる端子から出力される信号を用いて負荷の駆動を制御する場合には注意が必要である。

【0004】

一例として、入出力ポートから出力される信号が論理ハイのときに負荷を駆動(オン)し、ウオッチドッグタイマによるリセットが発生したときにも負荷を駆動し続ける場合は、入出力ポートの端子を正の電位に抵抗器でプルアップしておく必要がある。この場合、パワーオンリセットのときに前記信号が論理ハイとなる時があるため、ソフトウエアによる制御が開始される前から負荷が一時的に駆動されることとなる。

【0005】

例えば特許文献1では、モータ駆動回路のH型ブリッジ回路を構成するFETのゲートを駆動するCPU(ここではマイクロコンピュータを指す)の出力端子をプルアップ抵抗で電源側にプルアップし、ウオッチドッグタイマによるリセットの場合に前記FETの一部をオン状態にしてモータに発電制動を作用させる技術が開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−222432号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献1に開示された技術を一般的な負荷の駆動に応用した場合、望むと望まないとに関わらずパワーオンリセットのときに負荷が一時的に駆動されるという問題があった。

【0008】

本発明は斯かる事情に鑑みてなされたものであり、その目的とするところは、パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能な負荷駆動装置、及び該負荷駆動装置を備える負荷駆動制御装置を提供することにある。

【課題を解決するための手段】

【0009】

本発明に係る負荷駆動装置は、電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子を有し、該入力端子は所定の回路素子を介して前記電源に基づく所定電位に接続してあり、前記入力端子の電圧の高低に基づいて前記負荷を駆動する負荷駆動装置において、前記電源の電圧を微分する微分器と、該微分器で微分した微分値に基づいて前記回路素子の前記入力端子側の電圧を前記負荷を駆動しない電圧に制限する電圧制限器とを備えることを特徴とする。

【0010】

本発明にあっては、正の電圧(又は負の電圧)を与える電源から得られる正の所定電位(又は負の所定電位)に入力端子をプルアップ(又はプルダウン)する回路素子の入力端子側の電圧を、電源の電圧を微分した微分値に基づいて負荷を駆動しない正の電圧(又は負の電圧)に制限する。

これにより、電源の電圧が立ち上がる(又は立ち下がる)場合、微分値が正方向(又は負方向)に大きくなったときに、入力端子の電圧が負荷を駆動するに足りるレベルを越えないようにする。

【0011】

本発明に係る負荷駆動装置は、前記微分器は、前記電源がオフする場合の時定数をオンする場合の時定数より小さくしてあることを特徴とする。

【0012】

本発明にあっては、電源の電圧を微分する場合、電源がオフする方向に微分するときは、オンする方向に微分するときよりも小さい時定数で微分するため、微分値が微分前の値に戻るまでの時間は、電源がオンするときよりもオフするときの方が短い。

これにより、例えば、電源の電圧を立ち上げる場合に、外部の電源を接続するための接点にチャタリングが発生して電源が短時間内にオン/オフを繰り返したとしても、微分値の波形の下側(又は上側)の包絡線が接地電位から離れることを抑制する。この場合、電源が断続的にオンしたとしても、オンの都度微分値が正方向(又は負方向)に大きくなって入力端子の電圧を制限する。

従って、チャタリング時間より大きい時定数で入力端子の電圧を積分して遅延させ、積分値の高低に基づいて負荷を駆動することとした場合は、電源が短時間内にオン/オフを繰り返したとしても、積分値が負荷を駆動するに足りるレベルを越えないようにすることができる。

【0013】

本発明に係る負荷駆動装置は、電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子を有し、該入力端子は所定の回路素子を介して前記電源に基づく所定電位に接続してあり、前記入力端子の電圧の高低に基づいて前記負荷を駆動する負荷駆動装置において、前記電源側及び接地側の間に直列に接続されたコンデンサ及び抵抗からなり、前記電源の電圧を微分する微分器と、接地側及び前記回路素子の前記入力端子側の間に接続されており、前記微分器で微分した微分値に基づいて導通するスイッチング素子からなる電圧制限器とを備えることを特徴とする。

【0014】

本発明にあっては、正の電圧(又は負の電圧)を与える電源側と接地側との間に直列に接続されたコンデンサ及び抵抗からなる微分器が電源の電圧を微分した微分値に基づいて、回路素子の入力端子側と接地側との間に接続されたスイッチング素子が導通する。

これにより、電源の電圧が立ち上がる(又は立ち下がる)場合、微分値が正方向(又は負方向)に大きくなったときにスイッチング素子が導通して、入力端子の電圧が負荷を駆動するに足りるレベルを越えないようにする。

【0015】

本発明に係る負荷駆動装置は、前記微分器は、前記コンデンサ及び抵抗の接続点と接地側との間に、前記電源の電圧が立ち下がる(又は立ち上がる)時に導通する方向にダイオードを接続してあることを特徴とする。

【0016】

本発明にあっては、微分器のコンデンサ及び抵抗の接続点と接地側とに夫々ダイオードのカソードとアノードと(又はアノードとカソードと)を接続してあり、電源の電圧が立ち下がる(又は立ち上がる)時にダイオードが導通する。

つまり、微分器が電源の電圧を微分する場合、電源がオンする方向に微分するときの時定数はコンデンサ及び抵抗で決まり、電源がオフする方向に微分するときの時定数はダイオードと並列に接続された抵抗の抵抗値分だけ小さくなるため、微分値が微分前の値に戻るまでの時間がその分だけ短くなる。

これにより、例えば、電源の電圧が立ち上がる場合に、外部の電源を接続するための接点にチャタリングが発生して電源が短時間内にオン/オフを繰り返したとしても、微分値の波形の下側(又は上側)の包絡線が接地電位から離れることを抑制する。この場合、電源が断続的にオンしたとしても、オンの都度微分値が正方向(又は負方向)に大きくなって前記スイッチング素子が導通し、入力端子の電圧を制限する。

従って、チャタリング時間より大きい時定数で入力端子の電圧を積分して遅延させ、積分値の高低に基づいて負荷を駆動することとした場合は、電源が短時間内にオン/オフを繰り返したとしても、積分値が負荷を駆動するに足りるレベルを越えないようにすることができる。

【0017】

本発明に係る負荷駆動装置は、前記スイッチング素子は、導通を制御するための端子を有し、該端子にアノードが接続されており、前記負荷が駆動された場合に接地側へ導通するダイオードを備えることを特徴とする。

【0018】

本発明にあっては、スイッチング素子の導通を制御するための端子にアノードが接続されたダイオードが、負荷が駆動された場合に接地側へ導通する。

これにより、例えば、電源の電圧が立ち上がって負荷が駆動されている場合、電源の電圧が更に上昇(又は下降)して微分器の微分値が正方向(又は負方向)に大きくなったとしても、スイッチング素子の制御端子には接地側の電位が与えられるため、スイッチング素子は導通することがない。

従って、入力端子の電圧が負荷を駆動するに足りるレベルを超え続けるようにする。

【0019】

本発明に係る負荷駆動装置は、前記電圧制限器は、前記微分値が所定の正の閾値(又は負の閾値)を越える場合に動作するようにしてあり、前記微分器は、前記時間が経過するまで微分値が前記閾値を越えるようにしてあることを特徴とする。

【0020】

本発明にあっては、電源がオンされた時から所定時間が経過するまで、微分器の微分値が所定の正の閾値(又は負の閾値)を越えるようにしてあるため、微分値が前記閾値を越える場合に動作する電圧制限器が、所定時間が経過するまで動作し続ける。

これにより、電源がオンされた時から少なくとも負荷を駆動するための信号が入力端子に与えられるまでは、電圧制限器が入力端子の電圧を制限して負荷を駆動するに足りるレベルを越えないようにする。

【0021】

本発明に係る負荷駆動装置は、前記電圧制限器及び回路素子の接続点と前記入力端子との間に抵抗を接続してあり、該抵抗の抵抗値は、前記信号が前記負荷を駆動するように与えられた場合、前記電圧制限器の動作に関わらず前記入力端子の電圧が前記負荷を駆動する電圧を越えることになる値にしてあることを特徴とする。

【0022】

本発明にあっては、電圧制限器及び回路素子の接続点と入力端子との間に接続された抵抗の抵抗値は、入力端子に前記信号が負荷を駆動するように与えられた場合に、電圧制限器が入力端子の電圧を制限している/いないに関わらず、入力端子の電圧が負荷を駆動するに足りるレベルを越えることになる値とする。

これにより、電圧制限器が短絡又は開放の何れの方向に故障したとしても、負荷を駆動するための信号が与えられた場合に負荷を駆動することができる。また、前記信号に基づいて負荷を駆動している場合に、電源の電圧が急上昇して電圧制限器が入力端子の電圧を制限したとしても、負荷の駆動を継続することができる。

【0023】

本発明に係る負荷駆動装置は、電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子と、前記電源に基づく所定電位及び前記入力端子の間に接続された所定の回路素子と、前記入力端子の電圧の高低に基づいて前記負荷を駆動する駆動回路とを備える負荷駆動装置において、前記入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させる遅延器を備え、前記駆動回路は、前記遅延器が遅延させた遅延電圧の高低に基づいて前記負荷を駆動するようにしてあることを特徴とする。

【0024】

本発明にあっては、正の電圧(又は負の電圧)を発生する電源から得られる正の所定電位(又は負の所定電位)に所定の回路素子を介して接続された入力端子の電圧の立ち上がり(又は立ち下がり)を時間遅延させ、遅延させた遅延電圧の高低に基づいて駆動回路が負荷を駆動する。

これにより、回路素子によって所定電位にプルアップ(又はプルダウン)された入力端子の電圧が、電源の電圧と共に立ち上がる(又は立ち下がる)場合、入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させた遅延電圧が低い(又は高い)ときに、駆動回路が負荷を駆動しないようにする。

【0025】

本発明に係る負荷駆動装置は、電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子と、前記電源に基づく所定電位及び前記入力端子の間に接続された所定の回路素子と、前記入力端子の電圧の高低に基づいて前記負荷を駆動する駆動回路とを備える負荷駆動装置において、前記入力端子及び接地側の間に直列に接続された抵抗及びコンデンサからなり、前記入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させる遅延器を備え、前記駆動回路は、前記遅延器が遅延させた遅延電圧の高低に基づいて前記負荷を駆動するようにしてあることを特徴とする。

【0026】

本発明にあっては、入力端子及び接地側の間に直列に接続された抵抗及びコンデンサからなる遅延器が入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させ、遅延させた遅延電圧の高低に基づいて駆動回路が負荷を駆動する。

これにより、回路素子によって所定電位にプルアップ(又はプルダウン)された入力端子の電圧が、電源の電圧と共に立ち上がる(又は立ち下がる)場合、入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させた遅延電圧が低い(又は高い)ときに、駆動回路が負荷を駆動しないようにする。

【0027】

本発明に係る負荷駆動装置は、前記駆動回路は、前記遅延電圧が所定の正の閾値(又は負の閾値)を越える場合に動作するようにしてあり、前記遅延器は、前記時間が経過するまで遅延電圧が前記閾値を越えないようにしてあることを特徴とする。

【0028】

本発明にあっては、電源がオンされた時から所定時間が経過するまで、遅延器の遅延電圧が所定の正の閾値(又は負の閾値)を越えないようにしてあるため、遅延電圧が前記閾値を越える場合に動作する駆動回路が、所定時間が経過するまで動作しない。

これにより、電源がオンされた時から少なくとも負荷を駆動するための信号が入力端子に与えられるまでは、遅延器が入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させ、遅延電圧が、駆動回路が負荷を駆動するに足りるレベルを越えないようにする。

【0029】

本発明に係る負荷駆動制御装置は、上述した発明の何れか1つに記載の負荷駆動装置と、前記信号を前記入力端子に与える信号出力手段と、該信号出力手段が前記信号を与える前に前記負荷の駆動状態を検出する手段とを備え、該手段が検出した駆動状態に基づいて、前記信号出力手段が前記信号を与えるようにしてあることを特徴とする。

【0030】

本発明にあっては、負荷駆動装置の入力端子に信号を与える前に負荷の駆動状態を検出し、検出した駆動状態に応じて負荷を駆動させるための信号を入力端子に与える。

これにより、負荷が既に駆動されている場合(又は駆動されていない場合)、入力端子に与える信号が負荷を駆動させる(又はさせない)ようにする。

従って、例えば、ウオッチドッグタイマによるリセットの場合は、負荷駆動装置に負荷の駆動を継続させるように信号を与える。また、パワーオンリセットの場合は、負荷駆動装置に負荷を駆動しない状態を継続させるように信号を与える。

【0031】

本発明に係る負荷駆動制御装置は、前記信号出力手段が前記負荷を駆動させるように前記信号を与えているか否かを記憶する不揮発性の記憶手段を備え、前記信号出力手段は、前記記憶手段の記憶内容に基づいて、前記信号を与えるようにしてあることを特徴とする。

【0032】

本発明にあっては、負荷を駆動させるように信号を与えているか否かを不揮発性のメモリに記憶する。その後、リセットが発生した場合、メモリの記憶内容に基づいて、負荷を駆動させるための信号を入力端子に与える。

これにより、例えば、電源が一旦オフされた後に再度オンされた場合、前回電源がオンされていたときと同じようにして入力端子に信号を与える。

【発明の効果】

【0033】

本発明によれば、回路素子が所定電位に向けて上昇(又は下降)させる入力端子の電圧を、負荷を駆動しない電圧に制限する。

これにより、電源の電圧が立ち上がる(又は立ち下がる)場合、入力端子の電圧が負荷を駆動するに足りるレベルを越えないようにする。

従って、パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能となる。

【図面の簡単な説明】

【0034】

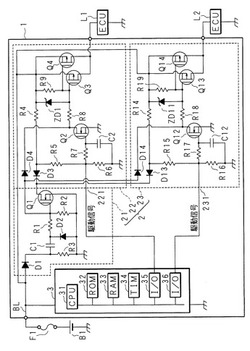

【図1】本発明の実施の形態1に係る負荷駆動制御装置の接続例を示す回路図である。

【図2】電源ラインの電圧が立ち上がった場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図3】コンデンサ及び抵抗の接続点に現れる微分電圧を模式的に示す説明図である。

【図4】WDTによるリセットが発生した場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図5】WDTによるリセットが発生した場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図6】入力端子の電圧に応じて駆動信号を出力するCPUの処理手順を示すフローチャートである。

【図7】出力ポート設定のサブルーチンに係るCPUの処理手順を示すフローチャートである。

【図8】RAMに記憶した負荷の駆動状態を読み出して駆動信号を出力するCPUの処理手順を示すフローチャートである。

【図9】本発明の実施の形態2に係る負荷駆動制御装置の接続例を示す回路図である。

【図10】電源ラインの電圧が立ち上がった場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図11】WDTによるリセットが発生した場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図12】駆動回路の出力の電圧に応じて駆動信号を出力するCPUの処理手順を示すフローチャートである。

【発明を実施するための形態】

【0035】

以下、本発明に係る負荷駆動装置を、負荷の駆動を制御する負荷駆動制御装置に適用した実施の形態について詳述する。

(実施の形態1)

図1は、本発明の実施の形態1に係る負荷駆動制御装置1の接続例を示す回路図である。図中1は負荷駆動制御装置であり、負荷駆動制御装置1は、ECUからなる負荷L1,L2を夫々駆動する駆動回路22,23及び微分電圧増幅回路21を有する負荷駆動装置2と、駆動回路22,23の入力端子221,231に夫々負荷L1,L2を駆動するための信号(以下、駆動信号という)を与える制御部3とを備える。負荷駆動装置2及び制御部3は、ヒューズF1を介して外部のバッテリ(電源)B1から正の電圧を与えられる電源ライン(所定電位)BLと接続されている。

【0036】

微分増幅回路21は、電源ラインBLにアノードを接続してあり電源ラインBLの電圧の立ち上がりで導通するダイオードD1と、ダイオードD1のカソード及び接地電位との間に直列に接続されて微分器を構成するコンデンサC1及び抵抗R1,R2とを備える。コンデンサC1のダイオードD1側及び抵抗R1側と接地電位との間には、夫々抵抗R3及びダイオードD2が接続されており、ダイオードD2は接地電位側がアノードとなるようにしてある。抵抗R1,R2の接続点には、ソース接地のNチャネル型の電界効果トランジスタ(以下、FETという)Q1のゲートに接続されており、FETQ1のドレインは、駆動回路22,23のダイオードD3,D13のカソードに接続されている。

【0037】

駆動回路23が有するダイオードD13,D14、コンデンサC12、抵抗R14〜R19、FETQ12〜Q14、及びツェナーダイオードZD11は、夫々駆動回路22が有するダイオードD3,D4、コンデンサC2、抵抗R4〜R9、FETQ2〜Q4、及びツェナーダイオードZD1と接続構成が同様であるため、以下では駆動回路22の接続構成を中心に説明する。

【0038】

ダイオードD3のアノードは、抵抗R4(所定の回路素子)を通じて電源ラインBLにプルアップしてあり、抵抗R4及び前記アノードの接続点と入力端子221との間には、抵抗R5が接続されている。入力端子221及び接地電位の間には、抵抗R5を通じて入力端子221に印加される電圧を分圧するための抵抗R6が接続されている。入力端子221及び接地電位の間には、更に、抵抗R7及びコンデンサC2が直列に接続されており、抵抗R7及びコンデンサC2の接続点は、ソース接地のNチャネル型のFETQ2のゲートに接続されている。抵抗R7及びコンデンサC2は、入力端子221の電圧を僅かに遅延させてFETQ2のゲートに与えるための積分器である。

【0039】

FETQ2のドレインは、一端子が電源ラインBLに接続された抵抗R9の他端子と、ソース及びドレインが夫々電源ラインBL及び負荷L1に接続されたPチャネル型FETQ3,Q4のゲートとに抵抗R8を介して接続されている。抵抗R9には、カソードが電源ラインBLに接続されたツェナーダイオードZD1が並列に接続されている。

FETQ2のドレインは、また、アノードがFETQ1のゲートに接続されたダイオードD4のカソードに接続されている。ダイオードD4のアノードには、駆動回路23のダイオードD14のアノードが接続されている。

【0040】

制御部3の中枢となるのはCPU31であり、CPU31は、プログラム等の情報を記憶するROM32、一時的に発生した情報を記憶する不揮発性のRAM(記憶手段)33、及び時間を計時するためのタイマ(TIM)34と互いにバス接続されている。CPU31は、ROM32に予め格納されている制御プログラムに従って入出力、演算等の処理を実行する。CPU31には、また、駆動回路22,23夫々の入力端子221,231に駆動信号を与えるための入出力ポート(I/O、信号出力手段)35,36がバス接続されている。

【0041】

以下、上述した構成における負荷駆動制御装置1の動作を場合分けして説明する。

(1)電源の電圧が立ち上がった場合

図2は、電源ラインBLの電圧が立ち上がった場合の負荷駆動制御装置1の動作の例を示すタイミングチャートである。図中横軸は時間(t)を表し、縦軸は、電源ラインBLの電圧(オン/オフ)、又は負荷駆動制御装置1の各部の電圧(H/L)を表す。図2(a)〜(g)は、夫々電源ラインBLの電圧、FETQ1のゲートの電圧、FETQ1のドレインの電圧、入力端子221の電圧、FETQ2のドレインの電圧、入出力ポート35が出力する駆動信号の電圧、及びFETQ3,Q4のドレインの電圧を示す。

【0042】

尚、抵抗R7及びコンデンサC2による時間遅れは、上記微分器の時定数に相当する時間より遙かに短いため、図2(d)では、入力端子221の電圧とFETQ2のゲートの電圧とがほぼ同時刻に変化するものとして示してある。また、時刻t0で図2(a)に示す電源ラインBLの電圧が立ち上がって制御部3にパワーオンリセットが発生し、パワーオンリセットが解除された後は、CPU31が、時刻t1までの間に入出力ポート35,36の初期化を含む初期化処理を行うものとする。これにより、時刻t0からt1までの間は、図2(f)に示すように、駆動信号の信号源インピーダンスがハイインピーダンスになるものとする(以下同様)。

【0043】

(1−1)時刻t0〜t1まで(所定時間)

時刻t0で電源ラインBLの電圧の立ち上がりがコンデンサC1により微分され、正の微分電圧(微分値)が抵抗R1,R2で分圧されてFETQ1のゲートに印加される。これにより、FETQ1がオンしてドレインが“L”となり、ダイオードD3が導通するため、抵抗R4,R5の接続点の電圧が低下して“L”となる。このため、入力端子221の電圧及びFETQ2のゲートの電圧も“L”となってFETQ2はオフとなり、FETQ2のドレイン及びFETQ3,Q4のゲートには抵抗R9を通じて電源ラインBLの電圧が印加される。従って、FETQ3,Q4がオフしてドレインが“L”となり、負荷L1が駆動されない状態となる。

【0044】

このように、FETQ1は、ダイオードD3を通じて抵抗R4,R5の接続点の電圧を“L”に制限するスイッチング素子(電圧制限器)として機能する。

尚、ダイオードD4,D14は、カソードがアノードより高電位となるため、導通しない状態となっている。また、ダイオードD3,D13は、駆動回路22のFETQ2のドレイン電圧と駆動回路23のFETQ13のドレイン電圧とが互いに干渉し合うのを防止する役目も果たしている。

【0045】

(1−2)時刻t1

時刻t1でCPU31が初期化処理を終えた場合、CPU31は、負荷L1の駆動状態を検出するために、入力ポートに設定してある入出力ポート35より入力端子221の電圧(H/L)を取り込む。その後、CPU31は、入出力ポート35を出力ポートに設定変更し、先に取り込んだ電圧の“H/L”に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“L”が出力される。

【0046】

(1−3)時刻t2

コンデンサC1及び抵抗R1,R2によって決まる時定数で上記微分電圧が低下し、時刻t2で所定の正の閾値を下回った場合、FETQ1のゲートの電圧が、FETQ1のオン/オフを反転させる閾値に達する。この場合、FETQ1がオフとなり、ドレインの電圧は、抵抗R4にプルアップされて“H”となるが、入力端子221には既に“L”の駆動信号が与えられているため、入力端子221の電圧に変化は生じない。従って、負荷L1が駆動されない状態が継続する。

【0047】

(1−4)時刻t3

本実施の形態1にあっては、時刻t0以前に電源がオンされているときの駆動信号の“H/L”の状態をRAM33に記憶してある。CPU31は、時刻t3でRAM33より上記状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。

例えば、駆動状態として“H”を記憶していたとき、CPU31は、時刻t3で駆動信号を“H”とする。これにより、入力端子221及びFETQ2のゲートの電圧が“H”となり、FETQ2がオンしてドレインが“L”となる。従って、FETQ3,Q4がオンしてドレインが“H”となり、負荷L1が駆動される状態となる。また、FETQ2のドレインが“L”となることにより、ダイオードD4が導通してFETQ1のゲートの電圧を確実に“L”とする。

【0048】

(2)電源の電圧が立ち上がるときにオン/オフを繰り返す場合

例えばバッテリB1を負荷駆動制御装置1に接続する場合、電源ラインBLの電圧が上下に変化するときは、電源ラインBLの電圧の立ち上がり及び立ち下がりがコンデンサC1によって微分されることとなる。

図3は、コンデンサC1及び抵抗R1の接続点に現れる微分電圧を模式的に示す説明図である。図3(a)は、仮にダイオードD2がない場合の微分電圧を示し、図3(b)は、ダイオードを図1のとおり接続してある場合の微分電圧を示す。

【0049】

(2−1)図3(a)に示す場合

ダイオードD2がない場合、電源ラインBLの電圧が立ち下がるときの微分器の時定数を決定する抵抗は、抵抗R1〜R3を直列に接続したものと等価になるため、このときの時定数は、前記電源がオンするときの時定数より大きくなることはない。この場合の微分電圧は、高/低変化する微分電圧によってコンデンサC1が充放電されるときに出入りする電荷の量が等しくなるまで、下側の包絡線が接地電位から負方向に離れるようになる。従って、微分電圧が低下してFETQ1がオンしなくなる虞がある。

【0050】

(2−2)図3(b)に示す場合

ダイオードD2を図1のとおり接続してある場合、電源ラインBLの電圧が立ち下がるときは、ダイオードD1が導通せずダイオードD2が導通するため、抵抗R3が微分器の時定数を決定する抵抗となる。ここで抵抗R3の抵抗値を抵抗R1及びR2の直列抵抗値より十分小さくした場合は、電源ラインBLの電圧が立ち上がった後にコンデンサC1の抵抗R1側から流出した正の電荷が、前記電源が立ち下がった後の比較的短い時間内に抵抗R3及びダイオードD2を通じて流入するようになる。従って、微分電圧の下側の包絡線が接地電位から負方向に離れることがないため、電源ラインBLの電圧が立ち上がった場合に、安定してFETQ1を導通させることができる。

【0051】

この場合、更に、抵抗R7及びコンデンサC2による遅れ時間を、電源ラインBLの電圧がオン/オフを繰り返す周期より比較的大きくしたときは、FETQ2がオフし続けるようにすることができる。これにより、FETQ3,Q4もオフし続けるため、電源ラインBLの電圧がオン/オフを繰り返す場合であっても、負荷L1が駆動されない状態を継続させることができる。

【0052】

(3)駆動信号により負荷L1が駆動されている場合

次に、図2の時刻t3が過ぎ、CPU31が“H/L”の駆動信号を駆動回路22に与える制御を行っている場合について説明する。

(3−1)FETQ1が故障した場合

FETQ1が、ドレイン及びソースが短絡する方向に故障した場合、ダイオードD3が導通して抵抗R4,R5の接続点の電圧が常に“L”となる。本実施の形態1にあっては、この場合にも入力端子221の電圧を“H”にする駆動電圧が与えられたときは、FETQ2がオンするように抵抗R5の抵抗値を定めてある。また、FETQ1が、ドレインが開放となる方向に故障した場合は、図2の時刻t2以降におけるFETQ1の状態と変わりがない。従って、FETQ1が、短絡又は開放の何れの方向に故障したとしても、駆動回路22は、CPU31から“H”(又は“L”)の駆動信号を与えられた場合に、負荷L1を駆動する(又は駆動しないようにする)ことができる。

【0053】

(3−2)電源ラインBLの電圧が変動した場合

入力端子221の電圧を“H”にする駆動電圧が与えられてFETQ2がオンしている場合に電源ラインBLの電圧が急激に上昇したときは、前記電圧の上昇分の立ち上がりがコンデンサC1により微分され、正の微分電圧(微分値)が抵抗R1,R2で分圧されてFETQ1のゲートに印加される。これにより、FETQ1がオンしてドレインが“L”となり、ダイオードD3が導通して抵抗R4,R5の接続点の電圧が“L”となる。この場合は、FETQ1が、ドレイン及びソースが短絡する方向に故障した場合、即ち(3−1)で上述した場合と同様であるため、駆動回路22は、負荷L1を駆動し続けることができる。

【0054】

(4)WDT(ウオッチドッグタイマ)によるリセットの場合

図4,5は、WDTによるリセットが発生した場合の負荷駆動制御装置1の動作の例を示すタイミングチャートである。図4,5では、夫々WDTによるリセットが発生したときに負荷L1を駆動していた場合と駆動していなかった場合とについて図示してある。図中横軸は時間(t)を表し、縦軸は、電源ラインBLの電圧(オン/オフ)、又は負荷駆動制御装置1の各部の電圧(H/L)を表す。図4(a)〜(g)は、夫々電源ラインBLの電圧、FETQ1のゲートの電圧、FETQ1のドレインの電圧、入力端子221の電圧、FETQ2のドレインの電圧、入出力ポート35が出力する駆動信号の電圧、及びFETQ3,Q4のドレインの電圧を示す(図5においても同様)。

【0055】

(4−1)図4に示す場合

時刻t0までは、図4(g)に示すようにFETQ3,Q4がオンしてドレインが“H”となり、負荷L1が駆動されている。時刻t0でWDTによるリセットが発生した場合、リセットによって入出力ポート35より出力される駆動信号の信号源インピーダンスがハイインピーダンスとなるが、図4(d)に示す入力端子221の電圧は既に“H”となっているため、FETQ2及びQ3,Q4がオンし続け、負荷L1が駆動され続ける。

【0056】

その後、時刻t1でCPU31が初期化処理を終えた場合、CPU31は、入力ポートに設定してある入出力ポート35より、負荷L1の駆動状態を検出するために入力端子221の電圧(H/L)を取り込む。そして、CPU31は、入出力ポート35を出力ポートに設定変更し、先に取り込んだ電圧の“H/L”に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“H”が出力される。

【0057】

時刻t3で、CPU31は、時刻t0以前にRAM33に記憶していた駆動信号の“H/L” の状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“H”となるが、駆動信号は、時刻t3以前に既に“H”となっているため、入力端子221、FETQ2のドレイン、FETQ3,Q4のドレイン、及びFETQ1のゲートには何の変化も現れない。

【0058】

尚、時刻t0〜t3又はそれ以降の何れの時点においても、FETQ2がオンしてドレインが“L”となっているため、ダイオードD4が導通してFETQ1のゲートは“L”を保持している。従って、この間に電源ラインBLの電圧が急激に上昇したとしても、FETQ1がオンしてドレインが“L”となることはなく、負荷L1は駆動され続ける。

【0059】

(4−2)図5に示す場合

時刻t0までは、駆動信号が入力端子221を“L”に駆動しており、FETQ2がオフしてドレインが“H”となり、FETQ3,Q4がオフしてのドレインが“L”となっているため、負荷L1は駆動されていない。時刻t0でWDTによるリセットが発生した場合、リセットによって入出力ポート35より出力される駆動信号の信号源インピーダンスがハイインピーダンスとなるため、入力端子221の電圧は、抵抗R4,R5を通じて電源ラインBLにプルアップされて“H”となる。これにより、FETQ2がオンしてドレインが“L”となり、FETQ3,Q4がオンしてのドレインが“H”となって負荷L1が駆動される。

【0060】

その後、時刻t1でCPU31が初期化処理を終えた場合については、図4の場合と同様であるため、その説明を省略する。

【0061】

時刻t3で、CPU31は、時刻t0以前にRAM33に記憶していた駆動信号の“H/L” の状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“L”となるため、入力端子221の電圧が“L”となり、FETQ2がオフしてドレインが“H”となる。従って、FETQ3,Q4がオフしてドレインが“L”となり、負荷L1が駆動されない時刻t0以前の状態に戻る。

【0062】

以下に、上述した構成の負荷駆動制御装置1の動作を、それを示すフローチャートを用いて説明する。

図6は、入力端子221の電圧に応じて駆動信号を出力するCPU31の処理手順を示すフローチャートであり、図7は、出力ポート設定のサブルーチンに係るCPU31の処理手順を示すフローチャートである。図6,7の処理は、ROM32に予め格納されている制御プログラムに従って実行される。また、図6の処理は、制御部3にリセット(例えば、パワーオンリセット又はWDTによるリセット)が発生した場合に起動されるようにしてある。

【0063】

図6の処理が起動された場合、CPU31は、RAM33の所定領域の初期化及び入出力ポート35,36の初期設定を含む初期化処理を行う(ステップS11)。この場合、入出力ポート35は入力ポートに設定する。その後、CPU31は、入出力ポート35を介して入力端子221の電圧(H/L)を取り込み(ステップS12)、入出力ポート35を出力ポートに設定変更する(ステップS13)。

【0064】

次いで、CPU31は、取り込んだ入力端子221の電圧が“H”であるか否かを判定する(ステップS14)。“H”であると判定した場合(ステップS14:YES)、CPU31は、引数を“H”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS15)、処理を終了する。“H”でないと判定した場合(ステップS14:NO)、CPU31は、引数を“L”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS16)、処理を終了する。

【0065】

図7に示す出力ポート設定に係るサブルーチンがメインルーチンから呼び出しされた場合、CPU31は、引数が“H”であるか否かを判定する(ステップS21)。“H”であると判定した場合(ステップS21:YES)、CPU31は、出力ポートに設定した入出力ポート35に“H”を出力させ(ステップS22)、RAM33の所定アドレスに“H”を記憶して(ステップS23)処理を終了する。“H”でないと判定した場合(ステップS21:NO)、CPU31は、出力ポートに設定した入出力ポート35に“L”を出力させ(ステップS24)、RAM33の所定アドレスに“L”を記憶して(ステップS25)処理を終了する。

【0066】

図8は、RAM33に記憶した負荷L1の駆動状態を読み出して駆動信号を出力するCPU31の処理手順を示すフローチャートである。以下の処理は、ROM32に予め格納されている制御プログラムに従って実行されるものであり、例えば図2,4,5の時刻t3において起動されるようにしてある。

尚、時刻t0以前に入力端子221に駆動信号が与えられる場合、CPU31が図7に示す出力ポート設定に係るサブルーチンを呼び出すことによってRAM33の所定のアドレスに駆動信号の“H/L”の状態が記憶されるものとする。

【0067】

図8の処理が起動された場合、CPU31は、RAM33の所定のアドレスの内容を読み出し(ステップS31)、読み出した値が“H”を示すものであるか否かを判定する(ステップS32)。“H”を示すものであると判定した場合(ステップS32:YES)、CPU31は、引数を“H”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS33)、処理を終了する。“H”を示すものではないと判定した場合(ステップS32:NO)、CPU31は、引数を“L”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS34)、処理を終了する。

【0068】

以上のように、本実施の形態1によれば、電源ラインに正の電圧を与えるバッテリを電源とし、電源ライン側と接地電位との間に直列に接続されたコンデンサ及び抵抗からなる微分器が電源ラインの電圧を微分した微分電圧に基づいて、入力端子を電源ラインにプルアップする抵抗の入力端子側と接地電位との間にダイオードを介して接続されたFET(スイッチング素子、電圧制限器)が導通する。

これにより、バッテリが接続されて電源ラインの電圧が立ち上がる場合、微分電圧が正方向に大きくなったときに、スイッチング素子が導通して、入力端子の電圧が負荷を駆動するに足りるレベルを超えないようにする。

従って、パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能となる。

【0069】

また、電源ラインの電圧を微分する場合、電源がオフする方向に微分するときは、微分器のコンデンサ及び抵抗の接続点と接地電位との間に接続されたダイオードが接地電位からコンデンサに向けて導通する。このため、電源がオフする方向に微分するときの時定数はダイオードと並列に接続された抵抗の抵抗値分だけ小さくなり、微分値が微分前の値に戻るまでの時間がその分だけ短くなる。

これにより、例えば、電源ラインの電圧を立ち上げる場合に、バッテリを接続するための接点にチャタリングが発生して電源ラインの電圧が上下に変化したとしても、微分電圧の下側の包絡線が接地電位から離れることを抑制する。この場合、電源が断続的に接続されたとしても、接続の都度微分電圧が正方向に大きくなってスイッチング素子が導通し、入力端子の電圧を制限する。

従って、チャタリング時間より大きい時定数で入力端子の電圧を積分して遅延させることにより、電源が短時間内にオン/オフを繰り返したとしても、積分値が負荷を駆動するに足りるレベルを越えないようにして、負荷が駆動されない状態を継続することが可能となる。

【0070】

更にまた、FET(スイッチング素子)のゲートにアノードが接続されたダイオードが、負荷が駆動された場合に接地電位へ導通する。

従って、一旦電源の電圧が立ち上がって負荷が駆動された後に、更に電圧が上昇した場合であっても、スイッチング素子(電圧制限器)が入力端子の電圧を制限することがないため、負荷が駆動されない状態を継続することが可能となる。

【0071】

更にまた、時刻t0から時刻t2まで、微分器の微分電圧を分圧した電圧がFET(スイッチング素子)のゲートの閾値を越えるようにしてあるため、時刻t0から少なくとも時刻t1が経過するまでは、前記FETが導通し続ける。

従って、電源がオンされた時から少なくとも負荷を駆動するための信号が入力端子に与えられるまでは、スイッチング素子(電圧制限器)が入力端子の電圧を制限して負荷が駆動されない状態を継続することが可能となる。

【0072】

更にまた、入力端子を電源ラインにプルアップする抵抗及びFET(スイッチング素子)の接続点と入力端子との間に接続された抵抗の抵抗値は、入力端子に駆動信号が負荷を駆動するように与えられた場合に、前記FETが導通している/いないに関わらず、入力端子の電圧が負荷を駆動するに足りるレベルを越えることになる値としてある。

従って、スイッチング素子(電圧制限器)が短絡又は開放の何れの方向に故障したとしても、負荷を駆動するための信号が与えられた場合に負荷を駆動することが可能となる。また、負荷を駆動するための信号が与えられて負荷を駆動している場合に、電源の電圧が急上昇してスイッチング素子(電圧制限器)が入力端子の電圧を制限したとしても、負荷の駆動を継続することが可能となる。

【0073】

更にまた、負荷駆動装置の入力端子に駆動信号を与える前に負荷の駆動状態として入力端子の電圧(H/L)を取り込み、取り込んだ電圧の“H/L”に対応する“H/L”の駆動信号を入力端子に与える。

従って、例えば、ウオッチドッグタイマによるリセットの場合は、負荷駆動装置に負荷の駆動を継続させ、パワーオンリセットの場合は、負荷駆動装置に負荷を駆動しない状態を継続させることが可能となる。

【0074】

更にまた、負荷を駆動させるように駆動信号を与えているか否かを不揮発性のRAMに記憶する。その後、リセットが発生した場合、RAMの記憶内容に基づいて、駆動信号を入力端子に与える。

従って、例えば、電源が一旦オフされた後に再度オンされた場合、前回電源がオンされていたときと同じ信号を入力端子に与えることが可能となる。

【0075】

尚、本実施の形態1にあっては、図1に示すように負荷駆動装置2が2つの駆動回路22,23を備えているが、これに限定されるものではなく、駆動回路を1つ、又は3つ以上備えるようにしてもよい。

【0076】

また、正の電圧を与えるバッテリB1を用いているが、これに限定されるものではなく、負の電圧を与えるバッテリを用いてもよい。この場合は、制御部3及び負荷駆動装置2が負電圧で動作するように構成する。

【0077】

更にまた、パワーオンリセット及びWDTによるリセットでは、リセットが発生している時間に差がないものとして図2,4,5を描いてあるが、これに限定されるものではなく、リセットの種類によって時刻t1が変動したとしても、時刻t2が後になる限り影響がない。

【0078】

更にまた、負荷駆動装置2の入力端子221,231に駆動信号を与える前に負荷L1,L2の駆動状態として入力端子221,231の電圧(H/L)を取り込んでいるが、これに限定されるものではなく、例えば、負荷駆動装置2の出力の電圧(H/L)を取り込むようにしてもよい。

【0079】

(実施の形態2)

実施の形態1が、電源の立ち上がりを微分した微分電圧に基づいて、スイッチング素子に負荷駆動回路の入力端子の電圧を制限させる形態であるのに対し、実施の形態2は、負荷駆動回路の入力端子の電圧の立ち上がりを時間遅延させた遅延電圧を駆動回路に与える形態である。

【0080】

図9は、本発明の実施の形態2に係る負荷駆動制御装置1aの接続例を示す回路図である。図中1aは負荷駆動制御装置であり、負荷駆動制御装置1aは、ECUからなる負荷L1を駆動する駆動回路22a及び遅延回路21aを有する負荷駆動装置2aと、負荷駆動装置2aの入力端子221aに駆動信号を与える制御部3とを備える。負荷駆動装置2a及び制御部3は、ヒューズF1を介して外部のバッテリ(電源)B1から正の電圧を与えられる電源ライン(所定電位)BLと接続されている。

【0081】

遅延回路21aは、入力端子221a及び接地電位の間に直列に接続されて遅延器を構成する抵抗R21及びコンデンサC21と、抵抗R21の両端子の間に直列に接続されており、カソードが入力端子221aに接続されたダイオードD21及び抵抗R22とを備える。入力端子221aは、抵抗R4(所定の回路素子)を通じて電源ラインBLにプルアップしてある。

【0082】

駆動回路22aは、遅延回路21aの抵抗R21及びコンデンサC21の接続点にゲートが接続されたソース接地のNチャネル型のFETQ2を備える。FETQ2のドレインは、一端子が電源ラインBLに接続された抵抗R9の他端子と、ソース及びドレインが夫々電源ラインBL及び負荷L1に接続されたPチャネル型FETQ3,Q4のゲートとに抵抗R8を介して接続されている。抵抗R9には、カソードが電源ラインBLに接続されたツェナーダイオードZD1が並列に接続されている。

【0083】

制御部3のCPU31には、負荷駆動装置2aの入力端子221aに駆動信号を与えるための入出力ポート(信号出力手段)35と、負荷L1の駆動状態を検出するための入出力ポート37とがバス接続されている。

【0084】

以下、上述した構成における負荷駆動制御装置1aの動作を場合分けして説明する。

(1)電源の電圧が立ち上がった場合

図10は、電源ラインBLの電圧が立ち上がった場合の負荷駆動制御装置1aの動作の例を示すタイミングチャートである。図中横軸は時間(t)を表し、縦軸は、電源ラインBLの電圧(オン/オフ)、又は負荷駆動制御装置1aの各部の電圧(H/L)を表す。図10(a)〜(f)は、夫々電源ラインBLの電圧、入力端子221aの電圧、FETQ2のゲートの電圧、FETQ2のドレインの電圧、入出力ポート35が出力する駆動信号の電圧、及びFETQ3,Q4のドレインの電圧を示す。(後述する図11においても同様)

【0085】

尚、時刻t0で図10(a)に示す電源ラインBLの電圧が立ち上がって制御部3にパワーオンリセットが発生し、パワーオンリセットが解除された後は、CPU31が、時刻t1までの間に入出力ポート35,37の初期化を含む初期化処理を行うものとする。これにより、時刻t0からt1までの間は、図10(e)に示すように、駆動信号の信号源インピーダンスがハイインピーダンスになるものとする(以下同様)。

【0086】

(1−1)時刻t0〜t1まで(所定時間)

時刻t0で電源ラインBLの電圧が立ち上がった場合、抵抗R4を通じて電源ラインBLにプルアップされた入力端子221aの電圧は即座に上昇する。この場合、時刻t0からコンデンサC21に電荷が蓄積され始めるため、入力端子221aの電圧は、電源ラインBLの電圧を抵抗R4及びR21で分圧した電圧を開始電圧として、電源ラインBLの電圧に向けて緩やかに上昇する。

【0087】

一方、抵抗R21及びコンデンサC21からなる遅延器の遅延電圧(遅延値)が与えられるFETQ2のゲートの電圧は、図10(c)に示すように接地電位から電源ラインBLの電圧に向けて上昇する。但し、少なくとも時刻t1までは、FETQ2のゲートの電圧がFETQ1をオンさせる閾値に達することがないため、FETQ2はオフしており、FETQ2のドレイン及びFETQ3,Q4のゲートには抵抗R9を通じて電源ラインBLの電圧が印加される。従って、FETQ3,Q4がオフしてドレインが“L”となり、負荷L1が駆動されない状態となる。

【0088】

(1−2)時刻t1

時刻t1でCPU31が初期化処理を終えた場合、CPU31は、負荷L1の駆動状態を検出するために、入力ポートに設定してある入出力ポート37よりFETQ3,4のドレインの電圧(H/L)を取り込み、取り込んだ電圧の“H/L”に対応する駆動信号を入出力ポート35より出力する。これにより、駆動信号は“L”となり、入力端子221aの電圧は接地電位となる。

【0089】

この場合、入力端子221a及びコンデンサC21の間には、ダイオードD21及び抵抗R22が接続してあり、抵抗R22の抵抗値は、抵抗R4及びR21の抵抗値より十分に小さい値であるため、コンデンサC21に蓄積されている電荷はR22を通じて急速に放電される。従って、FETQ2のゲートの電圧は速やかに下降し、FETQ2はオフを継続する。

【0090】

(1−3)時刻t3

時刻t3で、CPU31は、時刻t0以前にRAM33に記憶していた駆動信号の“H/L” の状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。例えば、時刻t0以前にRAM33に記憶していた駆動信号の状態が“H”であった場合、時刻t3で駆動信号は“H”となり、入力端子221aの電圧も“H”となる。この場合、入力端子221aの電圧は、接地電位を開始電圧とし、抵抗R21及びコンデンサC21によって決まる時定数で駆動信号の“H”の電圧に向けて比較的速やかに上昇する。

【0091】

(1−4)時刻t4

時刻t4でFETQ2のゲートの電圧がFETQ1のオン/オフを反転させる閾値に達した場合、FETQ2がオンしてドレインが“L”となる。従って、FETQ3,Q4がオンしてドレインが“H”となり、負荷L1が駆動される状態となる。

【0092】

(2)WDT(ウオッチドッグタイマ)によるリセットの場合

図11は、WDTによるリセットが発生した場合の負荷駆動制御装置1aの動作の例を示すタイミングチャートである。図11では、例として、WDTによるリセットが発生したときに負荷L1を駆動していた場合について図示してある。図中横軸は時間(t)を表し、縦軸は、電源ラインBLの電圧(オン/オフ)、又は負荷駆動制御装置1aの各部の電圧(H/L)を表す。

【0093】

時刻t0までは、図11(f)に示すようにFETQ3,Q4がオンしてドレインが“H”となり、負荷L1が駆動されている。時刻t0でWDTによるリセットが発生した場合、リセットによって入出力ポート35より出力される駆動信号の信号源インピーダンスがハイインピーダンスとなるが、図11(c)に示すFETQ2のゲートの電圧は既に“H”となっているため、FETQ2及びQ3,Q4がオンし続け、負荷L1が駆動され続ける。

【0094】

その後、時刻t1でCPU31が初期化処理を終えた場合、CPU31は、負荷L1の駆動状態を検出するために、入力ポートに設定してある入出力ポート37よりFETQ3,4のドレインの電圧(H/L)を取り込み、取り込んだ電圧の“H/L”に対応する駆動信号を入出力ポート35より出力する。これにより、駆動信号は“H”となり、入力端子221aの電圧は継続して“H”となるため、負荷L1は駆動され続ける。

【0095】

時刻t3で、CPU31は、時刻t0以前にRAM33に記憶していた駆動信号の“H/L” の状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“H”となるが、駆動信号は、時刻t3以前に既に“H”となっているため、入力端子221a、FETQ2のドレイン、FETQ3,Q4のドレイン、及びFETQ1のゲートには何の変化も現れない。

【0096】

以下に、上述した構成の負荷駆動制御装置1aの動作を、それを示すフローチャートを用いて説明する。

図12は、駆動回路22aの出力の電圧に応じて駆動信号を出力するCPU31の処理手順を示すフローチャートである。図12の処理は、ROM32に予め格納されている制御プログラムに従って実行される。また、図12の処理は、制御部3にリセット(例えば、パワーオンリセット又はWDTによるリセット)が発生した場合に起動されるようにしてある。

【0097】

図12の処理が起動された場合、CPU31は、RAM33の所定領域の初期化及び入出力ポート35,37の初期設定を含む初期化処理を行う(ステップS41)。この場合、入出力ポート35,37を夫々出力ポート及び入力ポートに設定する。その後、CPU31は、入出力ポート37を介して駆動回路22aの出力(即ちFETQ3,Q4のドレイン)の電圧(H/L)を取り込み(ステップS42)、取り込んだ駆動回路22aの出力の電圧が“H”であるか否かを判定する(ステップS43)。

【0098】

駆動回路22aの出力の電圧が“H”であると判定した場合(ステップS43:YES)、CPU31は、引数を“H”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS44)、処理を終了する。“H”でないと判定した場合(ステップS43:NO)、CPU31は、引数を“L”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS45)、処理を終了する。

【0099】

その他、実施の形態1に対応する箇所には同様の符号を付して、その詳細な説明を省略する。

【0100】

以上のように、本実施の形態2によれば、電源ラインに正の電圧を与えるバッテリを電源とし、電源ラインに抵抗を通じてプルアップされた入力端子と接地電位との間に直列に接続された抵抗及びコンデンサからなる遅延器が入力端子の電圧の立ち上がりを遅延させた遅延電圧の高低に基づいて、駆動回路が負荷を駆動する。

これにより、電源ラインにプルアップされた入力端子の電圧が、電源ラインの電圧と共に立ち上がる場合、入力端子の電圧の立ち上がりを遅延させた遅延電圧が低いときに、駆動回路が負荷を駆動しないようにする。

従って、パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能となる。

【0101】

また、時刻t0から時刻t2まで、遅延器の遅延電圧がFET(スイッチング素子)のゲートの閾値を越えないようにしてあるため、時刻t0から少なくとも時刻t1が経過するまでは、前記FETが導通しないこととなる。

従って、電源がオンされた時から少なくとも負荷を駆動するための信号が入力端子に与えられるまでは、遅延器が入力端子の電圧の立ち上がりを遅延させ、遅延電圧によって負荷が駆動されない状態を継続することが可能となる。

【0102】

尚、本実施の形態2にあっては、図10,11の時刻t1で負荷L1の駆動状態を検出するために、入出力ポート37よりFETQ3,4のドレインの電圧(H/L)を取り込んでいるが、これに限定されるものではなく、実施の形態1のように、入力端子221aの電圧(H/L)を取り込むようにしてもよい。

【符号の説明】

【0103】

1、1a 負荷駆動制御装置

2、2a 負荷駆動装置

22、23、22a 駆動回路

221、221a、231 入力端子

3 制御部

31 CPU

32 ROM

33 RAM(不揮発性の記憶手段)

35、36 入出力ポート(信号出力手段)

37 入出力ポート(負荷の駆動状態を検出する手段)

B1 バッテリ(電源)

BL 電源ライン(所定電位)

C1 コンデンサ(微分器の一部)

C21 コンデンサ(遅延器の一部)

D2 ダイオード(微分器の一部)

L1、L2 負荷

Q1 FET(スイッチング素子、電圧制限器)

R1、R2、R3 抵抗(微分器の一部)

R4 抵抗(所定の回路素子)

R5 抵抗(電圧制限器及び回路素子の接続点と入力端子との間に接続された抵抗)

R21 抵抗(遅延器の一部)

【技術分野】

【0001】

本発明は、回路リセットの場合に負荷を駆動するための信号が絶たれる負荷駆動装置、及び該負荷駆動装置を備える負荷駆動制御装置に関する。

【背景技術】

【0002】

近年、マイクロコンピュータの利用が盛んになり、電気機器における様々な入出力制御が、ハードウエア及び組み込みソフトウエアの組み合わせによって実現されている。例えば、マイクロコンピュータが出力した信号に基づいて負荷への電源供給を制御することにより、負荷を駆動するようなことが普通に行われている。

【0003】

ところで、過渡的な状態であるパワーオンリセットの場合、及び異常が検出された状態であるウオッチドッグタイマによるリセットの場合には、ハードウエア及びソフトウエアの両面から考慮すべきことが多い。特にマイクロコンピュータの入出力ポートのようにリセット時に出力インピーダンスがハイインピーダンスとなる端子から出力される信号を用いて負荷の駆動を制御する場合には注意が必要である。

【0004】

一例として、入出力ポートから出力される信号が論理ハイのときに負荷を駆動(オン)し、ウオッチドッグタイマによるリセットが発生したときにも負荷を駆動し続ける場合は、入出力ポートの端子を正の電位に抵抗器でプルアップしておく必要がある。この場合、パワーオンリセットのときに前記信号が論理ハイとなる時があるため、ソフトウエアによる制御が開始される前から負荷が一時的に駆動されることとなる。

【0005】

例えば特許文献1では、モータ駆動回路のH型ブリッジ回路を構成するFETのゲートを駆動するCPU(ここではマイクロコンピュータを指す)の出力端子をプルアップ抵抗で電源側にプルアップし、ウオッチドッグタイマによるリセットの場合に前記FETの一部をオン状態にしてモータに発電制動を作用させる技術が開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−222432号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献1に開示された技術を一般的な負荷の駆動に応用した場合、望むと望まないとに関わらずパワーオンリセットのときに負荷が一時的に駆動されるという問題があった。

【0008】

本発明は斯かる事情に鑑みてなされたものであり、その目的とするところは、パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能な負荷駆動装置、及び該負荷駆動装置を備える負荷駆動制御装置を提供することにある。

【課題を解決するための手段】

【0009】

本発明に係る負荷駆動装置は、電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子を有し、該入力端子は所定の回路素子を介して前記電源に基づく所定電位に接続してあり、前記入力端子の電圧の高低に基づいて前記負荷を駆動する負荷駆動装置において、前記電源の電圧を微分する微分器と、該微分器で微分した微分値に基づいて前記回路素子の前記入力端子側の電圧を前記負荷を駆動しない電圧に制限する電圧制限器とを備えることを特徴とする。

【0010】

本発明にあっては、正の電圧(又は負の電圧)を与える電源から得られる正の所定電位(又は負の所定電位)に入力端子をプルアップ(又はプルダウン)する回路素子の入力端子側の電圧を、電源の電圧を微分した微分値に基づいて負荷を駆動しない正の電圧(又は負の電圧)に制限する。

これにより、電源の電圧が立ち上がる(又は立ち下がる)場合、微分値が正方向(又は負方向)に大きくなったときに、入力端子の電圧が負荷を駆動するに足りるレベルを越えないようにする。

【0011】

本発明に係る負荷駆動装置は、前記微分器は、前記電源がオフする場合の時定数をオンする場合の時定数より小さくしてあることを特徴とする。

【0012】

本発明にあっては、電源の電圧を微分する場合、電源がオフする方向に微分するときは、オンする方向に微分するときよりも小さい時定数で微分するため、微分値が微分前の値に戻るまでの時間は、電源がオンするときよりもオフするときの方が短い。

これにより、例えば、電源の電圧を立ち上げる場合に、外部の電源を接続するための接点にチャタリングが発生して電源が短時間内にオン/オフを繰り返したとしても、微分値の波形の下側(又は上側)の包絡線が接地電位から離れることを抑制する。この場合、電源が断続的にオンしたとしても、オンの都度微分値が正方向(又は負方向)に大きくなって入力端子の電圧を制限する。

従って、チャタリング時間より大きい時定数で入力端子の電圧を積分して遅延させ、積分値の高低に基づいて負荷を駆動することとした場合は、電源が短時間内にオン/オフを繰り返したとしても、積分値が負荷を駆動するに足りるレベルを越えないようにすることができる。

【0013】

本発明に係る負荷駆動装置は、電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子を有し、該入力端子は所定の回路素子を介して前記電源に基づく所定電位に接続してあり、前記入力端子の電圧の高低に基づいて前記負荷を駆動する負荷駆動装置において、前記電源側及び接地側の間に直列に接続されたコンデンサ及び抵抗からなり、前記電源の電圧を微分する微分器と、接地側及び前記回路素子の前記入力端子側の間に接続されており、前記微分器で微分した微分値に基づいて導通するスイッチング素子からなる電圧制限器とを備えることを特徴とする。

【0014】

本発明にあっては、正の電圧(又は負の電圧)を与える電源側と接地側との間に直列に接続されたコンデンサ及び抵抗からなる微分器が電源の電圧を微分した微分値に基づいて、回路素子の入力端子側と接地側との間に接続されたスイッチング素子が導通する。

これにより、電源の電圧が立ち上がる(又は立ち下がる)場合、微分値が正方向(又は負方向)に大きくなったときにスイッチング素子が導通して、入力端子の電圧が負荷を駆動するに足りるレベルを越えないようにする。

【0015】

本発明に係る負荷駆動装置は、前記微分器は、前記コンデンサ及び抵抗の接続点と接地側との間に、前記電源の電圧が立ち下がる(又は立ち上がる)時に導通する方向にダイオードを接続してあることを特徴とする。

【0016】

本発明にあっては、微分器のコンデンサ及び抵抗の接続点と接地側とに夫々ダイオードのカソードとアノードと(又はアノードとカソードと)を接続してあり、電源の電圧が立ち下がる(又は立ち上がる)時にダイオードが導通する。

つまり、微分器が電源の電圧を微分する場合、電源がオンする方向に微分するときの時定数はコンデンサ及び抵抗で決まり、電源がオフする方向に微分するときの時定数はダイオードと並列に接続された抵抗の抵抗値分だけ小さくなるため、微分値が微分前の値に戻るまでの時間がその分だけ短くなる。

これにより、例えば、電源の電圧が立ち上がる場合に、外部の電源を接続するための接点にチャタリングが発生して電源が短時間内にオン/オフを繰り返したとしても、微分値の波形の下側(又は上側)の包絡線が接地電位から離れることを抑制する。この場合、電源が断続的にオンしたとしても、オンの都度微分値が正方向(又は負方向)に大きくなって前記スイッチング素子が導通し、入力端子の電圧を制限する。

従って、チャタリング時間より大きい時定数で入力端子の電圧を積分して遅延させ、積分値の高低に基づいて負荷を駆動することとした場合は、電源が短時間内にオン/オフを繰り返したとしても、積分値が負荷を駆動するに足りるレベルを越えないようにすることができる。

【0017】

本発明に係る負荷駆動装置は、前記スイッチング素子は、導通を制御するための端子を有し、該端子にアノードが接続されており、前記負荷が駆動された場合に接地側へ導通するダイオードを備えることを特徴とする。

【0018】

本発明にあっては、スイッチング素子の導通を制御するための端子にアノードが接続されたダイオードが、負荷が駆動された場合に接地側へ導通する。

これにより、例えば、電源の電圧が立ち上がって負荷が駆動されている場合、電源の電圧が更に上昇(又は下降)して微分器の微分値が正方向(又は負方向)に大きくなったとしても、スイッチング素子の制御端子には接地側の電位が与えられるため、スイッチング素子は導通することがない。

従って、入力端子の電圧が負荷を駆動するに足りるレベルを超え続けるようにする。

【0019】

本発明に係る負荷駆動装置は、前記電圧制限器は、前記微分値が所定の正の閾値(又は負の閾値)を越える場合に動作するようにしてあり、前記微分器は、前記時間が経過するまで微分値が前記閾値を越えるようにしてあることを特徴とする。

【0020】

本発明にあっては、電源がオンされた時から所定時間が経過するまで、微分器の微分値が所定の正の閾値(又は負の閾値)を越えるようにしてあるため、微分値が前記閾値を越える場合に動作する電圧制限器が、所定時間が経過するまで動作し続ける。

これにより、電源がオンされた時から少なくとも負荷を駆動するための信号が入力端子に与えられるまでは、電圧制限器が入力端子の電圧を制限して負荷を駆動するに足りるレベルを越えないようにする。

【0021】

本発明に係る負荷駆動装置は、前記電圧制限器及び回路素子の接続点と前記入力端子との間に抵抗を接続してあり、該抵抗の抵抗値は、前記信号が前記負荷を駆動するように与えられた場合、前記電圧制限器の動作に関わらず前記入力端子の電圧が前記負荷を駆動する電圧を越えることになる値にしてあることを特徴とする。

【0022】

本発明にあっては、電圧制限器及び回路素子の接続点と入力端子との間に接続された抵抗の抵抗値は、入力端子に前記信号が負荷を駆動するように与えられた場合に、電圧制限器が入力端子の電圧を制限している/いないに関わらず、入力端子の電圧が負荷を駆動するに足りるレベルを越えることになる値とする。

これにより、電圧制限器が短絡又は開放の何れの方向に故障したとしても、負荷を駆動するための信号が与えられた場合に負荷を駆動することができる。また、前記信号に基づいて負荷を駆動している場合に、電源の電圧が急上昇して電圧制限器が入力端子の電圧を制限したとしても、負荷の駆動を継続することができる。

【0023】

本発明に係る負荷駆動装置は、電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子と、前記電源に基づく所定電位及び前記入力端子の間に接続された所定の回路素子と、前記入力端子の電圧の高低に基づいて前記負荷を駆動する駆動回路とを備える負荷駆動装置において、前記入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させる遅延器を備え、前記駆動回路は、前記遅延器が遅延させた遅延電圧の高低に基づいて前記負荷を駆動するようにしてあることを特徴とする。

【0024】

本発明にあっては、正の電圧(又は負の電圧)を発生する電源から得られる正の所定電位(又は負の所定電位)に所定の回路素子を介して接続された入力端子の電圧の立ち上がり(又は立ち下がり)を時間遅延させ、遅延させた遅延電圧の高低に基づいて駆動回路が負荷を駆動する。

これにより、回路素子によって所定電位にプルアップ(又はプルダウン)された入力端子の電圧が、電源の電圧と共に立ち上がる(又は立ち下がる)場合、入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させた遅延電圧が低い(又は高い)ときに、駆動回路が負荷を駆動しないようにする。

【0025】

本発明に係る負荷駆動装置は、電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子と、前記電源に基づく所定電位及び前記入力端子の間に接続された所定の回路素子と、前記入力端子の電圧の高低に基づいて前記負荷を駆動する駆動回路とを備える負荷駆動装置において、前記入力端子及び接地側の間に直列に接続された抵抗及びコンデンサからなり、前記入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させる遅延器を備え、前記駆動回路は、前記遅延器が遅延させた遅延電圧の高低に基づいて前記負荷を駆動するようにしてあることを特徴とする。

【0026】

本発明にあっては、入力端子及び接地側の間に直列に接続された抵抗及びコンデンサからなる遅延器が入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させ、遅延させた遅延電圧の高低に基づいて駆動回路が負荷を駆動する。

これにより、回路素子によって所定電位にプルアップ(又はプルダウン)された入力端子の電圧が、電源の電圧と共に立ち上がる(又は立ち下がる)場合、入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させた遅延電圧が低い(又は高い)ときに、駆動回路が負荷を駆動しないようにする。

【0027】

本発明に係る負荷駆動装置は、前記駆動回路は、前記遅延電圧が所定の正の閾値(又は負の閾値)を越える場合に動作するようにしてあり、前記遅延器は、前記時間が経過するまで遅延電圧が前記閾値を越えないようにしてあることを特徴とする。

【0028】

本発明にあっては、電源がオンされた時から所定時間が経過するまで、遅延器の遅延電圧が所定の正の閾値(又は負の閾値)を越えないようにしてあるため、遅延電圧が前記閾値を越える場合に動作する駆動回路が、所定時間が経過するまで動作しない。

これにより、電源がオンされた時から少なくとも負荷を駆動するための信号が入力端子に与えられるまでは、遅延器が入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させ、遅延電圧が、駆動回路が負荷を駆動するに足りるレベルを越えないようにする。

【0029】

本発明に係る負荷駆動制御装置は、上述した発明の何れか1つに記載の負荷駆動装置と、前記信号を前記入力端子に与える信号出力手段と、該信号出力手段が前記信号を与える前に前記負荷の駆動状態を検出する手段とを備え、該手段が検出した駆動状態に基づいて、前記信号出力手段が前記信号を与えるようにしてあることを特徴とする。

【0030】

本発明にあっては、負荷駆動装置の入力端子に信号を与える前に負荷の駆動状態を検出し、検出した駆動状態に応じて負荷を駆動させるための信号を入力端子に与える。

これにより、負荷が既に駆動されている場合(又は駆動されていない場合)、入力端子に与える信号が負荷を駆動させる(又はさせない)ようにする。

従って、例えば、ウオッチドッグタイマによるリセットの場合は、負荷駆動装置に負荷の駆動を継続させるように信号を与える。また、パワーオンリセットの場合は、負荷駆動装置に負荷を駆動しない状態を継続させるように信号を与える。

【0031】

本発明に係る負荷駆動制御装置は、前記信号出力手段が前記負荷を駆動させるように前記信号を与えているか否かを記憶する不揮発性の記憶手段を備え、前記信号出力手段は、前記記憶手段の記憶内容に基づいて、前記信号を与えるようにしてあることを特徴とする。

【0032】

本発明にあっては、負荷を駆動させるように信号を与えているか否かを不揮発性のメモリに記憶する。その後、リセットが発生した場合、メモリの記憶内容に基づいて、負荷を駆動させるための信号を入力端子に与える。

これにより、例えば、電源が一旦オフされた後に再度オンされた場合、前回電源がオンされていたときと同じようにして入力端子に信号を与える。

【発明の効果】

【0033】

本発明によれば、回路素子が所定電位に向けて上昇(又は下降)させる入力端子の電圧を、負荷を駆動しない電圧に制限する。

これにより、電源の電圧が立ち上がる(又は立ち下がる)場合、入力端子の電圧が負荷を駆動するに足りるレベルを越えないようにする。

従って、パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能となる。

【図面の簡単な説明】

【0034】

【図1】本発明の実施の形態1に係る負荷駆動制御装置の接続例を示す回路図である。

【図2】電源ラインの電圧が立ち上がった場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図3】コンデンサ及び抵抗の接続点に現れる微分電圧を模式的に示す説明図である。

【図4】WDTによるリセットが発生した場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図5】WDTによるリセットが発生した場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図6】入力端子の電圧に応じて駆動信号を出力するCPUの処理手順を示すフローチャートである。

【図7】出力ポート設定のサブルーチンに係るCPUの処理手順を示すフローチャートである。

【図8】RAMに記憶した負荷の駆動状態を読み出して駆動信号を出力するCPUの処理手順を示すフローチャートである。

【図9】本発明の実施の形態2に係る負荷駆動制御装置の接続例を示す回路図である。

【図10】電源ラインの電圧が立ち上がった場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図11】WDTによるリセットが発生した場合の負荷駆動制御装置の動作の例を示すタイミングチャートである。

【図12】駆動回路の出力の電圧に応じて駆動信号を出力するCPUの処理手順を示すフローチャートである。

【発明を実施するための形態】

【0035】

以下、本発明に係る負荷駆動装置を、負荷の駆動を制御する負荷駆動制御装置に適用した実施の形態について詳述する。

(実施の形態1)

図1は、本発明の実施の形態1に係る負荷駆動制御装置1の接続例を示す回路図である。図中1は負荷駆動制御装置であり、負荷駆動制御装置1は、ECUからなる負荷L1,L2を夫々駆動する駆動回路22,23及び微分電圧増幅回路21を有する負荷駆動装置2と、駆動回路22,23の入力端子221,231に夫々負荷L1,L2を駆動するための信号(以下、駆動信号という)を与える制御部3とを備える。負荷駆動装置2及び制御部3は、ヒューズF1を介して外部のバッテリ(電源)B1から正の電圧を与えられる電源ライン(所定電位)BLと接続されている。

【0036】

微分増幅回路21は、電源ラインBLにアノードを接続してあり電源ラインBLの電圧の立ち上がりで導通するダイオードD1と、ダイオードD1のカソード及び接地電位との間に直列に接続されて微分器を構成するコンデンサC1及び抵抗R1,R2とを備える。コンデンサC1のダイオードD1側及び抵抗R1側と接地電位との間には、夫々抵抗R3及びダイオードD2が接続されており、ダイオードD2は接地電位側がアノードとなるようにしてある。抵抗R1,R2の接続点には、ソース接地のNチャネル型の電界効果トランジスタ(以下、FETという)Q1のゲートに接続されており、FETQ1のドレインは、駆動回路22,23のダイオードD3,D13のカソードに接続されている。

【0037】

駆動回路23が有するダイオードD13,D14、コンデンサC12、抵抗R14〜R19、FETQ12〜Q14、及びツェナーダイオードZD11は、夫々駆動回路22が有するダイオードD3,D4、コンデンサC2、抵抗R4〜R9、FETQ2〜Q4、及びツェナーダイオードZD1と接続構成が同様であるため、以下では駆動回路22の接続構成を中心に説明する。

【0038】

ダイオードD3のアノードは、抵抗R4(所定の回路素子)を通じて電源ラインBLにプルアップしてあり、抵抗R4及び前記アノードの接続点と入力端子221との間には、抵抗R5が接続されている。入力端子221及び接地電位の間には、抵抗R5を通じて入力端子221に印加される電圧を分圧するための抵抗R6が接続されている。入力端子221及び接地電位の間には、更に、抵抗R7及びコンデンサC2が直列に接続されており、抵抗R7及びコンデンサC2の接続点は、ソース接地のNチャネル型のFETQ2のゲートに接続されている。抵抗R7及びコンデンサC2は、入力端子221の電圧を僅かに遅延させてFETQ2のゲートに与えるための積分器である。

【0039】

FETQ2のドレインは、一端子が電源ラインBLに接続された抵抗R9の他端子と、ソース及びドレインが夫々電源ラインBL及び負荷L1に接続されたPチャネル型FETQ3,Q4のゲートとに抵抗R8を介して接続されている。抵抗R9には、カソードが電源ラインBLに接続されたツェナーダイオードZD1が並列に接続されている。

FETQ2のドレインは、また、アノードがFETQ1のゲートに接続されたダイオードD4のカソードに接続されている。ダイオードD4のアノードには、駆動回路23のダイオードD14のアノードが接続されている。

【0040】

制御部3の中枢となるのはCPU31であり、CPU31は、プログラム等の情報を記憶するROM32、一時的に発生した情報を記憶する不揮発性のRAM(記憶手段)33、及び時間を計時するためのタイマ(TIM)34と互いにバス接続されている。CPU31は、ROM32に予め格納されている制御プログラムに従って入出力、演算等の処理を実行する。CPU31には、また、駆動回路22,23夫々の入力端子221,231に駆動信号を与えるための入出力ポート(I/O、信号出力手段)35,36がバス接続されている。

【0041】

以下、上述した構成における負荷駆動制御装置1の動作を場合分けして説明する。

(1)電源の電圧が立ち上がった場合

図2は、電源ラインBLの電圧が立ち上がった場合の負荷駆動制御装置1の動作の例を示すタイミングチャートである。図中横軸は時間(t)を表し、縦軸は、電源ラインBLの電圧(オン/オフ)、又は負荷駆動制御装置1の各部の電圧(H/L)を表す。図2(a)〜(g)は、夫々電源ラインBLの電圧、FETQ1のゲートの電圧、FETQ1のドレインの電圧、入力端子221の電圧、FETQ2のドレインの電圧、入出力ポート35が出力する駆動信号の電圧、及びFETQ3,Q4のドレインの電圧を示す。

【0042】

尚、抵抗R7及びコンデンサC2による時間遅れは、上記微分器の時定数に相当する時間より遙かに短いため、図2(d)では、入力端子221の電圧とFETQ2のゲートの電圧とがほぼ同時刻に変化するものとして示してある。また、時刻t0で図2(a)に示す電源ラインBLの電圧が立ち上がって制御部3にパワーオンリセットが発生し、パワーオンリセットが解除された後は、CPU31が、時刻t1までの間に入出力ポート35,36の初期化を含む初期化処理を行うものとする。これにより、時刻t0からt1までの間は、図2(f)に示すように、駆動信号の信号源インピーダンスがハイインピーダンスになるものとする(以下同様)。

【0043】

(1−1)時刻t0〜t1まで(所定時間)

時刻t0で電源ラインBLの電圧の立ち上がりがコンデンサC1により微分され、正の微分電圧(微分値)が抵抗R1,R2で分圧されてFETQ1のゲートに印加される。これにより、FETQ1がオンしてドレインが“L”となり、ダイオードD3が導通するため、抵抗R4,R5の接続点の電圧が低下して“L”となる。このため、入力端子221の電圧及びFETQ2のゲートの電圧も“L”となってFETQ2はオフとなり、FETQ2のドレイン及びFETQ3,Q4のゲートには抵抗R9を通じて電源ラインBLの電圧が印加される。従って、FETQ3,Q4がオフしてドレインが“L”となり、負荷L1が駆動されない状態となる。

【0044】

このように、FETQ1は、ダイオードD3を通じて抵抗R4,R5の接続点の電圧を“L”に制限するスイッチング素子(電圧制限器)として機能する。

尚、ダイオードD4,D14は、カソードがアノードより高電位となるため、導通しない状態となっている。また、ダイオードD3,D13は、駆動回路22のFETQ2のドレイン電圧と駆動回路23のFETQ13のドレイン電圧とが互いに干渉し合うのを防止する役目も果たしている。

【0045】

(1−2)時刻t1

時刻t1でCPU31が初期化処理を終えた場合、CPU31は、負荷L1の駆動状態を検出するために、入力ポートに設定してある入出力ポート35より入力端子221の電圧(H/L)を取り込む。その後、CPU31は、入出力ポート35を出力ポートに設定変更し、先に取り込んだ電圧の“H/L”に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“L”が出力される。

【0046】

(1−3)時刻t2

コンデンサC1及び抵抗R1,R2によって決まる時定数で上記微分電圧が低下し、時刻t2で所定の正の閾値を下回った場合、FETQ1のゲートの電圧が、FETQ1のオン/オフを反転させる閾値に達する。この場合、FETQ1がオフとなり、ドレインの電圧は、抵抗R4にプルアップされて“H”となるが、入力端子221には既に“L”の駆動信号が与えられているため、入力端子221の電圧に変化は生じない。従って、負荷L1が駆動されない状態が継続する。

【0047】

(1−4)時刻t3

本実施の形態1にあっては、時刻t0以前に電源がオンされているときの駆動信号の“H/L”の状態をRAM33に記憶してある。CPU31は、時刻t3でRAM33より上記状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。

例えば、駆動状態として“H”を記憶していたとき、CPU31は、時刻t3で駆動信号を“H”とする。これにより、入力端子221及びFETQ2のゲートの電圧が“H”となり、FETQ2がオンしてドレインが“L”となる。従って、FETQ3,Q4がオンしてドレインが“H”となり、負荷L1が駆動される状態となる。また、FETQ2のドレインが“L”となることにより、ダイオードD4が導通してFETQ1のゲートの電圧を確実に“L”とする。

【0048】

(2)電源の電圧が立ち上がるときにオン/オフを繰り返す場合

例えばバッテリB1を負荷駆動制御装置1に接続する場合、電源ラインBLの電圧が上下に変化するときは、電源ラインBLの電圧の立ち上がり及び立ち下がりがコンデンサC1によって微分されることとなる。

図3は、コンデンサC1及び抵抗R1の接続点に現れる微分電圧を模式的に示す説明図である。図3(a)は、仮にダイオードD2がない場合の微分電圧を示し、図3(b)は、ダイオードを図1のとおり接続してある場合の微分電圧を示す。

【0049】

(2−1)図3(a)に示す場合

ダイオードD2がない場合、電源ラインBLの電圧が立ち下がるときの微分器の時定数を決定する抵抗は、抵抗R1〜R3を直列に接続したものと等価になるため、このときの時定数は、前記電源がオンするときの時定数より大きくなることはない。この場合の微分電圧は、高/低変化する微分電圧によってコンデンサC1が充放電されるときに出入りする電荷の量が等しくなるまで、下側の包絡線が接地電位から負方向に離れるようになる。従って、微分電圧が低下してFETQ1がオンしなくなる虞がある。

【0050】

(2−2)図3(b)に示す場合

ダイオードD2を図1のとおり接続してある場合、電源ラインBLの電圧が立ち下がるときは、ダイオードD1が導通せずダイオードD2が導通するため、抵抗R3が微分器の時定数を決定する抵抗となる。ここで抵抗R3の抵抗値を抵抗R1及びR2の直列抵抗値より十分小さくした場合は、電源ラインBLの電圧が立ち上がった後にコンデンサC1の抵抗R1側から流出した正の電荷が、前記電源が立ち下がった後の比較的短い時間内に抵抗R3及びダイオードD2を通じて流入するようになる。従って、微分電圧の下側の包絡線が接地電位から負方向に離れることがないため、電源ラインBLの電圧が立ち上がった場合に、安定してFETQ1を導通させることができる。

【0051】

この場合、更に、抵抗R7及びコンデンサC2による遅れ時間を、電源ラインBLの電圧がオン/オフを繰り返す周期より比較的大きくしたときは、FETQ2がオフし続けるようにすることができる。これにより、FETQ3,Q4もオフし続けるため、電源ラインBLの電圧がオン/オフを繰り返す場合であっても、負荷L1が駆動されない状態を継続させることができる。

【0052】

(3)駆動信号により負荷L1が駆動されている場合

次に、図2の時刻t3が過ぎ、CPU31が“H/L”の駆動信号を駆動回路22に与える制御を行っている場合について説明する。

(3−1)FETQ1が故障した場合

FETQ1が、ドレイン及びソースが短絡する方向に故障した場合、ダイオードD3が導通して抵抗R4,R5の接続点の電圧が常に“L”となる。本実施の形態1にあっては、この場合にも入力端子221の電圧を“H”にする駆動電圧が与えられたときは、FETQ2がオンするように抵抗R5の抵抗値を定めてある。また、FETQ1が、ドレインが開放となる方向に故障した場合は、図2の時刻t2以降におけるFETQ1の状態と変わりがない。従って、FETQ1が、短絡又は開放の何れの方向に故障したとしても、駆動回路22は、CPU31から“H”(又は“L”)の駆動信号を与えられた場合に、負荷L1を駆動する(又は駆動しないようにする)ことができる。

【0053】

(3−2)電源ラインBLの電圧が変動した場合

入力端子221の電圧を“H”にする駆動電圧が与えられてFETQ2がオンしている場合に電源ラインBLの電圧が急激に上昇したときは、前記電圧の上昇分の立ち上がりがコンデンサC1により微分され、正の微分電圧(微分値)が抵抗R1,R2で分圧されてFETQ1のゲートに印加される。これにより、FETQ1がオンしてドレインが“L”となり、ダイオードD3が導通して抵抗R4,R5の接続点の電圧が“L”となる。この場合は、FETQ1が、ドレイン及びソースが短絡する方向に故障した場合、即ち(3−1)で上述した場合と同様であるため、駆動回路22は、負荷L1を駆動し続けることができる。

【0054】

(4)WDT(ウオッチドッグタイマ)によるリセットの場合

図4,5は、WDTによるリセットが発生した場合の負荷駆動制御装置1の動作の例を示すタイミングチャートである。図4,5では、夫々WDTによるリセットが発生したときに負荷L1を駆動していた場合と駆動していなかった場合とについて図示してある。図中横軸は時間(t)を表し、縦軸は、電源ラインBLの電圧(オン/オフ)、又は負荷駆動制御装置1の各部の電圧(H/L)を表す。図4(a)〜(g)は、夫々電源ラインBLの電圧、FETQ1のゲートの電圧、FETQ1のドレインの電圧、入力端子221の電圧、FETQ2のドレインの電圧、入出力ポート35が出力する駆動信号の電圧、及びFETQ3,Q4のドレインの電圧を示す(図5においても同様)。

【0055】

(4−1)図4に示す場合

時刻t0までは、図4(g)に示すようにFETQ3,Q4がオンしてドレインが“H”となり、負荷L1が駆動されている。時刻t0でWDTによるリセットが発生した場合、リセットによって入出力ポート35より出力される駆動信号の信号源インピーダンスがハイインピーダンスとなるが、図4(d)に示す入力端子221の電圧は既に“H”となっているため、FETQ2及びQ3,Q4がオンし続け、負荷L1が駆動され続ける。

【0056】

その後、時刻t1でCPU31が初期化処理を終えた場合、CPU31は、入力ポートに設定してある入出力ポート35より、負荷L1の駆動状態を検出するために入力端子221の電圧(H/L)を取り込む。そして、CPU31は、入出力ポート35を出力ポートに設定変更し、先に取り込んだ電圧の“H/L”に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“H”が出力される。

【0057】

時刻t3で、CPU31は、時刻t0以前にRAM33に記憶していた駆動信号の“H/L” の状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“H”となるが、駆動信号は、時刻t3以前に既に“H”となっているため、入力端子221、FETQ2のドレイン、FETQ3,Q4のドレイン、及びFETQ1のゲートには何の変化も現れない。

【0058】

尚、時刻t0〜t3又はそれ以降の何れの時点においても、FETQ2がオンしてドレインが“L”となっているため、ダイオードD4が導通してFETQ1のゲートは“L”を保持している。従って、この間に電源ラインBLの電圧が急激に上昇したとしても、FETQ1がオンしてドレインが“L”となることはなく、負荷L1は駆動され続ける。

【0059】

(4−2)図5に示す場合

時刻t0までは、駆動信号が入力端子221を“L”に駆動しており、FETQ2がオフしてドレインが“H”となり、FETQ3,Q4がオフしてのドレインが“L”となっているため、負荷L1は駆動されていない。時刻t0でWDTによるリセットが発生した場合、リセットによって入出力ポート35より出力される駆動信号の信号源インピーダンスがハイインピーダンスとなるため、入力端子221の電圧は、抵抗R4,R5を通じて電源ラインBLにプルアップされて“H”となる。これにより、FETQ2がオンしてドレインが“L”となり、FETQ3,Q4がオンしてのドレインが“H”となって負荷L1が駆動される。

【0060】

その後、時刻t1でCPU31が初期化処理を終えた場合については、図4の場合と同様であるため、その説明を省略する。

【0061】

時刻t3で、CPU31は、時刻t0以前にRAM33に記憶していた駆動信号の“H/L” の状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“L”となるため、入力端子221の電圧が“L”となり、FETQ2がオフしてドレインが“H”となる。従って、FETQ3,Q4がオフしてドレインが“L”となり、負荷L1が駆動されない時刻t0以前の状態に戻る。

【0062】

以下に、上述した構成の負荷駆動制御装置1の動作を、それを示すフローチャートを用いて説明する。

図6は、入力端子221の電圧に応じて駆動信号を出力するCPU31の処理手順を示すフローチャートであり、図7は、出力ポート設定のサブルーチンに係るCPU31の処理手順を示すフローチャートである。図6,7の処理は、ROM32に予め格納されている制御プログラムに従って実行される。また、図6の処理は、制御部3にリセット(例えば、パワーオンリセット又はWDTによるリセット)が発生した場合に起動されるようにしてある。

【0063】

図6の処理が起動された場合、CPU31は、RAM33の所定領域の初期化及び入出力ポート35,36の初期設定を含む初期化処理を行う(ステップS11)。この場合、入出力ポート35は入力ポートに設定する。その後、CPU31は、入出力ポート35を介して入力端子221の電圧(H/L)を取り込み(ステップS12)、入出力ポート35を出力ポートに設定変更する(ステップS13)。

【0064】

次いで、CPU31は、取り込んだ入力端子221の電圧が“H”であるか否かを判定する(ステップS14)。“H”であると判定した場合(ステップS14:YES)、CPU31は、引数を“H”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS15)、処理を終了する。“H”でないと判定した場合(ステップS14:NO)、CPU31は、引数を“L”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS16)、処理を終了する。

【0065】

図7に示す出力ポート設定に係るサブルーチンがメインルーチンから呼び出しされた場合、CPU31は、引数が“H”であるか否かを判定する(ステップS21)。“H”であると判定した場合(ステップS21:YES)、CPU31は、出力ポートに設定した入出力ポート35に“H”を出力させ(ステップS22)、RAM33の所定アドレスに“H”を記憶して(ステップS23)処理を終了する。“H”でないと判定した場合(ステップS21:NO)、CPU31は、出力ポートに設定した入出力ポート35に“L”を出力させ(ステップS24)、RAM33の所定アドレスに“L”を記憶して(ステップS25)処理を終了する。

【0066】

図8は、RAM33に記憶した負荷L1の駆動状態を読み出して駆動信号を出力するCPU31の処理手順を示すフローチャートである。以下の処理は、ROM32に予め格納されている制御プログラムに従って実行されるものであり、例えば図2,4,5の時刻t3において起動されるようにしてある。

尚、時刻t0以前に入力端子221に駆動信号が与えられる場合、CPU31が図7に示す出力ポート設定に係るサブルーチンを呼び出すことによってRAM33の所定のアドレスに駆動信号の“H/L”の状態が記憶されるものとする。

【0067】

図8の処理が起動された場合、CPU31は、RAM33の所定のアドレスの内容を読み出し(ステップS31)、読み出した値が“H”を示すものであるか否かを判定する(ステップS32)。“H”を示すものであると判定した場合(ステップS32:YES)、CPU31は、引数を“H”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS33)、処理を終了する。“H”を示すものではないと判定した場合(ステップS32:NO)、CPU31は、引数を“L”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS34)、処理を終了する。

【0068】

以上のように、本実施の形態1によれば、電源ラインに正の電圧を与えるバッテリを電源とし、電源ライン側と接地電位との間に直列に接続されたコンデンサ及び抵抗からなる微分器が電源ラインの電圧を微分した微分電圧に基づいて、入力端子を電源ラインにプルアップする抵抗の入力端子側と接地電位との間にダイオードを介して接続されたFET(スイッチング素子、電圧制限器)が導通する。

これにより、バッテリが接続されて電源ラインの電圧が立ち上がる場合、微分電圧が正方向に大きくなったときに、スイッチング素子が導通して、入力端子の電圧が負荷を駆動するに足りるレベルを超えないようにする。

従って、パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能となる。

【0069】

また、電源ラインの電圧を微分する場合、電源がオフする方向に微分するときは、微分器のコンデンサ及び抵抗の接続点と接地電位との間に接続されたダイオードが接地電位からコンデンサに向けて導通する。このため、電源がオフする方向に微分するときの時定数はダイオードと並列に接続された抵抗の抵抗値分だけ小さくなり、微分値が微分前の値に戻るまでの時間がその分だけ短くなる。

これにより、例えば、電源ラインの電圧を立ち上げる場合に、バッテリを接続するための接点にチャタリングが発生して電源ラインの電圧が上下に変化したとしても、微分電圧の下側の包絡線が接地電位から離れることを抑制する。この場合、電源が断続的に接続されたとしても、接続の都度微分電圧が正方向に大きくなってスイッチング素子が導通し、入力端子の電圧を制限する。

従って、チャタリング時間より大きい時定数で入力端子の電圧を積分して遅延させることにより、電源が短時間内にオン/オフを繰り返したとしても、積分値が負荷を駆動するに足りるレベルを越えないようにして、負荷が駆動されない状態を継続することが可能となる。

【0070】

更にまた、FET(スイッチング素子)のゲートにアノードが接続されたダイオードが、負荷が駆動された場合に接地電位へ導通する。

従って、一旦電源の電圧が立ち上がって負荷が駆動された後に、更に電圧が上昇した場合であっても、スイッチング素子(電圧制限器)が入力端子の電圧を制限することがないため、負荷が駆動されない状態を継続することが可能となる。

【0071】

更にまた、時刻t0から時刻t2まで、微分器の微分電圧を分圧した電圧がFET(スイッチング素子)のゲートの閾値を越えるようにしてあるため、時刻t0から少なくとも時刻t1が経過するまでは、前記FETが導通し続ける。

従って、電源がオンされた時から少なくとも負荷を駆動するための信号が入力端子に与えられるまでは、スイッチング素子(電圧制限器)が入力端子の電圧を制限して負荷が駆動されない状態を継続することが可能となる。

【0072】

更にまた、入力端子を電源ラインにプルアップする抵抗及びFET(スイッチング素子)の接続点と入力端子との間に接続された抵抗の抵抗値は、入力端子に駆動信号が負荷を駆動するように与えられた場合に、前記FETが導通している/いないに関わらず、入力端子の電圧が負荷を駆動するに足りるレベルを越えることになる値としてある。

従って、スイッチング素子(電圧制限器)が短絡又は開放の何れの方向に故障したとしても、負荷を駆動するための信号が与えられた場合に負荷を駆動することが可能となる。また、負荷を駆動するための信号が与えられて負荷を駆動している場合に、電源の電圧が急上昇してスイッチング素子(電圧制限器)が入力端子の電圧を制限したとしても、負荷の駆動を継続することが可能となる。

【0073】

更にまた、負荷駆動装置の入力端子に駆動信号を与える前に負荷の駆動状態として入力端子の電圧(H/L)を取り込み、取り込んだ電圧の“H/L”に対応する“H/L”の駆動信号を入力端子に与える。

従って、例えば、ウオッチドッグタイマによるリセットの場合は、負荷駆動装置に負荷の駆動を継続させ、パワーオンリセットの場合は、負荷駆動装置に負荷を駆動しない状態を継続させることが可能となる。

【0074】

更にまた、負荷を駆動させるように駆動信号を与えているか否かを不揮発性のRAMに記憶する。その後、リセットが発生した場合、RAMの記憶内容に基づいて、駆動信号を入力端子に与える。

従って、例えば、電源が一旦オフされた後に再度オンされた場合、前回電源がオンされていたときと同じ信号を入力端子に与えることが可能となる。

【0075】

尚、本実施の形態1にあっては、図1に示すように負荷駆動装置2が2つの駆動回路22,23を備えているが、これに限定されるものではなく、駆動回路を1つ、又は3つ以上備えるようにしてもよい。

【0076】

また、正の電圧を与えるバッテリB1を用いているが、これに限定されるものではなく、負の電圧を与えるバッテリを用いてもよい。この場合は、制御部3及び負荷駆動装置2が負電圧で動作するように構成する。

【0077】

更にまた、パワーオンリセット及びWDTによるリセットでは、リセットが発生している時間に差がないものとして図2,4,5を描いてあるが、これに限定されるものではなく、リセットの種類によって時刻t1が変動したとしても、時刻t2が後になる限り影響がない。

【0078】

更にまた、負荷駆動装置2の入力端子221,231に駆動信号を与える前に負荷L1,L2の駆動状態として入力端子221,231の電圧(H/L)を取り込んでいるが、これに限定されるものではなく、例えば、負荷駆動装置2の出力の電圧(H/L)を取り込むようにしてもよい。

【0079】

(実施の形態2)

実施の形態1が、電源の立ち上がりを微分した微分電圧に基づいて、スイッチング素子に負荷駆動回路の入力端子の電圧を制限させる形態であるのに対し、実施の形態2は、負荷駆動回路の入力端子の電圧の立ち上がりを時間遅延させた遅延電圧を駆動回路に与える形態である。

【0080】

図9は、本発明の実施の形態2に係る負荷駆動制御装置1aの接続例を示す回路図である。図中1aは負荷駆動制御装置であり、負荷駆動制御装置1aは、ECUからなる負荷L1を駆動する駆動回路22a及び遅延回路21aを有する負荷駆動装置2aと、負荷駆動装置2aの入力端子221aに駆動信号を与える制御部3とを備える。負荷駆動装置2a及び制御部3は、ヒューズF1を介して外部のバッテリ(電源)B1から正の電圧を与えられる電源ライン(所定電位)BLと接続されている。

【0081】

遅延回路21aは、入力端子221a及び接地電位の間に直列に接続されて遅延器を構成する抵抗R21及びコンデンサC21と、抵抗R21の両端子の間に直列に接続されており、カソードが入力端子221aに接続されたダイオードD21及び抵抗R22とを備える。入力端子221aは、抵抗R4(所定の回路素子)を通じて電源ラインBLにプルアップしてある。

【0082】

駆動回路22aは、遅延回路21aの抵抗R21及びコンデンサC21の接続点にゲートが接続されたソース接地のNチャネル型のFETQ2を備える。FETQ2のドレインは、一端子が電源ラインBLに接続された抵抗R9の他端子と、ソース及びドレインが夫々電源ラインBL及び負荷L1に接続されたPチャネル型FETQ3,Q4のゲートとに抵抗R8を介して接続されている。抵抗R9には、カソードが電源ラインBLに接続されたツェナーダイオードZD1が並列に接続されている。

【0083】

制御部3のCPU31には、負荷駆動装置2aの入力端子221aに駆動信号を与えるための入出力ポート(信号出力手段)35と、負荷L1の駆動状態を検出するための入出力ポート37とがバス接続されている。

【0084】

以下、上述した構成における負荷駆動制御装置1aの動作を場合分けして説明する。

(1)電源の電圧が立ち上がった場合

図10は、電源ラインBLの電圧が立ち上がった場合の負荷駆動制御装置1aの動作の例を示すタイミングチャートである。図中横軸は時間(t)を表し、縦軸は、電源ラインBLの電圧(オン/オフ)、又は負荷駆動制御装置1aの各部の電圧(H/L)を表す。図10(a)〜(f)は、夫々電源ラインBLの電圧、入力端子221aの電圧、FETQ2のゲートの電圧、FETQ2のドレインの電圧、入出力ポート35が出力する駆動信号の電圧、及びFETQ3,Q4のドレインの電圧を示す。(後述する図11においても同様)

【0085】

尚、時刻t0で図10(a)に示す電源ラインBLの電圧が立ち上がって制御部3にパワーオンリセットが発生し、パワーオンリセットが解除された後は、CPU31が、時刻t1までの間に入出力ポート35,37の初期化を含む初期化処理を行うものとする。これにより、時刻t0からt1までの間は、図10(e)に示すように、駆動信号の信号源インピーダンスがハイインピーダンスになるものとする(以下同様)。

【0086】

(1−1)時刻t0〜t1まで(所定時間)

時刻t0で電源ラインBLの電圧が立ち上がった場合、抵抗R4を通じて電源ラインBLにプルアップされた入力端子221aの電圧は即座に上昇する。この場合、時刻t0からコンデンサC21に電荷が蓄積され始めるため、入力端子221aの電圧は、電源ラインBLの電圧を抵抗R4及びR21で分圧した電圧を開始電圧として、電源ラインBLの電圧に向けて緩やかに上昇する。

【0087】

一方、抵抗R21及びコンデンサC21からなる遅延器の遅延電圧(遅延値)が与えられるFETQ2のゲートの電圧は、図10(c)に示すように接地電位から電源ラインBLの電圧に向けて上昇する。但し、少なくとも時刻t1までは、FETQ2のゲートの電圧がFETQ1をオンさせる閾値に達することがないため、FETQ2はオフしており、FETQ2のドレイン及びFETQ3,Q4のゲートには抵抗R9を通じて電源ラインBLの電圧が印加される。従って、FETQ3,Q4がオフしてドレインが“L”となり、負荷L1が駆動されない状態となる。

【0088】

(1−2)時刻t1

時刻t1でCPU31が初期化処理を終えた場合、CPU31は、負荷L1の駆動状態を検出するために、入力ポートに設定してある入出力ポート37よりFETQ3,4のドレインの電圧(H/L)を取り込み、取り込んだ電圧の“H/L”に対応する駆動信号を入出力ポート35より出力する。これにより、駆動信号は“L”となり、入力端子221aの電圧は接地電位となる。

【0089】

この場合、入力端子221a及びコンデンサC21の間には、ダイオードD21及び抵抗R22が接続してあり、抵抗R22の抵抗値は、抵抗R4及びR21の抵抗値より十分に小さい値であるため、コンデンサC21に蓄積されている電荷はR22を通じて急速に放電される。従って、FETQ2のゲートの電圧は速やかに下降し、FETQ2はオフを継続する。

【0090】

(1−3)時刻t3

時刻t3で、CPU31は、時刻t0以前にRAM33に記憶していた駆動信号の“H/L” の状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。例えば、時刻t0以前にRAM33に記憶していた駆動信号の状態が“H”であった場合、時刻t3で駆動信号は“H”となり、入力端子221aの電圧も“H”となる。この場合、入力端子221aの電圧は、接地電位を開始電圧とし、抵抗R21及びコンデンサC21によって決まる時定数で駆動信号の“H”の電圧に向けて比較的速やかに上昇する。

【0091】

(1−4)時刻t4

時刻t4でFETQ2のゲートの電圧がFETQ1のオン/オフを反転させる閾値に達した場合、FETQ2がオンしてドレインが“L”となる。従って、FETQ3,Q4がオンしてドレインが“H”となり、負荷L1が駆動される状態となる。

【0092】

(2)WDT(ウオッチドッグタイマ)によるリセットの場合

図11は、WDTによるリセットが発生した場合の負荷駆動制御装置1aの動作の例を示すタイミングチャートである。図11では、例として、WDTによるリセットが発生したときに負荷L1を駆動していた場合について図示してある。図中横軸は時間(t)を表し、縦軸は、電源ラインBLの電圧(オン/オフ)、又は負荷駆動制御装置1aの各部の電圧(H/L)を表す。

【0093】

時刻t0までは、図11(f)に示すようにFETQ3,Q4がオンしてドレインが“H”となり、負荷L1が駆動されている。時刻t0でWDTによるリセットが発生した場合、リセットによって入出力ポート35より出力される駆動信号の信号源インピーダンスがハイインピーダンスとなるが、図11(c)に示すFETQ2のゲートの電圧は既に“H”となっているため、FETQ2及びQ3,Q4がオンし続け、負荷L1が駆動され続ける。

【0094】

その後、時刻t1でCPU31が初期化処理を終えた場合、CPU31は、負荷L1の駆動状態を検出するために、入力ポートに設定してある入出力ポート37よりFETQ3,4のドレインの電圧(H/L)を取り込み、取り込んだ電圧の“H/L”に対応する駆動信号を入出力ポート35より出力する。これにより、駆動信号は“H”となり、入力端子221aの電圧は継続して“H”となるため、負荷L1は駆動され続ける。

【0095】

時刻t3で、CPU31は、時刻t0以前にRAM33に記憶していた駆動信号の“H/L” の状態を読み出し、読み出した状態の“H/L” に対応するように駆動信号の“H/L”を決定して入出力ポート35より出力する。これにより、駆動信号は“H”となるが、駆動信号は、時刻t3以前に既に“H”となっているため、入力端子221a、FETQ2のドレイン、FETQ3,Q4のドレイン、及びFETQ1のゲートには何の変化も現れない。

【0096】

以下に、上述した構成の負荷駆動制御装置1aの動作を、それを示すフローチャートを用いて説明する。

図12は、駆動回路22aの出力の電圧に応じて駆動信号を出力するCPU31の処理手順を示すフローチャートである。図12の処理は、ROM32に予め格納されている制御プログラムに従って実行される。また、図12の処理は、制御部3にリセット(例えば、パワーオンリセット又はWDTによるリセット)が発生した場合に起動されるようにしてある。

【0097】

図12の処理が起動された場合、CPU31は、RAM33の所定領域の初期化及び入出力ポート35,37の初期設定を含む初期化処理を行う(ステップS41)。この場合、入出力ポート35,37を夫々出力ポート及び入力ポートに設定する。その後、CPU31は、入出力ポート37を介して駆動回路22aの出力(即ちFETQ3,Q4のドレイン)の電圧(H/L)を取り込み(ステップS42)、取り込んだ駆動回路22aの出力の電圧が“H”であるか否かを判定する(ステップS43)。

【0098】

駆動回路22aの出力の電圧が“H”であると判定した場合(ステップS43:YES)、CPU31は、引数を“H”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS44)、処理を終了する。“H”でないと判定した場合(ステップS43:NO)、CPU31は、引数を“L”にして出力ポート設定に係るサブルーチンを呼び出して実行し(ステップS45)、処理を終了する。

【0099】

その他、実施の形態1に対応する箇所には同様の符号を付して、その詳細な説明を省略する。

【0100】

以上のように、本実施の形態2によれば、電源ラインに正の電圧を与えるバッテリを電源とし、電源ラインに抵抗を通じてプルアップされた入力端子と接地電位との間に直列に接続された抵抗及びコンデンサからなる遅延器が入力端子の電圧の立ち上がりを遅延させた遅延電圧の高低に基づいて、駆動回路が負荷を駆動する。

これにより、電源ラインにプルアップされた入力端子の電圧が、電源ラインの電圧と共に立ち上がる場合、入力端子の電圧の立ち上がりを遅延させた遅延電圧が低いときに、駆動回路が負荷を駆動しないようにする。

従って、パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能となる。

【0101】

また、時刻t0から時刻t2まで、遅延器の遅延電圧がFET(スイッチング素子)のゲートの閾値を越えないようにしてあるため、時刻t0から少なくとも時刻t1が経過するまでは、前記FETが導通しないこととなる。

従って、電源がオンされた時から少なくとも負荷を駆動するための信号が入力端子に与えられるまでは、遅延器が入力端子の電圧の立ち上がりを遅延させ、遅延電圧によって負荷が駆動されない状態を継続することが可能となる。

【0102】

尚、本実施の形態2にあっては、図10,11の時刻t1で負荷L1の駆動状態を検出するために、入出力ポート37よりFETQ3,4のドレインの電圧(H/L)を取り込んでいるが、これに限定されるものではなく、実施の形態1のように、入力端子221aの電圧(H/L)を取り込むようにしてもよい。

【符号の説明】

【0103】

1、1a 負荷駆動制御装置

2、2a 負荷駆動装置

22、23、22a 駆動回路

221、221a、231 入力端子

3 制御部

31 CPU

32 ROM

33 RAM(不揮発性の記憶手段)

35、36 入出力ポート(信号出力手段)

37 入出力ポート(負荷の駆動状態を検出する手段)

B1 バッテリ(電源)

BL 電源ライン(所定電位)

C1 コンデンサ(微分器の一部)

C21 コンデンサ(遅延器の一部)

D2 ダイオード(微分器の一部)

L1、L2 負荷

Q1 FET(スイッチング素子、電圧制限器)

R1、R2、R3 抵抗(微分器の一部)

R4 抵抗(所定の回路素子)

R5 抵抗(電圧制限器及び回路素子の接続点と入力端子との間に接続された抵抗)

R21 抵抗(遅延器の一部)

【特許請求の範囲】

【請求項1】

電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子を有し、該入力端子は所定の回路素子を介して前記電源に基づく所定電位に接続してあり、前記入力端子の電圧の高低に基づいて前記負荷を駆動する負荷駆動装置において、

前記電源の電圧を微分する微分器と、

該微分器で微分した微分値に基づいて前記回路素子の前記入力端子側の電圧を前記負荷を駆動しない電圧に制限する電圧制限器と

を備えることを特徴とする負荷駆動装置。

【請求項2】

前記微分器は、前記電源がオフする場合の時定数をオンする場合の時定数より小さくしてあることを特徴とする請求項1に記載の負荷駆動装置。

【請求項3】

電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子を有し、該入力端子は所定の回路素子を介して前記電源に基づく所定電位に接続してあり、前記入力端子の電圧の高低に基づいて前記負荷を駆動する負荷駆動装置において、

前記電源側及び接地側の間に直列に接続されたコンデンサ及び抵抗からなり、前記電源の電圧を微分する微分器と、

接地側及び前記回路素子の前記入力端子側の間に接続されており、前記微分器で微分した微分値に基づいて導通するスイッチング素子からなる電圧制限器と

を備えることを特徴とする負荷駆動装置。

【請求項4】

前記微分器は、前記コンデンサ及び抵抗の接続点と接地側との間に、前記電源の電圧が立ち下がる(又は立ち上がる)時に導通する方向にダイオードを接続してあることを特徴とする請求項3に記載の負荷駆動装置。

【請求項5】

前記スイッチング素子は、導通を制御するための端子を有し、

該端子にアノードが接続されており、前記負荷が駆動された場合に接地側へ導通するダイオードを備えること

を特徴とする請求項3又は4に記載の負荷駆動装置。

【請求項6】

前記電圧制限器は、前記微分値が所定の正の閾値(又は負の閾値)を越える場合に動作するようにしてあり、

前記微分器は、前記時間が経過するまで微分値が前記閾値を越えるようにしてあること

を特徴とする請求項1から5までの何れか1項に記載の負荷駆動装置。

【請求項7】

前記電圧制限器及び回路素子の接続点と前記入力端子との間に抵抗を接続してあり、

該抵抗の抵抗値は、前記信号が前記負荷を駆動するように与えられた場合、前記電圧制限器の動作に関わらず前記入力端子の電圧が前記負荷を駆動する電圧を越えることになる値にしてあることを特徴とする請求項1から6までの何れか1項に記載の負荷駆動装置。

【請求項8】

電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子と、前記電源に基づく所定電位及び前記入力端子の間に接続された所定の回路素子と、前記入力端子の電圧の高低に基づいて前記負荷を駆動する駆動回路とを備える負荷駆動装置において、

前記入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させる遅延器を備え、

前記駆動回路は、前記遅延器が遅延させた遅延電圧の高低に基づいて前記負荷を駆動するようにしてあること

を特徴とする負荷駆動装置。

【請求項9】

電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子と、前記電源に基づく所定電位及び前記入力端子の間に接続された所定の回路素子と、前記入力端子の電圧の高低に基づいて前記負荷を駆動する駆動回路とを備える負荷駆動装置において、

前記入力端子及び接地側の間に直列に接続された抵抗及びコンデンサからなり、前記入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させる遅延器を備え、

前記駆動回路は、前記遅延器が遅延させた遅延電圧の高低に基づいて前記負荷を駆動するようにしてあること

を特徴とする負荷駆動装置。

【請求項10】

前記駆動回路は、前記遅延電圧が所定の正の閾値(又は負の閾値)を越える場合に動作するようにしてあり、

前記遅延器は、前記時間が経過するまで遅延電圧が前記閾値を越えないようにしてあること

を特徴とする請求項8又は9に記載の負荷駆動装置。

【請求項11】

請求項1から10までの何れか1項に記載の負荷駆動装置と、

前記信号を前記入力端子に与える信号出力手段と、

該信号出力手段が前記信号を与える前に前記負荷の駆動状態を検出する手段とを備え、

該手段が検出した駆動状態に基づいて、前記信号出力手段が前記信号を与えるようにしてあること

を特徴とする負荷駆動制御装置。

【請求項12】

前記信号出力手段が前記負荷を駆動させるように前記信号を与えているか否かを記憶する不揮発性の記憶手段を備え、

前記信号出力手段は、前記記憶手段の記憶内容に基づいて、前記信号を与えるようにしてあること

を特徴とする請求項11に記載の負荷駆動制御装置。

【請求項1】

電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子を有し、該入力端子は所定の回路素子を介して前記電源に基づく所定電位に接続してあり、前記入力端子の電圧の高低に基づいて前記負荷を駆動する負荷駆動装置において、

前記電源の電圧を微分する微分器と、

該微分器で微分した微分値に基づいて前記回路素子の前記入力端子側の電圧を前記負荷を駆動しない電圧に制限する電圧制限器と

を備えることを特徴とする負荷駆動装置。

【請求項2】

前記微分器は、前記電源がオフする場合の時定数をオンする場合の時定数より小さくしてあることを特徴とする請求項1に記載の負荷駆動装置。

【請求項3】

電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子を有し、該入力端子は所定の回路素子を介して前記電源に基づく所定電位に接続してあり、前記入力端子の電圧の高低に基づいて前記負荷を駆動する負荷駆動装置において、

前記電源側及び接地側の間に直列に接続されたコンデンサ及び抵抗からなり、前記電源の電圧を微分する微分器と、

接地側及び前記回路素子の前記入力端子側の間に接続されており、前記微分器で微分した微分値に基づいて導通するスイッチング素子からなる電圧制限器と

を備えることを特徴とする負荷駆動装置。

【請求項4】

前記微分器は、前記コンデンサ及び抵抗の接続点と接地側との間に、前記電源の電圧が立ち下がる(又は立ち上がる)時に導通する方向にダイオードを接続してあることを特徴とする請求項3に記載の負荷駆動装置。

【請求項5】

前記スイッチング素子は、導通を制御するための端子を有し、

該端子にアノードが接続されており、前記負荷が駆動された場合に接地側へ導通するダイオードを備えること

を特徴とする請求項3又は4に記載の負荷駆動装置。

【請求項6】

前記電圧制限器は、前記微分値が所定の正の閾値(又は負の閾値)を越える場合に動作するようにしてあり、

前記微分器は、前記時間が経過するまで微分値が前記閾値を越えるようにしてあること

を特徴とする請求項1から5までの何れか1項に記載の負荷駆動装置。

【請求項7】

前記電圧制限器及び回路素子の接続点と前記入力端子との間に抵抗を接続してあり、

該抵抗の抵抗値は、前記信号が前記負荷を駆動するように与えられた場合、前記電圧制限器の動作に関わらず前記入力端子の電圧が前記負荷を駆動する電圧を越えることになる値にしてあることを特徴とする請求項1から6までの何れか1項に記載の負荷駆動装置。

【請求項8】

電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子と、前記電源に基づく所定電位及び前記入力端子の間に接続された所定の回路素子と、前記入力端子の電圧の高低に基づいて前記負荷を駆動する駆動回路とを備える負荷駆動装置において、

前記入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させる遅延器を備え、

前記駆動回路は、前記遅延器が遅延させた遅延電圧の高低に基づいて前記負荷を駆動するようにしてあること

を特徴とする負荷駆動装置。

【請求項9】

電源がオンされた時から所定時間の経過後に負荷を駆動するための信号が与えられる入力端子と、前記電源に基づく所定電位及び前記入力端子の間に接続された所定の回路素子と、前記入力端子の電圧の高低に基づいて前記負荷を駆動する駆動回路とを備える負荷駆動装置において、

前記入力端子及び接地側の間に直列に接続された抵抗及びコンデンサからなり、前記入力端子の電圧の立ち上がり(又は立ち下がり)を遅延させる遅延器を備え、

前記駆動回路は、前記遅延器が遅延させた遅延電圧の高低に基づいて前記負荷を駆動するようにしてあること

を特徴とする負荷駆動装置。

【請求項10】

前記駆動回路は、前記遅延電圧が所定の正の閾値(又は負の閾値)を越える場合に動作するようにしてあり、

前記遅延器は、前記時間が経過するまで遅延電圧が前記閾値を越えないようにしてあること

を特徴とする請求項8又は9に記載の負荷駆動装置。

【請求項11】

請求項1から10までの何れか1項に記載の負荷駆動装置と、

前記信号を前記入力端子に与える信号出力手段と、

該信号出力手段が前記信号を与える前に前記負荷の駆動状態を検出する手段とを備え、

該手段が検出した駆動状態に基づいて、前記信号出力手段が前記信号を与えるようにしてあること

を特徴とする負荷駆動制御装置。

【請求項12】

前記信号出力手段が前記負荷を駆動させるように前記信号を与えているか否かを記憶する不揮発性の記憶手段を備え、

前記信号出力手段は、前記記憶手段の記憶内容に基づいて、前記信号を与えるようにしてあること

を特徴とする請求項11に記載の負荷駆動制御装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2010−239531(P2010−239531A)

【公開日】平成22年10月21日(2010.10.21)

【国際特許分類】

【出願番号】特願2009−87160(P2009−87160)

【出願日】平成21年3月31日(2009.3.31)

【出願人】(395011665)株式会社オートネットワーク技術研究所 (2,668)

【出願人】(000183406)住友電装株式会社 (6,135)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

【公開日】平成22年10月21日(2010.10.21)

【国際特許分類】

【出願日】平成21年3月31日(2009.3.31)

【出願人】(395011665)株式会社オートネットワーク技術研究所 (2,668)

【出願人】(000183406)住友電装株式会社 (6,135)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

[ Back to top ]