負荷駆動装置

【課題】複数の駆動回路とスイッチング素子との接続点を通じて、内部回路や基準点に電流が回り込むことを防止する。

【解決手段】電流の回り込みが発生し得る回り込み防止対象となる内部回路16、26とスイッチング素子であるIGBT1との間に回り込み防止回路15、25を配置する。そして、駆動回路10、20のうち作動させられない側の回り込み防止回路15、25をオフすることで、回り込み防止対象となる内部回路16、26にスイッチング素子となるIGBT1のゲート電圧が印加されないようにする。これにより、各内部回路16、26内で電流の回り込みが発生することを防止することが可能となる。

【解決手段】電流の回り込みが発生し得る回り込み防止対象となる内部回路16、26とスイッチング素子であるIGBT1との間に回り込み防止回路15、25を配置する。そして、駆動回路10、20のうち作動させられない側の回り込み防止回路15、25をオフすることで、回り込み防止対象となる内部回路16、26にスイッチング素子となるIGBT1のゲート電圧が印加されないようにする。これにより、各内部回路16、26内で電流の回り込みが発生することを防止することが可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電流の回り込み防止機能を有する負荷駆動装置に関するものである。

【背景技術】

【0002】

従来、特許文献1において、直流電源の正側と負側との間に接続される平滑用コンデンサに蓄積された電荷を放電する際に、全スイッチング素子をオン状態にし、過電流になる前にスイッチング素子をオフにする技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−232620号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、スイッチング素子の駆動制御を行うことで平滑用コンデンサに蓄積された電荷を放電することが可能となるものの、スイッチング素子の駆動制御を行う駆動回路に対する電力の供給が絶たれるとスイッチング素子を駆動できずに放電も行えなくなるという問題がある。この問題を解決する方法として、通常時に作動する駆動回路(以下、通常時駆動回路という)とは別に放電時に作動する駆動回路(以下、放電時駆動回路という)を設け、これら二つの駆動回路に別々の電源から供給が行われるようにするという回路構成が考えられる。

【0005】

ところが、二つの駆動回路から個別に出力する駆動信号によってスイッチング素子の駆動制御を行おうとすると、各駆動回路の接続点を通じて、一方の駆動回路から他方の駆動回路に電流が回り込む可能性がある。

【0006】

これに対して、図5に示す回路構成を採用することで、一方の駆動回路から他方の駆動回路に電流が回り込むことを防止することが可能となる。この回路構成では、スイッチング素子としてIGBT100を用いており、IGBT100を通常時駆動回路110と放電時駆動回路120にて駆動する。例えば、基本的には、通常時駆動回路110にてIGBT100を駆動し、緊急時には、通常時駆動回路110によるIGBT100を行わず、放電時駆動回路120を用いて確実にIGBT100に蓄積された電荷を引き抜くようにする。

【0007】

各駆動回路110、120は、駆動電圧生成回路111、121とオン側回路112、122およびオフ側回路113、123などを備えた構成とされ、別々の電源130、140からの電源供給に基づいて作動する。

【0008】

具体的には、各駆動回路110、120は、駆動電圧生成回路111、121が電源130、140からの電源供給に基づいてIGBT100のゲートに対して印加する駆動電圧を生成している。駆動電圧生成回路111の出力端子とIGBT100のゲートとの間にオン側回路112、122が備えられており、オン側回路112、122によって駆動電圧生成回路111、121とIGBT100との間をオン(接続)すると、駆動電圧生成回路111、121で生成される駆動電圧がオン側回路112、122を介してIGBT100に印加され、IGBT100が駆動される。また、IGBT100のゲートと基準電位とされる基準点との間にオフ側回路113、123が接続され、オフ側回路113、124によってIGBT100のゲートと基準点との間をオン(接続)すると、IGBT100に蓄積された電荷が基準点側に引き抜かれ、IGBT100がオフされる。

【0009】

このような構成において、オン側回路112、122とオフ側回路113、123との間に抵抗114a、114b、124a、124bを配置し、抵抗114a、124aと抵抗114b、124bの間に駆動電圧生成回路111、121の出力端子を接続すると共に、オン側回路112、122と抵抗114a、124aの間と電源130、140との間にスイッチ150、160を備えている。これらスイッチ150、160により、各駆動電源130、140とIGBT100をオンさせるためのオン側回路112、122との間をオンオフ制御できるようにしている。

【0010】

そして、通常時駆動回路110によってIGBT100を駆動する際には、放電時駆動回路120のスイッチ160をオフする。これにより、IGBT100のゲートに接続された各駆動回路110、120の接続点を通じて、オン側回路122やオフ側回路123を介して電源140側に電流が回り込もうとしても、抵抗114a、114bによって大きく減衰されることで、電流の回り込みを防止することが可能となる。逆に、放電時駆動回路120によってIGBT100を駆動する際には、通常時駆動回路110のスイッチ150をオフする。これにより、IGBT100のゲートに接続された各駆動回路110、120の接続点を通じて、オン側回路112やオフ側回路113を介して電源130側に電流が回り込もうとしても、抵抗124a、124bによって大きく減衰されることで、電流の回り込みを防止することが可能となる。このようにして、電流の回り込みを防止することが可能となる。

【0011】

しかし、各駆動回路110、120の電源130、140側を切り離して電流の回り込みを防止したとしても、IGBT100のゲートから基準点や内部回路に電流が回り込む回路構成とされる場合があり、上記の構成では、このような場合における電流の回り込みを防止できない。このため、このような場合の電流の回り込みが防止できるようにすることが望まれる。

【0012】

なお、ここではIGBT100のゲートからの電流の回り込みについて説明したが、IGBT100の他の部位、例えばセンス端子などのように複数の駆動回路が共通して接続される接続点を有する構成においても、電流の回り込みが発生する可能性がある。

【0013】

本発明は上記点に鑑みて、スイッチング素子の駆動を行う複数の駆動回路が備えられる場合において、複数の駆動回路とスイッチング素子との接続点を通じて、内部回路や基準点に電流が回り込むことを防止できる負荷駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0014】

上記目的を達成するため、請求項1に記載の発明では、第1駆動回路(10)には、スイッチング素子(1)の所定部位と電気的に接続される第1内部回路(16)が備えられていると共に、第2駆動回路(20)にも、スイッチング素子(1)の所定部位と電気的に接続される第2内部回路(26)が備えられており、第1駆動回路(10)の第1内部回路(16)とスイッチング素子(1)との間に、第2駆動回路(20)がスイッチング素子(1)を制御するときに、第1内部回路(16)とスイッチング素子(1)との間をオフすることで、第2内部回路(26)とスイッチング素子(1)との接続点から第1内部回路(16)への電流の回り込み防止する第1回り込み防止回路(15)が備えられていると共に、第2駆動回路(20)の第2内部回路(26)とスイッチング素子(1)との間に、第1駆動回路(10)がスイッチング素子(1)を制御するときに、第2内部回路(26)とスイッチング素子(1)との間をオフすることで、第1内部回路(16)とスイッチング素子(1)との接続点から第2内部回路(26)への電流の回り込み防止する第2回り込み防止回路(25)が備えられていることを特徴としている。

【0015】

このように、電流の回り込みが発生し得る回り込み防止対象となる第1、第2内部回路(16、26)とスイッチング素子(1)との間に第1、第2回り込み防止回路(15、25)を配置している。そして、第1、第2駆動回路(10、20)のうち作動させられない側の回り込み防止回路(15、25)をオフすることで、回り込み防止対象となる内部回路(16、26)にスイッチング素子(1)の所定部位の電圧が印加されないようにしている。これにより、電流の回り込みが発生することを防止することが可能となる。

【0016】

例えば、請求項2に記載したように、第1回り込み防止回路(15)は、第1電源(30)からの電源供給に基づいて定電流を生成する定電流源(15a)と、定電流源(15a)の定電流の流れをオンオフする制御スイッチ(15b)と、定電流源(15a)から流される定電流に基づいて第1内部回路(16)とスイッチング素子(1)との間のオンオフを制御するMOSFET(15g)と、MOSFET(15g)のゲートと所定電位とされる基準点との間に接続されたPNPトランジスタ(15e)と、PNPトランジスタ(15e)のベース−コレクタ間を参照電圧に固定する参照電圧回路(15f)とを有した構成とすることができる。この場合、第2駆動回路(20)がスイッチング素子(1)を制御するときに、当該第1回り込み回路(15)に備えられる制御スイッチ(15b)をオフしてMOSFET(15g)をオフすることで、第1内部回路(16)とスイッチング素子(1)との間をオフする。また、第2回り込み防止回路(25)も、第2電源(40)からの電源供給に基づいて定電流を生成する定電流源(25a)と、定電流源(25a)の定電流の流れをオンオフする制御スイッチ(25b)と、定電流源(25a)から流される定電流に基づいて第2内部回路(26)とスイッチング素子(1)との間のオンオフを制御するMOSFET(25g)と、MOSFET(25g)のゲートと所定電位とされる基準点との間に接続されたPNPトランジスタ(25e)と、PNPトランジスタ(25e)のベース−コレクタ間を参照電圧に固定する参照電圧回路(25f)とを有した構成とすることができる。この場合、第1駆動回路(10)がスイッチング素子(1)を制御するときに、当該第2回り込み回路(25)に備えられる制御スイッチ(25b)をオフしてMOSFET(25g)をオフすることで、第2内部回路(26)とスイッチング素子(1)との間をオフする。

【0017】

請求項3に記載の発明では、第1回り込み防止回路(15)に備えられるMOSFET(15g)のゲートにはツェナーダイオード(15c)とPNPトランジスタ(15d)が接続され、これらツェナーダイオード(15c)のツェナー降伏電圧とPNPトランジスタ(15d)の順方向電圧VfによってMOSFET(15g)のゲート−ソース間が固定されており、第2回り込み防止回路(25)に備えられるMOSFET(25g)のゲートにもツェナーダイオード(25c)とPNPトランジスタ(25d)が接続され、これらツェナーダイオード(25c)のツェナー降伏電圧とPNPトランジスタ(25d)の順方向電圧VfによってMOSFET(25g)のゲート−ソース間が固定されていることを特徴としている。

【0018】

このような構成とすることで、ソース基準としてMOSFET(15g、25g)が作動することになり、仮にノイズなどによりドレイン電圧変化が生じても、MOSFET(15g、25g)が誤オフしてしまうことを防止することができる。

【0019】

また、請求項4に記載したように、第1内部回路(16)および第2内部回路(26)が接続されるスイッチング素子(1)の所定部位として、スイッチング素子(1)の制御端子を挙げることができる。

【0020】

例えば、請求項5に記載したように、第1内部回路(16)および第2内部回路(26)をスイッチング素子(1)の制御端子であるゲートの電圧を監視するゲート電圧監視回路とすることができる。この場合、第1内部回路(16)にて構成されるゲート電圧監視回路は、スイッチング素子のゲート電圧を分圧する分圧抵抗(16a、16b)と、該分圧抵抗(16a、16b)による分圧電圧値をゲート閾値電圧と大小比較するコンパレータ(16c)とを有し、該コンパレータ(16c)の電源供給が第1電源(30)にて行われるようにし、第2内部回路(26)にて構成されるゲート電圧監視回路も、スイッチング素子のゲート電圧を分圧する分圧抵抗(26a、26b)と、該分圧抵抗(26a、26b)による分圧電圧値をゲート閾値電圧と大小比較するコンパレータ(26c)とを有し、該コンパレータ(26c)の電源供給が第2電源(40)にて行われるようにすることができる。

【0021】

このようなゲート電圧監視回路では、例えば第1駆動回路(10)が作動させられて第2駆動回路(20)が作動させられないときには、スイッチング素子(1)のゲートから第2内部回路(26)のコンパレータ(26c)の電源とされる第2電源(40)側に電流が回り込む可能性がある。このため、第2回り込み防止回路(25)にてスイッチング素子(1)のゲートと第2内部回路(26)との間をオフすることで、電流が回り込むことを防止することができる。

【0022】

また、請求項6に記載したように、第1内部回路(16)および第2内部回路(26)が接続されるスイッチング素子(1)の所定部位として、スイッチング素子(1)のセンス端子を挙げることもできる。

【0023】

例えば、請求項7に記載したように、第1内部回路(16)および第2内部回路(26)をスイッチング素子(1)のセンス端子のセンス電圧を監視するセンス電圧監視回路とすることができる。この場合、第1内部回路(16)にて構成されるセンス電圧監視回路は、スイッチング素子のセンス電圧をセンス閾値電圧と大小比較するコンパレータ(16d)を有し、該コンパレータ(16d)の電源供給が第1電源(30)にて行われるようにし、第2内部回路(26)にて構成されるセンス電圧監視回路も、スイッチング素子のゲート電圧をセンス閾値電圧と大小比較するコンパレータ(26d)を有し、該コンパレータ(26d)の電源供給が第2電源(40)にて行われるようにすることができる。

【0024】

このようなゲート電圧監視回路では、例えば第1駆動回路(10)が作動させられて第2駆動回路(20)が作動させられないときには、スイッチング素子(1)のセンス端子から第2内部回路(26)のコンパレータ(26d)の電源とされる第2電源(40)側に電流が回り込む可能性がある。このため、第2回り込み防止回路(25)にてスイッチング素子(1)のセンス端子と第2内部回路(26)との間をオフすることで、電流が回り込むことを防止することができる。

【0025】

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示すものである。

【図面の簡単な説明】

【0026】

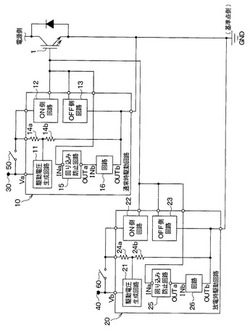

【図1】本発明の第1実施形態にかかる負荷駆動装置の回路構成を示した回路ブロック図である。

【図2】回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の具体的な回路例を示した図である。

【図3】本発明の第2実施形態にかかる負荷駆動装置の回路構成を示した回路ブロック図である。

【図4】回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の具体的な回路例を示した図である。

【図5】本発明者らが検討した負荷駆動装置の回路構成を示した回路ブロック図である。

【発明を実施するための形態】

【0027】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、図中、同一符号を付してある。

【0028】

(第1実施形態)

本発明の第1実施形態について説明する。図1は、本実施形態にかかる負荷駆動装置の回路構成を示した回路ブロック図である。また、図2は、図1に示す負荷駆動装置に備えられる各部の詳細構成を示した回路図である。以下、これらの図を参照して、本実施形態にかかる負荷駆動装置について説明する。

【0029】

図1に示すように、本実施形態の負荷駆動装置では、スイッチング素子としてIGBT1を用いており、IGBT1のゲート電圧を制御することにより、IGBT1をオンオフ制御し、負荷への電力供給を制御している。例えば、IGBT1は、図示しない電力変換装置において、電池への充電を制御するために用いられる。電力変換装置は、例えば、電源に対して平滑用コンデンサが接続されている共に平滑用コンデンサに対して並列的にダイオードおよび電池を有する直列回路が接続された構成とされる。そして、IGBT1のコレクタが平滑用コンデンサとダイオードのアノードとの間に接続され、IGBT1がオフされている間は、平滑用コンデンサにて一定の充電電圧に保ちながら電池への充電を行い、IGBT1をオフすると、平滑用コンデンサに蓄積された電荷を引き抜くことで電池への充電を停止させる。このような電力変換装置における負荷となる電池への充電制御のスイッチング素子等として、本実施形態のIGBT1を用いることができる。

【0030】

なお、ここでは電力変換装置における電池への充電制御のスイッチング素子としてIGBT1を適用する場合について説明したが、勿論、負荷への接続ラインのオンオフ制御を行う他の形態に適用されても良い。また、ここではIGBT1のコレクタが電源側に接続され、エミッタがGNDに接続される形態を例に挙げているが、エミッタが所定の電位とされる基準点に接続されても良い。すなわち、IGBT1のコレクタ側もしくはエミッタ側のいずれかに負荷が接続されるが、負荷がコレクタ側とエミッタ側のいずれに接続されるかで基準点の電位が変化する。例えば、IGBT1を複数個備えることでインバータを構成すれば、三相モータなどが負荷となり、三相それぞれの上アームもしくは下アームとして図1に示す負荷駆動装置を適用することができる。図1に示す負荷駆動装置が上アームとして適用されるものであれば、IGBT1のコレクタが電源に接続され、エミッタが三相モータに接続される。また、図1に示す負荷駆動装置が下アームとして適用されるものであれば、IGBT1のコレクタが三相モータに接続され、エミッタがGNDに接続される。このため、エミッタの接続先に応じて基準点の電位が変化することになる。

【0031】

図1に示すように、負荷駆動装置では、IGBT1を通常時駆動回路10と放電時駆動回路20にて駆動する。通常時駆動回路10と放電時駆動回路20は、同じ回路構成とされており、双方共に、IGBT1のオンオフ駆動を行うことができる構成とされている。例えば、通常時駆動回路10にてIGBT1を駆動し、緊急時には、通常時駆動回路10によるIGBT1の駆動を行わず、放電時駆動回路20を用いて確実にIGBT1に蓄積された電荷を引き抜くようにする。緊急時としては、負荷駆動装置を車載用に使用するような場合には、車両衝突時などが挙げられ、車両衝突時などに放電時駆動回路20を用いて確実にIGBT1に蓄積された電荷を引き抜くことで、電池への充電がオフされるようにしている。

【0032】

各駆動回路10、20は、駆動電圧生成回路11、21とオン側回路12、22およびオフ側回路13、23が備えられた構成とされている。各駆動回路10、20は、別々の電源30、40からの電源供給に基づいて作動し、各電源30、40が発生する電源電圧が各駆動回路10、20における駆動電圧生成回路11、21に印加されるようにしてある。各電源30、40からは、各駆動回路10、20に基本的には同じ電圧が印加されることで、各駆動回路10、20が作動させられることになるが、図1中には電源30から駆動電圧生成回路11に電圧Vaが印加され、電源40から駆動電圧生成回路21に電圧Vbが印加されるものとして記載してある。

【0033】

具体的には、各駆動回路10、20は、電源30、40からの電源供給に基づいて駆動電圧生成回路11、21でIGBT1のゲートに対して印加する駆動電圧を生成している。駆動電圧生成回路11の出力端子とIGBT1のゲートとの間にオン側回路12、22が備えられており、オン側回路12、22によって駆動電圧生成回路11、21とIGBT1との間をオン(接続)すると、駆動電圧生成回路11、21で生成される駆動電圧がオン側回路12、22を介してIGBT1に印加され、IGBT1が駆動される。また、IGBT1のゲートと基準点との間にオフ側回路13、23が接続され、オフ側回路13、23によってIGBT1のゲートと基準点との間をオン(接続)すると、IGBT1に蓄積された電荷が基準点側に引き抜かれ、IGBT1がオフされる。

【0034】

例えば、オン側回路12、22やオフ側回路13、23は、スイッチング素子などによって構成される。そして、図示しないマイコンなどの制御手段からIGBT1をオンすることを指令する駆動信号が入力されると、オン側回路12、22を構成するスイッチング素子がオンさせられると共にオフ側回路13、23を構成するスイッチング素子がオフさせられることで駆動電圧生成回路11、21が生成する駆動電圧をIGBT1のゲートに印加する。これにより、IGBT1のゲート電圧が上昇し、IGBT1がオンさせられる。一方、図示しないマイコンなどの制御手段からIGBT1をオフすることを指令する駆動信号が入力されると、オン側回路12、22を構成するスイッチング素子がオフさせられると共にオフ側回路13、23を構成するスイッチング素子がオンさせられることでIGBT1のゲートに蓄積された電荷が引き抜かれる。これにより、IGBT1のゲート電圧が低下し、IGBT1がオフさせられる。

【0035】

また、オン側回路12、22の入力端子と基準点との間には、抵抗14a、14b、24a、24bが配置されている。これら抵抗14a、24aと抵抗14b、24bの間には、駆動電圧生成回路11、21の出力端子が接続されている。このため、オン側回路12、22の入力端子と基準点との間は、抵抗14a、14b、24a、24bを介してフィードバックループを構成する。さらに、オン側回路12、22と抵抗14a、24aの間と電源30、40との間にスイッチ50、60が備えられている。これら各スイッチ50、60により、各電源30、40とIGBT1をオンさせるためのオン側回路12、22との間のオンオフを制御できるようにしており、スイッチ50、60がオンのときにはオン側回路12、22は電源30、40の電圧を受け、スイッチ50、60がオフのときにはオン側回路12、22は駆動電圧生成回路11、21で生成される駆動電圧を受ける。このため、スイッチ50、60のオンオフに伴ってオン側回路12、22への電力供給源を切り替えられるようにしてある。

【0036】

さらに、本実施形態の負荷駆動装置には、回り込み防止回路15、25が備えられていると共に、回り込み防止対象となる内部回路16、26が備えられている。回り込み防止対象となる内部回路16、26は、駆動回路10、20のうちの一方が作動させられて他方が作動させられない場合において、作動させられている側から作動させられない側に電流の回り込みを発生させる可能性がある回路である。回り込み防止回路15、25は、この回り込み防止対象となる内部回路16、26のハイサイド側に配置され、回り込み防止対象となる内部回路16、26への電流の回り込みを防止する。

【0037】

図2は、これら回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の具体的な回路例を示した図である。なお、図2では、回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の各部について両方の符号を付してあるが、同様の回路によって構成されているからであり、実際には各駆動回路10、20にそれぞれ別構成として備えられている。

【0038】

図2(a)に示すように、回り込み防止回路15、25は、定電流源15a、25a、制御スイッチ15b、25b、ツェナーダイオード15c、25c、第1トランジスタ15d、25d、第2トランジスタ15e、25e、参照電圧回路15f、25f、MOSFET15g、25gおよび抵抗15h、25hを備えた構成とされている。

【0039】

定電流源15a、25aは、各駆動回路10、20それぞれの電源30、40からの電源供給に基づいて定電流を生成する。制御スイッチ15b、25bは、定電流源15a、25aからMOSFET15g、25gのゲートへの電流供給経路をオンオフするもので、制御信号に基づいてオンオフ制御される。制御スイッチ15b、25bは、制御信号がハイレベルのときにオンされると共にローレベルのときにオフされる。制御信号は、図示しないマイコンから出力され、駆動回路10、20が作動させられるときにはハイレベル、作動させられないときにはローレベルになる。

【0040】

ツェナーダイオード15c、25cおよび第1トランジスタ15d、25dは、MOSFET15g、25gのゲート−ソース間電圧をクランプする役割を果たす。すなわち、ツェナーダイオード15c、25cのツェナー降伏電圧とPNPトランジスタで構成された第1トランジスタ15d、25dのベース−エミッタ間電圧(つまり順方向電圧Vf)を加算した電圧値にゲート−ソース間電圧を固定している。

【0041】

第2トランジスタ15e、25eと参照電圧回路15f、25fは、MOSFET15g、25gのゲート電圧を固定するためのものである。すなわち、PNPトランジスタにて構成された第2トランジスタ15e、25eと参照電圧回路15f、25fにて形成される参照電圧refを加算した電圧値にゲート電圧を固定できる。これにより、電源側の定電流が飽和することを防止でき、それによる回路の誤動作を防止できるようになっている。

【0042】

MOSFET15g、25gは、ドレインおよびソースがそれぞれ回り込み防止回路15、25における入力端子INaと出力端子OUTaとして用いられる。このMOSFET15g、25gがオンオフ制御させられることで、入力端子INaと出力端子OUTaのオンオフが制御され、回り込み防止回路15、25のオンオフが制御される。本実施形態の場合、MOSFET15g、25gは、NchMOSFETにて構成されており、定電流源15a、25aからの電流供給に基づいてゲートに対して電荷が蓄積されるとオンさせられ、制御スイッチ15b、25bがオフされて定電流源15a、25aからの電流供給がオフされるとゲートに蓄積された電荷が引き抜かれてオフされる。

【0043】

なお、抵抗15h、25hは、MOSFET15g、25gをオフするときのゲート電圧固定用のプルダウン抵抗である。

【0044】

また、図2(b)に示すように、回り込み防止対象となる内部回路16、26としては、例えばゲート電圧監視回路が挙げられる。ゲート電圧監視回路では、IGBT1のゲート電圧を入力し、これを抵抗16a、16b、26a、26bにて分圧した分圧電圧値をコンパレータ16c、26cにてゲート閾値電圧refと大小比較することでゲート電圧監視を行っている。コンパレータ16c、26cの電源供給は、各駆動回路10、20への電源供給を行っている電源30、40にて行われている。このゲート電圧監視回路では、例えば、IGBT1のゲート電圧の分圧電圧値がゲート閾値電圧ref未満のときにはローレベル、ゲート閾値電圧ref以上になるとハイレベルを出力することでゲート電圧を監視している。

【0045】

ゲート電圧監視回路の場合、電源供給オフや車両の衝突などによって電源30、40のいずれか一方から印加される電圧が低下すると、図2(b)中の矢印で示したように高電位側となるIGBT1のゲート側から低電位となるコンパレータ16c、26cの電源側に電流が回り込む可能性がある。このような回り込みを回り込み防止回路15、25によって防止する。

【0046】

このような回路構成により、本実施形態にかかる負荷駆動装置が構成されている。なお、ここでは負荷駆動装置の基本構成のみを示したが、IGBT1の温度検出回路などのような他の回路構成が備えられていても良い。また、IGBT1にはセンス端子が備えられており、センス端子を通じて過電流検出を行うこともできる。このような回路を備えることもできる。

【0047】

上記のような回路構成を有する負荷駆動装置は、以下のように作動する。

【0048】

まず、通常時には、通常時駆動回路10が作動させられることでIGBT1のオンオフ制御が行われる。すなわち、通常時駆動回路10のスイッチ50がオンされ、マイコンなどの制御手段からIGBT1をオンすることを指令する駆動信号が入力されると、オン側回路12がオンさせられると共にオフ側回路13がオフさせられる。これにより、電源30からIGBT1のゲートに対する電圧印加が行われてIGBT1がオンされ、IGBT1を通じて図示しない平滑コンデンサからの電荷の引き抜きが行われ、電池への充電が停止させられる。また、マイコンなどの制御手段からIGBT1をオフすることを指令する駆動信号が入力されると、オン側回路12がオフさせられると共にオフ側回路13がオンさせられる。これにより、IGBT1がオンされ、図示しない平滑コンデンサが所定電圧となるまで充電が行われると共に電池への充電が行われる。

【0049】

そして、回り込み防止対象となる内部回路16、26がゲート電圧監視回路とされている場合には、ゲート電圧監視回路にてIGBT1のゲート電圧が監視される。そして、ゲート電圧がゲート閾値電圧ref以上になったことが検出されると、例えばクランプ回路を作動させることでIGBT1をクランプ電圧にクランプし、短絡などによる過電流の発生を防止する。

【0050】

一方、通常時には、放電時駆動回路20は作動させられない。このため、放電時駆動回路20のスイッチ60がオフされる。これにより、IGBT1のゲートに接続された各駆動回路10、20の接続点を通じて、オン側回路12やオフ側回路13を介して電流が電源40側に回り込もうとしても、抵抗24a、24bによって大きく減衰されることで、電流の回り込みを防止することが可能となる。

【0051】

さらに、通常時駆動回路10における回り込み防止回路15では、制御信号としてハイレベルが入力されることで制御スイッチ15bがオンさせられ、定電流源15aからの定電流の供給に基づいてMOSFET15gがオンさせられる。したがって、回り込み防止回路15がオンさせられ、回り込み防止対象となる内部回路16にIGBT1のゲート電圧が入力されるようにできる。

【0052】

このとき、ツェナーダイオード15cおよび第1トランジスタ15dによてゲート−ソース間電圧がクランプされるため、ソース基準としてMOSFET15gが作動することになり、仮にノイズなどによりドレイン電圧変化が生じても、MOSFET15gが誤オフしてしまうことを防止することができる。IGBT駆動回路のように、高速スイッチングが行われる回路では、ドレイン電圧変化に対する誤オフは必要な特徴であり、高速スイッチングが行われてもMOSFET15gが誤オフしないようにできる。また、MOSFET15gのゲート電圧は、第2トランジスタ15eと参照電圧回路15fとによってクランプされるため、電源側の定電流が飽和することを防止でき、それによる回路の誤動作も防止することができる。

【0053】

一方、放電時駆動回路20については、制御信号としてローレベルが入力されることで制御スイッチ25bがオフさせられ、定電流源25aからの定電流の供給が停止されるため、MOSFET25gがオフさせられる。したがって、回り込み防止回路25がオフさせられ、回り込み防止対象となる内部回路26にIGBT1のゲート電圧が入力されない。このため、回り込み防止対象となる内部回路26がゲート電圧監視回路の場合に、電源供給オフによって電源40から印加される電圧が低下しても、図2(b)中の矢印で示したような電流の回り込みが生じることを防止できる。

【0054】

また、放電時には、上記通常時と同様の動作が放電時駆動回路20によって行われ、通常時駆動回路10は作動させられなくなる。この場合には、通常時駆動回路10におけるスイッチ50がオフさせられると共に回り込み防止回路15がオフさせられる。したがって、オン側回路12やオフ側回路13を通じて電流が電源30側に回り込もうとすることを防止できると共に、IGBT1のゲート電圧が回り込み防止対象となる内部回路16に印加されないようにでき、内部回路16内で電流の回り込みが生じることを防止できる。

【0055】

なお、上記回路構成の場合、回り込み防止回路15、25に印加されるゲート電圧は第1、第2電源30、40の電源電圧Va、Vbで制限される。このため、NchMOSFETにて構成されたMOSFET15g、25gのソース電圧(出力端子OUTaの電位)は、電源電圧Va(またはVb)−Vsat(定電流の飽和電圧)−Vt(MOSFET15g、25gの閾値電圧)までしか上がらない。したがって、これを満たすように使用する電圧範囲を調整している。

【0056】

以上説明したように、本実施形態の負荷駆動装置では、電流の回り込みが発生し得る回り込み防止対象となる内部回路16、26とスイッチング素子であるIGBT1との間に回り込み防止回路15、25を配置している。そして、駆動回路10、20のうち作動させられない側の回り込み防止回路15、25をオフすることで、回り込み防止対象となる内部回路16、26にスイッチング素子となるIGBT1のゲート電圧が印加されないようにしている。これにより、各内部回路16、26内で電流の回り込みが発生することを防止することが可能となる。

【0057】

(第2実施形態)

本発明の第2実施形態について説明する。本実施形態は、第1実施形態と異なる部位での電流の回り込みを防止するものであり、その他に関しては第1実施形態と同様であるため、第1実施形態と異なる部分についてのみ説明する。

【0058】

図3は、本実施形態にかかる負荷駆動装置の回路構成を示した回路ブロック図である。また、図4は、図3に示す負荷駆動装置に備えられる各部の詳細構成を示した回路図である。以下、これらの図を参照して、本実施形態にかかる負荷駆動装置について説明する。

【0059】

図3に示すように、本実施形態の負荷駆動装置の基本的なブロック構成は第1実施形態と同様であるが、本実施形態では、スイッチング素子のセンス端子に回り込み防止対象となる内部回路16、26が接続されている。そして、この内部回路16、26のハイサイド側には回り込み防止回路15、25が備えられており、センス端子を通じて内部回路16、26に電流の回り込みが発生することを防止している。

【0060】

具体的には、IGBT1のセンス端子(エミッタ端子)は、IGBT1のメインセルのコレクタ−エミッタ間に流れるメイン電流を所定比で減衰させたセンス電流を流す。このセンス電流に基づいて、メイン電流が過電流になっていることを検出している。センス端子と基準点(GND)との間には抵抗2が接続されており、センス端子と抵抗2との間の電圧をセンス電圧として、回り込み防止回路15、25を介して内部回路16、26に入力されるようにしている。センス電圧は、センス電流の電流値によって変化することから、このセンス電位が過電流閾値を超えるとメイン電流が過電流になっていると検出することができる。

【0061】

図4は、これら回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の具体的な回路例を示した図である。なお、図4では、回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の各部について両方の符号を付してあるが、同様の回路によって構成されているからであり、実際には各駆動回路10、20にそれぞれ別構成として備えられている。

【0062】

図4(a)に示すように、回り込み防止回路15、25は、第1実施形態の図2(a)で示したものと同じ回路構成とされており、回り込み防止回路15、25がオンオフ制御されることにより、内部回路16、26への電圧印加をオンオフできるように構成されている。

【0063】

図4(b)に示すように、回り込み防止対象となる内部回路16、26としてセンス電圧監視回路が適用されている。センス電圧監視回路では、IGBT1のセンス端子と抵抗2との間のセンス電圧を入力し、これをコンパレータ16d、26dにてゲート閾値電圧refと大小比較することでセンス電圧監視を行っている。コンパレータ16d、26dの電源供給は、各駆動回路10、20への電源供給を行っている電源30、40にて行われている。このセンス電圧監視回路では、例えば、IGBT1のセンス電圧が過電流が発生すると想定される過電流閾値電圧ref未満のときにはローレベル、過電流閾値電圧ref以上になるとハイレベルを出力することでセンス電圧を監視している。

【0064】

センス電圧監視回路の場合、電源供給オフや車両の衝突などによって電源30、40のいずれか一方から印加される電圧が低下すると、図4(b)中の矢印で示したように高電位側となるIGBT1のセンス端子側から低電位となるコンパレータ16d、26dの電源側に電流が回り込む可能性がある。このような回り込みを回り込み防止回路15、25によって防止する。

【0065】

このような回路構成により、本実施形態の負荷駆動装置が構成されている。このような負荷駆動装置も、基本的には、第1実施形態と同様の作動を行う。

【0066】

そして、通常時には、通常時駆動回路10における回り込み防止回路15では、制御信号としてハイレベルが入力されることで制御スイッチ15bがオンさせられ、定電流源15aからの定電流の供給に基づいてMOSFET15gがオンさせられる。したがって、回り込み防止回路15がオンさせられ、回り込み防止対象となる内部回路16にセンス電圧が入力され、内部回路16が構成するセンス電圧監視回路により、センス電圧に基づく過電流検出が行われる。

【0067】

このときには、放電時駆動回路20はオフされ、回り込み防止回路25には制御信号としてローレベルが入力されることで制御スイッチ25bがオフさせられ、定電流源25aからの定電流の供給が停止されるため、MOSFET25gがオフさせられる。したがって、回り込み防止回路25がオフさせられ、回り込み防止対象となる内部回路26にセンス電圧が入力されない。このため、回り込み防止対象となる内部回路26がセンス電圧監視回路の場合に、電源供給オフによって電源40から印加される電圧が低下しても、図4(b)中の矢印で示したような電流の回り込みが生じることを防止できる。

【0068】

また、放電時には、上記通常時と同様の動作が放電時駆動回路20によって行われ、通常時駆動回路10は作動させられなくなる。この場合には、通常時駆動回路10における回り込み防止回路15がオフさせられることで、センス電圧が回り込み防止対象となる内部回路16に印加されないようにできる。したがって、内部回路16内で電流の回り込みが生じることを防止できる。

【0069】

以上説明したように、本実施形態の負荷駆動装置でも、電流の回り込みが発生し得る回り込み防止対象となる内部回路16、26のハイサイド側に回り込み防止回路15、25を配置している。そして、駆動回路10、20のうち作動させられない側の回り込み防止回路15、25をオフすることで、回り込み防止対象となる内部回路16、26にスイッチング素子となるIGBT1のセンス電圧が印加されないようにしている。これにより、各内部回路16、26内で電流の回り込みが発生することを防止することが可能となる。

【0070】

(他の実施形態)

上記各実施形態では、スイッチング素子としてIGBT1を例に挙げて説明したが、他のスイッチング素子、例えばパワーMOSFETなどを用いる場合についても、本発明を適用することができる。すなわち、ゲートなどの制御端子への入力電圧を制御することで、負荷に繋がる接続ラインのオンオフ制御を行うスイッチング素子であれば、他のスイッチング素子であっても構わない。

【0071】

また、上記各実施形態では、内部回路16、26として、内部回路16、26内において電流の回り込みが発生する回路構成を例に挙げたが、内部回路16、26を通じて基準点に電流が回り込む回路構成とされることもある。この場合にも、その内部回路16、26のハイサイド側に回り込み防止回路15、25を配置することで、電流の回り込みを防止することが可能となる。

【0072】

さらに、上記各実施形態を組み合わせ、第1実施形態のゲート電圧監視回路と第2実施形態のセンス電圧監視回路の両方が備えられる形態とされる場合にも、本発明を適用するができる。その場合、各内部回路16、26のハイサイド側に回り込み防止回路15、25を備えるようにすればよい。

【符号の説明】

【0073】

1 IGBT

2 抵抗

10 通常時駆動回路(第1駆動回路))

11、21 駆動電圧生成回路

12、22 オン側回路

13、23 オフ側回路

14a、14b、24a、24b 抵抗

15、25 回り込み防止回路(第1、第2回り込み防止回路)

15a、25a 定電流源

15b、25b 制御スイッチ

15c、25c ツェナーダイオード

15d、25d、15e、25e 第1、第2トランジスタ

15f、25f 参照電圧回路

15h、25h 抵抗

16、26 内部回路(第1、第2内部回路))

16a、16b、26a、26b 抵抗

16c、26c、16d、26d コンパレータ

20 放電時駆動回路(第2駆動回路)

30、40 第1、第2電源

50、60 スイッチ

【技術分野】

【0001】

本発明は、電流の回り込み防止機能を有する負荷駆動装置に関するものである。

【背景技術】

【0002】

従来、特許文献1において、直流電源の正側と負側との間に接続される平滑用コンデンサに蓄積された電荷を放電する際に、全スイッチング素子をオン状態にし、過電流になる前にスイッチング素子をオフにする技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−232620号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、スイッチング素子の駆動制御を行うことで平滑用コンデンサに蓄積された電荷を放電することが可能となるものの、スイッチング素子の駆動制御を行う駆動回路に対する電力の供給が絶たれるとスイッチング素子を駆動できずに放電も行えなくなるという問題がある。この問題を解決する方法として、通常時に作動する駆動回路(以下、通常時駆動回路という)とは別に放電時に作動する駆動回路(以下、放電時駆動回路という)を設け、これら二つの駆動回路に別々の電源から供給が行われるようにするという回路構成が考えられる。

【0005】

ところが、二つの駆動回路から個別に出力する駆動信号によってスイッチング素子の駆動制御を行おうとすると、各駆動回路の接続点を通じて、一方の駆動回路から他方の駆動回路に電流が回り込む可能性がある。

【0006】

これに対して、図5に示す回路構成を採用することで、一方の駆動回路から他方の駆動回路に電流が回り込むことを防止することが可能となる。この回路構成では、スイッチング素子としてIGBT100を用いており、IGBT100を通常時駆動回路110と放電時駆動回路120にて駆動する。例えば、基本的には、通常時駆動回路110にてIGBT100を駆動し、緊急時には、通常時駆動回路110によるIGBT100を行わず、放電時駆動回路120を用いて確実にIGBT100に蓄積された電荷を引き抜くようにする。

【0007】

各駆動回路110、120は、駆動電圧生成回路111、121とオン側回路112、122およびオフ側回路113、123などを備えた構成とされ、別々の電源130、140からの電源供給に基づいて作動する。

【0008】

具体的には、各駆動回路110、120は、駆動電圧生成回路111、121が電源130、140からの電源供給に基づいてIGBT100のゲートに対して印加する駆動電圧を生成している。駆動電圧生成回路111の出力端子とIGBT100のゲートとの間にオン側回路112、122が備えられており、オン側回路112、122によって駆動電圧生成回路111、121とIGBT100との間をオン(接続)すると、駆動電圧生成回路111、121で生成される駆動電圧がオン側回路112、122を介してIGBT100に印加され、IGBT100が駆動される。また、IGBT100のゲートと基準電位とされる基準点との間にオフ側回路113、123が接続され、オフ側回路113、124によってIGBT100のゲートと基準点との間をオン(接続)すると、IGBT100に蓄積された電荷が基準点側に引き抜かれ、IGBT100がオフされる。

【0009】

このような構成において、オン側回路112、122とオフ側回路113、123との間に抵抗114a、114b、124a、124bを配置し、抵抗114a、124aと抵抗114b、124bの間に駆動電圧生成回路111、121の出力端子を接続すると共に、オン側回路112、122と抵抗114a、124aの間と電源130、140との間にスイッチ150、160を備えている。これらスイッチ150、160により、各駆動電源130、140とIGBT100をオンさせるためのオン側回路112、122との間をオンオフ制御できるようにしている。

【0010】

そして、通常時駆動回路110によってIGBT100を駆動する際には、放電時駆動回路120のスイッチ160をオフする。これにより、IGBT100のゲートに接続された各駆動回路110、120の接続点を通じて、オン側回路122やオフ側回路123を介して電源140側に電流が回り込もうとしても、抵抗114a、114bによって大きく減衰されることで、電流の回り込みを防止することが可能となる。逆に、放電時駆動回路120によってIGBT100を駆動する際には、通常時駆動回路110のスイッチ150をオフする。これにより、IGBT100のゲートに接続された各駆動回路110、120の接続点を通じて、オン側回路112やオフ側回路113を介して電源130側に電流が回り込もうとしても、抵抗124a、124bによって大きく減衰されることで、電流の回り込みを防止することが可能となる。このようにして、電流の回り込みを防止することが可能となる。

【0011】

しかし、各駆動回路110、120の電源130、140側を切り離して電流の回り込みを防止したとしても、IGBT100のゲートから基準点や内部回路に電流が回り込む回路構成とされる場合があり、上記の構成では、このような場合における電流の回り込みを防止できない。このため、このような場合の電流の回り込みが防止できるようにすることが望まれる。

【0012】

なお、ここではIGBT100のゲートからの電流の回り込みについて説明したが、IGBT100の他の部位、例えばセンス端子などのように複数の駆動回路が共通して接続される接続点を有する構成においても、電流の回り込みが発生する可能性がある。

【0013】

本発明は上記点に鑑みて、スイッチング素子の駆動を行う複数の駆動回路が備えられる場合において、複数の駆動回路とスイッチング素子との接続点を通じて、内部回路や基準点に電流が回り込むことを防止できる負荷駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0014】

上記目的を達成するため、請求項1に記載の発明では、第1駆動回路(10)には、スイッチング素子(1)の所定部位と電気的に接続される第1内部回路(16)が備えられていると共に、第2駆動回路(20)にも、スイッチング素子(1)の所定部位と電気的に接続される第2内部回路(26)が備えられており、第1駆動回路(10)の第1内部回路(16)とスイッチング素子(1)との間に、第2駆動回路(20)がスイッチング素子(1)を制御するときに、第1内部回路(16)とスイッチング素子(1)との間をオフすることで、第2内部回路(26)とスイッチング素子(1)との接続点から第1内部回路(16)への電流の回り込み防止する第1回り込み防止回路(15)が備えられていると共に、第2駆動回路(20)の第2内部回路(26)とスイッチング素子(1)との間に、第1駆動回路(10)がスイッチング素子(1)を制御するときに、第2内部回路(26)とスイッチング素子(1)との間をオフすることで、第1内部回路(16)とスイッチング素子(1)との接続点から第2内部回路(26)への電流の回り込み防止する第2回り込み防止回路(25)が備えられていることを特徴としている。

【0015】

このように、電流の回り込みが発生し得る回り込み防止対象となる第1、第2内部回路(16、26)とスイッチング素子(1)との間に第1、第2回り込み防止回路(15、25)を配置している。そして、第1、第2駆動回路(10、20)のうち作動させられない側の回り込み防止回路(15、25)をオフすることで、回り込み防止対象となる内部回路(16、26)にスイッチング素子(1)の所定部位の電圧が印加されないようにしている。これにより、電流の回り込みが発生することを防止することが可能となる。

【0016】

例えば、請求項2に記載したように、第1回り込み防止回路(15)は、第1電源(30)からの電源供給に基づいて定電流を生成する定電流源(15a)と、定電流源(15a)の定電流の流れをオンオフする制御スイッチ(15b)と、定電流源(15a)から流される定電流に基づいて第1内部回路(16)とスイッチング素子(1)との間のオンオフを制御するMOSFET(15g)と、MOSFET(15g)のゲートと所定電位とされる基準点との間に接続されたPNPトランジスタ(15e)と、PNPトランジスタ(15e)のベース−コレクタ間を参照電圧に固定する参照電圧回路(15f)とを有した構成とすることができる。この場合、第2駆動回路(20)がスイッチング素子(1)を制御するときに、当該第1回り込み回路(15)に備えられる制御スイッチ(15b)をオフしてMOSFET(15g)をオフすることで、第1内部回路(16)とスイッチング素子(1)との間をオフする。また、第2回り込み防止回路(25)も、第2電源(40)からの電源供給に基づいて定電流を生成する定電流源(25a)と、定電流源(25a)の定電流の流れをオンオフする制御スイッチ(25b)と、定電流源(25a)から流される定電流に基づいて第2内部回路(26)とスイッチング素子(1)との間のオンオフを制御するMOSFET(25g)と、MOSFET(25g)のゲートと所定電位とされる基準点との間に接続されたPNPトランジスタ(25e)と、PNPトランジスタ(25e)のベース−コレクタ間を参照電圧に固定する参照電圧回路(25f)とを有した構成とすることができる。この場合、第1駆動回路(10)がスイッチング素子(1)を制御するときに、当該第2回り込み回路(25)に備えられる制御スイッチ(25b)をオフしてMOSFET(25g)をオフすることで、第2内部回路(26)とスイッチング素子(1)との間をオフする。

【0017】

請求項3に記載の発明では、第1回り込み防止回路(15)に備えられるMOSFET(15g)のゲートにはツェナーダイオード(15c)とPNPトランジスタ(15d)が接続され、これらツェナーダイオード(15c)のツェナー降伏電圧とPNPトランジスタ(15d)の順方向電圧VfによってMOSFET(15g)のゲート−ソース間が固定されており、第2回り込み防止回路(25)に備えられるMOSFET(25g)のゲートにもツェナーダイオード(25c)とPNPトランジスタ(25d)が接続され、これらツェナーダイオード(25c)のツェナー降伏電圧とPNPトランジスタ(25d)の順方向電圧VfによってMOSFET(25g)のゲート−ソース間が固定されていることを特徴としている。

【0018】

このような構成とすることで、ソース基準としてMOSFET(15g、25g)が作動することになり、仮にノイズなどによりドレイン電圧変化が生じても、MOSFET(15g、25g)が誤オフしてしまうことを防止することができる。

【0019】

また、請求項4に記載したように、第1内部回路(16)および第2内部回路(26)が接続されるスイッチング素子(1)の所定部位として、スイッチング素子(1)の制御端子を挙げることができる。

【0020】

例えば、請求項5に記載したように、第1内部回路(16)および第2内部回路(26)をスイッチング素子(1)の制御端子であるゲートの電圧を監視するゲート電圧監視回路とすることができる。この場合、第1内部回路(16)にて構成されるゲート電圧監視回路は、スイッチング素子のゲート電圧を分圧する分圧抵抗(16a、16b)と、該分圧抵抗(16a、16b)による分圧電圧値をゲート閾値電圧と大小比較するコンパレータ(16c)とを有し、該コンパレータ(16c)の電源供給が第1電源(30)にて行われるようにし、第2内部回路(26)にて構成されるゲート電圧監視回路も、スイッチング素子のゲート電圧を分圧する分圧抵抗(26a、26b)と、該分圧抵抗(26a、26b)による分圧電圧値をゲート閾値電圧と大小比較するコンパレータ(26c)とを有し、該コンパレータ(26c)の電源供給が第2電源(40)にて行われるようにすることができる。

【0021】

このようなゲート電圧監視回路では、例えば第1駆動回路(10)が作動させられて第2駆動回路(20)が作動させられないときには、スイッチング素子(1)のゲートから第2内部回路(26)のコンパレータ(26c)の電源とされる第2電源(40)側に電流が回り込む可能性がある。このため、第2回り込み防止回路(25)にてスイッチング素子(1)のゲートと第2内部回路(26)との間をオフすることで、電流が回り込むことを防止することができる。

【0022】

また、請求項6に記載したように、第1内部回路(16)および第2内部回路(26)が接続されるスイッチング素子(1)の所定部位として、スイッチング素子(1)のセンス端子を挙げることもできる。

【0023】

例えば、請求項7に記載したように、第1内部回路(16)および第2内部回路(26)をスイッチング素子(1)のセンス端子のセンス電圧を監視するセンス電圧監視回路とすることができる。この場合、第1内部回路(16)にて構成されるセンス電圧監視回路は、スイッチング素子のセンス電圧をセンス閾値電圧と大小比較するコンパレータ(16d)を有し、該コンパレータ(16d)の電源供給が第1電源(30)にて行われるようにし、第2内部回路(26)にて構成されるセンス電圧監視回路も、スイッチング素子のゲート電圧をセンス閾値電圧と大小比較するコンパレータ(26d)を有し、該コンパレータ(26d)の電源供給が第2電源(40)にて行われるようにすることができる。

【0024】

このようなゲート電圧監視回路では、例えば第1駆動回路(10)が作動させられて第2駆動回路(20)が作動させられないときには、スイッチング素子(1)のセンス端子から第2内部回路(26)のコンパレータ(26d)の電源とされる第2電源(40)側に電流が回り込む可能性がある。このため、第2回り込み防止回路(25)にてスイッチング素子(1)のセンス端子と第2内部回路(26)との間をオフすることで、電流が回り込むことを防止することができる。

【0025】

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示すものである。

【図面の簡単な説明】

【0026】

【図1】本発明の第1実施形態にかかる負荷駆動装置の回路構成を示した回路ブロック図である。

【図2】回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の具体的な回路例を示した図である。

【図3】本発明の第2実施形態にかかる負荷駆動装置の回路構成を示した回路ブロック図である。

【図4】回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の具体的な回路例を示した図である。

【図5】本発明者らが検討した負荷駆動装置の回路構成を示した回路ブロック図である。

【発明を実施するための形態】

【0027】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、図中、同一符号を付してある。

【0028】

(第1実施形態)

本発明の第1実施形態について説明する。図1は、本実施形態にかかる負荷駆動装置の回路構成を示した回路ブロック図である。また、図2は、図1に示す負荷駆動装置に備えられる各部の詳細構成を示した回路図である。以下、これらの図を参照して、本実施形態にかかる負荷駆動装置について説明する。

【0029】

図1に示すように、本実施形態の負荷駆動装置では、スイッチング素子としてIGBT1を用いており、IGBT1のゲート電圧を制御することにより、IGBT1をオンオフ制御し、負荷への電力供給を制御している。例えば、IGBT1は、図示しない電力変換装置において、電池への充電を制御するために用いられる。電力変換装置は、例えば、電源に対して平滑用コンデンサが接続されている共に平滑用コンデンサに対して並列的にダイオードおよび電池を有する直列回路が接続された構成とされる。そして、IGBT1のコレクタが平滑用コンデンサとダイオードのアノードとの間に接続され、IGBT1がオフされている間は、平滑用コンデンサにて一定の充電電圧に保ちながら電池への充電を行い、IGBT1をオフすると、平滑用コンデンサに蓄積された電荷を引き抜くことで電池への充電を停止させる。このような電力変換装置における負荷となる電池への充電制御のスイッチング素子等として、本実施形態のIGBT1を用いることができる。

【0030】

なお、ここでは電力変換装置における電池への充電制御のスイッチング素子としてIGBT1を適用する場合について説明したが、勿論、負荷への接続ラインのオンオフ制御を行う他の形態に適用されても良い。また、ここではIGBT1のコレクタが電源側に接続され、エミッタがGNDに接続される形態を例に挙げているが、エミッタが所定の電位とされる基準点に接続されても良い。すなわち、IGBT1のコレクタ側もしくはエミッタ側のいずれかに負荷が接続されるが、負荷がコレクタ側とエミッタ側のいずれに接続されるかで基準点の電位が変化する。例えば、IGBT1を複数個備えることでインバータを構成すれば、三相モータなどが負荷となり、三相それぞれの上アームもしくは下アームとして図1に示す負荷駆動装置を適用することができる。図1に示す負荷駆動装置が上アームとして適用されるものであれば、IGBT1のコレクタが電源に接続され、エミッタが三相モータに接続される。また、図1に示す負荷駆動装置が下アームとして適用されるものであれば、IGBT1のコレクタが三相モータに接続され、エミッタがGNDに接続される。このため、エミッタの接続先に応じて基準点の電位が変化することになる。

【0031】

図1に示すように、負荷駆動装置では、IGBT1を通常時駆動回路10と放電時駆動回路20にて駆動する。通常時駆動回路10と放電時駆動回路20は、同じ回路構成とされており、双方共に、IGBT1のオンオフ駆動を行うことができる構成とされている。例えば、通常時駆動回路10にてIGBT1を駆動し、緊急時には、通常時駆動回路10によるIGBT1の駆動を行わず、放電時駆動回路20を用いて確実にIGBT1に蓄積された電荷を引き抜くようにする。緊急時としては、負荷駆動装置を車載用に使用するような場合には、車両衝突時などが挙げられ、車両衝突時などに放電時駆動回路20を用いて確実にIGBT1に蓄積された電荷を引き抜くことで、電池への充電がオフされるようにしている。

【0032】

各駆動回路10、20は、駆動電圧生成回路11、21とオン側回路12、22およびオフ側回路13、23が備えられた構成とされている。各駆動回路10、20は、別々の電源30、40からの電源供給に基づいて作動し、各電源30、40が発生する電源電圧が各駆動回路10、20における駆動電圧生成回路11、21に印加されるようにしてある。各電源30、40からは、各駆動回路10、20に基本的には同じ電圧が印加されることで、各駆動回路10、20が作動させられることになるが、図1中には電源30から駆動電圧生成回路11に電圧Vaが印加され、電源40から駆動電圧生成回路21に電圧Vbが印加されるものとして記載してある。

【0033】

具体的には、各駆動回路10、20は、電源30、40からの電源供給に基づいて駆動電圧生成回路11、21でIGBT1のゲートに対して印加する駆動電圧を生成している。駆動電圧生成回路11の出力端子とIGBT1のゲートとの間にオン側回路12、22が備えられており、オン側回路12、22によって駆動電圧生成回路11、21とIGBT1との間をオン(接続)すると、駆動電圧生成回路11、21で生成される駆動電圧がオン側回路12、22を介してIGBT1に印加され、IGBT1が駆動される。また、IGBT1のゲートと基準点との間にオフ側回路13、23が接続され、オフ側回路13、23によってIGBT1のゲートと基準点との間をオン(接続)すると、IGBT1に蓄積された電荷が基準点側に引き抜かれ、IGBT1がオフされる。

【0034】

例えば、オン側回路12、22やオフ側回路13、23は、スイッチング素子などによって構成される。そして、図示しないマイコンなどの制御手段からIGBT1をオンすることを指令する駆動信号が入力されると、オン側回路12、22を構成するスイッチング素子がオンさせられると共にオフ側回路13、23を構成するスイッチング素子がオフさせられることで駆動電圧生成回路11、21が生成する駆動電圧をIGBT1のゲートに印加する。これにより、IGBT1のゲート電圧が上昇し、IGBT1がオンさせられる。一方、図示しないマイコンなどの制御手段からIGBT1をオフすることを指令する駆動信号が入力されると、オン側回路12、22を構成するスイッチング素子がオフさせられると共にオフ側回路13、23を構成するスイッチング素子がオンさせられることでIGBT1のゲートに蓄積された電荷が引き抜かれる。これにより、IGBT1のゲート電圧が低下し、IGBT1がオフさせられる。

【0035】

また、オン側回路12、22の入力端子と基準点との間には、抵抗14a、14b、24a、24bが配置されている。これら抵抗14a、24aと抵抗14b、24bの間には、駆動電圧生成回路11、21の出力端子が接続されている。このため、オン側回路12、22の入力端子と基準点との間は、抵抗14a、14b、24a、24bを介してフィードバックループを構成する。さらに、オン側回路12、22と抵抗14a、24aの間と電源30、40との間にスイッチ50、60が備えられている。これら各スイッチ50、60により、各電源30、40とIGBT1をオンさせるためのオン側回路12、22との間のオンオフを制御できるようにしており、スイッチ50、60がオンのときにはオン側回路12、22は電源30、40の電圧を受け、スイッチ50、60がオフのときにはオン側回路12、22は駆動電圧生成回路11、21で生成される駆動電圧を受ける。このため、スイッチ50、60のオンオフに伴ってオン側回路12、22への電力供給源を切り替えられるようにしてある。

【0036】

さらに、本実施形態の負荷駆動装置には、回り込み防止回路15、25が備えられていると共に、回り込み防止対象となる内部回路16、26が備えられている。回り込み防止対象となる内部回路16、26は、駆動回路10、20のうちの一方が作動させられて他方が作動させられない場合において、作動させられている側から作動させられない側に電流の回り込みを発生させる可能性がある回路である。回り込み防止回路15、25は、この回り込み防止対象となる内部回路16、26のハイサイド側に配置され、回り込み防止対象となる内部回路16、26への電流の回り込みを防止する。

【0037】

図2は、これら回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の具体的な回路例を示した図である。なお、図2では、回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の各部について両方の符号を付してあるが、同様の回路によって構成されているからであり、実際には各駆動回路10、20にそれぞれ別構成として備えられている。

【0038】

図2(a)に示すように、回り込み防止回路15、25は、定電流源15a、25a、制御スイッチ15b、25b、ツェナーダイオード15c、25c、第1トランジスタ15d、25d、第2トランジスタ15e、25e、参照電圧回路15f、25f、MOSFET15g、25gおよび抵抗15h、25hを備えた構成とされている。

【0039】

定電流源15a、25aは、各駆動回路10、20それぞれの電源30、40からの電源供給に基づいて定電流を生成する。制御スイッチ15b、25bは、定電流源15a、25aからMOSFET15g、25gのゲートへの電流供給経路をオンオフするもので、制御信号に基づいてオンオフ制御される。制御スイッチ15b、25bは、制御信号がハイレベルのときにオンされると共にローレベルのときにオフされる。制御信号は、図示しないマイコンから出力され、駆動回路10、20が作動させられるときにはハイレベル、作動させられないときにはローレベルになる。

【0040】

ツェナーダイオード15c、25cおよび第1トランジスタ15d、25dは、MOSFET15g、25gのゲート−ソース間電圧をクランプする役割を果たす。すなわち、ツェナーダイオード15c、25cのツェナー降伏電圧とPNPトランジスタで構成された第1トランジスタ15d、25dのベース−エミッタ間電圧(つまり順方向電圧Vf)を加算した電圧値にゲート−ソース間電圧を固定している。

【0041】

第2トランジスタ15e、25eと参照電圧回路15f、25fは、MOSFET15g、25gのゲート電圧を固定するためのものである。すなわち、PNPトランジスタにて構成された第2トランジスタ15e、25eと参照電圧回路15f、25fにて形成される参照電圧refを加算した電圧値にゲート電圧を固定できる。これにより、電源側の定電流が飽和することを防止でき、それによる回路の誤動作を防止できるようになっている。

【0042】

MOSFET15g、25gは、ドレインおよびソースがそれぞれ回り込み防止回路15、25における入力端子INaと出力端子OUTaとして用いられる。このMOSFET15g、25gがオンオフ制御させられることで、入力端子INaと出力端子OUTaのオンオフが制御され、回り込み防止回路15、25のオンオフが制御される。本実施形態の場合、MOSFET15g、25gは、NchMOSFETにて構成されており、定電流源15a、25aからの電流供給に基づいてゲートに対して電荷が蓄積されるとオンさせられ、制御スイッチ15b、25bがオフされて定電流源15a、25aからの電流供給がオフされるとゲートに蓄積された電荷が引き抜かれてオフされる。

【0043】

なお、抵抗15h、25hは、MOSFET15g、25gをオフするときのゲート電圧固定用のプルダウン抵抗である。

【0044】

また、図2(b)に示すように、回り込み防止対象となる内部回路16、26としては、例えばゲート電圧監視回路が挙げられる。ゲート電圧監視回路では、IGBT1のゲート電圧を入力し、これを抵抗16a、16b、26a、26bにて分圧した分圧電圧値をコンパレータ16c、26cにてゲート閾値電圧refと大小比較することでゲート電圧監視を行っている。コンパレータ16c、26cの電源供給は、各駆動回路10、20への電源供給を行っている電源30、40にて行われている。このゲート電圧監視回路では、例えば、IGBT1のゲート電圧の分圧電圧値がゲート閾値電圧ref未満のときにはローレベル、ゲート閾値電圧ref以上になるとハイレベルを出力することでゲート電圧を監視している。

【0045】

ゲート電圧監視回路の場合、電源供給オフや車両の衝突などによって電源30、40のいずれか一方から印加される電圧が低下すると、図2(b)中の矢印で示したように高電位側となるIGBT1のゲート側から低電位となるコンパレータ16c、26cの電源側に電流が回り込む可能性がある。このような回り込みを回り込み防止回路15、25によって防止する。

【0046】

このような回路構成により、本実施形態にかかる負荷駆動装置が構成されている。なお、ここでは負荷駆動装置の基本構成のみを示したが、IGBT1の温度検出回路などのような他の回路構成が備えられていても良い。また、IGBT1にはセンス端子が備えられており、センス端子を通じて過電流検出を行うこともできる。このような回路を備えることもできる。

【0047】

上記のような回路構成を有する負荷駆動装置は、以下のように作動する。

【0048】

まず、通常時には、通常時駆動回路10が作動させられることでIGBT1のオンオフ制御が行われる。すなわち、通常時駆動回路10のスイッチ50がオンされ、マイコンなどの制御手段からIGBT1をオンすることを指令する駆動信号が入力されると、オン側回路12がオンさせられると共にオフ側回路13がオフさせられる。これにより、電源30からIGBT1のゲートに対する電圧印加が行われてIGBT1がオンされ、IGBT1を通じて図示しない平滑コンデンサからの電荷の引き抜きが行われ、電池への充電が停止させられる。また、マイコンなどの制御手段からIGBT1をオフすることを指令する駆動信号が入力されると、オン側回路12がオフさせられると共にオフ側回路13がオンさせられる。これにより、IGBT1がオンされ、図示しない平滑コンデンサが所定電圧となるまで充電が行われると共に電池への充電が行われる。

【0049】

そして、回り込み防止対象となる内部回路16、26がゲート電圧監視回路とされている場合には、ゲート電圧監視回路にてIGBT1のゲート電圧が監視される。そして、ゲート電圧がゲート閾値電圧ref以上になったことが検出されると、例えばクランプ回路を作動させることでIGBT1をクランプ電圧にクランプし、短絡などによる過電流の発生を防止する。

【0050】

一方、通常時には、放電時駆動回路20は作動させられない。このため、放電時駆動回路20のスイッチ60がオフされる。これにより、IGBT1のゲートに接続された各駆動回路10、20の接続点を通じて、オン側回路12やオフ側回路13を介して電流が電源40側に回り込もうとしても、抵抗24a、24bによって大きく減衰されることで、電流の回り込みを防止することが可能となる。

【0051】

さらに、通常時駆動回路10における回り込み防止回路15では、制御信号としてハイレベルが入力されることで制御スイッチ15bがオンさせられ、定電流源15aからの定電流の供給に基づいてMOSFET15gがオンさせられる。したがって、回り込み防止回路15がオンさせられ、回り込み防止対象となる内部回路16にIGBT1のゲート電圧が入力されるようにできる。

【0052】

このとき、ツェナーダイオード15cおよび第1トランジスタ15dによてゲート−ソース間電圧がクランプされるため、ソース基準としてMOSFET15gが作動することになり、仮にノイズなどによりドレイン電圧変化が生じても、MOSFET15gが誤オフしてしまうことを防止することができる。IGBT駆動回路のように、高速スイッチングが行われる回路では、ドレイン電圧変化に対する誤オフは必要な特徴であり、高速スイッチングが行われてもMOSFET15gが誤オフしないようにできる。また、MOSFET15gのゲート電圧は、第2トランジスタ15eと参照電圧回路15fとによってクランプされるため、電源側の定電流が飽和することを防止でき、それによる回路の誤動作も防止することができる。

【0053】

一方、放電時駆動回路20については、制御信号としてローレベルが入力されることで制御スイッチ25bがオフさせられ、定電流源25aからの定電流の供給が停止されるため、MOSFET25gがオフさせられる。したがって、回り込み防止回路25がオフさせられ、回り込み防止対象となる内部回路26にIGBT1のゲート電圧が入力されない。このため、回り込み防止対象となる内部回路26がゲート電圧監視回路の場合に、電源供給オフによって電源40から印加される電圧が低下しても、図2(b)中の矢印で示したような電流の回り込みが生じることを防止できる。

【0054】

また、放電時には、上記通常時と同様の動作が放電時駆動回路20によって行われ、通常時駆動回路10は作動させられなくなる。この場合には、通常時駆動回路10におけるスイッチ50がオフさせられると共に回り込み防止回路15がオフさせられる。したがって、オン側回路12やオフ側回路13を通じて電流が電源30側に回り込もうとすることを防止できると共に、IGBT1のゲート電圧が回り込み防止対象となる内部回路16に印加されないようにでき、内部回路16内で電流の回り込みが生じることを防止できる。

【0055】

なお、上記回路構成の場合、回り込み防止回路15、25に印加されるゲート電圧は第1、第2電源30、40の電源電圧Va、Vbで制限される。このため、NchMOSFETにて構成されたMOSFET15g、25gのソース電圧(出力端子OUTaの電位)は、電源電圧Va(またはVb)−Vsat(定電流の飽和電圧)−Vt(MOSFET15g、25gの閾値電圧)までしか上がらない。したがって、これを満たすように使用する電圧範囲を調整している。

【0056】

以上説明したように、本実施形態の負荷駆動装置では、電流の回り込みが発生し得る回り込み防止対象となる内部回路16、26とスイッチング素子であるIGBT1との間に回り込み防止回路15、25を配置している。そして、駆動回路10、20のうち作動させられない側の回り込み防止回路15、25をオフすることで、回り込み防止対象となる内部回路16、26にスイッチング素子となるIGBT1のゲート電圧が印加されないようにしている。これにより、各内部回路16、26内で電流の回り込みが発生することを防止することが可能となる。

【0057】

(第2実施形態)

本発明の第2実施形態について説明する。本実施形態は、第1実施形態と異なる部位での電流の回り込みを防止するものであり、その他に関しては第1実施形態と同様であるため、第1実施形態と異なる部分についてのみ説明する。

【0058】

図3は、本実施形態にかかる負荷駆動装置の回路構成を示した回路ブロック図である。また、図4は、図3に示す負荷駆動装置に備えられる各部の詳細構成を示した回路図である。以下、これらの図を参照して、本実施形態にかかる負荷駆動装置について説明する。

【0059】

図3に示すように、本実施形態の負荷駆動装置の基本的なブロック構成は第1実施形態と同様であるが、本実施形態では、スイッチング素子のセンス端子に回り込み防止対象となる内部回路16、26が接続されている。そして、この内部回路16、26のハイサイド側には回り込み防止回路15、25が備えられており、センス端子を通じて内部回路16、26に電流の回り込みが発生することを防止している。

【0060】

具体的には、IGBT1のセンス端子(エミッタ端子)は、IGBT1のメインセルのコレクタ−エミッタ間に流れるメイン電流を所定比で減衰させたセンス電流を流す。このセンス電流に基づいて、メイン電流が過電流になっていることを検出している。センス端子と基準点(GND)との間には抵抗2が接続されており、センス端子と抵抗2との間の電圧をセンス電圧として、回り込み防止回路15、25を介して内部回路16、26に入力されるようにしている。センス電圧は、センス電流の電流値によって変化することから、このセンス電位が過電流閾値を超えるとメイン電流が過電流になっていると検出することができる。

【0061】

図4は、これら回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の具体的な回路例を示した図である。なお、図4では、回り込み防止回路15、25と回り込み防止対象となる内部回路16、26の各部について両方の符号を付してあるが、同様の回路によって構成されているからであり、実際には各駆動回路10、20にそれぞれ別構成として備えられている。

【0062】

図4(a)に示すように、回り込み防止回路15、25は、第1実施形態の図2(a)で示したものと同じ回路構成とされており、回り込み防止回路15、25がオンオフ制御されることにより、内部回路16、26への電圧印加をオンオフできるように構成されている。

【0063】

図4(b)に示すように、回り込み防止対象となる内部回路16、26としてセンス電圧監視回路が適用されている。センス電圧監視回路では、IGBT1のセンス端子と抵抗2との間のセンス電圧を入力し、これをコンパレータ16d、26dにてゲート閾値電圧refと大小比較することでセンス電圧監視を行っている。コンパレータ16d、26dの電源供給は、各駆動回路10、20への電源供給を行っている電源30、40にて行われている。このセンス電圧監視回路では、例えば、IGBT1のセンス電圧が過電流が発生すると想定される過電流閾値電圧ref未満のときにはローレベル、過電流閾値電圧ref以上になるとハイレベルを出力することでセンス電圧を監視している。

【0064】

センス電圧監視回路の場合、電源供給オフや車両の衝突などによって電源30、40のいずれか一方から印加される電圧が低下すると、図4(b)中の矢印で示したように高電位側となるIGBT1のセンス端子側から低電位となるコンパレータ16d、26dの電源側に電流が回り込む可能性がある。このような回り込みを回り込み防止回路15、25によって防止する。

【0065】

このような回路構成により、本実施形態の負荷駆動装置が構成されている。このような負荷駆動装置も、基本的には、第1実施形態と同様の作動を行う。

【0066】

そして、通常時には、通常時駆動回路10における回り込み防止回路15では、制御信号としてハイレベルが入力されることで制御スイッチ15bがオンさせられ、定電流源15aからの定電流の供給に基づいてMOSFET15gがオンさせられる。したがって、回り込み防止回路15がオンさせられ、回り込み防止対象となる内部回路16にセンス電圧が入力され、内部回路16が構成するセンス電圧監視回路により、センス電圧に基づく過電流検出が行われる。

【0067】

このときには、放電時駆動回路20はオフされ、回り込み防止回路25には制御信号としてローレベルが入力されることで制御スイッチ25bがオフさせられ、定電流源25aからの定電流の供給が停止されるため、MOSFET25gがオフさせられる。したがって、回り込み防止回路25がオフさせられ、回り込み防止対象となる内部回路26にセンス電圧が入力されない。このため、回り込み防止対象となる内部回路26がセンス電圧監視回路の場合に、電源供給オフによって電源40から印加される電圧が低下しても、図4(b)中の矢印で示したような電流の回り込みが生じることを防止できる。

【0068】

また、放電時には、上記通常時と同様の動作が放電時駆動回路20によって行われ、通常時駆動回路10は作動させられなくなる。この場合には、通常時駆動回路10における回り込み防止回路15がオフさせられることで、センス電圧が回り込み防止対象となる内部回路16に印加されないようにできる。したがって、内部回路16内で電流の回り込みが生じることを防止できる。

【0069】

以上説明したように、本実施形態の負荷駆動装置でも、電流の回り込みが発生し得る回り込み防止対象となる内部回路16、26のハイサイド側に回り込み防止回路15、25を配置している。そして、駆動回路10、20のうち作動させられない側の回り込み防止回路15、25をオフすることで、回り込み防止対象となる内部回路16、26にスイッチング素子となるIGBT1のセンス電圧が印加されないようにしている。これにより、各内部回路16、26内で電流の回り込みが発生することを防止することが可能となる。

【0070】

(他の実施形態)

上記各実施形態では、スイッチング素子としてIGBT1を例に挙げて説明したが、他のスイッチング素子、例えばパワーMOSFETなどを用いる場合についても、本発明を適用することができる。すなわち、ゲートなどの制御端子への入力電圧を制御することで、負荷に繋がる接続ラインのオンオフ制御を行うスイッチング素子であれば、他のスイッチング素子であっても構わない。

【0071】

また、上記各実施形態では、内部回路16、26として、内部回路16、26内において電流の回り込みが発生する回路構成を例に挙げたが、内部回路16、26を通じて基準点に電流が回り込む回路構成とされることもある。この場合にも、その内部回路16、26のハイサイド側に回り込み防止回路15、25を配置することで、電流の回り込みを防止することが可能となる。

【0072】

さらに、上記各実施形態を組み合わせ、第1実施形態のゲート電圧監視回路と第2実施形態のセンス電圧監視回路の両方が備えられる形態とされる場合にも、本発明を適用するができる。その場合、各内部回路16、26のハイサイド側に回り込み防止回路15、25を備えるようにすればよい。

【符号の説明】

【0073】

1 IGBT

2 抵抗

10 通常時駆動回路(第1駆動回路))

11、21 駆動電圧生成回路

12、22 オン側回路

13、23 オフ側回路

14a、14b、24a、24b 抵抗

15、25 回り込み防止回路(第1、第2回り込み防止回路)

15a、25a 定電流源

15b、25b 制御スイッチ

15c、25c ツェナーダイオード

15d、25d、15e、25e 第1、第2トランジスタ

15f、25f 参照電圧回路

15h、25h 抵抗

16、26 内部回路(第1、第2内部回路))

16a、16b、26a、26b 抵抗

16c、26c、16d、26d コンパレータ

20 放電時駆動回路(第2駆動回路)

30、40 第1、第2電源

50、60 スイッチ

【特許請求の範囲】

【請求項1】

制御端子への入力電圧に基づいて、負荷に接続される接続ラインのオンオフ制御を行うスイッチング素子(1)と、

第1電源(30)を電源として作動させられ、前記スイッチング素子(1)の前記制御端子の入力電圧印加を行う第1駆動回路(10)と、

前記第1電源(30)とは異なる第2電源(40)を電源として作動させられ、前記第1駆動回路(10)が作動させられていないときに、前記スイッチング素子(1)の前記制御端子の入力電圧印加を行う第2駆動回路(20)と、を備えてなる負荷駆動装置において、

前記第1駆動回路(10)には、前記スイッチング素子(1)の所定部位と電気的に接続される第1内部回路(16)が備えられていると共に、前記第2駆動回路(20)にも、前記スイッチング素子(1)の所定部位と電気的に接続される第2内部回路(26)が備えられており、

前記第1駆動回路(10)の前記第1内部回路(16)と前記スイッチング素子(1)との間に、前記第2駆動回路(20)が前記スイッチング素子(1)を制御するときに、前記第1内部回路(16)と前記スイッチング素子(1)との間をオフすることで、前記第2内部回路(26)と前記スイッチング素子(1)との接続点から前記第1内部回路(16)への電流の回り込み防止する第1回り込み防止回路(15)が備えられていると共に、

前記第2駆動回路(20)の前記第2内部回路(26)と前記スイッチング素子(1)との間に、前記第1駆動回路(10)が前記スイッチング素子(1)を制御するときに、前記第2内部回路(26)と前記スイッチング素子(1)との間をオフすることで、前記第1内部回路(16)と前記スイッチング素子(1)との接続点から前記第2内部回路(26)への電流の回り込み防止する第2回り込み防止回路(25)が備えられていることを特徴とする負荷駆動装置。

【請求項2】

前記第1回り込み防止回路(15)は、

前記第1電源(30)からの電源供給に基づいて定電流を生成する定電流源(15a)と、

前記定電流源(15a)の定電流の流れをオンオフする制御スイッチ(15b)と、

前記定電流源(15a)から流される定電流に基づいて前記第1内部回路(16)と前記スイッチング素子(1)との間のオンオフを制御するMOSFET(15g)と、

前記MOSFET(15g)のゲートと所定電位とされる基準点との間に接続されたPNPトランジスタ(15e)と、

前記PNPトランジスタ(15e)のベース−コレクタ間を参照電圧に固定する参照電圧回路(15f)とを有し、

前記第2駆動回路(20)が前記スイッチング素子(1)を制御するときに、当該第1回り込み回路(15)に備えられる前記制御スイッチ(15b)をオフして前記MOSFET(15g)をオフすることで、前記第1内部回路(16)と前記スイッチング素子(1)との間をオフし、

前記第2回り込み防止回路(25)は、

前記第2電源(40)からの電源供給に基づいて定電流を生成する定電流源(25a)と、

前記定電流源(25a)の定電流の流れをオンオフする制御スイッチ(25b)と、

前記定電流源(25a)から流される定電流に基づいて前記第2内部回路(26)と前記スイッチング素子(1)との間のオンオフを制御するMOSFET(25g)と、

前記MOSFET(25g)のゲートと所定電位とされる基準点との間に接続されたPNPトランジスタ(25e)と、

前記PNPトランジスタ(25e)のベース−コレクタ間を参照電圧に固定する参照電圧回路(25f)とを有し、

前記第1駆動回路(10)が前記スイッチング素子(1)を制御するときに、当該第2回り込み回路(25)に備えられる前記制御スイッチ(25b)をオフして前記MOSFET(25g)をオフすることで、前記第2内部回路(26)と前記スイッチング素子(1)との間をオフすることを特徴とする請求項1に記載の負荷駆動装置。

【請求項3】

前記第1回り込み防止回路(15)に備えられる前記MOSFET(15g)のゲートにはツェナーダイオード(15c)とPNPトランジスタ(15d)が接続され、これらツェナーダイオード(15c)のツェナー降伏電圧とPNPトランジスタ(15d)の順方向電圧Vfによって前記MOSFET(15g)のゲート−ソース間が固定されており、

前記第2回り込み防止回路(25)に備えられる前記MOSFET(25g)のゲートにもツェナーダイオード(25c)とPNPトランジスタ(25d)が接続され、これらツェナーダイオード(25c)のツェナー降伏電圧とPNPトランジスタ(25d)の順方向電圧Vfによって前記MOSFET(25g)のゲート−ソース間が固定されていることを特徴とする請求項2に記載の負荷駆動装置。

【請求項4】

前記第1内部回路(16)および前記第2内部回路(26)は、前記スイッチング素子(1)の所定部位として、前記スイッチング素子(1)の制御端子に接続されていることを特徴とする請求項1ないし3のいずれか1つに記載の負荷駆動装置。

【請求項5】

前記第1内部回路(16)および前記第2内部回路(26)は、

前記スイッチング素子(1)の制御端子であるゲートの電圧を監視するゲート電圧監視回路であり、

前記第1内部回路(16)にて構成される前記ゲート電圧監視回路は、前記スイッチング素子のゲート電圧を分圧する分圧抵抗(16a、16b)と、該分圧抵抗(16a、16b)による分圧電圧値をゲート閾値電圧と大小比較するコンパレータ(16c)とを有し、該コンパレータ(16c)の電源供給が前記第1電源(30)にて行われており、

前記第2内部回路(26)にて構成される前記ゲート電圧監視回路も、前記スイッチング素子のゲート電圧を分圧する分圧抵抗(26a、26b)と、該分圧抵抗(26a、26b)による分圧電圧値をゲート閾値電圧と大小比較するコンパレータ(26c)とを有し、該コンパレータ(26c)の電源供給が前記第2電源(40)にて行われていることを特徴とする請求項4に記載の負荷駆動装置。

【請求項6】

前記第1内部回路(16)および前記第2内部回路(26)は、前記スイッチング素子(1)の所定部位として、前記スイッチング素子(1)のセンス端子に接続されていることを特徴とする請求項1ないし5のいずれか1つに記載の負荷駆動装置。

【請求項7】

前記第1内部回路(16)および前記第2内部回路(26)は、

前記スイッチング素子(1)のセンス端子のセンス電圧を監視するセンス電圧監視回路であり、

前記第1内部回路(16)にて構成される前記センス電圧監視回路は、前記スイッチング素子のセンス電圧をセンス閾値電圧と大小比較するコンパレータ(16d)を有し、該コンパレータ(16d)の電源供給が前記第1電源(30)にて行われており、

前記第2内部回路(26)にて構成される前記センス電圧監視回路も、前記スイッチング素子のゲート電圧をセンス閾値電圧と大小比較するコンパレータ(26d)を有し、該コンパレータ(26d)の電源供給が前記第2電源(40)にて行われていることを特徴とする請求項6に記載の負荷駆動装置。

【請求項1】

制御端子への入力電圧に基づいて、負荷に接続される接続ラインのオンオフ制御を行うスイッチング素子(1)と、

第1電源(30)を電源として作動させられ、前記スイッチング素子(1)の前記制御端子の入力電圧印加を行う第1駆動回路(10)と、

前記第1電源(30)とは異なる第2電源(40)を電源として作動させられ、前記第1駆動回路(10)が作動させられていないときに、前記スイッチング素子(1)の前記制御端子の入力電圧印加を行う第2駆動回路(20)と、を備えてなる負荷駆動装置において、

前記第1駆動回路(10)には、前記スイッチング素子(1)の所定部位と電気的に接続される第1内部回路(16)が備えられていると共に、前記第2駆動回路(20)にも、前記スイッチング素子(1)の所定部位と電気的に接続される第2内部回路(26)が備えられており、

前記第1駆動回路(10)の前記第1内部回路(16)と前記スイッチング素子(1)との間に、前記第2駆動回路(20)が前記スイッチング素子(1)を制御するときに、前記第1内部回路(16)と前記スイッチング素子(1)との間をオフすることで、前記第2内部回路(26)と前記スイッチング素子(1)との接続点から前記第1内部回路(16)への電流の回り込み防止する第1回り込み防止回路(15)が備えられていると共に、

前記第2駆動回路(20)の前記第2内部回路(26)と前記スイッチング素子(1)との間に、前記第1駆動回路(10)が前記スイッチング素子(1)を制御するときに、前記第2内部回路(26)と前記スイッチング素子(1)との間をオフすることで、前記第1内部回路(16)と前記スイッチング素子(1)との接続点から前記第2内部回路(26)への電流の回り込み防止する第2回り込み防止回路(25)が備えられていることを特徴とする負荷駆動装置。

【請求項2】

前記第1回り込み防止回路(15)は、

前記第1電源(30)からの電源供給に基づいて定電流を生成する定電流源(15a)と、

前記定電流源(15a)の定電流の流れをオンオフする制御スイッチ(15b)と、

前記定電流源(15a)から流される定電流に基づいて前記第1内部回路(16)と前記スイッチング素子(1)との間のオンオフを制御するMOSFET(15g)と、

前記MOSFET(15g)のゲートと所定電位とされる基準点との間に接続されたPNPトランジスタ(15e)と、

前記PNPトランジスタ(15e)のベース−コレクタ間を参照電圧に固定する参照電圧回路(15f)とを有し、

前記第2駆動回路(20)が前記スイッチング素子(1)を制御するときに、当該第1回り込み回路(15)に備えられる前記制御スイッチ(15b)をオフして前記MOSFET(15g)をオフすることで、前記第1内部回路(16)と前記スイッチング素子(1)との間をオフし、

前記第2回り込み防止回路(25)は、

前記第2電源(40)からの電源供給に基づいて定電流を生成する定電流源(25a)と、

前記定電流源(25a)の定電流の流れをオンオフする制御スイッチ(25b)と、

前記定電流源(25a)から流される定電流に基づいて前記第2内部回路(26)と前記スイッチング素子(1)との間のオンオフを制御するMOSFET(25g)と、

前記MOSFET(25g)のゲートと所定電位とされる基準点との間に接続されたPNPトランジスタ(25e)と、

前記PNPトランジスタ(25e)のベース−コレクタ間を参照電圧に固定する参照電圧回路(25f)とを有し、

前記第1駆動回路(10)が前記スイッチング素子(1)を制御するときに、当該第2回り込み回路(25)に備えられる前記制御スイッチ(25b)をオフして前記MOSFET(25g)をオフすることで、前記第2内部回路(26)と前記スイッチング素子(1)との間をオフすることを特徴とする請求項1に記載の負荷駆動装置。

【請求項3】

前記第1回り込み防止回路(15)に備えられる前記MOSFET(15g)のゲートにはツェナーダイオード(15c)とPNPトランジスタ(15d)が接続され、これらツェナーダイオード(15c)のツェナー降伏電圧とPNPトランジスタ(15d)の順方向電圧Vfによって前記MOSFET(15g)のゲート−ソース間が固定されており、

前記第2回り込み防止回路(25)に備えられる前記MOSFET(25g)のゲートにもツェナーダイオード(25c)とPNPトランジスタ(25d)が接続され、これらツェナーダイオード(25c)のツェナー降伏電圧とPNPトランジスタ(25d)の順方向電圧Vfによって前記MOSFET(25g)のゲート−ソース間が固定されていることを特徴とする請求項2に記載の負荷駆動装置。

【請求項4】

前記第1内部回路(16)および前記第2内部回路(26)は、前記スイッチング素子(1)の所定部位として、前記スイッチング素子(1)の制御端子に接続されていることを特徴とする請求項1ないし3のいずれか1つに記載の負荷駆動装置。

【請求項5】

前記第1内部回路(16)および前記第2内部回路(26)は、

前記スイッチング素子(1)の制御端子であるゲートの電圧を監視するゲート電圧監視回路であり、

前記第1内部回路(16)にて構成される前記ゲート電圧監視回路は、前記スイッチング素子のゲート電圧を分圧する分圧抵抗(16a、16b)と、該分圧抵抗(16a、16b)による分圧電圧値をゲート閾値電圧と大小比較するコンパレータ(16c)とを有し、該コンパレータ(16c)の電源供給が前記第1電源(30)にて行われており、

前記第2内部回路(26)にて構成される前記ゲート電圧監視回路も、前記スイッチング素子のゲート電圧を分圧する分圧抵抗(26a、26b)と、該分圧抵抗(26a、26b)による分圧電圧値をゲート閾値電圧と大小比較するコンパレータ(26c)とを有し、該コンパレータ(26c)の電源供給が前記第2電源(40)にて行われていることを特徴とする請求項4に記載の負荷駆動装置。

【請求項6】

前記第1内部回路(16)および前記第2内部回路(26)は、前記スイッチング素子(1)の所定部位として、前記スイッチング素子(1)のセンス端子に接続されていることを特徴とする請求項1ないし5のいずれか1つに記載の負荷駆動装置。

【請求項7】

前記第1内部回路(16)および前記第2内部回路(26)は、

前記スイッチング素子(1)のセンス端子のセンス電圧を監視するセンス電圧監視回路であり、

前記第1内部回路(16)にて構成される前記センス電圧監視回路は、前記スイッチング素子のセンス電圧をセンス閾値電圧と大小比較するコンパレータ(16d)を有し、該コンパレータ(16d)の電源供給が前記第1電源(30)にて行われており、

前記第2内部回路(26)にて構成される前記センス電圧監視回路も、前記スイッチング素子のゲート電圧をセンス閾値電圧と大小比較するコンパレータ(26d)を有し、該コンパレータ(26d)の電源供給が前記第2電源(40)にて行われていることを特徴とする請求項6に記載の負荷駆動装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−228116(P2012−228116A)

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願番号】特願2011−95231(P2011−95231)

【出願日】平成23年4月21日(2011.4.21)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願日】平成23年4月21日(2011.4.21)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]