超低消費電力CMOSベースのバイオセンサ回路

【課題】 超低消費電力CMOSベースのバイオセンサ回路を提供する。

【解決手段】 電荷を有する材料を同定するように構成された装置であって、この装置は、第2の電界効果トランジスタ(FET)に結合された第1のFETを含む反転利得増幅器を有し、第1のFETのゲートは、電荷を検知するように構成され、かつ、増幅器の出力は、材料を同定するための電荷の測定値を与える。

【解決手段】 電荷を有する材料を同定するように構成された装置であって、この装置は、第2の電界効果トランジスタ(FET)に結合された第1のFETを含む反転利得増幅器を有し、第1のFETのゲートは、電荷を検知するように構成され、かつ、増幅器の出力は、材料を同定するための電荷の測定値を与える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、生体分子を検知することに関し、より具体的には、電界効果トランジスタ・ベースのセンサを用いた生体分子の検出を自動化する電子回路に関する。

【背景技術】

【0002】

たんぱく質又はウィルスを含み得る生体分子は、多くの疾患において重要な役割を果たす。従って、生体分子(biological molecule又はbiomolecule)の同定は、改善された、費用効率が高い病気診断及び治療に不可欠である。

【0003】

生体分子を検出するのに用いられる従来技術には、蛍光標識法又は放射性標識法、及びパッチ・クランプ法が含まれる。残念なことに、これらの従来技術は、労働集約的で高価であることがあり、その結果、これらの技術の費用効率がもっと高かったとしたら救われたであろう患者の数が減少する。

【発明の概要】

【発明が解決しようとする課題】

【0004】

従って、生体分子を検出するための改善された技術の必要性が存在する。より具体的には、改善された技術は、従来技術に比べて労働集約的でなく、かつ、安価なものである必要がある。

【課題を解決するための手段】

【0005】

電荷を有する材料を同定するように構成された装置を設けることにより、従来技術の欠点が克服され、付加的な利点が与えられ、この装置は、第2の電界効果トランジスタ(FET)に結合された第1のFETを含む反転利得増幅器を有し、第1のFETのゲートが電荷を検知するように構成され、増幅器の出力は、材料を同定するための電荷の測定値を与える。

【0006】

第1の電界効果トランジスタ(FET)のゲートにより電荷を検知することであって、第1のFET及び第2のFETは電荷の測定値を与える出力を有する反転利得増幅器回路を形成する、当該検知することと、反転利得増幅器回路により電荷を測定して材料を同定することとを含む、電荷を有する材料を同定する方法も開示される。

【0007】

第1の電界効果トランジスタ(FET)のゲートにより電荷を検知することであって、第1のFET及び第2のFETは電荷の測定値を与える出力を有する反転利得増幅器回路を形成する、当該検知することと、反転利得増幅器回路により電荷を測定して材料を同定することと、測定値を格納すること、測定値を分析することと、測定値をユーザに提示することのうちの少なくとも1つと、を含む方法を実装することにより、電荷を有する材料を同定するための機械実行可能命令を含む非一時的(non-transitory)機械可読媒体がさらに開示される。

【0008】

上述した方法に対応するシステム及びコンピュータ・プログラム製品もまた本明細書で説明され、特許請求される。

【0009】

さらなる特徴及び利点が、本発明の例示的な実施形態の技術を通して実現される。本発明の他の実施形態及び態様は、本明細書で詳細に説明され、特許請求される本発明の一部とみなされる。利点及び特徴を有する本発明をより良く理解するために、説明及び図面を参照されたい。

【0010】

本発明と考えられる主題は、本明細書の終わりの特許請求の範囲において具体的に示され、明確に特許請求されている。本発明の前述及び他の目的、特徴、並びに利点は、同様の要素に同様の番号が付けられている添付図面と併せて用いられる以下の詳細な説明から明らかである。

【図面の簡単な説明】

【0011】

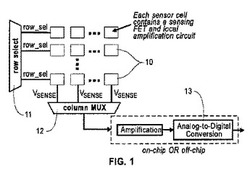

【図1】センサ・セルのアレイの例示的な実施形態を示す。

【図2】生体分子を検知するように構成された電界効果トランジスタ(FET)の例示的な実施形態を示す。

【図3】センサFETを含む反転利得増幅器回路の概略図を示す。

【図4】反転利得増幅器回路の反転利得特性の態様を示す。

【図5】反転利得増幅器回路の出力を検知ラインに結合するコンポーネントにおいて低い抵抗を有するように構成された回路を有する1つのセンサ・セルの態様を示す。

【図6】測定値を得るために選択されないセンサ・セル10内のFETをオフにするように構成された回路の態様を示す。

【図7】反転利得増幅器回路においてp型FETのソースと直列配置されたp型FETを有し、かつ、反転利得増幅器回路の電源を切るように構成された、回路の態様を示す。

【図8】反転利得増幅器回路においてセンサFETのソースと直列配置されたn型FETを有し、かつ、反転利得増幅器回路の電源を切るように構成された、回路の態様を示す。

【図9】VSENSEラインからの測定信号を減結合し、増幅するように構成され、同じくVX信号がVSENSEラインに伝送される前に、VX信号をΔVGNの範囲で線形増幅する増幅回路及び減結合回路の態様を示す。

【図10】反転利得増幅器の出力対センサFETのゲート電圧のプロットを示す。

【図11】反転利得増幅器への電流路を遮断するための実施形態を示す。

【図12】反転利得増幅器への電流路を遮断するための実施形態を示す。

【図13】反転利得増幅器回路におけるセンサFET及び別のFETの電圧閾値の変化に対応する、センサFETのゲート電圧のバイアス点の移動を示す。

【図14】関連した電荷を有する生体分子を同定する方法の一例を示す。

【発明を実施するための形態】

【0012】

生体分子を検知又は検出するための改善された技術が開示され、本明細書において検知(sensing)及び検出(detecting)という用語は、交換可能に用いられる。装置及び方法を含む技術は、生体分子を検知するためのセンサとして電界効果トランジスタ(FET)を用いることを必要とする。この技術は、FETセンサを用いた生体分子の検出、従って同定を自動化する回路の実施形態を提供する。さらに、この技術は、標準的な相補型金属酸化膜半導体(CMOS)技術を用いて、自動化された検知プラットフォームを製造することを必要とする。従って、自動化された検出及び標準的な製造技術により、効率的で費用効率の高い生体分子の検出が提供される。

【0013】

センサ・セルのアレイが、生体分子を検出するために用いられ、そこで各々のセンサ・セルは、少なくとも1つのFETセンサと、FETセンサからの信号を増幅するための関連回路とを含む。電圧読み値のような信号を用いて、生体分子を検出する。さらに、特定のセンサ・セルからの読み値(すなわち、信号)を選択するため、及び、電力を節約するために、回路を設けることができる。

【0014】

センサ・セルのアレイを用いることには、少なくとも2つの利点がある。1つの利点は、1つのセンサの読み値を用いて、別のセンサ・セルからの読み値を確認又は検証できることである。別の利点は、特定のセンサ・セルが、特定のタイプの生体分子を検出するように最適化されたFETセンサを有し得ることである。

【0015】

ここで図1を参照されたい。図1は、センサ・セル10のアレイの例示的な実施形態を示す。各々のセンサ・セル10は、生体分子を検知し、生体分子を検出するために用いることができる、電圧読み値のような信号を提供するように構成される。図1の実施形態におけるセンサ・セル10のアレイは、各セル10が行番号及び列番号により定められるマトリクス構成である。図1の実施形態において、行選択回路11は、選択された行における各センサ・セル10に通電することにより読み取られるセル10の行を選択するように構成される。列多重化回路12は、各列における1つのセル10からの信号を読み取るように構成される。従って、行を選択することにより、行内の各セル10が、列多重化回路12により読み取られる。

【0016】

さらに図1を参照すると、各セル10についての増幅信号又は電圧読み値は、VSENSEと呼ばれる。VSENSEは、さらなる処理のためにアレイの外に移送されるように、比較的長い相互接続ラインに送られる。VSENSEは、センサ・セル10の外で再び増幅し、次に、アナログ・デジタル変換器(ADC)13を介してデジタル信号に変換することができる。1つの実施形態においては、行内にあるセンサ・セル10と同じ数のADCが存在し得るので、各行からの全てのVSENSE出力を同時にデジタル信号に変換することができる。別の実施形態においては、より少ないADCが存在し得る。より少ないADCを用いることで、VSENSE信号を、列多重化回路を用いて順番に選択することが必要になる。これにより、アナログ・デジタル変換を行うのにより多くの時間がかかるが、半導体チップ上で必要とされる面積が少なくなるという利点がある。

【0017】

ここで図2を参照されたい。図2は、生体分子21を検知するように構成されたFET20の例示的な実施形態を示す。図2の実施形態におけるFET20は、ゲート誘電体23で覆われたフィン22を有するfinFETである。ゲート誘電体23の1つの限定されない実施形態は、SiO2/HfO2である。ゲート誘電体23は、生体分子21に付着するように構成されたゲート表面材料24で覆われている。FET20は、従来の上部ゲートをもたない。電解質25がゲート表面材料24を囲み、上部ゲートとして働く。フィン22及びゲート誘電体23は、FET20のバックゲートであるシリコン層27の上に配置された埋め込み酸化物(BOX)層26の上に配置される。

【0018】

FET20のドレイン電流は、閾値以下(sub-threshold)領域で動作される。生体分子21を検知するために、生体分子21はゲート表面材料24に結合し、電荷をゲート誘電体23に移送する。ゲート誘電体23における電荷はドレイン電流に影響を与え、このことは、FET20のドレイン・ソース間電圧に影響を与える。測定されたドレイン・ソース間電圧が、VSENSEである。各々の異なる生体分子21は、一般に、固有の電荷を有するため、VSENSEの測定値を用いて、検出された特定の生体分子21を同定することができる。

【0019】

生体分子21を検知するためにFET20を用いる利点は、FET20が、生体分子21の電荷に対して高い感度をもつことである。高感度は、小さい閾値以下勾配の結果としてもたらされ、ゲート電圧の小さな変化がドレイン電流の大きい変化を引き起こし、ドレイン・ソース間電圧(すなわちVSENSE)の大きな変化をもたらす。非finFETと比較すると、finFETにおけるゲート誘電体23の大きな表面積は、応答時間の改善をもたらす。FET20として用いられるfinFETは、ゲート誘電体23の表面積をさらに増大させるために、単一のフィン又はフィンのアレイを有することができる。

【0020】

図2の実施形態はfinFETを示すが、他のタイプのFETを用いて、生体分子21を検出することもできる。FET20は、一般に、相補型金属酸化膜半導体(CMOS)技術を用いて実装される。

【0021】

ここで図3を参照されたい。図3は、反転利得増幅器回路30の概略図を示す。反転利得増幅器回路30は、生体分子21を検知するためのセンサとしてのFET20を含む。図3の実施形態において、FET20は、n型FETであり、FET N1と示される。FET N1は、p型FET、すなわちFET P1と直列に結合される。つまり、FET N1のドレインはFET P1のドレインに結合され、FET P1のソースは、電圧VDD1を供給する、VDD1と示される電源に結合される。FET N1及びFET P1は共に反転利得増幅器回路30を形成する。さらに、別のn型FET、すなわちFET N2は、生体分子21の検出された電荷に関連する、FET N1の出力Vxを、VSENSEライン31に伝える。VSENSEライン31において読み取られた電圧は、VSENSEと呼ばれる。図3の実施形態において、VSENSEライン31は、センサ・セル10の外にある。FET N2は、行選択回路11から「行選択」信号(すなわち、row_sel)を受け取るように構成されているので、FET N2のゲートに通電されると(すなわち、VDD1に設定されると)、出力電圧VxがVSENSEライン31に結合される。FET N2が「オン」であるとき、VSENSEは、概ねVxと同じになる。

【0022】

ここで図4を参照されたい。図4は、反転利得増幅器回路30の反転利得特性の態様を示す。増幅器回路30の出力が、FET N1のゲート電圧VGNに対してグラフ化される。検知FET N1は、閾値以下領域で動作するようにバイアスがかけられ、0<VGN<VT,N1となる。p型FET P1は、VGP≦VDD1−VT,P1となるように動作するようにバイアスがかけられ、ここで、VT,P1はP型FET P1の閾値である。FET N1のゲート電圧VGNが増大する場合、電圧Vxは、図4における曲線の動作領域の勾配に応じて低減する。同様に、FET N1のゲート電圧VGNが低減する場合、電圧Vxは、その曲線の動作領域の勾配に応じて。FET N1の感度が高いために、一般に、VGNの小さな変化は、Vxの大きな変化をもたらす。

【0023】

ここで図5を参照されたい。図5は、VxをVSENSEラインに結合するコンポーネントにおいて低抵抗を有するように構成された回路を有するセンサ・セル10の態様を示す。図5の回路において、p型FET、FET P2が、FET N2に対して並列配置され、FET N2のゲートが、行選択信号の補数に結合される。この構成により、広範囲のVxの値がVSENSEラインに伝えられる。しかしながら、この構成はまた、読み取りのために選択されていないセンサ・セル10における漏れも増大させることが留意される。

【0024】

選択されていないセンサ・セル10において、VDD1と接地GNDとの間に電流路がある。これにより、読み取りのためにセル10にアクセスされていなかったとしても、センサ・セル10による電力消費がもたらされ得る。この電力消費を克服する技術の3つの例が、図6、図7、及び図8を参照して本明細書に開示される。

【0025】

ここで図6を参照されたい。図6は、読み取りのために選択されていないセンサ・セル10内のFET P1をオフにするように構成された回路の態様を示す。図6の回路は、VDD1と、アレイの行における全てのFET P1のゲートとの間に配置されたp型FET、すなわちFET P8を含む。さらに、n型FET N9及びp型FET P9が並列接続され、それらのドレインがつなぎ合わされ、VGPに接続され、それらのソースは、アレイの行における全てのFET P1のゲートに接続される。FET P8及びFET N9のゲートは、行イネーブル信号「row_sel」に接続される。FET P9のゲートは、「row_sel」信号の補数に接続される。この回路は、行内の全てのセンサ・セル10に共通である。行内の全てのセンサ・セル10は、共通のVGPを有する。選択されていないセンサ・セル10において、行選択は「0」となり、従って、FET P8はオンとなり、行内の全てのFET P1のゲートをVDD1に接続する。従って、全ての選択されていないセンサ・セル10においては、FET P1はオフにされ、VDD1からGNDへの経路を流れる電流を停止させる。選択された行において、FET P8はオフとなり、FET P9及びFET N9はオンとなり、行内の全てのFET P1のゲートがVGPに接続される。

【0026】

ここで図7を参照されたい。図7は、FET P1と直列配置された、すなわち電源VDD1とFET P1のソースとの間に配置されたp型FET、すなわちFET P3を有する回路の態様を示す。行が選択されていないとき、すなわち行選択信号が低いとき、FET P3はオフにされ、従って、VDD1からGNDへの経路を流れる電流が停止される。

【0027】

ここで図8を参照されたい。図8は、FET N1と直列配置された、すなわちFETN1のソースと接地GNDとの間に配置されたn型FET、すなわちFET N3を有する回路の態様を示す。行が選択されていないとき、すなわち行選択信号が低いとき、FET N3はオフにされ、従って、VDD1からGNDへの経路を流れる電流が停止される。

【0028】

図1を参照すると、幾つかのセンサ・セル10を共通のVSENSEラインに接続し、非常に長い、従って、比較的大きい抵抗及びキャパシタンスを有するVSENSEラインをもたらすことができる。任意の所与の時点において、他の選択されていないセンサ・セル10におけるFET N2(図3、図5、図7及び図8に示される)がオフである間、1つの選択されたセンサ・セル10だけが、VSENSEラインに伝送された測定値を有することができる。FET N1及びFET P1は、閾値以下領域で動作し、深飽和状態(deep saturation)(VGN=VDD1及びVGP=0であるときに生じる)で動作しないので、FET N1及びFET P1を通る電流は非常に低いものである。従って、VX信号を、FET N1及びFET P1を通してVSENSEラインに接続する接続ラインの充電及び/又は放電が、VX信号への著しい雑音の一因となり得る。さらに、充電及び/又は放電は、VSENSEラインに伝送されたVX信号を安定化させるのにかかる時間量を増大させ得る。雑音を防止し、安定化時間を低減させるために、接続ライン内に配置された増幅及び減結合回路が開示される。

【0029】

ここで図9を参照されたい。図9は、VSENSEラインからのVX信号を減結合し、同じく、VX信号がVSENSEラインに伝送される前に、VX信号をΔVGNの範囲に線形増幅する増幅及び減結合回路90の態様を示す。増幅及び減結合回路90は、n型FET、すなわちFET N4及びFET N5と、p型FET、すなわちFET P4及びFET P5とを含む。FET N4、FET N5、FET P4及びFET P5は、図9に示されるように、(1)VX信号をもたらす反転利得増幅器回路30におけるノードと(2)VSENSEラインとの間に構成される。FET N4及びFET P4は、入力としてVX信号を、出力としてVSENSEを有するインバータ構成であることが留意される。FET N5及びFET P5は、フィードバック・トランジスタである。別の実施形態において、独立したバックゲート制御を有するfinFETのようなマルチゲートFETを、単一ゲートFETの代わりに用いて、増幅及び減結合回路90を作製することができる。FET N4及びFET N5は、バックゲートとしてFET N5を有する単一のマルチゲートFETと置き換えることができる。同様に、FET P4及びFET P5は、バックゲートとしてFET P5を有する単一のマルチゲートFETと置き換えることもできる。図9に示されるように、増幅及び減結合回路90は、VSENSEについての所望の電圧範囲を達成するように、別個の電源VDD2(電圧VDD2を有する)に結合される。

【0030】

反転利得増幅器回路30は、VGNの変化に起因するVXの変化に基づいている。VGNの変化に起因するVXの変化は、ΔVX/ΔVGNが所定の範囲のΔVGNにおける定関数である場合、決定論的に相関し得る。FEN N1及びFET P1は反転利得回路を形成するので、利得は、バイアス点の近くで、すなわち図4に示されるようなVGNの選択された値において、非常に高くなる。VGNの増幅は有益であるが、低い値又は高い値のVGNにおけるVXの飽和のために、増幅がΔVGNの値の範囲を制限することがある。ΔVGNの値の全範囲においてΔVXとΔVGNとの間に相関を有することが好ましい。

【0031】

ここで図10を参照されたい。図10は、VSENSE及びVX対VGNのプロットを示す。線形化回路は、バイアス点から広範囲のΔVGNにおけるVSENSEとVGNとの間の線形相関をもたらすことが留意される。図10はまた、フィードバックFET N5及びFET P5を有する及びこれらを有さないVSENSEのプロットも示す。フィードバックがない場合、反転利得増幅器回路30の出力は、非常に高い増幅を有し、そのため、VGNのわずかな変化に対して大きなVSENSEの変化が生じる可能性がある。従って、VSENSEは、VGNの大きな変化に対して飽和することがある。この飽和の可能性により、VGNの動作領域が制限され、従って、生体分子21の電荷の大きな変化を検出することに起因する、VGNの大きな変化を検出するために、フィードバックが必要となる。

【0032】

増幅及び減結合回路90における電力消費を低減させるために、図9に示されるように、電源VDD2とGNDとの間の電流路を遮断することができる。図11は、p型FET、すなわちFET P6を、電源VDD2とFET P4及びP5のソースとの間に配置することによって電流路を遮断するための実施形態を示す。図12は、n型FET、すなわちFET N6を、FET N4及びFET N5のソースと接地との間に配置することにより電流路を遮断するための別の実施形態を示す。

【0033】

電流遮断回路を含むことができる増幅及び減結合回路90は、各々のセンサ・セル10内に実装することができ、又は代替的に、回路90を列内のセンサ・セル10と共有することによって実装することもできる。共有する実施形態においては、増幅及び減結合回路90は、VSENSEラインと図1に示される列多重化回路12との間に結合され、各々のセンサ・セル10が必要とする面積を低減させる。

【0034】

次に、製造関連のばらつきを緩和するためのセンサ較正について説明する。センサ・セル10のアレイを製造するために用いられる半導体チップにおける製造の不完全性のために、生体検知セル10内のFETが、所望のゲート長、幅、閾値電圧等をもたないことがある。従って、ΔVGNへのVSENSEの製造前較正(pre-fabrication calibration)が正確でないことがある。そこで、各センサ・セル10の製造後較正(post-fabrication calibration)が開示される。製造後較正は、次の方法で達成することができる。第1に、製造前の分析に基づいてVGNを選択する。第2に、製造されたチップにおいて、VGNを印加し、各々のセンサ・セル10についてVSENSE(V0SENSEと呼ばれる)を測定する。この較正測定において、生体分子21が存在しないことが留意される。V0SENSEは、デジタル信号に変換されたアナログ電圧信号であり、これはチップの上に統合された又は外部接続の従来の半導体メモリ内に格納することができる。各々のセンサ・セル10についての格納されたV0SENSEのデジタル値は、そのセンサ・セル10が行う将来の測定のための基準点として働く。第3に、実際の検知用途において、測定されたVSENSEのデジタル値は、オリジナルのV0SENSEの格納値を参照する。この較正技術は、ハードウェアのどのような変更も必要としない。従って、迅速な較正、すなわちV0SENSEの測定後、同じハードウェアを、異なる種類の生体分子21に繰り返し使用することができる。

【0035】

次に、異なるバイアス点(VGN)を必要とし得る様々な生体分子21を試験するためのセンサ調整について説明する。検知FET N1の動作範囲は、バイアス点VGNの選択によって決まる。FET N1のゲートに結合している間、生体分子21は、VGNによる如何なる抵抗も受けるべきではない。異なる生体分子21が、異なるバイアス点、すなわちVGN値を必要とする場合、類似の±ΔVGN値を定めることができる。このことは、FET N1及びFET N1P1の閾値電圧VTを動的に制御することによって達成することができる。図13は、FET N1及びFET P1のVTの変化に伴うバイアス点VGNの移動を示す。このΔVT,N1,P1は、基板コンタクトを有するFET N1及びFET P1(すなわち、単一ゲートFET)の基板バイアスを変えることによって達成することができる。finFETのようなマルチゲートFETにおいては、これらのFETのバックゲート(又は第2のゲート)における電圧バイアスを制御することによって、VTを動的に変更することができる。

【0036】

図14は、関連した電荷を有する生体分子21を同定するための方法140の一例を示す。方法140は、FET20のゲート誘電体23により生体分子21の電荷を検知すること(ステップ141)を必要とする。FET20及び別のFETは、反転利得増幅器回路30を形成するように構成される。さらに、方法140は、反転利得増幅器回路によりゲートにおける電荷を測定して、生体分子21を同定すること(ステップ142)を必要とする。

【0037】

方法140及び上述の議論は、生体分子21の同定に関するものであるが、ゲート誘電体23に付着し得る電荷を有するいずれの材料を同定することもできる。一般に、各々の試験生体分子21/試験材料と関連付けられた基準電荷を定めるために、異なる生体分子21及び異なる電荷を有する材料の試験及び/又は分析が用いられる。このように、測定された電荷を基準電荷と比較することにより、生体分子21/材料を同定することができる。

【0038】

1つの実施形態においては、センサ10のアレイを1つのCMOSデバイス又は半導体「チップ」に組み込み、製造コストを下げ、信頼性を向上させることができる。さらに、行選択回路11、列多重化回路12、及びADC13のような、センサ10のアレイと共に用いられる他のコンポーネントを同じCMOSデバイスに組み込むこともできる。

【0039】

本発明の能力は、ソフトウェア、ファームウェア、ハードウェア、又はこれらの何らかの組み合わせの形で実装することができる。

【0040】

一例として、本発明の1つ又は複数の態様を、例えば、コンピュータ使用可能媒体を有する製品(例えば、1つ又は複数のコンピュータ・プログラム製品)内に含ませることができる。この媒体は、例えば、本発明の能力を提供し、助長するためのコンピュータ可読プログラム・コード手段を内部に組み入れている。この製品は、コンピュータ・システムの一部として含ませることができ、又は別個に販売することができる。

【0041】

さらに、本発明の能力を実施するように機械により実行可能な命令の少なくとも1つのプログラムを明確に具体化する、機械により読み取り可能な、少なくとも1つのプログラム・ストレージ・デバイスを提供することができる。

【0042】

本明細書での教示を支援して、デジタル及び/又はアナログ・システムを含む、種々の分析用コンポーネントを用いることができる。システムは、プロセッサ、ストレージ媒体、メモリ、入力、出力、通信リンク、ユーザ・インターフェース(プリンタ又はディスプレイのような)、ソフトウェア・プログラム、信号プロセッサ(デジタル又はアナログ)のようなコンポーネント、並びに当技術分野においてよく理解される幾つかの方法のいずれかで、本明細書に開示される装置及び方法の動作及び分析を提供する他のそうしたコンポーネント(レジスタ、キャパシタ、インダクタ及び他のもの)を有することができる。これらの教示は、必ずしもではないが、実行時にコンピュータに本発明の方法を実施させる、メモリ(ROM、RAM)、光学(CD−ROM)、又は磁気(ディスク、ハードドライブ)、或いはいずれかの他のタイプを含むコンピュータ可読媒体上に格納された一組のコンピュータ実行可能命令と併せて実装できると考えられる。これらの命令は、本開示において説明される機能に加えて、機器の動作、制御、データ収集、及び分析、並びにシステム設計者、所有者、ユーザ又は他のそのような人員が関連すると考える他の機能を提供することができる。

【0043】

本明細書で示されるフロー図は、例にすぎない。本発明の思想から逸脱することなく、本明細書で説明されるこれらの図又はステップ(若しくは動作)に対して多くの変形があり得る。例えば、ステップを異なる順番で行ってもよく、或いは、ステップを付加、削除又は変更してもよい。これらの変形の全ては、特許請求される本発明の一部と考えられる。

【0044】

実施形態の要素は、冠詞「1つ(a)」又は「1つ(an)」を用いて導入されている。この冠詞は、1つ又は複数の要素があることを意味するように意図される。「含む(including)」及び「有する(having)」という用語は、列挙された要素以外の付加的な要素があり得るように、包括的であることが意図される。接続詞「又は(or)」は、少なくとも2つの用語のリストと共に用いられるとき、いずれかの用語又は用語の組み合わせを意味するように意図される。「第1」、「第2」「第3」等という用語は、要素を区別するために用いられ、特定の順番を示すために用いられるものではない。「結合する(couple)」という用語は、別のコンポーネントに直接結合される、或いは1つ又は複数の中間コンポーネントを介して別のコンポーネントに間接的に結合される1つのコンポーネントに関する。

【0045】

好ましい実施形態を参照して本発明を説明してきたが、当業者であれば、本発明の範囲を逸脱することなく、種々の変更を行うことができること、及び、均等物をその要素と置き換えることができることを理解するであろう。さらに、本発明の本質的な範囲から逸脱することなく、特定の状態又は材料を本発明の教示に適合させるように、多くの修正を行うことができる。従って、本発明は、本発明を実行するために考えられる最良の形態として開示される特定の実施形態に限定されるものではなく、本発明は、添付の特許請求の範囲内に入る全ての実施形態を含むことが意図される。

【符号の説明】

【0046】

10:センサ・セル

11:行選択回路

12:列多重化回路

13:アナログ・デジタル変換器(ADC)

20:電界効果トランジスタ(FET)

21:生体分子

22:フィン

23:ゲート誘電体

24:ゲート表面材料

25:電解質

26:埋め込み酸化物(BOX)層

27:シリコン層

30:反転利得増幅器回路

31:VSENSEライン

90:増幅及び減結合回路

【技術分野】

【0001】

本発明は、一般に、生体分子を検知することに関し、より具体的には、電界効果トランジスタ・ベースのセンサを用いた生体分子の検出を自動化する電子回路に関する。

【背景技術】

【0002】

たんぱく質又はウィルスを含み得る生体分子は、多くの疾患において重要な役割を果たす。従って、生体分子(biological molecule又はbiomolecule)の同定は、改善された、費用効率が高い病気診断及び治療に不可欠である。

【0003】

生体分子を検出するのに用いられる従来技術には、蛍光標識法又は放射性標識法、及びパッチ・クランプ法が含まれる。残念なことに、これらの従来技術は、労働集約的で高価であることがあり、その結果、これらの技術の費用効率がもっと高かったとしたら救われたであろう患者の数が減少する。

【発明の概要】

【発明が解決しようとする課題】

【0004】

従って、生体分子を検出するための改善された技術の必要性が存在する。より具体的には、改善された技術は、従来技術に比べて労働集約的でなく、かつ、安価なものである必要がある。

【課題を解決するための手段】

【0005】

電荷を有する材料を同定するように構成された装置を設けることにより、従来技術の欠点が克服され、付加的な利点が与えられ、この装置は、第2の電界効果トランジスタ(FET)に結合された第1のFETを含む反転利得増幅器を有し、第1のFETのゲートが電荷を検知するように構成され、増幅器の出力は、材料を同定するための電荷の測定値を与える。

【0006】

第1の電界効果トランジスタ(FET)のゲートにより電荷を検知することであって、第1のFET及び第2のFETは電荷の測定値を与える出力を有する反転利得増幅器回路を形成する、当該検知することと、反転利得増幅器回路により電荷を測定して材料を同定することとを含む、電荷を有する材料を同定する方法も開示される。

【0007】

第1の電界効果トランジスタ(FET)のゲートにより電荷を検知することであって、第1のFET及び第2のFETは電荷の測定値を与える出力を有する反転利得増幅器回路を形成する、当該検知することと、反転利得増幅器回路により電荷を測定して材料を同定することと、測定値を格納すること、測定値を分析することと、測定値をユーザに提示することのうちの少なくとも1つと、を含む方法を実装することにより、電荷を有する材料を同定するための機械実行可能命令を含む非一時的(non-transitory)機械可読媒体がさらに開示される。

【0008】

上述した方法に対応するシステム及びコンピュータ・プログラム製品もまた本明細書で説明され、特許請求される。

【0009】

さらなる特徴及び利点が、本発明の例示的な実施形態の技術を通して実現される。本発明の他の実施形態及び態様は、本明細書で詳細に説明され、特許請求される本発明の一部とみなされる。利点及び特徴を有する本発明をより良く理解するために、説明及び図面を参照されたい。

【0010】

本発明と考えられる主題は、本明細書の終わりの特許請求の範囲において具体的に示され、明確に特許請求されている。本発明の前述及び他の目的、特徴、並びに利点は、同様の要素に同様の番号が付けられている添付図面と併せて用いられる以下の詳細な説明から明らかである。

【図面の簡単な説明】

【0011】

【図1】センサ・セルのアレイの例示的な実施形態を示す。

【図2】生体分子を検知するように構成された電界効果トランジスタ(FET)の例示的な実施形態を示す。

【図3】センサFETを含む反転利得増幅器回路の概略図を示す。

【図4】反転利得増幅器回路の反転利得特性の態様を示す。

【図5】反転利得増幅器回路の出力を検知ラインに結合するコンポーネントにおいて低い抵抗を有するように構成された回路を有する1つのセンサ・セルの態様を示す。

【図6】測定値を得るために選択されないセンサ・セル10内のFETをオフにするように構成された回路の態様を示す。

【図7】反転利得増幅器回路においてp型FETのソースと直列配置されたp型FETを有し、かつ、反転利得増幅器回路の電源を切るように構成された、回路の態様を示す。

【図8】反転利得増幅器回路においてセンサFETのソースと直列配置されたn型FETを有し、かつ、反転利得増幅器回路の電源を切るように構成された、回路の態様を示す。

【図9】VSENSEラインからの測定信号を減結合し、増幅するように構成され、同じくVX信号がVSENSEラインに伝送される前に、VX信号をΔVGNの範囲で線形増幅する増幅回路及び減結合回路の態様を示す。

【図10】反転利得増幅器の出力対センサFETのゲート電圧のプロットを示す。

【図11】反転利得増幅器への電流路を遮断するための実施形態を示す。

【図12】反転利得増幅器への電流路を遮断するための実施形態を示す。

【図13】反転利得増幅器回路におけるセンサFET及び別のFETの電圧閾値の変化に対応する、センサFETのゲート電圧のバイアス点の移動を示す。

【図14】関連した電荷を有する生体分子を同定する方法の一例を示す。

【発明を実施するための形態】

【0012】

生体分子を検知又は検出するための改善された技術が開示され、本明細書において検知(sensing)及び検出(detecting)という用語は、交換可能に用いられる。装置及び方法を含む技術は、生体分子を検知するためのセンサとして電界効果トランジスタ(FET)を用いることを必要とする。この技術は、FETセンサを用いた生体分子の検出、従って同定を自動化する回路の実施形態を提供する。さらに、この技術は、標準的な相補型金属酸化膜半導体(CMOS)技術を用いて、自動化された検知プラットフォームを製造することを必要とする。従って、自動化された検出及び標準的な製造技術により、効率的で費用効率の高い生体分子の検出が提供される。

【0013】

センサ・セルのアレイが、生体分子を検出するために用いられ、そこで各々のセンサ・セルは、少なくとも1つのFETセンサと、FETセンサからの信号を増幅するための関連回路とを含む。電圧読み値のような信号を用いて、生体分子を検出する。さらに、特定のセンサ・セルからの読み値(すなわち、信号)を選択するため、及び、電力を節約するために、回路を設けることができる。

【0014】

センサ・セルのアレイを用いることには、少なくとも2つの利点がある。1つの利点は、1つのセンサの読み値を用いて、別のセンサ・セルからの読み値を確認又は検証できることである。別の利点は、特定のセンサ・セルが、特定のタイプの生体分子を検出するように最適化されたFETセンサを有し得ることである。

【0015】

ここで図1を参照されたい。図1は、センサ・セル10のアレイの例示的な実施形態を示す。各々のセンサ・セル10は、生体分子を検知し、生体分子を検出するために用いることができる、電圧読み値のような信号を提供するように構成される。図1の実施形態におけるセンサ・セル10のアレイは、各セル10が行番号及び列番号により定められるマトリクス構成である。図1の実施形態において、行選択回路11は、選択された行における各センサ・セル10に通電することにより読み取られるセル10の行を選択するように構成される。列多重化回路12は、各列における1つのセル10からの信号を読み取るように構成される。従って、行を選択することにより、行内の各セル10が、列多重化回路12により読み取られる。

【0016】

さらに図1を参照すると、各セル10についての増幅信号又は電圧読み値は、VSENSEと呼ばれる。VSENSEは、さらなる処理のためにアレイの外に移送されるように、比較的長い相互接続ラインに送られる。VSENSEは、センサ・セル10の外で再び増幅し、次に、アナログ・デジタル変換器(ADC)13を介してデジタル信号に変換することができる。1つの実施形態においては、行内にあるセンサ・セル10と同じ数のADCが存在し得るので、各行からの全てのVSENSE出力を同時にデジタル信号に変換することができる。別の実施形態においては、より少ないADCが存在し得る。より少ないADCを用いることで、VSENSE信号を、列多重化回路を用いて順番に選択することが必要になる。これにより、アナログ・デジタル変換を行うのにより多くの時間がかかるが、半導体チップ上で必要とされる面積が少なくなるという利点がある。

【0017】

ここで図2を参照されたい。図2は、生体分子21を検知するように構成されたFET20の例示的な実施形態を示す。図2の実施形態におけるFET20は、ゲート誘電体23で覆われたフィン22を有するfinFETである。ゲート誘電体23の1つの限定されない実施形態は、SiO2/HfO2である。ゲート誘電体23は、生体分子21に付着するように構成されたゲート表面材料24で覆われている。FET20は、従来の上部ゲートをもたない。電解質25がゲート表面材料24を囲み、上部ゲートとして働く。フィン22及びゲート誘電体23は、FET20のバックゲートであるシリコン層27の上に配置された埋め込み酸化物(BOX)層26の上に配置される。

【0018】

FET20のドレイン電流は、閾値以下(sub-threshold)領域で動作される。生体分子21を検知するために、生体分子21はゲート表面材料24に結合し、電荷をゲート誘電体23に移送する。ゲート誘電体23における電荷はドレイン電流に影響を与え、このことは、FET20のドレイン・ソース間電圧に影響を与える。測定されたドレイン・ソース間電圧が、VSENSEである。各々の異なる生体分子21は、一般に、固有の電荷を有するため、VSENSEの測定値を用いて、検出された特定の生体分子21を同定することができる。

【0019】

生体分子21を検知するためにFET20を用いる利点は、FET20が、生体分子21の電荷に対して高い感度をもつことである。高感度は、小さい閾値以下勾配の結果としてもたらされ、ゲート電圧の小さな変化がドレイン電流の大きい変化を引き起こし、ドレイン・ソース間電圧(すなわちVSENSE)の大きな変化をもたらす。非finFETと比較すると、finFETにおけるゲート誘電体23の大きな表面積は、応答時間の改善をもたらす。FET20として用いられるfinFETは、ゲート誘電体23の表面積をさらに増大させるために、単一のフィン又はフィンのアレイを有することができる。

【0020】

図2の実施形態はfinFETを示すが、他のタイプのFETを用いて、生体分子21を検出することもできる。FET20は、一般に、相補型金属酸化膜半導体(CMOS)技術を用いて実装される。

【0021】

ここで図3を参照されたい。図3は、反転利得増幅器回路30の概略図を示す。反転利得増幅器回路30は、生体分子21を検知するためのセンサとしてのFET20を含む。図3の実施形態において、FET20は、n型FETであり、FET N1と示される。FET N1は、p型FET、すなわちFET P1と直列に結合される。つまり、FET N1のドレインはFET P1のドレインに結合され、FET P1のソースは、電圧VDD1を供給する、VDD1と示される電源に結合される。FET N1及びFET P1は共に反転利得増幅器回路30を形成する。さらに、別のn型FET、すなわちFET N2は、生体分子21の検出された電荷に関連する、FET N1の出力Vxを、VSENSEライン31に伝える。VSENSEライン31において読み取られた電圧は、VSENSEと呼ばれる。図3の実施形態において、VSENSEライン31は、センサ・セル10の外にある。FET N2は、行選択回路11から「行選択」信号(すなわち、row_sel)を受け取るように構成されているので、FET N2のゲートに通電されると(すなわち、VDD1に設定されると)、出力電圧VxがVSENSEライン31に結合される。FET N2が「オン」であるとき、VSENSEは、概ねVxと同じになる。

【0022】

ここで図4を参照されたい。図4は、反転利得増幅器回路30の反転利得特性の態様を示す。増幅器回路30の出力が、FET N1のゲート電圧VGNに対してグラフ化される。検知FET N1は、閾値以下領域で動作するようにバイアスがかけられ、0<VGN<VT,N1となる。p型FET P1は、VGP≦VDD1−VT,P1となるように動作するようにバイアスがかけられ、ここで、VT,P1はP型FET P1の閾値である。FET N1のゲート電圧VGNが増大する場合、電圧Vxは、図4における曲線の動作領域の勾配に応じて低減する。同様に、FET N1のゲート電圧VGNが低減する場合、電圧Vxは、その曲線の動作領域の勾配に応じて。FET N1の感度が高いために、一般に、VGNの小さな変化は、Vxの大きな変化をもたらす。

【0023】

ここで図5を参照されたい。図5は、VxをVSENSEラインに結合するコンポーネントにおいて低抵抗を有するように構成された回路を有するセンサ・セル10の態様を示す。図5の回路において、p型FET、FET P2が、FET N2に対して並列配置され、FET N2のゲートが、行選択信号の補数に結合される。この構成により、広範囲のVxの値がVSENSEラインに伝えられる。しかしながら、この構成はまた、読み取りのために選択されていないセンサ・セル10における漏れも増大させることが留意される。

【0024】

選択されていないセンサ・セル10において、VDD1と接地GNDとの間に電流路がある。これにより、読み取りのためにセル10にアクセスされていなかったとしても、センサ・セル10による電力消費がもたらされ得る。この電力消費を克服する技術の3つの例が、図6、図7、及び図8を参照して本明細書に開示される。

【0025】

ここで図6を参照されたい。図6は、読み取りのために選択されていないセンサ・セル10内のFET P1をオフにするように構成された回路の態様を示す。図6の回路は、VDD1と、アレイの行における全てのFET P1のゲートとの間に配置されたp型FET、すなわちFET P8を含む。さらに、n型FET N9及びp型FET P9が並列接続され、それらのドレインがつなぎ合わされ、VGPに接続され、それらのソースは、アレイの行における全てのFET P1のゲートに接続される。FET P8及びFET N9のゲートは、行イネーブル信号「row_sel」に接続される。FET P9のゲートは、「row_sel」信号の補数に接続される。この回路は、行内の全てのセンサ・セル10に共通である。行内の全てのセンサ・セル10は、共通のVGPを有する。選択されていないセンサ・セル10において、行選択は「0」となり、従って、FET P8はオンとなり、行内の全てのFET P1のゲートをVDD1に接続する。従って、全ての選択されていないセンサ・セル10においては、FET P1はオフにされ、VDD1からGNDへの経路を流れる電流を停止させる。選択された行において、FET P8はオフとなり、FET P9及びFET N9はオンとなり、行内の全てのFET P1のゲートがVGPに接続される。

【0026】

ここで図7を参照されたい。図7は、FET P1と直列配置された、すなわち電源VDD1とFET P1のソースとの間に配置されたp型FET、すなわちFET P3を有する回路の態様を示す。行が選択されていないとき、すなわち行選択信号が低いとき、FET P3はオフにされ、従って、VDD1からGNDへの経路を流れる電流が停止される。

【0027】

ここで図8を参照されたい。図8は、FET N1と直列配置された、すなわちFETN1のソースと接地GNDとの間に配置されたn型FET、すなわちFET N3を有する回路の態様を示す。行が選択されていないとき、すなわち行選択信号が低いとき、FET N3はオフにされ、従って、VDD1からGNDへの経路を流れる電流が停止される。

【0028】

図1を参照すると、幾つかのセンサ・セル10を共通のVSENSEラインに接続し、非常に長い、従って、比較的大きい抵抗及びキャパシタンスを有するVSENSEラインをもたらすことができる。任意の所与の時点において、他の選択されていないセンサ・セル10におけるFET N2(図3、図5、図7及び図8に示される)がオフである間、1つの選択されたセンサ・セル10だけが、VSENSEラインに伝送された測定値を有することができる。FET N1及びFET P1は、閾値以下領域で動作し、深飽和状態(deep saturation)(VGN=VDD1及びVGP=0であるときに生じる)で動作しないので、FET N1及びFET P1を通る電流は非常に低いものである。従って、VX信号を、FET N1及びFET P1を通してVSENSEラインに接続する接続ラインの充電及び/又は放電が、VX信号への著しい雑音の一因となり得る。さらに、充電及び/又は放電は、VSENSEラインに伝送されたVX信号を安定化させるのにかかる時間量を増大させ得る。雑音を防止し、安定化時間を低減させるために、接続ライン内に配置された増幅及び減結合回路が開示される。

【0029】

ここで図9を参照されたい。図9は、VSENSEラインからのVX信号を減結合し、同じく、VX信号がVSENSEラインに伝送される前に、VX信号をΔVGNの範囲に線形増幅する増幅及び減結合回路90の態様を示す。増幅及び減結合回路90は、n型FET、すなわちFET N4及びFET N5と、p型FET、すなわちFET P4及びFET P5とを含む。FET N4、FET N5、FET P4及びFET P5は、図9に示されるように、(1)VX信号をもたらす反転利得増幅器回路30におけるノードと(2)VSENSEラインとの間に構成される。FET N4及びFET P4は、入力としてVX信号を、出力としてVSENSEを有するインバータ構成であることが留意される。FET N5及びFET P5は、フィードバック・トランジスタである。別の実施形態において、独立したバックゲート制御を有するfinFETのようなマルチゲートFETを、単一ゲートFETの代わりに用いて、増幅及び減結合回路90を作製することができる。FET N4及びFET N5は、バックゲートとしてFET N5を有する単一のマルチゲートFETと置き換えることができる。同様に、FET P4及びFET P5は、バックゲートとしてFET P5を有する単一のマルチゲートFETと置き換えることもできる。図9に示されるように、増幅及び減結合回路90は、VSENSEについての所望の電圧範囲を達成するように、別個の電源VDD2(電圧VDD2を有する)に結合される。

【0030】

反転利得増幅器回路30は、VGNの変化に起因するVXの変化に基づいている。VGNの変化に起因するVXの変化は、ΔVX/ΔVGNが所定の範囲のΔVGNにおける定関数である場合、決定論的に相関し得る。FEN N1及びFET P1は反転利得回路を形成するので、利得は、バイアス点の近くで、すなわち図4に示されるようなVGNの選択された値において、非常に高くなる。VGNの増幅は有益であるが、低い値又は高い値のVGNにおけるVXの飽和のために、増幅がΔVGNの値の範囲を制限することがある。ΔVGNの値の全範囲においてΔVXとΔVGNとの間に相関を有することが好ましい。

【0031】

ここで図10を参照されたい。図10は、VSENSE及びVX対VGNのプロットを示す。線形化回路は、バイアス点から広範囲のΔVGNにおけるVSENSEとVGNとの間の線形相関をもたらすことが留意される。図10はまた、フィードバックFET N5及びFET P5を有する及びこれらを有さないVSENSEのプロットも示す。フィードバックがない場合、反転利得増幅器回路30の出力は、非常に高い増幅を有し、そのため、VGNのわずかな変化に対して大きなVSENSEの変化が生じる可能性がある。従って、VSENSEは、VGNの大きな変化に対して飽和することがある。この飽和の可能性により、VGNの動作領域が制限され、従って、生体分子21の電荷の大きな変化を検出することに起因する、VGNの大きな変化を検出するために、フィードバックが必要となる。

【0032】

増幅及び減結合回路90における電力消費を低減させるために、図9に示されるように、電源VDD2とGNDとの間の電流路を遮断することができる。図11は、p型FET、すなわちFET P6を、電源VDD2とFET P4及びP5のソースとの間に配置することによって電流路を遮断するための実施形態を示す。図12は、n型FET、すなわちFET N6を、FET N4及びFET N5のソースと接地との間に配置することにより電流路を遮断するための別の実施形態を示す。

【0033】

電流遮断回路を含むことができる増幅及び減結合回路90は、各々のセンサ・セル10内に実装することができ、又は代替的に、回路90を列内のセンサ・セル10と共有することによって実装することもできる。共有する実施形態においては、増幅及び減結合回路90は、VSENSEラインと図1に示される列多重化回路12との間に結合され、各々のセンサ・セル10が必要とする面積を低減させる。

【0034】

次に、製造関連のばらつきを緩和するためのセンサ較正について説明する。センサ・セル10のアレイを製造するために用いられる半導体チップにおける製造の不完全性のために、生体検知セル10内のFETが、所望のゲート長、幅、閾値電圧等をもたないことがある。従って、ΔVGNへのVSENSEの製造前較正(pre-fabrication calibration)が正確でないことがある。そこで、各センサ・セル10の製造後較正(post-fabrication calibration)が開示される。製造後較正は、次の方法で達成することができる。第1に、製造前の分析に基づいてVGNを選択する。第2に、製造されたチップにおいて、VGNを印加し、各々のセンサ・セル10についてVSENSE(V0SENSEと呼ばれる)を測定する。この較正測定において、生体分子21が存在しないことが留意される。V0SENSEは、デジタル信号に変換されたアナログ電圧信号であり、これはチップの上に統合された又は外部接続の従来の半導体メモリ内に格納することができる。各々のセンサ・セル10についての格納されたV0SENSEのデジタル値は、そのセンサ・セル10が行う将来の測定のための基準点として働く。第3に、実際の検知用途において、測定されたVSENSEのデジタル値は、オリジナルのV0SENSEの格納値を参照する。この較正技術は、ハードウェアのどのような変更も必要としない。従って、迅速な較正、すなわちV0SENSEの測定後、同じハードウェアを、異なる種類の生体分子21に繰り返し使用することができる。

【0035】

次に、異なるバイアス点(VGN)を必要とし得る様々な生体分子21を試験するためのセンサ調整について説明する。検知FET N1の動作範囲は、バイアス点VGNの選択によって決まる。FET N1のゲートに結合している間、生体分子21は、VGNによる如何なる抵抗も受けるべきではない。異なる生体分子21が、異なるバイアス点、すなわちVGN値を必要とする場合、類似の±ΔVGN値を定めることができる。このことは、FET N1及びFET N1P1の閾値電圧VTを動的に制御することによって達成することができる。図13は、FET N1及びFET P1のVTの変化に伴うバイアス点VGNの移動を示す。このΔVT,N1,P1は、基板コンタクトを有するFET N1及びFET P1(すなわち、単一ゲートFET)の基板バイアスを変えることによって達成することができる。finFETのようなマルチゲートFETにおいては、これらのFETのバックゲート(又は第2のゲート)における電圧バイアスを制御することによって、VTを動的に変更することができる。

【0036】

図14は、関連した電荷を有する生体分子21を同定するための方法140の一例を示す。方法140は、FET20のゲート誘電体23により生体分子21の電荷を検知すること(ステップ141)を必要とする。FET20及び別のFETは、反転利得増幅器回路30を形成するように構成される。さらに、方法140は、反転利得増幅器回路によりゲートにおける電荷を測定して、生体分子21を同定すること(ステップ142)を必要とする。

【0037】

方法140及び上述の議論は、生体分子21の同定に関するものであるが、ゲート誘電体23に付着し得る電荷を有するいずれの材料を同定することもできる。一般に、各々の試験生体分子21/試験材料と関連付けられた基準電荷を定めるために、異なる生体分子21及び異なる電荷を有する材料の試験及び/又は分析が用いられる。このように、測定された電荷を基準電荷と比較することにより、生体分子21/材料を同定することができる。

【0038】

1つの実施形態においては、センサ10のアレイを1つのCMOSデバイス又は半導体「チップ」に組み込み、製造コストを下げ、信頼性を向上させることができる。さらに、行選択回路11、列多重化回路12、及びADC13のような、センサ10のアレイと共に用いられる他のコンポーネントを同じCMOSデバイスに組み込むこともできる。

【0039】

本発明の能力は、ソフトウェア、ファームウェア、ハードウェア、又はこれらの何らかの組み合わせの形で実装することができる。

【0040】

一例として、本発明の1つ又は複数の態様を、例えば、コンピュータ使用可能媒体を有する製品(例えば、1つ又は複数のコンピュータ・プログラム製品)内に含ませることができる。この媒体は、例えば、本発明の能力を提供し、助長するためのコンピュータ可読プログラム・コード手段を内部に組み入れている。この製品は、コンピュータ・システムの一部として含ませることができ、又は別個に販売することができる。

【0041】

さらに、本発明の能力を実施するように機械により実行可能な命令の少なくとも1つのプログラムを明確に具体化する、機械により読み取り可能な、少なくとも1つのプログラム・ストレージ・デバイスを提供することができる。

【0042】

本明細書での教示を支援して、デジタル及び/又はアナログ・システムを含む、種々の分析用コンポーネントを用いることができる。システムは、プロセッサ、ストレージ媒体、メモリ、入力、出力、通信リンク、ユーザ・インターフェース(プリンタ又はディスプレイのような)、ソフトウェア・プログラム、信号プロセッサ(デジタル又はアナログ)のようなコンポーネント、並びに当技術分野においてよく理解される幾つかの方法のいずれかで、本明細書に開示される装置及び方法の動作及び分析を提供する他のそうしたコンポーネント(レジスタ、キャパシタ、インダクタ及び他のもの)を有することができる。これらの教示は、必ずしもではないが、実行時にコンピュータに本発明の方法を実施させる、メモリ(ROM、RAM)、光学(CD−ROM)、又は磁気(ディスク、ハードドライブ)、或いはいずれかの他のタイプを含むコンピュータ可読媒体上に格納された一組のコンピュータ実行可能命令と併せて実装できると考えられる。これらの命令は、本開示において説明される機能に加えて、機器の動作、制御、データ収集、及び分析、並びにシステム設計者、所有者、ユーザ又は他のそのような人員が関連すると考える他の機能を提供することができる。

【0043】

本明細書で示されるフロー図は、例にすぎない。本発明の思想から逸脱することなく、本明細書で説明されるこれらの図又はステップ(若しくは動作)に対して多くの変形があり得る。例えば、ステップを異なる順番で行ってもよく、或いは、ステップを付加、削除又は変更してもよい。これらの変形の全ては、特許請求される本発明の一部と考えられる。

【0044】

実施形態の要素は、冠詞「1つ(a)」又は「1つ(an)」を用いて導入されている。この冠詞は、1つ又は複数の要素があることを意味するように意図される。「含む(including)」及び「有する(having)」という用語は、列挙された要素以外の付加的な要素があり得るように、包括的であることが意図される。接続詞「又は(or)」は、少なくとも2つの用語のリストと共に用いられるとき、いずれかの用語又は用語の組み合わせを意味するように意図される。「第1」、「第2」「第3」等という用語は、要素を区別するために用いられ、特定の順番を示すために用いられるものではない。「結合する(couple)」という用語は、別のコンポーネントに直接結合される、或いは1つ又は複数の中間コンポーネントを介して別のコンポーネントに間接的に結合される1つのコンポーネントに関する。

【0045】

好ましい実施形態を参照して本発明を説明してきたが、当業者であれば、本発明の範囲を逸脱することなく、種々の変更を行うことができること、及び、均等物をその要素と置き換えることができることを理解するであろう。さらに、本発明の本質的な範囲から逸脱することなく、特定の状態又は材料を本発明の教示に適合させるように、多くの修正を行うことができる。従って、本発明は、本発明を実行するために考えられる最良の形態として開示される特定の実施形態に限定されるものではなく、本発明は、添付の特許請求の範囲内に入る全ての実施形態を含むことが意図される。

【符号の説明】

【0046】

10:センサ・セル

11:行選択回路

12:列多重化回路

13:アナログ・デジタル変換器(ADC)

20:電界効果トランジスタ(FET)

21:生体分子

22:フィン

23:ゲート誘電体

24:ゲート表面材料

25:電解質

26:埋め込み酸化物(BOX)層

27:シリコン層

30:反転利得増幅器回路

31:VSENSEライン

90:増幅及び減結合回路

【特許請求の範囲】

【請求項1】

電荷を有する材料を同定するように構成された装置であって、前記装置は、

第2の電界効果トランジスタ(FET)に結合された第1のFETを含む反転利得増幅器を含み、

前記第1のFETのゲートは前記電荷を検知するように構成され、前記増幅器の出力は、前記材料を同定するための前記電荷の測定値をもたらす、装置。

【請求項2】

前記材料は生体分子である、請求項1に記載の装置。

【請求項3】

前記第1のFETはn型FETであり、前記第2のFETはp型FETである、請求項1に記載の装置。

【請求項4】

前記第1のFETには、前記第1のFETの電圧閾値を下回るバイアスがかけられる、請求項3に記載の装置。

【請求項5】

前記第1のFETのドレインは、ノードにおいて前記第2のFETのドレインに結合され、前記ノードにおける電圧が前記出力を与える、請求項3に記載の装置。

【請求項6】

前記第2のFETのソースは、第1の電源に結合される、請求項5に記載の装置。

【請求項7】

前記第2のFETのゲートと前記第1の電源との間に配置され、かつ、前記第2のFETをオフにするように構成された第3のFETをさらに含む、請求項6に記載の装置。

【請求項8】

前記出力は、前記出力を受け取るように構成された検知ラインに与えられる、請求項6に記載の装置。

【請求項9】

前記ノードと前記検知ラインとの間に配置され、かつ、前記ノードに結合されたドレインと、前記検知ラインに結合されたソースとを有する、第3のn型FETをさらに含み、前記第3のFETは、選択回路からの信号を受け取り、前記出力を前記検知ラインに送るのを可能にするように構成される、請求項8に記載の装置。

【請求項10】

前記ノードと前記検知ラインとの間に配置され、かつ、前記ノードに結合されたドレインと、前記検知ラインに結合されたソースとを有する、第4のp型FETをさらに含み、前記第4のFETは、前記選択回路からの前記信号を受け取り、前記出力を前記検知ラインに送るのを可能にするように構成される、請求項9に記載の装置。

【請求項11】

前記ノードと、前記第3のFET及び前記第4のFETの前記ドレインとの間に配置された増幅及び減結合回路をさらに含む、請求項10に記載の装置。

【請求項12】

前記増幅及び減結合回路は、

各々が、前記第1のノードに結合されたゲート及び第2のノードに結合されたドレインを有する、第5のn型FET及び第6のp型FETと、

各々が、前記第2のノードに結合されたゲート及びドレインを有する、第7のn型FET及び第8のp型FETと、

を含み、

前記第2のノードは、前記第3のFET及び前記第4のFETの前記ドレインに結合される、請求項11に記載の装置。

【請求項13】

前記第6のFETのソース及び前記第8のFETのソースは、第2の電源に結合される、請求項12に記載の装置。

【請求項14】

センサ・セルのアレイをさらに含み、各々のセンサ・セルは、前記材料を同定するように構成され、かつ、前記反転利得増幅器を含む、請求項1に記載の装置。

【請求項15】

前記センサ・セルのアレイは、1つのCMOSデバイスに組み込まれる、請求項14に記載の装置。

【請求項16】

行選択回路と、前記アレイ内の各センサ・セルから前記電荷の前記測定値を取得するように構成された列多重化回路とをさらに含む、請求項14に記載の装置。

【請求項17】

前記第1のFETは、finFET及び金属酸化膜半導体(MOSFET)からなる群から選択されたものである、請求項1に記載の装置。

【請求項18】

電荷を有する材料を同定する方法であって、前記方法は、

第1の電界効果トランジスタ(FET)のゲートにより前記電荷を検知することであって、前記第1のFET及び第2のFETは、前記電荷の測定値を与える出力を有する反転利得増幅器回路を形成する、当該検知することと、

前記反転利得増幅器回路により前記電荷を測定して前記材料を同定することと、

を含む方法。

【請求項19】

前記測定することは、前記測定された電荷を基準材料の電荷と比較して、前記材料を同定することを含む、請求項18に記載の方法。

【請求項20】

前記ゲートにおける電荷なしで、前記第1のFETを較正して、較正の基準をもたらすことをさらに含む、請求項18に記載の方法。

【請求項21】

各々が前記反転利得増幅器回路を含むセンサ・セルのアレイにより前記電荷を測定することをさらに含む、請求項18に記載の方法。

【請求項22】

第1の電界効果トランジスタ(FET)のゲートにより電荷を検知することであって、前記第1のFET及び第2のFETは、前記電荷の測定値を与える出力を有する反転利得増幅器回路を形成する、当該検知することと、

前記反転利得増幅器回路により前記電荷を測定して材料を同定することと、

前記測定値を格納すること、前記測定値を分析すること、及び前記測定値をユーザに提示することの少なくとも1つと、

を含む方法を実施することによって、電荷を有する材料を同定するための機械実行可能命令を含む、非一時的機械可読媒体。

【請求項1】

電荷を有する材料を同定するように構成された装置であって、前記装置は、

第2の電界効果トランジスタ(FET)に結合された第1のFETを含む反転利得増幅器を含み、

前記第1のFETのゲートは前記電荷を検知するように構成され、前記増幅器の出力は、前記材料を同定するための前記電荷の測定値をもたらす、装置。

【請求項2】

前記材料は生体分子である、請求項1に記載の装置。

【請求項3】

前記第1のFETはn型FETであり、前記第2のFETはp型FETである、請求項1に記載の装置。

【請求項4】

前記第1のFETには、前記第1のFETの電圧閾値を下回るバイアスがかけられる、請求項3に記載の装置。

【請求項5】

前記第1のFETのドレインは、ノードにおいて前記第2のFETのドレインに結合され、前記ノードにおける電圧が前記出力を与える、請求項3に記載の装置。

【請求項6】

前記第2のFETのソースは、第1の電源に結合される、請求項5に記載の装置。

【請求項7】

前記第2のFETのゲートと前記第1の電源との間に配置され、かつ、前記第2のFETをオフにするように構成された第3のFETをさらに含む、請求項6に記載の装置。

【請求項8】

前記出力は、前記出力を受け取るように構成された検知ラインに与えられる、請求項6に記載の装置。

【請求項9】

前記ノードと前記検知ラインとの間に配置され、かつ、前記ノードに結合されたドレインと、前記検知ラインに結合されたソースとを有する、第3のn型FETをさらに含み、前記第3のFETは、選択回路からの信号を受け取り、前記出力を前記検知ラインに送るのを可能にするように構成される、請求項8に記載の装置。

【請求項10】

前記ノードと前記検知ラインとの間に配置され、かつ、前記ノードに結合されたドレインと、前記検知ラインに結合されたソースとを有する、第4のp型FETをさらに含み、前記第4のFETは、前記選択回路からの前記信号を受け取り、前記出力を前記検知ラインに送るのを可能にするように構成される、請求項9に記載の装置。

【請求項11】

前記ノードと、前記第3のFET及び前記第4のFETの前記ドレインとの間に配置された増幅及び減結合回路をさらに含む、請求項10に記載の装置。

【請求項12】

前記増幅及び減結合回路は、

各々が、前記第1のノードに結合されたゲート及び第2のノードに結合されたドレインを有する、第5のn型FET及び第6のp型FETと、

各々が、前記第2のノードに結合されたゲート及びドレインを有する、第7のn型FET及び第8のp型FETと、

を含み、

前記第2のノードは、前記第3のFET及び前記第4のFETの前記ドレインに結合される、請求項11に記載の装置。

【請求項13】

前記第6のFETのソース及び前記第8のFETのソースは、第2の電源に結合される、請求項12に記載の装置。

【請求項14】

センサ・セルのアレイをさらに含み、各々のセンサ・セルは、前記材料を同定するように構成され、かつ、前記反転利得増幅器を含む、請求項1に記載の装置。

【請求項15】

前記センサ・セルのアレイは、1つのCMOSデバイスに組み込まれる、請求項14に記載の装置。

【請求項16】

行選択回路と、前記アレイ内の各センサ・セルから前記電荷の前記測定値を取得するように構成された列多重化回路とをさらに含む、請求項14に記載の装置。

【請求項17】

前記第1のFETは、finFET及び金属酸化膜半導体(MOSFET)からなる群から選択されたものである、請求項1に記載の装置。

【請求項18】

電荷を有する材料を同定する方法であって、前記方法は、

第1の電界効果トランジスタ(FET)のゲートにより前記電荷を検知することであって、前記第1のFET及び第2のFETは、前記電荷の測定値を与える出力を有する反転利得増幅器回路を形成する、当該検知することと、

前記反転利得増幅器回路により前記電荷を測定して前記材料を同定することと、

を含む方法。

【請求項19】

前記測定することは、前記測定された電荷を基準材料の電荷と比較して、前記材料を同定することを含む、請求項18に記載の方法。

【請求項20】

前記ゲートにおける電荷なしで、前記第1のFETを較正して、較正の基準をもたらすことをさらに含む、請求項18に記載の方法。

【請求項21】

各々が前記反転利得増幅器回路を含むセンサ・セルのアレイにより前記電荷を測定することをさらに含む、請求項18に記載の方法。

【請求項22】

第1の電界効果トランジスタ(FET)のゲートにより電荷を検知することであって、前記第1のFET及び第2のFETは、前記電荷の測定値を与える出力を有する反転利得増幅器回路を形成する、当該検知することと、

前記反転利得増幅器回路により前記電荷を測定して材料を同定することと、

前記測定値を格納すること、前記測定値を分析すること、及び前記測定値をユーザに提示することの少なくとも1つと、

を含む方法を実施することによって、電荷を有する材料を同定するための機械実行可能命令を含む、非一時的機械可読媒体。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公表番号】特表2013−516613(P2013−516613A)

【公表日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2012−547326(P2012−547326)

【出願日】平成23年1月3日(2011.1.3)

【国際出願番号】PCT/US2011/020007

【国際公開番号】WO2011/082395

【国際公開日】平成23年7月7日(2011.7.7)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【Fターム(参考)】

【公表日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年1月3日(2011.1.3)

【国際出願番号】PCT/US2011/020007

【国際公開番号】WO2011/082395

【国際公開日】平成23年7月7日(2011.7.7)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【Fターム(参考)】

[ Back to top ]