超音波トランスデューサの製造方法

【課題】下部電極を各素子に分割することで段差が生じても、上部電極の抵抗上昇、メンブレンへのダメージおよび上部電極と下部電極間の絶縁耐性低下を低減する技術を提供する。

【解決手段】複数の下部電極203と、下部電極を覆う絶縁膜204と、絶縁膜204上に下部電極203と重なるように形成された複数の空洞部205と、空洞部205の間を埋める絶縁膜3401と、空洞部205および絶縁膜3401を覆う絶縁膜206と、絶縁膜206上に空洞部205と重なるように形成された複数の上部電極207とそれらを結ぶ複数の配線208を備えた超音波トランスデューサにおいて、空洞部205と絶縁膜3401の表面が同じ高さに平坦化されている。

【解決手段】複数の下部電極203と、下部電極を覆う絶縁膜204と、絶縁膜204上に下部電極203と重なるように形成された複数の空洞部205と、空洞部205の間を埋める絶縁膜3401と、空洞部205および絶縁膜3401を覆う絶縁膜206と、絶縁膜206上に空洞部205と重なるように形成された複数の上部電極207とそれらを結ぶ複数の配線208を備えた超音波トランスデューサにおいて、空洞部205と絶縁膜3401の表面が同じ高さに平坦化されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、超音波トランスデューサおよびその製造方法に関するものである。特に、MEMS(Micro Electro Mechanical System)技術により製造した超音波トランスデューサと、その最適な製造方法に関する。

【背景技術】

【0002】

超音波トランスデューサは超音波を送信、受信することにより、人体内の腫瘍などの診断装置に用いられている。

【0003】

これまでは、圧電体の振動を利用した超音波トランスデューサが用いられてきたが、近年のMEMS技術の進歩により、電極の間に空洞部を挟みこんだ構造による振動部をシリコン基板上に作製した容量検出型超音波トランスデューサ(CMUT:Capacitive Micromachined Ultrasonic Transducer)が実用化を目指して盛んに開発されている。

【0004】

例えば、米国特許第6320239B1号明細書(特許文献1)には、シリコン基板を下部電極に用いたCMUT開示されている。

【0005】

また、米国特許第6271620B1号明細書(特許文献2)および2003 IEEE ULTRASONICS SYMPOSIUM、p577−p580(非特許文献1)には、パターニングされた下部電極上に形成した構造のCMUTが開示されている。

【0006】

また、米国特許第6571445B2号明細書(特許文献3)および米国特許第6562650B2号明細書(特許文献4)には、シリコン基板上に形成した信号処理回路の上層にCMUTを形成する技術が開示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第6320239B1号明細書

【特許文献2】米国特許第6271620B1号明細書

【特許文献3】米国特許第6571445B2号明細書

【特許文献4】米国特許第6562650B2号明細書

【非特許文献】

【0008】

【非特許文献1】2003 IEEE ULTRASONICS SYMPOSIUM、p577−p580

【発明の概要】

【発明が解決しようとする課題】

【0009】

ところで、CMUTは、従来の圧電体を用いたトランスデューサと比較して、使用できる超音波の周波数帯域が広い、あるいは高感度であるなどの利点がある。またLSI加工技術を用いて作製するので微細加工が可能である。特に、素子をアレイ状に配置して、素子の上部電極と下部電極を直交配置し、そのクロスポイントの素子を独立に制御する場合や、素子を完全に独立して制御する場合には、CMUTは必須となると考えられる。何故ならば、各素子への配線が必要になり、アレイ内の配線数は膨大な数になることが考えられるが、LSI加工技術を用いて作製できるので、微細な配線が可能であり、さらには超音波送受信部からの信号処理回路の1チップへの混載も、CMUTでは可能だからである。

【0010】

図1、図2を用いてCMUTアレイの基本的な構造および動作を説明する。

【0011】

図1はCMUTアレイの上面図である。203は下部電極、205は空洞部、207は上部電極、208は上部電極を結ぶ配線、210は空洞部205を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔210は、空洞部205に接続されている。101は、上部電極207へ電源供給するために下部電極と同層に設けたパッドへのパッド開口部であり、102はパッドと配線208を接続するプラグである。すなわち、プラグ102を介して上部電極207を結ぶ配線208とパッドが接続されている。103は下部電極203に電源供給するためのパッド開口部である。上部電極207および配線208と、下部電極203の間に、下部電極203および空洞部205を覆うように絶縁膜が形成されているが、空洞部205、下部電極203を示すために図示していない。

【0012】

図2(a)は、図1のA−A’方向の断面を示しており、図2(b)は図1のB−B’方向の断面を示している。図2(a)および図2(b)に示すように、半導体基板201に形成された絶縁膜202上に下部電極203が形成されている。下部電極203の上層には絶縁膜204を介して空洞部205が形成されている。空洞部205を覆うように絶縁膜206が形成され、絶縁膜206の上層に上部電極207と上部電極を結ぶ配線208が形成されている。上部電極207および配線208の上層には絶縁膜209と絶縁膜211が形成されている。また、絶縁膜206および絶縁膜209にはこれらの膜を貫通するウェットエッチング孔210が形成されている。このウェットエッチング孔210は、空洞部205を形成するために形成されたものであり、空洞部205の形成後、絶縁膜211によって埋め込まれている。

【0013】

図1および図2から明らかであるが、上部電極と下部電極が直交するために、上部電極を結ぶ配線は下部電極による段差部を乗り越える構造となる。

【0014】

以下に、超音波を発信する動作について説明する。上部電極207へ接続するパッド開口部101と、下部電極203へのパッド開口部103へ直流電圧と交流電圧を重畳すると、上部電極207と下部電極203の間に静電気力が働き、上部電極と下部電極が交わるクロスポイントのCMUTセルのメンブレンを構成する空洞部205上の上部電極207および絶縁膜206、209、211が印加した交流電圧の周波数で振動し、超音波を発信する。

【0015】

逆に、超音波を受信する場合は、デバイスの表面に到達した超音波の圧力により、空洞部205上の絶縁膜206、209、211および上部電極207が振動する。この振動により、上部電極207と下部電極203との間の距離が変化するため、電極間の電気容量の変化として超音波を検出できる。すなわち、電極間の距離が変化することにより、電極間の電気容量が変わり、電流が流れる。この電流を検知することにより超音波を検出することができる。

【0016】

上記動作原理からも明らかであるが、電極間の電圧印加に起因する静電力によるメンブレンの振動と、振動による電極間の電気容量変化を利用して超音波の発信および受信を行うので、電極間の電圧差の安定性、電極間距離やメンブレンの厚さの安定性が、デバイスの安定した動作や信頼性確保には重要な点となる。

【0017】

特許文献1では、下部電極としてイオン注入を行ったシリコン基板を用いたCMUTアレイが開示されている。しかし、この構造ではシリコン基板の抵抗が大きいために、CMUTアレイ内部での下部電極の電圧降下を抑制するためには、外部からの駆動電源供給をCMUTの直近に行う必要があり、アレイ状にCMUTを多数配置した場合、電源供給箇所も多数必要となる。

【0018】

特許文献2、3、4および非特許文献1には、CMUTアレイの下部電極に金属膜を使用する構造が示されている。特許文献2、3および4では、アルミニウム(Al)やタングステン(W)、銅(Cu)といった材料を用いた厚さ250nmから500nmの下部電極の例が開示され、非特許文献1ではクロムを材料にした厚さ150nmの下部電極の例が示されている。しかし、上記に示した金属膜を用いた下部電極であっても、CMUTアレイ内部での電圧降下を抑制するためには、500nm以上の厚さの下部電極が必須である。

【0019】

したがって、下部電極を各素子に分割することによる500nm以上の下部電極の段差が必然的に生じることになる。この段差を上部電極を結ぶ配線が乗り越える構造になるが、配線となる金属膜を形成する際に、段差部での金属膜のカバレッジが平坦部より低下し、段差部での金属膜の膜厚が薄くなってしまう。その結果、上部電極の抵抗上昇の原因となる。また、上部電極パターンを加工する際には、段差部の余分な金属膜を除去するために過剰なエッチングを行う必要があり、金属膜の下地膜が削れてしまうなどのダメージは入ってしまう。このことは、CMUTセルのメンブレンを構成する膜が薄くなることを意味し、CMUTセルの周波数特性変動の原因となる。さらに、下部電極と上部電極を絶縁する絶縁膜のカバレッジも、段差部では平坦部よりも低下するので、段差部での絶縁膜の厚さが薄くなることで絶縁耐性も低下し、デバイスの信頼性が低下する。

【0020】

また、空洞部による段差も上部電極を結ぶ配線が乗り越える構造になるので、下部電極による段差部と同様に、デバイス安定性や信頼性の低下に繋がる。特に、メンブレンを大きく振動させて、強い送信音を出す場合は、メンブレンが可動できる範囲を大きく確保する必要があり、したがって、空洞部の厚さを大きくする必要があるので、空洞部による段差の影響も無視できなくなる。

【0021】

そこで、本発明の目的は、下部電極を各素子に分割することによる段差や、空洞部による段差が生じても、上部電極の抵抗上昇、メンブレンへのダメージおよび上部電極と下部電極間の絶縁耐性低下を抑制する構造と製造方法を提供することにある。

【0022】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0023】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0024】

本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部を覆う第2絶縁膜と、(e)前記第2絶縁膜上に前記空洞部と重なるように配置された第2電極と、(f)前記第2電極に接続する配線を備え、前記第1電極の外周部と上面から見て重なる前記配線の幅が、前記第1電極の外周部と上面から見て重ならない前記配線の幅よりも太いことを特徴とするものである。

【0025】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部を覆う第2絶縁膜と、(e)前記第2絶縁膜上に前記空洞部と重なるように配置された第2電極と、(f)前記第2電極に接続する配線を備え、前記第1電極の外周部がテーパ角を持つことにより前記第1電極の段差が緩和されていること特徴とするものである。そして、前記第1電極による段差が500nm以上であること特徴とする。さらに、上面から見て、前記第1電極の外周部と重なる前記配線の幅が、上面から見て、前記第1電極の外周部と重ならない前記配線の幅よりも太いことを特徴とするものである。

【0026】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部を覆う第2絶縁膜と、(e)前記第2絶縁膜上に前記空洞部と重なるように配置された第2電極と、(f)前記第2電極に接続する配線を備え、前記第1電極の外周部に絶縁膜によるサイドウォールを形成することにより前記第1電極の段差が緩和されていること特徴とするものである。そして、前記第1電極による段差が500nm以上であること特徴とする。さらに、上面から見て、前記サイドウォールと重なる前記配線の幅が、上面から見て、前記サイドウォールと重ならない前記配線の幅よりも太いことを特徴とするものである。

【0027】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部を覆う第2絶縁膜と、(e)前記第2絶縁膜上に前記空洞部と重なるように配置された第2電極と、(f)前記第2電極に接続する配線を備え、前記第1電極による段差と前記空洞部による段差の一方あるいは両方が緩和されていることを特徴とするものである。

【0028】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極の間を埋める第1絶縁膜と、(c)前記第1電極および前記第1絶縁膜を覆う第2絶縁膜と、(d)前記第2絶縁膜上に前記第1電極と重なるように配置された空洞部と、(e)前記空洞部を覆う第3絶縁膜と、(f)前記第3絶縁膜上に前記空洞部と重なるように配置された第2電極と、(g)前記第2電極に接続する配線とを備え、前記第1電極と前記第1絶縁膜の表面が同じ高さに平坦化されていることを特徴とするものである。そして、前記第1電極の厚さが500nm以上であること特徴とする。

【0029】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部の間を埋める第2絶縁膜と、(e)前記空洞部および前記第2絶縁膜を覆う第3絶縁膜と、(f)前記第3絶縁膜上に前記空洞部と重なるように配置された第2電極と、(g)前記第2電極に接続する配線とを備え、前記空洞部と前記第2絶縁膜の表面が同じ高さに平坦化されていることを特徴とするものである。

【0030】

本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜を平坦化し、前記第1電極の表面を露出する工程と、(d)前記第1電極および前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(f)前記犠牲層および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(g)前記第3絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(h)前記第2電極に接続する配線を形成する工程と、(i)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(j)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(k)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(l)第5絶縁膜により前記開口部を埋め込み、前記空洞部を封止する工程とを備えることを特徴とするものである。そして、前記第1電極の厚さが500nm以上であること特徴とする。

【0031】

また、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(d)前記犠牲層および前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜を平坦化し、前記犠牲層の表面を露出する工程と、(f)前記第2絶縁膜および前記犠牲層を覆う第3絶縁膜を形成する工程と、(g)前記第3絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(h)前記第2電極に接続する配線を形成する工程と、(i)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(j)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(k)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(l)第5絶縁膜により前記開口部を埋め込み、前記空洞部を封止する工程とを備えることを特徴とするものである。

【0032】

さらに、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(d)前記犠牲層を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(f)前記第2電極に接続する配線を形成する工程と、(g)前記第2電極と前記配線および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(h)前記第2絶縁膜および前記第3絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(i)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(j)第4絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備え、前記配線を形成する工程において、上面から見て、前記第1電極の外周部と重なる前記配線の幅を、上面から見て、前記第1電極の外周部と重ならない前記配線の幅よりも太く形成することを特徴とするものである。

【0033】

また、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(d)前記犠牲層を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記犠牲層と重なる複数の第2電極を形成する工程と、(f)前記第2電極に接続する配線を形成する工程と、(g)前記第2電極と前記配線および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(h)前記第2絶縁膜および前記第3絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(i)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(j)第4絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備え、前記第1電極を形成する工程において、前記第1電極の外周部がテーパ角を持つように形成することを特徴とするものである。そして、前記第1電極の厚さが500nm以上であること特徴とする。さらに、前記配線を形成する工程において、上面から見て、前記第1電極の外周部と重なる前記配線の幅が、上面から見て、前記第1電極の外周部と重ならない前記配線の幅よりも太く形成することを特徴とするものである。

【0034】

また、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜をエッチングし、前記第1電極の外周部にサイドウォールを形成する工程と、(d)前記第1電極および前記サイドウォールを覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記第1電極と重なる犠牲層を形成する工程と、(f)前記犠牲層および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(g)前記第3絶縁膜上に前記犠牲層と重なる複数の第2電極を形成する工程と、(h)前記第2電極に接続する配線を形成する工程と、(i)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(j)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(k)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(l)第5絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備えることを特徴とするものである。そして、前記第1電極の厚さが500nm以上であること特徴とする。さらに、前記配線を形成する工程において、上面から見て前記サイドウォールと重なる前記配線の幅を、上面から見て前記サイドウォールと重ならない前記配線の幅よりも太く形成することを特徴とするものである。

【0035】

また、本発明による超音波トランスデューサの製造方法は、(a)第1絶縁膜をパターニングして第1窪みを形成する工程と、(b)前記第1窪みに第1導電膜を埋め込む工程と、(c)前記第1導電膜を、前記第1絶縁膜の表面が露出するまで平坦化し、前記第1絶縁膜に埋め込まれた第1電極を形成する工程と、(d)前記第1電極および前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(f)前記犠牲層および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(g)前記第3絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(h)前記第2電極に接続する配線を形成する工程と、(i)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(j)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(k)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(l)第5絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備えることを特徴とするものである。そして、前記第1窪みの深さが500nm以上であること特徴とする。

【0036】

また、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(d)前記第2絶縁膜に前記第1絶縁膜に達する複数の第1窪みを形成する工程と、(e)前記第1窪みに犠牲層となる膜を埋め込む工程と、(f)前記犠牲層となる膜を前記第2絶縁膜の表面が露出するまで平坦化し、前記第2絶縁膜に埋め込まれた犠牲層を形成する工程と、(g)前記犠牲層および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(h)前記第3絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(i)前記第2電極に接続する配線を形成する工程と、(j)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(k)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(l)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(m)第5絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備えることを特徴とするものである。

【発明の効果】

【0037】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0038】

下部電極および空洞部の段差を緩和することで、下部電極および空洞部の段差部での上部電極の膜厚低下を低減できるので抵抗の上昇を抑制できる。また、上部電極加工でのメンブレンへのダメージを低減することもできる。さらに、上部電極と下部電極間の絶縁耐性の低下も抑制できる構造と、その製造方法を提供することができる。

【図面の簡単な説明】

【0039】

【図1】本発明者らが検討した超音波トランスデューサの上面図である。

【図2】(a)は図1、図3のA−A’線で切断した断面図であり、(b)は図1、図3のB−B’線で切断した断面図である。

【図3】本発明の実施の形態1における超音波トランスデューサを示した上面図である。

【図4】(a)は図3のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図3のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図5】(a)は図4(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図4(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図6】(a)は図5(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図5(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図7】(a)は図6(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図6(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図8】(a)は図7(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図7(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図9】(a)は図8(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図8(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図10】(a)は図9(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図9(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図11】(a)は図10(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図10(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図12】本発明の実施の形態1における超音波トランスデューサを示した上面図である。

【図13】本発明の実施の形態1における超音波トランスデューサを示した上面図である。

【図14】本発明の実施の形態2における超音波トランスデューサを示した上面図である。

【図15】(a)は図14のA−A’線で切断した断面図であり、(b)は図14のB−B’線で切断した断面図である。

【図16】本発明の実施の形態3における超音波トランスデューサを示した上面図である。

【図17】(a)は図16のA−A’線で切断した断面図であり、(b)は図16のB−B’線で切断した断面図である。

【図18】(a)は図16のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図16のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図19】(a)は図18(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図18(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図20】(a)は図19(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図19(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図21】本発明の実施の形態4における超音波トランスデューサを示した上面図である。

【図22】(a)は図21のA−A’線で切断した断面図であり、(b)は図21のB−B’線で切断した断面図である。

【図23】(a)は図21のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図21のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図24】(a)は図23(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図23(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図25】(a)は図21のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図21のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図26】(a)は図25(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図25(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図27】(a)は図26(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図26(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図28】(a)は図27(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図27(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図29】本発明の実施の形態5における超音波トランスデューサを示した上面図である。

【図30】(a)は図29のA−A’線で切断した断面図であり、(b)は図29のB−B’線で切断した断面図である。

【図31】(a)は図29のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図29のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図32】(a)は図31(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図31(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図33】(a)は図32(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図32(b)に続く超音波トランスデューサの製造工程を示した断面図である。

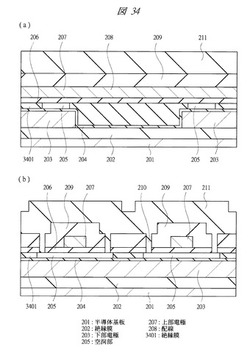

【図34】本発明の実施の形態6における超音波トランスデューサの断面図である。(a)は図1のA−A’線で切断した断面図であり、(b)は図1のB−B’線で切断した断面図である。

【図35】(a)は図34(a)で示した超音波トランスデューサの製造工程を示した断面図であり、(b)は図34(b)で示した超音波トランスデューサの製造工程を示した断面図である。

【図36】(a)は図35(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図35(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図37】(a)は図36(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図36(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図38】本発明の実施の形態7における超音波トランスデューサを示した上面図である。

【図39】(a)は図38のA−A’線で切断した断面図であり、(b)は図38のB−B’線で切断した断面図である。

【図40】本発明の実施の形態8における超音波トランスデューサを示した上面図である。

【図41】(a)は図40のA−A’線で切断した断面図であり、(b)は図40のB−B’線で切断した断面図である。

【図42】本発明の実施の形態9における超音波トランスデューサを示した上面図である。

【図43】(a)は図42のA−A’線で切断した断面図であり、(b)は図42のB−B’線で切断した断面図である。

【発明を実施するための形態】

【0040】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0041】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

【0042】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

【0043】

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうではないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0044】

なお、平面図であっても理解を容易にするため、ハッチングを付す場合がある。

【0045】

下記の実施の形態の記載では、超音波トランスデューサの、上部電極の抵抗上昇の抑制、メンブレンへのダメージ低減、上下電極間の絶縁耐性の低下を抑制するという目的を、段差部での上部電極間を結ぶ配線幅を太くすること、段差部を緩和した構造とすることで実現している。

【0046】

(実施の形態1)

図3は本実施の形態1のCMUTアレイの上面図である。403は下部電極、412は空洞部、407は上部電極、408は上部電極を結ぶ配線、411は空洞部を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔411は、空洞部412に接続されている。301は、上部電極407へ電源供給するために下部電極と同層に設けたパッドへのパッド開口部であり、302はパッドと配線408を接続するプラグである。すなわち、プラグ302を介して上部電極407を結ぶ配線408とパッドが接続されている。303は下部電極403に電源供給するためのパッド開口部である。上部電極407および配線408と、下部電極403の間に、下部電極403および空洞部412を覆うように絶縁膜が形成されているが、空洞部412、下部電極403を示すために図示していない。図3のA−A’断面、B−B’断面はそれぞれ図2(a)、(b)と同様になる。

【0047】

本実施の形態1の特徴は、図3中の409に示すように、下部電極403の段差部での上部電極を結ぶ配線408の配線幅を段差部以外の配線幅よりも太くした点にある。このような構成にすることにより、上部電極407および配線408となる導電膜を堆積する際の段差部で、カバレッジが平坦部より低く、膜厚が薄くなっても、配線の抵抗上昇を抑制できる。すなわち、段差部において、配線409の膜厚が薄くなっても、配線409の配線幅を太くすることで、段差部における配線409の抵抗の上昇を抑制できる。配線408の配線幅に比べて配線409の配線幅は例えば倍程度に太くなっている。具体的には、例えば配線408の配線幅が3μm程度であるとすると、配線409の配線幅は6μm程度になっている。

【0048】

また、段差部のみの配線幅を太くすることで、下部電極403と上部電極を結ぶ配線408の重なり部が大幅に増えることはなく、下部電極403と配線408間の寄生容量の増加も抑制することができる。図3では、配線の太幅化を、対向する下部電極403の段差部間の全てで行っているが、段差部のみを太幅化してもよいことは自明である。特に下部電極403の抵抗を低くするため、下部電極403の厚さを500nm以上にすると、、下部電極403による段差が500nm以上になる。すると、上部電極407および配線408となる導電膜を堆積する際の段差部で、カバレッジが平坦部より低く、膜厚が薄くなることが顕在化する。したがって、本実施の形態1に示すように、下部電極403の段差部に形成される配線409の配線幅を段差部以外の領域に形成される配線408の配線幅より太くする構成は、下部電極403による段差が500nm以上である場合に特に有効である。

【0049】

次に、図面を用いて本実施の形態1に記載されたCMUTアレイの製造方法を説明する。図4〜図11中の(a)は、図3中のA−A’方向の断面を示しており、図4〜図11中の(b)は、図3中のB−B’方向の断面を示している。

【0050】

まず、図4(a)、(b)に示すように、半導体基板401上にプラズマCVD(Chemical Vapor Deposition)法でシリコン酸化膜による絶縁膜402を堆積し、その後、スパッタリング法で窒化チタン膜とアルミニウム合金膜と窒化チタン膜をそれぞれ100nm、600nm、100nm積層する。ここで、半導体基板401と絶縁膜402の間には、信号処理などを行なう集積回路を形成することも可能である。例えば、半導体基板401上にMISFET(Metal Insulator Semiconductor Field Effect Transistor)が形成され、このMISFET上に多層配線が形成される。そして、多層配線上に絶縁膜402が形成される。これらの集積回路は、通常の半導体製造技術を使用して形成される。

【0051】

その後、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極403を形成する。この下部電極403上にプラズマCVD法によりシリコン酸化膜による絶縁膜404を100nm堆積させる。

【0052】

次に、絶縁膜404の上面に多結晶シリコン膜をプラズマCVD法により200nm堆積する。そして、フォトリソグラフィ技術とドライエッチング技術により、下部電極403上に多結晶シリコン膜を残す。この残された部分が犠牲層405となり、その後の工程で空洞部となる。(図5(a)、(b))。

【0053】

続いて、犠牲層405、絶縁膜404を覆うように、プラズマCVD法によりシリコン酸化膜による絶縁膜406を200nm堆積する。(図6(a)、(b))。

【0054】

次に、CMUTの上部電極407および上部電極を結ぶ配線408を形成するため、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜の積層膜をそれぞれ50nm、300nm、50nm堆積する。そして、フォトリソグラフィ技術とドライエッチング技術により、上部電極407と配線408を形成する(図7(a)、(b))。このときに、下部電極403の段差部での配線409は、フォトリソグラフィのためのマスクで配線幅を太くしておくことで、追加工程なく段差部のみ配線幅を太くすることができる。

【0055】

次にプラズマCVD法により、シリコン窒化膜による絶縁膜410を絶縁膜406、上部電極407および配線408を覆うように500nm堆積する(図8(a)、(b))。続いて、絶縁膜410および406にフォトリソグラフィ技術とドライエッチング技術を使用して犠牲層405に到達するウェットエッチング孔411を形成する(図9(a)、(b))。

【0056】

その後、ウェットエッチング孔411を介して、犠牲層405を水酸化カリウムでウェットエッチングすることにより空洞部412を形成する(図10(a)、(b))。

【0057】

次に、ウェットエッチング孔411を埋め込むために、プラズマCVD法によりシリコン窒化膜による絶縁膜413を800nm堆積する。(図11(a)、(b))。このようにして、本実施の形態1におけるCMUTアレイを形成することができる。

【0058】

以上説明したように、本実施の形態1のCMUTアレイによれば、上部電極407および配線408となる導電膜を堆積する際の段差部でのステップカバレッジが平坦部より低く、膜厚が薄くなっても、下部電極403の段差部での上部電極を結ぶ配線408の配線幅を段差部以外の配線幅よりも太くすることで、配線の抵抗上昇を抑制できる。また、段差部のみの配線幅を太くすることで、下部電極403と上部電極を結ぶ配線408の重なり部が大幅に増えることはなく、下部電極と配線間の寄生容量の増加も抑制することができる。

【0059】

図3において示したCMUTアレイは、下部電極403と上部電極407のクロスポイントに2行1列のCMUTセルを配置した形態であるが、多数行多数列のCMUTセルを配置した場合でも同様である。図12には3行4列のCMUTセルをクロスポイントに配置した形態の上面図を示してある。この場合も、下部電極403の段差部での上部電極407を接続する配線409の幅を太くすることで同様の効果が得られる。また、図12では、下部電極403の段差部での配線409のそれぞれを太くしたが、同じ上部電極を結ぶ配線であれば、図13に示すように、下部電極403の段差部のみ一括して接続することで、下部電極403と配線409の寄生容量は増加するものの、それぞれの配線を太くする効果と同様の効果が得られる。

【0060】

なお、図3、図12、図13において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0061】

また、本実施の形態1として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜(Spin−on−Glass)あるいは金属膜などであってもよい。

【0062】

(実施の形態2)

本実施の形態2におけるCMUTアレイは下部電極による段差を緩和するために、下部電極の外周部をテーパ形状にしたことを特徴とするものである。

【0063】

図14は本実施の形態2のCMUTアレイの上面図である。1503は下部電極、1505は空洞部、1507は上部電極、1508は上部電極1507を結ぶ配線、1510は空洞部1505を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔1510は、空洞部1505に接続されている。1401は、上部電極1507へ電源供給するために下部電極1503と同層に設けたパッドへのパッド開口部であり、1402はパッドと配線1508を接続するプラグである。すなわち、プラグ1402を介して上部電極1507を結ぶ配線1508とパッドが接続されている。1403は下部電極1503に電源供給するためのパッド開口部である。下部電極1503の外周部にはテーパ部1512を形成している。上部電極1507および配線1508と、下部電極1503の間に空洞部1505、テーパ部1512および下部電極1503を覆うように絶縁膜が形成されているが、空洞部1505、下部電極1503、テーパ部1512を示すために図示していない。

【0064】

図15(a)は図14のA−A’方向の断面を示しており、図15(b)は図14のB−B’方向の断面を示している。図15(a)および図15(b)に示すように、半導体基板1501に形成された絶縁膜1502上に下部電極1503が形成されている。下部電極1503の側壁はテーパ形状1512にされている。下部電極1503の上層には絶縁膜1504を介して空洞部1505が形成されている。

【0065】

空洞部1505を囲むように絶縁膜1506が形成され、絶縁膜1506の上層に上部電極1507と上部電極を結ぶ配線1508が形成されている。

【0066】

上部電極1507および配線1508の上層には絶縁膜1509と絶縁膜1511が形成されている。また、絶縁膜1506および絶縁膜1509にはこれらの膜を貫通するウェットエッチング孔1510が形成されている。このウェットエッチング孔1510は、空洞部1505を形成するために形成されたものであり、空洞部1505の形成後、絶縁膜1511によって埋め込まれている。

【0067】

本実施の形態2の特徴は、図14および図15(a)、(b)に示すように、下部電極1503の外周部がテーパ形状になっている点にある。

【0068】

このような構成にすることにより、下部電極1503による段差が緩和され、配線1508の段差部でのステップカバレッジが向上し、配線の抵抗上昇および断線を抑制できる。特に、下部電極1503による段差が500nm以上あると、段差部でのステップカバレッジが一層低下するので、下部電極1503による段差が500nm以上ある場合に、段差部にテーパ部1512を設けることが有効である。

【0069】

また、上部電極1507および配線1508をパターニングする際に、下部電極1503による局所的な段差が緩和されているので、段差部の配線材料を除去するためのオーバーエッチング量も低減できる。つまり、オーバーエッチング量が多いと、上部電極1507の下層にある絶縁膜1506が削れることでCMUTセルのメンブレン膜厚が変化し、動作特性変動の原因となる。しかし、本実施の形態2で示した構造では、下部電極の側壁をテーパ形状に形成することで、局所的な段差を緩和しているので、オーバーエッチング量を減らすことができ、絶縁膜1506の削れ量が低減でき、動作安定性を向上させることができる。

【0070】

さらに、下部電極1503と上部電極1507を絶縁する絶縁膜1504、1506も、下部電極の側壁をテーパ形状にすることで下部電極段差部での膜厚低下が少なく、絶縁耐性の低下を抑制し、デバイスの信頼性を向上できる。

【0071】

また、前記実施の形態1で示したように、下部電極1503の側壁のテーパ部1512と重なる配線のみ配線幅を太くすれば、配線の抵抗上昇および断線を一層抑制できる。

【0072】

本実施の形態2におけるCMUTアレイの製造方法は、前記実施の形態1とほぼ同様であり、下部電極1503のパターニングの際に、側壁をテーパ形状にする点が異なる。

【0073】

下部電極1503の側壁にテーパ角を持たせるためには、ドライエッチング技術で下部電極1503をパターニングする場合、下部電極1503となる金属材料のエッチングガスに炭化水素などの堆積性のガスを混合することで行える。例えば、実施の形態1で示したように下部電極1503が窒化チタン膜とアルミニウム合金膜と窒化チタン膜を積層膜である場合、パターニングは塩素を含むエッチングガスが通常用いられるが、そこに、メタンやジフロロメタン等のガスを混合することで、制御よくテーパ形状にパターニングできる。また、下部電極1503のパターニングをウェットエッチング技術で行うことでも同様にテーパ形状を得ることができる。

【0074】

なお、図14において示したCMUTアレイは、下部電極1503と上部電極1507のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極をテーパ形状にパターニングすることにより同様の効果が得られる。

【0075】

また、図14において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0076】

また、本実施の形態2として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0077】

(実施の形態3)

本実施の形態3におけるCMUTアレイは下部電極による段差を緩和するために、下部電極の外周部にサイドウォールを設けたことを特徴とするものである。

【0078】

図16は本実施の形態のCMUTアレイの上面図である。1703は下部電極、1705は空洞部、1707は上部電極、1708は上部電極1707を結ぶ配線、1710は空洞部1705を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔1710は、空洞部1705に接続されている。1601は、上部電極1707へ電源供給するために下部電極1703と同層に設けたパッドへのパッド開口部であり、1602はパッドと配線1708を接続するプラグである。すなわち、プラグ1602を介して上部電極1707を結ぶ配線1708とパッドが接続されている。1603は下部電極1703に電源供給するためのパッド開口部である。下部電極1703の外周部にはサイドウォール1712が形成されている。上部電極1707および配線1708と、下部電極1703の間に空洞部1705、サイドウォール1712および下部電極1703を覆うように絶縁膜が形成されているが、空洞部1705、下部電極1703、サイドウォール1712を示すために図示していない。

【0079】

図17(a)は図16のA−A’方向の断面を示しており、図17(b)は図16のB−B’方向の断面を示している。図17(a)および図17(b)に示すように、半導体基板1701に形成された絶縁膜1702上に下部電極1703が形成されている。下部電極1703の側壁には絶縁膜によるサイドウォール1712が形成されている。下部電極1703およびサイドウォール1712の上層には絶縁膜1704を介して空洞部1705が形成されている。

【0080】

空洞部1705を囲むように絶縁膜1706を形成し、絶縁膜1706の上層に上部電極1707と上部電極を結ぶ配線1708が形成されている。

【0081】

上部電極1707および配線1708の上層には絶縁膜1709と絶縁膜1711が形成されている。また、絶縁膜1706および絶縁膜1709にはこれらの膜を貫通するウェットエッチング孔1710が形成されている。このウェットエッチング孔1710は、空洞部1705を形成するために形成されたものであり、空洞部1705の形成後、絶縁膜1711によって埋め込まれている。

【0082】

本実施の形態3の特徴は、図16および図17(a)、(b)に示すように、下部電極1703の外周部に絶縁膜によるサイドウォール1712を設けた点にある。

【0083】

このような構成にすることにより、下部電極1703による段差が緩和され、配線1708の段差部でのステップカバレッジが向上し、配線の抵抗上昇および断線を抑制できる。特に、下部電極1703による段差が500nm以上あると、段差部でのステップカバレッジが一層低下するので、下部電極1703による段差が500nm以上ある場合に、下部電極1703の外周部にサイドウォール1712を設けることが有効である。

【0084】

また、上部電極1707および配線1708をパターニングする際に、下部電極1703による局所的な段差が緩和されているので、段差部の配線材料を除去するためのオーバーエッチング量も低減できる。つまり、オーバーエッチング量が多いと、上部電極1707の下層にある絶縁膜1706が削れることでCMUTセルのメンブレン膜厚が変化し、動作特性変動の原因となる。しかし、本実施の形態3で示した構造では、下部電極の外周にサイドウォールを形成することで、局所的な段差を緩和しているので、オーバーエッチング量を減らすことができ、絶縁膜1706の削れ量が低減でき、動作安定性を向上させることができる。

【0085】

さらに、下部電極1703と上部電極1707を絶縁する絶縁膜1704、1706も、サイドウォール1712を形成することで下部電極1703の段差部における膜厚低下を少なくすることができ、絶縁耐性の低下を抑制し、デバイスの信頼性を向上できる。

【0086】

さらに、前記実施の形態1で示したように、サイドウォール1712と重なる配線のみの配線幅を太くすれば、配線の抵抗上昇および断線を一層抑制できる。

【0087】

本実施の形態3におけるCMUTアレイの製造方法は、前記実施の形態1とほぼ同様であり、下部電極1703の外周部にサイドウォール1712を形成する点が異なる。

【0088】

図18〜図20に下部電極形成後からサイドウォール形成までの製造方法を示す。各図の(a)は図16のA−A’断面、(b)は図16のB−B’断面を示している。

【0089】

まず、図18(a)、(b)に示すように、半導体基板1701上にプラズマCVD法でシリコン酸化膜による絶縁膜1702を形成した後に、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜をそれぞれ100nm、600nm、100nm積層し、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極1703を形成する。下部電極1703上にプラズマCVD法によりシリコン酸化膜による絶縁膜1901を600nm堆積させる。(図19(a)(b))。

【0090】

次に、シリコン酸化膜による絶縁膜1901をドライエッチング技術により下部電極1703の表面が露出するまで異方性エッチングすることで、下部電極1703の外周部にシリコン酸化膜よりなるサイドウォール1712を形成できる。(図20(a)(b))。これ以降の工程は前記実施の形態1と同様である。

【0091】

なお、図16において示したCMUTアレイは、下部電極1703と上部電極1707のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極の外周部にサイドウォールを設けることにより同様の効果が得られる。

【0092】

また、図16において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0093】

また、本実施の形態3として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0094】

(実施の形態4)

本実施の形態4におけるCMUTアレイは下部電極による段差を緩和するために、下部電極の上面で平坦化を行ったことを特徴とするものである。

【0095】

図21に本実施の形態4におけるCMUTアレイの上面図を示す。2203は下部電極、2206は空洞部、2208は上部電極、2209は上部電極2208を結ぶ配線、2211は空洞部2206を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔2211は、空洞部2206に接続されている。

【0096】

2101は、上部電極2208へ電源供給するために下部電極2203と同層に設けたパッドへのパッド開口部であり、2102はパッドと配線2209を接続するプラグである。すなわち、プラグ2102を介して上部電極2208を結ぶ配線2209とパッドが接続されている。

【0097】

2103は、下部電極2203に電源供給するためのパッド開口部である。2204は絶縁膜であり、下部電極2203の隙間に埋め込まれている。上部電極2208および配線2209と、下部電極2203の間に空洞部2206および下部電極2203を覆うように絶縁膜が形成されているが、空洞部2206、下部電極2203、および絶縁膜2204を示すために図示していない。

【0098】

図22(a)は図21のA−A’方向の断面を示しており、図22(b)は図21のB−B’方向の断面を示している。

【0099】

図22(a)および図22(b)に示すように、半導体基板2201に形成された絶縁膜2202上に下部電極2203が形成されている。下部電極2203の間には、絶縁膜2204が埋め込まれて、下部電極2203の上面と絶縁膜2204の上面の高さが一致するように平坦化されている。下部電極2203と絶縁膜2204の上層には絶縁膜2205が形成され、下部電極2203上には絶縁膜2205を介して空洞部2206が形成されている。空洞部2206を囲むように絶縁膜2207が形成され、絶縁膜2207の上層に上部電極2208および上部電極を結ぶ配線2209が形成されている。上部電極2208および配線2209の上層には絶縁膜2210と絶縁膜2212が形成されている。また、絶縁膜2210および絶縁膜2207にはこれらの膜を貫通するウェットエッチング孔2211が形成されている。このウェットエッチング孔2211は、空洞部2206を形成するために形成されたものであり、空洞部2206の形成後、絶縁膜2212によって埋め込まれている。

【0100】

本実施の形態4の特徴は、図21、図22(a)、(b)に示すように下部電極2203の間を絶縁膜2204で埋め込んで、平坦化を行った点にある。

【0101】

このような構成にすることにより、下部電極2203による段差がなくなり、上部電極2208を結ぶ配線2209の段差部でのカバレッジの低下が無く、配線の抵抗上昇および断線を抑制できる。特に、下部電極2203による段差が500nm以上あると、段差部でのステップカバレッジが一層低下するので、下部電極2203による段差が500nm以上ある場合に、下部電極2203の間に絶縁膜2204を埋め込んで平坦化することが有効である。

【0102】

また、上部電極2208をパターニングする際に、下部電極2203による段差部が無いために配線材料をエッチングするためのオーバーエッチング量も低減できる。つまり、オーバーエッチング量が多いと、上部電極2208の下層にある絶縁膜2207が削れることでCMUTセルのメンブレン膜厚が変化し、動作特性変動の原因となる。しかし、本実施の形態4で示した構造では、下部電極の隙間を絶縁膜で埋め込み、平坦化しているので、段差が無くなり、オーバーエッチング量を減らすことができる。すなわち、絶縁膜2207の削れ量が低減でき、動作安定性を向上させることができる。

【0103】

さらに、下部電極2203と上部電極2208を絶縁する絶縁膜2205、2207も、下部電極2203による段差が無いことから、絶縁耐性が低下せず、デバイスの信頼性を向上できる。

【0104】

本実施の形態4におけるCMUTアレイの製造方法は、前記実施の形態1とほぼ同様であり、下部電極の間に絶縁膜を埋め込んで平坦化する点が異なる。

【0105】

図23、図24には下部電極の間を埋め込む絶縁膜の形成後から絶縁膜の平坦化までを示してある。各図の(a)は図21のA−A’断面、(b)は図21のB−B’断面を示している。

【0106】

まず、図23(a)、(b)に示すように、半導体基板2201上にプラズマCVD法によりシリコン酸化膜による絶縁膜2202を形成し、その後、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜を100nm、600nm、100nm積層した後に、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極2203を形成する。下部電極2203上にプラズマCVD法によりシリコン酸化膜による絶縁膜2301を1400nm堆積させる。

【0107】

次に、シリコン酸化膜による絶縁膜2301をCMP(Chemical Mechanical Polishing)技術により、下部電極2203の表面が露出するまで平坦化を行うことで、下部電極の間に埋め込まれ平坦化されたシリコン酸化膜による絶縁膜2204を形成することができる。(図24(a)(b))。これ以降の工程は前記実施の形態1と同様である。

【0108】

本実施の形態4ではシリコン酸化膜による絶縁膜2301を下部電極2203の表面が露出するまでCMP技術により平坦化を行ったが、下部電極2203の表面が露出する直前までCMP技術により平坦化を行い、その後、ドライエッチング技術により、下部電極2203の表面が露出するまでシリコン酸化膜による絶縁膜2301をエッチングしても同様の形状が得られる。

【0109】

シリコン酸化膜の平坦化を精度よく行うために、図25〜図28に示すように、CMP技術による平坦化プロセスの停止膜を挿入してもよい。各図の(a)は図21のA−A’断面、(b)は図21のB−B’断面を示している。図25(a)、(b)に示すように、下部電極2203を形成後に、平坦化CMPプロセスの停止膜として、プラズマCVD法によりシリコン窒化膜による絶縁膜2501を200nm形成する。その後、プラズマCVD法によりシリコン酸化膜による絶縁膜2601をシリコン窒化膜による絶縁膜2501上に1400nm堆積する。(図26(a)、(b))。引き続き、シリコン酸化膜による絶縁膜2601をCMP技術によりシリコン窒化膜による絶縁膜2501の上面が露出するまで研磨することにより平坦化を行う。(図27(a)、(b))。このとき、シリコン酸化膜とシリコン窒化膜のCMPでの研磨速度比が2〜3であるので、シリコン窒化膜による絶縁膜2501上面で研磨を制御よく停止することが可能である。その後、シリコン酸化膜による絶縁膜2601とシリコン窒化膜による絶縁膜2501をドライエッチングにより等速エッチングすることにより、下部電極2203の表面を露出させ、下部電極の間が平坦化された構造を形成することができる。(図28(a)、(b))。

【0110】

さらに、本実施の形態4では、下部電極2203の間を埋め込む絶縁膜2204をプラズマCVD法で形成したが、塗布法によりSOG膜を埋め込んでもよい。その場合、SOG膜埋め込み後、ドライエッチングによって、下部電極の表面が露出するまでエッチバックを行うことにより、図24や図28と同様の平坦化された構造を得ることができる。

【0111】

また、ダマシン法による埋め込み配線で下部電極を形成しても、同様の下部電極の上面で平坦化された構造を得ることができる。その場合は、絶縁膜にエッチングで予め溝形状を形成しておき、下部電極となる材料をこの溝に埋め込み、溝からはみ出した余分な下部電極材料を研磨し、除去することで実現できる。

【0112】

なお、図21において示したCMUTアレイは、下部電極2203と上部電極2208のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極の上面で平坦化を行うことにより同様の効果が得られる。

【0113】

また、図21において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0114】

また、本実施の形態4として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0115】

(実施の形態5)

本実施の形態5におけるCMUTアレイは下部電極による段差を緩和するために、下部電極の上面で平坦化を行い、かつ平坦化のためのダミーパターンを下部電極と同層に形成することを特徴とするものである。

【0116】

図29に本実施の形態5のCMUTアレイの上面図を示す。3003は下部電極、3007は空洞部、3009は上部電極、3010は上部電極3009を結ぶ配線、3012は空洞部3007を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔3012は、空洞部3007に接続されている。

【0117】

2901は、上部電極3009へ電源供給するために下部電極3003と同層に設けたパッドへのパッド開口部であり、2902はパッドと配線3010を接続するプラグである。すなわち、プラグ2902を介して上部電極3009を結ぶ配線3010とパッドが接続されている。2903は下部電極3003に電源供給するためのパッド開口部である。下部電極3003の間に平坦化のためのダミーパターン3004が形成されている。3005はダミーパターン3004と下部電極3003の隙間に埋め込んだ絶縁膜である。

【0118】

上部電極3009および配線3010と、下部電極3003の間に空洞部3007、ダミーパターン3004、絶縁膜3005および下部電極3003を覆うように絶縁膜が形成されているが、空洞部3007、下部電極3003、ダミーパターン3004、絶縁膜3005を示すために図示していない。

【0119】

図30に本実施の形態5におけるCMUTアレイの断面を示す。図30(a)は図29のA−A’方向の断面を示しており、図30(b)は図29のB−B’方向の断面を示している。

【0120】

図30(a)および図30(b)に示すように、半導体基板3001に形成された絶縁膜3002上に下部電極3003が形成されている。平坦化のためのダミーパターン3004も下部電極3003と同時に形成している。つまり、下部電極3003とダミーパターン3004は同一の高さで形成されている。

【0121】

下部電極3003とダミーパターン3004の間には、絶縁膜3005が埋め込まれ、下部電極3003およびダミーパターン3004の上面と絶縁膜3005の上面の高さが一致するように平坦化されている。絶縁膜3005は、下部電極3003とダミーパターン3004とを電気的に絶縁するために設けられている。

【0122】

下部電極3003、ダミーパターン3004および絶縁膜3005の上層には絶縁膜3006が形成され、下部電極3003上には絶縁膜3006を介して空洞部3007が形成されている。空洞部3007を囲むように絶縁膜3008が形成され、絶縁膜3008の上層に上部電極3009および上部電極を結ぶ配線3010が形成されている。上部電極3009および配線3010の上層には絶縁膜3011と絶縁膜3013が形成されている。また、絶縁膜3011および絶縁膜3008にはこれらの膜を貫通するウェットエッチング孔3012が形成されている。このウェットエッチング孔3012は、空洞部3007を形成するために形成されたものであり、空洞部3007の形成後、絶縁膜3013によって埋め込まれている。

【0123】

本実施の形態5の特徴は、図29、図30(a)、(b)に示すように下部電極3003の間にダミーパターン3004を設けて、下部電極3003とダミーパターン3004の隙間に絶縁膜3005で埋め込み、平坦化した点にある。

【0124】

このような構成にすることにより、下部電極3003による段差の平坦化のためのCMPプロセスでの平坦性を一層向上させることができる。つまり、ダミーパターン3004が無いと、絶縁膜3005のCMP研磨時に、ディッシングと呼ばれる現象によって、下地に下部電極3003が存在しない領域の絶縁膜3005の落ち込み量が多くなってしまう可能性がある。しかし、本実施の形態5で示した構造では、ダミーパターン3004によって、絶縁膜3005のCMPによる平坦性が向上し、下部電極3003による段差を一層緩和することができるので、配線3010の抵抗上昇および断線を抑制できる。すなわち、下部電極3003の間に、下部電極3003と同じ材料から構成されているダミーパターン3004を形成することにより、ダミーパターン3004を形成しない場合のディッシングを防止することができる。特に、下部電極3003による段差が500nm以上あると、段差部でのステップカバレッジが一層低下するので、下部電極3003による段差が500nm以上ある場合に、下部電極3003の間にダミーパターン3004および絶縁膜3005を埋め込んで平坦化することが有効である。

【0125】

また、上部電極3009をパターニングする際のオーバーエッチング量も低減でき、絶縁膜3008の削れ量が低減でき、動作安定性を向上させることができる。

【0126】

さらに、下部電極3003と上部電極3009を絶縁する絶縁膜3006、3008も、下部電極3003による段差が無いことから、絶縁耐性が低下せず、デバイスの信頼性を向上できる。

【0127】

本実施の形態5におけるCMUTアレイの製造方法は、前記実施の形態4とほぼ同様であり、下部電極と同層にダミーパターンを形成する点が異なる。

【0128】

図31〜図33は下部電極と平坦化のためのダミーパターン形成と、下部電極の間を埋め込む絶縁膜の形成後から絶縁膜の平坦化までの製造方法を示してある。各図の(a)は図29のA−A’方向の断面、(b)は図29のB−B’方向の断面を示している。

【0129】

まず、図31(a)、(b)に示すように、半導体基板3001上にプラズマCVD法によりシリコン酸化膜による絶縁膜3002を形成する。その後、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜をそれぞれ100nm、600nm、100nm積層した後に、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極3003を形成する。このときに、平坦化のためのダミーパターン3004も同時に形成する。下部電極3003とダミーパターン3004上にプラズマCVD法によりシリコン酸化膜による絶縁膜3005を1400nm堆積させる。(図32(a)、(b))。

【0130】

次に、シリコン酸化膜による絶縁膜3005をCMP技術により下部電極3003およびダミーパターン3004の表面が露出するまで平坦化を行うことで、下部電極とダミーパターンの間に埋め込まれ、平坦化されたシリコン酸化膜による絶縁膜3005の構造を形成することができる。(図33(a)(b))。これ以降の工程は前記実施の形態4と同様である。

【0131】

本実施の形態5ではシリコン酸化膜を下部電極3003とダミーパターン3004の表面が露出するまでCMP技術により平坦化を行ったが、下部電極3003とダミーパターン3004の表面が露出する直前までCMP技術により平坦化を行い、その後、ドライエッチング技術により、下部電極3003とダミーパターン3004の表面が露出するまでシリコン酸化膜をエッチングしても同様の形状が得られる。

【0132】

また、シリコン酸化膜の平坦化を精度よく行うために、CMPによる平坦化プロセスの停止膜を、下部電極3003とダミーパターン3004の上層に挿入してもよい。

【0133】

さらに、本実施の形態5では、下部電極3003とダミーパターン3004の隙間を埋め込む絶縁膜3005をプラズマCVD法で形成したが、塗布法によりSOG膜を埋め込んでもよい。その場合、SOG膜を塗布することにより下部電極3003とダミーパターン3004の隙間を埋め込んだ後、ドライエッチングによって、下部電極3003とダミーパターン3004の表面が露出するまでエッチバックを行うことにより、図33と同様の平坦化された構造を得ることができる。

【0134】

また、ダマシン法による埋め込み配線で下部電極3003を形成しても、同様の平坦化された構造を得ることができる。その場合は、絶縁膜にエッチングにより予め下部電極用の溝とダミーパターン用の溝を形成しておき、下部電極3003となる材料をこれらの溝に埋め込み、溝からはみ出した余分な下部電極材料を研磨し、除去することで実現できる。

【0135】

なお、図29において示したCMUTアレイは、下部電極3003と上部電極3009のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極の上面で平坦化を行い、かつ平坦化のためのダミーパターンを下部電極と同層に形成することにより同様の効果が得られる。

【0136】

また、図29において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0137】

また、本実施の形態5として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0138】

(実施の形態6)

本実施の形態6におけるCMUTアレイは下部電極および空洞部による段差を緩和するために、空洞部上で平坦化を行うことを特徴とするものである。

【0139】

本実施の形態6のCMUTアレイ上面図は、電極や空洞部の配置に関して、図1と同様であるので、図34に本実施の形態6におけるCMUTアレイの断面を示し説明する。図34(a)は図1のA−A’断面を示しており、図34(b)は図1のB−B’断面を示している。

【0140】

図34(a)および図34(b)に示すように、半導体基板201に形成された絶縁膜202上に下部電極203が形成されている。下部電極203上には絶縁膜204を介して空洞部205が形成されている。絶縁膜204と空洞部205を覆うように絶縁膜3401を形成し、空洞部の上面と同じ高さになるように絶縁膜3401を平坦化している。

【0141】

空洞部205および絶縁膜3401を覆うように絶縁膜206を形成し、絶縁膜206の上層に上部電極207と上部電極を結ぶ配線208が形成されている。上部電極207および配線208の上層には絶縁膜209と絶縁膜211が形成されている。また、絶縁膜209および絶縁膜206にはこれらの膜を貫通するウェットエッチング孔210が形成されている。このウェットエッチング孔210は、空洞部205を形成するために形成されたものであり、空洞部205の形成後、絶縁膜211によって埋め込まれている。

【0142】

本実施の形態6の特徴は、図34(a)、(b)に示すように空洞部205の上面で絶縁膜3401を平坦化した点にある。

【0143】

このような構成にすることにより、下部電極203による段差とともに、空洞部205による段差も一括して緩和することができ、上部電極を結ぶ配線208が段差の影響を受けることなく、配線の抵抗上昇および断線を抑制できる。

【0144】

また、上部電極207をパターニングする際に、段差が無いために、配線材料をエッチングするためのオーバーエッチング量も低減できる。つまり、オーバーエッチング量が多いと、上部電極207の下層にある絶縁膜206が削れることでCMUTセルのメンブレン膜厚が変化し、動作特性変動の原因となるが、本実施の形態6で示した構造では、絶縁膜206の削れ量が低減できるので、動作安定性を向上させることができる。

【0145】

さらに、図34(a)に示すように、配線208は平坦化された絶縁膜206上に配置されるので、下部電極との絶縁耐性が低下せず、デバイスの信頼性を向上できる。

【0146】

本実施の形態6におけるCMUTアレイの製造方法は、前記実施の形態1とほぼ同様であり、空洞部上面で平坦化を行った点が異なる。

【0147】

図35〜図37は犠牲層形成と、その後の絶縁膜埋め込み、絶縁膜平坦化までを示している。各図の(a)は図1のA−A’方向の断面、(b)は図1のB−B’方向の断面に対応している。

【0148】

まず、図35(a)、(b)に示すように、半導体基板201上にプラズマCVD法によりシリコン酸化膜による絶縁膜202を形成した後、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜を100nm、600nm、100nm積層した後に、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極203を形成する。この下部電極203上にプラズマCVD法によりシリコン酸化膜による絶縁膜204を100nm堆積させる。次に、シリコン酸化膜による絶縁膜204の上面に多結晶シリコン膜をプラズマCVD法により200nm堆積する。そして、フォトリソグラフィ技術とドライエッチング技術により、多結晶シリコン膜を残す。この残された部分が犠牲層3501となり、その後の工程で図34の空洞部205となる。

【0149】

次に、犠牲層3501およびシリコン酸化膜による絶縁膜204を覆うようにプラズマCVD法でシリコン酸化膜による絶縁膜3401を1400nm堆積させる。(図36(a)、(b))。

【0150】

その後、CMP技術により、犠牲層3501の上面が露出するまで、シリコン酸化膜による絶縁膜3401を研磨することで、犠牲層上面で平坦化された構造を得ることができる。(図37(a)、(b))。その後の工程は前記実施の形態1と同様である。

【0151】

本実施の形態6では、シリコン酸化膜による絶縁膜3401を犠牲層3501の上面が露出するまでCMP技術により平坦化を行ったが、犠牲層3501の上面が露出する直前までCMP技術により平坦化を行い、その後、ドライエッチング技術により、犠牲層3501の上面が露出するまでシリコン酸化膜による絶縁膜3401をエッチングしても同様の構造が得られる。

【0152】

また、シリコン酸化膜による絶縁膜3401の平坦化を精度よく行うために、CMPによる平坦化プロセスの停止膜を、犠牲層3501と絶縁膜204の上層に挿入してもよい。その場合、絶縁膜3401の研磨を平坦化プロセス停止膜で精度よく停止した後に、犠牲層3501の上面が露出するまで、ドライエッチングによって停止膜および絶縁膜3401を等速エッチングすることで、同様の平坦化された構造を得ることができる。

【0153】

さらに、本実施の形態6では、平坦化を行う絶縁膜3401をプラズマCVD法で形成したが、塗布法によりSOG膜を埋め込んでもよい。その場合、SOG膜を塗布した後に、ドライエッチングによって、犠牲層の上面が露出するまでエッチバックを行うことにより、図37と同様の平坦化された構造を得ることができる。

【0154】

なお、図1において示したCMUTアレイは、下部電極203と上部電極207のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、空洞部上で平坦化を行うことにより同様の効果が得られる。

【0155】

また、図1において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0156】

また、本実施の形態6として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0157】

(実施の形態7)

本実施の形態7におけるCMUTアレイは下部電極および空洞部による段差を緩和するために、下部電極と同層に平坦化のためのダミーパターンを形成する点と、空洞部上で平坦化を行うことを特徴とするものである。

【0158】

本実施の形態7のCMUTアレイの上面図を図38に示す。

【0159】

3903は下部電極、3906は空洞部、3909は上部電極、3910は上部電極3909を結ぶ配線、3912は空洞部3906を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔3912は、空洞部3906に接続されている。

【0160】

3801は、上部電極3909へ電源供給するために下部電極3903と同層に設けたパッドへのパッド開口部であり、3802はパッドと配線3910を接続するプラグである。すなわち、プラグ3802を介して上部電極3909を結ぶ配線3910とパッドが接続されている。3803は下部電極3903に電源供給するためのパッド開口部である。下部電極3903の間に平坦化のためのダミーパターン3904を形成してある。上部電極3909と下部電極3903の間に、空洞部3906、ダミーパターン3904および下部電極3903を覆うように絶縁膜が形成されているが、空洞部3906、下部電極3903、ダミーパターン3904を示すために図示していない。

【0161】

図39に本実施の形態7におけるCMUTアレイの断面を示す。図39(a)は図38のA−A’断面を示しており、図39(b)は図38のB−B’断面を示している。

【0162】

図39(a)および図39(b)に示すように、半導体基板3901に形成された絶縁膜3902上に下部電極3903が形成されている。平坦化のためのダミーパターン3904も下部電極3903と同時に形成している。下部電極3903上には絶縁膜3905を介して空洞部3906が形成されている。絶縁膜3905と空洞部3906を覆うように絶縁膜3907を形成し、空洞部の上面と同じ高さになるように絶縁膜3907を平坦化している。空洞部3906および絶縁膜3907を覆うように絶縁膜3908を形成し、絶縁膜3908の上層に上部電極3909と上部電極3909を結ぶ配線3910が形成されている。上部電極3909の上層には絶縁膜3911と絶縁膜3913が形成されている。また、絶縁膜3908および絶縁膜3911にはこれらの膜を貫通するウェットエッチング孔3912が形成されている。このウェットエッチング孔3912は、空洞部3906を形成するために形成されたものであり、空洞部3906の形成後、絶縁膜3913によって埋め込まれている。

【0163】

本実施の形態7の特徴は、図38および図39(a)、(b)に示すように、下部電極3903の間にダミーパターン3904を設けて、下部電極3903とダミーパターン3904の隙間と、空洞部3906、絶縁膜3905上に絶縁膜3907を形成し、空洞部3906上面で絶縁膜3907を平坦化した点にある。

【0164】

このような構成にすることにより、下部電極3903による段差の平坦化のためのCMPプロセスでの平坦性を一層向上させることができる。

【0165】

つまり、ダミーパターン3904が無いと、ディッシングと呼ばれる現象によって、絶縁膜3907のCMP工程時に、下地に下部電極3903が存在しない領域の絶縁膜3907の落ち込み量が多くなってしまう。しかし、本実施の形態7で示した構造では、ダミーパターン3904によって、絶縁膜3907のCMPによる平坦性が向上し、下部電極3903による段差を一層緩和することができる。

【0166】

したがって、ダミーパターン3904が無い場合と比較して、上部電極3909を結ぶ配線3910が段差の影響を一層受けることなく、配線の抵抗上昇および断線を抑制できる。

【0167】

また、上部電極3910をパターニングする際に、段差が無いために配線材料をエッチングするためのオーバーエッチング量もより低減できる。さらに、図39(a)に示すように、配線3910は平坦化された絶縁膜3908上に配置されるので、下部電極3903との間の絶縁耐性が低下せず、デバイスの信頼性を向上できる。

【0168】

本実施の形態7におけるCMUTアレイの製造方法は、前記実施の形態6とほぼ同様であり、下部電極と同層に平坦化のためのダミーパターンを形成した点が異なるのみである。

【0169】

また、平坦化の方法も、前記実施の形態6と同様に、プラズマCVD法による絶縁膜形成後、CMPプロセスにより平坦化しても、CMPプロセスとドライエッチングの組み合わせで平坦化してもよい。さらに、平坦化プロセスの停止膜を、空洞部の上層に挿入し、絶縁膜の研磨を平坦化プロセス停止膜で精度よく停止した後に、犠牲層の上面が露出するまで、ドライエッチングによって停止膜および絶縁膜を等速エッチングすることでも同様の平坦化された構造を得ることができる。

【0170】

また、CMPプロセスを使用せずに、塗布法によりSOG膜を埋め込み、ドライエッチングによって、犠牲層の上面が露出するまでエッチバックを行うことでも同様の平坦化された構造を得ることができる。

【0171】

また、空洞部3906の上面で平坦化された構造を得るためには、空洞部3906のもととなる犠牲層をダマシン法により形成しても同様の構造を得ることができる。その場合は、絶縁膜にエッチングによって予め犠牲層用の溝を形成しておき、犠牲層となる材料を溝に埋め込み、溝からはみ出した余分な材料を研磨することで実現できる。

【0172】

なお、図38において示したCMUTアレイは、下部電極3903と上部電極3909のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極と同層に平坦化のためのダミーパターンを形成する点と、空洞部上で平坦化を行うことにより同様の効果が得られる。

【0173】

また、図38において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0174】

また、本実施の形態7として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0175】

(実施の形態8)

本実施の形態8におけるCMUTアレイは下部電極および空洞部による段差を緩和するために、下部電極および空洞部と同層に平坦化のためのダミーパターンを形成する点と、空洞部上で平坦化を行うことを特徴とするものである。

【0176】

図40に本実施の形態8のCMUTアレイの上面図を示す。4103は下部電極、4106は空洞部、4110は上部電極、4111は上部電極4110を結ぶ配線、4113は空洞部4106を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔4113は、空洞部4106に接続されている。4001は、上部電極4110へ電源供給するために下部電極4103と同層に設けたパッドへのパッド開口部であり、4002はパッドと配線4111を接続するプラグである。すなわち、プラグ4002を介して上部電極4110を結ぶ配線4111とパッドが接続されている。4003は下部電極4103に電源供給するためのパッド開口部である。下部電極4103の間に平坦化のためのダミーパターン4104を下部電極4103と同層に形成してある。また、4107は空洞部と同層に形成したダミーパターンである。

【0177】

上部電極4110と下部電極4103の間に、空洞部4106、ダミーパターン4104、4107および下部電極4103を覆うように絶縁膜が形成されているが、空洞部4106、下部電極4103、ダミーパターン4104、4107を示すために図示していない。

【0178】

図41に本実施の形態8におけるCMUTアレイの断面を示す。図41(a)は図40のA−A’断面を示しており、図41(b)は図40のB−B’断面を示している。

【0179】

図41(a)および図41(b)に示すように、半導体基板4101に形成された絶縁膜4102上に下部電極4103が形成されている。

【0180】

平坦化のためのダミーパターン4104も下部電極4103と同時に形成している。下部電極4103上には絶縁膜4105を介して空洞部4106が形成してある。空洞部と同層にも平坦化のためのダミーパターン4107を形成してある。絶縁膜4105、空洞部4106およびダミーパターン4107を覆うように絶縁膜4108を形成し、空洞部の上面と同じ高さになるように絶縁膜4108を平坦化している。空洞部4106、ダミーパターン4107および絶縁膜4108を覆うように絶縁膜4109を形成し、絶縁膜4109の上層に上部電極4110と上部電極を結ぶ配線4111が形成されている。上部電極4110の上層には絶縁膜4112と絶縁膜4114が形成されている。また、絶縁膜4109および絶縁膜4112にはこれらの膜を貫通するウェットエッチング孔4113が形成されている。このウェットエッチング孔4113は、空洞部4106を形成するために形成されたものであり、空洞部4106の形成後、絶縁膜4114によって埋め込まれている。

【0181】

本実施の形態8の特徴は、図40および図41(a)、(b)に示すように、下部電極4103と同じ層と、空洞部と同じ層にダミーパターン4104と4107を設けて、下部電極4103とダミーパターン4104、空洞部4106とダミーパターン4107の隙間を絶縁膜4108で埋め込み、空洞部4106上面で絶縁膜4108を平坦化した点にある。

【0182】

このような構成にすることにより、下部電極4103および空洞部4106による段差の平坦化のためのCMPプロセスで、平坦性を一層向上させることができる。

【0183】

つまり、ダミーパターン4104、4107が無いと、ディッシングと呼ばれる現象によって、絶縁膜4108のCMP研磨時に、下地に下部電極4103あるいは空洞部4106が存在しない領域の絶縁膜4108の落ち込み量が多くなってしまう。しかし、本実施の形態8で示した構造では、ダミーパターン4104および4107によって、絶縁膜4108のCMPによる平坦性が向上し、下部電極4103および空洞部4106による段差を一層緩和することができる。

【0184】

また、上部電極4110をパターニングする際に、段差が無いために配線材料をエッチングするためのオーバーエッチング量もより低減できる。さらに、図41(a)に示すように、配線4111は平坦化された絶縁膜4109上に配置されるので、下部電極4103との絶縁耐性が低下せず、デバイスの信頼性を向上できる。

【0185】

本実施の形態8におけるCMUTアレイの製造方法は、空洞部と同層に平坦化のためのダミーパターンを形成した点を除き、前記実施の形態7と同様である。

【0186】

本実施の形態8においても前記実施の形態7の場合と同様に、平坦化プロセスをCMP技術のみで行っても、またCMP技術とドライエッチング技術の組み合わせで行っても良いことは自明である。また、前記実施の形態7の場合と同様にCMPプロセスの停止膜を犠牲層の上層に挿入してもよい。

【0187】

さらに、本実施の形態8でも、平坦化を行う絶縁膜を塗布法によるSOG膜を埋め込んでもよい。その場合、SOG膜を塗布した後に、ドライエッチングによって、犠牲層の上面が露出するまでエッチバックを行うことにより、図41と同様の平坦化された構造を得ることができる。

【0188】

また、空洞部4106の上面で平坦化された構造を得るためには、空洞部4106のもととなる犠牲層をダマシン法により形成しても同様の構造を得ることができる。その場合は、絶縁膜にエッチングにより予め犠牲層用の溝を形成しておき、犠牲層となる材料を溝に埋め込み、溝からはみ出した余分な材料を研磨することで実現できる。

【0189】

なお、図40において示したCMUTアレイは、下部電極4103と上部電極4110のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極および空洞部と同層に平坦化のためのダミーパターンを形成する点と、空洞部上で平坦化を行うことにより同様の効果が得られる。

【0190】

また、図40において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0191】

また、本実施の形態8として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0192】

(実施の形態9)

本実施の形態9におけるCMUTアレイは下部電極および空洞部による段差を緩和するために、下部電極および空洞部と同層に平坦化のためのダミーパターンを形成する点と、下部電極上および空洞部上で平坦化を行うことを特徴とするものである。

【0193】

図42に本実施の形態9のCMUTアレイの上面図を示す。4303は下部電極、4307は空洞部、4311は上部電極、4312は上部電極4311を結ぶ配線、4314は空洞部4307を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔4314は、空洞部4307に接続されている。4201は、上部電極4311へ電源供給するために下部電極4303と同層に設けたパッドへのパッド開口部であり、4202はパッドと配線4312を接続するプラグである。すなわち、プラグ4202を介して上部電極4311を結ぶ配線4312とパッドが接続されている。4203は下部電極4303に電源供給するためのパッド開口部である。4308は空洞部と同層に形成したダミーパターンである。下部電極4303の間に平坦化のためのダミーパターンを下部電極4303と同層に形成してあるが、ダミーパターン4308に覆われているので図示していない。上部電極4311と下部電極4303の間に、空洞部4307、下部電極と同層のダミーパターン、空洞部と同層のダミーパターン4308および下部電極4303を覆うように絶縁膜が形成されているが、空洞部4307、下部電極4303、ダミーパターン4308を示すために図示していない。

【0194】

図43に本実施の形態9におけるCMUTアレイの断面を示す。図43(a)は図42のA−A’断面を示しており、図43(b)は図42のB−B’断面を示している。

【0195】

図43(a)および図43(b)に示すように、半導体基板4301に形成された絶縁膜4302上にCMUTの下部電極4303が形成されている。

【0196】

平坦化のためのダミーパターン4304も下部電極4303と同時に形成している。下部電極4303とダミーパターン4304の間には、絶縁膜4305が埋め込まれて、下部電極4303の上面と絶縁膜4305の上面の高さが一致するように平坦化されている。下部電極4303、ダミーパターン4304および絶縁膜4305の上層には絶縁膜4306が形成され、下部電極4303上には絶縁膜4306を介して空洞部4307が形成されている。

【0197】

空洞部4307と同層にも平坦化のためのダミーパターン4308を形成している。絶縁膜4306、空洞部4307およびダミーパターン4308を覆うように絶縁膜4309を形成し、空洞部の上面と同じ高さになるように絶縁膜4309を平坦化している。空洞部4307、ダミーパターン4308および絶縁膜4309を覆うように絶縁膜4310を形成し、絶縁膜4310の上層に上部電極4311と上部電極を結ぶ配線4312が形成されている。上部電極4311の上層には絶縁膜4313と絶縁膜4315が形成されている。また、絶縁膜4310および絶縁膜4313にはこれらの膜を貫通するウェットエッチング孔4314が形成されている。このウェットエッチング孔4314は、空洞部4307を形成するために形成されたものであり、空洞部4307の形成後、絶縁膜4315によって埋め込まれている。

【0198】

本実施の形態9の特徴は、図42および図43(a)、(b)に示すように、下部電極4303と同層にダミーパターン4304を設けて、下部電極4303とダミーパターン4304の隙間に絶縁膜4305を埋め込み、下部電極上面で絶縁膜4305を平坦化している点にある。そしてさらに、空洞部4307と同層にダミーパターン4308を設けて、空洞部4307とダミーパターン4308の隙間に絶縁膜4309を埋め込み、空洞部4307上面で絶縁膜4309を平坦化した点にある。

【0199】

このような構成にすることにより、下部電極4303上で平坦化を行っているので、空洞部4307と同層のダミーパターン4308を、下部電極4303の配置によらず配置することができ、下部電極4303および空洞部4307による段差の平坦化のためのプロセスでの平坦性を一層向上させることができる。

【0200】

つまり、下部電極4303上で平坦化を行っていない場合、空洞部4307と同層のダミーパターン4308は、下部電極4303上あるいは下部電極4303と同層のダミーパターン4304上にしか配置することができない。したがって、空洞部4307および空洞部4307と同層のダミーパターン4308が配置されていない領域がディッシングと呼ばれる現象によって、絶縁膜4309のCMP研磨時に、絶縁膜4309の落ち込み量が多くなってしまう。しかし、本実施の形態9で示した構造では、図42、図43(a)、(b)で示すように、空洞部4307と同層のダミーパターン4308を下部電極4303および下部電極4303と同層のダミーパターン4304の配置に依存せず配置できるので、空洞部4307と、空洞部4307と同層のダミーパターン4308の隙間に埋め込んだ絶縁膜のCMPによる平坦性が向上し、空洞部4307による段差を一層緩和することができる。

【0201】

本実施の形態9におけるCMUTアレイの製造方法は、下部電極と同層にダミーパターンを配置し平坦化する点は前記実施の形態5と同様である。空洞部と同層に平坦化のためのダミーパターンを配置し平坦化する点は、下部電極と下部電極と同層のダミーパターンの配置に依存せずダミーパターンを配置する点を除き、前記実施の形態8と同様である。

【0202】

本実施の形態9においても、平坦化プロセスをCMP技術のみで行っても、またCMP技術とドライエッチング技術の組み合わせで行っても良いことは自明である。また、CMPプロセスの停止膜を犠牲層の上層に挿入してもよい。

【0203】

さらに、本実施の形態9でも、平坦化を行う絶縁膜を塗布法によるSOG膜を埋め込んでもよい。その場合、SOG膜を塗布した後に、ドライエッチングによって、犠牲層の上面が露出するまでエッチバックを行うことにより、図43と同様の平坦化された構造を得ることができる。

【0204】

なお、図42において示したCMUTアレイは、下部電極4303と上部電極4311のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極および空洞部と同層に平坦化のためのダミーパターンを形成する点と、下部電極上および空洞部上で平坦化を行うことにより同様の効果が得られる。

【0205】

また、図42において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0206】

また、本実施の形態9として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0207】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0208】

本発明の超音波トランスデューサは、医療用を始めとする超音波を用いた検査を行う機関、および検査装置を製造する製造業に幅広く利用することができる。また、製造方法は超音波トランスデューサを製造する製造業に幅広く利用することができる。

【符号の説明】

【0209】

101,103,301,303,1401,1403,1601,1603,2101,2103,2901,2903,3801,3803,4001,4003,4201,4203 パッド開口部

102,302,1402,1602,2202,2902,3802,4002,4202 プラグ

201,401,1501,1701,2201,3001,3901,4101,4301 半導体基板

202,204,206,209,211,402,404,406,410,413,1502,1504,1506,1509,1511,1702,1704,1706,1709,1711,1901,2202,2204,2205,2207,2210,2212,2301,2501,2601,3002,3005,3006,3008,3011,3013,3401,3902,3905,3907,3908,3911,3913,4102,4105,4108,4109,4112,4114,4302,4305,4306,4309,4310,4313,4315 絶縁膜

203,403,1503,1703,2203,3003,3903,4103,4303 下部電極

205,412,1505,1705,2206,3007,3906,4106,4307 空洞部

207,407,1507,1707,2208,3009,3909,4110,4311 上部電極

208,408,409,1508,1708,2209,3010,3910,4111,4312 配線

210,411,1510,1710,2211,3012,3912,4113,4314 ウェットエッチング孔

405,3501 犠牲層

1512 テーパ部

1712 サイドウォール

3004,3904,4104,4107,4304,4308 ダミーパターン

【技術分野】

【0001】

本発明は、超音波トランスデューサおよびその製造方法に関するものである。特に、MEMS(Micro Electro Mechanical System)技術により製造した超音波トランスデューサと、その最適な製造方法に関する。

【背景技術】

【0002】

超音波トランスデューサは超音波を送信、受信することにより、人体内の腫瘍などの診断装置に用いられている。

【0003】

これまでは、圧電体の振動を利用した超音波トランスデューサが用いられてきたが、近年のMEMS技術の進歩により、電極の間に空洞部を挟みこんだ構造による振動部をシリコン基板上に作製した容量検出型超音波トランスデューサ(CMUT:Capacitive Micromachined Ultrasonic Transducer)が実用化を目指して盛んに開発されている。

【0004】

例えば、米国特許第6320239B1号明細書(特許文献1)には、シリコン基板を下部電極に用いたCMUT開示されている。

【0005】

また、米国特許第6271620B1号明細書(特許文献2)および2003 IEEE ULTRASONICS SYMPOSIUM、p577−p580(非特許文献1)には、パターニングされた下部電極上に形成した構造のCMUTが開示されている。

【0006】

また、米国特許第6571445B2号明細書(特許文献3)および米国特許第6562650B2号明細書(特許文献4)には、シリコン基板上に形成した信号処理回路の上層にCMUTを形成する技術が開示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第6320239B1号明細書

【特許文献2】米国特許第6271620B1号明細書

【特許文献3】米国特許第6571445B2号明細書

【特許文献4】米国特許第6562650B2号明細書

【非特許文献】

【0008】

【非特許文献1】2003 IEEE ULTRASONICS SYMPOSIUM、p577−p580

【発明の概要】

【発明が解決しようとする課題】

【0009】

ところで、CMUTは、従来の圧電体を用いたトランスデューサと比較して、使用できる超音波の周波数帯域が広い、あるいは高感度であるなどの利点がある。またLSI加工技術を用いて作製するので微細加工が可能である。特に、素子をアレイ状に配置して、素子の上部電極と下部電極を直交配置し、そのクロスポイントの素子を独立に制御する場合や、素子を完全に独立して制御する場合には、CMUTは必須となると考えられる。何故ならば、各素子への配線が必要になり、アレイ内の配線数は膨大な数になることが考えられるが、LSI加工技術を用いて作製できるので、微細な配線が可能であり、さらには超音波送受信部からの信号処理回路の1チップへの混載も、CMUTでは可能だからである。

【0010】

図1、図2を用いてCMUTアレイの基本的な構造および動作を説明する。

【0011】

図1はCMUTアレイの上面図である。203は下部電極、205は空洞部、207は上部電極、208は上部電極を結ぶ配線、210は空洞部205を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔210は、空洞部205に接続されている。101は、上部電極207へ電源供給するために下部電極と同層に設けたパッドへのパッド開口部であり、102はパッドと配線208を接続するプラグである。すなわち、プラグ102を介して上部電極207を結ぶ配線208とパッドが接続されている。103は下部電極203に電源供給するためのパッド開口部である。上部電極207および配線208と、下部電極203の間に、下部電極203および空洞部205を覆うように絶縁膜が形成されているが、空洞部205、下部電極203を示すために図示していない。

【0012】

図2(a)は、図1のA−A’方向の断面を示しており、図2(b)は図1のB−B’方向の断面を示している。図2(a)および図2(b)に示すように、半導体基板201に形成された絶縁膜202上に下部電極203が形成されている。下部電極203の上層には絶縁膜204を介して空洞部205が形成されている。空洞部205を覆うように絶縁膜206が形成され、絶縁膜206の上層に上部電極207と上部電極を結ぶ配線208が形成されている。上部電極207および配線208の上層には絶縁膜209と絶縁膜211が形成されている。また、絶縁膜206および絶縁膜209にはこれらの膜を貫通するウェットエッチング孔210が形成されている。このウェットエッチング孔210は、空洞部205を形成するために形成されたものであり、空洞部205の形成後、絶縁膜211によって埋め込まれている。

【0013】

図1および図2から明らかであるが、上部電極と下部電極が直交するために、上部電極を結ぶ配線は下部電極による段差部を乗り越える構造となる。

【0014】

以下に、超音波を発信する動作について説明する。上部電極207へ接続するパッド開口部101と、下部電極203へのパッド開口部103へ直流電圧と交流電圧を重畳すると、上部電極207と下部電極203の間に静電気力が働き、上部電極と下部電極が交わるクロスポイントのCMUTセルのメンブレンを構成する空洞部205上の上部電極207および絶縁膜206、209、211が印加した交流電圧の周波数で振動し、超音波を発信する。

【0015】

逆に、超音波を受信する場合は、デバイスの表面に到達した超音波の圧力により、空洞部205上の絶縁膜206、209、211および上部電極207が振動する。この振動により、上部電極207と下部電極203との間の距離が変化するため、電極間の電気容量の変化として超音波を検出できる。すなわち、電極間の距離が変化することにより、電極間の電気容量が変わり、電流が流れる。この電流を検知することにより超音波を検出することができる。

【0016】

上記動作原理からも明らかであるが、電極間の電圧印加に起因する静電力によるメンブレンの振動と、振動による電極間の電気容量変化を利用して超音波の発信および受信を行うので、電極間の電圧差の安定性、電極間距離やメンブレンの厚さの安定性が、デバイスの安定した動作や信頼性確保には重要な点となる。

【0017】

特許文献1では、下部電極としてイオン注入を行ったシリコン基板を用いたCMUTアレイが開示されている。しかし、この構造ではシリコン基板の抵抗が大きいために、CMUTアレイ内部での下部電極の電圧降下を抑制するためには、外部からの駆動電源供給をCMUTの直近に行う必要があり、アレイ状にCMUTを多数配置した場合、電源供給箇所も多数必要となる。

【0018】

特許文献2、3、4および非特許文献1には、CMUTアレイの下部電極に金属膜を使用する構造が示されている。特許文献2、3および4では、アルミニウム(Al)やタングステン(W)、銅(Cu)といった材料を用いた厚さ250nmから500nmの下部電極の例が開示され、非特許文献1ではクロムを材料にした厚さ150nmの下部電極の例が示されている。しかし、上記に示した金属膜を用いた下部電極であっても、CMUTアレイ内部での電圧降下を抑制するためには、500nm以上の厚さの下部電極が必須である。

【0019】

したがって、下部電極を各素子に分割することによる500nm以上の下部電極の段差が必然的に生じることになる。この段差を上部電極を結ぶ配線が乗り越える構造になるが、配線となる金属膜を形成する際に、段差部での金属膜のカバレッジが平坦部より低下し、段差部での金属膜の膜厚が薄くなってしまう。その結果、上部電極の抵抗上昇の原因となる。また、上部電極パターンを加工する際には、段差部の余分な金属膜を除去するために過剰なエッチングを行う必要があり、金属膜の下地膜が削れてしまうなどのダメージは入ってしまう。このことは、CMUTセルのメンブレンを構成する膜が薄くなることを意味し、CMUTセルの周波数特性変動の原因となる。さらに、下部電極と上部電極を絶縁する絶縁膜のカバレッジも、段差部では平坦部よりも低下するので、段差部での絶縁膜の厚さが薄くなることで絶縁耐性も低下し、デバイスの信頼性が低下する。

【0020】

また、空洞部による段差も上部電極を結ぶ配線が乗り越える構造になるので、下部電極による段差部と同様に、デバイス安定性や信頼性の低下に繋がる。特に、メンブレンを大きく振動させて、強い送信音を出す場合は、メンブレンが可動できる範囲を大きく確保する必要があり、したがって、空洞部の厚さを大きくする必要があるので、空洞部による段差の影響も無視できなくなる。

【0021】

そこで、本発明の目的は、下部電極を各素子に分割することによる段差や、空洞部による段差が生じても、上部電極の抵抗上昇、メンブレンへのダメージおよび上部電極と下部電極間の絶縁耐性低下を抑制する構造と製造方法を提供することにある。

【0022】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0023】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0024】

本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部を覆う第2絶縁膜と、(e)前記第2絶縁膜上に前記空洞部と重なるように配置された第2電極と、(f)前記第2電極に接続する配線を備え、前記第1電極の外周部と上面から見て重なる前記配線の幅が、前記第1電極の外周部と上面から見て重ならない前記配線の幅よりも太いことを特徴とするものである。

【0025】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部を覆う第2絶縁膜と、(e)前記第2絶縁膜上に前記空洞部と重なるように配置された第2電極と、(f)前記第2電極に接続する配線を備え、前記第1電極の外周部がテーパ角を持つことにより前記第1電極の段差が緩和されていること特徴とするものである。そして、前記第1電極による段差が500nm以上であること特徴とする。さらに、上面から見て、前記第1電極の外周部と重なる前記配線の幅が、上面から見て、前記第1電極の外周部と重ならない前記配線の幅よりも太いことを特徴とするものである。

【0026】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部を覆う第2絶縁膜と、(e)前記第2絶縁膜上に前記空洞部と重なるように配置された第2電極と、(f)前記第2電極に接続する配線を備え、前記第1電極の外周部に絶縁膜によるサイドウォールを形成することにより前記第1電極の段差が緩和されていること特徴とするものである。そして、前記第1電極による段差が500nm以上であること特徴とする。さらに、上面から見て、前記サイドウォールと重なる前記配線の幅が、上面から見て、前記サイドウォールと重ならない前記配線の幅よりも太いことを特徴とするものである。

【0027】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部を覆う第2絶縁膜と、(e)前記第2絶縁膜上に前記空洞部と重なるように配置された第2電極と、(f)前記第2電極に接続する配線を備え、前記第1電極による段差と前記空洞部による段差の一方あるいは両方が緩和されていることを特徴とするものである。

【0028】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極の間を埋める第1絶縁膜と、(c)前記第1電極および前記第1絶縁膜を覆う第2絶縁膜と、(d)前記第2絶縁膜上に前記第1電極と重なるように配置された空洞部と、(e)前記空洞部を覆う第3絶縁膜と、(f)前記第3絶縁膜上に前記空洞部と重なるように配置された第2電極と、(g)前記第2電極に接続する配線とを備え、前記第1電極と前記第1絶縁膜の表面が同じ高さに平坦化されていることを特徴とするものである。そして、前記第1電極の厚さが500nm以上であること特徴とする。

【0029】

また、本発明による超音波トランスデューサは、(a)第1電極と、(b)前記第1電極を覆う第1絶縁膜と、(c)前記第1絶縁膜上に前記第1電極と重なるように配置された空洞部と、(d)前記空洞部の間を埋める第2絶縁膜と、(e)前記空洞部および前記第2絶縁膜を覆う第3絶縁膜と、(f)前記第3絶縁膜上に前記空洞部と重なるように配置された第2電極と、(g)前記第2電極に接続する配線とを備え、前記空洞部と前記第2絶縁膜の表面が同じ高さに平坦化されていることを特徴とするものである。

【0030】

本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜を平坦化し、前記第1電極の表面を露出する工程と、(d)前記第1電極および前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(f)前記犠牲層および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(g)前記第3絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(h)前記第2電極に接続する配線を形成する工程と、(i)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(j)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(k)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(l)第5絶縁膜により前記開口部を埋め込み、前記空洞部を封止する工程とを備えることを特徴とするものである。そして、前記第1電極の厚さが500nm以上であること特徴とする。

【0031】

また、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(d)前記犠牲層および前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜を平坦化し、前記犠牲層の表面を露出する工程と、(f)前記第2絶縁膜および前記犠牲層を覆う第3絶縁膜を形成する工程と、(g)前記第3絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(h)前記第2電極に接続する配線を形成する工程と、(i)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(j)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(k)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(l)第5絶縁膜により前記開口部を埋め込み、前記空洞部を封止する工程とを備えることを特徴とするものである。

【0032】

さらに、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(d)前記犠牲層を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(f)前記第2電極に接続する配線を形成する工程と、(g)前記第2電極と前記配線および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(h)前記第2絶縁膜および前記第3絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(i)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(j)第4絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備え、前記配線を形成する工程において、上面から見て、前記第1電極の外周部と重なる前記配線の幅を、上面から見て、前記第1電極の外周部と重ならない前記配線の幅よりも太く形成することを特徴とするものである。

【0033】

また、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(d)前記犠牲層を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記犠牲層と重なる複数の第2電極を形成する工程と、(f)前記第2電極に接続する配線を形成する工程と、(g)前記第2電極と前記配線および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(h)前記第2絶縁膜および前記第3絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(i)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(j)第4絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備え、前記第1電極を形成する工程において、前記第1電極の外周部がテーパ角を持つように形成することを特徴とするものである。そして、前記第1電極の厚さが500nm以上であること特徴とする。さらに、前記配線を形成する工程において、上面から見て、前記第1電極の外周部と重なる前記配線の幅が、上面から見て、前記第1電極の外周部と重ならない前記配線の幅よりも太く形成することを特徴とするものである。

【0034】

また、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜をエッチングし、前記第1電極の外周部にサイドウォールを形成する工程と、(d)前記第1電極および前記サイドウォールを覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記第1電極と重なる犠牲層を形成する工程と、(f)前記犠牲層および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(g)前記第3絶縁膜上に前記犠牲層と重なる複数の第2電極を形成する工程と、(h)前記第2電極に接続する配線を形成する工程と、(i)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(j)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(k)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(l)第5絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備えることを特徴とするものである。そして、前記第1電極の厚さが500nm以上であること特徴とする。さらに、前記配線を形成する工程において、上面から見て前記サイドウォールと重なる前記配線の幅を、上面から見て前記サイドウォールと重ならない前記配線の幅よりも太く形成することを特徴とするものである。

【0035】

また、本発明による超音波トランスデューサの製造方法は、(a)第1絶縁膜をパターニングして第1窪みを形成する工程と、(b)前記第1窪みに第1導電膜を埋め込む工程と、(c)前記第1導電膜を、前記第1絶縁膜の表面が露出するまで平坦化し、前記第1絶縁膜に埋め込まれた第1電極を形成する工程と、(d)前記第1電極および前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(e)前記第2絶縁膜上に前記第1電極と重なるように犠牲層を形成する工程と、(f)前記犠牲層および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(g)前記第3絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(h)前記第2電極に接続する配線を形成する工程と、(i)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(j)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(k)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(l)第5絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備えることを特徴とするものである。そして、前記第1窪みの深さが500nm以上であること特徴とする。

【0036】

また、本発明による超音波トランスデューサの製造方法は、(a)導電膜をパターニングして第1電極を形成する工程と、(b)前記第1電極を覆う第1絶縁膜を形成する工程と、(c)前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(d)前記第2絶縁膜に前記第1絶縁膜に達する複数の第1窪みを形成する工程と、(e)前記第1窪みに犠牲層となる膜を埋め込む工程と、(f)前記犠牲層となる膜を前記第2絶縁膜の表面が露出するまで平坦化し、前記第2絶縁膜に埋め込まれた犠牲層を形成する工程と、(g)前記犠牲層および前記第2絶縁膜を覆う第3絶縁膜を形成する工程と、(h)前記第3絶縁膜上に前記犠牲層と重なる第2電極を形成する工程と、(i)前記第2電極に接続する配線を形成する工程と、(j)前記第2電極と前記配線および前記第3絶縁膜を覆う第4絶縁膜を形成する工程と、(k)前記第3絶縁膜および前記第4絶縁膜を貫通して前記犠牲層に達する開口部を形成する工程と、(l)前記開口部を利用して前記犠牲層を除去することにより空洞部を形成する工程と、(m)第5絶縁膜により前記開口部を埋め込み、空洞部を封止する工程とを備えることを特徴とするものである。

【発明の効果】

【0037】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0038】

下部電極および空洞部の段差を緩和することで、下部電極および空洞部の段差部での上部電極の膜厚低下を低減できるので抵抗の上昇を抑制できる。また、上部電極加工でのメンブレンへのダメージを低減することもできる。さらに、上部電極と下部電極間の絶縁耐性の低下も抑制できる構造と、その製造方法を提供することができる。

【図面の簡単な説明】

【0039】

【図1】本発明者らが検討した超音波トランスデューサの上面図である。

【図2】(a)は図1、図3のA−A’線で切断した断面図であり、(b)は図1、図3のB−B’線で切断した断面図である。

【図3】本発明の実施の形態1における超音波トランスデューサを示した上面図である。

【図4】(a)は図3のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図3のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図5】(a)は図4(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図4(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図6】(a)は図5(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図5(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図7】(a)は図6(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図6(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図8】(a)は図7(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図7(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図9】(a)は図8(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図8(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図10】(a)は図9(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図9(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図11】(a)は図10(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図10(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図12】本発明の実施の形態1における超音波トランスデューサを示した上面図である。

【図13】本発明の実施の形態1における超音波トランスデューサを示した上面図である。

【図14】本発明の実施の形態2における超音波トランスデューサを示した上面図である。

【図15】(a)は図14のA−A’線で切断した断面図であり、(b)は図14のB−B’線で切断した断面図である。

【図16】本発明の実施の形態3における超音波トランスデューサを示した上面図である。

【図17】(a)は図16のA−A’線で切断した断面図であり、(b)は図16のB−B’線で切断した断面図である。

【図18】(a)は図16のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図16のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図19】(a)は図18(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図18(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図20】(a)は図19(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図19(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図21】本発明の実施の形態4における超音波トランスデューサを示した上面図である。

【図22】(a)は図21のA−A’線で切断した断面図であり、(b)は図21のB−B’線で切断した断面図である。

【図23】(a)は図21のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図21のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図24】(a)は図23(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図23(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図25】(a)は図21のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図21のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図26】(a)は図25(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図25(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図27】(a)は図26(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図26(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図28】(a)は図27(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図27(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図29】本発明の実施の形態5における超音波トランスデューサを示した上面図である。

【図30】(a)は図29のA−A’線で切断した断面図であり、(b)は図29のB−B’線で切断した断面図である。

【図31】(a)は図29のA−A’線で切断した断面での超音波トランスデューサの製造工程を示した断面図であり、(b)は図29のB−B’線で切断した断面での超音波トランスデューサの製造工程を示した断面図である。

【図32】(a)は図31(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図31(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図33】(a)は図32(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図32(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図34】本発明の実施の形態6における超音波トランスデューサの断面図である。(a)は図1のA−A’線で切断した断面図であり、(b)は図1のB−B’線で切断した断面図である。

【図35】(a)は図34(a)で示した超音波トランスデューサの製造工程を示した断面図であり、(b)は図34(b)で示した超音波トランスデューサの製造工程を示した断面図である。

【図36】(a)は図35(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図35(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図37】(a)は図36(a)に続く超音波トランスデューサの製造工程を示した断面図であり、(b)は図36(b)に続く超音波トランスデューサの製造工程を示した断面図である。

【図38】本発明の実施の形態7における超音波トランスデューサを示した上面図である。

【図39】(a)は図38のA−A’線で切断した断面図であり、(b)は図38のB−B’線で切断した断面図である。

【図40】本発明の実施の形態8における超音波トランスデューサを示した上面図である。

【図41】(a)は図40のA−A’線で切断した断面図であり、(b)は図40のB−B’線で切断した断面図である。

【図42】本発明の実施の形態9における超音波トランスデューサを示した上面図である。

【図43】(a)は図42のA−A’線で切断した断面図であり、(b)は図42のB−B’線で切断した断面図である。

【発明を実施するための形態】

【0040】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0041】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

【0042】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

【0043】

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうではないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0044】

なお、平面図であっても理解を容易にするため、ハッチングを付す場合がある。

【0045】

下記の実施の形態の記載では、超音波トランスデューサの、上部電極の抵抗上昇の抑制、メンブレンへのダメージ低減、上下電極間の絶縁耐性の低下を抑制するという目的を、段差部での上部電極間を結ぶ配線幅を太くすること、段差部を緩和した構造とすることで実現している。

【0046】

(実施の形態1)

図3は本実施の形態1のCMUTアレイの上面図である。403は下部電極、412は空洞部、407は上部電極、408は上部電極を結ぶ配線、411は空洞部を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔411は、空洞部412に接続されている。301は、上部電極407へ電源供給するために下部電極と同層に設けたパッドへのパッド開口部であり、302はパッドと配線408を接続するプラグである。すなわち、プラグ302を介して上部電極407を結ぶ配線408とパッドが接続されている。303は下部電極403に電源供給するためのパッド開口部である。上部電極407および配線408と、下部電極403の間に、下部電極403および空洞部412を覆うように絶縁膜が形成されているが、空洞部412、下部電極403を示すために図示していない。図3のA−A’断面、B−B’断面はそれぞれ図2(a)、(b)と同様になる。

【0047】

本実施の形態1の特徴は、図3中の409に示すように、下部電極403の段差部での上部電極を結ぶ配線408の配線幅を段差部以外の配線幅よりも太くした点にある。このような構成にすることにより、上部電極407および配線408となる導電膜を堆積する際の段差部で、カバレッジが平坦部より低く、膜厚が薄くなっても、配線の抵抗上昇を抑制できる。すなわち、段差部において、配線409の膜厚が薄くなっても、配線409の配線幅を太くすることで、段差部における配線409の抵抗の上昇を抑制できる。配線408の配線幅に比べて配線409の配線幅は例えば倍程度に太くなっている。具体的には、例えば配線408の配線幅が3μm程度であるとすると、配線409の配線幅は6μm程度になっている。

【0048】

また、段差部のみの配線幅を太くすることで、下部電極403と上部電極を結ぶ配線408の重なり部が大幅に増えることはなく、下部電極403と配線408間の寄生容量の増加も抑制することができる。図3では、配線の太幅化を、対向する下部電極403の段差部間の全てで行っているが、段差部のみを太幅化してもよいことは自明である。特に下部電極403の抵抗を低くするため、下部電極403の厚さを500nm以上にすると、、下部電極403による段差が500nm以上になる。すると、上部電極407および配線408となる導電膜を堆積する際の段差部で、カバレッジが平坦部より低く、膜厚が薄くなることが顕在化する。したがって、本実施の形態1に示すように、下部電極403の段差部に形成される配線409の配線幅を段差部以外の領域に形成される配線408の配線幅より太くする構成は、下部電極403による段差が500nm以上である場合に特に有効である。

【0049】

次に、図面を用いて本実施の形態1に記載されたCMUTアレイの製造方法を説明する。図4〜図11中の(a)は、図3中のA−A’方向の断面を示しており、図4〜図11中の(b)は、図3中のB−B’方向の断面を示している。

【0050】

まず、図4(a)、(b)に示すように、半導体基板401上にプラズマCVD(Chemical Vapor Deposition)法でシリコン酸化膜による絶縁膜402を堆積し、その後、スパッタリング法で窒化チタン膜とアルミニウム合金膜と窒化チタン膜をそれぞれ100nm、600nm、100nm積層する。ここで、半導体基板401と絶縁膜402の間には、信号処理などを行なう集積回路を形成することも可能である。例えば、半導体基板401上にMISFET(Metal Insulator Semiconductor Field Effect Transistor)が形成され、このMISFET上に多層配線が形成される。そして、多層配線上に絶縁膜402が形成される。これらの集積回路は、通常の半導体製造技術を使用して形成される。

【0051】

その後、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極403を形成する。この下部電極403上にプラズマCVD法によりシリコン酸化膜による絶縁膜404を100nm堆積させる。

【0052】

次に、絶縁膜404の上面に多結晶シリコン膜をプラズマCVD法により200nm堆積する。そして、フォトリソグラフィ技術とドライエッチング技術により、下部電極403上に多結晶シリコン膜を残す。この残された部分が犠牲層405となり、その後の工程で空洞部となる。(図5(a)、(b))。

【0053】

続いて、犠牲層405、絶縁膜404を覆うように、プラズマCVD法によりシリコン酸化膜による絶縁膜406を200nm堆積する。(図6(a)、(b))。

【0054】

次に、CMUTの上部電極407および上部電極を結ぶ配線408を形成するため、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜の積層膜をそれぞれ50nm、300nm、50nm堆積する。そして、フォトリソグラフィ技術とドライエッチング技術により、上部電極407と配線408を形成する(図7(a)、(b))。このときに、下部電極403の段差部での配線409は、フォトリソグラフィのためのマスクで配線幅を太くしておくことで、追加工程なく段差部のみ配線幅を太くすることができる。

【0055】

次にプラズマCVD法により、シリコン窒化膜による絶縁膜410を絶縁膜406、上部電極407および配線408を覆うように500nm堆積する(図8(a)、(b))。続いて、絶縁膜410および406にフォトリソグラフィ技術とドライエッチング技術を使用して犠牲層405に到達するウェットエッチング孔411を形成する(図9(a)、(b))。

【0056】

その後、ウェットエッチング孔411を介して、犠牲層405を水酸化カリウムでウェットエッチングすることにより空洞部412を形成する(図10(a)、(b))。

【0057】

次に、ウェットエッチング孔411を埋め込むために、プラズマCVD法によりシリコン窒化膜による絶縁膜413を800nm堆積する。(図11(a)、(b))。このようにして、本実施の形態1におけるCMUTアレイを形成することができる。

【0058】

以上説明したように、本実施の形態1のCMUTアレイによれば、上部電極407および配線408となる導電膜を堆積する際の段差部でのステップカバレッジが平坦部より低く、膜厚が薄くなっても、下部電極403の段差部での上部電極を結ぶ配線408の配線幅を段差部以外の配線幅よりも太くすることで、配線の抵抗上昇を抑制できる。また、段差部のみの配線幅を太くすることで、下部電極403と上部電極を結ぶ配線408の重なり部が大幅に増えることはなく、下部電極と配線間の寄生容量の増加も抑制することができる。

【0059】

図3において示したCMUTアレイは、下部電極403と上部電極407のクロスポイントに2行1列のCMUTセルを配置した形態であるが、多数行多数列のCMUTセルを配置した場合でも同様である。図12には3行4列のCMUTセルをクロスポイントに配置した形態の上面図を示してある。この場合も、下部電極403の段差部での上部電極407を接続する配線409の幅を太くすることで同様の効果が得られる。また、図12では、下部電極403の段差部での配線409のそれぞれを太くしたが、同じ上部電極を結ぶ配線であれば、図13に示すように、下部電極403の段差部のみ一括して接続することで、下部電極403と配線409の寄生容量は増加するものの、それぞれの配線を太くする効果と同様の効果が得られる。

【0060】

なお、図3、図12、図13において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0061】

また、本実施の形態1として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜(Spin−on−Glass)あるいは金属膜などであってもよい。

【0062】

(実施の形態2)

本実施の形態2におけるCMUTアレイは下部電極による段差を緩和するために、下部電極の外周部をテーパ形状にしたことを特徴とするものである。

【0063】

図14は本実施の形態2のCMUTアレイの上面図である。1503は下部電極、1505は空洞部、1507は上部電極、1508は上部電極1507を結ぶ配線、1510は空洞部1505を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔1510は、空洞部1505に接続されている。1401は、上部電極1507へ電源供給するために下部電極1503と同層に設けたパッドへのパッド開口部であり、1402はパッドと配線1508を接続するプラグである。すなわち、プラグ1402を介して上部電極1507を結ぶ配線1508とパッドが接続されている。1403は下部電極1503に電源供給するためのパッド開口部である。下部電極1503の外周部にはテーパ部1512を形成している。上部電極1507および配線1508と、下部電極1503の間に空洞部1505、テーパ部1512および下部電極1503を覆うように絶縁膜が形成されているが、空洞部1505、下部電極1503、テーパ部1512を示すために図示していない。

【0064】

図15(a)は図14のA−A’方向の断面を示しており、図15(b)は図14のB−B’方向の断面を示している。図15(a)および図15(b)に示すように、半導体基板1501に形成された絶縁膜1502上に下部電極1503が形成されている。下部電極1503の側壁はテーパ形状1512にされている。下部電極1503の上層には絶縁膜1504を介して空洞部1505が形成されている。

【0065】

空洞部1505を囲むように絶縁膜1506が形成され、絶縁膜1506の上層に上部電極1507と上部電極を結ぶ配線1508が形成されている。

【0066】

上部電極1507および配線1508の上層には絶縁膜1509と絶縁膜1511が形成されている。また、絶縁膜1506および絶縁膜1509にはこれらの膜を貫通するウェットエッチング孔1510が形成されている。このウェットエッチング孔1510は、空洞部1505を形成するために形成されたものであり、空洞部1505の形成後、絶縁膜1511によって埋め込まれている。

【0067】

本実施の形態2の特徴は、図14および図15(a)、(b)に示すように、下部電極1503の外周部がテーパ形状になっている点にある。

【0068】

このような構成にすることにより、下部電極1503による段差が緩和され、配線1508の段差部でのステップカバレッジが向上し、配線の抵抗上昇および断線を抑制できる。特に、下部電極1503による段差が500nm以上あると、段差部でのステップカバレッジが一層低下するので、下部電極1503による段差が500nm以上ある場合に、段差部にテーパ部1512を設けることが有効である。

【0069】

また、上部電極1507および配線1508をパターニングする際に、下部電極1503による局所的な段差が緩和されているので、段差部の配線材料を除去するためのオーバーエッチング量も低減できる。つまり、オーバーエッチング量が多いと、上部電極1507の下層にある絶縁膜1506が削れることでCMUTセルのメンブレン膜厚が変化し、動作特性変動の原因となる。しかし、本実施の形態2で示した構造では、下部電極の側壁をテーパ形状に形成することで、局所的な段差を緩和しているので、オーバーエッチング量を減らすことができ、絶縁膜1506の削れ量が低減でき、動作安定性を向上させることができる。

【0070】

さらに、下部電極1503と上部電極1507を絶縁する絶縁膜1504、1506も、下部電極の側壁をテーパ形状にすることで下部電極段差部での膜厚低下が少なく、絶縁耐性の低下を抑制し、デバイスの信頼性を向上できる。

【0071】

また、前記実施の形態1で示したように、下部電極1503の側壁のテーパ部1512と重なる配線のみ配線幅を太くすれば、配線の抵抗上昇および断線を一層抑制できる。

【0072】

本実施の形態2におけるCMUTアレイの製造方法は、前記実施の形態1とほぼ同様であり、下部電極1503のパターニングの際に、側壁をテーパ形状にする点が異なる。

【0073】

下部電極1503の側壁にテーパ角を持たせるためには、ドライエッチング技術で下部電極1503をパターニングする場合、下部電極1503となる金属材料のエッチングガスに炭化水素などの堆積性のガスを混合することで行える。例えば、実施の形態1で示したように下部電極1503が窒化チタン膜とアルミニウム合金膜と窒化チタン膜を積層膜である場合、パターニングは塩素を含むエッチングガスが通常用いられるが、そこに、メタンやジフロロメタン等のガスを混合することで、制御よくテーパ形状にパターニングできる。また、下部電極1503のパターニングをウェットエッチング技術で行うことでも同様にテーパ形状を得ることができる。

【0074】

なお、図14において示したCMUTアレイは、下部電極1503と上部電極1507のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極をテーパ形状にパターニングすることにより同様の効果が得られる。

【0075】

また、図14において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0076】

また、本実施の形態2として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0077】

(実施の形態3)

本実施の形態3におけるCMUTアレイは下部電極による段差を緩和するために、下部電極の外周部にサイドウォールを設けたことを特徴とするものである。

【0078】

図16は本実施の形態のCMUTアレイの上面図である。1703は下部電極、1705は空洞部、1707は上部電極、1708は上部電極1707を結ぶ配線、1710は空洞部1705を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔1710は、空洞部1705に接続されている。1601は、上部電極1707へ電源供給するために下部電極1703と同層に設けたパッドへのパッド開口部であり、1602はパッドと配線1708を接続するプラグである。すなわち、プラグ1602を介して上部電極1707を結ぶ配線1708とパッドが接続されている。1603は下部電極1703に電源供給するためのパッド開口部である。下部電極1703の外周部にはサイドウォール1712が形成されている。上部電極1707および配線1708と、下部電極1703の間に空洞部1705、サイドウォール1712および下部電極1703を覆うように絶縁膜が形成されているが、空洞部1705、下部電極1703、サイドウォール1712を示すために図示していない。

【0079】

図17(a)は図16のA−A’方向の断面を示しており、図17(b)は図16のB−B’方向の断面を示している。図17(a)および図17(b)に示すように、半導体基板1701に形成された絶縁膜1702上に下部電極1703が形成されている。下部電極1703の側壁には絶縁膜によるサイドウォール1712が形成されている。下部電極1703およびサイドウォール1712の上層には絶縁膜1704を介して空洞部1705が形成されている。

【0080】

空洞部1705を囲むように絶縁膜1706を形成し、絶縁膜1706の上層に上部電極1707と上部電極を結ぶ配線1708が形成されている。

【0081】

上部電極1707および配線1708の上層には絶縁膜1709と絶縁膜1711が形成されている。また、絶縁膜1706および絶縁膜1709にはこれらの膜を貫通するウェットエッチング孔1710が形成されている。このウェットエッチング孔1710は、空洞部1705を形成するために形成されたものであり、空洞部1705の形成後、絶縁膜1711によって埋め込まれている。

【0082】

本実施の形態3の特徴は、図16および図17(a)、(b)に示すように、下部電極1703の外周部に絶縁膜によるサイドウォール1712を設けた点にある。

【0083】

このような構成にすることにより、下部電極1703による段差が緩和され、配線1708の段差部でのステップカバレッジが向上し、配線の抵抗上昇および断線を抑制できる。特に、下部電極1703による段差が500nm以上あると、段差部でのステップカバレッジが一層低下するので、下部電極1703による段差が500nm以上ある場合に、下部電極1703の外周部にサイドウォール1712を設けることが有効である。

【0084】

また、上部電極1707および配線1708をパターニングする際に、下部電極1703による局所的な段差が緩和されているので、段差部の配線材料を除去するためのオーバーエッチング量も低減できる。つまり、オーバーエッチング量が多いと、上部電極1707の下層にある絶縁膜1706が削れることでCMUTセルのメンブレン膜厚が変化し、動作特性変動の原因となる。しかし、本実施の形態3で示した構造では、下部電極の外周にサイドウォールを形成することで、局所的な段差を緩和しているので、オーバーエッチング量を減らすことができ、絶縁膜1706の削れ量が低減でき、動作安定性を向上させることができる。

【0085】

さらに、下部電極1703と上部電極1707を絶縁する絶縁膜1704、1706も、サイドウォール1712を形成することで下部電極1703の段差部における膜厚低下を少なくすることができ、絶縁耐性の低下を抑制し、デバイスの信頼性を向上できる。

【0086】

さらに、前記実施の形態1で示したように、サイドウォール1712と重なる配線のみの配線幅を太くすれば、配線の抵抗上昇および断線を一層抑制できる。

【0087】

本実施の形態3におけるCMUTアレイの製造方法は、前記実施の形態1とほぼ同様であり、下部電極1703の外周部にサイドウォール1712を形成する点が異なる。

【0088】

図18〜図20に下部電極形成後からサイドウォール形成までの製造方法を示す。各図の(a)は図16のA−A’断面、(b)は図16のB−B’断面を示している。

【0089】

まず、図18(a)、(b)に示すように、半導体基板1701上にプラズマCVD法でシリコン酸化膜による絶縁膜1702を形成した後に、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜をそれぞれ100nm、600nm、100nm積層し、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極1703を形成する。下部電極1703上にプラズマCVD法によりシリコン酸化膜による絶縁膜1901を600nm堆積させる。(図19(a)(b))。

【0090】

次に、シリコン酸化膜による絶縁膜1901をドライエッチング技術により下部電極1703の表面が露出するまで異方性エッチングすることで、下部電極1703の外周部にシリコン酸化膜よりなるサイドウォール1712を形成できる。(図20(a)(b))。これ以降の工程は前記実施の形態1と同様である。

【0091】

なお、図16において示したCMUTアレイは、下部電極1703と上部電極1707のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極の外周部にサイドウォールを設けることにより同様の効果が得られる。

【0092】

また、図16において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0093】

また、本実施の形態3として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0094】

(実施の形態4)

本実施の形態4におけるCMUTアレイは下部電極による段差を緩和するために、下部電極の上面で平坦化を行ったことを特徴とするものである。

【0095】

図21に本実施の形態4におけるCMUTアレイの上面図を示す。2203は下部電極、2206は空洞部、2208は上部電極、2209は上部電極2208を結ぶ配線、2211は空洞部2206を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔2211は、空洞部2206に接続されている。

【0096】

2101は、上部電極2208へ電源供給するために下部電極2203と同層に設けたパッドへのパッド開口部であり、2102はパッドと配線2209を接続するプラグである。すなわち、プラグ2102を介して上部電極2208を結ぶ配線2209とパッドが接続されている。

【0097】

2103は、下部電極2203に電源供給するためのパッド開口部である。2204は絶縁膜であり、下部電極2203の隙間に埋め込まれている。上部電極2208および配線2209と、下部電極2203の間に空洞部2206および下部電極2203を覆うように絶縁膜が形成されているが、空洞部2206、下部電極2203、および絶縁膜2204を示すために図示していない。

【0098】

図22(a)は図21のA−A’方向の断面を示しており、図22(b)は図21のB−B’方向の断面を示している。

【0099】

図22(a)および図22(b)に示すように、半導体基板2201に形成された絶縁膜2202上に下部電極2203が形成されている。下部電極2203の間には、絶縁膜2204が埋め込まれて、下部電極2203の上面と絶縁膜2204の上面の高さが一致するように平坦化されている。下部電極2203と絶縁膜2204の上層には絶縁膜2205が形成され、下部電極2203上には絶縁膜2205を介して空洞部2206が形成されている。空洞部2206を囲むように絶縁膜2207が形成され、絶縁膜2207の上層に上部電極2208および上部電極を結ぶ配線2209が形成されている。上部電極2208および配線2209の上層には絶縁膜2210と絶縁膜2212が形成されている。また、絶縁膜2210および絶縁膜2207にはこれらの膜を貫通するウェットエッチング孔2211が形成されている。このウェットエッチング孔2211は、空洞部2206を形成するために形成されたものであり、空洞部2206の形成後、絶縁膜2212によって埋め込まれている。

【0100】

本実施の形態4の特徴は、図21、図22(a)、(b)に示すように下部電極2203の間を絶縁膜2204で埋め込んで、平坦化を行った点にある。

【0101】

このような構成にすることにより、下部電極2203による段差がなくなり、上部電極2208を結ぶ配線2209の段差部でのカバレッジの低下が無く、配線の抵抗上昇および断線を抑制できる。特に、下部電極2203による段差が500nm以上あると、段差部でのステップカバレッジが一層低下するので、下部電極2203による段差が500nm以上ある場合に、下部電極2203の間に絶縁膜2204を埋め込んで平坦化することが有効である。

【0102】

また、上部電極2208をパターニングする際に、下部電極2203による段差部が無いために配線材料をエッチングするためのオーバーエッチング量も低減できる。つまり、オーバーエッチング量が多いと、上部電極2208の下層にある絶縁膜2207が削れることでCMUTセルのメンブレン膜厚が変化し、動作特性変動の原因となる。しかし、本実施の形態4で示した構造では、下部電極の隙間を絶縁膜で埋め込み、平坦化しているので、段差が無くなり、オーバーエッチング量を減らすことができる。すなわち、絶縁膜2207の削れ量が低減でき、動作安定性を向上させることができる。

【0103】

さらに、下部電極2203と上部電極2208を絶縁する絶縁膜2205、2207も、下部電極2203による段差が無いことから、絶縁耐性が低下せず、デバイスの信頼性を向上できる。

【0104】

本実施の形態4におけるCMUTアレイの製造方法は、前記実施の形態1とほぼ同様であり、下部電極の間に絶縁膜を埋め込んで平坦化する点が異なる。

【0105】

図23、図24には下部電極の間を埋め込む絶縁膜の形成後から絶縁膜の平坦化までを示してある。各図の(a)は図21のA−A’断面、(b)は図21のB−B’断面を示している。

【0106】

まず、図23(a)、(b)に示すように、半導体基板2201上にプラズマCVD法によりシリコン酸化膜による絶縁膜2202を形成し、その後、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜を100nm、600nm、100nm積層した後に、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極2203を形成する。下部電極2203上にプラズマCVD法によりシリコン酸化膜による絶縁膜2301を1400nm堆積させる。

【0107】

次に、シリコン酸化膜による絶縁膜2301をCMP(Chemical Mechanical Polishing)技術により、下部電極2203の表面が露出するまで平坦化を行うことで、下部電極の間に埋め込まれ平坦化されたシリコン酸化膜による絶縁膜2204を形成することができる。(図24(a)(b))。これ以降の工程は前記実施の形態1と同様である。

【0108】

本実施の形態4ではシリコン酸化膜による絶縁膜2301を下部電極2203の表面が露出するまでCMP技術により平坦化を行ったが、下部電極2203の表面が露出する直前までCMP技術により平坦化を行い、その後、ドライエッチング技術により、下部電極2203の表面が露出するまでシリコン酸化膜による絶縁膜2301をエッチングしても同様の形状が得られる。

【0109】

シリコン酸化膜の平坦化を精度よく行うために、図25〜図28に示すように、CMP技術による平坦化プロセスの停止膜を挿入してもよい。各図の(a)は図21のA−A’断面、(b)は図21のB−B’断面を示している。図25(a)、(b)に示すように、下部電極2203を形成後に、平坦化CMPプロセスの停止膜として、プラズマCVD法によりシリコン窒化膜による絶縁膜2501を200nm形成する。その後、プラズマCVD法によりシリコン酸化膜による絶縁膜2601をシリコン窒化膜による絶縁膜2501上に1400nm堆積する。(図26(a)、(b))。引き続き、シリコン酸化膜による絶縁膜2601をCMP技術によりシリコン窒化膜による絶縁膜2501の上面が露出するまで研磨することにより平坦化を行う。(図27(a)、(b))。このとき、シリコン酸化膜とシリコン窒化膜のCMPでの研磨速度比が2〜3であるので、シリコン窒化膜による絶縁膜2501上面で研磨を制御よく停止することが可能である。その後、シリコン酸化膜による絶縁膜2601とシリコン窒化膜による絶縁膜2501をドライエッチングにより等速エッチングすることにより、下部電極2203の表面を露出させ、下部電極の間が平坦化された構造を形成することができる。(図28(a)、(b))。

【0110】

さらに、本実施の形態4では、下部電極2203の間を埋め込む絶縁膜2204をプラズマCVD法で形成したが、塗布法によりSOG膜を埋め込んでもよい。その場合、SOG膜埋め込み後、ドライエッチングによって、下部電極の表面が露出するまでエッチバックを行うことにより、図24や図28と同様の平坦化された構造を得ることができる。

【0111】

また、ダマシン法による埋め込み配線で下部電極を形成しても、同様の下部電極の上面で平坦化された構造を得ることができる。その場合は、絶縁膜にエッチングで予め溝形状を形成しておき、下部電極となる材料をこの溝に埋め込み、溝からはみ出した余分な下部電極材料を研磨し、除去することで実現できる。

【0112】

なお、図21において示したCMUTアレイは、下部電極2203と上部電極2208のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極の上面で平坦化を行うことにより同様の効果が得られる。

【0113】

また、図21において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0114】

また、本実施の形態4として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0115】

(実施の形態5)

本実施の形態5におけるCMUTアレイは下部電極による段差を緩和するために、下部電極の上面で平坦化を行い、かつ平坦化のためのダミーパターンを下部電極と同層に形成することを特徴とするものである。

【0116】

図29に本実施の形態5のCMUTアレイの上面図を示す。3003は下部電極、3007は空洞部、3009は上部電極、3010は上部電極3009を結ぶ配線、3012は空洞部3007を形成するためのウェットエッチング孔である。すなわち、ウェットエッチング孔3012は、空洞部3007に接続されている。

【0117】

2901は、上部電極3009へ電源供給するために下部電極3003と同層に設けたパッドへのパッド開口部であり、2902はパッドと配線3010を接続するプラグである。すなわち、プラグ2902を介して上部電極3009を結ぶ配線3010とパッドが接続されている。2903は下部電極3003に電源供給するためのパッド開口部である。下部電極3003の間に平坦化のためのダミーパターン3004が形成されている。3005はダミーパターン3004と下部電極3003の隙間に埋め込んだ絶縁膜である。

【0118】

上部電極3009および配線3010と、下部電極3003の間に空洞部3007、ダミーパターン3004、絶縁膜3005および下部電極3003を覆うように絶縁膜が形成されているが、空洞部3007、下部電極3003、ダミーパターン3004、絶縁膜3005を示すために図示していない。

【0119】

図30に本実施の形態5におけるCMUTアレイの断面を示す。図30(a)は図29のA−A’方向の断面を示しており、図30(b)は図29のB−B’方向の断面を示している。

【0120】

図30(a)および図30(b)に示すように、半導体基板3001に形成された絶縁膜3002上に下部電極3003が形成されている。平坦化のためのダミーパターン3004も下部電極3003と同時に形成している。つまり、下部電極3003とダミーパターン3004は同一の高さで形成されている。

【0121】

下部電極3003とダミーパターン3004の間には、絶縁膜3005が埋め込まれ、下部電極3003およびダミーパターン3004の上面と絶縁膜3005の上面の高さが一致するように平坦化されている。絶縁膜3005は、下部電極3003とダミーパターン3004とを電気的に絶縁するために設けられている。

【0122】

下部電極3003、ダミーパターン3004および絶縁膜3005の上層には絶縁膜3006が形成され、下部電極3003上には絶縁膜3006を介して空洞部3007が形成されている。空洞部3007を囲むように絶縁膜3008が形成され、絶縁膜3008の上層に上部電極3009および上部電極を結ぶ配線3010が形成されている。上部電極3009および配線3010の上層には絶縁膜3011と絶縁膜3013が形成されている。また、絶縁膜3011および絶縁膜3008にはこれらの膜を貫通するウェットエッチング孔3012が形成されている。このウェットエッチング孔3012は、空洞部3007を形成するために形成されたものであり、空洞部3007の形成後、絶縁膜3013によって埋め込まれている。

【0123】

本実施の形態5の特徴は、図29、図30(a)、(b)に示すように下部電極3003の間にダミーパターン3004を設けて、下部電極3003とダミーパターン3004の隙間に絶縁膜3005で埋め込み、平坦化した点にある。

【0124】

このような構成にすることにより、下部電極3003による段差の平坦化のためのCMPプロセスでの平坦性を一層向上させることができる。つまり、ダミーパターン3004が無いと、絶縁膜3005のCMP研磨時に、ディッシングと呼ばれる現象によって、下地に下部電極3003が存在しない領域の絶縁膜3005の落ち込み量が多くなってしまう可能性がある。しかし、本実施の形態5で示した構造では、ダミーパターン3004によって、絶縁膜3005のCMPによる平坦性が向上し、下部電極3003による段差を一層緩和することができるので、配線3010の抵抗上昇および断線を抑制できる。すなわち、下部電極3003の間に、下部電極3003と同じ材料から構成されているダミーパターン3004を形成することにより、ダミーパターン3004を形成しない場合のディッシングを防止することができる。特に、下部電極3003による段差が500nm以上あると、段差部でのステップカバレッジが一層低下するので、下部電極3003による段差が500nm以上ある場合に、下部電極3003の間にダミーパターン3004および絶縁膜3005を埋め込んで平坦化することが有効である。

【0125】

また、上部電極3009をパターニングする際のオーバーエッチング量も低減でき、絶縁膜3008の削れ量が低減でき、動作安定性を向上させることができる。

【0126】

さらに、下部電極3003と上部電極3009を絶縁する絶縁膜3006、3008も、下部電極3003による段差が無いことから、絶縁耐性が低下せず、デバイスの信頼性を向上できる。

【0127】

本実施の形態5におけるCMUTアレイの製造方法は、前記実施の形態4とほぼ同様であり、下部電極と同層にダミーパターンを形成する点が異なる。

【0128】

図31〜図33は下部電極と平坦化のためのダミーパターン形成と、下部電極の間を埋め込む絶縁膜の形成後から絶縁膜の平坦化までの製造方法を示してある。各図の(a)は図29のA−A’方向の断面、(b)は図29のB−B’方向の断面を示している。

【0129】

まず、図31(a)、(b)に示すように、半導体基板3001上にプラズマCVD法によりシリコン酸化膜による絶縁膜3002を形成する。その後、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜をそれぞれ100nm、600nm、100nm積層した後に、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極3003を形成する。このときに、平坦化のためのダミーパターン3004も同時に形成する。下部電極3003とダミーパターン3004上にプラズマCVD法によりシリコン酸化膜による絶縁膜3005を1400nm堆積させる。(図32(a)、(b))。

【0130】

次に、シリコン酸化膜による絶縁膜3005をCMP技術により下部電極3003およびダミーパターン3004の表面が露出するまで平坦化を行うことで、下部電極とダミーパターンの間に埋め込まれ、平坦化されたシリコン酸化膜による絶縁膜3005の構造を形成することができる。(図33(a)(b))。これ以降の工程は前記実施の形態4と同様である。

【0131】

本実施の形態5ではシリコン酸化膜を下部電極3003とダミーパターン3004の表面が露出するまでCMP技術により平坦化を行ったが、下部電極3003とダミーパターン3004の表面が露出する直前までCMP技術により平坦化を行い、その後、ドライエッチング技術により、下部電極3003とダミーパターン3004の表面が露出するまでシリコン酸化膜をエッチングしても同様の形状が得られる。

【0132】

また、シリコン酸化膜の平坦化を精度よく行うために、CMPによる平坦化プロセスの停止膜を、下部電極3003とダミーパターン3004の上層に挿入してもよい。

【0133】

さらに、本実施の形態5では、下部電極3003とダミーパターン3004の隙間を埋め込む絶縁膜3005をプラズマCVD法で形成したが、塗布法によりSOG膜を埋め込んでもよい。その場合、SOG膜を塗布することにより下部電極3003とダミーパターン3004の隙間を埋め込んだ後、ドライエッチングによって、下部電極3003とダミーパターン3004の表面が露出するまでエッチバックを行うことにより、図33と同様の平坦化された構造を得ることができる。

【0134】

また、ダマシン法による埋め込み配線で下部電極3003を形成しても、同様の平坦化された構造を得ることができる。その場合は、絶縁膜にエッチングにより予め下部電極用の溝とダミーパターン用の溝を形成しておき、下部電極3003となる材料をこれらの溝に埋め込み、溝からはみ出した余分な下部電極材料を研磨し、除去することで実現できる。

【0135】

なお、図29において示したCMUTアレイは、下部電極3003と上部電極3009のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、下部電極の上面で平坦化を行い、かつ平坦化のためのダミーパターンを下部電極と同層に形成することにより同様の効果が得られる。

【0136】

また、図29において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0137】

また、本実施の形態5として示したCMUTセルを構成する材料は、その組み合わせの一つを示したものである。犠牲層の材料も、犠牲層の周りを囲む材料とのウェットエッチング選択性が確保することができればよい。したがって、多結晶シリコン膜の他に、SOG膜あるいは金属膜などであってもよい。

【0138】

(実施の形態6)

本実施の形態6におけるCMUTアレイは下部電極および空洞部による段差を緩和するために、空洞部上で平坦化を行うことを特徴とするものである。

【0139】

本実施の形態6のCMUTアレイ上面図は、電極や空洞部の配置に関して、図1と同様であるので、図34に本実施の形態6におけるCMUTアレイの断面を示し説明する。図34(a)は図1のA−A’断面を示しており、図34(b)は図1のB−B’断面を示している。

【0140】

図34(a)および図34(b)に示すように、半導体基板201に形成された絶縁膜202上に下部電極203が形成されている。下部電極203上には絶縁膜204を介して空洞部205が形成されている。絶縁膜204と空洞部205を覆うように絶縁膜3401を形成し、空洞部の上面と同じ高さになるように絶縁膜3401を平坦化している。

【0141】

空洞部205および絶縁膜3401を覆うように絶縁膜206を形成し、絶縁膜206の上層に上部電極207と上部電極を結ぶ配線208が形成されている。上部電極207および配線208の上層には絶縁膜209と絶縁膜211が形成されている。また、絶縁膜209および絶縁膜206にはこれらの膜を貫通するウェットエッチング孔210が形成されている。このウェットエッチング孔210は、空洞部205を形成するために形成されたものであり、空洞部205の形成後、絶縁膜211によって埋め込まれている。

【0142】

本実施の形態6の特徴は、図34(a)、(b)に示すように空洞部205の上面で絶縁膜3401を平坦化した点にある。

【0143】

このような構成にすることにより、下部電極203による段差とともに、空洞部205による段差も一括して緩和することができ、上部電極を結ぶ配線208が段差の影響を受けることなく、配線の抵抗上昇および断線を抑制できる。

【0144】

また、上部電極207をパターニングする際に、段差が無いために、配線材料をエッチングするためのオーバーエッチング量も低減できる。つまり、オーバーエッチング量が多いと、上部電極207の下層にある絶縁膜206が削れることでCMUTセルのメンブレン膜厚が変化し、動作特性変動の原因となるが、本実施の形態6で示した構造では、絶縁膜206の削れ量が低減できるので、動作安定性を向上させることができる。

【0145】

さらに、図34(a)に示すように、配線208は平坦化された絶縁膜206上に配置されるので、下部電極との絶縁耐性が低下せず、デバイスの信頼性を向上できる。

【0146】

本実施の形態6におけるCMUTアレイの製造方法は、前記実施の形態1とほぼ同様であり、空洞部上面で平坦化を行った点が異なる。

【0147】

図35〜図37は犠牲層形成と、その後の絶縁膜埋め込み、絶縁膜平坦化までを示している。各図の(a)は図1のA−A’方向の断面、(b)は図1のB−B’方向の断面に対応している。

【0148】

まず、図35(a)、(b)に示すように、半導体基板201上にプラズマCVD法によりシリコン酸化膜による絶縁膜202を形成した後、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜を100nm、600nm、100nm積層した後に、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極203を形成する。この下部電極203上にプラズマCVD法によりシリコン酸化膜による絶縁膜204を100nm堆積させる。次に、シリコン酸化膜による絶縁膜204の上面に多結晶シリコン膜をプラズマCVD法により200nm堆積する。そして、フォトリソグラフィ技術とドライエッチング技術により、多結晶シリコン膜を残す。この残された部分が犠牲層3501となり、その後の工程で図34の空洞部205となる。

【0149】

次に、犠牲層3501およびシリコン酸化膜による絶縁膜204を覆うようにプラズマCVD法でシリコン酸化膜による絶縁膜3401を1400nm堆積させる。(図36(a)、(b))。

【0150】

その後、CMP技術により、犠牲層3501の上面が露出するまで、シリコン酸化膜による絶縁膜3401を研磨することで、犠牲層上面で平坦化された構造を得ることができる。(図37(a)、(b))。その後の工程は前記実施の形態1と同様である。

【0151】

本実施の形態6では、シリコン酸化膜による絶縁膜3401を犠牲層3501の上面が露出するまでCMP技術により平坦化を行ったが、犠牲層3501の上面が露出する直前までCMP技術により平坦化を行い、その後、ドライエッチング技術により、犠牲層3501の上面が露出するまでシリコン酸化膜による絶縁膜3401をエッチングしても同様の構造が得られる。

【0152】

また、シリコン酸化膜による絶縁膜3401の平坦化を精度よく行うために、CMPによる平坦化プロセスの停止膜を、犠牲層3501と絶縁膜204の上層に挿入してもよい。その場合、絶縁膜3401の研磨を平坦化プロセス停止膜で精度よく停止した後に、犠牲層3501の上面が露出するまで、ドライエッチングによって停止膜および絶縁膜3401を等速エッチングすることで、同様の平坦化された構造を得ることができる。

【0153】

さらに、本実施の形態6では、平坦化を行う絶縁膜3401をプラズマCVD法で形成したが、塗布法によりSOG膜を埋め込んでもよい。その場合、SOG膜を塗布した後に、ドライエッチングによって、犠牲層の上面が露出するまでエッチバックを行うことにより、図37と同様の平坦化された構造を得ることができる。

【0154】

なお、図1において示したCMUTアレイは、下部電極203と上部電極207のクロスポイントに2行1列のCMUTセルを配置した形態であるが、前記実施の形態1で示したように、多数行多数列のCMUTセルを配置した場合でも、空洞部上で平坦化を行うことにより同様の効果が得られる。

【0155】

また、図1において、CMUTセルは六角形の形状をしているが、形状はこれに限らず、例えば、円形形状をしていてもよい。

【0156】