送信ドライバ回路

【課題】信号の伝送速度が速い差動通信においても、コモンモード電圧の発生を適切に抑制できる送信ドライバ回路を提供する。

【解決手段】レベルホールド回路3は、通信信号出力部2が差動信号の電圧レベルを変化させる際に伝送線路5に発生するコモンモード電圧の変化を検出し、その検出レベルをレベルホールドする。そして、信号処理回路4は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整する。

【解決手段】レベルホールド回路3は、通信信号出力部2が差動信号の電圧レベルを変化させる際に伝送線路5に発生するコモンモード電圧の変化を検出し、その検出レベルをレベルホールドする。そして、信号処理回路4は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一対の信号線により差動信号を伝送する伝送線路に接続され、その伝送線路を介して信号を送信するための送信ドライバ回路に関する。

【背景技術】

【0002】

一対の信号線により差動信号を伝送する伝送線路については、送信ドライバ回路が一方の信号線(+)の電位を上昇させると同時に他方の信号線(−)の電位を低下させるようにドライブすることで差動信号を伝送する。この時、信号線(+)の電位を上昇させるタイミングと信号線(−)の電位を低下させるタイミングとの間にズレが生じて双方の電位の変化が非対称になると、伝送線路上にコモンモード電圧が発生してノイズとなる。

【0003】

このようなノイズの発生を防止する従来技術として、例えば特許文献1には、信号線VH,VLのそれぞれの電位変化の対称性が崩れた状態に応じて発生する電流を送信ドライバ回路にフィードバックさせることで、信号線VH,VLをそれぞれドライブするスイッチング素子をスイッチングさせるタイミングを調整し、コモンモード電圧の発生を抑制する技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−260799号公報(図1参照)

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1の技術は、伝送線路に発生するコモンモード電圧を検出してから、電流をフィードバックさせるまでにある程度の時間を要するため、例えばFlexRay(登録商標)のように伝送線路を高速でスイッチングする差動通信では、リアルタイムでのフィードバック制御が間に合わず、コモンモード電圧の発生を抑制することができないという問題がある。

【0006】

本発明は上記事情に鑑みてなされたものであり、その目的は、信号の伝送速度が速い差動通信においても、コモンモード電圧の発生を適切に抑制できる送信ドライバ回路を提供することにある。

【課題を解決するための手段】

【0007】

請求項1記載の送信ドライバ回路によれば、コモンモード検出手段は、信号出力部が差動信号の電圧レベルを変化させる際に伝送線路に発生するコモンモード電圧又は電流(以下、説明の都合上「コモンモード電圧」とのみ称す)の変化を検出し、その検出レベルをレベルホールドする。そして、制御部は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、信号出力部による電圧の出力状態を調整する。このように構成すれば、制御部が、コモンモード電圧の発生状態に応じてフィードバック制御を行うことで、差動信号を送信する毎にコモンモード電圧を順次低減させることができ、差動信号を高速に伝送する場合でもコモンモード電圧を確実に低減することができるので、ノイズの発生を抑制することが可能となる。

【0008】

請求項2記載の送信ドライバ回路によれば、制御部は、コモンモード電圧の検出レベルが上限基準値を上回ると、信号線の一方の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は信号線の他方の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整する。この場合、信号線の電圧レベルをハイからローに変化させるタイミングが適正なタイミングよりも遅いか、または信号線の電圧レベルをローからハイに変化させるタイミングが適正なタイミングよりも速くなっていることで、コモンモード電圧は上限基準値を上回る山型の波形となっている。したがって、上記の各タイミングをそれぞれ逆方向に変化させるように調整すれば、山型波形のコモンモード電圧を低減できる。

【0009】

一方、制御部は、コモンモード電圧の検出レベルが下限基準値を下回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより速くするように調整する。この場合、信号線の電圧レベルをハイからローに変化させるタイミング,または信号線の電圧レベルをローからハイに変化させるタイミングが山型の場合と逆になっていることで、コモンモード電圧は下限基準値を下回る谷型の波形となっている。したがって、上記の各タイミングをそれぞれ逆方向に変化させるように調整すれば、谷型波形のコモンモード電圧を低減できる。

【0010】

請求項3記載の送信ドライバ回路によれば、制御部は、検出レベルと上限基準値との差又は検出レベルと下限基準値との差に応じて、信号出力部による電圧の出力状態を調整する。すなわち、信号出力部による電圧の出力状態の調整量は、コモンモード電圧の検出レベルと基準値との差に応じて決まるので、コモンモード電圧を低減するための調整をより短時間に完了することができる。

【0011】

請求項4記載の送信ドライバ回路によれば、制御部は、検出レベルが上限基準値以内であり、且つ下限基準値以内である場合は、以降に自身の動作を停止させる。この場合、コモンモード電圧が発生しているとしても許容範囲内にあると考えられるので、その時点での信号出力部による電圧の出力状態を維持すれば良く、以降に制御部が調整を行う必要はない。したがって、制御部の動作を停止させて消費電力を低減することができる。

【0012】

請求項5記載の送信ドライバ回路によれば、制御部は、コモンモード検出手段による検出レベルを、オフセット検出手段により検出された差動信号電圧のDCオフセットレベルに基づき補正した値を上限基準値及び下限基準値と比較する。すなわち、伝送線路の信号線に実際に付与されているハイ,ローレベルの電圧の状態によっては、DCオフセットが発生している場合がある。そこで、制御部が、コモンモード検出手段による検出レベルをDCオフセットレベルに基づき補正すれば、コモンモード電圧の発生状態をより正確に検出することができる。

【0013】

請求項6記載の送信ドライバ回路によれば、コモンモード検出手段は、コモンモード電圧の微分値を検出し、制御部は、その微分値の検出レベルを上限基準値及び下限基準値と比較する。このように構成すれば、コモンモード電圧の変化率の大きさを検出できるので、請求項5のようにDCオフセットレベルを検出して補正する必要が無くなる。

【0014】

請求項7記載の送信ドライバ回路によれば、制御部は、ピークホールド手段によって検出されたコモンモード電圧のピーク値を上限基準値と比較すると共に、ボトムホールド手段によって検出されたコモンモード電圧のボトム値を下限基準値と比較する。したがって、コモンモード電圧が変化した場合の波形のピーク値,ボトム値を検出して、コモンモード電圧が発生している場合の波形振幅の大きさを正確に捉えることができる。

【0015】

請求項8記載の送信ドライバ回路によれば、制御部は、ピーク値が上限基準値を上回ると共にボトム値が下限基準値を下回ると両者の平均値を求め、その平均値が、一対の信号線間の中間基準電位よりも高いか或いは低いかに応じて、コモンモード電圧を低減するための調整方向を決定する。すなわち、このケースでは、コモンモード電圧の波形が正側と負側とに大きなピークを有する山谷型となっているので、両者の平均値を中間基準電位と比較した結果に応じて調整方向を決定すれば、ノイズの発生原因としてより影響が大きい方の波形振幅を低減するように調整できる。

【0016】

請求項9記載の送信ドライバ回路によれば、第1計時手段は、信号出力部が差動信号の電圧レベルを変化させる際に、伝送線路の一方の電位が低下を開始した時点から計時を開始し、第2計時手段は、伝送線路の他方の電位が上昇を開始した時点から計時を開始し、それぞれの伝送線路の電位が互いに等しくなった時点で計時を停止させて第1時間及び第2時間をそれぞれ計時する。制御部は、第1時間と第2時間との差である第1時間差を求めると、第1時間差が正であれば第1時間差と第1基準値とを比較し、第1時間差が負であれば第2時間と第1時間との差である第2時間差を求めて第2基準値とを比較する。その結果、第1時間差が第1基準値を上回るか又は第2時間差が第2基準値を上回ると、次回の信号送信時に発生するコモンモード電圧又は電流を低減するように、信号出力部による電圧の出力状態を調整する。

【0017】

すなわち、第1時間と第2時間とが等しい場合は、伝送線路の一方の電位が低下する速度と、伝送線路の他方の電位が上昇する速度とが等しくなっているのでコモンモード電圧は発生せず、第1時間と第2時間とが異なればコモンモード電圧が発生する。そして、第1時間差(>0)が第1基準値を上回った場合の波形は山型であり、第2時間差(>0)が第2基準値を上回っていれば波形は谷型であるから、それぞれの波形に応じて信号出力部による電圧の出力状態をフィードバック制御すれば、コモンモード電圧を低減するように調整できる。

【0018】

請求項10記載の送信ドライバ回路によれば、制御部は、第1時間差が第1基準値を上回ると、信号線の一方の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は信号線の他方の電圧レベルをローからハイに変化させるタイミングをより速くするように調整する。また、第2時間差が第2基準値を上回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整する。このように調整すれば、請求項2と同様にして、コモンモード電圧の波形に応じて当該電圧を低減するよう調整できる。

【0019】

請求項11記載の送信ドライバ回路によれば、制御部は、第1時間差と第1基準値との差又は第2時間差と第2基準値との差とに応じて、信号出力部による電圧の出力状態を調整する。したがって、請求項3と同様に、コモンモード電圧を低減するための調整を、より短時間に完了することができる。

【0020】

請求項12記載の送信ドライバ回路によれば、制御部は、第1時間差が第1基準値以内であり、又は第2時間差が第2基準値以内である場合は、以降に自身の動作を停止させる。したがって、請求項4と同様に、制御部が調整を行う必要はない場合に動作を停止させて消費電力を低減することができる。

【0021】

請求項13記載の送信ドライバ回路によれば、信号出力部は、高電位点又は低電位点と信号線との間に接続される駆動用半導体スイッチング素子をスイッチングさせて差動信号の電圧レベルを変化させ、また、高電位点又は低電位点と駆動用半導体スイッチング素子の制御端子との間に接続される制御用半導体スイッチング素子をスイッチングさせて、前記制御端子に出力する制御電圧を変化させる。そして、高電位点又は低電位点と、制御用半導体スイッチング素子との間に接続される抵抗素子の抵抗値を調整するので、これにより、駆動用半導体スイッチング素子の制御端子に通電する経路の抵抗値を変化させて、信号線の電圧レベルを変化させるタイミングを変更することができる。

【0022】

請求項14記載の送信ドライバ回路によれば、信号出力部は、高電位点又は低電位点と信号線との間に接続される半導体スイッチング素子をスイッチングさせて差動信号の電圧レベルを変化させ、高電位点又は低電位点と、半導体スイッチング素子との間に接続される抵抗素子の抵抗値を調整可能に構成されている。これにより、半導体スイッチング素子が信号線のレベルをハイ,ロー間で変化させる場合に、信号線と高電位点又は低電位点との間で通電する経路の抵抗値を変化させて、信号線の電圧レベルを変化させるタイミングを変更することができる。

【0023】

請求項15記載の送信ドライバ回路によれば、信号出力部は、高電位点又は低電位点と信号線との間に接続される半導体スイッチング素子をスイッチングさせて差動信号の電圧レベルを変化させ、制御信号の入力端子と、半導体スイッチング素子の制御端子との間に接続される複数個の遅延素子を備え、複数個の遅延素子の直列接続数を変更可能に構成されている。このように構成すれば、制御信号が半導体スイッチング素子の制御端子に入力される経路の遅延時間を変化させて、信号線の電圧レベルを変化させるタイミングを変更することができる。

【図面の簡単な説明】

【0024】

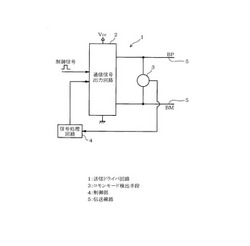

【図1】第1実施例であり、送信ドライバ回路の構成を概略的に示す図

【図2】(a)は通信プロトコルがFlexRayである場合の伝送線路のドライブ状態を示す図、(b)はコモンモード電圧の検出結果に応じたフィードバック制御を説明する図

【図3】信号処理回路による制御内容を概略的に示すフローチャート

【図4】送信ドライバ回路の構成をより具体的に示す図

【図5】コモンモード電圧をサンプル/ホールドするタイミングを示す図

【図6】(a)はコモンモード電圧が「山型」,「谷型」の場合の波形を示す図、(b)はステップS3,S5の内容をより詳細に示す図

【図7】通信信号出力回路並びにゲート駆動部を構成する各MOSFETのオンオフ状態をモデル的に示す図

【図8】第2実施例を示す図4相当図

【図9】第3実施例を示す図4相当図

【図10】第4実施例を示す図4相当図

【図11】ピーク/ボトムホールド回路の具体構成を示す図

【図12】図5相当図

【図13】図6相当図

【図14】第5実施例を示す図4相当図

【図15】第6実施例を示す図6(b)相当図

【図16】第7実施例を示す図6(b)相当図

【図17】第8実施例を示す図4相当図

【図18】図12相当図

【図19】第9実施例を示す図4相当図

【図20】電圧変化時間検出回路の詳細構成を示す図

【図21】タイミングチャート

【図22】図6(b)相当図

【図23】第10実施例を示す図19相当図

【図24】図21相当図

【発明を実施するための形態】

【0025】

(第1実施例)

以下、第1実施例について図1ないし図7を参照して説明する。先ず、本発明の概略を、図1ないし図3を参照して説明する。図1は、送信ドライバ回路の構成を概略的に示している。送信ドライバ回路1は、通信信号出力回路2,レベルホールド回路(コモンモード検出手段)3,信号処理回路(制御部)4で構成されている。通信信号出力回路2は、外部より与えられる制御信号に応じて、一対の信号線BP,BMからなる伝送線路5をハイレベル,又はローレベルにドライブすることで、差動信号を出力する。また、通信信号出力回路2は上記のように伝送線路5をドライブする際に、信号線BP,BMに対する電圧の出力状態を調整可能に構成されている。ここでの「電圧の出力状態」とは、ドライブを開始するタイミングや、電圧の立ち上り,立下りの傾きや、ハイレベル,ローレベルのピーク値等を言う。

【0026】

レベルホールド回路3は、信号線BP,BM間に接続されており、伝送線路5に発生するコモンモード電圧のレベルをホールドして信号処理回路4に出力する。信号処理回路4は、マイクロコンピュータで構成されており、レベルホールド回路3より与えられるコモンモード電圧のレベルに応じて、次回に差動信号を送信する際に通信信号出力回路2を制御する。すなわち、上述のように通信信号出力回路2が伝送線路5をドライブする際に、信号線BP,BMに対する電圧の出力状態を調整してコモンモード電圧が低減するようにフィードバック制御する。

【0027】

ここで、図2(a)は、通信プロトコルがFlexRayである場合の伝送線路5のドライブ状態を示している。FlexRayでは、同図に示すように信号の状態がData1(ハイレベル),Data0(ローレベル)間で変化する場合に、信号線BP,BMの電位が反転するようにドライブが行われる。すると、双方の電位が等しくなる電圧波形のクロスポイント付近のタイミングでコモンモード電圧Vcomが発生することが多い。例えば、電源Vcc(高電位点)が5Vで信号線BP,BMの中間基準電位が2.5Vである場合、コモンモード電圧Vcomは数10mV程度の振幅で、30n〜40n秒程度の時間発生する。そこで本実施例では、図2(b)に示すように、コモンモード電圧Vcomの検出結果に応じて、信号処理回路4が次回に差動信号を送信する際に通信信号出力回路2を制御することで、コモンモード電圧Vcomを順次低減させるようにフィードバック制御する。

【0028】

図3は、信号処理回路4によるフィードバック制御の内容を概略的に示すフローチャートである。先ず、レベルホールド回路3より与えられるコモンモード電圧をA/D変換して読み込み、コモンモード電圧が山型/谷型の何れの波形であるかを判断する(ステップS1)。山型とは、コモンモード電圧が伝送線路5の中間電位を上回る振幅方向に発生する場合であり、谷型とは、コモンモード電圧が伝送線路5の中間電位を下回る振幅方向に発生する場合である。

山型である場合はステップS2に移行して、コモンモード電圧が上限基準値以内か否かを判断する。上限基準値以内であれば(YES)、ノイズとしての影響は無視できる程度であるから処理を終了する(「開始」に戻る)。一方、コモンモード電圧が上限基準値を超えていれば(NO)、次回の信号送信時にコモンモード電圧を低下させる方向に通信信号出力回路2を調整する(ステップS3)。

【0029】

また、ステップS1においてコモンモード電圧が谷型である場合はステップS4に移行して、コモンモード電圧が下限基準値以内か否かを判断する。下限基準値以内であれば(YES)処理を終了し、下限基準値を下回っていれば(NO)、次回の信号送信時にコモンモード電圧を上昇させる方向に通信信号出力回路2を調整する(ステップS5)。以上のようにしてフィードバック制御を繰り返すことで、図2(b)に示すように(山型の場合)コモンモード電圧を低減することが可能となる。

【0030】

図4は、図1に示す送信ドライバ回路1の構成をより具体的に示したものである。図4(a)において、通信信号出力回路2は、4つのMOSFET11PP,11PN,11MP,11MN(駆動用半導体スイッチング素子)からなる駆動素子部12と、駆動素子部12の各MOSFET11にゲート信号を出力するゲート駆動部13PP,13PN,13MP,13MNとで構成されている。ゲート駆動部13PP,13PNには、外部からの制御信号がNOTゲート50P,50Nを介して与えられており、ゲート駆動部13MP,13MNには、前記制御信号がそのまま与えられている。また、ゲート駆動部13PP〜13MNには、信号処理回路4からのスイッチ切替え信号が個別に与えられている。上記制御信号は、信号処理回路4にも入力されている。

【0031】

電源Vccとグランド(低電位点)との間には、PチャネルMOSFET11PP及びNチャネルMOSFET11PNの直列回路と、PチャネルMOSFET11MP及びNチャネルMOSFET11MNの直列回路とが接続されている。PチャネルMOSFET11PP及びNチャネルMOSFET11PNの共通接続点(ドレイン)は信号線BPに接続されており、PチャネルMOSFET11MP及びNチャネルMOSFET11MNの共通接続点(ドレイン)は信号線BMに接続されている。

【0032】

信号線BP,BMの間には、サンプルホールド回路3Sを構成する抵抗素子14a及び14bの直列回路が接続されており、それらの共通接続点は、オペアンプ15の非反転入力端子に接続されている。オペアンプ15の反転入力端子は、抵抗素子16及び17,コンデンサ18の直列回路を介してグランドに接続されており、また、互いに接続方向が異なる2つのダイオード19及び20を介してオペアンプ15の出力端子に接続されている。これらのダイオード19及び20は、オペアンプ15の出力レベルを制限するために配置されている。そして、オペアンプ15の出力端子は、スイッチ21を介して抵抗素子16及び17の共通接続点に接続されており、その共通接続点は信号処理回路4の入力端子に接続されている。スイッチ21のオンオフ制御は、信号処理回路4によって行われる。

【0033】

また、図4(b)は、ゲート駆動部13の内部回路を示している。尚、ゲート駆動部13PP,13PN,13MP,13MNの構成は何れも共通であるため、モデル的に1つだけを示す。電源Vccとグランドとの間には、駆動素子部12の何れかのMOSFET11のゲート(制御端子)には、PチャネルMOSFET22P及びNチャネルMOSFET22N(制御用半導体スイッチング素子)のドレインが接続されている。そして、電源VG(=Vccでも良い)とPチャネルMOSFET22Pのソースとの間には、スイッチ及び抵抗素子の直列回路を複数並列に接続して構成される抵抗アレイ部RApが接続されており、NチャネルMOSFET22Nのソースとグランドとの間には、同様にスイッチ及び抵抗素子の直列回路を複数並列に接続して構成される抵抗アレイ部RAnが接続されている。そして、信号処理回路4は、抵抗アレイ部RAp,RAnに個別の切替え信号を与えて、それらのスイッチのオンオフを切り替える。

【0034】

次に、本実施例の作用について図5及び図6も参照して説明する。図5は、通信信号出力回路2に与えられる制御信号のレベルがロー,ハイ,ローに変化することで、伝送線路5の差動信号がData1,Data0,Data1に変化する場合に、サンプルホールド回路3がコモンモード電圧をサンプル/ホールドするタイミングを示している。制御信号のレベルがローの場合、ゲート駆動部13PP,13PNにはハイレベルの信号が与えられ、ゲート駆動部13MP,13MNにはローレベルの信号が与えられる。これにより、ゲート駆動部13PP,13PNではPチャネルMOSFET22Nがオンとなっており、ゲート駆動部13MP,13MNではNチャネルMOSFET22Pがオンとなっている。その結果、駆動素子部12でPチャネルMOSFET11PPがオン、NチャネルMOSFET11MNがオンするので、信号線BPのレベルがハイ,信号線BMのレベルはローとなっている((a),(b)参照)。

【0035】

そして、制御信号のレベルがローからハイに変化すると、上記の各信号の状態が反転するので、信号線BPのレベルがロー,信号線BMのレベルはハイに変化する((a),(b)参照)。コモンモード電圧は、制御信号の立ち上り,立下りのタイミングから若干の遅延の後、信号線BP,BMの電圧が変化して双方のレベルが同一となるクロスポイントの付近で発生する((c)参照)。

【0036】

コモンモード電圧が発生する場合とは、上記のクロスポイントが中間基準電位(例えば2.5V)から変動した場合であり、サンプルホールド回路3Sのオペアンプ15の出力端子には、上記中間基準電位から変動した電圧が山型,谷型に出力される。そこで、信号処理回路4は、制御信号の立ち上りタイミングを起点として、立下りタイミングに係る前後にサンプルホールド回路3のスイッチ21を一定期間オンさせるようにモノパルス信号を出力し、コモンモード電圧のレベルをサンプリングさせる((d)参照)。

【0037】

図6(b)は、図3で示したフローチャートのステップS3,S5の内容を、図4に示す構成に合わせてより詳細にしたものである。尚、図6(a)は、コモンモード電圧Vcomが「山型」の場合,「谷型」の場合の波形を示す。コモンモード電圧が上限基準値を超えた場合のステップS3では、ゲート駆動部13PP(BP_Pch),13PN(BP_Nch),13MP(BM_Pch),13MN(BM_Nch)がそれぞれ内蔵する抵抗アレイ部RAp,RAnのスイッチを(1)〜(8)に示すように切り替えることで駆動素子部12の各MOSFET11のゲート抵抗値を変化させ、次回の信号送信時に発生するコモンモード電圧の振幅を低減させる。

【0038】

尚、各ゲート駆動部13における抵抗アレイ部RAp,RAnの初期状態では、例えばスイッチの半分程度をオンさせており、この状態からスイッチをオンさせる数を増やせば抵抗値が低下し、スイッチをオンさせる数を減らせば抵抗値が上昇することになる。具体的には、各ゲート駆動部13における抵抗アレイ部RApの抵抗値を大きくするようにスイッチをオンさせる数を減らし、抵抗アレイ部RAnの抵抗値を小さくするようにスイッチをオンさせる数を増やす。また、これら(1)〜(8)は必ずしも全て同時に実行する必要はなく、少なくとも1つ以上を実行すれば良い。一方、コモンモード電圧が下限基準値を超えた場合のステップS5では、(1)〜(8)における抵抗アレイ部RAp,RAnの抵抗値の大小変化を逆にする。

【0039】

ここで、図7は、ステップS3,S5における抵抗アレイ部RAp,RAnの抵抗値の切替えを説明するため、通信信号出力回路2並びにゲート駆動部13を構成する各MOSFETのオンオフ状態をモデル的に示したもので、信号線BPがハイレベル,信号線BMがローレベルとなる場合である。信号線BP側のゲート駆動部13ではNチャネルMOSFETがオンしており、信号線BM側のゲート駆動部13ではPチャネルMOSFETがオンしている。

【0040】

この時、図5に示すように、信号線BPのレベルがローからハイ,信号線BPのレベルがハイからローに変化するタイミングでコモンモード電圧が上限基準値を超えた際に想定されるのは、信号線BP側の電位変化のタイミングが相対的に速いか、信号線BM側の電位変化のタイミングが相対的に遅い場合である。したがって、コモンモード電圧のレベルを低減するには、信号線BP,BMの電位変化のタイミングが上記と逆方向となるように調整すれば良い。

【0041】

そこで、ステップS3において上述のように各部の抵抗値を調整することで、信号線BP側については、例えばPチャネルMOSFET11PPのオンタイミングを遅延させる方向に、NチャネルMOSFET11PNのオフタイミングを速める方向に調整する。一方、信号線BM側については、PチャネルMOSFET11MPのオフタイミングを遅延させる方向に、NチャネルMOSFET11MNのオンタイミングを速める方向に調整する。これにより、信号線BP側の電位変化を相対的に遅くし、信号線BM側の電位変化を相対的に速くするように変化させる。

【0042】

また、コモンモード電圧が下限基準値を超えた際に想定されるのは、信号線BP側,BM側の電位変化タイミングの相対的な遅速関係が上限基準値を超えた場合と逆になるので、ステップS5においては、例えば信号線BP側の電位変化を相対的に速くし、信号線BM側の電位変化を相対的に遅くするように変化させる。尚、ここで述べた電位変化の遅速関係は、信号線BPのレベルがハイからローに,信号線BPのレベルがローからハイに変化するタイミングについては逆になるが、結果としてステップS3,S5における調整方向がそのまま適用される。

【0043】

また、図6(b)に示す処理を繰り返し実行する際に、次回は、今回の各抵抗値の設定を維持した状態を基準として、抵抗値を変化させる方向を決定する。例えば、今回の処理でコモンモード電圧が上限基準値を超えた結果、ステップS3中の何れか1つのスイッチ切替えを行い、次回の処理でもコモンモード電圧が上限基準値を超えている場合は、上記スイッチの切替えは維持したまま他の(1)〜(8)の何れかのスイッチ切替えを追加するか、若しくは今回切り替えたものと同じスイッチが属する抵抗アレイ部RAについて、スイッチ切替え数をより多くすることで対応する。

【0044】

以上のように本実施例によれば、レベルホールド回路3(サンプルホールド回路3S)は、通信信号出力部2が差動信号の電圧レベルを変化させる際に伝送線路5に発生するコモンモード電圧の変化を検出し、その検出レベルをレベルホールドする。そして、信号処理回路4は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整する。すなわち、信号処理回路4が、コモンモード電圧の発生状態に応じてフィードバック制御を行うことでコモンモード電圧を順次低減させて、差動信号を高速に伝送する場合でもコモンモード電圧を確実に低減することができ、ノイズの発生を抑制することが可能となる。

【0045】

そして、信号処理回路4は、コモンモード電圧の検出レベルが上限基準値を上回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整することで、コモンモード電圧が山型の波形となっている場合に当該電圧を低減できる。

また、信号処理回路4は、コモンモード電圧の検出レベルが下限基準値を下回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより速くするように調整することで、コモンモード電圧が谷型の波形となっている場合に当該電圧を低減できる。

【0046】

更に、通信信号出力部2は、電源Vccとグランドとの間に接続されるMOSFET11PP,11PN,11MP,11MNをスイッチングさせて差動信号の電圧レベルを変化させ、また、電源VG又はグランドとMOSFET11のゲートとの間に接続されるMOSFET22をスイッチングさせて、前記ゲートに出力する制御電圧を変化させる。この場合、電源VG又はグランドとMOSFET22との間における通電経路の抵抗値を調整することになるので、これにより、MOSFET11のゲートに通電する経路の抵抗値を変化させて、信号線の電圧レベルを変化させるタイミングを変更することができる。

【0047】

(第2実施例)

図8は第2実施例であり、第1実施例と同一部分には同一符号を付して説明を省略し、以下異なる部分について説明する。第2実施例の送信ドライバ回路23は、第1実施例ではゲート駆動部13に配置していた抵抗アレイ部RAp,RAnを、駆動素子部24の内部に配置した構成となっている。尚、図8は信号線BP側のみを示しているが、信号線BP側についても同様に構成されている。すなわち、電源VccとPチャネルMOSFET11PP,11MPのソースとの間,NチャネルMOSFET11PN,11MNのソースとグランドとの間に抵抗アレイ部RAp,RAnが挿入されており、信号処理回路4は、それらのスイッチを切り替えて各MOSFET11のソース側の抵抗値を第1実施例と同様に切り替える。

【0048】

以上のように構成される第2実施例によれば、送信ドライバ回路23は、電源VccとPチャネルMOSFET11PP,11MPのソースとの間,NチャネルMOSFET11PN,11MNのソースとグランドとの間に挿入した抵抗アレイ部RAp,RAnの抵抗値を変化させて、信号線BP,BMの電圧レベルを変化させるタイミングを変更するので、第1実施例と同様に制御することで、コモンモード電圧の発生レベルを低減するように調整できる。

【0049】

(第3実施例)

図9は第3実施例であり、第1実施例と異なる部分のみ説明する。図9に示すサンプルホールド回路3Sでは、抵抗素子14a及び14b(オフセット検出手段)の共通接続点がコンデンサ25(オフセット検出手段)を介してグランドに接続されていると共に、信号処理回路4aの入力端子に接続されている。以上が送信ドライバ回路26を構成している。信号処理回路4aは、上記入力端子の電圧をA/D変換して読み込むことで、コモンモード電圧のDCオフセット分を考慮することができる。すなわち、各回路素子の定数ずれ等により、信号線BP,BM間の中間基準電位が必ずしも2.5Vを示さない場合があるので、信号処理回路4aがステップS1においてコモンモード電圧のサンプルホールド値を読み込んだ際に、DCオフセット分を考慮して補正することでコモンモード電圧をより正確に把握できる。

以上のように第3実施例によれば、信号処理回路4aは、サンプルホールド回路3Sによる検出レベルを、抵抗素子14a及び14bの共通接続点に与えられる差動信号電圧のDCオフセットレベルに基づき補正した値を上限基準値及び下限基準値と比較するので、コモンモード電圧の発生状態をより正確に検出することができる。

【0050】

(第4実施例)

図10ないし図13は第4実施例を示すものであり、第3実施例と異なる部分を説明する。図10に示す送信ドライバ回路27は、サンプルホールド回路3Sに替えてピーク/ボトムホールド回路3PBが配置されている。そして、ピーク/ボトムホールド回路3PBより出力されるピークホールド値及びボトムホールド値は、信号処理回路4に替わる信号処理回路(制御部)28に入力されている。

【0051】

図11は、ピーク/ボトムホールド回路3PBの具体構成を示す。ピーク/ボトムホールド回路3PBは、ピークホールド回路3P(ピークホールド手段)と、ボトムホールド回路3B(ボトムホールド手段)とで構成されている。ピークホールド回路3Pは、非反転入力端子が抵抗素子14a及び14bの共通接続点に接続されるオペアンプ29Pと、オペアンプ29Pの出力端子がダイオード30Pを介して非反転入力端子に接続されるオペアンプ31Pとを備えている。

【0052】

オペアンプ31Pの出力端子は、自身及びオペアンプ29Pの反転入力端子に接続されていると共に、信号処理回路28の入力端子に接続されている。また、オペアンプ29Pの反転入力端子は、ダイオード32Pを介して自身の出力端子に接続されている。オペアンプ31Pの非反転入力端子とグランドとの間には、抵抗素子33P及びコンデンサ34Pの直列回路と、スイッチ35Pとが接続されている。スイッチ35Pは、ピークレベル保持用のコンデンサ34Pを放電させてリセットするためにオンされ、そのオンオフ制御は信号処理回路28によって行われる。

【0053】

一方、ボトムホールド回路3Bは、ピークホールド回路3Pと略対象に構成されており、対応する構成には符号Pに替えて符号Bを付して示している。但し、ダイオード30B,32Bの接続方向は、ピークホールド回路3Pのダイオード30P,32Pとは逆になっている。

【0054】

次に、第4実施例の作用について図12及び図13も参照して説明する。図12は、第1実施例の図5相当図であり、信号処理回路28がピークホールド回路3P,ボトムホールド回路3Bによってピークホールド,ボトムホールドを行わせるタイミング,すなわちスイッチ35P,35Bをオン→オフ(ホールド)→オン(リセット)に切り替えるタイミングを(d)に示す。この場合、ホールド期間の始期は第1実施例のサンプルホールドタイミングに等しく設定されるが、ホールド期間の終期は、コモンモード電圧が発生している期間よりも確実に長くなるように、第1実施例のサンプルホールドタイミングよりも遅くなっている。第4実施例では、コモンモード電圧のピーク値とボトム値を検出することで、当該電圧振幅が山谷型,谷山型に変化する場合(図6(a)参照)についても対応する。

【0055】

図13は図6相当図であり、図13(a)には、コモンモード電圧が山谷型,谷山型に変化する場合の波形を示している。すなわち、これらは何れも、電圧波形が中間基準電位に対して高低方向に変動するもので、山谷型とは、山側のピーク値が谷側のボトム値よりも大きい場合を称し、谷山型とは、逆に谷側のボトム値が山側のピーク値よりも大きい場合を称する。

【0056】

図13(b)において、信号処理回路28は、ピークホールド回路3Pからのピークホールド値を読取ると(ステップS11)、ステップS2においてそのピークホールド値が上限基準値以内か否か判断する。また、信号処理回路28は、ボトムホールド回路3Bからのボトムホールド値を読取ると(ステップS12)、ステップS4においてそのボトムホールド値が下限基準値以内か否か判断する。尚、図13(b)では、ステップS11及びステップS2の処理と、ステップS12及びステップS4の処理とが並列に実行されるように示されているが、実際にはこれらはシリアルに実行される。

【0057】

そして、ステップS2,S4の少なくとも一方で「NO」と判断すると、信号処理回路28は、ピークホールド値とボトムホールド値との平均をとり、中間基準電位Vrefと比較する(ステップS13)。(平均値>Vref)であればコモンモード電圧は山谷型であるからステップS3を実行し、(平均値<Vref)であればコモンモード電圧は谷山型であるからステップS5を実行する。それから、コンデンサ34を放電させて(ステップS15)ステップS11,S12に戻る。尚、図示はしないが、ステップS14において(平均値=Vref)の場合はそのままステップS15に移行する。

【0058】

以上のように第4実施例によれば、信号処理回路28は、ピークホールド回路3Pによって検出されたコモンモード電圧のピーク値を上限基準値と比較すると共に、ボトムホールド回路3Bによって検出されたコモンモード電圧のボトム値を下限基準値と比較する。したがって、コモンモード電圧が変化した場合の波形のピーク値,ボトム値を検出して、コモンモード電圧が発生している場合の波形振幅の大きさを正確に捉えることができる。

【0059】

そして、信号処理回路28は、ピーク値が上限基準値を上回ると共にボトム値が下限基準値を下回ると両者の平均値を求め、その平均値が、一対の信号線間の中間基準電位よりも高いか或いは低いかに応じてコモンモード電圧を低減するための調整方向を決定するので、ノイズの発生原因としてより影響が大きい側の波形振幅を低減するように調整できる。

【0060】

(第5実施例)

図14は第5実施例である。第5実施例はゲート駆動部13に替わるゲート駆動部36の構成を示す。ゲート駆動部36は、直列に接続される2n個(nは2以上の自然数)のNOTゲート(遅延素子)37と、これらのうち初段のNOTゲート37の入力端子と、そこから2個先き毎のNOTゲート37の入力端子と、最後段のNOTゲート37の出力端子とにそれぞれ一端が接続される(n+1)個のスイッチ38とで構成されている。n個のスイッチ38の他端は共通に接続されており、外部からの制御信号が与えられる。そして、スイッチ38のオンオフ制御は信号処理回路4,4A,28等により制御される。

【0061】

以上のように構成される第5実施例によれば、ゲート駆動部36は、制御信号の入力端子と、MOSFET11のゲートとの間に接続される2n個のNOTゲートを備え、それらの直列接続数を2個単位で変更可能に構成されるので、例えば信号処理回路4が(n+1)個のスイッチ38のうち何れか1つをオンすることで、駆動素子部12にゲート信号を出力するタイミングに異なる遅延時間を付与することができる。また、遅延素子としては、その他ディレイライン等を用いても良く、この場合は素子の直列接続数を少なくとも1個ずつ変化させるように切り替えれば良い。

【0062】

(第6実施例)

図15は第6実施例を示す図6(b)相当図であり、ステップS3,S5に替えてステップS21,S22が配置されている。第6実施例では、ステップS2で「NO」と判断すると、ステップS21においてサンプルホールド値と上限基準値との差を求める。そして、その差の値から、コモンモード電圧が上限基準値以内となる第1実施例におけるゲート抵抗値や、第2実施例における駆動素子部24の出力抵抗値,若しくは第5実施例における遅延時間を求め、スイッチの切り替えを行う。また、ステップS4で「NO」と判断した場合も、ステップS22においてサンプルホールド値と下限基準値との差を求め、その差の値から、コモンモード電圧が下限基準値以内となるゲート抵抗値等を求め、スイッチの切り替えを行う。尚、上記の抵抗値や遅延時間については、予めシミュレーションや実測などにより求めておくようにする。

【0063】

以上のように第6実施例によれば、信号処理回路28は、検出レベルと上限基準値との差又は検出レベルと下限基準値との差に応じて、信号出力部による電圧の出力状態を調整する。通信信号出力部2による電圧の出力状態の調整量は、コモンモード電圧の検出レベルと基準値との差に応じて決まるので、したがって、コモンモード電圧を低減するための調整を、より短時間に完了することができる。尚、第6実施例を第4実施例に適用する場合には、放電用のスイッチ35は不要である。

【0064】

(第7実施例)

図16は第7実施例を示す図6(b)相当図である。第7実施例では、ステップS2,S4で「YES」と判断すると、処理を終了する前に信号処理回路4(又は4a,28)の動作を自身で停止させる(ステップS31,S32)。すなわち、この場合はデフォルトの設定,若しくはフィードバック制御を何回か実行した段階でコモンモード電圧の発生レベルが基準値以内となっているので、以降に信号処理回路4等が調整を行う必要が無い。したがって、信号処理回路4等の動作を停止させて消費電力を低減する。

以上のように第7実施例によれば、信号処理回路4は、検出レベルが上限基準値以内であり、且つ下限基準値以内である場合は、以降に自身の動作を停止させるので、信号処理回路4が調整を行う必要はない場合に、不要な電力消費を低減することができる。

【0065】

(第8実施例)

図17及び図18は第8実施例を示すものであり、第4実施例と異なる部分を説明する。第8実施例の送信ドライバ回路37は、第4実施例の送信ドライバ回路27におけるピーク/ボトムホールド回路3PBの内部に、微分回路38を追加した構成となっている。微分回路38は、周知のようにオペアンプ38aと、コンデンサ38bと、抵抗素子38cとで構成されており、微分回路38の入力端子は抵抗素子14a及び14bの共通接続点に接続されており、出力端子はピークホールド回路3P,ボトムホールド回路3Bの入力端子に接続されている。

【0066】

次に、第8実施例の作用について図18を参照して説明する。図18は図12相当図であり、図18(d)には、微分回路38より出力されるコモンモード電圧の微分波形を示している。図18(c)に示す山型の電圧波形の場合、その微分波形は山谷型となるので、山のピークレベルと谷のボトムレベルとが検出される。したがって、第8実施例の処理は、第4実施例の図13(b)に示すフローチャートと同様になる。

以上のように第8実施例によれば、ピーク/ボトムホールド回路3PBの内部に微分回路38を配置してコモンモード電圧の微分値を検出し、信号処理回路28は、その微分値の検出レベルを上限基準値及び下限基準値と比較するので、コモンモード電圧の変化率の大きさを検出でき、第3実施例のようにDCオフセットを検出して補正する必要が無くなる。

【0067】

(第9実施例)

図19ないし図22は第9実施例を示すものである。第9実施例の送信ドライバ回路41は、レベルホールド回路3に替えて電圧変化時間検出回路42を備えており、図20は、その電圧変化時間検出回路42の詳細構成を示している。電圧変化時間検出回路42は、ハイ側時間検出回路42H(第1計時手段)と、ロー側時間検出回路42L(第2計時手段)とで構成されている。電源とグランドとの間には、電流源43(P,M)と、スイッチ44(P,M)と、コンデンサ45(P,M)との直列回路が接続されている。コンパレータ46Pは、信号線BPの電位と、比較用の電圧であるBP側基準値とを比較し、前者が後者を下回った場合にハイレベルのStart信号をスイッチ44Pに出力する。BP側基準値は、信号線BPのハイレベル電位よりも若干低いレベルに設定されている(図21(b)参照)。

【0068】

また、コンパレータ46Mは、信号線BMの電位と、比較用の電圧であるBM側基準値とを比較し、前者が後者を上回った場合にハイレベルのStart信号をスイッチ44Mに出力する。BM側基準値は、信号線BMのローレベル電位よりも若干高いレベルに設定されている(図21(b)参照)。そして、コンパレータ46Cは、信号線BPの電位と信号線BMの電位とが同じレベルになると、ハイレベルのStop信号をスイッチ44P,44Mに出力する。スイッチ44P,44Mは、Start信号がハイレベルになるとオンし、その状態からStop信号がハイレベルになるとオフするように構成されている。また、コンデンサ45(P,M)には、スイッチ47(P,M)及び抵抗素子48(P,M)の直列回路が並列に接続されており、スイッチ47(P,M)のオンオフ制御は信号処理回路(制御部)49によって行われる。

【0069】

次に、第9実施例の作用について図21及び図22を参照して説明する。第9実施例では、制御信号がローからハイに変化することで、信号線BPのレベルがハイからローに変化し、且つ信号線BMのレベルがローからハイに変化する期間に、スイッチ47(P,M)のオンオフを制御してコンデンサ45(P,M)を充電する。尚、スイッチ44(P,M)及び47(P,M)は初期状態でオフしており、コンデンサ45(P,M)は放電されて、端子電圧は0Vであるとする。

【0070】

すなわち、上記の期間において、信号線BPのレベルがハイからローへの変化を開始してBP側基準値を下回ると、コンパレータ46PはStart信号をスイッチ44Pに出力し、スイッチ44Pはターンオンする。同時に信号線BMのレベルがローからハイへの変化を開始してBM側基準値を上回ると、コンパレータ46MはStart信号をスイッチ44Mに出力し、スイッチ44Mはターンオンする。これにより、コンデンサ45(P,M)は電流源43(P,M)によって充電される。

【0071】

その状態から、信号線BPの電位と信号線BMの電位とがクロスポイントに達して同じレベルになると、コンパレータ46Cは、Stop信号をスイッチ44(P,M)に出力する。これにより、スイッチ44(P,M)はターンオフしてコンデンサ45(P,M)の充電は停止される。したがって、この時点でのコンデンサ45Pの充電電位は、信号線BPのレベルがハイからローへの変化を開始してからクロスポイントに達するまでの時間に比例し、コンデンサ45Mの充電電位は、信号線BMのレベルがローからハイへの変化を開始してからクロスポイントに達するまでの時間に比例している。

【0072】

図22は、信号処理回路49の処理内容を示すフローチャートである。信号処理回路49は、制御信号のレベルがローからハイに変化すると(ステップS41:YES)、その時点から若干の時間が経過してコンパレータ46CがStop信号を出力した以降のタイミングで、電圧変化時間検出回路42よりコンデンサ45P,45Mの端子電圧(第1,第2時間)をA/D変換して読み込む(ステップS42)。そして、コンデンサ45P(BP側),45M(BM側)の端子電圧の大小を比較し(ステップS43)、(BP側>BM側)であれば(YES)ステップS44に移行し、(BP側<BM側)であれば(NO)ステップS45に移行する。

【0073】

ステップS44では、コンデンサ45Pの端子電圧からコンデンサ45Mの端子電圧を減じた差(第1時間差)が基準値以内か否かを判断し、ステップS45では、逆にコンデンサ45Mの端子電圧からコンデンサ45Pの端子電圧を減じた差(第2時間差)が基準値以内か否かを判断する。そして、ステップS44で「NO」と判断するとステップS5を実行し、ステップS45で「NO」と判断するとステップS3を実行する。

【0074】

ここで、ステップS44で「NO」と判断するケースは、図21(b)に示すように、信号線BP側の電位が低下するタイミングが信号線BMの電位が上昇するタイミングよりも速く、クロスポイントが低電位側にずれてコモンモード電圧が谷型に発生する場合に対応する。したがって、ステップS5を実行する。一方、ステップS45で「NO」と判断するケースは、上記とは逆に、信号線BP側の電位が低下するタイミングよりも信号線BMの電位が上昇するタイミングが速く、クロスポイントが高電位側にずれてコモンモード電圧が山型に発生する場合に対応する。したがって、ステップS3を実行する。ステップS3又はS5の実行後は、スイッチ47P,47Mをオンすることでコンデンサ45P,45Mを放電させる(ステップS46)。それから、ステップS41に戻る。

【0075】

以上のように第9実施例によれば、ハイ側時間検出回路42Hは、通信信号出力部2が差動信号の電圧レベルを変化させる際に、信号線BPの電位が低下を開始した時点から計時を開始し、ロー側時間検出回路42Lは、信号線BMの電位が上昇を開始した時点から計時を開始し、信号線BP,BMの電位が互いに等しくなった時点で計時を停止させて第1時間及び第2時間をそれぞれ計時する。信号処理回路49は、第1時間と第2時間との差である第1時間差を求め、第1時間差が正であれば第1時間差と第1基準値とを比較し、第1時間差が負であれば第2時間差を求めて第2基準値とを比較する。その結果、第1時間差が第1基準値を上回るか又は第2時間差が第2基準値を上回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整するようにした。したがって、コモンモード電圧波形が山型の場合と、谷型の場合とに応じて、通信信号出力部2による電圧の出力状態をフィードバック制御することで、コモンモード電圧を低減するように調整できる。

【0076】

また、信号処理回路49は、第1時間差が第1基準値を上回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより速くするように調整し、第2時間差が第2基準値を上回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整する。したがって、第1実施例と同様にして、コモンモード電圧の波形に応じて当該電圧を低減するよう調整できる。

【0077】

尚、信号処理回路49にStop信号を入力するようにして、ステップS41では、信号処理回路49は、制御信号のレベルがローからハイに変化した後、コンパレータ46CがStop信号を出力したことを確認してステップS42に移行しても良い。また、第9実施例は、制御信号のレベルがハイからローに変化して、信号線BP,BMのレベル変化が上記と逆になる場合について実施しても良い。

【0078】

(第10実施例)

図23及び図24は第10実施例を示すものであり、第9実施例と異なる部分について説明する。第10実施例の送信ドライバ回路51は、上記実施例のように信号線BP,BM間の電位が反転せず、例えばCANのように差動信号が、中間基準電位(差動電圧0V,レセッシブ)と、信号線BP側が高電位方向に,信号線BM側が低電位方向に変化する(ドミナント)との間で変化する場合に対応した構成となっている。通信信号出力回路52は、電源Vccとグランドとの間に接続される、PチャネルMOSFET53P,抵抗素子54a及び54b,NチャネルMOSFET53N(駆動用半導体スイッチング素子)の直列回路で構成されている。

【0079】

PチャネルMOSFET53Pはゲート駆動部55Pによって駆動され、NチャネルMOSFET53Nはゲート駆動部55Nによって駆動される。ゲート駆動部55P,55Nの構成は、例えば第1実施例のゲート駆動部13と同様であり、それらのスイッチ切替えは、信号処理回路(制御部)56によって行われる。ゲート駆動部55P側には、制御信号がNOTゲート57を介して与えられている。そして、信号線BP,BM間には第9実施例の電圧変化時間検出回路42が接続されている。

【0080】

第10実施例において、電圧変化時間検出回路42は第9実施例と全く同様に動作する。したがって、信号処理回路56も図22に示すフローチャートを実行すれば良い。但し、ステップS3,S5においては、ゲート駆動部BP_Nch,BM_Pchに対応する構成が存在しないので、それらについての制御は行わない。尚、図24(b)に示しているように、制御信号の立下りタイミングでスイッチ44P,44Mをオンして、信号線BP側の電位がBP側基準値を超えた場合にスイッチ44Pをオフし、信号線BM側の電位がBM側基準値を下回った場合にスイッチ44Mをオフして、ステップS42においてコンデンサ45P,45Mの充電電圧を読み込んでも良い。

以上のように第10実施例によれば、差動信号の伝送形態が、CANのようにレセッシブ,ドミナント間で変化する場合についても、第9実施例と同様の効果が得られる。

【0081】

本発明は上記し、又は図面に記載した実施例にのみ限定されるものではなく、以下のような変型又は拡張が可能である。

コモンモード電圧に替えて、コモンモード電流を検出しても良い。

第9実施例において、第1,第2計時手段は、コンデンサ45に替えてカウンタを用いることで、Start信号とStop信号とが出力される時間を計測しても良い。

第9,第10実施例について、第6実施例と同様に、BP側,BM側の端子電圧の差に応じて、ステップS3,S5における調整を一回で行うようにしても良い。

第8ないし第10実施例に、第7実施例を組み合わせて実行しても良い。

半導体スイッチング素子はMOSFETに限ることなく、バイポーラトランジスタを用

いても良い。

【符号の説明】

【0082】

図面中、1は送信ドライバ回路、2は通信信号出力回路、3はレベルホールド回路(コモンモード検出手段)、3Sはサンプルホールド回路(コモンモード検出手段)、3Pはピークホールド回路(ピークホールド手段)、3Bはボトムホールド回路(ボトムホールド手段)、4は信号処理回路(制御部)、5は伝送線路、11はMOSFET(駆動用半導体スイッチング素子)、14は抵抗素子(オフセット検出手段)、22はMOSFET(制御用半導体スイッチング素子)、23は送信ドライバ回路、25はコンデンサ(オフセット検出手段)、26,27は送信ドライバ回路、28は信号処理回路(制御部)、37はNOTゲート(遅延素子)、37は送信ドライバ回路、38は微分回路、41は送信ドライバ回路、42Hはハイ側時間検出回路(第1計時手段)、42Lはロー側時間検出回路(第2計時手段)、49は信号処理回路(制御部)、51は送信ドライバ回路、52は通信信号出力回路、53はMOSFET(駆動用半導体スイッチング素子)、56は信号処理回路(制御部)を示す。

【技術分野】

【0001】

本発明は、一対の信号線により差動信号を伝送する伝送線路に接続され、その伝送線路を介して信号を送信するための送信ドライバ回路に関する。

【背景技術】

【0002】

一対の信号線により差動信号を伝送する伝送線路については、送信ドライバ回路が一方の信号線(+)の電位を上昇させると同時に他方の信号線(−)の電位を低下させるようにドライブすることで差動信号を伝送する。この時、信号線(+)の電位を上昇させるタイミングと信号線(−)の電位を低下させるタイミングとの間にズレが生じて双方の電位の変化が非対称になると、伝送線路上にコモンモード電圧が発生してノイズとなる。

【0003】

このようなノイズの発生を防止する従来技術として、例えば特許文献1には、信号線VH,VLのそれぞれの電位変化の対称性が崩れた状態に応じて発生する電流を送信ドライバ回路にフィードバックさせることで、信号線VH,VLをそれぞれドライブするスイッチング素子をスイッチングさせるタイミングを調整し、コモンモード電圧の発生を抑制する技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−260799号公報(図1参照)

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1の技術は、伝送線路に発生するコモンモード電圧を検出してから、電流をフィードバックさせるまでにある程度の時間を要するため、例えばFlexRay(登録商標)のように伝送線路を高速でスイッチングする差動通信では、リアルタイムでのフィードバック制御が間に合わず、コモンモード電圧の発生を抑制することができないという問題がある。

【0006】

本発明は上記事情に鑑みてなされたものであり、その目的は、信号の伝送速度が速い差動通信においても、コモンモード電圧の発生を適切に抑制できる送信ドライバ回路を提供することにある。

【課題を解決するための手段】

【0007】

請求項1記載の送信ドライバ回路によれば、コモンモード検出手段は、信号出力部が差動信号の電圧レベルを変化させる際に伝送線路に発生するコモンモード電圧又は電流(以下、説明の都合上「コモンモード電圧」とのみ称す)の変化を検出し、その検出レベルをレベルホールドする。そして、制御部は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、信号出力部による電圧の出力状態を調整する。このように構成すれば、制御部が、コモンモード電圧の発生状態に応じてフィードバック制御を行うことで、差動信号を送信する毎にコモンモード電圧を順次低減させることができ、差動信号を高速に伝送する場合でもコモンモード電圧を確実に低減することができるので、ノイズの発生を抑制することが可能となる。

【0008】

請求項2記載の送信ドライバ回路によれば、制御部は、コモンモード電圧の検出レベルが上限基準値を上回ると、信号線の一方の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は信号線の他方の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整する。この場合、信号線の電圧レベルをハイからローに変化させるタイミングが適正なタイミングよりも遅いか、または信号線の電圧レベルをローからハイに変化させるタイミングが適正なタイミングよりも速くなっていることで、コモンモード電圧は上限基準値を上回る山型の波形となっている。したがって、上記の各タイミングをそれぞれ逆方向に変化させるように調整すれば、山型波形のコモンモード電圧を低減できる。

【0009】

一方、制御部は、コモンモード電圧の検出レベルが下限基準値を下回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより速くするように調整する。この場合、信号線の電圧レベルをハイからローに変化させるタイミング,または信号線の電圧レベルをローからハイに変化させるタイミングが山型の場合と逆になっていることで、コモンモード電圧は下限基準値を下回る谷型の波形となっている。したがって、上記の各タイミングをそれぞれ逆方向に変化させるように調整すれば、谷型波形のコモンモード電圧を低減できる。

【0010】

請求項3記載の送信ドライバ回路によれば、制御部は、検出レベルと上限基準値との差又は検出レベルと下限基準値との差に応じて、信号出力部による電圧の出力状態を調整する。すなわち、信号出力部による電圧の出力状態の調整量は、コモンモード電圧の検出レベルと基準値との差に応じて決まるので、コモンモード電圧を低減するための調整をより短時間に完了することができる。

【0011】

請求項4記載の送信ドライバ回路によれば、制御部は、検出レベルが上限基準値以内であり、且つ下限基準値以内である場合は、以降に自身の動作を停止させる。この場合、コモンモード電圧が発生しているとしても許容範囲内にあると考えられるので、その時点での信号出力部による電圧の出力状態を維持すれば良く、以降に制御部が調整を行う必要はない。したがって、制御部の動作を停止させて消費電力を低減することができる。

【0012】

請求項5記載の送信ドライバ回路によれば、制御部は、コモンモード検出手段による検出レベルを、オフセット検出手段により検出された差動信号電圧のDCオフセットレベルに基づき補正した値を上限基準値及び下限基準値と比較する。すなわち、伝送線路の信号線に実際に付与されているハイ,ローレベルの電圧の状態によっては、DCオフセットが発生している場合がある。そこで、制御部が、コモンモード検出手段による検出レベルをDCオフセットレベルに基づき補正すれば、コモンモード電圧の発生状態をより正確に検出することができる。

【0013】

請求項6記載の送信ドライバ回路によれば、コモンモード検出手段は、コモンモード電圧の微分値を検出し、制御部は、その微分値の検出レベルを上限基準値及び下限基準値と比較する。このように構成すれば、コモンモード電圧の変化率の大きさを検出できるので、請求項5のようにDCオフセットレベルを検出して補正する必要が無くなる。

【0014】

請求項7記載の送信ドライバ回路によれば、制御部は、ピークホールド手段によって検出されたコモンモード電圧のピーク値を上限基準値と比較すると共に、ボトムホールド手段によって検出されたコモンモード電圧のボトム値を下限基準値と比較する。したがって、コモンモード電圧が変化した場合の波形のピーク値,ボトム値を検出して、コモンモード電圧が発生している場合の波形振幅の大きさを正確に捉えることができる。

【0015】

請求項8記載の送信ドライバ回路によれば、制御部は、ピーク値が上限基準値を上回ると共にボトム値が下限基準値を下回ると両者の平均値を求め、その平均値が、一対の信号線間の中間基準電位よりも高いか或いは低いかに応じて、コモンモード電圧を低減するための調整方向を決定する。すなわち、このケースでは、コモンモード電圧の波形が正側と負側とに大きなピークを有する山谷型となっているので、両者の平均値を中間基準電位と比較した結果に応じて調整方向を決定すれば、ノイズの発生原因としてより影響が大きい方の波形振幅を低減するように調整できる。

【0016】

請求項9記載の送信ドライバ回路によれば、第1計時手段は、信号出力部が差動信号の電圧レベルを変化させる際に、伝送線路の一方の電位が低下を開始した時点から計時を開始し、第2計時手段は、伝送線路の他方の電位が上昇を開始した時点から計時を開始し、それぞれの伝送線路の電位が互いに等しくなった時点で計時を停止させて第1時間及び第2時間をそれぞれ計時する。制御部は、第1時間と第2時間との差である第1時間差を求めると、第1時間差が正であれば第1時間差と第1基準値とを比較し、第1時間差が負であれば第2時間と第1時間との差である第2時間差を求めて第2基準値とを比較する。その結果、第1時間差が第1基準値を上回るか又は第2時間差が第2基準値を上回ると、次回の信号送信時に発生するコモンモード電圧又は電流を低減するように、信号出力部による電圧の出力状態を調整する。

【0017】

すなわち、第1時間と第2時間とが等しい場合は、伝送線路の一方の電位が低下する速度と、伝送線路の他方の電位が上昇する速度とが等しくなっているのでコモンモード電圧は発生せず、第1時間と第2時間とが異なればコモンモード電圧が発生する。そして、第1時間差(>0)が第1基準値を上回った場合の波形は山型であり、第2時間差(>0)が第2基準値を上回っていれば波形は谷型であるから、それぞれの波形に応じて信号出力部による電圧の出力状態をフィードバック制御すれば、コモンモード電圧を低減するように調整できる。

【0018】

請求項10記載の送信ドライバ回路によれば、制御部は、第1時間差が第1基準値を上回ると、信号線の一方の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は信号線の他方の電圧レベルをローからハイに変化させるタイミングをより速くするように調整する。また、第2時間差が第2基準値を上回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整する。このように調整すれば、請求項2と同様にして、コモンモード電圧の波形に応じて当該電圧を低減するよう調整できる。

【0019】

請求項11記載の送信ドライバ回路によれば、制御部は、第1時間差と第1基準値との差又は第2時間差と第2基準値との差とに応じて、信号出力部による電圧の出力状態を調整する。したがって、請求項3と同様に、コモンモード電圧を低減するための調整を、より短時間に完了することができる。

【0020】

請求項12記載の送信ドライバ回路によれば、制御部は、第1時間差が第1基準値以内であり、又は第2時間差が第2基準値以内である場合は、以降に自身の動作を停止させる。したがって、請求項4と同様に、制御部が調整を行う必要はない場合に動作を停止させて消費電力を低減することができる。

【0021】

請求項13記載の送信ドライバ回路によれば、信号出力部は、高電位点又は低電位点と信号線との間に接続される駆動用半導体スイッチング素子をスイッチングさせて差動信号の電圧レベルを変化させ、また、高電位点又は低電位点と駆動用半導体スイッチング素子の制御端子との間に接続される制御用半導体スイッチング素子をスイッチングさせて、前記制御端子に出力する制御電圧を変化させる。そして、高電位点又は低電位点と、制御用半導体スイッチング素子との間に接続される抵抗素子の抵抗値を調整するので、これにより、駆動用半導体スイッチング素子の制御端子に通電する経路の抵抗値を変化させて、信号線の電圧レベルを変化させるタイミングを変更することができる。

【0022】

請求項14記載の送信ドライバ回路によれば、信号出力部は、高電位点又は低電位点と信号線との間に接続される半導体スイッチング素子をスイッチングさせて差動信号の電圧レベルを変化させ、高電位点又は低電位点と、半導体スイッチング素子との間に接続される抵抗素子の抵抗値を調整可能に構成されている。これにより、半導体スイッチング素子が信号線のレベルをハイ,ロー間で変化させる場合に、信号線と高電位点又は低電位点との間で通電する経路の抵抗値を変化させて、信号線の電圧レベルを変化させるタイミングを変更することができる。

【0023】

請求項15記載の送信ドライバ回路によれば、信号出力部は、高電位点又は低電位点と信号線との間に接続される半導体スイッチング素子をスイッチングさせて差動信号の電圧レベルを変化させ、制御信号の入力端子と、半導体スイッチング素子の制御端子との間に接続される複数個の遅延素子を備え、複数個の遅延素子の直列接続数を変更可能に構成されている。このように構成すれば、制御信号が半導体スイッチング素子の制御端子に入力される経路の遅延時間を変化させて、信号線の電圧レベルを変化させるタイミングを変更することができる。

【図面の簡単な説明】

【0024】

【図1】第1実施例であり、送信ドライバ回路の構成を概略的に示す図

【図2】(a)は通信プロトコルがFlexRayである場合の伝送線路のドライブ状態を示す図、(b)はコモンモード電圧の検出結果に応じたフィードバック制御を説明する図

【図3】信号処理回路による制御内容を概略的に示すフローチャート

【図4】送信ドライバ回路の構成をより具体的に示す図

【図5】コモンモード電圧をサンプル/ホールドするタイミングを示す図

【図6】(a)はコモンモード電圧が「山型」,「谷型」の場合の波形を示す図、(b)はステップS3,S5の内容をより詳細に示す図

【図7】通信信号出力回路並びにゲート駆動部を構成する各MOSFETのオンオフ状態をモデル的に示す図

【図8】第2実施例を示す図4相当図

【図9】第3実施例を示す図4相当図

【図10】第4実施例を示す図4相当図

【図11】ピーク/ボトムホールド回路の具体構成を示す図

【図12】図5相当図

【図13】図6相当図

【図14】第5実施例を示す図4相当図

【図15】第6実施例を示す図6(b)相当図

【図16】第7実施例を示す図6(b)相当図

【図17】第8実施例を示す図4相当図

【図18】図12相当図

【図19】第9実施例を示す図4相当図

【図20】電圧変化時間検出回路の詳細構成を示す図

【図21】タイミングチャート

【図22】図6(b)相当図

【図23】第10実施例を示す図19相当図

【図24】図21相当図

【発明を実施するための形態】

【0025】

(第1実施例)

以下、第1実施例について図1ないし図7を参照して説明する。先ず、本発明の概略を、図1ないし図3を参照して説明する。図1は、送信ドライバ回路の構成を概略的に示している。送信ドライバ回路1は、通信信号出力回路2,レベルホールド回路(コモンモード検出手段)3,信号処理回路(制御部)4で構成されている。通信信号出力回路2は、外部より与えられる制御信号に応じて、一対の信号線BP,BMからなる伝送線路5をハイレベル,又はローレベルにドライブすることで、差動信号を出力する。また、通信信号出力回路2は上記のように伝送線路5をドライブする際に、信号線BP,BMに対する電圧の出力状態を調整可能に構成されている。ここでの「電圧の出力状態」とは、ドライブを開始するタイミングや、電圧の立ち上り,立下りの傾きや、ハイレベル,ローレベルのピーク値等を言う。

【0026】

レベルホールド回路3は、信号線BP,BM間に接続されており、伝送線路5に発生するコモンモード電圧のレベルをホールドして信号処理回路4に出力する。信号処理回路4は、マイクロコンピュータで構成されており、レベルホールド回路3より与えられるコモンモード電圧のレベルに応じて、次回に差動信号を送信する際に通信信号出力回路2を制御する。すなわち、上述のように通信信号出力回路2が伝送線路5をドライブする際に、信号線BP,BMに対する電圧の出力状態を調整してコモンモード電圧が低減するようにフィードバック制御する。

【0027】

ここで、図2(a)は、通信プロトコルがFlexRayである場合の伝送線路5のドライブ状態を示している。FlexRayでは、同図に示すように信号の状態がData1(ハイレベル),Data0(ローレベル)間で変化する場合に、信号線BP,BMの電位が反転するようにドライブが行われる。すると、双方の電位が等しくなる電圧波形のクロスポイント付近のタイミングでコモンモード電圧Vcomが発生することが多い。例えば、電源Vcc(高電位点)が5Vで信号線BP,BMの中間基準電位が2.5Vである場合、コモンモード電圧Vcomは数10mV程度の振幅で、30n〜40n秒程度の時間発生する。そこで本実施例では、図2(b)に示すように、コモンモード電圧Vcomの検出結果に応じて、信号処理回路4が次回に差動信号を送信する際に通信信号出力回路2を制御することで、コモンモード電圧Vcomを順次低減させるようにフィードバック制御する。

【0028】

図3は、信号処理回路4によるフィードバック制御の内容を概略的に示すフローチャートである。先ず、レベルホールド回路3より与えられるコモンモード電圧をA/D変換して読み込み、コモンモード電圧が山型/谷型の何れの波形であるかを判断する(ステップS1)。山型とは、コモンモード電圧が伝送線路5の中間電位を上回る振幅方向に発生する場合であり、谷型とは、コモンモード電圧が伝送線路5の中間電位を下回る振幅方向に発生する場合である。

山型である場合はステップS2に移行して、コモンモード電圧が上限基準値以内か否かを判断する。上限基準値以内であれば(YES)、ノイズとしての影響は無視できる程度であるから処理を終了する(「開始」に戻る)。一方、コモンモード電圧が上限基準値を超えていれば(NO)、次回の信号送信時にコモンモード電圧を低下させる方向に通信信号出力回路2を調整する(ステップS3)。

【0029】

また、ステップS1においてコモンモード電圧が谷型である場合はステップS4に移行して、コモンモード電圧が下限基準値以内か否かを判断する。下限基準値以内であれば(YES)処理を終了し、下限基準値を下回っていれば(NO)、次回の信号送信時にコモンモード電圧を上昇させる方向に通信信号出力回路2を調整する(ステップS5)。以上のようにしてフィードバック制御を繰り返すことで、図2(b)に示すように(山型の場合)コモンモード電圧を低減することが可能となる。

【0030】

図4は、図1に示す送信ドライバ回路1の構成をより具体的に示したものである。図4(a)において、通信信号出力回路2は、4つのMOSFET11PP,11PN,11MP,11MN(駆動用半導体スイッチング素子)からなる駆動素子部12と、駆動素子部12の各MOSFET11にゲート信号を出力するゲート駆動部13PP,13PN,13MP,13MNとで構成されている。ゲート駆動部13PP,13PNには、外部からの制御信号がNOTゲート50P,50Nを介して与えられており、ゲート駆動部13MP,13MNには、前記制御信号がそのまま与えられている。また、ゲート駆動部13PP〜13MNには、信号処理回路4からのスイッチ切替え信号が個別に与えられている。上記制御信号は、信号処理回路4にも入力されている。

【0031】

電源Vccとグランド(低電位点)との間には、PチャネルMOSFET11PP及びNチャネルMOSFET11PNの直列回路と、PチャネルMOSFET11MP及びNチャネルMOSFET11MNの直列回路とが接続されている。PチャネルMOSFET11PP及びNチャネルMOSFET11PNの共通接続点(ドレイン)は信号線BPに接続されており、PチャネルMOSFET11MP及びNチャネルMOSFET11MNの共通接続点(ドレイン)は信号線BMに接続されている。

【0032】

信号線BP,BMの間には、サンプルホールド回路3Sを構成する抵抗素子14a及び14bの直列回路が接続されており、それらの共通接続点は、オペアンプ15の非反転入力端子に接続されている。オペアンプ15の反転入力端子は、抵抗素子16及び17,コンデンサ18の直列回路を介してグランドに接続されており、また、互いに接続方向が異なる2つのダイオード19及び20を介してオペアンプ15の出力端子に接続されている。これらのダイオード19及び20は、オペアンプ15の出力レベルを制限するために配置されている。そして、オペアンプ15の出力端子は、スイッチ21を介して抵抗素子16及び17の共通接続点に接続されており、その共通接続点は信号処理回路4の入力端子に接続されている。スイッチ21のオンオフ制御は、信号処理回路4によって行われる。

【0033】

また、図4(b)は、ゲート駆動部13の内部回路を示している。尚、ゲート駆動部13PP,13PN,13MP,13MNの構成は何れも共通であるため、モデル的に1つだけを示す。電源Vccとグランドとの間には、駆動素子部12の何れかのMOSFET11のゲート(制御端子)には、PチャネルMOSFET22P及びNチャネルMOSFET22N(制御用半導体スイッチング素子)のドレインが接続されている。そして、電源VG(=Vccでも良い)とPチャネルMOSFET22Pのソースとの間には、スイッチ及び抵抗素子の直列回路を複数並列に接続して構成される抵抗アレイ部RApが接続されており、NチャネルMOSFET22Nのソースとグランドとの間には、同様にスイッチ及び抵抗素子の直列回路を複数並列に接続して構成される抵抗アレイ部RAnが接続されている。そして、信号処理回路4は、抵抗アレイ部RAp,RAnに個別の切替え信号を与えて、それらのスイッチのオンオフを切り替える。

【0034】

次に、本実施例の作用について図5及び図6も参照して説明する。図5は、通信信号出力回路2に与えられる制御信号のレベルがロー,ハイ,ローに変化することで、伝送線路5の差動信号がData1,Data0,Data1に変化する場合に、サンプルホールド回路3がコモンモード電圧をサンプル/ホールドするタイミングを示している。制御信号のレベルがローの場合、ゲート駆動部13PP,13PNにはハイレベルの信号が与えられ、ゲート駆動部13MP,13MNにはローレベルの信号が与えられる。これにより、ゲート駆動部13PP,13PNではPチャネルMOSFET22Nがオンとなっており、ゲート駆動部13MP,13MNではNチャネルMOSFET22Pがオンとなっている。その結果、駆動素子部12でPチャネルMOSFET11PPがオン、NチャネルMOSFET11MNがオンするので、信号線BPのレベルがハイ,信号線BMのレベルはローとなっている((a),(b)参照)。

【0035】

そして、制御信号のレベルがローからハイに変化すると、上記の各信号の状態が反転するので、信号線BPのレベルがロー,信号線BMのレベルはハイに変化する((a),(b)参照)。コモンモード電圧は、制御信号の立ち上り,立下りのタイミングから若干の遅延の後、信号線BP,BMの電圧が変化して双方のレベルが同一となるクロスポイントの付近で発生する((c)参照)。

【0036】

コモンモード電圧が発生する場合とは、上記のクロスポイントが中間基準電位(例えば2.5V)から変動した場合であり、サンプルホールド回路3Sのオペアンプ15の出力端子には、上記中間基準電位から変動した電圧が山型,谷型に出力される。そこで、信号処理回路4は、制御信号の立ち上りタイミングを起点として、立下りタイミングに係る前後にサンプルホールド回路3のスイッチ21を一定期間オンさせるようにモノパルス信号を出力し、コモンモード電圧のレベルをサンプリングさせる((d)参照)。

【0037】

図6(b)は、図3で示したフローチャートのステップS3,S5の内容を、図4に示す構成に合わせてより詳細にしたものである。尚、図6(a)は、コモンモード電圧Vcomが「山型」の場合,「谷型」の場合の波形を示す。コモンモード電圧が上限基準値を超えた場合のステップS3では、ゲート駆動部13PP(BP_Pch),13PN(BP_Nch),13MP(BM_Pch),13MN(BM_Nch)がそれぞれ内蔵する抵抗アレイ部RAp,RAnのスイッチを(1)〜(8)に示すように切り替えることで駆動素子部12の各MOSFET11のゲート抵抗値を変化させ、次回の信号送信時に発生するコモンモード電圧の振幅を低減させる。

【0038】

尚、各ゲート駆動部13における抵抗アレイ部RAp,RAnの初期状態では、例えばスイッチの半分程度をオンさせており、この状態からスイッチをオンさせる数を増やせば抵抗値が低下し、スイッチをオンさせる数を減らせば抵抗値が上昇することになる。具体的には、各ゲート駆動部13における抵抗アレイ部RApの抵抗値を大きくするようにスイッチをオンさせる数を減らし、抵抗アレイ部RAnの抵抗値を小さくするようにスイッチをオンさせる数を増やす。また、これら(1)〜(8)は必ずしも全て同時に実行する必要はなく、少なくとも1つ以上を実行すれば良い。一方、コモンモード電圧が下限基準値を超えた場合のステップS5では、(1)〜(8)における抵抗アレイ部RAp,RAnの抵抗値の大小変化を逆にする。

【0039】

ここで、図7は、ステップS3,S5における抵抗アレイ部RAp,RAnの抵抗値の切替えを説明するため、通信信号出力回路2並びにゲート駆動部13を構成する各MOSFETのオンオフ状態をモデル的に示したもので、信号線BPがハイレベル,信号線BMがローレベルとなる場合である。信号線BP側のゲート駆動部13ではNチャネルMOSFETがオンしており、信号線BM側のゲート駆動部13ではPチャネルMOSFETがオンしている。

【0040】

この時、図5に示すように、信号線BPのレベルがローからハイ,信号線BPのレベルがハイからローに変化するタイミングでコモンモード電圧が上限基準値を超えた際に想定されるのは、信号線BP側の電位変化のタイミングが相対的に速いか、信号線BM側の電位変化のタイミングが相対的に遅い場合である。したがって、コモンモード電圧のレベルを低減するには、信号線BP,BMの電位変化のタイミングが上記と逆方向となるように調整すれば良い。

【0041】

そこで、ステップS3において上述のように各部の抵抗値を調整することで、信号線BP側については、例えばPチャネルMOSFET11PPのオンタイミングを遅延させる方向に、NチャネルMOSFET11PNのオフタイミングを速める方向に調整する。一方、信号線BM側については、PチャネルMOSFET11MPのオフタイミングを遅延させる方向に、NチャネルMOSFET11MNのオンタイミングを速める方向に調整する。これにより、信号線BP側の電位変化を相対的に遅くし、信号線BM側の電位変化を相対的に速くするように変化させる。

【0042】

また、コモンモード電圧が下限基準値を超えた際に想定されるのは、信号線BP側,BM側の電位変化タイミングの相対的な遅速関係が上限基準値を超えた場合と逆になるので、ステップS5においては、例えば信号線BP側の電位変化を相対的に速くし、信号線BM側の電位変化を相対的に遅くするように変化させる。尚、ここで述べた電位変化の遅速関係は、信号線BPのレベルがハイからローに,信号線BPのレベルがローからハイに変化するタイミングについては逆になるが、結果としてステップS3,S5における調整方向がそのまま適用される。

【0043】

また、図6(b)に示す処理を繰り返し実行する際に、次回は、今回の各抵抗値の設定を維持した状態を基準として、抵抗値を変化させる方向を決定する。例えば、今回の処理でコモンモード電圧が上限基準値を超えた結果、ステップS3中の何れか1つのスイッチ切替えを行い、次回の処理でもコモンモード電圧が上限基準値を超えている場合は、上記スイッチの切替えは維持したまま他の(1)〜(8)の何れかのスイッチ切替えを追加するか、若しくは今回切り替えたものと同じスイッチが属する抵抗アレイ部RAについて、スイッチ切替え数をより多くすることで対応する。

【0044】

以上のように本実施例によれば、レベルホールド回路3(サンプルホールド回路3S)は、通信信号出力部2が差動信号の電圧レベルを変化させる際に伝送線路5に発生するコモンモード電圧の変化を検出し、その検出レベルをレベルホールドする。そして、信号処理回路4は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整する。すなわち、信号処理回路4が、コモンモード電圧の発生状態に応じてフィードバック制御を行うことでコモンモード電圧を順次低減させて、差動信号を高速に伝送する場合でもコモンモード電圧を確実に低減することができ、ノイズの発生を抑制することが可能となる。

【0045】

そして、信号処理回路4は、コモンモード電圧の検出レベルが上限基準値を上回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整することで、コモンモード電圧が山型の波形となっている場合に当該電圧を低減できる。

また、信号処理回路4は、コモンモード電圧の検出レベルが下限基準値を下回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより速くするように調整することで、コモンモード電圧が谷型の波形となっている場合に当該電圧を低減できる。

【0046】

更に、通信信号出力部2は、電源Vccとグランドとの間に接続されるMOSFET11PP,11PN,11MP,11MNをスイッチングさせて差動信号の電圧レベルを変化させ、また、電源VG又はグランドとMOSFET11のゲートとの間に接続されるMOSFET22をスイッチングさせて、前記ゲートに出力する制御電圧を変化させる。この場合、電源VG又はグランドとMOSFET22との間における通電経路の抵抗値を調整することになるので、これにより、MOSFET11のゲートに通電する経路の抵抗値を変化させて、信号線の電圧レベルを変化させるタイミングを変更することができる。

【0047】

(第2実施例)

図8は第2実施例であり、第1実施例と同一部分には同一符号を付して説明を省略し、以下異なる部分について説明する。第2実施例の送信ドライバ回路23は、第1実施例ではゲート駆動部13に配置していた抵抗アレイ部RAp,RAnを、駆動素子部24の内部に配置した構成となっている。尚、図8は信号線BP側のみを示しているが、信号線BP側についても同様に構成されている。すなわち、電源VccとPチャネルMOSFET11PP,11MPのソースとの間,NチャネルMOSFET11PN,11MNのソースとグランドとの間に抵抗アレイ部RAp,RAnが挿入されており、信号処理回路4は、それらのスイッチを切り替えて各MOSFET11のソース側の抵抗値を第1実施例と同様に切り替える。

【0048】

以上のように構成される第2実施例によれば、送信ドライバ回路23は、電源VccとPチャネルMOSFET11PP,11MPのソースとの間,NチャネルMOSFET11PN,11MNのソースとグランドとの間に挿入した抵抗アレイ部RAp,RAnの抵抗値を変化させて、信号線BP,BMの電圧レベルを変化させるタイミングを変更するので、第1実施例と同様に制御することで、コモンモード電圧の発生レベルを低減するように調整できる。

【0049】

(第3実施例)

図9は第3実施例であり、第1実施例と異なる部分のみ説明する。図9に示すサンプルホールド回路3Sでは、抵抗素子14a及び14b(オフセット検出手段)の共通接続点がコンデンサ25(オフセット検出手段)を介してグランドに接続されていると共に、信号処理回路4aの入力端子に接続されている。以上が送信ドライバ回路26を構成している。信号処理回路4aは、上記入力端子の電圧をA/D変換して読み込むことで、コモンモード電圧のDCオフセット分を考慮することができる。すなわち、各回路素子の定数ずれ等により、信号線BP,BM間の中間基準電位が必ずしも2.5Vを示さない場合があるので、信号処理回路4aがステップS1においてコモンモード電圧のサンプルホールド値を読み込んだ際に、DCオフセット分を考慮して補正することでコモンモード電圧をより正確に把握できる。

以上のように第3実施例によれば、信号処理回路4aは、サンプルホールド回路3Sによる検出レベルを、抵抗素子14a及び14bの共通接続点に与えられる差動信号電圧のDCオフセットレベルに基づき補正した値を上限基準値及び下限基準値と比較するので、コモンモード電圧の発生状態をより正確に検出することができる。

【0050】

(第4実施例)

図10ないし図13は第4実施例を示すものであり、第3実施例と異なる部分を説明する。図10に示す送信ドライバ回路27は、サンプルホールド回路3Sに替えてピーク/ボトムホールド回路3PBが配置されている。そして、ピーク/ボトムホールド回路3PBより出力されるピークホールド値及びボトムホールド値は、信号処理回路4に替わる信号処理回路(制御部)28に入力されている。

【0051】

図11は、ピーク/ボトムホールド回路3PBの具体構成を示す。ピーク/ボトムホールド回路3PBは、ピークホールド回路3P(ピークホールド手段)と、ボトムホールド回路3B(ボトムホールド手段)とで構成されている。ピークホールド回路3Pは、非反転入力端子が抵抗素子14a及び14bの共通接続点に接続されるオペアンプ29Pと、オペアンプ29Pの出力端子がダイオード30Pを介して非反転入力端子に接続されるオペアンプ31Pとを備えている。

【0052】

オペアンプ31Pの出力端子は、自身及びオペアンプ29Pの反転入力端子に接続されていると共に、信号処理回路28の入力端子に接続されている。また、オペアンプ29Pの反転入力端子は、ダイオード32Pを介して自身の出力端子に接続されている。オペアンプ31Pの非反転入力端子とグランドとの間には、抵抗素子33P及びコンデンサ34Pの直列回路と、スイッチ35Pとが接続されている。スイッチ35Pは、ピークレベル保持用のコンデンサ34Pを放電させてリセットするためにオンされ、そのオンオフ制御は信号処理回路28によって行われる。

【0053】

一方、ボトムホールド回路3Bは、ピークホールド回路3Pと略対象に構成されており、対応する構成には符号Pに替えて符号Bを付して示している。但し、ダイオード30B,32Bの接続方向は、ピークホールド回路3Pのダイオード30P,32Pとは逆になっている。

【0054】

次に、第4実施例の作用について図12及び図13も参照して説明する。図12は、第1実施例の図5相当図であり、信号処理回路28がピークホールド回路3P,ボトムホールド回路3Bによってピークホールド,ボトムホールドを行わせるタイミング,すなわちスイッチ35P,35Bをオン→オフ(ホールド)→オン(リセット)に切り替えるタイミングを(d)に示す。この場合、ホールド期間の始期は第1実施例のサンプルホールドタイミングに等しく設定されるが、ホールド期間の終期は、コモンモード電圧が発生している期間よりも確実に長くなるように、第1実施例のサンプルホールドタイミングよりも遅くなっている。第4実施例では、コモンモード電圧のピーク値とボトム値を検出することで、当該電圧振幅が山谷型,谷山型に変化する場合(図6(a)参照)についても対応する。

【0055】

図13は図6相当図であり、図13(a)には、コモンモード電圧が山谷型,谷山型に変化する場合の波形を示している。すなわち、これらは何れも、電圧波形が中間基準電位に対して高低方向に変動するもので、山谷型とは、山側のピーク値が谷側のボトム値よりも大きい場合を称し、谷山型とは、逆に谷側のボトム値が山側のピーク値よりも大きい場合を称する。

【0056】

図13(b)において、信号処理回路28は、ピークホールド回路3Pからのピークホールド値を読取ると(ステップS11)、ステップS2においてそのピークホールド値が上限基準値以内か否か判断する。また、信号処理回路28は、ボトムホールド回路3Bからのボトムホールド値を読取ると(ステップS12)、ステップS4においてそのボトムホールド値が下限基準値以内か否か判断する。尚、図13(b)では、ステップS11及びステップS2の処理と、ステップS12及びステップS4の処理とが並列に実行されるように示されているが、実際にはこれらはシリアルに実行される。

【0057】

そして、ステップS2,S4の少なくとも一方で「NO」と判断すると、信号処理回路28は、ピークホールド値とボトムホールド値との平均をとり、中間基準電位Vrefと比較する(ステップS13)。(平均値>Vref)であればコモンモード電圧は山谷型であるからステップS3を実行し、(平均値<Vref)であればコモンモード電圧は谷山型であるからステップS5を実行する。それから、コンデンサ34を放電させて(ステップS15)ステップS11,S12に戻る。尚、図示はしないが、ステップS14において(平均値=Vref)の場合はそのままステップS15に移行する。

【0058】

以上のように第4実施例によれば、信号処理回路28は、ピークホールド回路3Pによって検出されたコモンモード電圧のピーク値を上限基準値と比較すると共に、ボトムホールド回路3Bによって検出されたコモンモード電圧のボトム値を下限基準値と比較する。したがって、コモンモード電圧が変化した場合の波形のピーク値,ボトム値を検出して、コモンモード電圧が発生している場合の波形振幅の大きさを正確に捉えることができる。

【0059】

そして、信号処理回路28は、ピーク値が上限基準値を上回ると共にボトム値が下限基準値を下回ると両者の平均値を求め、その平均値が、一対の信号線間の中間基準電位よりも高いか或いは低いかに応じてコモンモード電圧を低減するための調整方向を決定するので、ノイズの発生原因としてより影響が大きい側の波形振幅を低減するように調整できる。

【0060】

(第5実施例)

図14は第5実施例である。第5実施例はゲート駆動部13に替わるゲート駆動部36の構成を示す。ゲート駆動部36は、直列に接続される2n個(nは2以上の自然数)のNOTゲート(遅延素子)37と、これらのうち初段のNOTゲート37の入力端子と、そこから2個先き毎のNOTゲート37の入力端子と、最後段のNOTゲート37の出力端子とにそれぞれ一端が接続される(n+1)個のスイッチ38とで構成されている。n個のスイッチ38の他端は共通に接続されており、外部からの制御信号が与えられる。そして、スイッチ38のオンオフ制御は信号処理回路4,4A,28等により制御される。

【0061】

以上のように構成される第5実施例によれば、ゲート駆動部36は、制御信号の入力端子と、MOSFET11のゲートとの間に接続される2n個のNOTゲートを備え、それらの直列接続数を2個単位で変更可能に構成されるので、例えば信号処理回路4が(n+1)個のスイッチ38のうち何れか1つをオンすることで、駆動素子部12にゲート信号を出力するタイミングに異なる遅延時間を付与することができる。また、遅延素子としては、その他ディレイライン等を用いても良く、この場合は素子の直列接続数を少なくとも1個ずつ変化させるように切り替えれば良い。

【0062】

(第6実施例)

図15は第6実施例を示す図6(b)相当図であり、ステップS3,S5に替えてステップS21,S22が配置されている。第6実施例では、ステップS2で「NO」と判断すると、ステップS21においてサンプルホールド値と上限基準値との差を求める。そして、その差の値から、コモンモード電圧が上限基準値以内となる第1実施例におけるゲート抵抗値や、第2実施例における駆動素子部24の出力抵抗値,若しくは第5実施例における遅延時間を求め、スイッチの切り替えを行う。また、ステップS4で「NO」と判断した場合も、ステップS22においてサンプルホールド値と下限基準値との差を求め、その差の値から、コモンモード電圧が下限基準値以内となるゲート抵抗値等を求め、スイッチの切り替えを行う。尚、上記の抵抗値や遅延時間については、予めシミュレーションや実測などにより求めておくようにする。

【0063】

以上のように第6実施例によれば、信号処理回路28は、検出レベルと上限基準値との差又は検出レベルと下限基準値との差に応じて、信号出力部による電圧の出力状態を調整する。通信信号出力部2による電圧の出力状態の調整量は、コモンモード電圧の検出レベルと基準値との差に応じて決まるので、したがって、コモンモード電圧を低減するための調整を、より短時間に完了することができる。尚、第6実施例を第4実施例に適用する場合には、放電用のスイッチ35は不要である。

【0064】

(第7実施例)

図16は第7実施例を示す図6(b)相当図である。第7実施例では、ステップS2,S4で「YES」と判断すると、処理を終了する前に信号処理回路4(又は4a,28)の動作を自身で停止させる(ステップS31,S32)。すなわち、この場合はデフォルトの設定,若しくはフィードバック制御を何回か実行した段階でコモンモード電圧の発生レベルが基準値以内となっているので、以降に信号処理回路4等が調整を行う必要が無い。したがって、信号処理回路4等の動作を停止させて消費電力を低減する。

以上のように第7実施例によれば、信号処理回路4は、検出レベルが上限基準値以内であり、且つ下限基準値以内である場合は、以降に自身の動作を停止させるので、信号処理回路4が調整を行う必要はない場合に、不要な電力消費を低減することができる。

【0065】

(第8実施例)

図17及び図18は第8実施例を示すものであり、第4実施例と異なる部分を説明する。第8実施例の送信ドライバ回路37は、第4実施例の送信ドライバ回路27におけるピーク/ボトムホールド回路3PBの内部に、微分回路38を追加した構成となっている。微分回路38は、周知のようにオペアンプ38aと、コンデンサ38bと、抵抗素子38cとで構成されており、微分回路38の入力端子は抵抗素子14a及び14bの共通接続点に接続されており、出力端子はピークホールド回路3P,ボトムホールド回路3Bの入力端子に接続されている。

【0066】

次に、第8実施例の作用について図18を参照して説明する。図18は図12相当図であり、図18(d)には、微分回路38より出力されるコモンモード電圧の微分波形を示している。図18(c)に示す山型の電圧波形の場合、その微分波形は山谷型となるので、山のピークレベルと谷のボトムレベルとが検出される。したがって、第8実施例の処理は、第4実施例の図13(b)に示すフローチャートと同様になる。

以上のように第8実施例によれば、ピーク/ボトムホールド回路3PBの内部に微分回路38を配置してコモンモード電圧の微分値を検出し、信号処理回路28は、その微分値の検出レベルを上限基準値及び下限基準値と比較するので、コモンモード電圧の変化率の大きさを検出でき、第3実施例のようにDCオフセットを検出して補正する必要が無くなる。

【0067】

(第9実施例)

図19ないし図22は第9実施例を示すものである。第9実施例の送信ドライバ回路41は、レベルホールド回路3に替えて電圧変化時間検出回路42を備えており、図20は、その電圧変化時間検出回路42の詳細構成を示している。電圧変化時間検出回路42は、ハイ側時間検出回路42H(第1計時手段)と、ロー側時間検出回路42L(第2計時手段)とで構成されている。電源とグランドとの間には、電流源43(P,M)と、スイッチ44(P,M)と、コンデンサ45(P,M)との直列回路が接続されている。コンパレータ46Pは、信号線BPの電位と、比較用の電圧であるBP側基準値とを比較し、前者が後者を下回った場合にハイレベルのStart信号をスイッチ44Pに出力する。BP側基準値は、信号線BPのハイレベル電位よりも若干低いレベルに設定されている(図21(b)参照)。

【0068】

また、コンパレータ46Mは、信号線BMの電位と、比較用の電圧であるBM側基準値とを比較し、前者が後者を上回った場合にハイレベルのStart信号をスイッチ44Mに出力する。BM側基準値は、信号線BMのローレベル電位よりも若干高いレベルに設定されている(図21(b)参照)。そして、コンパレータ46Cは、信号線BPの電位と信号線BMの電位とが同じレベルになると、ハイレベルのStop信号をスイッチ44P,44Mに出力する。スイッチ44P,44Mは、Start信号がハイレベルになるとオンし、その状態からStop信号がハイレベルになるとオフするように構成されている。また、コンデンサ45(P,M)には、スイッチ47(P,M)及び抵抗素子48(P,M)の直列回路が並列に接続されており、スイッチ47(P,M)のオンオフ制御は信号処理回路(制御部)49によって行われる。

【0069】

次に、第9実施例の作用について図21及び図22を参照して説明する。第9実施例では、制御信号がローからハイに変化することで、信号線BPのレベルがハイからローに変化し、且つ信号線BMのレベルがローからハイに変化する期間に、スイッチ47(P,M)のオンオフを制御してコンデンサ45(P,M)を充電する。尚、スイッチ44(P,M)及び47(P,M)は初期状態でオフしており、コンデンサ45(P,M)は放電されて、端子電圧は0Vであるとする。

【0070】

すなわち、上記の期間において、信号線BPのレベルがハイからローへの変化を開始してBP側基準値を下回ると、コンパレータ46PはStart信号をスイッチ44Pに出力し、スイッチ44Pはターンオンする。同時に信号線BMのレベルがローからハイへの変化を開始してBM側基準値を上回ると、コンパレータ46MはStart信号をスイッチ44Mに出力し、スイッチ44Mはターンオンする。これにより、コンデンサ45(P,M)は電流源43(P,M)によって充電される。

【0071】

その状態から、信号線BPの電位と信号線BMの電位とがクロスポイントに達して同じレベルになると、コンパレータ46Cは、Stop信号をスイッチ44(P,M)に出力する。これにより、スイッチ44(P,M)はターンオフしてコンデンサ45(P,M)の充電は停止される。したがって、この時点でのコンデンサ45Pの充電電位は、信号線BPのレベルがハイからローへの変化を開始してからクロスポイントに達するまでの時間に比例し、コンデンサ45Mの充電電位は、信号線BMのレベルがローからハイへの変化を開始してからクロスポイントに達するまでの時間に比例している。

【0072】

図22は、信号処理回路49の処理内容を示すフローチャートである。信号処理回路49は、制御信号のレベルがローからハイに変化すると(ステップS41:YES)、その時点から若干の時間が経過してコンパレータ46CがStop信号を出力した以降のタイミングで、電圧変化時間検出回路42よりコンデンサ45P,45Mの端子電圧(第1,第2時間)をA/D変換して読み込む(ステップS42)。そして、コンデンサ45P(BP側),45M(BM側)の端子電圧の大小を比較し(ステップS43)、(BP側>BM側)であれば(YES)ステップS44に移行し、(BP側<BM側)であれば(NO)ステップS45に移行する。

【0073】

ステップS44では、コンデンサ45Pの端子電圧からコンデンサ45Mの端子電圧を減じた差(第1時間差)が基準値以内か否かを判断し、ステップS45では、逆にコンデンサ45Mの端子電圧からコンデンサ45Pの端子電圧を減じた差(第2時間差)が基準値以内か否かを判断する。そして、ステップS44で「NO」と判断するとステップS5を実行し、ステップS45で「NO」と判断するとステップS3を実行する。

【0074】

ここで、ステップS44で「NO」と判断するケースは、図21(b)に示すように、信号線BP側の電位が低下するタイミングが信号線BMの電位が上昇するタイミングよりも速く、クロスポイントが低電位側にずれてコモンモード電圧が谷型に発生する場合に対応する。したがって、ステップS5を実行する。一方、ステップS45で「NO」と判断するケースは、上記とは逆に、信号線BP側の電位が低下するタイミングよりも信号線BMの電位が上昇するタイミングが速く、クロスポイントが高電位側にずれてコモンモード電圧が山型に発生する場合に対応する。したがって、ステップS3を実行する。ステップS3又はS5の実行後は、スイッチ47P,47Mをオンすることでコンデンサ45P,45Mを放電させる(ステップS46)。それから、ステップS41に戻る。

【0075】

以上のように第9実施例によれば、ハイ側時間検出回路42Hは、通信信号出力部2が差動信号の電圧レベルを変化させる際に、信号線BPの電位が低下を開始した時点から計時を開始し、ロー側時間検出回路42Lは、信号線BMの電位が上昇を開始した時点から計時を開始し、信号線BP,BMの電位が互いに等しくなった時点で計時を停止させて第1時間及び第2時間をそれぞれ計時する。信号処理回路49は、第1時間と第2時間との差である第1時間差を求め、第1時間差が正であれば第1時間差と第1基準値とを比較し、第1時間差が負であれば第2時間差を求めて第2基準値とを比較する。その結果、第1時間差が第1基準値を上回るか又は第2時間差が第2基準値を上回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整するようにした。したがって、コモンモード電圧波形が山型の場合と、谷型の場合とに応じて、通信信号出力部2による電圧の出力状態をフィードバック制御することで、コモンモード電圧を低減するように調整できる。

【0076】

また、信号処理回路49は、第1時間差が第1基準値を上回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより速くするように調整し、第2時間差が第2基準値を上回ると、信号線の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は信号線の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整する。したがって、第1実施例と同様にして、コモンモード電圧の波形に応じて当該電圧を低減するよう調整できる。

【0077】

尚、信号処理回路49にStop信号を入力するようにして、ステップS41では、信号処理回路49は、制御信号のレベルがローからハイに変化した後、コンパレータ46CがStop信号を出力したことを確認してステップS42に移行しても良い。また、第9実施例は、制御信号のレベルがハイからローに変化して、信号線BP,BMのレベル変化が上記と逆になる場合について実施しても良い。

【0078】

(第10実施例)

図23及び図24は第10実施例を示すものであり、第9実施例と異なる部分について説明する。第10実施例の送信ドライバ回路51は、上記実施例のように信号線BP,BM間の電位が反転せず、例えばCANのように差動信号が、中間基準電位(差動電圧0V,レセッシブ)と、信号線BP側が高電位方向に,信号線BM側が低電位方向に変化する(ドミナント)との間で変化する場合に対応した構成となっている。通信信号出力回路52は、電源Vccとグランドとの間に接続される、PチャネルMOSFET53P,抵抗素子54a及び54b,NチャネルMOSFET53N(駆動用半導体スイッチング素子)の直列回路で構成されている。

【0079】

PチャネルMOSFET53Pはゲート駆動部55Pによって駆動され、NチャネルMOSFET53Nはゲート駆動部55Nによって駆動される。ゲート駆動部55P,55Nの構成は、例えば第1実施例のゲート駆動部13と同様であり、それらのスイッチ切替えは、信号処理回路(制御部)56によって行われる。ゲート駆動部55P側には、制御信号がNOTゲート57を介して与えられている。そして、信号線BP,BM間には第9実施例の電圧変化時間検出回路42が接続されている。

【0080】

第10実施例において、電圧変化時間検出回路42は第9実施例と全く同様に動作する。したがって、信号処理回路56も図22に示すフローチャートを実行すれば良い。但し、ステップS3,S5においては、ゲート駆動部BP_Nch,BM_Pchに対応する構成が存在しないので、それらについての制御は行わない。尚、図24(b)に示しているように、制御信号の立下りタイミングでスイッチ44P,44Mをオンして、信号線BP側の電位がBP側基準値を超えた場合にスイッチ44Pをオフし、信号線BM側の電位がBM側基準値を下回った場合にスイッチ44Mをオフして、ステップS42においてコンデンサ45P,45Mの充電電圧を読み込んでも良い。

以上のように第10実施例によれば、差動信号の伝送形態が、CANのようにレセッシブ,ドミナント間で変化する場合についても、第9実施例と同様の効果が得られる。

【0081】

本発明は上記し、又は図面に記載した実施例にのみ限定されるものではなく、以下のような変型又は拡張が可能である。

コモンモード電圧に替えて、コモンモード電流を検出しても良い。

第9実施例において、第1,第2計時手段は、コンデンサ45に替えてカウンタを用いることで、Start信号とStop信号とが出力される時間を計測しても良い。

第9,第10実施例について、第6実施例と同様に、BP側,BM側の端子電圧の差に応じて、ステップS3,S5における調整を一回で行うようにしても良い。

第8ないし第10実施例に、第7実施例を組み合わせて実行しても良い。

半導体スイッチング素子はMOSFETに限ることなく、バイポーラトランジスタを用

いても良い。

【符号の説明】

【0082】

図面中、1は送信ドライバ回路、2は通信信号出力回路、3はレベルホールド回路(コモンモード検出手段)、3Sはサンプルホールド回路(コモンモード検出手段)、3Pはピークホールド回路(ピークホールド手段)、3Bはボトムホールド回路(ボトムホールド手段)、4は信号処理回路(制御部)、5は伝送線路、11はMOSFET(駆動用半導体スイッチング素子)、14は抵抗素子(オフセット検出手段)、22はMOSFET(制御用半導体スイッチング素子)、23は送信ドライバ回路、25はコンデンサ(オフセット検出手段)、26,27は送信ドライバ回路、28は信号処理回路(制御部)、37はNOTゲート(遅延素子)、37は送信ドライバ回路、38は微分回路、41は送信ドライバ回路、42Hはハイ側時間検出回路(第1計時手段)、42Lはロー側時間検出回路(第2計時手段)、49は信号処理回路(制御部)、51は送信ドライバ回路、52は通信信号出力回路、53はMOSFET(駆動用半導体スイッチング素子)、56は信号処理回路(制御部)を示す。

【特許請求の範囲】

【請求項1】

一対の信号線により差動信号を伝送する伝送線路に接続され、前記伝送線路を介して信号を送信するための送信ドライバ回路において、

前記差動信号の電圧をローレベルとハイレベルとの間で変化させる際に、電圧レベルを変化させるタイミングを調整可能に構成される信号出力部と、

この信号出力部が前記差動信号の電圧レベルを変化させる際に前記伝送線路に発生するコモンモード電圧又は電流の変化を検出し、その検出レベルをレベルホールドするコモンモード検出手段と、

前記検出レベルを上限基準値及び下限基準値と比較し、前記検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧又は電流を低減するように、前記信号出力部による前記電圧の出力状態を調整する制御部とを備えたことを特徴とする送信ドライバ回路。

【請求項2】

前記制御部は、前記検出レベルが前記上限基準値を上回ると、前記信号線の一方の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は前記信号線の他方の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整し、

前記検出レベルが前記下限基準値を下回ると、前記信号線の一方の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は前記信号線の他方の電圧レベルをローからハイに変化させるタイミングをより速くするように調整することを特徴とする請求項1記載の送信ドライバ回路。

【請求項3】

前記制御部は、前記検出レベルと前記上限基準値との差又は前記検出レベルと前記下限基準値との差に応じて、前記信号出力部による前記電圧の出力状態を調整することを特徴とする請求項1又は2記載の送信ドライバ回路。

【請求項4】

前記制御部は、前記検出レベルが前記上限基準値以内であり、且つ前記下限基準値以内である場合は、以降に自身の動作を停止させることを特徴とする請求項1ないし3の何れかに記載の送信ドライバ回路。

【請求項5】

差動信号電圧のDCオフセットレベルを検出するオフセット検出手段を備え、

前記制御部は、前記コモンモード検出手段による検出レベルを、前記DCオフセットレベルに基づき補正した値を、前記上限基準値及び前記下限基準値と比較することを特徴とする請求項1ないし4の何れかに記載の送信ドライバ回路。

【請求項6】

前記コモンモード検出手段は、前記コモンモード電圧又は電流の微分値を検出し、

前記制御部は、前記微分値の検出レベルを上限基準値及び下限基準値と比較することを特徴とする請求項1ないし4の記載の送信ドライバ回路。

【請求項7】

前記コモンモード検出手段は、前記コモンモード電圧又は電流について、ピーク値を検出してホールドするピークホールド手段と、ボトム値を検出してホールドするボトムホールド手段とを備え、

前記制御部は、前記ピークホールド手段によって検出されたピーク値を上限基準値と比較すると共に、前記ボトムホールド手段によって検出されたボトム値を下限基準値と比較することを特徴とする請求項1ないし5の何れかに記載の送信ドライバ回路。

【請求項8】

前記制御部は、前記ピーク値が前記上限基準値を上回ると共に前記ボトム値が前記下限基準値を下回ると、前記ピーク値と前記ボトム値との平均値を求め、

前記平均値が、前記一対の信号線間の中間基準電位よりも高いか或いは低いかに応じて、前記コモンモード電圧又は電流を低減するための調整方向を決定することを特徴とする請求項7記載の送信ドライバ回路。

【請求項9】

一対の信号線により差動信号を伝送する伝送線路に接続され、前記伝送線路を介して信号を送信するための送信ドライバ回路において、

前記差動信号の電圧をローレベルとハイレベルとの間で変化させる際に、電圧レベルを変化させるタイミングを調整可能に構成される信号出力部と、

この信号出力部が前記差動信号の電圧レベルを変化させる際に、前記伝送線路の一方の電位が低下を開始した時点から計時を開始する第1計時手段と、前記伝送線路の他方の電位が上昇を開始した時点から計時を開始する第2計時手段と、

前記第1及び第2計時手段が、それぞれの伝送線路の電位が互いに等しくなった時点で計時を停止させることで第1時間及び第2時間をそれぞれ計時すると、前記第1時間と前記第2時間との差である第1時間差を求め、前記第1時間差が正である場合は前記第1時間差と第1基準値とを比較し、

前記第1時間差が負である場合は前記第2時間と前記第1時間との差である第2時間差を求め、前記第2時間差と第2基準値とを比較し、

前記第1時間差が前記第1基準値を上回るか又は前記第2時間差が第2基準値を上回ると、次回の信号送信時に発生するコモンモード電圧又は電流を低減するように、前記信号出力部による前記電圧の出力状態を調整する制御部とを備えたことを特徴とする送信ドライバ回路。

【請求項10】

前記制御部は、前記第1時間差が前記第1基準値を上回ると、前記信号線の一方の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は前記信号線の他方の電圧レベルをローからハイに変化させるタイミングをより速くするように調整し、前記第2時間差が前記第2基準値を上回ると、前記信号線の一方の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は前記信号線の他方の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整することを特徴とする請求項9記載の送信ドライバ回路。

【請求項11】

前記制御部は、前記第1時間差と前記第1基準値との差又は前記第2時間差と前記第2基準値との差とに応じて、前記信号出力部による前記電圧の出力状態を調整することを特徴とする請求項9又は10記載の送信ドライバ回路。

【請求項12】

前記制御部は、前記第1時間差が前記第1基準値以内であり、又は前記第2時間差が前記第2基準値以内である場合は、以降に自身の動作を停止させることを特徴とする請求項9ないし11の何れかに記載の送信ドライバ回路。

【請求項13】

前記信号出力部は、高電位点又は低電位点と前記信号線との間に接続される駆動用半導体スイッチング素子をスイッチングさせて前記差動信号の電圧レベルを変化させ、

高電位点又は低電位点と前記駆動用半導体スイッチング素子の制御端子との間に接続される制御用半導体スイッチング素子をスイッチングさせて、前記制御端子に出力する制御電圧を変化させ、

前記高電位点又は低電位点と、前記制御用半導体スイッチング素子との間に接続される抵抗素子の抵抗値を調整可能に構成されていることを特徴とする請求項1ないし12の何れかに記載の送信ドライバ回路。

【請求項14】

前記信号出力部は、高電位点又は低電位点と前記信号線との間に接続される半導体スイッチング素子をスイッチングさせて前記差動信号の電圧レベルを変化させ、

前記高電位点又は低電位点と、前記半導体スイッチング素子との間に接続される抵抗素子の抵抗値を調整可能に構成されていることを特徴とする請求項1ないし12の何れかに記載の送信ドライバ回路。

【請求項15】

前記信号出力部は、高電位点又は低電位点と前記信号線との間に接続される半導体スイッチング素子をスイッチングさせて前記差動信号の電圧レベルを変化させ、

制御信号の入力端子と、前記半導体スイッチング素子の制御端子との間に接続される複数個の遅延素子を備え、前記複数個の遅延素子の直列接続数を変更可能に構成されていることを特徴とする請求項1ないし12の何れかに記載の送信ドライバ回路。

【請求項1】

一対の信号線により差動信号を伝送する伝送線路に接続され、前記伝送線路を介して信号を送信するための送信ドライバ回路において、

前記差動信号の電圧をローレベルとハイレベルとの間で変化させる際に、電圧レベルを変化させるタイミングを調整可能に構成される信号出力部と、

この信号出力部が前記差動信号の電圧レベルを変化させる際に前記伝送線路に発生するコモンモード電圧又は電流の変化を検出し、その検出レベルをレベルホールドするコモンモード検出手段と、

前記検出レベルを上限基準値及び下限基準値と比較し、前記検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧又は電流を低減するように、前記信号出力部による前記電圧の出力状態を調整する制御部とを備えたことを特徴とする送信ドライバ回路。

【請求項2】

前記制御部は、前記検出レベルが前記上限基準値を上回ると、前記信号線の一方の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は前記信号線の他方の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整し、

前記検出レベルが前記下限基準値を下回ると、前記信号線の一方の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は前記信号線の他方の電圧レベルをローからハイに変化させるタイミングをより速くするように調整することを特徴とする請求項1記載の送信ドライバ回路。

【請求項3】

前記制御部は、前記検出レベルと前記上限基準値との差又は前記検出レベルと前記下限基準値との差に応じて、前記信号出力部による前記電圧の出力状態を調整することを特徴とする請求項1又は2記載の送信ドライバ回路。

【請求項4】

前記制御部は、前記検出レベルが前記上限基準値以内であり、且つ前記下限基準値以内である場合は、以降に自身の動作を停止させることを特徴とする請求項1ないし3の何れかに記載の送信ドライバ回路。

【請求項5】

差動信号電圧のDCオフセットレベルを検出するオフセット検出手段を備え、

前記制御部は、前記コモンモード検出手段による検出レベルを、前記DCオフセットレベルに基づき補正した値を、前記上限基準値及び前記下限基準値と比較することを特徴とする請求項1ないし4の何れかに記載の送信ドライバ回路。

【請求項6】

前記コモンモード検出手段は、前記コモンモード電圧又は電流の微分値を検出し、

前記制御部は、前記微分値の検出レベルを上限基準値及び下限基準値と比較することを特徴とする請求項1ないし4の記載の送信ドライバ回路。

【請求項7】

前記コモンモード検出手段は、前記コモンモード電圧又は電流について、ピーク値を検出してホールドするピークホールド手段と、ボトム値を検出してホールドするボトムホールド手段とを備え、

前記制御部は、前記ピークホールド手段によって検出されたピーク値を上限基準値と比較すると共に、前記ボトムホールド手段によって検出されたボトム値を下限基準値と比較することを特徴とする請求項1ないし5の何れかに記載の送信ドライバ回路。

【請求項8】

前記制御部は、前記ピーク値が前記上限基準値を上回ると共に前記ボトム値が前記下限基準値を下回ると、前記ピーク値と前記ボトム値との平均値を求め、

前記平均値が、前記一対の信号線間の中間基準電位よりも高いか或いは低いかに応じて、前記コモンモード電圧又は電流を低減するための調整方向を決定することを特徴とする請求項7記載の送信ドライバ回路。

【請求項9】

一対の信号線により差動信号を伝送する伝送線路に接続され、前記伝送線路を介して信号を送信するための送信ドライバ回路において、

前記差動信号の電圧をローレベルとハイレベルとの間で変化させる際に、電圧レベルを変化させるタイミングを調整可能に構成される信号出力部と、

この信号出力部が前記差動信号の電圧レベルを変化させる際に、前記伝送線路の一方の電位が低下を開始した時点から計時を開始する第1計時手段と、前記伝送線路の他方の電位が上昇を開始した時点から計時を開始する第2計時手段と、

前記第1及び第2計時手段が、それぞれの伝送線路の電位が互いに等しくなった時点で計時を停止させることで第1時間及び第2時間をそれぞれ計時すると、前記第1時間と前記第2時間との差である第1時間差を求め、前記第1時間差が正である場合は前記第1時間差と第1基準値とを比較し、

前記第1時間差が負である場合は前記第2時間と前記第1時間との差である第2時間差を求め、前記第2時間差と第2基準値とを比較し、

前記第1時間差が前記第1基準値を上回るか又は前記第2時間差が第2基準値を上回ると、次回の信号送信時に発生するコモンモード電圧又は電流を低減するように、前記信号出力部による前記電圧の出力状態を調整する制御部とを備えたことを特徴とする送信ドライバ回路。

【請求項10】

前記制御部は、前記第1時間差が前記第1基準値を上回ると、前記信号線の一方の電圧レベルをハイからローに変化させるタイミングをより遅くするか、及び/又は前記信号線の他方の電圧レベルをローからハイに変化させるタイミングをより速くするように調整し、前記第2時間差が前記第2基準値を上回ると、前記信号線の一方の電圧レベルをハイからローに変化させるタイミングをより速くするか、及び/又は前記信号線の他方の電圧レベルをローからハイに変化させるタイミングをより遅くするように調整することを特徴とする請求項9記載の送信ドライバ回路。

【請求項11】

前記制御部は、前記第1時間差と前記第1基準値との差又は前記第2時間差と前記第2基準値との差とに応じて、前記信号出力部による前記電圧の出力状態を調整することを特徴とする請求項9又は10記載の送信ドライバ回路。

【請求項12】

前記制御部は、前記第1時間差が前記第1基準値以内であり、又は前記第2時間差が前記第2基準値以内である場合は、以降に自身の動作を停止させることを特徴とする請求項9ないし11の何れかに記載の送信ドライバ回路。

【請求項13】

前記信号出力部は、高電位点又は低電位点と前記信号線との間に接続される駆動用半導体スイッチング素子をスイッチングさせて前記差動信号の電圧レベルを変化させ、

高電位点又は低電位点と前記駆動用半導体スイッチング素子の制御端子との間に接続される制御用半導体スイッチング素子をスイッチングさせて、前記制御端子に出力する制御電圧を変化させ、

前記高電位点又は低電位点と、前記制御用半導体スイッチング素子との間に接続される抵抗素子の抵抗値を調整可能に構成されていることを特徴とする請求項1ないし12の何れかに記載の送信ドライバ回路。

【請求項14】

前記信号出力部は、高電位点又は低電位点と前記信号線との間に接続される半導体スイッチング素子をスイッチングさせて前記差動信号の電圧レベルを変化させ、

前記高電位点又は低電位点と、前記半導体スイッチング素子との間に接続される抵抗素子の抵抗値を調整可能に構成されていることを特徴とする請求項1ないし12の何れかに記載の送信ドライバ回路。

【請求項15】

前記信号出力部は、高電位点又は低電位点と前記信号線との間に接続される半導体スイッチング素子をスイッチングさせて前記差動信号の電圧レベルを変化させ、

制御信号の入力端子と、前記半導体スイッチング素子の制御端子との間に接続される複数個の遅延素子を備え、前記複数個の遅延素子の直列接続数を変更可能に構成されていることを特徴とする請求項1ないし12の何れかに記載の送信ドライバ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【公開番号】特開2012−169905(P2012−169905A)

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願番号】特願2011−29732(P2011−29732)

【出願日】平成23年2月15日(2011.2.15)

【出願人】(000004695)株式会社日本自動車部品総合研究所 (1,981)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願日】平成23年2月15日(2011.2.15)

【出願人】(000004695)株式会社日本自動車部品総合研究所 (1,981)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]