送信モジュール

【課題】 コアアイソレータ素子の挿入損失の増加を抑制した、送信モジュールを提供する。

【解決手段】 回路基板2は、グランドパターン3A〜3Dを備えた多層基板である。回路基板2には、電力増幅器10およびコアアイソレータ素子14が実装される。電力増幅器10およびコアアイソレータ素子14は、樹脂層12によって覆われる。樹脂層12の表面にはシールド層13が設けられる。コアアイソレータ素子14の天面14Aと、天面14Aと対向するシールド層13の天面シールド層13Aとの間隔、コアアイソレータ素子14の側面と、この側面と対向するシールド層13の側面シールド層との間隔を、所定の距離だけ離間して、コアアイソレータ素子14による挿入損失の増加を抑制する。

【解決手段】 回路基板2は、グランドパターン3A〜3Dを備えた多層基板である。回路基板2には、電力増幅器10およびコアアイソレータ素子14が実装される。電力増幅器10およびコアアイソレータ素子14は、樹脂層12によって覆われる。樹脂層12の表面にはシールド層13が設けられる。コアアイソレータ素子14の天面14Aと、天面14Aと対向するシールド層13の天面シールド層13Aとの間隔、コアアイソレータ素子14の側面と、この側面と対向するシールド層13の側面シールド層との間隔を、所定の距離だけ離間して、コアアイソレータ素子14による挿入損失の増加を抑制する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、送信信号を電力増幅して出力する送信モジュールに関する。

【背景技術】

【0002】

コアアイソレータ素子を用いた、予め定められた特定方向にのみ信号を伝送し、逆方向には伝送しない特性を有するモジュールが知られている(例えば、特許文献1参照)。なお、コアアイソレータ素子は、複数の中心電極を設けたフェライトと、それに直流磁界を印加する永久磁石とによって構成されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】国際公開第2008/087788号

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、コアアイソレータ素子を用いたモジュールを高周波の送信機に用いる場合は、電波ノイズの影響を低減するために、金属ケース等のシールド部材でモジュールを覆い、シールドする必要がある。なお、製品の小型化に伴い、モジュールの低背化が要求される。一方、コアアイソレータ素子は、永久磁石およびフェライトによって構成されるため、他の電子部品に比べて高さ寸法が大きくなる傾向にある。この結果、シールド部材は、高さ寸法が大きいコアアイソレータ素子に近接して配置される。また、回路基板の内部や底面にはグランドパターンが設けられるが、回路基板の小型化に伴い、グランドパターンとコアアイソレータ素子との離間距離が短くなる傾向にある。このように、コアアイソレータ素子と、シールド部材やグランドパターンとが近接して配置されると、コアアイソレータ素子による挿入損失が増加するという問題を発明者は見出した。

【0005】

本発明は上述の問題に鑑みなされたものであり、本発明の目的は、コアアイソレータ素子による挿入損失の増加を抑制した送信モジュールを提供することにある。

【課題を解決するための手段】

【0006】

上記課題を解決するために、請求項1の発明は、回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器とを有し、該電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、前記回路基板に設けたグランド電位となるグランドパターンと、少なくとも前記コアアイソレータ素子を覆う、前記回路基板の実装面に設けられた絶縁性の樹脂層と、該樹脂層の表面を覆う導電性材料からなるシールド部とを備え、前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールド部との離間距離の少なくとも一方を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴としている。

【0007】

請求項2の発明は、回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器とを有し、該電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、前記回路基板に設けたグランド電位となるグランドパターンと、少なくとも前記コアアイソレータ素子を覆うシールドケースとを備え、前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールドケースとの離間距離の少なくとも一方を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴としている。

【0008】

請求項3の発明では、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールド部との離間距離の少なくとも一方を広く離間したときに得られる、前記コアアイソレータ素子の挿入損失の最低値に比べて、挿入損失の増加分が0.02dB以下となる間隔に、前記抑制手段により離間させている。

【0009】

請求項4の発明では、前記抑制手段により、前記コアアイソレータ素子の天面と、該天面と対向する前記シールド部との離間距離を80μm以上としている。

【0010】

請求項5の発明では、前記抑制手段により、前記コアアイソレータ素子の側面と、該側面と対向する前記シールド部との離間距離を100μm以上としている。

【0011】

請求項6の発明では、前記抑制手段により、前記コアアイソレータ素子の下面と、該下面と対向する前記グランドパターンとの離間距離を80μm以上としている。

【0012】

請求項7の発明では、前記回路基板は多層基板であって、前記グランドパターンは複数層に形成されてなり、前記グランドパターンのうち少なくとも前記コアアイソレータ素子に近接して対向配置された前記グランドパターンにおける、前記コアアイソレータ素子と対面する領域を少なくとも除去している。

【0013】

請求項8の発明は、回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器と、前記回路基板に設けられたグランド電位となるグランドパターンとを有し、前記電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴としている。

【発明の効果】

【0014】

請求項1の発明によれば、コアアイソレータ素子の周囲には抑制手段を設けたから、抑制手段によって、コアアイソレータ素子とグランドパターンとの離間距離、コアアイソレータ素子とシールド部との離間距離の少なくとも一方を所定の間隔に離間させることができる。これにより、グランドパターンやシールド部をコアアイソレータ素子に近付けて配置したときでも、これに伴う挿入損失の増加を抑制することができる。

【0015】

請求項2の発明によれば、コアアイソレータ素子の周囲には抑制手段を設けたから、抑制手段によって、コアアイソレータ素子とグランドパターンとの離間距離、コアアイソレータ素子とシールドケースとの離間距離の少なくとも一方を所定の間隔に離間させることができる。これにより、グランドパターンやシールドケースをコアアイソレータ素子に近付けて配置したときでも、これに伴う挿入損失の増加を抑制することができる。

【0016】

請求項3の発明によれば、抑制手段により、コアアイソレータ素子とグランドパターンとの離間距離、コアアイソレータ素子とシールド部との離間距離の少なくとも一方を広く離間したときに得られる、コアアイソレータ素子の挿入損失の最低値に比べて、挿入損失の増加分が0.02dB以下となる間隔に離間させた。このため、グランドパターンやシールド部をコアアイソレータ素子に近付けて配置したときでも、挿入損失の最低値に比べて、挿入損失の増加分を0.02dB以下に抑制することができる。

【0017】

請求項4の発明によれば、抑制手段により、コアアイソレータ素子の天面とシールド部との離間距離を80μm以上にしたから、挿入損失の最低値に比べて、挿入損失の増加分を0.02dB以下に抑制することができる。

【0018】

請求項5の発明によれば、抑制手段により、コアアイソレータ素子の側面とシールド部との離間距離を100μm以上にしたから、挿入損失の最低値に比べて、挿入損失の増加分を0.02dB以下に抑制することができる。

【0019】

請求項6の発明によれば、抑制手段により、コアアイソレータ素子の下面とグランドパターンとの離間距離を80μm以上にしたから、挿入損失の最低値に比べて、挿入損失の増加分を0.02dB以下に抑制することができる。

【0020】

請求項7の発明によれば、多層基板の複数層のグランドパターンのうち少なくともコアアイソレータ素子に近接して対向配置されたグランドパターンにおける、コアアイソレータ素子と対面する領域を少なくとも除去した。このため、コアアイソレータ素子の下面とグランドパターンとの離間距離を大きくして、挿入損失の増加を抑制することができる。

【0021】

請求項8の発明によれば、コアアイソレータ素子の周囲には抑制手段を設けたから、抑制手段によって、グランドパターンとコアアイソレータ素子との離間距離を所定の間隔に離間させることができる。これにより、グランドパターンをコアアイソレータ素子に近付けて配置したときでも、これに伴う挿入損失の増加を抑制することができる。

【図面の簡単な説明】

【0022】

【図1】第1の実施の形態による送信モジュールを、シールド層の一部を省いた状態で示す斜視図である。

【図2】図1の送信モジュールを構成する回路基板および電子部品を説明するための、分解斜視図である。

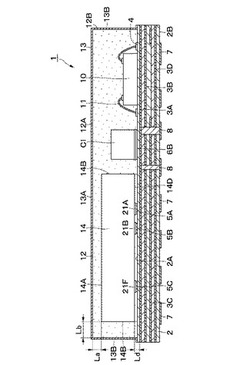

【図3】図1の送信モジュールを、線A−Aに沿って切断した断面図である。

【図4】図1のコアアイソレータ素子を説明するための、分解斜視図である。

【図5】図4のフェライトを示す、斜視図である。

【図6】図1の送信モジュールに係るアイソレータ回路の、等価回路図である。

【図7】コアアイソレータ素子の天面と、天面と対向して設けた第1のテスト用天面シールド部との離間距離を変え、コアアイソレータ素子による挿入損失の抑制効果を確かめるための実験を示す模式図である。

【図8】コアアイソレータ素子による挿入損失の周波数特性を示す特性線図である。

【図9】コアアイソレータ素子の天面および第1のテスト用天面シールド部の離間距離と、W-CDMAの使用帯域でのコアアイソレータ素子による挿入損失の最低値との関係を示す特性線図である。

【図10】コアアイソレータ素子の短辺側面と、短辺側面と対向して設けた第2のテスト用短辺側面シールド部との離間距離を変え、コアアイソレータ素子による挿入損失の抑制効果を確かめるための実験を示す模式図である。

【図11】コアアイソレータ素子の長辺側面と、長辺側面と対向して設けた第2のテスト用長辺側面シールド部との離間距離を変え、コアアイソレータ素子による挿入損失の抑制効果を確かめるための実験を示す模式図である。

【図12】コアアイソレータ素子の短辺側面および第2のテスト用短辺側面シールド部の離間距離と、W-CDMAの使用帯域でのコアアイソレータ素子による挿入損失の最低値との関係を示す特性線図である。

【図13】図1の送信モジュールと同様位置で切断した、第2の実施の形態の断面図である。

【図14】図1の送信モジュールと同様位置で切断した、第3の実施の形態の断面図である。

【図15】図1の送信モジュールと同様位置で切断した、第4の実施の形態の断面図である。

【図16】図1の送信モジュールと同様位置で切断した、第5の実施の形態の断面図である。

【発明を実施するための形態】

【0023】

以下、本発明の実施の形態による送信モジュールを、添付図面を参照しつつ詳細に説明する。

【0024】

図1ないし図3に、第1の実施の形態による送信モジュール1を示す。送信モジュール1は、回路基板2と、回路基板2に実装された電子部品、具体的には、電力増幅器10、コアアイソレータ素子14、整合用のコンデンサCS1,CS2、コンデンサC1,C2、抵抗Rと、各電子部品の表面にモールドされた絶縁性の樹脂層12と、樹脂層の表面に形成されたシールド層13とを備える。

【0025】

回路基板2は、高密度化を図るため、多層基板が一般的に用いられる。多層基板は、例えば、表裏面にグランドパターン3A〜3Dや配線パターン(図示せず)が形成された複数層の絶縁層(図示せず)を、絶縁性のプリプレグ層(図示せず)を介して積層したものである。従って、回路基板2には、電子部品の実装面となる上面2Aから、下面2Bに向けて、グランドパターン3A〜3Dが順番に積層して形成される。回路基板2の上面2Aには、ボンディングワイヤ11を介して、電力増幅器10と電気的に接続するためのパッド4が形成される。また、コアアイソレータ素子14の接続端子である導体接続部21A,21B,21Fと電気的に接続するためのパッド5A,5B,5Cと、コンデンサC1,C2,CS1,CS2および抵抗Rの接続端子と電気的に接続するための対をなすパッド6A,6Bが5対形成される。各パッドには、所定の電子部品が実装される。

【0026】

また、回路基板2の下面2Bには、送信信号TXの入力や出力を行うため、および、電力増幅器10の駆動電圧を供給するための各種の電極7が形成されると共に、グランドパターン3A〜3Dを外部のグランド電位と電気的に接続するためのグランド電極8等が形成される。なお、回路基板2は、両面基板でもよい。また、回路基板2は、ガラスエポキシ基板あるいはビルドアップ基板のような樹脂基板、LTCC(Low Temperature Co-fired Ceramics)基板やアルミナ(Al2O3)基板のようなセラミック基板等のいずれでもよい。

【0027】

電力増幅器10は、入力端子から入力される高周波(例えば数百MHz〜数GHz)の送信信号TXを電力増幅し、増幅した送信信号TXAを出力端子に向けて出力する。電力増幅器10は、例えばヘテロ接合バイポーラトランジスタ等によって構成され、ボンディングワイヤ11を介して回路基板2のパッド4と電気的に接続される。なお、電力増幅器10と回路基板2とは、フリップチップ実装しても良い。

【0028】

樹脂層12は、回路基板2の上面2Aに有機性樹脂をモールドすることによって形成された、略直方体状の硬化体である。樹脂層12は、送信モジュール1の短絡不良の発生防止、耐湿性向上、電子部品に加わる衝撃の緩衝などを目的として設けられる。このため、樹脂層12の層厚は、一番薄いところで、少なくとも50μm以上あることが望ましい。樹脂層12としては、絶縁性を有し、流動性が良く、かつ、密着性にすぐれた材料が選択され、通常は、エポキシ系樹脂が用いられる。なお、樹脂層12は、実装される電子部品の一部にのみモールドしてもよい。

【0029】

シールド層13は、樹脂層12の天面12Aに設けられた天面シールド層13Aと、樹脂層12の短辺側面12Bに設けられた短辺側面シールド層13Bと、樹脂層12の長辺側面12Cに設けられた長辺側面シールド層13Cとから一体に構成された導電層である。シールド層13は、例えば、回路基板2の周縁にまで延びる、グランドパターン3A〜3Dあるいはグランドパターン3A〜3Dと電気的に接続された配線パターン(図示せず)を介して、グランド電位と電気的に接続される。シールド層13は、例えば、金、銀、銅、アルミニウム等の金属材料を用いて形成される。なお、シールド層13は、シールド部の一例として、数十μm程度の厚さに銀ペーストを塗布することによって形成した。しかしながら、シールド部は、これに限られず、スパッタ、蒸着等の手段を用いて、樹脂層12の表面に金属材料の導電膜を形成してもよいし、金属ケースでもよいし、プラスチックケースの表面に金属材料の導電膜を形成したものなど、シールド効果があるものならばどのようなものでもよい。

【0030】

図4および図5を用いて、コアアイソレータ素子14について説明する。コアアイソレータ素子14は、フェライト15、第1のインダクタンス素子L1を構成する第1の導体パターン16、第2のインダクタンス素子L2を構成する第2の導体パターン17、永久磁石22A,22B等によって構成される。

【0031】

板状体に形成されたフェライト15の対向する第1,第2の長辺側面15A,15Bには、電気的に絶縁された第1の導体パターン16および第2の導体パターン17が形成される。また、フェライト15の上面15Cおよび下面15Dには、等間隔に凹部18,19が形成される。これらの凹部18,19には、導体材料が充填され、導体接続部20A〜20E,21A〜21Fを形成する。コアアイソレータ素子14を回路基板2に実装する場合、フェライト15の下面15Dに設けられた一部の導体接続部21A,21B,21Fが、コアアイソレータ素子14を回路基板2に実装するための接続端子として使用される。このため、コアアイソレータ素子14を回路基板2に実装すると、フェライト15の第1,第2の長辺側面15A,15Bは回路基板2の上面2Aに対して立設する。このため、コアアイソレータ素子14は、他の電子部品に比べて高さ寸法が大きくなる傾向にある。

【0032】

第1の導体パターン16は、透視状態でほぼ重なるように形成される、第1の長辺側面15Aの絶縁膜に設けられた導体パターン部16Aと、第2の長辺側面15Bの絶縁膜に設けられた導体パターン部16Bとから構成される。導体パターン部16Aは、第1の長辺側面15Aにおける右下端から垂直に立ち上がり、その先端側で2本に分岐して、比較的小さな角度で平行に左上がりに傾斜し、さらに、その先端側で一つにまとまって左上端に垂直に立ち上がる導体である。

【0033】

導体パターン部16Aの下端は、後述の導体パターン部17Aの下端が電気的に接続される導体接続部21Bと電気的に共通接続される。導体パターン部16Aの上端は、フェライト15の上面15Cに形成された導体接続部20Eに接続され、第2の長辺側面15Bに回り込む。さらに、導体パターン部16Aの上端は、導体接続部20Eを介して、導体パターン部16Bの上端に接続される。導体パターン部16Bは、第2の長辺側面15Bにおける上端から下端に向けて垂直に立ち下がり、その先端側で2本に分岐して、比較的小さな角度で平行に右下がり傾斜し、さらに、その先端側で一つにまとまって左下端に垂直に立ち下がる導体である。なお、導体パターン部16Bの下端が電気的に接続される導体接続部21Aは、接続端子として用いられる。この結果、導体パターン部16A,16Bは導体接続部20Eを介して直列接続され、フェライト15の表面を1ターン巻回する第1のインダクタンス素子L1を構成する。

【0034】

第2の導体パターン17は、第1の長辺側面15Aに設けられた4つの導体パターン部17A〜17Dと、第2の長辺側面15Bに設けられた4つの導体パターン部17E〜17Hとから構成される。導体パターン部17A〜17Dは、第1の長辺側面15Aにおける下端から上端に向けて左上がりに、比較的大きな角度で傾斜する平行に形成された導体である。導体パターン部17A〜17Dの下端のそれぞれは、フェライト15の下面15Dに形成された導体接続部21B〜21Eと電気的に接続される。なお、導体パターン部17Aの下端が電気的に接続される導体接続部21Bは、回路基板2と電気的に接続するための接続端子として用いられる。導体パターン部17A〜17Dの上端のそれぞれは、フェライト15の上面15Cに形成された導体接続部20A〜20Dに接続され、第2の長辺側面15Bに回り込む。さらに、導体パターン部17A〜17Dの上端のそれぞれは、導体接続部20A〜20Dを介して、導体パターン部17E〜17Hのそれぞれの上端に接続される。導体パターン部17E〜17Hは、第2の長辺側面15Bにおける上端から下端に向けて垂直に立ち下がる平行に形成された導体である。導体パターン部17E〜17Hの下端はそれぞれ、フェライト15の下面15Dに形成された導体接続部21C〜21Fと電気的に接続される。なお、導体パターン部17Hの下端が電気的に接続される導体接続部21Fは、接続端子として用いられる。この結果、導体パターン部17A〜17Hは導体接続部20A〜20D,21B〜21Eを介して直列接続され、フェライト15の表面を4ターン巻回する第2のインダクタンス素子L2を構成する。

【0035】

第2の導体パターン17の表面には、第1の導体パターン16と電気的に絶縁するための絶縁膜(図示せず)が形成される。

【0036】

永久磁石22A,22Bは板状体に形成され、フェライト15の第1,第2の長辺側面15A,15Bと同一寸法の長辺側面形状を有する。永久磁石22Aは、一方の長辺側面側がS極に、他方の長辺側面側がN極に形成され、永久磁石22AのS極はフェライト15の第1の長辺側面15Aと対向配置される。永久磁石22Bは、一方の長辺側面側がS極に、他方の長辺側面側がN極に形成され、永久磁石22BのN極はフェライト15の第2の長辺側面15Bと対向配置される。永久磁石22A,22Bは、例えば一液性の熱硬化型エポキシ接着剤からなる接着剤23を用いて、第1,第2の長辺側面15A,15Bにそれぞれ接着される。この結果、永久磁石22A,22Bは、これらの間に回路基板2の上面2Aに沿って上面2Aと略並行な磁界φを形成すると共に、フェライト15の第1,第2の長辺側面15A,15Bに形成された第1,第2の導体パターン16,17に対して略垂直で均一な磁界φを印加する。

【0037】

図6に、コアアイソレータ素子14、整合用のコンデンサCS1,CS2、コンデンサC1および抵抗Rによって構成される、アイソレータ回路24の等価回路図を示す。アイソレータ回路24の入力ポートP1は、電力増幅器10の出力端子に接続されると共に、整合用のコンデンサCS1を介して、第1のインダクタンス素子L1の一端に接続される。第1のインダクタンス素子L1の他端は、整合用のコンデンサCS2を介してアイソレータ回路24の出力ポートP2に接続されると共に、第2のインダクタンス素子L2の一端に接続される。第2のインダクタンス素子L2の他端は、アイソレータ回路24のグランドポートP3に接続される。また、第1のインダクタンス素子L1の両端には、コンデンサC1および抵抗Rが並列接続され、第1の並列共振回路を構成する。また、第2のインダクタンス素子L2の両端には、コンデンサC2が並列接続され、第2の並列共振回路を構成する。この結果、第1の並列共振回路でアイソレーション特性(逆方向減衰特性)が最大となる周波数が設定され、第2の並列共振回路で挿入損特性が最小となる周波数が設定される。

【0038】

次に、送信モジュール1において、コアアイソレータ素子14の天面14Aと、天面14Aと対向する天面シールド層13Aとを所定の間隔に離間することにより、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段の効果を示すための実験を、図7を用いて模式的に説明する。

【0039】

実験には、各電子部品を回路基板2に実装しただけで、樹脂層12をモールドしていない送信モジュール1Aを用いた。また、シールド層13に相当するものとして、第1のテスト用シールドケース31を用いた。第1のテスト用シールドケース31は、長方形状の第1のテスト用天面シールド部31Aと、このテスト用天面シールド部31Aの短辺および長辺のそれぞれから垂設する第1のテスト用短辺側面シールド部31Bと、第1のテスト用長辺側面シールド部31Cとから一体に形成される。なお、第1のテスト用シールドケース31は、例えば、弾力性のある厚みが50〜100μm程度の銅箔を折り曲げて形成した。また、第1のテスト用シールドケース31でコアアイソレータ素子14を覆うと共に、第1のテスト用シールドケース31をグランド電位に電気的に接続した。

【0040】

回路基板2を定盤上に固定し、第1のテスト用天面シールド部31Aを回路基板2の厚さ方向(上下方向)にプランジャPで押圧した。弾性によって、第1のテスト用短辺側面シールド部31Bおよび第1のテスト用長辺側面シールド部31Cが撓むため、テスト用天面シールド部31Aが上下方向に変位し、第1のテスト用天面シールド部31Aとコアアイソレータ素子14の天面14Aとの離間する距離Laを変えることができる。このとき、1750〜2150MHzの周波数帯域の疑似信号を送信モジュール1Aに入力し、距離Laと、コアアイソレータ素子14による挿入損失との関係を測定した。また、例えば、W-CDMA(Wideband Code Division Multiple Access)の使用帯域である1920〜1980MHzの周波数の疑似信号を送信モジュール1Aに入力し、距離Laと、コアアイソレータ素子14による挿入損失の最低値との関係を測定した。

【0041】

図8に示すように、1750〜2150MHzの周波数帯域において、第1のテスト用天面シールド部31Aとコアアイソレータ素子14の天面14Aとの距離Laが小さくなると、すなわち、第1のテスト用天面シールド部31Aとコアアイソレータ素子14の天面14Aとが近付くと、挿入損失は増加する傾向にある。一方、距離Laが80μm以上の場合には、挿入損失は殆ど変化しなくなる。

【0042】

また、図9に示すように、1920〜1980MHzのW-CDMAの使用帯域におけるコアアイソレータ素子14による挿入損失の最低値は、距離Laを80μm以上に設定すると、第1のテスト用天面シールド部31Aとコアアイソレータ素子14との距離Laを広く離したとき、例えば、距離Laが1mmのときとほぼ変わらず、距離Laを広く離したときに対する許容値Cとして例えば0.02dB以下に抑制することできる。

【0043】

次に、送信モジュール1において、コアアイソレータ素子14の側面(短辺側面14B、長辺側面14C)と、シールド層13の短辺側面シールド層13Bあるいは長辺側面シールド層13Cを所定の間隔に離間することにより、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段の効果を示すための実験を、図10および図11を用いて模式的に説明する。

【0044】

上述した実験と同様、送信モジュール1Aと、第2のテスト用シールドケース32を用いた。第2のテスト用シールドケース32は、コアアイソレータ素子14の側面近傍に、コアアイソレータ素子14の側面と対向して載置できるように、第1のテスト用シールドケース31よりも小型に形成される。なお、第2のテスト用シールドケース32は、細長い直方体形状の第2のテスト用天面シールド部32Aと、このテスト用天面シールド部32Aの短辺および長辺のそれぞれから垂設する第2のテスト用短辺側面シールド部32Bと、第2のテスト用長辺側面シールド部32Cとから一体に形成される。なお、第2のテスト用シールドケース32は、例えば、弾力性のある厚みが50〜100μm程度の銅箔を折り曲げて形成した。

【0045】

第2のテスト用短辺側面シールド部32Bを、コアアイソレータ素子14のフェライト15の短辺側面と対向させて配置した。そして、第2のテスト用短辺側面シールド部32Bを第1の水平方向(図10の左右方向)に移動させ、第2のテスト用短辺側面シールド部32Bとコアアイソレータ素子14の短辺側面14Bとが離間する距離Lbを変えた。このとき、上述した実験と同様、1750〜2150MHzの周波数帯域の疑似信号を送信モジュール1Aに入力し、距離Lbと、コアアイソレータ素子14による挿入損失との関係を測定した。また、例えば、W-CDMAの使用帯域である1920〜1980MHzの周波数の疑似信号を送信モジュール1Aに入力し、距離Lbと、コアアイソレータ素子14による挿入損失の最低値との関係を測定した。

【0046】

さらに、第2のテスト用長辺側面シールド部32Cを、コアアイソレータ素子14のフェライト15の長辺側面と対向させて配置した。そして、第2のテスト用長辺側面シールド部32Cを第2の水平方向(図11の左右方向)に移動させ、第2のテスト用長辺側面シールド部32Cとコアアイソレータ素子14の長辺側面14Cとが離間する距離Lcを変えた。このとき、上述した実験と同様、1750〜2150MHzの周波数帯域の疑似信号を送信モジュール1Aに入力し、距離Lcと、コアアイソレータ素子14による挿入損失との関係を測定した。また、例えば、W-CDMAの使用帯域である1920〜1980MHzの周波数の疑似信号を送信モジュール1Aに入力し、距離Lcと、コアアイソレータ素子14による挿入損失の最低値との関係を測定した。

【0047】

この結果、図8に示した、コアアイソレータ素子14による挿入損失と周波数との関係と同様の測定結果(図示せず)が得られた。また、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段として、距離Lcに比べて、距離Lbの影響が大きいことが分かった。

【0048】

図12に、1920〜1980MHzのW-CDMAの使用帯域における、コアアイソレータ素子14の短辺側面14Bと第2のテスト用短辺側面シールド部32Bとの離間距離Lbと、コアアイソレータ素子14による挿入損失の最低値との関係を示す。挿入損失の最低値は、距離Lbを100μm以上に設定すると、第2のテスト用短辺側面シールド部32Bとコアアイソレータ素子14との距離Lbを広く離したとき、例えば、距離Lbが1mmのときとほぼ変わらず、距離Lbを広く離したときに対する許容値Cとして例えば0.02dB以下に抑制することできる。

【0049】

また、詳細な説明は省略するが、第1のテスト用天面シールド部31Aとコアアイソレータ素子14の天面14Aとの距離Laと、コアアイソレータ素子14による挿入損失の増加の抑制との関係は、コアアイソレータ素子14の下面14Dと回路基板2に形成されたグランドパターン3Aとの距離Ldと、コアアイソレータ素子14による挿入損失の増加の抑制との関係についても、同様に当てはまる。すなわち、距離Ldを80μm以上に設定することにより、コアアイソレータ素子14による挿入損失の増加を抑制することができる。

【0050】

なお、第1および第2のテスト用シールドケース31,32をコアアイソレータ素子14から離間して配置すること、また、グランドパターン3Aをコアアイソレータ素子14の下面14Dから離間して配置することにより、コアアイソレータ素子14による挿入損失の増加を抑制できる理由として、第1および第2のテスト用シールドケース31,32がコアアイソレータ素子14の天面14A、短辺側面14Bあるいは長辺側面14Cに接近し過ぎると、また、グランドパターン3Aがコアアイソレータ素子14の下面14Dに接近し過ぎると、永久磁石22A,22Bによって、フェライト15の第1,第2の長辺側面15A,15Bに対して略垂直に均一印加されていた磁界φの均一性が乱れ、第1のインダクタンス素子L1および第2のインダクタンス素子L2のインダクタンス値が変化することに起因すると思われる。

【0051】

従って、送信モジュール1における天面シールド層13Aとコアアイソレータ素子14の天面14Aとが離間する距離Laを80μm以上とすることが、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段として効果的である。

【0052】

また、送信モジュール1における短辺側面シールド層13Bとコアアイソレータ素子14の短辺側面14Bとが離間する距離Lbを100μm以上とすることが、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段として効果的である。

【0053】

さらに、送信モジュール1における回路基板2の上面2A側に形成されたグランドパターン3Aとコアアイソレータ素子14の下面14Dとが離間する距離Ldを、距離Laと同様に80μm以上とすることが、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段として効果的である。

【0054】

なお、送信モジュール1において、シールド層13とコアアイソレータ素子14との離間する各距離La〜Ldと、コアアイソレータ素子14による挿入損失の増加を抑制する効果の関係についてのみ説明した。しかしながら、送信モジュール1の構造に応じて、最適な距離に各距離La〜Ldを設定すれば、コアアイソレータ素子14による挿入損失の増加を相乗的に抑制することができることはいうまでもない。すなわち、距離La、距離Lb、距離Lc、距離Ldについてのそれぞれの最適距離を、送信モジュール1に構造に応じて設定することにより、送信モジュール1におけるコアアイソレータ素子14による挿入損失の増加を最も効率良く抑制することができる。

【0055】

なお、本実施の形態では、シールド層13とコアアイソレータ素子14との距離La〜Ldを広く離したときの挿入損失の増加に対する許容値Cを0.02dBとしてシールド層13とコアアイソレータ素子14との距離La〜Ldを決めたが、本発明はこれに限らず、所望の挿入損失や使用帯域等に応じてこれらの許容値や最小値は適宜設定できるものである。

【0056】

次に、図13に、本発明の第2の実施の形態である送信モジュール41の断面図を示す。本実施の形態では、前記第1の実施の形態と同一の構成要素に同一の符号を付し、その説明を省略する。

【0057】

回路基板42は、第1の実施の形態による回路基板2と同様に、表裏面にグランドパターン43A〜43Dや配線パターン(図示せず)が形成された複数層の絶縁層(図示せず)を、絶縁性のプリプレグ層(図示せず)を介して積層した多層基板である。グランドパターン43A〜43Dは、電子部品の実装面となる回路基板42の上面42Aから、下面42Bに向けて、順番に積層して形成される。

【0058】

また、回路基板42の上面42A側に位置し、例えば、コアアイソレータ素子14の下面14Dから80μm離間した距離近傍にある少なくともグランドパターン43A,43Bには、コアアイソレータ素子14の下面14Dと対面した部分を除去した除去部44が形成される。除去部44の面積は、製造公差に相当するマージンを考慮して、コアアイソレータ素子14の下面14Dの外形よりも大きな面積をもって形成される。

【0059】

このため、コアアイソレータ素子14の下面14Dから80μm離間した距離近傍にはグランド電位となるパターンがなくなり、結果的に、コアアイソレータ素子14の下面14Dとグランドパターン43A,43Bとの距離を80μm離間させたことになる。かくして、第2の実施の形態でも、第1の実施の形態と同様の作用効果を得ることができる。また、コアアイソレータ素子14の下面14Dと、回路基板42の実装面となる上面42Aとの距離を広く設計する必要がなくなるので、送信モジュール41を低背化することができる。

【0060】

なお、除去部44を設けると共に、第1の実施の形態で説明した如く、コアアイソレータ素子14とシールド層13とを所定の距離だけ離間することにより、コアアイソレータ素子14による挿入損失の増加を相乗的に抑制できることはいうまでもない。

【0061】

次に、図14に、本発明の第3の実施の形態である送信モジュール51の断面図を示す。本実施の形態では、前記第1の実施の形態と同一の構成要素に同一の符号を付し、その説明を省略する。

【0062】

シールドケース52は、第1の実施の形態によるシールド層13と同様に、コアアイソレータ素子14の天面14Aを覆う天面シールドケース52Aと、天面シールドケース52Aの短辺から回路基板2側に向けて垂下して設けられた短辺側面シールドケース52Bと、天面シールドケース52Aの短辺から回路基板2側に向けて垂下して設けられた長辺側面シールドケース52Cとから一体に構成された導電性の箱体である。シールドケース52は、例えば、回路基板2の周縁にまで延びる、グランドパターン3A〜3Dあるいはグランドパターン3A〜3Dと電気的に接続された配線パターンを介して、グランド電位と電気的に接続される。シールドケース52は、例えば、銀、銅、アルミニウム等の金属材料を用いて形成される。なお、電力増幅器10の表面には、耐湿性等の理由から一般的にはポッティング樹脂53が設けられるが、必ずしも設けなくてもよい。

【0063】

コアアイソレータ素子14とシールドケース52とは、第1の実施の形態と同様に、所定距離を離間して配置形成される。かくして、第3の実施の形態でも第1の実施の形態と同様の作用効果を得ることができる。

【0064】

次に、図15に、本発明の第4の実施の形態である送信モジュール61の断面図を示す。本実施の形態では、前記第1の実施の形態と同一の構成要素に同一の符号を付し、その説明を省略する。

【0065】

送信モジュール61の回路基板2の上面2Aには、シールド部が設けられない。一方、コアアイソレータ素子14の下面14Dとグランドパターン3Aとの間の距離Ldを、例えば最小値として80μm以上離間させる。なお、電力増幅器10の表面には、ポッティング樹脂を設けてもよく、設けなくてもよい。

【0066】

かくして、第4の実施の形態でも、第1の実施の形態と同様の作用効果を得ることができる。

【0067】

次に、図16に、本発明の第5の実施の形態である送信モジュール71の断面図を示す。本実施の形態では、前記第2の実施の形態と同一の構成要素に同一の符号を付し、その説明を省略する。

【0068】

送信モジュール71の回路基板42の上面42Aには、シールド部が設けられない。一方、回路基板42の上面42A側に位置し、例えば、コアアイソレータ素子14の下面14Dから80μm離間した距離近傍にある少なくともグランドパターン43A,43Bには、コアアイソレータ素子14の下面14Dと対面した部分を除去した除去部44が形成される。なお、電力増幅器10の表面には、ポッティング樹脂を設けてもよく、設けなくてもよい。かくして、第5の実施の形態でも、第2の実施の形態と同様の作用効果を得ることができる。

【0069】

なお、前記各実施の形態では、非可逆回路素子としてのコアアイソレータ素子14はアイソレータ回路24を構成するものとしたが、サーキュレータを構成してもよい。また、コアアイソレータ素子14に接続されるコンデンサC1,C2,CS1,CS2および抵抗Rをチップ部品によって形成するものとしたが、これらのコンデンサ、抵抗等の受動素子は回路基板の内部に形成してもよい。また、送信モジュールには、整合回路を構成するコンデンサ素子やインダクタンス素子を付け加えても良い。

【0070】

また、前記各実施の形態では、回路基板2,42は4層のグランドパターン3A〜3D,43A〜43Dを備えた多層基板によって構成した。しかし、本発明はこれに限らず、回路基板は、2層、3層または5層以上のグランドパターンを備えた多層基板によって構成してもよく、内部に単一のグランドパターンを備えた多層基板によって構成してもよい。また、回路基板は、片面基板や、両面基板によって構成してもよい。

【0071】

また、前記各実施の形態では、絶縁性の樹脂材料を用いて一様な樹脂層12を形成する構成としたが、例えば国際公開第2008/087788号に記載されたように、非磁性樹脂材料からなる最内層と磁性樹脂材料からなる磁性樹脂層とによって2層にモールドした樹脂層を設ける構成としてもよい。

【0072】

また、前記第1および第2の実施の形態では、導電性の金属薄膜からなるシールド層13によってシールド部を形成したが、第3の実施の形態と同様のシールドケース52を用いてシールド部を形成してもよい。

【0073】

また、前記各実施の形態では、送信信号がW-CDMA帯域となる1920〜1980MHzに設定された送信モジュール1,41,51,61,71を例に挙げて説明したが、他の使用帯域の送信信号に用いる送信モジュールに適用してもよい。

【符号の説明】

【0074】

1,41,51,61,71 送信モジュール

2,42 回路基板

3A〜3D,43A〜43D グランドパターン

10 電力増幅器

12 樹脂層

13 シールド層

14 コアアイソレータ素子

14A 天面

14B 短辺側面

14C 長辺側面

14D 下面

44 除去部

52 シールドケース

【技術分野】

【0001】

本発明は、送信信号を電力増幅して出力する送信モジュールに関する。

【背景技術】

【0002】

コアアイソレータ素子を用いた、予め定められた特定方向にのみ信号を伝送し、逆方向には伝送しない特性を有するモジュールが知られている(例えば、特許文献1参照)。なお、コアアイソレータ素子は、複数の中心電極を設けたフェライトと、それに直流磁界を印加する永久磁石とによって構成されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】国際公開第2008/087788号

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、コアアイソレータ素子を用いたモジュールを高周波の送信機に用いる場合は、電波ノイズの影響を低減するために、金属ケース等のシールド部材でモジュールを覆い、シールドする必要がある。なお、製品の小型化に伴い、モジュールの低背化が要求される。一方、コアアイソレータ素子は、永久磁石およびフェライトによって構成されるため、他の電子部品に比べて高さ寸法が大きくなる傾向にある。この結果、シールド部材は、高さ寸法が大きいコアアイソレータ素子に近接して配置される。また、回路基板の内部や底面にはグランドパターンが設けられるが、回路基板の小型化に伴い、グランドパターンとコアアイソレータ素子との離間距離が短くなる傾向にある。このように、コアアイソレータ素子と、シールド部材やグランドパターンとが近接して配置されると、コアアイソレータ素子による挿入損失が増加するという問題を発明者は見出した。

【0005】

本発明は上述の問題に鑑みなされたものであり、本発明の目的は、コアアイソレータ素子による挿入損失の増加を抑制した送信モジュールを提供することにある。

【課題を解決するための手段】

【0006】

上記課題を解決するために、請求項1の発明は、回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器とを有し、該電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、前記回路基板に設けたグランド電位となるグランドパターンと、少なくとも前記コアアイソレータ素子を覆う、前記回路基板の実装面に設けられた絶縁性の樹脂層と、該樹脂層の表面を覆う導電性材料からなるシールド部とを備え、前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールド部との離間距離の少なくとも一方を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴としている。

【0007】

請求項2の発明は、回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器とを有し、該電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、前記回路基板に設けたグランド電位となるグランドパターンと、少なくとも前記コアアイソレータ素子を覆うシールドケースとを備え、前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールドケースとの離間距離の少なくとも一方を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴としている。

【0008】

請求項3の発明では、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールド部との離間距離の少なくとも一方を広く離間したときに得られる、前記コアアイソレータ素子の挿入損失の最低値に比べて、挿入損失の増加分が0.02dB以下となる間隔に、前記抑制手段により離間させている。

【0009】

請求項4の発明では、前記抑制手段により、前記コアアイソレータ素子の天面と、該天面と対向する前記シールド部との離間距離を80μm以上としている。

【0010】

請求項5の発明では、前記抑制手段により、前記コアアイソレータ素子の側面と、該側面と対向する前記シールド部との離間距離を100μm以上としている。

【0011】

請求項6の発明では、前記抑制手段により、前記コアアイソレータ素子の下面と、該下面と対向する前記グランドパターンとの離間距離を80μm以上としている。

【0012】

請求項7の発明では、前記回路基板は多層基板であって、前記グランドパターンは複数層に形成されてなり、前記グランドパターンのうち少なくとも前記コアアイソレータ素子に近接して対向配置された前記グランドパターンにおける、前記コアアイソレータ素子と対面する領域を少なくとも除去している。

【0013】

請求項8の発明は、回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器と、前記回路基板に設けられたグランド電位となるグランドパターンとを有し、前記電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴としている。

【発明の効果】

【0014】

請求項1の発明によれば、コアアイソレータ素子の周囲には抑制手段を設けたから、抑制手段によって、コアアイソレータ素子とグランドパターンとの離間距離、コアアイソレータ素子とシールド部との離間距離の少なくとも一方を所定の間隔に離間させることができる。これにより、グランドパターンやシールド部をコアアイソレータ素子に近付けて配置したときでも、これに伴う挿入損失の増加を抑制することができる。

【0015】

請求項2の発明によれば、コアアイソレータ素子の周囲には抑制手段を設けたから、抑制手段によって、コアアイソレータ素子とグランドパターンとの離間距離、コアアイソレータ素子とシールドケースとの離間距離の少なくとも一方を所定の間隔に離間させることができる。これにより、グランドパターンやシールドケースをコアアイソレータ素子に近付けて配置したときでも、これに伴う挿入損失の増加を抑制することができる。

【0016】

請求項3の発明によれば、抑制手段により、コアアイソレータ素子とグランドパターンとの離間距離、コアアイソレータ素子とシールド部との離間距離の少なくとも一方を広く離間したときに得られる、コアアイソレータ素子の挿入損失の最低値に比べて、挿入損失の増加分が0.02dB以下となる間隔に離間させた。このため、グランドパターンやシールド部をコアアイソレータ素子に近付けて配置したときでも、挿入損失の最低値に比べて、挿入損失の増加分を0.02dB以下に抑制することができる。

【0017】

請求項4の発明によれば、抑制手段により、コアアイソレータ素子の天面とシールド部との離間距離を80μm以上にしたから、挿入損失の最低値に比べて、挿入損失の増加分を0.02dB以下に抑制することができる。

【0018】

請求項5の発明によれば、抑制手段により、コアアイソレータ素子の側面とシールド部との離間距離を100μm以上にしたから、挿入損失の最低値に比べて、挿入損失の増加分を0.02dB以下に抑制することができる。

【0019】

請求項6の発明によれば、抑制手段により、コアアイソレータ素子の下面とグランドパターンとの離間距離を80μm以上にしたから、挿入損失の最低値に比べて、挿入損失の増加分を0.02dB以下に抑制することができる。

【0020】

請求項7の発明によれば、多層基板の複数層のグランドパターンのうち少なくともコアアイソレータ素子に近接して対向配置されたグランドパターンにおける、コアアイソレータ素子と対面する領域を少なくとも除去した。このため、コアアイソレータ素子の下面とグランドパターンとの離間距離を大きくして、挿入損失の増加を抑制することができる。

【0021】

請求項8の発明によれば、コアアイソレータ素子の周囲には抑制手段を設けたから、抑制手段によって、グランドパターンとコアアイソレータ素子との離間距離を所定の間隔に離間させることができる。これにより、グランドパターンをコアアイソレータ素子に近付けて配置したときでも、これに伴う挿入損失の増加を抑制することができる。

【図面の簡単な説明】

【0022】

【図1】第1の実施の形態による送信モジュールを、シールド層の一部を省いた状態で示す斜視図である。

【図2】図1の送信モジュールを構成する回路基板および電子部品を説明するための、分解斜視図である。

【図3】図1の送信モジュールを、線A−Aに沿って切断した断面図である。

【図4】図1のコアアイソレータ素子を説明するための、分解斜視図である。

【図5】図4のフェライトを示す、斜視図である。

【図6】図1の送信モジュールに係るアイソレータ回路の、等価回路図である。

【図7】コアアイソレータ素子の天面と、天面と対向して設けた第1のテスト用天面シールド部との離間距離を変え、コアアイソレータ素子による挿入損失の抑制効果を確かめるための実験を示す模式図である。

【図8】コアアイソレータ素子による挿入損失の周波数特性を示す特性線図である。

【図9】コアアイソレータ素子の天面および第1のテスト用天面シールド部の離間距離と、W-CDMAの使用帯域でのコアアイソレータ素子による挿入損失の最低値との関係を示す特性線図である。

【図10】コアアイソレータ素子の短辺側面と、短辺側面と対向して設けた第2のテスト用短辺側面シールド部との離間距離を変え、コアアイソレータ素子による挿入損失の抑制効果を確かめるための実験を示す模式図である。

【図11】コアアイソレータ素子の長辺側面と、長辺側面と対向して設けた第2のテスト用長辺側面シールド部との離間距離を変え、コアアイソレータ素子による挿入損失の抑制効果を確かめるための実験を示す模式図である。

【図12】コアアイソレータ素子の短辺側面および第2のテスト用短辺側面シールド部の離間距離と、W-CDMAの使用帯域でのコアアイソレータ素子による挿入損失の最低値との関係を示す特性線図である。

【図13】図1の送信モジュールと同様位置で切断した、第2の実施の形態の断面図である。

【図14】図1の送信モジュールと同様位置で切断した、第3の実施の形態の断面図である。

【図15】図1の送信モジュールと同様位置で切断した、第4の実施の形態の断面図である。

【図16】図1の送信モジュールと同様位置で切断した、第5の実施の形態の断面図である。

【発明を実施するための形態】

【0023】

以下、本発明の実施の形態による送信モジュールを、添付図面を参照しつつ詳細に説明する。

【0024】

図1ないし図3に、第1の実施の形態による送信モジュール1を示す。送信モジュール1は、回路基板2と、回路基板2に実装された電子部品、具体的には、電力増幅器10、コアアイソレータ素子14、整合用のコンデンサCS1,CS2、コンデンサC1,C2、抵抗Rと、各電子部品の表面にモールドされた絶縁性の樹脂層12と、樹脂層の表面に形成されたシールド層13とを備える。

【0025】

回路基板2は、高密度化を図るため、多層基板が一般的に用いられる。多層基板は、例えば、表裏面にグランドパターン3A〜3Dや配線パターン(図示せず)が形成された複数層の絶縁層(図示せず)を、絶縁性のプリプレグ層(図示せず)を介して積層したものである。従って、回路基板2には、電子部品の実装面となる上面2Aから、下面2Bに向けて、グランドパターン3A〜3Dが順番に積層して形成される。回路基板2の上面2Aには、ボンディングワイヤ11を介して、電力増幅器10と電気的に接続するためのパッド4が形成される。また、コアアイソレータ素子14の接続端子である導体接続部21A,21B,21Fと電気的に接続するためのパッド5A,5B,5Cと、コンデンサC1,C2,CS1,CS2および抵抗Rの接続端子と電気的に接続するための対をなすパッド6A,6Bが5対形成される。各パッドには、所定の電子部品が実装される。

【0026】

また、回路基板2の下面2Bには、送信信号TXの入力や出力を行うため、および、電力増幅器10の駆動電圧を供給するための各種の電極7が形成されると共に、グランドパターン3A〜3Dを外部のグランド電位と電気的に接続するためのグランド電極8等が形成される。なお、回路基板2は、両面基板でもよい。また、回路基板2は、ガラスエポキシ基板あるいはビルドアップ基板のような樹脂基板、LTCC(Low Temperature Co-fired Ceramics)基板やアルミナ(Al2O3)基板のようなセラミック基板等のいずれでもよい。

【0027】

電力増幅器10は、入力端子から入力される高周波(例えば数百MHz〜数GHz)の送信信号TXを電力増幅し、増幅した送信信号TXAを出力端子に向けて出力する。電力増幅器10は、例えばヘテロ接合バイポーラトランジスタ等によって構成され、ボンディングワイヤ11を介して回路基板2のパッド4と電気的に接続される。なお、電力増幅器10と回路基板2とは、フリップチップ実装しても良い。

【0028】

樹脂層12は、回路基板2の上面2Aに有機性樹脂をモールドすることによって形成された、略直方体状の硬化体である。樹脂層12は、送信モジュール1の短絡不良の発生防止、耐湿性向上、電子部品に加わる衝撃の緩衝などを目的として設けられる。このため、樹脂層12の層厚は、一番薄いところで、少なくとも50μm以上あることが望ましい。樹脂層12としては、絶縁性を有し、流動性が良く、かつ、密着性にすぐれた材料が選択され、通常は、エポキシ系樹脂が用いられる。なお、樹脂層12は、実装される電子部品の一部にのみモールドしてもよい。

【0029】

シールド層13は、樹脂層12の天面12Aに設けられた天面シールド層13Aと、樹脂層12の短辺側面12Bに設けられた短辺側面シールド層13Bと、樹脂層12の長辺側面12Cに設けられた長辺側面シールド層13Cとから一体に構成された導電層である。シールド層13は、例えば、回路基板2の周縁にまで延びる、グランドパターン3A〜3Dあるいはグランドパターン3A〜3Dと電気的に接続された配線パターン(図示せず)を介して、グランド電位と電気的に接続される。シールド層13は、例えば、金、銀、銅、アルミニウム等の金属材料を用いて形成される。なお、シールド層13は、シールド部の一例として、数十μm程度の厚さに銀ペーストを塗布することによって形成した。しかしながら、シールド部は、これに限られず、スパッタ、蒸着等の手段を用いて、樹脂層12の表面に金属材料の導電膜を形成してもよいし、金属ケースでもよいし、プラスチックケースの表面に金属材料の導電膜を形成したものなど、シールド効果があるものならばどのようなものでもよい。

【0030】

図4および図5を用いて、コアアイソレータ素子14について説明する。コアアイソレータ素子14は、フェライト15、第1のインダクタンス素子L1を構成する第1の導体パターン16、第2のインダクタンス素子L2を構成する第2の導体パターン17、永久磁石22A,22B等によって構成される。

【0031】

板状体に形成されたフェライト15の対向する第1,第2の長辺側面15A,15Bには、電気的に絶縁された第1の導体パターン16および第2の導体パターン17が形成される。また、フェライト15の上面15Cおよび下面15Dには、等間隔に凹部18,19が形成される。これらの凹部18,19には、導体材料が充填され、導体接続部20A〜20E,21A〜21Fを形成する。コアアイソレータ素子14を回路基板2に実装する場合、フェライト15の下面15Dに設けられた一部の導体接続部21A,21B,21Fが、コアアイソレータ素子14を回路基板2に実装するための接続端子として使用される。このため、コアアイソレータ素子14を回路基板2に実装すると、フェライト15の第1,第2の長辺側面15A,15Bは回路基板2の上面2Aに対して立設する。このため、コアアイソレータ素子14は、他の電子部品に比べて高さ寸法が大きくなる傾向にある。

【0032】

第1の導体パターン16は、透視状態でほぼ重なるように形成される、第1の長辺側面15Aの絶縁膜に設けられた導体パターン部16Aと、第2の長辺側面15Bの絶縁膜に設けられた導体パターン部16Bとから構成される。導体パターン部16Aは、第1の長辺側面15Aにおける右下端から垂直に立ち上がり、その先端側で2本に分岐して、比較的小さな角度で平行に左上がりに傾斜し、さらに、その先端側で一つにまとまって左上端に垂直に立ち上がる導体である。

【0033】

導体パターン部16Aの下端は、後述の導体パターン部17Aの下端が電気的に接続される導体接続部21Bと電気的に共通接続される。導体パターン部16Aの上端は、フェライト15の上面15Cに形成された導体接続部20Eに接続され、第2の長辺側面15Bに回り込む。さらに、導体パターン部16Aの上端は、導体接続部20Eを介して、導体パターン部16Bの上端に接続される。導体パターン部16Bは、第2の長辺側面15Bにおける上端から下端に向けて垂直に立ち下がり、その先端側で2本に分岐して、比較的小さな角度で平行に右下がり傾斜し、さらに、その先端側で一つにまとまって左下端に垂直に立ち下がる導体である。なお、導体パターン部16Bの下端が電気的に接続される導体接続部21Aは、接続端子として用いられる。この結果、導体パターン部16A,16Bは導体接続部20Eを介して直列接続され、フェライト15の表面を1ターン巻回する第1のインダクタンス素子L1を構成する。

【0034】

第2の導体パターン17は、第1の長辺側面15Aに設けられた4つの導体パターン部17A〜17Dと、第2の長辺側面15Bに設けられた4つの導体パターン部17E〜17Hとから構成される。導体パターン部17A〜17Dは、第1の長辺側面15Aにおける下端から上端に向けて左上がりに、比較的大きな角度で傾斜する平行に形成された導体である。導体パターン部17A〜17Dの下端のそれぞれは、フェライト15の下面15Dに形成された導体接続部21B〜21Eと電気的に接続される。なお、導体パターン部17Aの下端が電気的に接続される導体接続部21Bは、回路基板2と電気的に接続するための接続端子として用いられる。導体パターン部17A〜17Dの上端のそれぞれは、フェライト15の上面15Cに形成された導体接続部20A〜20Dに接続され、第2の長辺側面15Bに回り込む。さらに、導体パターン部17A〜17Dの上端のそれぞれは、導体接続部20A〜20Dを介して、導体パターン部17E〜17Hのそれぞれの上端に接続される。導体パターン部17E〜17Hは、第2の長辺側面15Bにおける上端から下端に向けて垂直に立ち下がる平行に形成された導体である。導体パターン部17E〜17Hの下端はそれぞれ、フェライト15の下面15Dに形成された導体接続部21C〜21Fと電気的に接続される。なお、導体パターン部17Hの下端が電気的に接続される導体接続部21Fは、接続端子として用いられる。この結果、導体パターン部17A〜17Hは導体接続部20A〜20D,21B〜21Eを介して直列接続され、フェライト15の表面を4ターン巻回する第2のインダクタンス素子L2を構成する。

【0035】

第2の導体パターン17の表面には、第1の導体パターン16と電気的に絶縁するための絶縁膜(図示せず)が形成される。

【0036】

永久磁石22A,22Bは板状体に形成され、フェライト15の第1,第2の長辺側面15A,15Bと同一寸法の長辺側面形状を有する。永久磁石22Aは、一方の長辺側面側がS極に、他方の長辺側面側がN極に形成され、永久磁石22AのS極はフェライト15の第1の長辺側面15Aと対向配置される。永久磁石22Bは、一方の長辺側面側がS極に、他方の長辺側面側がN極に形成され、永久磁石22BのN極はフェライト15の第2の長辺側面15Bと対向配置される。永久磁石22A,22Bは、例えば一液性の熱硬化型エポキシ接着剤からなる接着剤23を用いて、第1,第2の長辺側面15A,15Bにそれぞれ接着される。この結果、永久磁石22A,22Bは、これらの間に回路基板2の上面2Aに沿って上面2Aと略並行な磁界φを形成すると共に、フェライト15の第1,第2の長辺側面15A,15Bに形成された第1,第2の導体パターン16,17に対して略垂直で均一な磁界φを印加する。

【0037】

図6に、コアアイソレータ素子14、整合用のコンデンサCS1,CS2、コンデンサC1および抵抗Rによって構成される、アイソレータ回路24の等価回路図を示す。アイソレータ回路24の入力ポートP1は、電力増幅器10の出力端子に接続されると共に、整合用のコンデンサCS1を介して、第1のインダクタンス素子L1の一端に接続される。第1のインダクタンス素子L1の他端は、整合用のコンデンサCS2を介してアイソレータ回路24の出力ポートP2に接続されると共に、第2のインダクタンス素子L2の一端に接続される。第2のインダクタンス素子L2の他端は、アイソレータ回路24のグランドポートP3に接続される。また、第1のインダクタンス素子L1の両端には、コンデンサC1および抵抗Rが並列接続され、第1の並列共振回路を構成する。また、第2のインダクタンス素子L2の両端には、コンデンサC2が並列接続され、第2の並列共振回路を構成する。この結果、第1の並列共振回路でアイソレーション特性(逆方向減衰特性)が最大となる周波数が設定され、第2の並列共振回路で挿入損特性が最小となる周波数が設定される。

【0038】

次に、送信モジュール1において、コアアイソレータ素子14の天面14Aと、天面14Aと対向する天面シールド層13Aとを所定の間隔に離間することにより、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段の効果を示すための実験を、図7を用いて模式的に説明する。

【0039】

実験には、各電子部品を回路基板2に実装しただけで、樹脂層12をモールドしていない送信モジュール1Aを用いた。また、シールド層13に相当するものとして、第1のテスト用シールドケース31を用いた。第1のテスト用シールドケース31は、長方形状の第1のテスト用天面シールド部31Aと、このテスト用天面シールド部31Aの短辺および長辺のそれぞれから垂設する第1のテスト用短辺側面シールド部31Bと、第1のテスト用長辺側面シールド部31Cとから一体に形成される。なお、第1のテスト用シールドケース31は、例えば、弾力性のある厚みが50〜100μm程度の銅箔を折り曲げて形成した。また、第1のテスト用シールドケース31でコアアイソレータ素子14を覆うと共に、第1のテスト用シールドケース31をグランド電位に電気的に接続した。

【0040】

回路基板2を定盤上に固定し、第1のテスト用天面シールド部31Aを回路基板2の厚さ方向(上下方向)にプランジャPで押圧した。弾性によって、第1のテスト用短辺側面シールド部31Bおよび第1のテスト用長辺側面シールド部31Cが撓むため、テスト用天面シールド部31Aが上下方向に変位し、第1のテスト用天面シールド部31Aとコアアイソレータ素子14の天面14Aとの離間する距離Laを変えることができる。このとき、1750〜2150MHzの周波数帯域の疑似信号を送信モジュール1Aに入力し、距離Laと、コアアイソレータ素子14による挿入損失との関係を測定した。また、例えば、W-CDMA(Wideband Code Division Multiple Access)の使用帯域である1920〜1980MHzの周波数の疑似信号を送信モジュール1Aに入力し、距離Laと、コアアイソレータ素子14による挿入損失の最低値との関係を測定した。

【0041】

図8に示すように、1750〜2150MHzの周波数帯域において、第1のテスト用天面シールド部31Aとコアアイソレータ素子14の天面14Aとの距離Laが小さくなると、すなわち、第1のテスト用天面シールド部31Aとコアアイソレータ素子14の天面14Aとが近付くと、挿入損失は増加する傾向にある。一方、距離Laが80μm以上の場合には、挿入損失は殆ど変化しなくなる。

【0042】

また、図9に示すように、1920〜1980MHzのW-CDMAの使用帯域におけるコアアイソレータ素子14による挿入損失の最低値は、距離Laを80μm以上に設定すると、第1のテスト用天面シールド部31Aとコアアイソレータ素子14との距離Laを広く離したとき、例えば、距離Laが1mmのときとほぼ変わらず、距離Laを広く離したときに対する許容値Cとして例えば0.02dB以下に抑制することできる。

【0043】

次に、送信モジュール1において、コアアイソレータ素子14の側面(短辺側面14B、長辺側面14C)と、シールド層13の短辺側面シールド層13Bあるいは長辺側面シールド層13Cを所定の間隔に離間することにより、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段の効果を示すための実験を、図10および図11を用いて模式的に説明する。

【0044】

上述した実験と同様、送信モジュール1Aと、第2のテスト用シールドケース32を用いた。第2のテスト用シールドケース32は、コアアイソレータ素子14の側面近傍に、コアアイソレータ素子14の側面と対向して載置できるように、第1のテスト用シールドケース31よりも小型に形成される。なお、第2のテスト用シールドケース32は、細長い直方体形状の第2のテスト用天面シールド部32Aと、このテスト用天面シールド部32Aの短辺および長辺のそれぞれから垂設する第2のテスト用短辺側面シールド部32Bと、第2のテスト用長辺側面シールド部32Cとから一体に形成される。なお、第2のテスト用シールドケース32は、例えば、弾力性のある厚みが50〜100μm程度の銅箔を折り曲げて形成した。

【0045】

第2のテスト用短辺側面シールド部32Bを、コアアイソレータ素子14のフェライト15の短辺側面と対向させて配置した。そして、第2のテスト用短辺側面シールド部32Bを第1の水平方向(図10の左右方向)に移動させ、第2のテスト用短辺側面シールド部32Bとコアアイソレータ素子14の短辺側面14Bとが離間する距離Lbを変えた。このとき、上述した実験と同様、1750〜2150MHzの周波数帯域の疑似信号を送信モジュール1Aに入力し、距離Lbと、コアアイソレータ素子14による挿入損失との関係を測定した。また、例えば、W-CDMAの使用帯域である1920〜1980MHzの周波数の疑似信号を送信モジュール1Aに入力し、距離Lbと、コアアイソレータ素子14による挿入損失の最低値との関係を測定した。

【0046】

さらに、第2のテスト用長辺側面シールド部32Cを、コアアイソレータ素子14のフェライト15の長辺側面と対向させて配置した。そして、第2のテスト用長辺側面シールド部32Cを第2の水平方向(図11の左右方向)に移動させ、第2のテスト用長辺側面シールド部32Cとコアアイソレータ素子14の長辺側面14Cとが離間する距離Lcを変えた。このとき、上述した実験と同様、1750〜2150MHzの周波数帯域の疑似信号を送信モジュール1Aに入力し、距離Lcと、コアアイソレータ素子14による挿入損失との関係を測定した。また、例えば、W-CDMAの使用帯域である1920〜1980MHzの周波数の疑似信号を送信モジュール1Aに入力し、距離Lcと、コアアイソレータ素子14による挿入損失の最低値との関係を測定した。

【0047】

この結果、図8に示した、コアアイソレータ素子14による挿入損失と周波数との関係と同様の測定結果(図示せず)が得られた。また、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段として、距離Lcに比べて、距離Lbの影響が大きいことが分かった。

【0048】

図12に、1920〜1980MHzのW-CDMAの使用帯域における、コアアイソレータ素子14の短辺側面14Bと第2のテスト用短辺側面シールド部32Bとの離間距離Lbと、コアアイソレータ素子14による挿入損失の最低値との関係を示す。挿入損失の最低値は、距離Lbを100μm以上に設定すると、第2のテスト用短辺側面シールド部32Bとコアアイソレータ素子14との距離Lbを広く離したとき、例えば、距離Lbが1mmのときとほぼ変わらず、距離Lbを広く離したときに対する許容値Cとして例えば0.02dB以下に抑制することできる。

【0049】

また、詳細な説明は省略するが、第1のテスト用天面シールド部31Aとコアアイソレータ素子14の天面14Aとの距離Laと、コアアイソレータ素子14による挿入損失の増加の抑制との関係は、コアアイソレータ素子14の下面14Dと回路基板2に形成されたグランドパターン3Aとの距離Ldと、コアアイソレータ素子14による挿入損失の増加の抑制との関係についても、同様に当てはまる。すなわち、距離Ldを80μm以上に設定することにより、コアアイソレータ素子14による挿入損失の増加を抑制することができる。

【0050】

なお、第1および第2のテスト用シールドケース31,32をコアアイソレータ素子14から離間して配置すること、また、グランドパターン3Aをコアアイソレータ素子14の下面14Dから離間して配置することにより、コアアイソレータ素子14による挿入損失の増加を抑制できる理由として、第1および第2のテスト用シールドケース31,32がコアアイソレータ素子14の天面14A、短辺側面14Bあるいは長辺側面14Cに接近し過ぎると、また、グランドパターン3Aがコアアイソレータ素子14の下面14Dに接近し過ぎると、永久磁石22A,22Bによって、フェライト15の第1,第2の長辺側面15A,15Bに対して略垂直に均一印加されていた磁界φの均一性が乱れ、第1のインダクタンス素子L1および第2のインダクタンス素子L2のインダクタンス値が変化することに起因すると思われる。

【0051】

従って、送信モジュール1における天面シールド層13Aとコアアイソレータ素子14の天面14Aとが離間する距離Laを80μm以上とすることが、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段として効果的である。

【0052】

また、送信モジュール1における短辺側面シールド層13Bとコアアイソレータ素子14の短辺側面14Bとが離間する距離Lbを100μm以上とすることが、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段として効果的である。

【0053】

さらに、送信モジュール1における回路基板2の上面2A側に形成されたグランドパターン3Aとコアアイソレータ素子14の下面14Dとが離間する距離Ldを、距離Laと同様に80μm以上とすることが、コアアイソレータ素子14による挿入損失の増加を抑制する抑制手段として効果的である。

【0054】

なお、送信モジュール1において、シールド層13とコアアイソレータ素子14との離間する各距離La〜Ldと、コアアイソレータ素子14による挿入損失の増加を抑制する効果の関係についてのみ説明した。しかしながら、送信モジュール1の構造に応じて、最適な距離に各距離La〜Ldを設定すれば、コアアイソレータ素子14による挿入損失の増加を相乗的に抑制することができることはいうまでもない。すなわち、距離La、距離Lb、距離Lc、距離Ldについてのそれぞれの最適距離を、送信モジュール1に構造に応じて設定することにより、送信モジュール1におけるコアアイソレータ素子14による挿入損失の増加を最も効率良く抑制することができる。

【0055】

なお、本実施の形態では、シールド層13とコアアイソレータ素子14との距離La〜Ldを広く離したときの挿入損失の増加に対する許容値Cを0.02dBとしてシールド層13とコアアイソレータ素子14との距離La〜Ldを決めたが、本発明はこれに限らず、所望の挿入損失や使用帯域等に応じてこれらの許容値や最小値は適宜設定できるものである。

【0056】

次に、図13に、本発明の第2の実施の形態である送信モジュール41の断面図を示す。本実施の形態では、前記第1の実施の形態と同一の構成要素に同一の符号を付し、その説明を省略する。

【0057】

回路基板42は、第1の実施の形態による回路基板2と同様に、表裏面にグランドパターン43A〜43Dや配線パターン(図示せず)が形成された複数層の絶縁層(図示せず)を、絶縁性のプリプレグ層(図示せず)を介して積層した多層基板である。グランドパターン43A〜43Dは、電子部品の実装面となる回路基板42の上面42Aから、下面42Bに向けて、順番に積層して形成される。

【0058】

また、回路基板42の上面42A側に位置し、例えば、コアアイソレータ素子14の下面14Dから80μm離間した距離近傍にある少なくともグランドパターン43A,43Bには、コアアイソレータ素子14の下面14Dと対面した部分を除去した除去部44が形成される。除去部44の面積は、製造公差に相当するマージンを考慮して、コアアイソレータ素子14の下面14Dの外形よりも大きな面積をもって形成される。

【0059】

このため、コアアイソレータ素子14の下面14Dから80μm離間した距離近傍にはグランド電位となるパターンがなくなり、結果的に、コアアイソレータ素子14の下面14Dとグランドパターン43A,43Bとの距離を80μm離間させたことになる。かくして、第2の実施の形態でも、第1の実施の形態と同様の作用効果を得ることができる。また、コアアイソレータ素子14の下面14Dと、回路基板42の実装面となる上面42Aとの距離を広く設計する必要がなくなるので、送信モジュール41を低背化することができる。

【0060】

なお、除去部44を設けると共に、第1の実施の形態で説明した如く、コアアイソレータ素子14とシールド層13とを所定の距離だけ離間することにより、コアアイソレータ素子14による挿入損失の増加を相乗的に抑制できることはいうまでもない。

【0061】

次に、図14に、本発明の第3の実施の形態である送信モジュール51の断面図を示す。本実施の形態では、前記第1の実施の形態と同一の構成要素に同一の符号を付し、その説明を省略する。

【0062】

シールドケース52は、第1の実施の形態によるシールド層13と同様に、コアアイソレータ素子14の天面14Aを覆う天面シールドケース52Aと、天面シールドケース52Aの短辺から回路基板2側に向けて垂下して設けられた短辺側面シールドケース52Bと、天面シールドケース52Aの短辺から回路基板2側に向けて垂下して設けられた長辺側面シールドケース52Cとから一体に構成された導電性の箱体である。シールドケース52は、例えば、回路基板2の周縁にまで延びる、グランドパターン3A〜3Dあるいはグランドパターン3A〜3Dと電気的に接続された配線パターンを介して、グランド電位と電気的に接続される。シールドケース52は、例えば、銀、銅、アルミニウム等の金属材料を用いて形成される。なお、電力増幅器10の表面には、耐湿性等の理由から一般的にはポッティング樹脂53が設けられるが、必ずしも設けなくてもよい。

【0063】

コアアイソレータ素子14とシールドケース52とは、第1の実施の形態と同様に、所定距離を離間して配置形成される。かくして、第3の実施の形態でも第1の実施の形態と同様の作用効果を得ることができる。

【0064】

次に、図15に、本発明の第4の実施の形態である送信モジュール61の断面図を示す。本実施の形態では、前記第1の実施の形態と同一の構成要素に同一の符号を付し、その説明を省略する。

【0065】

送信モジュール61の回路基板2の上面2Aには、シールド部が設けられない。一方、コアアイソレータ素子14の下面14Dとグランドパターン3Aとの間の距離Ldを、例えば最小値として80μm以上離間させる。なお、電力増幅器10の表面には、ポッティング樹脂を設けてもよく、設けなくてもよい。

【0066】

かくして、第4の実施の形態でも、第1の実施の形態と同様の作用効果を得ることができる。

【0067】

次に、図16に、本発明の第5の実施の形態である送信モジュール71の断面図を示す。本実施の形態では、前記第2の実施の形態と同一の構成要素に同一の符号を付し、その説明を省略する。

【0068】

送信モジュール71の回路基板42の上面42Aには、シールド部が設けられない。一方、回路基板42の上面42A側に位置し、例えば、コアアイソレータ素子14の下面14Dから80μm離間した距離近傍にある少なくともグランドパターン43A,43Bには、コアアイソレータ素子14の下面14Dと対面した部分を除去した除去部44が形成される。なお、電力増幅器10の表面には、ポッティング樹脂を設けてもよく、設けなくてもよい。かくして、第5の実施の形態でも、第2の実施の形態と同様の作用効果を得ることができる。

【0069】

なお、前記各実施の形態では、非可逆回路素子としてのコアアイソレータ素子14はアイソレータ回路24を構成するものとしたが、サーキュレータを構成してもよい。また、コアアイソレータ素子14に接続されるコンデンサC1,C2,CS1,CS2および抵抗Rをチップ部品によって形成するものとしたが、これらのコンデンサ、抵抗等の受動素子は回路基板の内部に形成してもよい。また、送信モジュールには、整合回路を構成するコンデンサ素子やインダクタンス素子を付け加えても良い。

【0070】

また、前記各実施の形態では、回路基板2,42は4層のグランドパターン3A〜3D,43A〜43Dを備えた多層基板によって構成した。しかし、本発明はこれに限らず、回路基板は、2層、3層または5層以上のグランドパターンを備えた多層基板によって構成してもよく、内部に単一のグランドパターンを備えた多層基板によって構成してもよい。また、回路基板は、片面基板や、両面基板によって構成してもよい。

【0071】

また、前記各実施の形態では、絶縁性の樹脂材料を用いて一様な樹脂層12を形成する構成としたが、例えば国際公開第2008/087788号に記載されたように、非磁性樹脂材料からなる最内層と磁性樹脂材料からなる磁性樹脂層とによって2層にモールドした樹脂層を設ける構成としてもよい。

【0072】

また、前記第1および第2の実施の形態では、導電性の金属薄膜からなるシールド層13によってシールド部を形成したが、第3の実施の形態と同様のシールドケース52を用いてシールド部を形成してもよい。

【0073】

また、前記各実施の形態では、送信信号がW-CDMA帯域となる1920〜1980MHzに設定された送信モジュール1,41,51,61,71を例に挙げて説明したが、他の使用帯域の送信信号に用いる送信モジュールに適用してもよい。

【符号の説明】

【0074】

1,41,51,61,71 送信モジュール

2,42 回路基板

3A〜3D,43A〜43D グランドパターン

10 電力増幅器

12 樹脂層

13 シールド層

14 コアアイソレータ素子

14A 天面

14B 短辺側面

14C 長辺側面

14D 下面

44 除去部

52 シールドケース

【特許請求の範囲】

【請求項1】

回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器とを有し、該電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、

前記回路基板に設けたグランド電位となるグランドパターンと、

少なくとも前記コアアイソレータ素子を覆う、前記回路基板の実装面に設けられた絶縁性の樹脂層と、

該樹脂層の表面を覆う導電性材料からなるシールド部とを備え、

前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールド部との離間距離の少なくとも一方を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴とする送信モジュール。

【請求項2】

回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器とを有し、該電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、

前記回路基板に設けたグランド電位となるグランドパターンと、

少なくとも前記コアアイソレータ素子を覆うシールドケースとを備え、

前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールドケースとの離間距離の少なくとも一方を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴とする送信モジュール。

【請求項3】

前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールド部との離間距離の少なくとも一方を広く離間したときに得られる、前記コアアイソレータ素子の挿入損失の最低値に比べて、挿入損失の増加分が0.02dB以下となる間隔に、前記抑制手段により離間させてなる請求項1または2に記載の送信モジュール。

【請求項4】

前記抑制手段により、前記コアアイソレータ素子の天面と、該天面と対向する前記シールド部との離間距離を80μm以上とした請求項1ないし3のいずれかに記載の送信モジュール。

【請求項5】

前記抑制手段により、前記コアアイソレータ素子の側面と、該側面と対向する前記シールド部との離間距離を100μm以上とした請求項1ないし4のいずれかに記載の送信モジュール。

【請求項6】

前記抑制手段により、前記コアアイソレータ素子の下面と、該下面と対向する前記グランドパターンとの離間距離を80μm以上とした請求項1ないし5のいずれかに記載の送信モジュール。

【請求項7】

前記回路基板は多層基板であって、前記グランドパターンは複数層に形成されてなり、

前記グランドパターンのうち少なくとも前記コアアイソレータ素子に近接して対向配置された前記グランドパターンにおける、前記コアアイソレータ素子と対面する領域を少なくとも除去してなる請求項1ないし6のいずれかに記載の送信モジュール。

【請求項8】

回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器と、前記回路基板に設けられたグランド電位となるグランドパターンとを有し、前記電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、

前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴とする送信モジュール。

【請求項1】

回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器とを有し、該電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、

前記回路基板に設けたグランド電位となるグランドパターンと、

少なくとも前記コアアイソレータ素子を覆う、前記回路基板の実装面に設けられた絶縁性の樹脂層と、

該樹脂層の表面を覆う導電性材料からなるシールド部とを備え、

前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールド部との離間距離の少なくとも一方を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴とする送信モジュール。

【請求項2】

回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器とを有し、該電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、

前記回路基板に設けたグランド電位となるグランドパターンと、

少なくとも前記コアアイソレータ素子を覆うシールドケースとを備え、

前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールドケースとの離間距離の少なくとも一方を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴とする送信モジュール。

【請求項3】

前記コアアイソレータ素子と前記グランドパターンとの離間距離、前記コアアイソレータ素子と前記シールド部との離間距離の少なくとも一方を広く離間したときに得られる、前記コアアイソレータ素子の挿入損失の最低値に比べて、挿入損失の増加分が0.02dB以下となる間隔に、前記抑制手段により離間させてなる請求項1または2に記載の送信モジュール。

【請求項4】

前記抑制手段により、前記コアアイソレータ素子の天面と、該天面と対向する前記シールド部との離間距離を80μm以上とした請求項1ないし3のいずれかに記載の送信モジュール。

【請求項5】

前記抑制手段により、前記コアアイソレータ素子の側面と、該側面と対向する前記シールド部との離間距離を100μm以上とした請求項1ないし4のいずれかに記載の送信モジュール。

【請求項6】

前記抑制手段により、前記コアアイソレータ素子の下面と、該下面と対向する前記グランドパターンとの離間距離を80μm以上とした請求項1ないし5のいずれかに記載の送信モジュール。

【請求項7】

前記回路基板は多層基板であって、前記グランドパターンは複数層に形成されてなり、

前記グランドパターンのうち少なくとも前記コアアイソレータ素子に近接して対向配置された前記グランドパターンにおける、前記コアアイソレータ素子と対面する領域を少なくとも除去してなる請求項1ないし6のいずれかに記載の送信モジュール。

【請求項8】

回路基板と、該回路基板に実装されたコアアイソレータ素子と電力増幅器と、前記回路基板に設けられたグランド電位となるグランドパターンとを有し、前記電力増幅器の出力側に前記コアアイソレータ素子が接続されてなる送信モジュールであって、

前記コアアイソレータ素子の周囲には、前記コアアイソレータ素子と前記グランドパターンとの離間距離を所定の間隔に離間させてなる、前記コアアイソレータ素子による挿入損失の増加を抑制する抑制手段を設けたことを特徴とする送信モジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2013−70287(P2013−70287A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−208241(P2011−208241)

【出願日】平成23年9月23日(2011.9.23)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月23日(2011.9.23)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]