通信装置

【課題】 複数個の装置のそれぞれから要求パケットが繰り返し受信される状況において、複数個の装置間の要求パケットの受信タイミングを近づけ得る技術を提供する。

【解決手段】 多機能機10は、PC100からステータス要求パケットを受信し、PC200からステータス要求パケットを受信する。多機能機10は、PC100からのステータス要求パケットに対する応答パケットをPC100に送信し、PC200からのステータス要求パケットに対する応答パケットをPC200に送信する。多機能機10は、PC200からのステータス要求パケットの受信からPC200への応答パケットの送信までの時間が、PC100からのステータス要求パケットの受信からPC200への応答パケットの送信までの時間よりも長くなるように、PC200への送信タイミングを決定する。

【解決手段】 多機能機10は、PC100からステータス要求パケットを受信し、PC200からステータス要求パケットを受信する。多機能機10は、PC100からのステータス要求パケットに対する応答パケットをPC100に送信し、PC200からのステータス要求パケットに対する応答パケットをPC200に送信する。多機能機10は、PC200からのステータス要求パケットの受信からPC200への応答パケットの送信までの時間が、PC100からのステータス要求パケットの受信からPC200への応答パケットの送信までの時間よりも長くなるように、PC200への送信タイミングを決定する。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書では、外部装置から送信される要求パケットに対する応答パケットを送信する通信装置を開示する。

【背景技術】

【0002】

特許文献1には、クライアントコンピュータに接続されるMFP(多機能周辺装置)が開示されている。MFPは、クライアントコンピュータからイベント記述子列が受信されると、イベント記述子列に対する応答として、成功メッセージ又はエラーメッセージを、クライアントコンピュータに送信する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−154823号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記の特許文献1の技術では、例えば、MFPが、複数個のクライアントコンピュータのそれぞれから、イベント記述子列を繰り返し受信する状況では、イベント記述子列の受信タイミングにばらつきが生じる可能性がある。この場合、MFPは、効率的な処理を実行することができない可能性がある。

【0005】

本明細書では、複数個の装置のそれぞれから要求パケットが繰り返し受信される状況において、複数個の装置間の要求パケットの受信タイミングを近づけ得る技術を提供する。

【課題を解決するための手段】

【0006】

本明細書によって開示される技術は、第1の装置と第2の装置とのそれぞれに接続される通信装置である。第1の装置は、第1の要求パケットを通信装置に送信して、第1の要求パケットに対する第1の応答パケットを、通信装置から受信する処理を繰り返し実行する。第1の装置は、第1の応答パケットを受信してから所定の期間が経過する際に、第1の要求パケットを新たに送信する。第2の装置は、第2の要求パケットを通信装置に送信して、第2の要求パケットに対する第2の応答パケットを、通信装置から受信する処理を繰り返し実行する。第2の装置は、第2の応答パケットを受信してから上記の所定の期間が経過する際に、第2の要求パケットを新たに送信する。通信装置は、受信制御部と、送信制御部と、決定部と、を備える。受信制御部は、第1の装置から第1の要求パケットを受信し、第2の装置から第2の要求パケットを受信する。送信制御部は、第1の要求パケットに対する第1の応答パケットを第1の装置に送信し、第2の要求パケットに対する第2の応答パケットを第2の装置に送信する。決定部は、第2の応答パケットを第2の装置に送信するための送信タイミングを決定する。決定部は、第2の要求パケットの受信から当該第2の要求パケットに対する第2の応答パケットの送信までの期間が、第1の要求パケットの受信から当該第1の要求パケットに対する第1の応答パケットの送信までの期間よりも長くなるように、送信タイミングを決定する。送信制御部は、決定済みの送信タイミングで、第2の応答パケットを第2の装置に送信する。

【0007】

上記の構成では、通信装置は、第2の要求パケットの受信から第2の応答パケットの送信までの期間が、第1の要求パケットの受信から第1の応答パケットの送信までの期間よりも長くなるようなタイミングで、第2の応答パケットを送信する。この構成によれば、特定の第2の要求パケットに対する第2の応答パケットの送信タイミングを、上記の特定の第2の要求パケットの次に受信される特定の第1の要求パケットに対する第1の応答パケットの送信タイミングに近づけ得る。第1の装置と第2の装置との両者は、応答パケットを受信してから所定の期間が経過すると、次の要求パケットを送信する。このため、上記の特定の第2の要求パケットの次に受信される第2の要求パケットの受信タイミングを、上記の特定の第1の要求パケットの次に受信される第1の要求パケットの受信タイミングに近づけ得る。

【0008】

なお、上記の通信装置を実現するための制御方法、コンピュータプログラム、及び、当該コンピュータプログラムが記憶された記憶媒体も、新規で有用である。また、上記の通信装置と上記の第1及び第2の装置とを含むシステムも新規で有用である。

【図面の簡単な説明】

【0009】

【図1】ネットワークシステムの構成を示す。

【図2】応答処理のフローチャートを示す。

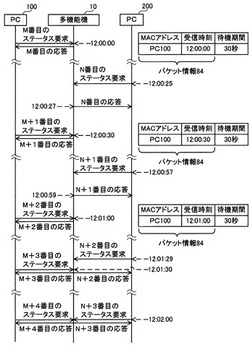

【図3】各装置の動作を表わすシーケンス図を示す。

【発明を実施するための形態】

【0010】

図1に示すように、ネットワークシステム2は、PC100,200と、多機能機(即ちPC100,200の周辺機器)10と、を備える。各装置10,100,200は、LAN4を介して、相互に通信可能である。

【0011】

(多機能機10の構成)

図1に示すように、多機能機10は、ASIC(Application Specific Integrated Circuit)12、フラッシュメモリ70、SDRAM80、ネットワークインターフェイス90、表示パネル92、及び、画像形成部94を備える。

【0012】

ASIC12は、メインCPU20、メイン用クロック回路30、サブCPU40、サブ用クロック回路50、SRAM60、SDRAM制御回路64、及び、MACコントローラ66を備える。

【0013】

メインCPU20は、SDRAM80に記憶されているプログラム82に従って様々な処理を実行する。これにより、受信制御部22と送信制御部24と決定部26との各機能が実現される。メイン用クロック回路30は、メインCPU20にクロック信号を供給する。メイン用クロック回路30からメインCPU20にクロック信号が供給されている間は、メインCPU20は非スリープ状態である。メインCPU20にクロック信号が供給されていない間は、メインCPU20はスリープ状態である。メインCPU20のスリープ状態は、メインCPU20の非スリープ状態と比較して、消費電力が低い状態である。メイン用クロック回路30は、サブCPU40によって制御される。即ち、サブCPU40によって、メインCPU20へのクロック信号の供給及び停止が制御される。

【0014】

サブCPU40は、SRAM60に記憶されているプログラム62に従って様々な処理を実行する。これにより、受信制御部42と移行制御部48との各機能が実現される。サブ用クロック回路50は、サブCPU40にクロック信号を供給する。サブ用クロック回路50のクロック信号の周波数は、メイン用クロック回路30のクロック信号の周波数よりも低い。従って、メインCPU20を駆動するための消費電力と比べて、サブCPU40を駆動するための消費電力は低い。なお、メインCPU20の処理速度は、サブCPU40の処理速度よりも速い。サブ用クロック回路50は、多機能機10の電源がONにされるとサブCPU40にクロック信号を供給し、多機能機10の電源がOFFにされるとクロック信号を停止する。即ち、サブCPU40は、多機能機10の電源がONされている間、クロック信号が供給されている状態(非スリープ状態)で維持される。変形例では、サブCPU40は、メインCPU20が非スリープ状態である間、スリープ状態であってもよい。即ち、サブ用クロック回路50は、メインCPU20が非スリープ状態である間、サブCPU40へのクロック信号を停止してもよい。

【0015】

SRAM60は、各CPU20,40からアクセス可能である。多機能機10の電源がONされると、メインCPU20は、フラッシュメモリ70内の圧縮されたプログラム72を展開して、展開済みのプログラム62をSRAM60に記憶する。

【0016】

SDRAM制御回路64は、サブCPU40からの指示に従って、SDRAM80に対するクロック信号の供給の開始又は停止をして、消費電力が比較的に高い通常動作モードと、消費電力が比較的に低いセルフリフレッシュモードと、の間でSDRAM80の状態を移行させる。

【0017】

MACコントローラ66は、ネットワークインターフェイス90に接続されている。MACコントローラ66は、LAN4を介して、ネットワークインターフェイス90でパケットが受信されると、メインCPU20又はサブCPU40の割込コントローラ(図示省略)にパケット割込要求信号を供給する。

【0018】

フラッシュメモリ70は、ASIC12の外部に設けられている。フラッシュメモリ70は、各CPU20,40からアクセス可能である。フラッシュメモリ70は、各CPU20,40によって実行されるプログラム62,82が圧縮された状態のプログラム72を記憶している。

【0019】

SDRAM80は、メインCPU20からアクセス可能である。SDRAM80は、SRAM60よりもメモリの総容量が大きく、各CPU20,40がアクセス(読み出し、書き込み)可能な速度が高速である。このため、SDRAM80の消費電力は、SRAM60の消費電力と比べて高い。SDRAM80は、SDRAM制御回路64によって制御され、通常動作モードとセルフリフレッシュモードとの間で状態が移行する。また、SDRAM80は、パケット情報84を記憶することができる。パケット情報84とは、ステータス要求パケットの受信時刻と、当該ステータス要求パケットの送信元のデバイス(例えばPC100)のMACアドレスと、が対応付けられた情報である(図3参照)。

【0020】

表示パネル92は、メインCPU20からの指示に従って、情報を表示する。表示パネル92には、ユーザからの操作を受け付けるためのタッチボタンが配置される。画像形成部94は、インクジェット方式又はレーザ方式の画像形成機構を備え、メインCPU20からの指示に従って、外部のデバイス(例えばPC100,200)から受信される印刷データによって表わされる画像を、印刷用紙に印刷する。

【0021】

(多機能機10の状態移行)

多機能機10の状態は、レディ状態とスリープ状態との間で移行する。多機能機10の電源がONされると、多機能機10は、レディ状態となる。

【0022】

(レディ状態)

多機能機10がレディ状態である場合、2個のCPU20,40は非スリープ状態(2個のクロック回路30,50からそれぞれクロック信号が供給されている状態)であり、2個のRAM60,80は通常動作モードである。この状態では、メインCPU20は、通常の処理を実行することができる。上記の通常の処理は、印刷指示パケットに従った印刷処理、ユーザの表示パネル92への操作に従った表示処理等を含む。なお、メインCPU20は、多機能機10がレディ状態である場合、SDRAM80に、レディ状態を示す状態変数を記憶させる。

【0023】

(スリープ状態)

多機能機10は、サブCPU40が後述する図2のS16等の処理を実行することによって、レディ状態からスリープ状態に移行する。多機能機10がスリープ状態である場合、メインCPU20はスリープ状態であり(メイン用クロック回路30からのクロック信号が停止されている状態)、サブCPU40は非スリープ状態であり(サブ用クロック回路50からのクロック信号が供給されている状態)、SRAM60は通常動作モードであり、SDRAM80はセルフリフレッシュモードである。多機能機10がスリープ状態であって、メインCPU20が上記の通常の処理(印刷処理、表示処理等)を実行すべき場合には、多機能機10は、レディ状態に移行する。

【0024】

なお、メインCPU20は、多機能機10がレディ状態からスリープ状態に移行される際に、SDRAM80内の状態変数を、SRAM60に移動させる。サブCPU40は、多機能機10がスリープ状態に移行されると、SRAM60内の状態変数を、スリープ状態を示す状態変数に変更する。さらに、サブCPU40は、多機能機10がスリープ状態からレディ状態に移行される際に、SRAM60内の状態変数を、SDRAM80に移動させる。メインCPU20は、多機能機10がレディ状態に移行されると、SDRAM80内の状態変数を、レディ状態を示す状態変数に変更する。

【0025】

(PC100の構成)

PC100には、多機能機10のステータスを監視するためのステータス監視プログラム(例えばステータスモニタ)がインストールされている。ユーザは、PC100を操作することによって、ステータス監視プログラムを起動させることができる。PC100は、ステータス監視プログラムが起動されると、多機能機10から多機能機10のステータス情報を取得する。

【0026】

具体的には、PC100は、ステータス監視プログラムが起動されると、ステータス要求パケットを、多機能機10に送信する。なお、ステータス要求パケットは、PC100のMACアドレスを含む。PC100は、ステータス要求パケットの応答として、多機能機10からステータス情報を含む応答パケットを受信する。PC100は、受信された応答パケットに従って、ステータス情報をPC100の表示部に表示させる。PC100は、応答パケットの受信から予め決められた待機期間(本実施例では30秒間)が経過する際に、ステータス要求パケットを、多機能機10に新たに送信する。即ち、PC100は、ステータス監視プログラムが起動されている間、ステータス要求パケットの送信処理と、応答パケットの受信処理と、を繰り返し実行する。

【0027】

なお、ステータス情報は、多機能機10の状態(スリープ状態又はレディ状態)、印刷用紙の有無、トナーの有無、及び、実行中の印刷のエラー情報(例えば用紙詰まり、画像形成部の故障等)を示す情報を含む。

【0028】

PC100は、およそ30秒間隔(上記の待機期間)で、多機能機10からステータス情報を繰り返し取得する。これにより、PC100のユーザは、多機能機10の最新のステータスを確認することができる。この構成によれば、例えば、PC100のユーザは、多機能機10の画像形成部94に印刷処理を実行させている場合に、印刷用紙が無くなったことを早期に知ることができる。また、PC100がステータス情報を多機能機10から定期的に取得するため、PC100のユーザは、多機能機10のステータス情報を、PC100に取得させるための操作を実行しなくて済む。

【0029】

PC100は、ステータス要求パケットを多機能機10に送信してから、2秒間(以下では「タイムアウト時間」と呼ぶ)経過しても、応答パケットが多機能機10から受信されない場合、応答パケットを受信できないと判断する。この場合、PC100は、再度、ステータス要求パケットを、多機能機10に送信する。PC100は、予め決められた個数のステータス要求パケットを送信しても、タイムアウト時間内に応答パケットが受信されない場合、通信エラーを示す情報を、PC100の表示部に表示させる。これにより、PC100のユーザは、多機能機10とPC100とが通信できないことを知ることができる。

【0030】

なお、PC100は、ステータス要求パケットを多機能機10に送信してからタイムアウト時間が経過した後に、応答パケットが多機能機10から受信されたとしても、応答パケットに従ったステータス情報を、PC100の表示部に表示させない。

【0031】

PC200は、PC100と同様の構成を備える。即ち、PC200は、ステータス監視プログラムが起動されると、ステータス要求パケットを、多機能機10に送信する送信処理と、多機能機10から応答パケットを受信する受信処理と、を繰り返し実行する。

【0032】

(メインCPU20及びサブCPU40が実行する処理)

次いで、図2を参照して、メインCPU20及びサブCPU40が実行する処理の内容について説明する。本処理は、多機能機10の電源がONされている間、繰り返し実行される。多機能機10の電源がONされたタイミングでは、多機能機10はレディ状態である。即ち、多機能機10の電源がONされたタイミングでは、メインCPU20が本処理を実行する。

【0033】

S12では、受信制御部22は、LAN4を介して、パケットが受信されたのか否かを判断する。ネットワークインターフェイス90でパケットが受信される場合、MACコントローラ66は、パケット割込要求信号を、メインCPU20に供給する。受信制御部22は、パケット割込要求信号を取得すると、受信されたパケットを、ネットワークインターフェイス90からSDRAM80に移動させる。S12では、受信制御部22は、SDRAM80に受信済みのパケットが存在するのか否かを判断する。

【0034】

パケットが受信されていない場合(S12でNO)、S14において、メインCPU20は、メインCPU20をスリープ状態に移行可能(即ち多機能機10をスリープ状態に移行可能)であるのか否かを判断する。例えば、メインCPU20は、以下の(1)〜(5)の条件を含む複数個の条件の全てでNOと判断される場合に、スリープ状態に移行可能(S14でYES)と判断し、複数個の条件のうち、少なくとも1個の条件でYESと判断される場合に、スリープ状態に移行不可能(S14でNO)と判断する。

【0035】

上記の複数個の条件は、(1)多機能機10がパケットを外部に送信中であるのか否か、(2)未処理パケットがSDRAM80に記憶されているのか否か、(3)多機能機10にTCP接続しているデバイス(例えばPC100)があるのか否か、(4)多機能機10が起動又はシャットダウンのための処理を実行しているのか否か、(5)ネットワークの負荷が高いのか否か、を含む。

【0036】

例えば、メインCPU20がPC100等からのパケットに対する応答を送信している場合には、上記の(1)でYESと判断される。例えば、多機能機10がWebサーバ機能を有しており、PC100が多機能機10のWebサーバにTCP接続中である場合には、上記の(3)でYESと判断される。例えば、S14の処理を実行する直前の所定の期間に受信されたパケット数が所定の個数を超えている場合には、多機能機10が処理すべきパケットを受信する可能性が高いために、上記の(5)でYESと判断される。従って、ここで示されるように、上記の(1)〜(5)の条件のうち、少なくとも1個の条件でYESと判断される場合に、スリープ状態に移行不可能(S14でNO)と判断する。

【0037】

一方、上記の(1)〜(5)の条件の全てでNOと判断される場合に、メインCPU20がスリープ状態に移行可能(S14でYES)と判断される。このS14でYESの場合、S16において、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる。具体的には、移行制御部48は、メイン用クロック回路30にクロック供給の停止を指示する。この結果、メインCPU20は、非スリープ状態からスリープ状態に移行する。なお、S16では、さらに、移行制御部48は、SDRAM80を通常動作モードからセルフリフレッシュモードに移行させる。これにより、多機能機10は、スリープ状態となる。なお、SDRAM80がセルフリフレッシュモードである間は、SDRAM80に情報を書き込んだり、SDRAM80から情報を読み込んだりすることができない。例えば、ネットワークインターフェイス90で受信されたパケットをSDRAM80に記憶させることができない。

【0038】

なお、メインCPU20は、S16でスリープ状態に移行する前に、多機能機10をレディ状態からスリープ状態に移行するために、以下の処理を実行する。即ち、メインCPU20は、代理応答情報を、SDRAM80からSRAM60に移動させる。代理応答情報は、メインCPU20がスリープ状態である間に受信されたパケットに従った処理を、サブCPU40が実行するための情報(例えば多機能機10のIPアドレス、MACアドレス、ノード名等)を含む。また、メインCPU20は、LAN4を介して受信されるパケットを記憶するためのRAMを、SDRAM80からSRAM60に切り替える。続いて、メインCPU20は、サブCPU40以外からの割込要求をマスク(禁止)する。次いで、メインCPU20は、サブCPU40に処理を開始させるための開始信号を、サブCPU40に供給する。サブCPU40は、開始信号が取得されると、S16の処理を実行する。なお、メインCPU20は、WAIT命令を実行する。WAIT命令が実行されると、メインCPU20は、サブCPU40から割込要求信号が供給されるまで待機する実行停止状態となる。

【0039】

S16が終了すると、S12に戻る。即ち、メインCPU20がスリープ状態である間に、S12が実行される。この場合、サブCPU40の受信制御部42がS12を実行する。S12でNOの場合、S14において、メインCPU20が既にスリープ状態であるために、NOと判断され、S12に戻る。

【0040】

以下のS18の処理では、S12において、サブCPU40の受信制御部42が、パケットが受信されたと判断する場合(メインCPU20がスリープ状態である間にパケットが受信される場合)について説明する。

【0041】

S18では、サブCPU40は、メインCPU20がスリープ状態であるのか否かを判断する。具体的には、サブCPU40は、SRAM60内の状態変数を確認して、多機能機10がスリープ状態であるのか否かを判断することによって、メインCPU20がスリープ状態であるのか否かを判断する。この場合では、S18にてYESと判断され、次いで、S20では、サブCPU40は、S12で受信されたパケットを解析することによって、サブCPU40自身がパケットに従った処理を実行することができるのか否かを判断する。

【0042】

例えば、サブCPU40は、SRAM60内の代理応答情報を用いて、S12で受信されたパケットに従った応答処理を実行可能であるのか否かを判断する。サブCPU40が代理して実行可能な応答処理は、例えば、PINGに対する応答、ARP(Address Resolution Protocol)のパケットに対する応答等を含む。なお、S12で受信されたパケットがPC100,200からのステータス要求パケットである場合、サブCPU40は、サブCPU40自身がパケットに従った処理を実行することができないと判断する。

【0043】

S20でYESの場合、S22において、サブCPU40は、S12で受信されたパケットに従った処理を実行して、S12に戻る。S20でNOの場合、S24において、移行制御部48は、メインCPU20をスリープ状態から非スリープ状態に移行する。具体的には、移行制御部48は、メイン用クロック回路30に、メインCPU20にクロック供給を開始するよう指示する。この結果、メインCPU20にクロックが供給され、メインCPU20がスリープ状態から非スリープ状態に移行する。移行制御部48は、メインCPU20に割込要求信号を供給する。

【0044】

サブCPU40は、さらに、SDRAM80をセルフリフレッシュモードから通常動作モードに移行させる処理、外部デバイスからの受信パケットの記憶先をSRAM60からSDRAM80に切り替える処理、SRAM60内の情報をSDRAM80に移動させる処理等を実行する。

【0045】

メインCPU20は、サブCPU40から割込要求信号が供給されると、WAIT命令を解除する。メインCPU20は、SRAM60に記憶されている未処理のパケットを、SDRAM80に移動させる。

【0046】

S26において、メインCPU20は、S12で受信されたパケットが、ステータス要求パケットであるのか否かを判断する。具体的には、メインCPU20は、S12で受信されたパケットが、SNMP(Simple Network Management Protocol)のオブジェクトデータを要求するパケットであるのか否かを判断する。例えば、メインCPU20は、パケットの宛先ポート番号がSNMPを示すポート番号(即ち「161」)であり、かつ、パケットのSNMPメッセージに含まれるPDU(Protocol Data Unit)タイプがGetRequest又はGetNextRequestを示す場合に、ステータス要求パケットであると判断する。

【0047】

ステータス要求パケットでないと判断される場合(S26でNO)、S28において、メインCPU20は、S12で受信されたパケットに応じた処理(例えば上記の通常の処理(印刷指示パケットに従った印刷処理等))を実行して、S12に戻る。

【0048】

一方、ステータス要求パケットであると判断される場合(S26でYES)、S30において、メインCPU20は、SDRAM80にパケット情報84が記憶されているのか否かを判断する。パケット情報84がSDRAM80に記憶されていない場合(S30でNO)にS34に進み、記憶されている場合(S30でYES)にS32に進む。

【0049】

S32では、メインCPU20は、S12で受信されたステータス要求パケットの送信元のデバイスが、パケット情報84として記憶されているデバイスと一致するのか否かを判断する。具体的には、メインCPU20は、ステータス要求パケットに含まれる送信元のデバイスのMACアドレスと、パケット情報84に含まれるMACアドレスと、が一致するのか否かを判断する。ここで、上述した2つのMACアドレスが一致する場合、S32でYESと判断されS34に進み、一方、上述した2つのMACアドレスが異なる場合、S32でNOと判断されS36に進む。

【0050】

S34では、メインCPU20は、SDRAM80に、パケット情報84を記憶させる。S30でNOと判断された場合(即ちパケット情報84が記憶されていない場合)に実行されるS34では、メインCPU20は、ステータス要求パケットの送信元デバイスのMACアドレスと、当該ステータス要求パケットの受信時刻と、を対応付けて、SDRAM80に記憶させる。一方、S32でYESと判断された場合(即ちSDRAM80に既にパケット情報84が記憶されている場合)に実行されるS34では、メインCPU20は、パケット情報84に含まれる前回のステータス要求パケットの受信時刻を、今回のステータス要求パケットの受信時刻に更新する。S34が終了すると、S46に進む。なお、メインCPU20は、SDRAM80に記憶されているパケット情報84に含まれるMACアドレスに対応するデバイス(例えばPC100)から予め決められた期間(例えば1分間)が経過しても、次のステータス要求が受信されない場合、SDRAM80に記憶されているパケット情報84を削除する。

【0051】

一方、上述したように、今回のS12で受信されたステータス要求パケットの送信元のデバイス(以下では「PC200」を例として説明する)が、パケット情報84として記憶されているデバイス(以下では「PC100」を例として説明する)と異なる場合(S32でNOの場合)に、S36の処理が実行される。S36では、決定部26は、SDRAM80に記憶されているパケット情報84を用いて、PC100から次回のステータス要求パケットを受信する時刻である次回パケット受信時刻を算出する。具体的には、決定部26は、パケット情報84に含まれる受信時刻に、SDRAM80に予め記憶されている待機期間(即ち30秒)を加算することによって、次回パケット受信時刻を算出する。なお、多機能機10のベンダは、待機期間(即ち30秒)を、予めSDRAM80に記憶させる。変形例では、メインCPU20は、PC100からステータス要求パケットが受信される間隔を用いて、待機期間を特定し、特定された待機期間をSDRAM80に記憶させてもよい。

【0052】

次いで、S38では、S12でPC200から受信されたステータス要求パケットの受信時刻が、S36で算出されたPC100の次回パケット受信時刻とほぼ等しいのか否かを判断する。ここで「受信時刻がほぼ等しい」とは、例えば、ステータス要求パケットの受信時刻と次回パケット受信時刻との差分が、上記のタイムアウト時間よりも短い(例えば上記のタイムアウト時間の10分の1(即ち0.2秒))状態を意味する。

【0053】

なお、PC100は、前回のステータス要求パケットに対する応答パケットを受信してから待機期間が経過する際に、次回のステータス要求パケットを送信する。従って、厳密には、決定部26は、PC100が前回のステータス要求パケットに対する応答パケットを受信した時刻に、待機期間を加算することによって、次回パケット受信時刻を算出しなければならない。しかしながら、多機能機10がPC100からステータス要求パケットを受信してから、PCが多機能機10からステータス要求パケットに対する応答パケットを受信するまでの期間は、非常に短い。そのため、実質的に、ステータス要求パケットを多機能機10が受信する時刻と、当該ステータス要求パケットに対する応答パケットをPC100が受信する時刻とは、ほぼ等しい。

【0054】

ここで、上述した2つのパケット受信時刻がほぼ等しい場合、S38でYESと判断されS46に進み、一方、上述した2つのパケット受信時刻が略等しくない場合、S38でNOと判断され、S40に進む。S40では、決定部26は、S36で算出された次回パケット受信時刻と、S12におけるステータス要求パケットの受信時刻と、の差分(即ちX秒)が、上記のタイムアウト時間(即ち2秒間)よりも大きいのか否かを判断する。上記の差分(即ちX秒)がタイムアウト時間よりも大きい場合(S40でYES)、S42において、決定部26は、S12で受信されたステータス要求パケットの応答パケットを送信する送信タイミングを、S12で受信されたPC200のステータス要求パケットの受信時刻にタイムアウト時間(即ち2秒間)を加算した時刻に決定する。S42が終了すると、S46に進む。この構成によれば、ステータス要求パケットの送信元のデバイス(即ちPC200)が、ステータス要求パケットの応答を受信できないと判断することを回避することができる。

【0055】

なお、PC200は、ステータス要求パケットを送信してからタイムアウト時間が経過しても、応答パケットが多機能機10から受信されない場合に、応答を受信できないと判断する。従って、厳密には、決定部26は、S40及びS42において、以下の処理を実行すべきである。即ち、S40の処理では、決定部26は、上記の差分(即ちX秒)が、タイムアウト時間から多機能機10とPC200との間の往復の通信時間を減算した特定の時間よりも大きいのか否かを判断すべきである。そして、S42の処理では、決定部26は、S12で受信されたPC200のステータス要求パケットに対する応答パケットを送信する送信タイミングを、当該ステータス要求パケットの受信時刻に上記の特定の時間を加算した時刻に決定すべきである。しかしながら、多機能機10とPC200との間の往復の通信時間は、タイムアウト時間と比較して、無視できるほど短い。このため、S40及びS42の処理のように、タイムアウト時間を用いて決定された送信タイミングで応答パケットが送信されても、PC200がステータス要求パケットの応答を受信できないと判断するという事態は発生しない。

【0056】

一方、S40でNOの場合、即ち、X秒がタイムアウト時間よりも小さい場合、S44において、決定部26は、応答パケットの送信タイミングを、S12で受信されたPC200のステータス要求パケットの受信時刻にX秒を加算した時刻に決定する。S44が終了すると、S46に進む。S34、S42、又はS44の処理が終了した後、又はS38でYESと判断された後、S46では、送信制御部24は、S12のステータス要求パケットの応答として、多機能機10の現在のステータス情報を含む応答パケットを、S12のステータス要求パケットの送信元のデバイスに送信して、S12に戻る。S34の処理が実行され又はS38でYESと判断された後に実行されるS46では、送信制御部24は、ステータス要求パケットに対応する応答パケットを生成すると直ちに(待機せずに)、応答パケットを送信する。この場合、ステータス要求パケットが受信されてから、応答パケットが送信されるまでの時間は、非常に短い。一方、S42又はS44の処理が実行された後に実行されるS34では、送信制御部24は、ステータス要求パケットに対応する応答パケットを生成した後に、S42又はS44で決定されたタイミングまで待機し、決定されたタイミングが到来すると、応答パケットを送信する。

【0057】

なお、メインCPU20の受信制御部22が、S12において、パケットを受信したと判断した場合(多機能機10がレディ状態である間にパケットが受信された場合)には、メインCPU20は、S18でNOと判断し、S26以降の処理を実行する。S26以降の処理は、上記と同様である。

【0058】

(本実施例の効果)

図3を参照して、各装置10,100,200の動作と、本実施例の効果と、を説明する。なお、図3では、メインCPU20がスリープ状態である状況で開始される。

【0059】

12:00:00では、PC100は、M(Mは1以上の整数)番目のステータス要求パケットを、多機能機10に送信する。M番目のステータス要求パケットが受信されると、移行制御部48は、メインCPU20を非スリープ状態に移行させる(図2のS24)。メインCPU20は、PC100のMACアドレス(即ち「PC100」)と対応付けて、受信時刻(即ち「12:00:00」)を、記憶させる(即ちパケット情報84)(図2のS34)。送信制御部24は、M番目のステータス要求パケットの応答として、M番目の応答パケットを生成する。送信制御部24は、M番目の応答パケットが生成されると、直ちに、PC100に送信する(図2のS46)。

【0060】

M番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0061】

次いで、12:00:25では、PC200は、N(Nは1以上の整数)番目のステータス要求パケットを、多機能機10に送信する。N番目のステータス要求パケットが受信されると、移行制御部48は、メインCPU20を非スリープ状態に移行させる(図2のS24)。

【0062】

決定部26は、パケット情報84の受信時刻「12:00:00」に、待機期間(即ち30秒間)を加算して、次回パケット受信時刻(PC100からM+1番目のステータス要求パケットの受信時刻)(即ち「12:00:30」)を算出する(図2のS36)。算出された次回パケット受信時刻と、N番目のステータス要求パケットの受信時刻(即ち「12:00:25」)と、の差分(即ち5秒間)が、タイムアウト時間(即ち2秒間)よりも長い(図2のS40でYES)。このため、決定部26は、N番目のステータス要求パケットの応答として、N番目の応答パケットを送信する送信タイミングを、N番目のステータス要求パケットの受信時刻「12:00:25」にタイムアウト時間を加算した「12:00:27」に決定する(図2のS42)。送信制御部24は、N番目の応答パケットを、12:00:27に送信する(図2のS46)。上記の構成によれば、多機能機10は、N番目の応答パケットの送信タイミングを、M+1番目のステータス要求パケットに対するM+1番目の応答パケットの送信タイミングに近づけることができる。この結果、N+1番目の要求パケットの受信タイミングを、M+2番目の要求パケットの受信タイミングに近づけることができる。

【0063】

N番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0064】

次いで、12:00:30では、PC100は、M+1番目のステータス要求パケットを、多機能機10に送信する。なお、厳密には、PC100は、M番目の応答パケットを受信してから30秒後に、M+1番目のステータス要求パケットを送信する。しかしながら、PC100は、M番目のステータス要求パケットを送信してから、M番目の応答パケットを受信するまでの期間が非常に短いため、実質的に、M番目のステータス要求パケットの送信からM+1番目のステータス要求パケットの送信までの期間が、30秒間であると言うことができる。

【0065】

移行制御部48は、M+1番目のステータス要求パケットが受信されると、メインCPU20を非スリープ状態に移行する(図2のS24)。メインCPU20は、パケット情報84を記憶(図2のS34)する。送信制御部24は、M+1番目のステータス要求パケットの応答として、M+1番目の応答パケットを生成し、生成されたM+1番目の応答パケットを、直ちに送信する(図2のS46)。M+1番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0066】

12:00:57では、PC200は、N+1番目のステータス要求パケットを、多機能機10に送信する。移行制御部48は、N+1番目のステータス要求パケットが受信されると、メインCPU20を非スリープ状態に移行する(図2のS24)。

【0067】

決定部26は、パケット情報84の受信時刻「12:00:30」に、待機期間(30秒)を加算して、次回パケット受信時刻(PC100からM+1番目のステータス要求パケットの受信時刻)(即ち「12:01:00」)を算出する(図2のS36)。算出された次回パケット受信時刻と、N+1番目のステータス要求パケットの受信時刻(即ち「12:00:57」)と、の差分(即ち3秒間)が、タイムアウト時間(即ち2秒間)よりも長い(図2のS40でYES)。このため、決定部26は、N+1番目のステータス要求パケットの応答として、N+1番目の応答パケットを送信する送信タイミングを、N+1番目のステータス要求パケットの受信時刻「12:00:57」にタイムアウト時間を加算した「12:00:59」に決定する(図2のS42)。送信制御部24は、N+1番目の応答パケットを、12:00:59に送信する(図2のS46)。上記の構成では、多機能機10は、N+1番目の応答パケットの送信タイミングを、M+2番目の要求パケットに対するM+2番目の応答パケットの送信タイミングに近づけることができる。この結果、N+2番目の要求パケットの受信タイミングを、M+3番目の要求パケットの受信タイミングに近づけることができる。

【0068】

N+1番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0069】

時刻12:01:00において、PC100は、M+2番目のステータス要求パケットを、多機能機10に送信する。M+2番目のステータス要求パケットが受信されると、移行制御部48は、メインCPU20を非スリープ状態に移行する(図2のS24)。メインCPU20は、パケット情報84を記憶(図2のS34)する。送信制御部24は、M+2番目のステータス要求パケットの応答として、M+2番目の応答パケットを生成し、生成されたM+2番目の応答パケットを、直ちに送信する(図2のS46)。M+2番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0070】

時刻12:01:29において、PC200は、N+2番目のステータス要求パケットを、多機能機10に送信する。N+2番目のステータス要求パケットが受信されると、移行制御部48は、メインCPU20を非スリープ状態に移行する(図2のS24)。

【0071】

決定部26は、パケット情報84の受信時刻「12:00:30」に、待機期間(30秒)を加算して、次回パケット受信時刻(PC100からM+3番目のステータス要求パケットの受信時刻)(即ち「12:01:30」)を算出する(図2のS36)。算出された次回パケット受信時刻と、N+2番目のステータス要求パケットの受信時刻(即ち「12:01:29」)と、の差分が、タイムアウト時間(即ち2秒間)よりも短い(図2のS40でNO)。このため、決定部26は、N+2番目のステータス要求パケットの応答として、N+2番目の応答パケットを送信する送信タイミングを、N+2番目のステータス要求パケットの受信時刻「12:01:29」に、差分である1秒間を加算した「12:01:30」に決定する(図2のS44)。この構成では、PC200への応答パケットの送信タイミングを、PC100からのステータス要求パケットの受信タイミングを用いて決定している。この結果、PC200からのステータス要求パケットの受信タイミングを、PC100からのステータス要求パケットの受信タイミングに、適切に近づけることができる。

【0072】

PC100は、12:01:30に、M+3番目のステータス要求パケットを、多機能機10に送信する。このタイミングは、N+2番目の応答パケットを送信する送信タイミングに等しいため、メインCPU20は、非スリープ状態に維持されている。送信制御部24は、M+3番目のステータス要求パケットの応答として、生成されたM+3番目の応答パケットを、直ちに、PC100に送信する(図2のS46)。さらに、送信制御部24は、N+2番目の応答パケットの送信タイミング「12:01:30」が到来したため、N+2番目の応答パケットを、PC200に送信する(図2のS46)。この結果、M+3番目の応答パケットの送信タイミングと、N+2番目の応答パケットの送信タイミングと、をほぼ等しくさせることができる。なお、実際には、送信制御部24は、応答パケットを順番に送信するために、送信タイミングが厳密的な意味で一致しない。

【0073】

M+2番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0074】

12:02:00になると、受信制御部42は、PC100及びPC200のそれぞれから、M+4番目のステータス要求パケットと、N+3番目のステータス要求パケットと、を受信する。この構成によれば、多機能機10は、PC100からのステータス要求パケットとPC200からのステータス要求パケットとを、ほぼ等しいタイミングで受信することができる。

【0075】

なお、「ほぼ等しいタイミングで受信する」とは、例えば、例えば、ステータス要求パケットの受信時刻とS36で算出された次回パケット受信時刻との差分が、上記のタイムアウト時間よりも短い(例えば上記のタイムアウト時間の10分の1(即ち0.2秒))状態を意味する。あるいは、「ほぼ等しいタイミングで受信する」とは、図2のS12で受信されたステータス要求パケットについて、図2のS46の処理が実行された後、図2のS12に戻るまでの期間よりも短い状態を意味する。

【0076】

また、多機能機10は、PC200からのステータス要求パケットの受信タイミングを、PC100からのステータス要求パケットの受信タイミングに、近づけることによって、メインCPU200がスリープ状態から非スリープ状態に移行される頻度を低くすることができる。この結果、多機能機10の省電力を低減することができる。特に、図2のS12においてPC100から受信されたステータス要求パケットについての応答パケットの送信(図2のS46)後、図2のS12に戻るまでの間に、PC200からのステータス要求パケットが受信されている場合、S12でYESと判断され、メインCPU20がスリープ状態に移行されることを回避することができる。

【0077】

本実施例では、多機能機10は、PC200からのステータス要求パケットの受信から応答パケットの送信までの時間が、PC100からの要求パケットの受信から応答パケットの送信までの時間よりも長くなるようなタイミングで、PC200からの応答パケットを送信する。この構成によれば、PC200からのステータス要求パケットに対する応答パケットの送信タイミングを、PC200からのステータス要求パケットの次に受信されるPC100からのステータスの要求パケットに対する応答パケットの送信タイミングに近づけることができる。この結果、PC200からのステータス要求パケットの受信タイミングを、PC100からのステータス要求パケットの受信タイミングに近づける。

【0078】

(対応関係)

上記の多機能機10、PC100及びPC200のそれぞれが、「通信装置」、「第1の装置」及び「第2の装置」の一例である。PC100から送信されるステータス要求パケットが「第1の要求パケット」の一例であり、PC200から送信されるステータス要求パケットが「第2の要求パケット」の一例である。メインCPU20とサブCPU40とが「プロセッサ」の一例である。2個のPCU20,40が共に非スリープ状態である状態が「高消費状態」の一例であり、メインPCU20がスリープ状態であり、サブCPU40が非スリープ状態である状態が「低消費状態」の一例である。

【0079】

以上、本発明の実施形態について詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

【0080】

(変形例)

(1)上記の実施例では、多機能機10は、2個のCPU20,40を備えるが、これに代えて、多機能機10は、メインCPU20のみを備えていてもよい。この場合、メインCPU20に供給されるクロック信号の周波数が低い状態と高い状態とに移行してもよい。クロック信号の周波数が高い状態では、メインCPU20の消費電力が比較的に高く、クロック信号の周波数が低い状態では、メインCPU20の消費電力が比較的に低い。この変形例では、メインCPU20が「プロセッサ」の一例であり、メインCPU20に供給されるクロック信号の周波数が高い状態が「高消費状態」の一例であり、メインCPU20に供給されるクロック信号の周波数が低い状態が「低消費状態」の一例である。

【0081】

(2)上記の実施例では、決定部26は、SDRAM80に記憶されているパケット情報84を用いて、応答パケットの送信タイミングを決定している(図2のS36からS44)。しかしながら、決定部26は、PC100からのステータス要求パケットの受信タイミングと、PC200からのステータス要求パケットの受信タイミングと、が予め決められた間隔(例えば1秒間)以下となるまで、PC200からのステータス要求パケットに対する応答パケットの送信タイミングを、ステータス要求パケットの受信タイミングから予め決められた時間(例えば1秒間)だけ加算したタイミングに決定してもよい。本変形例も、「決定部は、第2の要求パケットの受信から当該第2の要求パケットに対する第2の応答パケットの送信までの時間が、第1の要求パケットの受信から当該第1の要求パケットに対する第1の応答パケットの送信までの時間よりも長くなるように、送信タイミングを決定する」という構成に含まれる。

【0082】

(3)上記の実施例では、メインCPU20がプログラム82に従って処理を実行することによって、決定部26の機能が実現されている。しかしながら、サブCPU40がプログラム62に従って処理を実行することによって、決定部の機能が実行されてもよい。この場合、図2のS26、S30からS44までの処理を、サブCPU40が実行してもよい。

【0083】

(4)上記の実施例では、メインCPU20が非スリープ状態である間にステータス要求パケットが受信される場合と、メインCPU20がスリープ状態である間にステータス要求パケットが受信される場合と、の両方の場合において、決定部26は、送信タイミングを決定している(図2のS42及びS44)。しかしながら、メインCPU20が非スリープ状態である間にステータス要求パケットが受信される場合には、決定部26は、送信タイミングを決定せず、直ちに、応答パケットを送信してもよい。この構成によれば、メインCPU20が非スリープ状態である間にステータス要求パケットが受信される場合には、応答パケットの送信タイミングの決定処理を実行しなくて済む。

【0084】

(5)上記の実施例では、決定部26は、パケット情報84に記憶されているデバイス(例えばPC100)への応答パケットの送信タイミングを決定しない。しかしながら、決定部26は、パケット情報84に記憶されているデバイス(例えばPC100)への応答パケットの送信タイミングを決定してもよい。即ち、決定部26は、受信される全てのステータス要求パケットへの応答パケットの送信タイミングを決定してもよい。

【0085】

(6)多機能機10に接続されるPCの個数に限りはない。多機能機10は、多数個のPCからのステータス要求パケットの受信タイミングが、パケット情報84に記憶されているPC100のステータス要求パケットの受信タイミングに近づくように、多数個のPCへの応答パケットの送信タイミングを決定してもよい。さらに、多数個のPCが多機能機10に接続される場合、多機能機10は、1個以上のPCのステータス要求パケットの受信時刻を、パケット情報84に記憶してもよい。そして、多機能機10は、パケット情報84に記憶されているPC以外の多数個のPCのステータス要求パケットのそれぞれの受信タイミングが、パケット情報84に含まれる1個以上PCのいずれかのPCに対応する受信タイミングに近づくように、応答パケットの送信タイミングを決定してもよい。例えば、多機能機10に10個のPCが接続されている場合、多機能機10は、5個のPCを第1グループとして、他の5個のグループを第2グループとして分類してもよい。多機能機10は、第1グループの中の1個の基準PCの受信タイミングに、第1グループの中の他の4個のPCの受信タイミングを近づけてもよい。同様に、多機能機10は、第2グループの中の1個の基準PCの受信タイミングに、第2グループの中の他の4個のPCの受信タイミングを近づけてもよい。この場合、第1グループの中の上記の基準PCの受信タイミングと、第2グループの中の上記の基準PCの受信タイミングと、は一致しなくてもよい。

【0086】

(7)上記の実施例では、決定部26は、PC100からのステータス要求パケットの受信時刻と待機期間とを用いて、PC200への応答パケットの送信タイミングを決定する(図2のS40)。しかしながら、決定部26は、多機能機10がPC100からのステータス要求パケットに対する応答パケットの送信タイミング、あるいは、PC100がステータス要求パケットに対する応答パケットの受信タイミングを用いて、PC200への応答パケットの送信タイミングを決定してもよい。本変形例では、多機能機10がPC100からのステータス要求パケットに対する応答パケットの送信タイミング、あるいは、PC100がステータス要求パケットに対する応答パケットの受信イミングが、「第1の要求パケットの受信に関するタイミング」の一例である。

【0087】

(8)上記の実施例では、メインCPU20がプログラム82に従って処理を実行することによって、各部22〜26が実現されるが、各部22〜26の少なくとも1個は、論理回路等のハードウェアで実現されてもよい。また、サブCPU40がプログラム62に従って処理を実行することによって、各部42、48が実現されるが、各部42、48の少なくとも1個は、論理回路等のハードウェアで実現されてもよい。

【0088】

(8)「通信装置」は、多機能機でなくてもよく、PC、プリンタ、サーバ、PDA等の通信装置であってもよい。

【0089】

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0090】

2:ネットワークシステム、10:多機能機、20:メインCPU、22:受信制御部、24:送信制御部、26:決定部、40:サブCPU、42:受信制御部、48:移行制御部、60:SRAM、70:フラッシュメモリ、80:SDRAM、100,200:PC

【技術分野】

【0001】

本明細書では、外部装置から送信される要求パケットに対する応答パケットを送信する通信装置を開示する。

【背景技術】

【0002】

特許文献1には、クライアントコンピュータに接続されるMFP(多機能周辺装置)が開示されている。MFPは、クライアントコンピュータからイベント記述子列が受信されると、イベント記述子列に対する応答として、成功メッセージ又はエラーメッセージを、クライアントコンピュータに送信する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−154823号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記の特許文献1の技術では、例えば、MFPが、複数個のクライアントコンピュータのそれぞれから、イベント記述子列を繰り返し受信する状況では、イベント記述子列の受信タイミングにばらつきが生じる可能性がある。この場合、MFPは、効率的な処理を実行することができない可能性がある。

【0005】

本明細書では、複数個の装置のそれぞれから要求パケットが繰り返し受信される状況において、複数個の装置間の要求パケットの受信タイミングを近づけ得る技術を提供する。

【課題を解決するための手段】

【0006】

本明細書によって開示される技術は、第1の装置と第2の装置とのそれぞれに接続される通信装置である。第1の装置は、第1の要求パケットを通信装置に送信して、第1の要求パケットに対する第1の応答パケットを、通信装置から受信する処理を繰り返し実行する。第1の装置は、第1の応答パケットを受信してから所定の期間が経過する際に、第1の要求パケットを新たに送信する。第2の装置は、第2の要求パケットを通信装置に送信して、第2の要求パケットに対する第2の応答パケットを、通信装置から受信する処理を繰り返し実行する。第2の装置は、第2の応答パケットを受信してから上記の所定の期間が経過する際に、第2の要求パケットを新たに送信する。通信装置は、受信制御部と、送信制御部と、決定部と、を備える。受信制御部は、第1の装置から第1の要求パケットを受信し、第2の装置から第2の要求パケットを受信する。送信制御部は、第1の要求パケットに対する第1の応答パケットを第1の装置に送信し、第2の要求パケットに対する第2の応答パケットを第2の装置に送信する。決定部は、第2の応答パケットを第2の装置に送信するための送信タイミングを決定する。決定部は、第2の要求パケットの受信から当該第2の要求パケットに対する第2の応答パケットの送信までの期間が、第1の要求パケットの受信から当該第1の要求パケットに対する第1の応答パケットの送信までの期間よりも長くなるように、送信タイミングを決定する。送信制御部は、決定済みの送信タイミングで、第2の応答パケットを第2の装置に送信する。

【0007】

上記の構成では、通信装置は、第2の要求パケットの受信から第2の応答パケットの送信までの期間が、第1の要求パケットの受信から第1の応答パケットの送信までの期間よりも長くなるようなタイミングで、第2の応答パケットを送信する。この構成によれば、特定の第2の要求パケットに対する第2の応答パケットの送信タイミングを、上記の特定の第2の要求パケットの次に受信される特定の第1の要求パケットに対する第1の応答パケットの送信タイミングに近づけ得る。第1の装置と第2の装置との両者は、応答パケットを受信してから所定の期間が経過すると、次の要求パケットを送信する。このため、上記の特定の第2の要求パケットの次に受信される第2の要求パケットの受信タイミングを、上記の特定の第1の要求パケットの次に受信される第1の要求パケットの受信タイミングに近づけ得る。

【0008】

なお、上記の通信装置を実現するための制御方法、コンピュータプログラム、及び、当該コンピュータプログラムが記憶された記憶媒体も、新規で有用である。また、上記の通信装置と上記の第1及び第2の装置とを含むシステムも新規で有用である。

【図面の簡単な説明】

【0009】

【図1】ネットワークシステムの構成を示す。

【図2】応答処理のフローチャートを示す。

【図3】各装置の動作を表わすシーケンス図を示す。

【発明を実施するための形態】

【0010】

図1に示すように、ネットワークシステム2は、PC100,200と、多機能機(即ちPC100,200の周辺機器)10と、を備える。各装置10,100,200は、LAN4を介して、相互に通信可能である。

【0011】

(多機能機10の構成)

図1に示すように、多機能機10は、ASIC(Application Specific Integrated Circuit)12、フラッシュメモリ70、SDRAM80、ネットワークインターフェイス90、表示パネル92、及び、画像形成部94を備える。

【0012】

ASIC12は、メインCPU20、メイン用クロック回路30、サブCPU40、サブ用クロック回路50、SRAM60、SDRAM制御回路64、及び、MACコントローラ66を備える。

【0013】

メインCPU20は、SDRAM80に記憶されているプログラム82に従って様々な処理を実行する。これにより、受信制御部22と送信制御部24と決定部26との各機能が実現される。メイン用クロック回路30は、メインCPU20にクロック信号を供給する。メイン用クロック回路30からメインCPU20にクロック信号が供給されている間は、メインCPU20は非スリープ状態である。メインCPU20にクロック信号が供給されていない間は、メインCPU20はスリープ状態である。メインCPU20のスリープ状態は、メインCPU20の非スリープ状態と比較して、消費電力が低い状態である。メイン用クロック回路30は、サブCPU40によって制御される。即ち、サブCPU40によって、メインCPU20へのクロック信号の供給及び停止が制御される。

【0014】

サブCPU40は、SRAM60に記憶されているプログラム62に従って様々な処理を実行する。これにより、受信制御部42と移行制御部48との各機能が実現される。サブ用クロック回路50は、サブCPU40にクロック信号を供給する。サブ用クロック回路50のクロック信号の周波数は、メイン用クロック回路30のクロック信号の周波数よりも低い。従って、メインCPU20を駆動するための消費電力と比べて、サブCPU40を駆動するための消費電力は低い。なお、メインCPU20の処理速度は、サブCPU40の処理速度よりも速い。サブ用クロック回路50は、多機能機10の電源がONにされるとサブCPU40にクロック信号を供給し、多機能機10の電源がOFFにされるとクロック信号を停止する。即ち、サブCPU40は、多機能機10の電源がONされている間、クロック信号が供給されている状態(非スリープ状態)で維持される。変形例では、サブCPU40は、メインCPU20が非スリープ状態である間、スリープ状態であってもよい。即ち、サブ用クロック回路50は、メインCPU20が非スリープ状態である間、サブCPU40へのクロック信号を停止してもよい。

【0015】

SRAM60は、各CPU20,40からアクセス可能である。多機能機10の電源がONされると、メインCPU20は、フラッシュメモリ70内の圧縮されたプログラム72を展開して、展開済みのプログラム62をSRAM60に記憶する。

【0016】

SDRAM制御回路64は、サブCPU40からの指示に従って、SDRAM80に対するクロック信号の供給の開始又は停止をして、消費電力が比較的に高い通常動作モードと、消費電力が比較的に低いセルフリフレッシュモードと、の間でSDRAM80の状態を移行させる。

【0017】

MACコントローラ66は、ネットワークインターフェイス90に接続されている。MACコントローラ66は、LAN4を介して、ネットワークインターフェイス90でパケットが受信されると、メインCPU20又はサブCPU40の割込コントローラ(図示省略)にパケット割込要求信号を供給する。

【0018】

フラッシュメモリ70は、ASIC12の外部に設けられている。フラッシュメモリ70は、各CPU20,40からアクセス可能である。フラッシュメモリ70は、各CPU20,40によって実行されるプログラム62,82が圧縮された状態のプログラム72を記憶している。

【0019】

SDRAM80は、メインCPU20からアクセス可能である。SDRAM80は、SRAM60よりもメモリの総容量が大きく、各CPU20,40がアクセス(読み出し、書き込み)可能な速度が高速である。このため、SDRAM80の消費電力は、SRAM60の消費電力と比べて高い。SDRAM80は、SDRAM制御回路64によって制御され、通常動作モードとセルフリフレッシュモードとの間で状態が移行する。また、SDRAM80は、パケット情報84を記憶することができる。パケット情報84とは、ステータス要求パケットの受信時刻と、当該ステータス要求パケットの送信元のデバイス(例えばPC100)のMACアドレスと、が対応付けられた情報である(図3参照)。

【0020】

表示パネル92は、メインCPU20からの指示に従って、情報を表示する。表示パネル92には、ユーザからの操作を受け付けるためのタッチボタンが配置される。画像形成部94は、インクジェット方式又はレーザ方式の画像形成機構を備え、メインCPU20からの指示に従って、外部のデバイス(例えばPC100,200)から受信される印刷データによって表わされる画像を、印刷用紙に印刷する。

【0021】

(多機能機10の状態移行)

多機能機10の状態は、レディ状態とスリープ状態との間で移行する。多機能機10の電源がONされると、多機能機10は、レディ状態となる。

【0022】

(レディ状態)

多機能機10がレディ状態である場合、2個のCPU20,40は非スリープ状態(2個のクロック回路30,50からそれぞれクロック信号が供給されている状態)であり、2個のRAM60,80は通常動作モードである。この状態では、メインCPU20は、通常の処理を実行することができる。上記の通常の処理は、印刷指示パケットに従った印刷処理、ユーザの表示パネル92への操作に従った表示処理等を含む。なお、メインCPU20は、多機能機10がレディ状態である場合、SDRAM80に、レディ状態を示す状態変数を記憶させる。

【0023】

(スリープ状態)

多機能機10は、サブCPU40が後述する図2のS16等の処理を実行することによって、レディ状態からスリープ状態に移行する。多機能機10がスリープ状態である場合、メインCPU20はスリープ状態であり(メイン用クロック回路30からのクロック信号が停止されている状態)、サブCPU40は非スリープ状態であり(サブ用クロック回路50からのクロック信号が供給されている状態)、SRAM60は通常動作モードであり、SDRAM80はセルフリフレッシュモードである。多機能機10がスリープ状態であって、メインCPU20が上記の通常の処理(印刷処理、表示処理等)を実行すべき場合には、多機能機10は、レディ状態に移行する。

【0024】

なお、メインCPU20は、多機能機10がレディ状態からスリープ状態に移行される際に、SDRAM80内の状態変数を、SRAM60に移動させる。サブCPU40は、多機能機10がスリープ状態に移行されると、SRAM60内の状態変数を、スリープ状態を示す状態変数に変更する。さらに、サブCPU40は、多機能機10がスリープ状態からレディ状態に移行される際に、SRAM60内の状態変数を、SDRAM80に移動させる。メインCPU20は、多機能機10がレディ状態に移行されると、SDRAM80内の状態変数を、レディ状態を示す状態変数に変更する。

【0025】

(PC100の構成)

PC100には、多機能機10のステータスを監視するためのステータス監視プログラム(例えばステータスモニタ)がインストールされている。ユーザは、PC100を操作することによって、ステータス監視プログラムを起動させることができる。PC100は、ステータス監視プログラムが起動されると、多機能機10から多機能機10のステータス情報を取得する。

【0026】

具体的には、PC100は、ステータス監視プログラムが起動されると、ステータス要求パケットを、多機能機10に送信する。なお、ステータス要求パケットは、PC100のMACアドレスを含む。PC100は、ステータス要求パケットの応答として、多機能機10からステータス情報を含む応答パケットを受信する。PC100は、受信された応答パケットに従って、ステータス情報をPC100の表示部に表示させる。PC100は、応答パケットの受信から予め決められた待機期間(本実施例では30秒間)が経過する際に、ステータス要求パケットを、多機能機10に新たに送信する。即ち、PC100は、ステータス監視プログラムが起動されている間、ステータス要求パケットの送信処理と、応答パケットの受信処理と、を繰り返し実行する。

【0027】

なお、ステータス情報は、多機能機10の状態(スリープ状態又はレディ状態)、印刷用紙の有無、トナーの有無、及び、実行中の印刷のエラー情報(例えば用紙詰まり、画像形成部の故障等)を示す情報を含む。

【0028】

PC100は、およそ30秒間隔(上記の待機期間)で、多機能機10からステータス情報を繰り返し取得する。これにより、PC100のユーザは、多機能機10の最新のステータスを確認することができる。この構成によれば、例えば、PC100のユーザは、多機能機10の画像形成部94に印刷処理を実行させている場合に、印刷用紙が無くなったことを早期に知ることができる。また、PC100がステータス情報を多機能機10から定期的に取得するため、PC100のユーザは、多機能機10のステータス情報を、PC100に取得させるための操作を実行しなくて済む。

【0029】

PC100は、ステータス要求パケットを多機能機10に送信してから、2秒間(以下では「タイムアウト時間」と呼ぶ)経過しても、応答パケットが多機能機10から受信されない場合、応答パケットを受信できないと判断する。この場合、PC100は、再度、ステータス要求パケットを、多機能機10に送信する。PC100は、予め決められた個数のステータス要求パケットを送信しても、タイムアウト時間内に応答パケットが受信されない場合、通信エラーを示す情報を、PC100の表示部に表示させる。これにより、PC100のユーザは、多機能機10とPC100とが通信できないことを知ることができる。

【0030】

なお、PC100は、ステータス要求パケットを多機能機10に送信してからタイムアウト時間が経過した後に、応答パケットが多機能機10から受信されたとしても、応答パケットに従ったステータス情報を、PC100の表示部に表示させない。

【0031】

PC200は、PC100と同様の構成を備える。即ち、PC200は、ステータス監視プログラムが起動されると、ステータス要求パケットを、多機能機10に送信する送信処理と、多機能機10から応答パケットを受信する受信処理と、を繰り返し実行する。

【0032】

(メインCPU20及びサブCPU40が実行する処理)

次いで、図2を参照して、メインCPU20及びサブCPU40が実行する処理の内容について説明する。本処理は、多機能機10の電源がONされている間、繰り返し実行される。多機能機10の電源がONされたタイミングでは、多機能機10はレディ状態である。即ち、多機能機10の電源がONされたタイミングでは、メインCPU20が本処理を実行する。

【0033】

S12では、受信制御部22は、LAN4を介して、パケットが受信されたのか否かを判断する。ネットワークインターフェイス90でパケットが受信される場合、MACコントローラ66は、パケット割込要求信号を、メインCPU20に供給する。受信制御部22は、パケット割込要求信号を取得すると、受信されたパケットを、ネットワークインターフェイス90からSDRAM80に移動させる。S12では、受信制御部22は、SDRAM80に受信済みのパケットが存在するのか否かを判断する。

【0034】

パケットが受信されていない場合(S12でNO)、S14において、メインCPU20は、メインCPU20をスリープ状態に移行可能(即ち多機能機10をスリープ状態に移行可能)であるのか否かを判断する。例えば、メインCPU20は、以下の(1)〜(5)の条件を含む複数個の条件の全てでNOと判断される場合に、スリープ状態に移行可能(S14でYES)と判断し、複数個の条件のうち、少なくとも1個の条件でYESと判断される場合に、スリープ状態に移行不可能(S14でNO)と判断する。

【0035】

上記の複数個の条件は、(1)多機能機10がパケットを外部に送信中であるのか否か、(2)未処理パケットがSDRAM80に記憶されているのか否か、(3)多機能機10にTCP接続しているデバイス(例えばPC100)があるのか否か、(4)多機能機10が起動又はシャットダウンのための処理を実行しているのか否か、(5)ネットワークの負荷が高いのか否か、を含む。

【0036】

例えば、メインCPU20がPC100等からのパケットに対する応答を送信している場合には、上記の(1)でYESと判断される。例えば、多機能機10がWebサーバ機能を有しており、PC100が多機能機10のWebサーバにTCP接続中である場合には、上記の(3)でYESと判断される。例えば、S14の処理を実行する直前の所定の期間に受信されたパケット数が所定の個数を超えている場合には、多機能機10が処理すべきパケットを受信する可能性が高いために、上記の(5)でYESと判断される。従って、ここで示されるように、上記の(1)〜(5)の条件のうち、少なくとも1個の条件でYESと判断される場合に、スリープ状態に移行不可能(S14でNO)と判断する。

【0037】

一方、上記の(1)〜(5)の条件の全てでNOと判断される場合に、メインCPU20がスリープ状態に移行可能(S14でYES)と判断される。このS14でYESの場合、S16において、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる。具体的には、移行制御部48は、メイン用クロック回路30にクロック供給の停止を指示する。この結果、メインCPU20は、非スリープ状態からスリープ状態に移行する。なお、S16では、さらに、移行制御部48は、SDRAM80を通常動作モードからセルフリフレッシュモードに移行させる。これにより、多機能機10は、スリープ状態となる。なお、SDRAM80がセルフリフレッシュモードである間は、SDRAM80に情報を書き込んだり、SDRAM80から情報を読み込んだりすることができない。例えば、ネットワークインターフェイス90で受信されたパケットをSDRAM80に記憶させることができない。

【0038】

なお、メインCPU20は、S16でスリープ状態に移行する前に、多機能機10をレディ状態からスリープ状態に移行するために、以下の処理を実行する。即ち、メインCPU20は、代理応答情報を、SDRAM80からSRAM60に移動させる。代理応答情報は、メインCPU20がスリープ状態である間に受信されたパケットに従った処理を、サブCPU40が実行するための情報(例えば多機能機10のIPアドレス、MACアドレス、ノード名等)を含む。また、メインCPU20は、LAN4を介して受信されるパケットを記憶するためのRAMを、SDRAM80からSRAM60に切り替える。続いて、メインCPU20は、サブCPU40以外からの割込要求をマスク(禁止)する。次いで、メインCPU20は、サブCPU40に処理を開始させるための開始信号を、サブCPU40に供給する。サブCPU40は、開始信号が取得されると、S16の処理を実行する。なお、メインCPU20は、WAIT命令を実行する。WAIT命令が実行されると、メインCPU20は、サブCPU40から割込要求信号が供給されるまで待機する実行停止状態となる。

【0039】

S16が終了すると、S12に戻る。即ち、メインCPU20がスリープ状態である間に、S12が実行される。この場合、サブCPU40の受信制御部42がS12を実行する。S12でNOの場合、S14において、メインCPU20が既にスリープ状態であるために、NOと判断され、S12に戻る。

【0040】

以下のS18の処理では、S12において、サブCPU40の受信制御部42が、パケットが受信されたと判断する場合(メインCPU20がスリープ状態である間にパケットが受信される場合)について説明する。

【0041】

S18では、サブCPU40は、メインCPU20がスリープ状態であるのか否かを判断する。具体的には、サブCPU40は、SRAM60内の状態変数を確認して、多機能機10がスリープ状態であるのか否かを判断することによって、メインCPU20がスリープ状態であるのか否かを判断する。この場合では、S18にてYESと判断され、次いで、S20では、サブCPU40は、S12で受信されたパケットを解析することによって、サブCPU40自身がパケットに従った処理を実行することができるのか否かを判断する。

【0042】

例えば、サブCPU40は、SRAM60内の代理応答情報を用いて、S12で受信されたパケットに従った応答処理を実行可能であるのか否かを判断する。サブCPU40が代理して実行可能な応答処理は、例えば、PINGに対する応答、ARP(Address Resolution Protocol)のパケットに対する応答等を含む。なお、S12で受信されたパケットがPC100,200からのステータス要求パケットである場合、サブCPU40は、サブCPU40自身がパケットに従った処理を実行することができないと判断する。

【0043】

S20でYESの場合、S22において、サブCPU40は、S12で受信されたパケットに従った処理を実行して、S12に戻る。S20でNOの場合、S24において、移行制御部48は、メインCPU20をスリープ状態から非スリープ状態に移行する。具体的には、移行制御部48は、メイン用クロック回路30に、メインCPU20にクロック供給を開始するよう指示する。この結果、メインCPU20にクロックが供給され、メインCPU20がスリープ状態から非スリープ状態に移行する。移行制御部48は、メインCPU20に割込要求信号を供給する。

【0044】

サブCPU40は、さらに、SDRAM80をセルフリフレッシュモードから通常動作モードに移行させる処理、外部デバイスからの受信パケットの記憶先をSRAM60からSDRAM80に切り替える処理、SRAM60内の情報をSDRAM80に移動させる処理等を実行する。

【0045】

メインCPU20は、サブCPU40から割込要求信号が供給されると、WAIT命令を解除する。メインCPU20は、SRAM60に記憶されている未処理のパケットを、SDRAM80に移動させる。

【0046】

S26において、メインCPU20は、S12で受信されたパケットが、ステータス要求パケットであるのか否かを判断する。具体的には、メインCPU20は、S12で受信されたパケットが、SNMP(Simple Network Management Protocol)のオブジェクトデータを要求するパケットであるのか否かを判断する。例えば、メインCPU20は、パケットの宛先ポート番号がSNMPを示すポート番号(即ち「161」)であり、かつ、パケットのSNMPメッセージに含まれるPDU(Protocol Data Unit)タイプがGetRequest又はGetNextRequestを示す場合に、ステータス要求パケットであると判断する。

【0047】

ステータス要求パケットでないと判断される場合(S26でNO)、S28において、メインCPU20は、S12で受信されたパケットに応じた処理(例えば上記の通常の処理(印刷指示パケットに従った印刷処理等))を実行して、S12に戻る。

【0048】

一方、ステータス要求パケットであると判断される場合(S26でYES)、S30において、メインCPU20は、SDRAM80にパケット情報84が記憶されているのか否かを判断する。パケット情報84がSDRAM80に記憶されていない場合(S30でNO)にS34に進み、記憶されている場合(S30でYES)にS32に進む。

【0049】

S32では、メインCPU20は、S12で受信されたステータス要求パケットの送信元のデバイスが、パケット情報84として記憶されているデバイスと一致するのか否かを判断する。具体的には、メインCPU20は、ステータス要求パケットに含まれる送信元のデバイスのMACアドレスと、パケット情報84に含まれるMACアドレスと、が一致するのか否かを判断する。ここで、上述した2つのMACアドレスが一致する場合、S32でYESと判断されS34に進み、一方、上述した2つのMACアドレスが異なる場合、S32でNOと判断されS36に進む。

【0050】

S34では、メインCPU20は、SDRAM80に、パケット情報84を記憶させる。S30でNOと判断された場合(即ちパケット情報84が記憶されていない場合)に実行されるS34では、メインCPU20は、ステータス要求パケットの送信元デバイスのMACアドレスと、当該ステータス要求パケットの受信時刻と、を対応付けて、SDRAM80に記憶させる。一方、S32でYESと判断された場合(即ちSDRAM80に既にパケット情報84が記憶されている場合)に実行されるS34では、メインCPU20は、パケット情報84に含まれる前回のステータス要求パケットの受信時刻を、今回のステータス要求パケットの受信時刻に更新する。S34が終了すると、S46に進む。なお、メインCPU20は、SDRAM80に記憶されているパケット情報84に含まれるMACアドレスに対応するデバイス(例えばPC100)から予め決められた期間(例えば1分間)が経過しても、次のステータス要求が受信されない場合、SDRAM80に記憶されているパケット情報84を削除する。

【0051】

一方、上述したように、今回のS12で受信されたステータス要求パケットの送信元のデバイス(以下では「PC200」を例として説明する)が、パケット情報84として記憶されているデバイス(以下では「PC100」を例として説明する)と異なる場合(S32でNOの場合)に、S36の処理が実行される。S36では、決定部26は、SDRAM80に記憶されているパケット情報84を用いて、PC100から次回のステータス要求パケットを受信する時刻である次回パケット受信時刻を算出する。具体的には、決定部26は、パケット情報84に含まれる受信時刻に、SDRAM80に予め記憶されている待機期間(即ち30秒)を加算することによって、次回パケット受信時刻を算出する。なお、多機能機10のベンダは、待機期間(即ち30秒)を、予めSDRAM80に記憶させる。変形例では、メインCPU20は、PC100からステータス要求パケットが受信される間隔を用いて、待機期間を特定し、特定された待機期間をSDRAM80に記憶させてもよい。

【0052】

次いで、S38では、S12でPC200から受信されたステータス要求パケットの受信時刻が、S36で算出されたPC100の次回パケット受信時刻とほぼ等しいのか否かを判断する。ここで「受信時刻がほぼ等しい」とは、例えば、ステータス要求パケットの受信時刻と次回パケット受信時刻との差分が、上記のタイムアウト時間よりも短い(例えば上記のタイムアウト時間の10分の1(即ち0.2秒))状態を意味する。

【0053】

なお、PC100は、前回のステータス要求パケットに対する応答パケットを受信してから待機期間が経過する際に、次回のステータス要求パケットを送信する。従って、厳密には、決定部26は、PC100が前回のステータス要求パケットに対する応答パケットを受信した時刻に、待機期間を加算することによって、次回パケット受信時刻を算出しなければならない。しかしながら、多機能機10がPC100からステータス要求パケットを受信してから、PCが多機能機10からステータス要求パケットに対する応答パケットを受信するまでの期間は、非常に短い。そのため、実質的に、ステータス要求パケットを多機能機10が受信する時刻と、当該ステータス要求パケットに対する応答パケットをPC100が受信する時刻とは、ほぼ等しい。

【0054】

ここで、上述した2つのパケット受信時刻がほぼ等しい場合、S38でYESと判断されS46に進み、一方、上述した2つのパケット受信時刻が略等しくない場合、S38でNOと判断され、S40に進む。S40では、決定部26は、S36で算出された次回パケット受信時刻と、S12におけるステータス要求パケットの受信時刻と、の差分(即ちX秒)が、上記のタイムアウト時間(即ち2秒間)よりも大きいのか否かを判断する。上記の差分(即ちX秒)がタイムアウト時間よりも大きい場合(S40でYES)、S42において、決定部26は、S12で受信されたステータス要求パケットの応答パケットを送信する送信タイミングを、S12で受信されたPC200のステータス要求パケットの受信時刻にタイムアウト時間(即ち2秒間)を加算した時刻に決定する。S42が終了すると、S46に進む。この構成によれば、ステータス要求パケットの送信元のデバイス(即ちPC200)が、ステータス要求パケットの応答を受信できないと判断することを回避することができる。

【0055】

なお、PC200は、ステータス要求パケットを送信してからタイムアウト時間が経過しても、応答パケットが多機能機10から受信されない場合に、応答を受信できないと判断する。従って、厳密には、決定部26は、S40及びS42において、以下の処理を実行すべきである。即ち、S40の処理では、決定部26は、上記の差分(即ちX秒)が、タイムアウト時間から多機能機10とPC200との間の往復の通信時間を減算した特定の時間よりも大きいのか否かを判断すべきである。そして、S42の処理では、決定部26は、S12で受信されたPC200のステータス要求パケットに対する応答パケットを送信する送信タイミングを、当該ステータス要求パケットの受信時刻に上記の特定の時間を加算した時刻に決定すべきである。しかしながら、多機能機10とPC200との間の往復の通信時間は、タイムアウト時間と比較して、無視できるほど短い。このため、S40及びS42の処理のように、タイムアウト時間を用いて決定された送信タイミングで応答パケットが送信されても、PC200がステータス要求パケットの応答を受信できないと判断するという事態は発生しない。

【0056】

一方、S40でNOの場合、即ち、X秒がタイムアウト時間よりも小さい場合、S44において、決定部26は、応答パケットの送信タイミングを、S12で受信されたPC200のステータス要求パケットの受信時刻にX秒を加算した時刻に決定する。S44が終了すると、S46に進む。S34、S42、又はS44の処理が終了した後、又はS38でYESと判断された後、S46では、送信制御部24は、S12のステータス要求パケットの応答として、多機能機10の現在のステータス情報を含む応答パケットを、S12のステータス要求パケットの送信元のデバイスに送信して、S12に戻る。S34の処理が実行され又はS38でYESと判断された後に実行されるS46では、送信制御部24は、ステータス要求パケットに対応する応答パケットを生成すると直ちに(待機せずに)、応答パケットを送信する。この場合、ステータス要求パケットが受信されてから、応答パケットが送信されるまでの時間は、非常に短い。一方、S42又はS44の処理が実行された後に実行されるS34では、送信制御部24は、ステータス要求パケットに対応する応答パケットを生成した後に、S42又はS44で決定されたタイミングまで待機し、決定されたタイミングが到来すると、応答パケットを送信する。

【0057】

なお、メインCPU20の受信制御部22が、S12において、パケットを受信したと判断した場合(多機能機10がレディ状態である間にパケットが受信された場合)には、メインCPU20は、S18でNOと判断し、S26以降の処理を実行する。S26以降の処理は、上記と同様である。

【0058】

(本実施例の効果)

図3を参照して、各装置10,100,200の動作と、本実施例の効果と、を説明する。なお、図3では、メインCPU20がスリープ状態である状況で開始される。

【0059】

12:00:00では、PC100は、M(Mは1以上の整数)番目のステータス要求パケットを、多機能機10に送信する。M番目のステータス要求パケットが受信されると、移行制御部48は、メインCPU20を非スリープ状態に移行させる(図2のS24)。メインCPU20は、PC100のMACアドレス(即ち「PC100」)と対応付けて、受信時刻(即ち「12:00:00」)を、記憶させる(即ちパケット情報84)(図2のS34)。送信制御部24は、M番目のステータス要求パケットの応答として、M番目の応答パケットを生成する。送信制御部24は、M番目の応答パケットが生成されると、直ちに、PC100に送信する(図2のS46)。

【0060】

M番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0061】

次いで、12:00:25では、PC200は、N(Nは1以上の整数)番目のステータス要求パケットを、多機能機10に送信する。N番目のステータス要求パケットが受信されると、移行制御部48は、メインCPU20を非スリープ状態に移行させる(図2のS24)。

【0062】

決定部26は、パケット情報84の受信時刻「12:00:00」に、待機期間(即ち30秒間)を加算して、次回パケット受信時刻(PC100からM+1番目のステータス要求パケットの受信時刻)(即ち「12:00:30」)を算出する(図2のS36)。算出された次回パケット受信時刻と、N番目のステータス要求パケットの受信時刻(即ち「12:00:25」)と、の差分(即ち5秒間)が、タイムアウト時間(即ち2秒間)よりも長い(図2のS40でYES)。このため、決定部26は、N番目のステータス要求パケットの応答として、N番目の応答パケットを送信する送信タイミングを、N番目のステータス要求パケットの受信時刻「12:00:25」にタイムアウト時間を加算した「12:00:27」に決定する(図2のS42)。送信制御部24は、N番目の応答パケットを、12:00:27に送信する(図2のS46)。上記の構成によれば、多機能機10は、N番目の応答パケットの送信タイミングを、M+1番目のステータス要求パケットに対するM+1番目の応答パケットの送信タイミングに近づけることができる。この結果、N+1番目の要求パケットの受信タイミングを、M+2番目の要求パケットの受信タイミングに近づけることができる。

【0063】

N番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0064】

次いで、12:00:30では、PC100は、M+1番目のステータス要求パケットを、多機能機10に送信する。なお、厳密には、PC100は、M番目の応答パケットを受信してから30秒後に、M+1番目のステータス要求パケットを送信する。しかしながら、PC100は、M番目のステータス要求パケットを送信してから、M番目の応答パケットを受信するまでの期間が非常に短いため、実質的に、M番目のステータス要求パケットの送信からM+1番目のステータス要求パケットの送信までの期間が、30秒間であると言うことができる。

【0065】

移行制御部48は、M+1番目のステータス要求パケットが受信されると、メインCPU20を非スリープ状態に移行する(図2のS24)。メインCPU20は、パケット情報84を記憶(図2のS34)する。送信制御部24は、M+1番目のステータス要求パケットの応答として、M+1番目の応答パケットを生成し、生成されたM+1番目の応答パケットを、直ちに送信する(図2のS46)。M+1番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0066】

12:00:57では、PC200は、N+1番目のステータス要求パケットを、多機能機10に送信する。移行制御部48は、N+1番目のステータス要求パケットが受信されると、メインCPU20を非スリープ状態に移行する(図2のS24)。

【0067】

決定部26は、パケット情報84の受信時刻「12:00:30」に、待機期間(30秒)を加算して、次回パケット受信時刻(PC100からM+1番目のステータス要求パケットの受信時刻)(即ち「12:01:00」)を算出する(図2のS36)。算出された次回パケット受信時刻と、N+1番目のステータス要求パケットの受信時刻(即ち「12:00:57」)と、の差分(即ち3秒間)が、タイムアウト時間(即ち2秒間)よりも長い(図2のS40でYES)。このため、決定部26は、N+1番目のステータス要求パケットの応答として、N+1番目の応答パケットを送信する送信タイミングを、N+1番目のステータス要求パケットの受信時刻「12:00:57」にタイムアウト時間を加算した「12:00:59」に決定する(図2のS42)。送信制御部24は、N+1番目の応答パケットを、12:00:59に送信する(図2のS46)。上記の構成では、多機能機10は、N+1番目の応答パケットの送信タイミングを、M+2番目の要求パケットに対するM+2番目の応答パケットの送信タイミングに近づけることができる。この結果、N+2番目の要求パケットの受信タイミングを、M+3番目の要求パケットの受信タイミングに近づけることができる。

【0068】

N+1番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0069】

時刻12:01:00において、PC100は、M+2番目のステータス要求パケットを、多機能機10に送信する。M+2番目のステータス要求パケットが受信されると、移行制御部48は、メインCPU20を非スリープ状態に移行する(図2のS24)。メインCPU20は、パケット情報84を記憶(図2のS34)する。送信制御部24は、M+2番目のステータス要求パケットの応答として、M+2番目の応答パケットを生成し、生成されたM+2番目の応答パケットを、直ちに送信する(図2のS46)。M+2番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0070】

時刻12:01:29において、PC200は、N+2番目のステータス要求パケットを、多機能機10に送信する。N+2番目のステータス要求パケットが受信されると、移行制御部48は、メインCPU20を非スリープ状態に移行する(図2のS24)。

【0071】

決定部26は、パケット情報84の受信時刻「12:00:30」に、待機期間(30秒)を加算して、次回パケット受信時刻(PC100からM+3番目のステータス要求パケットの受信時刻)(即ち「12:01:30」)を算出する(図2のS36)。算出された次回パケット受信時刻と、N+2番目のステータス要求パケットの受信時刻(即ち「12:01:29」)と、の差分が、タイムアウト時間(即ち2秒間)よりも短い(図2のS40でNO)。このため、決定部26は、N+2番目のステータス要求パケットの応答として、N+2番目の応答パケットを送信する送信タイミングを、N+2番目のステータス要求パケットの受信時刻「12:01:29」に、差分である1秒間を加算した「12:01:30」に決定する(図2のS44)。この構成では、PC200への応答パケットの送信タイミングを、PC100からのステータス要求パケットの受信タイミングを用いて決定している。この結果、PC200からのステータス要求パケットの受信タイミングを、PC100からのステータス要求パケットの受信タイミングに、適切に近づけることができる。

【0072】

PC100は、12:01:30に、M+3番目のステータス要求パケットを、多機能機10に送信する。このタイミングは、N+2番目の応答パケットを送信する送信タイミングに等しいため、メインCPU20は、非スリープ状態に維持されている。送信制御部24は、M+3番目のステータス要求パケットの応答として、生成されたM+3番目の応答パケットを、直ちに、PC100に送信する(図2のS46)。さらに、送信制御部24は、N+2番目の応答パケットの送信タイミング「12:01:30」が到来したため、N+2番目の応答パケットを、PC200に送信する(図2のS46)。この結果、M+3番目の応答パケットの送信タイミングと、N+2番目の応答パケットの送信タイミングと、をほぼ等しくさせることができる。なお、実際には、送信制御部24は、応答パケットを順番に送信するために、送信タイミングが厳密的な意味で一致しない。

【0073】

M+2番目の応答パケットが送信されると、移行制御部48は、メインCPU20を、非スリープ状態からスリープ状態に移行させる(図2のS16)。

【0074】

12:02:00になると、受信制御部42は、PC100及びPC200のそれぞれから、M+4番目のステータス要求パケットと、N+3番目のステータス要求パケットと、を受信する。この構成によれば、多機能機10は、PC100からのステータス要求パケットとPC200からのステータス要求パケットとを、ほぼ等しいタイミングで受信することができる。

【0075】

なお、「ほぼ等しいタイミングで受信する」とは、例えば、例えば、ステータス要求パケットの受信時刻とS36で算出された次回パケット受信時刻との差分が、上記のタイムアウト時間よりも短い(例えば上記のタイムアウト時間の10分の1(即ち0.2秒))状態を意味する。あるいは、「ほぼ等しいタイミングで受信する」とは、図2のS12で受信されたステータス要求パケットについて、図2のS46の処理が実行された後、図2のS12に戻るまでの期間よりも短い状態を意味する。

【0076】

また、多機能機10は、PC200からのステータス要求パケットの受信タイミングを、PC100からのステータス要求パケットの受信タイミングに、近づけることによって、メインCPU200がスリープ状態から非スリープ状態に移行される頻度を低くすることができる。この結果、多機能機10の省電力を低減することができる。特に、図2のS12においてPC100から受信されたステータス要求パケットについての応答パケットの送信(図2のS46)後、図2のS12に戻るまでの間に、PC200からのステータス要求パケットが受信されている場合、S12でYESと判断され、メインCPU20がスリープ状態に移行されることを回避することができる。

【0077】

本実施例では、多機能機10は、PC200からのステータス要求パケットの受信から応答パケットの送信までの時間が、PC100からの要求パケットの受信から応答パケットの送信までの時間よりも長くなるようなタイミングで、PC200からの応答パケットを送信する。この構成によれば、PC200からのステータス要求パケットに対する応答パケットの送信タイミングを、PC200からのステータス要求パケットの次に受信されるPC100からのステータスの要求パケットに対する応答パケットの送信タイミングに近づけることができる。この結果、PC200からのステータス要求パケットの受信タイミングを、PC100からのステータス要求パケットの受信タイミングに近づける。

【0078】

(対応関係)

上記の多機能機10、PC100及びPC200のそれぞれが、「通信装置」、「第1の装置」及び「第2の装置」の一例である。PC100から送信されるステータス要求パケットが「第1の要求パケット」の一例であり、PC200から送信されるステータス要求パケットが「第2の要求パケット」の一例である。メインCPU20とサブCPU40とが「プロセッサ」の一例である。2個のPCU20,40が共に非スリープ状態である状態が「高消費状態」の一例であり、メインPCU20がスリープ状態であり、サブCPU40が非スリープ状態である状態が「低消費状態」の一例である。

【0079】

以上、本発明の実施形態について詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

【0080】

(変形例)

(1)上記の実施例では、多機能機10は、2個のCPU20,40を備えるが、これに代えて、多機能機10は、メインCPU20のみを備えていてもよい。この場合、メインCPU20に供給されるクロック信号の周波数が低い状態と高い状態とに移行してもよい。クロック信号の周波数が高い状態では、メインCPU20の消費電力が比較的に高く、クロック信号の周波数が低い状態では、メインCPU20の消費電力が比較的に低い。この変形例では、メインCPU20が「プロセッサ」の一例であり、メインCPU20に供給されるクロック信号の周波数が高い状態が「高消費状態」の一例であり、メインCPU20に供給されるクロック信号の周波数が低い状態が「低消費状態」の一例である。

【0081】

(2)上記の実施例では、決定部26は、SDRAM80に記憶されているパケット情報84を用いて、応答パケットの送信タイミングを決定している(図2のS36からS44)。しかしながら、決定部26は、PC100からのステータス要求パケットの受信タイミングと、PC200からのステータス要求パケットの受信タイミングと、が予め決められた間隔(例えば1秒間)以下となるまで、PC200からのステータス要求パケットに対する応答パケットの送信タイミングを、ステータス要求パケットの受信タイミングから予め決められた時間(例えば1秒間)だけ加算したタイミングに決定してもよい。本変形例も、「決定部は、第2の要求パケットの受信から当該第2の要求パケットに対する第2の応答パケットの送信までの時間が、第1の要求パケットの受信から当該第1の要求パケットに対する第1の応答パケットの送信までの時間よりも長くなるように、送信タイミングを決定する」という構成に含まれる。

【0082】

(3)上記の実施例では、メインCPU20がプログラム82に従って処理を実行することによって、決定部26の機能が実現されている。しかしながら、サブCPU40がプログラム62に従って処理を実行することによって、決定部の機能が実行されてもよい。この場合、図2のS26、S30からS44までの処理を、サブCPU40が実行してもよい。

【0083】

(4)上記の実施例では、メインCPU20が非スリープ状態である間にステータス要求パケットが受信される場合と、メインCPU20がスリープ状態である間にステータス要求パケットが受信される場合と、の両方の場合において、決定部26は、送信タイミングを決定している(図2のS42及びS44)。しかしながら、メインCPU20が非スリープ状態である間にステータス要求パケットが受信される場合には、決定部26は、送信タイミングを決定せず、直ちに、応答パケットを送信してもよい。この構成によれば、メインCPU20が非スリープ状態である間にステータス要求パケットが受信される場合には、応答パケットの送信タイミングの決定処理を実行しなくて済む。

【0084】

(5)上記の実施例では、決定部26は、パケット情報84に記憶されているデバイス(例えばPC100)への応答パケットの送信タイミングを決定しない。しかしながら、決定部26は、パケット情報84に記憶されているデバイス(例えばPC100)への応答パケットの送信タイミングを決定してもよい。即ち、決定部26は、受信される全てのステータス要求パケットへの応答パケットの送信タイミングを決定してもよい。

【0085】

(6)多機能機10に接続されるPCの個数に限りはない。多機能機10は、多数個のPCからのステータス要求パケットの受信タイミングが、パケット情報84に記憶されているPC100のステータス要求パケットの受信タイミングに近づくように、多数個のPCへの応答パケットの送信タイミングを決定してもよい。さらに、多数個のPCが多機能機10に接続される場合、多機能機10は、1個以上のPCのステータス要求パケットの受信時刻を、パケット情報84に記憶してもよい。そして、多機能機10は、パケット情報84に記憶されているPC以外の多数個のPCのステータス要求パケットのそれぞれの受信タイミングが、パケット情報84に含まれる1個以上PCのいずれかのPCに対応する受信タイミングに近づくように、応答パケットの送信タイミングを決定してもよい。例えば、多機能機10に10個のPCが接続されている場合、多機能機10は、5個のPCを第1グループとして、他の5個のグループを第2グループとして分類してもよい。多機能機10は、第1グループの中の1個の基準PCの受信タイミングに、第1グループの中の他の4個のPCの受信タイミングを近づけてもよい。同様に、多機能機10は、第2グループの中の1個の基準PCの受信タイミングに、第2グループの中の他の4個のPCの受信タイミングを近づけてもよい。この場合、第1グループの中の上記の基準PCの受信タイミングと、第2グループの中の上記の基準PCの受信タイミングと、は一致しなくてもよい。

【0086】

(7)上記の実施例では、決定部26は、PC100からのステータス要求パケットの受信時刻と待機期間とを用いて、PC200への応答パケットの送信タイミングを決定する(図2のS40)。しかしながら、決定部26は、多機能機10がPC100からのステータス要求パケットに対する応答パケットの送信タイミング、あるいは、PC100がステータス要求パケットに対する応答パケットの受信タイミングを用いて、PC200への応答パケットの送信タイミングを決定してもよい。本変形例では、多機能機10がPC100からのステータス要求パケットに対する応答パケットの送信タイミング、あるいは、PC100がステータス要求パケットに対する応答パケットの受信イミングが、「第1の要求パケットの受信に関するタイミング」の一例である。

【0087】

(8)上記の実施例では、メインCPU20がプログラム82に従って処理を実行することによって、各部22〜26が実現されるが、各部22〜26の少なくとも1個は、論理回路等のハードウェアで実現されてもよい。また、サブCPU40がプログラム62に従って処理を実行することによって、各部42、48が実現されるが、各部42、48の少なくとも1個は、論理回路等のハードウェアで実現されてもよい。

【0088】

(8)「通信装置」は、多機能機でなくてもよく、PC、プリンタ、サーバ、PDA等の通信装置であってもよい。

【0089】

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0090】

2:ネットワークシステム、10:多機能機、20:メインCPU、22:受信制御部、24:送信制御部、26:決定部、40:サブCPU、42:受信制御部、48:移行制御部、60:SRAM、70:フラッシュメモリ、80:SDRAM、100,200:PC

【特許請求の範囲】

【請求項1】

第1の要求パケットを通信装置に送信して、前記第1の要求パケットに対する第1の応答パケットを、前記通信装置から受信する処理を繰り返し実行し、前記第1の応答パケットを受信してから所定の期間が経過する際に、前記第1の要求パケットを新たに送信する第1の装置と、

第2の要求パケットを前記通信装置に送信して、前記第2の要求パケットに対する第2の応答パケットを、前記通信装置から受信する処理を繰り返し実行し、前記第2の応答パケットを受信してから前記所定の期間が経過する際に、前記第2の要求パケットを新たに送信する第2の装置と、

のそれぞれに接続される前記通信装置であって、

前記第1の装置から前記第1の要求パケットを受信し、前記第2の装置から前記第2の要求パケットを受信する受信制御部と、

前記第1の要求パケットに対する前記第1の応答パケットを前記第1の装置に送信し、前記第2の要求パケットに対する前記第2の応答パケットを前記第2の装置に送信する送信制御部と、

前記第2の応答パケットを前記第2の装置に送信するための送信タイミングを決定する決定部であって、前記第2の要求パケットの受信から当該第2の要求パケットに対する前記第2の応答パケットの送信までの期間が、前記第1の要求パケットの受信から当該第1の要求パケットに対する前記第1の応答パケットの送信までの期間よりも長くなるように、前記送信タイミングを決定する前記決定部と、

を備え、

前記送信制御部は、決定済みの前記送信タイミングで、前記第2の応答パケットを前記第2の装置に送信する、通信装置。

【請求項2】

前記受信制御部は、前記第1の装置からM番目(前記Mは1以上の整数)の前記第1の要求パケットを受信し、前記第1の装置から前記M番目の前記第1の要求パケットが受信された後であって、前記第1の装置からM+1番目の前記第1の要求パケットが受信される前に、前記第2の装置からN番目(前記Nは1以上の整数)の前記第2の要求パケットを受信し、

前記送信制御部は、前記M番目の第1の要求パケットに対するM番目の前記第1の応答パケットを前記第1の装置に送信し、前記N番目の第2の要求パケットに対するN番目の前記第2の応答パケットを前記第2の装置に送信し、

前記決定部は、前記N番目の第2の要求パケットの受信から前記N番目の第2の応答パケットの送信までの期間が、前記M番目の第1の要求パケットの受信から前記M番目の第1の応答パケットの送信までの期間よりも長くなるように、前記N番目の第2の応答パケットの送信タイミングを決定し、

前記送信制御部は、決定済みの前記送信タイミングで、前記N番目の第2の応答パケットを前記第2の装置に送信する、請求項1に記載の通信装置。

【請求項3】

前記決定部は、前記第1の要求パケットの受信に関するタイミングを用いて、前記第2の応答パケットの前記送信タイミングを決定する、請求項1又は2に記載の通信装置。

【請求項4】

前記決定部は、前記第1の要求パケットが受信されるタイミングと、前記第2の要求パケットが受信されるタイミングと、がほぼ等しくなるまで、前記第2の要求パケットが受信される毎に、前記第2の応答パケットの前記送信タイミングを決定し、

前記送信制御部は、前記第2の要求パケットが受信される毎に、当該第2の要求パケットについて決定される前記送信タイミングで、当該第2の要求パケットに対する前記第2の応答パケットを送信する、請求項1から3のいずれか一項に記載の通信装置。

【請求項5】

前記第2の装置は、

前記第2の要求パケットを前記通信装置に送信してから特定の期間が経過する前に、当該第2の要求パケットに対する前記第2の応答パケットが受信される場合には、前記第2の応答パケットに従った処理を実行し、

前記第2の要求パケットを前記通信装置に送信してから前記特定の期間が経過した後に、当該第2の要求パケットに対する前記第2の応答パケットが受信されても、前記第2の応答パケットに従った処理を実行せず、

前記決定部は、前記第2の要求パケットの受信から当該第2の要求パケットに対する前記第2の応答パケットの送信までの前記期間が、前記特定の期間以下になるように、前記送信タイミングを決定する、請求項1から4のいずれか一項に記載の通信装置。

【請求項6】

前記受信制御部は、前記第1の装置からM番目(前記Mは1以上の整数)の前記第1の要求パケットを受信し、前記第1の装置から前記M番目の前記第1の要求パケットが受信された後であって、前記第1の装置からM+1番目の前記第1の要求パケットが受信される前に、前記第2の装置からN番目(前記Nは1以上の整数)の前記第2の要求パケットを受信し、

前記送信制御部は、前記M番目の第1の要求パケットに対するM番目の前記第1の応答パケットを前記第1の装置に送信し、前記N番目の第2の要求パケットに対するN番目の前記第2の応答パケットを前記第2の装置に送信し、

前記決定部は、

前記M+1番目の第1の要求パケットの受信タイミングと、前記N番目の第2の要求パケットの受信タイミングと、の間の特定の差分が、前記特定の期間よりも長い場合に、前記N番目の第2の要求パケットの受信から、前記N番目の第2の応答パケットの送信までの期間が、前記特定の期間に一致するように、前記N番目の第2の応答パケットの前記送信タイミングを決定し、

前記特定の差分が、前記特定の期間よりも短い場合に、前記N番目の第2の要求パケットの受信から、前記N番目の第2の応答パケットの送信までの期間が、前記特定の差分に一致するように、前記N番目の第2の応答パケットの前記送信タイミングを決定する、請求項5に記載の通信装置。

【請求項7】

消費電力が比較的に高い高消費状態と、消費電力が比較的に低い低消費状態と、の間で移行可能であるプロセッサを備え、

前記プロセッサは、前記受信制御部と、前記送信制御部と、前記決定部と、移行制御部と、を備え、

前記移行制御部は、前記プロセッサを前記高消費状態と前記低消費状態との間で移行させ、

前記プロセッサが前記低消費状態である間に、前記第1の要求パケットが受信される場合に、

前記移行制御部は、前記プロセッサを前記低消費状態から前記高消費状態に移行させ、

前記送信制御部は、前記プロセッサが前記高消費状態である間に、前記第1の要求パケットに対する前記第1の応答パケットを送信し、

前記プロセッサが前記低消費状態である間に、前記第2の要求パケットが受信される場合に、

前記移行制御部は、前記プロセッサを前記低消費状態から前記高消費状態に移行させ、

前記送信制御部は、前記プロセッサが前記高消費状態である間に、前記第2の要求パケットに対する前記第2の応答パケットを送信する、請求項1から6のいずれか一項に記載の通信装置。

【請求項8】

第1の要求パケットを通信装置に送信して、前記第1の要求パケットに対する第1の応答パケットを、前記通信装置から受信する処理を繰り返し実行し、前記第1の応答パケットを受信してから所定の期間が経過する際に、前記第1の要求パケットを新たに送信する第1の装置と、

第2の要求パケットを前記通信装置に送信して、前記第2の要求パケットに対する第2の応答パケットを、前記通信装置から受信する処理を繰り返し実行し、前記第2の応答パケットを受信してから前記所定の期間が経過する際に、前記第2の要求パケットを新たに送信する第2の装置と、

のそれぞれに接続される前記通信装置のためのコンピュータプログラムであって、

前記通信装置に搭載されるコンピュータに、

前記第1の装置から前記第1の要求パケットを受信し、前記第2の装置から前記第2の要求パケットを受信する受信制御処理と、

前記第1の要求パケットに対する前記第1の応答パケットを前記第1の装置に送信し、前記第2の要求パケットに対する前記第2の応答パケットを前記第2の装置に送信する送信制御処理と、

前記第2の応答パケットを前記第2の装置に送信するための送信タイミングを決定する決定処理であって、前記第2の要求パケットの受信から当該第2の要求パケットに対する前記第2の応答パケットの送信までの時間が、前記第1の要求パケットの受信から当該第1の要求パケットに対する前記第1の応答パケットの送信までの時間よりも長くなるように、前記送信タイミングを決定する前記決定処理と、

を実行させ、

前記送信制御処理では、決定済みの前記送信タイミングで、前記第2の応答パケットを前記第2の装置に送信する、コンピュータプログラム。

【請求項1】

第1の要求パケットを通信装置に送信して、前記第1の要求パケットに対する第1の応答パケットを、前記通信装置から受信する処理を繰り返し実行し、前記第1の応答パケットを受信してから所定の期間が経過する際に、前記第1の要求パケットを新たに送信する第1の装置と、

第2の要求パケットを前記通信装置に送信して、前記第2の要求パケットに対する第2の応答パケットを、前記通信装置から受信する処理を繰り返し実行し、前記第2の応答パケットを受信してから前記所定の期間が経過する際に、前記第2の要求パケットを新たに送信する第2の装置と、

のそれぞれに接続される前記通信装置であって、

前記第1の装置から前記第1の要求パケットを受信し、前記第2の装置から前記第2の要求パケットを受信する受信制御部と、

前記第1の要求パケットに対する前記第1の応答パケットを前記第1の装置に送信し、前記第2の要求パケットに対する前記第2の応答パケットを前記第2の装置に送信する送信制御部と、

前記第2の応答パケットを前記第2の装置に送信するための送信タイミングを決定する決定部であって、前記第2の要求パケットの受信から当該第2の要求パケットに対する前記第2の応答パケットの送信までの期間が、前記第1の要求パケットの受信から当該第1の要求パケットに対する前記第1の応答パケットの送信までの期間よりも長くなるように、前記送信タイミングを決定する前記決定部と、

を備え、

前記送信制御部は、決定済みの前記送信タイミングで、前記第2の応答パケットを前記第2の装置に送信する、通信装置。

【請求項2】

前記受信制御部は、前記第1の装置からM番目(前記Mは1以上の整数)の前記第1の要求パケットを受信し、前記第1の装置から前記M番目の前記第1の要求パケットが受信された後であって、前記第1の装置からM+1番目の前記第1の要求パケットが受信される前に、前記第2の装置からN番目(前記Nは1以上の整数)の前記第2の要求パケットを受信し、

前記送信制御部は、前記M番目の第1の要求パケットに対するM番目の前記第1の応答パケットを前記第1の装置に送信し、前記N番目の第2の要求パケットに対するN番目の前記第2の応答パケットを前記第2の装置に送信し、

前記決定部は、前記N番目の第2の要求パケットの受信から前記N番目の第2の応答パケットの送信までの期間が、前記M番目の第1の要求パケットの受信から前記M番目の第1の応答パケットの送信までの期間よりも長くなるように、前記N番目の第2の応答パケットの送信タイミングを決定し、

前記送信制御部は、決定済みの前記送信タイミングで、前記N番目の第2の応答パケットを前記第2の装置に送信する、請求項1に記載の通信装置。

【請求項3】

前記決定部は、前記第1の要求パケットの受信に関するタイミングを用いて、前記第2の応答パケットの前記送信タイミングを決定する、請求項1又は2に記載の通信装置。

【請求項4】

前記決定部は、前記第1の要求パケットが受信されるタイミングと、前記第2の要求パケットが受信されるタイミングと、がほぼ等しくなるまで、前記第2の要求パケットが受信される毎に、前記第2の応答パケットの前記送信タイミングを決定し、

前記送信制御部は、前記第2の要求パケットが受信される毎に、当該第2の要求パケットについて決定される前記送信タイミングで、当該第2の要求パケットに対する前記第2の応答パケットを送信する、請求項1から3のいずれか一項に記載の通信装置。

【請求項5】

前記第2の装置は、

前記第2の要求パケットを前記通信装置に送信してから特定の期間が経過する前に、当該第2の要求パケットに対する前記第2の応答パケットが受信される場合には、前記第2の応答パケットに従った処理を実行し、

前記第2の要求パケットを前記通信装置に送信してから前記特定の期間が経過した後に、当該第2の要求パケットに対する前記第2の応答パケットが受信されても、前記第2の応答パケットに従った処理を実行せず、

前記決定部は、前記第2の要求パケットの受信から当該第2の要求パケットに対する前記第2の応答パケットの送信までの前記期間が、前記特定の期間以下になるように、前記送信タイミングを決定する、請求項1から4のいずれか一項に記載の通信装置。

【請求項6】

前記受信制御部は、前記第1の装置からM番目(前記Mは1以上の整数)の前記第1の要求パケットを受信し、前記第1の装置から前記M番目の前記第1の要求パケットが受信された後であって、前記第1の装置からM+1番目の前記第1の要求パケットが受信される前に、前記第2の装置からN番目(前記Nは1以上の整数)の前記第2の要求パケットを受信し、

前記送信制御部は、前記M番目の第1の要求パケットに対するM番目の前記第1の応答パケットを前記第1の装置に送信し、前記N番目の第2の要求パケットに対するN番目の前記第2の応答パケットを前記第2の装置に送信し、

前記決定部は、

前記M+1番目の第1の要求パケットの受信タイミングと、前記N番目の第2の要求パケットの受信タイミングと、の間の特定の差分が、前記特定の期間よりも長い場合に、前記N番目の第2の要求パケットの受信から、前記N番目の第2の応答パケットの送信までの期間が、前記特定の期間に一致するように、前記N番目の第2の応答パケットの前記送信タイミングを決定し、

前記特定の差分が、前記特定の期間よりも短い場合に、前記N番目の第2の要求パケットの受信から、前記N番目の第2の応答パケットの送信までの期間が、前記特定の差分に一致するように、前記N番目の第2の応答パケットの前記送信タイミングを決定する、請求項5に記載の通信装置。

【請求項7】

消費電力が比較的に高い高消費状態と、消費電力が比較的に低い低消費状態と、の間で移行可能であるプロセッサを備え、

前記プロセッサは、前記受信制御部と、前記送信制御部と、前記決定部と、移行制御部と、を備え、

前記移行制御部は、前記プロセッサを前記高消費状態と前記低消費状態との間で移行させ、

前記プロセッサが前記低消費状態である間に、前記第1の要求パケットが受信される場合に、

前記移行制御部は、前記プロセッサを前記低消費状態から前記高消費状態に移行させ、

前記送信制御部は、前記プロセッサが前記高消費状態である間に、前記第1の要求パケットに対する前記第1の応答パケットを送信し、

前記プロセッサが前記低消費状態である間に、前記第2の要求パケットが受信される場合に、

前記移行制御部は、前記プロセッサを前記低消費状態から前記高消費状態に移行させ、

前記送信制御部は、前記プロセッサが前記高消費状態である間に、前記第2の要求パケットに対する前記第2の応答パケットを送信する、請求項1から6のいずれか一項に記載の通信装置。

【請求項8】

第1の要求パケットを通信装置に送信して、前記第1の要求パケットに対する第1の応答パケットを、前記通信装置から受信する処理を繰り返し実行し、前記第1の応答パケットを受信してから所定の期間が経過する際に、前記第1の要求パケットを新たに送信する第1の装置と、

第2の要求パケットを前記通信装置に送信して、前記第2の要求パケットに対する第2の応答パケットを、前記通信装置から受信する処理を繰り返し実行し、前記第2の応答パケットを受信してから前記所定の期間が経過する際に、前記第2の要求パケットを新たに送信する第2の装置と、

のそれぞれに接続される前記通信装置のためのコンピュータプログラムであって、

前記通信装置に搭載されるコンピュータに、

前記第1の装置から前記第1の要求パケットを受信し、前記第2の装置から前記第2の要求パケットを受信する受信制御処理と、

前記第1の要求パケットに対する前記第1の応答パケットを前記第1の装置に送信し、前記第2の要求パケットに対する前記第2の応答パケットを前記第2の装置に送信する送信制御処理と、

前記第2の応答パケットを前記第2の装置に送信するための送信タイミングを決定する決定処理であって、前記第2の要求パケットの受信から当該第2の要求パケットに対する前記第2の応答パケットの送信までの時間が、前記第1の要求パケットの受信から当該第1の要求パケットに対する前記第1の応答パケットの送信までの時間よりも長くなるように、前記送信タイミングを決定する前記決定処理と、

を実行させ、

前記送信制御処理では、決定済みの前記送信タイミングで、前記第2の応答パケットを前記第2の装置に送信する、コンピュータプログラム。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−213074(P2012−213074A)

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願番号】特願2011−78107(P2011−78107)

【出願日】平成23年3月31日(2011.3.31)

【出願人】(000005267)ブラザー工業株式会社 (13,856)

【Fターム(参考)】

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願日】平成23年3月31日(2011.3.31)

【出願人】(000005267)ブラザー工業株式会社 (13,856)

【Fターム(参考)】

[ Back to top ]