遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法

【課題】簡易な処理によって遅延素子の遅延情報を出力する遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法を提供すること。

【解決手段】本発明にかかる遅延検出回路10は、基準信号生成部11と、遅延チェーン12と、保持部13と、を備える。基準信号生成部11は、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくともクロック信号の一周期の間は第2のレベルが維持される基準信号を生成する。遅延チェーン12は、多段接続された複数の遅延ゲート12−1〜12−nを有し、基準信号が入力される。保持部13は、クロック信号に同期して複数の遅延ゲート12−1〜12−nの出力信号を保持し、前記遅延手段の遅延情報を出力する。

【解決手段】本発明にかかる遅延検出回路10は、基準信号生成部11と、遅延チェーン12と、保持部13と、を備える。基準信号生成部11は、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくともクロック信号の一周期の間は第2のレベルが維持される基準信号を生成する。遅延チェーン12は、多段接続された複数の遅延ゲート12−1〜12−nを有し、基準信号が入力される。保持部13は、クロック信号に同期して複数の遅延ゲート12−1〜12−nの出力信号を保持し、前記遅延手段の遅延情報を出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法に関し、特に多段接続された遅延手段を備える遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法に関する。

【背景技術】

【0002】

近年、半導体集積回路は、低電力化を図るために電源電圧を下げる方法が一般的に採用されている。電源電圧をどこまで下げられるのかを把握するためには、半導体集積回路の遅延特性を測定する必要がある。そのため、遅延特性を測定する様々な方法が提案されている。

【0003】

例えば、特許文献1には、リングオシレータをある一定時間発振させて、カウンタで発信回数をカウントし、カウント値に基づいて遅延情報を取得する方法が開示されている(特許文献1の図2、図3参照)。

【0004】

特許文献2及び3には、電源電圧に応じた遅延時間で信号を遅延させる遅延ユニットを複数段直列に接続して、一定時間における信号の通過段数に基づいて遅延値を算出する方法が開示されている(特許文献2の図1、特許文献3の図6参照)。

【0005】

特許文献4に開示されたクロック異常検出システムは、多段接続された複数の遅延素子(ディレイセル)を用いて、基準クロック信号を遅延させ、各段の遅延素子から遅延信号を出力する。クロック異常検出システムは、出力された複数の遅延信号の中から、遅延前の基準クロック信号に同期する遅延信号を複数検出する。そして、クロック異常検出システムは、検出された複数の遅延信号に基づいて、基準クロック信号の一周期に係る遅延素子の段数を算出し、基準クロック信号の異常を検出する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】国際公開第2007/034540号

【特許文献2】特開2007−322235号公報

【特許文献3】特許第4617721号

【特許文献4】特開2004−362509号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献1に開示された方法は、ある程度の精度で測定を行うためには、十分な発振回数を確保できる測定時間が必要となる。

【0008】

また、特許文献2に開示された方法は、パルス遅延回路を起動するタイミングを決める起動用パルスと、ラッチ&エンコーダのラッチタイミングを決める計測用パルスと、の位相差が異なる。そのため、遅延特性を測定する際には、2つのパルスの位相差時間を把握しておく必要がある。同様に、特許文献3に開示された方法も、起動用パルスの位相と計測用パルスの位相とが異なるため、2つのパルスの位相差時間を把握しておく必要がある。

【0009】

特許文献4に開示されたクロック異常検出システムにおいては、多段接続された複数の遅延素子に入力される起動用パルスと、各遅延素子からの出力信号を保持するフリップフロップの保持タイミングを決める計測用パルスとは、同位相のクロック信号である。

【0010】

しかし、クロック信号の一周期に係る遅延素子の段数を計測するために、遅延前のクロック信号に同期する遅延後のクロック信号を複数検出し、検出された複数のクロック信号が経由した遅延素子の数の差を算出する遅延段数演算部が別途必要となる。

【0011】

つまり、特許文献1〜4に開示された遅延特性の測定方法は、いずれも処理が複雑であり、測定時間も長くなってしまうという問題があった。

【0012】

本発明は、このような問題を解決するためになされたものであり、簡易な処理によって遅延素子の遅延情報を検出する遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明にかかる遅延検出回路は、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期の間は前記第2のレベルが維持される基準信号を生成する基準信号生成手段と、多段接続された複数の遅延手段を有し、前記基準信号が入力される遅延チェーンと、前記クロック信号に同期して複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する保持手段と、を備えるものである。

【0014】

本発明にかかる電源電圧設定回路は、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期は前記第2のレベルが維持される基準信号を生成する基準信号生成手段と、電源から基準電圧が印加され、多段接続された複数の遅延手段を有し、前記基準信号が入力される遅延チェーンと、前記クロック信号に同期して、複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する保持手段と、前記遅延情報に基づいて、前記電源が出力する前記基準電圧を制御する制御手段と、を備えるものである。

【0015】

本発明にかかる遅延検出回路の制御方法は、多段接続された複数の遅延手段を有する遅延チェーンを備える遅延検出回路の制御方法であって、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期の間は前記第2のレベルが維持される基準信号を生成し、前記基準信号を前記遅延チェーンに入力し、前記クロック信号に同期して複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力するものである。

【発明の効果】

【0016】

本発明により、簡易な処理によって遅延素子の遅延情報を検出する遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法を提供することができる。

【図面の簡単な説明】

【0017】

【図1】実施の形態1にかかる半導体集積回路のブロック図である。

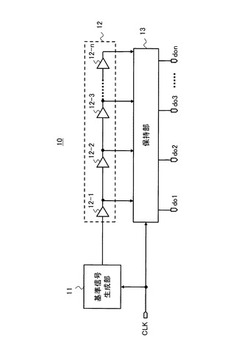

【図2】実施の形態1にかかる遅延検出回路のブロック図である。

【図3】実施の形態2にかかる遅延検出回路の回路図である。

【図4】実施の形態2にかかる遅延検出回路の動作を示すタイミングチャートである。

【図5】実施の形態2にかかる遅延検出回路の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0018】

<実施の形態1>

以下、図面を参照して本発明の実施の形態について説明する。本実施の形態にかかる半導体集積回路1のブロック図を図1に示す。半導体集積回路1は、遅延検出回路10と、論理回路30と、判定回路40と、を備える。遅延検出回路10と論理回路30とは外部の電源50と接続される。電源50は、遅延検出回路10と論理回路30とに基準電圧VDDを供給する。また、遅延検出回路10及び論理回路30にはクロック信号CLKが入力される。

【0019】

遅延検出回路10は、多段接続された遅延素子を有し、半導体集積回路1の遅延特性を測定する。具体的には、遅延検出回路10は、論理回路30において用いられている遅延素子の遅延情報を出力する。遅延検出回路10の詳細な構成については後述する。

【0020】

論理回路30は、複数の論理素子や遅延素子から構成され、入力信号(図示省略)に対して論理演算を行う。このとき、遅延検出回路10の遅延素子及び論理回路30の遅延素子を含む各素子には電源50からの基準電圧VDDが供給される。なお、論理回路30が有する遅延素子と遅延検出回路10が有する遅延素子とは、同じ遅延特性(基準電圧VDDに対する遅延値の変化量)を有する遅延素子である。そのため、遅延検出回路10における遅延素子の一段あたりの遅延値に基づいて、論理回路30における遅延素子の遅延値が測定できる。

【0021】

判定回路40(制御手段)は、遅延検出回路10から入力される遅延情報に基づいて、電源50が出力する基準電圧VDDを制御する制御信号を出力する。具体的には、判定回路40は、遅延情報に基づいて、遅延手段の遅延値を算出する。そして、遅延値が論理回路30において要求される所定の遅延値よりも短い場合、判定回路40は、基準電圧VDDを下げるように電源50に指示する。一方、遅延値が論理回路30において要求される所定の遅延値よりも長い場合、判定回路40は、基準電圧VDDを上げるように電源50に指示する。つまり、判定回路40は、遅延検出回路10から入力される遅延値が論理回路30において要求される所定の遅延値を超えない範囲で、基準電圧VDDがより低くなるように電源50を制御する。これにより、論理回路30の動作に影響を与えることなく、低電力化を図ることができる。なお、遅延検出回路10と判定回路40とが電源電圧設定回路を構成する。

【0022】

次に、遅延検出回路10の詳細な構成について、図2を参照して説明する。図2は、本実施の形態にかかる遅延検出回路10のブロック図である。遅延検出回路10は、基準信号生成部11と、遅延チェーン12と、保持部13と、を備える。なお、基準信号生成部11と保持部13とには、クロック信号CLKが入力される。

【0023】

基準信号生成部11は、入力されたクロック信号CLKに同期して第1のレベルから第2のレベルに変化し、少なくともクロック信号の一周期の間は第2のレベルが維持される基準信号を生成する。基準信号生成部11は、生成した基準信号を遅延チェーン12に出力する。

【0024】

このとき、第1のレベルとは、例えばL(Low)レベルを意味し、第2のレベルとは、例えばH(High)レベルを意味する。つまり、第1のレベルと第2のレベルが異なるレベルであればよい。また、クロック信号CLKに同期して第1のレベルから第2のレベルに変化するとは、例えば、クロック信号CLKの立ち上がりに同期して、LレベルからHレベルに変化することを意味する。さらに、少なくともクロック信号CLKの一周期の間は第2のレベルが維持されるとは、例えば、LレベルからHレベルに変化した後は、少なくともクロック信号CLKの一周期の間はHレベルから変化しないことを意味する。勿論、第1のレベルをHレベルとし、第2のレベルをLレベルとしてもよい。さらに、Lレベル及びHレベルに替えて、"0"及び"1"を用いてもよい。

【0025】

遅延チェーン12は、多段接続された複数の遅延ゲート(遅延手段)12−1〜12−nを有する。遅延チェーン12には、基準信号生成部11が生成した基準信号が入力される。基準信号は、各段に設けられた遅延ゲート12−1〜12−nの遅延値に応じて遅延しながら、遅延ゲート12−1〜12−nを伝搬する。なお、各遅延ゲート12−1〜12−nの遅延値は同一である。

【0026】

遅延ゲート12−1〜12−nの各段の出力信号は保持部13に入力される。各段の出力信号は、基準信号が経由した遅延ゲートの数に応じて遅延した信号である。より詳細には、各段の出力信号は、基準信号が経由した遅延ゲートの遅延値の合計時間だけ遅延した信号である。言い換えると、各段の出力信号は、遅延ゲート一つあたりの遅延値を、経由した遅延ゲートの数で乗じた時間だけ基準信号が遅延した信号である。

【0027】

保持部13は、クロック信号CLKに同期して複数の遅延ゲート12−1〜12−nの出力信号を保持する。保持部13は、例えばフリップフロップ等のラッチ回路から構成される。そして、保持部13は、保持した出力信号に応じた遅延情報として信号do1〜donを出力する。ここで、遅延情報とは、遅延ゲート12−1〜12−nの遅延に関する情報である。具体的には、所定の時間(例えば、クロック信号CLKの一周期)の間に、基準信号が伝搬した遅延ゲートの段数を示す情報である。

【0028】

続いて、本実施の形態にかかる遅延検出回路10及び判定回路40の動作について説明する。まず、基準信号生成部11は、第1のレベルの基準信号を遅延チェーン12に対して出力する。その後、基準信号生成部11は、クロック信号CLKに同期して、基準信号を第1のレベルから第2のレベルに変化させる。

【0029】

保持部13は、クロック信号CLKに同期して、遅延チェーン12の遅延ゲート12−1〜12−nから出力される出力信号を保持する。例えば、保持部13は、基準信号が第1のレベルから第2のレベルに変化してから、一周期経過後に、クロック信号CLKに同期して遅延ゲート12−1〜12−nから出力される出力信号を保持する。

【0030】

このとき、基準信号生成部11が第2のレベルの基準信号を出力してからクロック信号CLKの一周期の間に、第2のレベルの基準信号が伝搬した遅延ゲートの出力信号は第2のレベルとなる。一方、未だ第2のレベルの基準信号が伝搬していない遅延ゲートの出力信号は第1のレベルのままとなる。つまり、保持部13が保持する複数の出力信号のうち、遅延ゲート12−1から第2のレベルの基準信号が伝搬した遅延ゲート(例えば、遅延ゲート12−(m−1)とする)までの出力信号が連続して第2のレベルとなる。一方、第2のレベルの基準信号が伝搬した遅延ゲート(遅延ゲート12−(m−1))の次段の遅延ゲート(遅延ゲート12−m)から遅延ゲート12−nまでの出力信号が連続して第1のレベルとなる。

【0031】

保持部13は、保持した遅延ゲート12−1〜12−nの出力信号に応じた遅延情報を出力する。具体的には、保持部13は、保持した遅延ゲート12−1の出力信号を信号do1として出力する。同様に、保持部13は、保持した遅延ゲート12−2〜12−nの出力信号を信号do2〜donとして出力する。つまり、保持部13は、遅延情報として、第2のレベルの信号do1〜do(m−1)を出力し、第1のレベルの信号dom〜donを出力する。保持部13が出力した遅延情報のうち、第2のレベルの信号を計数することにより、クロック信号CLKの一周期の間に、第2のレベルの基準信号が伝搬した遅延ゲートの段数を検出できる。上記の例では、第2のレベルの信号はdo1〜do(m−1)の(m−1)であるため、第2のレベルの基準信号が伝搬した遅延ゲートの段数は(m−1)段となる。

【0032】

判定回路40は、保持部13から出力された遅延情報を参照し、クロック信号CLKの一周期の時間を、第2のレベルの基準信号が伝搬した遅延ゲートの段数で除することにより、遅延ゲート12−1〜12−nの一段あたりの遅延値を算出する。なお、遅延ゲート12−1〜12−nの一段あたりの遅延値を算出するためには、第2のレベルの基準信号が遅延チェーン12を伝搬した時間を、第2のレベルの基準信号が伝搬した遅延ゲートの段数で除すればよい。そのため、例えば、判定回路40は、クロック信号CLKの二周期の時間を、二周期の間に第2のレベルの基準信号が伝搬した遅延ゲートの段数で除してもよい。

【0033】

そして、判定回路40は、算出した遅延ゲート12−1〜12−nの一段あたりの遅延値に基づいて、電源50が出力する基準電圧VDDを制御する制御信号を出力する。

【0034】

以上のように、本実施の形態にかかる遅延検出回路10の構成によれば、基準信号生成部11が、クロック信号CLKに同期して第1のレベルから第2のレベルに変化し、少なくともクロック信号の一周期の間は第2のレベルが維持される基準信号を遅延チェーン12に出力する。そして、保持部13が、クロック信号CLKに同期して、遅延チェーン12の各遅延ゲート12−1〜12−nの出力信号を保持し、遅延ゲート12−1〜12−nの遅延情報を出力する。これにより、少なくとも一周期の間に第2のレベルの基準信号が伝搬した遅延ゲート12−1〜12−nの段数を検出することができる。さらに、判定回路40は、クロック信号CLKの周期のみを知っていればよく、複数の信号の位相差時間を把握する必要もない。

【0035】

加えて、第2のレベルの基準信号は、クロック信号CLKの一周期の間は、第2のレベルが維持される。そのため、複数の遅延ゲート12−1〜12−nの出力信号のうち、第2のレベルに変化した出力信号は、一周期の間は第2のレベルのまま維持される。したがって、遅延チェーン12の先頭から第2のレベルの基準信号が伝搬した遅延ゲートまでの遅延ゲート(遅延ゲート12−1〜12−(m−1))から、第2のレベルの出力信号が出力される。つまり、第2のレベルの出力信号を計数する際に、毎回遅延チェーン12の先頭(遅延ゲート12−1)から第2のレベルの出力信号の数を数えればよい。その結果、計数を始める遅延ゲートを毎回検出しなくて済むため、計数処理の負担が軽減される。

【0036】

言い換えると、遅延チェーン12において第1のレベルの出力信号と第2のレベルの出力信号との境界を複数検出して、検出された複数の境界の間の遅延ゲートの個数を算出する遅延段数演算部を別途設ける必要がない。このように、本実施の形態にかかる遅延検出回路10は、簡易な処理によって遅延ゲートの遅延値を算出することができる。

【0037】

<実施の形態2>

本発明にかかる実施の形態2について説明する。本実施の形態にかかる遅延検出回路20の構成例を図3に示す。遅延検出回路20は、遅延チェーン12と、遅延検出データ信号起動レジスタ21と、計測レジスタ22−1〜22−nと、セレクタ回路23−1〜23−nと、リセット回路24と、ホールド指示回路25と、を備える。なお、遅延チェーン12は、実施の形態1と同様の構成であるため、詳細な説明を省略する。

【0038】

遅延検出データ信号起動レジスタ21には、入力信号dinが入力される。遅延検出データ信号起動レジスタ21は、入力信号dinをクロック信号CLKに同期して取り込み、遅延検出データ信号dm(基準信号)として出力する。

【0039】

計測レジスタ22−1〜22−nは、セレクタ回路23−1〜23−nを介して、遅延チェーン12の遅延ゲート12−1〜12−nと接続される。計測レジスタ22−1〜22−nは、クロック信号CLKに同期して、遅延ゲート12−1〜12−nの出力信号又は計測レジスタ22−1〜22−nの出力信号を保持する。

【0040】

セレクタ回路23−1〜23−nは、リセット回路24の制御信号に応じて、遅延ゲート12−1〜12−nの出力信号又は計測レジスタ22−1〜22−nの出力信号のいずれか一方を選択し、計測レジスタ22−1〜22−nに出力する。具体的には、セレクタ回路23−1〜23−nは、制御信号が"0"(Lレベル)の場合は、遅延ゲート12−1〜12−nの出力信号を選択する。一方、セレクタ回路23−1〜23−nは、制御信号が"1"(Hレベル)の場合、計測レジスタ22−1〜22−nの出力信号を選択する。

【0041】

リセット回路24は、AND回路であり、イネーブル信号enと、ホールド指示回路25の出力信号とが入力される。リセット回路24は、イネーブル信号en及びホールド指示回路25の出力信号の双方が"0"である場合、又は、いずれか一方が"1"である場合に、セレクタ回路23−1〜23−nに対して"0"を出力する。このため、セレクタ回路23−1〜23−nは、遅延ゲート12−1〜12−nの出力信号を選択する。

【0042】

一方、リセット回路24は、イネーブル信号en及びホールド指示回路25の出力信号の双方が共に"1"である場合、セレクタ回路23−1〜23−nに対して"1"を出力する。このため、セレクタ回路23−1〜23−nは、計測レジスタ22−1〜22−nの出力信号を選択する。

【0043】

ホールド指示回路25は、OR回路であり、計測レジスタ22−1〜22−nが保持する全ての出力信号が入力される。ホールド指示回路25は、計測レジスタ22−1〜22−nが保持する出力信号に"0"と"1"との双方が含まれる場合、リセット回路24に対して"1"を出力する。言い換えると、ホールド指示回路25は、計測レジスタ22−1〜22−nが保持する信号のうち、少なくとも一つの出力信号が"1"であり、その他の計測レジスタの出力信号が"0"である場合、リセット回路24に対して"1"を出力する。

【0044】

続いて、本実施の形態にかかる遅延検出回路20の動作について、図4のタイミングチャートを参照して説明する。まず、イネーブル信号en及び入力信号dinを"0"にする。遅延検出データ信号起動レジスタ21及び計測レジスタ22−1〜22−nは、クロック信号CLKに同期して"0"を保持する。これにより、遅延検出データ信号起動レジスタ21及び計測レジスタ22−1〜22−nをリセットする。

【0045】

次に、イネーブル信号en及び入力信号dinを"0"から"1"に変化させる(図4の時刻t1)。すると、遅延検出データ信号起動レジスタ21は、クロック信号CLKに同期して、"1"に変化した入力信号dinを保持する。このため、遅延検出データ信号起動レジスタ21の出力信号である遅延検出データ信号dmが、"0"から"1"に変化する(図4の時刻t2)。遅延検出データ信号起動レジスタ21は、"1"を遅延チェーン12に対して出力する。

【0046】

遅延検出データ信号起動レジスタ21から遅延検出データ信号dmの"1"が出力されると、遅延検出データ信号dmは、遅延チェーン12の各遅延ゲートを伝搬していく。

【0047】

そして、遅延検出データ信号dmが"1"に変化してから、一周期経過後、計測レジスタ22−1〜22−nは、クロック信号CLKに同期して、遅延ゲート12−1〜12−nの出力信号を保持する(図4の時刻t3)。

【0048】

図4に示す例においては、計測レジスタ22−1〜22−(m−1)が、時刻t3において"1"を保持したため、計測レジスタ22−1〜22−(m−1)の出力信号do1〜do(m−1)は、"0"から"1"に変化している。

【0049】

一方、計測レジスタ22−m〜22−nは、時刻t3において"0"を保持したため、計測レジスタ22−m〜22−nの出力信号dom〜donは"0"のまま変化していない。

【0050】

つまり、時刻t2において、クロック信号CLKに同期して遅延チェーン12に出力された遅延検出データ信号"1"は、時刻t2から時刻t3までの間、つまりクロック信号CLKの一周期の間に、遅延ゲート12−1から12−(m−1)まで伝搬したことになる。

【0051】

このとき、計測レジスタ22−1〜22−(m−1)の出力信号do1〜do(m−1)は"1"であり、計測レジスタ22−m〜22−nの出力信号dom〜donは"0"である。そのため、ホールド指示回路25には、"1"及び"0"が入力される。その結果、ホールド指示回路25は、"1"をリセット回路24に出力する。

【0052】

上記したように、リセット回路24に入力されているイネーブル信号enは"1"であるため、リセット回路24の入力信号は共に"1"となる。そのため、リセット回路24の出力信号selは、"0"から"1"に変化する(図4の時刻t3)。これにより、セレクタ回路23−1〜23−nは、計測レジスタ22−1〜22−nの出力信号を選択する。つまり、計測レジスタ22−1〜22−nには、計測レジスタ22−1〜22−nが出力した信号が入力されることとなるため、計測レジスタ22−1〜22−nが保持した値がホールドされる。

【0053】

計測レジスタ22−1〜22−nによってホールドされた遅延ゲート12−1〜12−nの出力信号は、判定回路40に入力される。判定回路40は、入力された出力信号do1〜donのうち"1"の計数を行う。本実施の形態においては、出力信号do(m−1)までが"1"であるため、"1"の数は(m−1)個である。

【0054】

判定回路40は、クロック信号CLKの一周期の時間を(m−1)で除する。これにより、遅延ゲート12−1〜12−nの一段あたりの遅延値(遅延時間)が算出される。その後の処理については、実施の形態1と同様であるため、詳細な説明は省略する。

【0055】

上述した図4のタイミングチャートにおいては、入力信号dinを"0"から"1"に変化させた場合について説明したが、これに限られるものではない。図5のタイミングチャートに示すように、最初に"1"の入力信号dinを入力し、計測レジスタ22−1〜22−nに"1"を保持させてから、入力信号dinを"1"から"0"に変化させてもよい。

【0056】

この場合も、図4において説明した処理と同様に、遅延検出データ信号dmが"1"から"0"に変化してから、一周期の間に、"0"が遅延チェーン12のどこまで伝搬したのかを検出することにより、遅延値を算出できる。具体的には、判定回路40は、遅延検出データ信号dmが"1"から"0"に変化してから、一周期経過後に計測レジスタ22−1〜22−nが保持した値のうち、"0"の個数を数える(図5においては(m−1)個)。そして、判定回路40は、一周期の時間を"0"の個数で除することにより、遅延ゲート12−1〜12−nの一段あたりの遅延値を算出する。

【0057】

以上のように、本実施の形態にかかる遅延検出回路20の構成によれば、遅延検出データ信号起動レジスタ21が、入力信号dinに基づいて、クロック信号CLKに同期して"0"から"1"に変化し、少なくともクロック信号の一周期の間は"1"が維持される遅延検出データ信号dmを遅延チェーン12に出力する。そして、計測レジスタ22−1〜22−nが、クロック信号CLKに同期して、遅延チェーン12の各遅延ゲート12−1〜12−nの出力信号を保持し、遅延情報を出力する。これにより、少なくとも一周期の間に遅延検出データ信号dmが伝搬した遅延ゲート12−1〜12−nの段数を検出することができる。

【0058】

また、遅延検出データ信号dmは、"0"から"1"に変化した後はそのレベルが維持される。そのため、遅延ゲート12−1〜12−nの出力信号のうち、"1"に変化した出力信号は"1"のまま維持される。その結果、"1"の出力信号が、遅延チェーン12の先頭(遅延ゲート12−1)から"1"が伝搬した遅延ゲート(遅延ゲート12−(m−1))まで連続して出力される。したがって、計測レジスタ22−1〜22−nの先頭(計測レジスタ22−1)から連続する"1"の数を算出するだけで、一周期の間に遅延検出データ信号dmが伝搬した遅延ゲートの段数を検出できる。つまり、段数検出の処理負担が軽減される。

【0059】

さらに、本実施の形態にかかる遅延検出回路20は、全てのブロックがデジタル回路を用いて構成された単相クロック同期回路であり、容易に設計可能である。また、遅延検出データ信号dm(起動用パルス)と計測レジスタ22−1〜22−nに入力される計測用パルスとを同一のクロック信号CLKで同期させている。そのため、クロック信号CLKの一周期の間に遅延検出データ信号dmが伝搬した遅延ゲートの段数を正確に検出できると共に、起動用パルスと計測用パルスとの位相差時間を把握しておく必要もない。

【0060】

加えて、本実施の形態においては、図4及び図5に示すように、遅延検出データ信号dmを立ち上げ又は立ち下げてから(図4の時刻t2)、一周期後に計測レジスタ22−1〜22−nが保持した値を測定することにより、遅延検出データ信号dmが伝搬した段数を検出できる。つまり、計測を開始してから一周期後には、遅延検出データ信号dmが伝搬した段数を検出できるため、短時間で遅延値を算出できる。

【0061】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更及び組み合わせをすることが可能である。例えば、上述した実施の形態においては、遅延ゲート12−1〜12−nが同一の遅延値を有しているが、同一であることに限られない。また、遅延検出回路10、20は、遅延情報として、各遅延ゲート12−1〜12−nの出力信号の全てを出力しているが、第2のレベルの基準信号が伝搬した遅延ゲートのうちの一番後段側の遅延ゲートの番号のみを遅延情報として出力してもよい。

【符号の説明】

【0062】

1 半導体集積回路

10、20 遅延検出回路

11 基準信号生成部

12 遅延チェーン

12−1〜12−n 遅延ゲート

13 保持部

14 遅延値算出部

21 遅延検出データ信号起動レジスタ

22−1〜22−n 計測レジスタ

23−1〜23−n セレクタ回路

24 リセット回路

25 ホールド指示回路

30 論理回路

40 判定回路

50 電源

【技術分野】

【0001】

本発明は遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法に関し、特に多段接続された遅延手段を備える遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法に関する。

【背景技術】

【0002】

近年、半導体集積回路は、低電力化を図るために電源電圧を下げる方法が一般的に採用されている。電源電圧をどこまで下げられるのかを把握するためには、半導体集積回路の遅延特性を測定する必要がある。そのため、遅延特性を測定する様々な方法が提案されている。

【0003】

例えば、特許文献1には、リングオシレータをある一定時間発振させて、カウンタで発信回数をカウントし、カウント値に基づいて遅延情報を取得する方法が開示されている(特許文献1の図2、図3参照)。

【0004】

特許文献2及び3には、電源電圧に応じた遅延時間で信号を遅延させる遅延ユニットを複数段直列に接続して、一定時間における信号の通過段数に基づいて遅延値を算出する方法が開示されている(特許文献2の図1、特許文献3の図6参照)。

【0005】

特許文献4に開示されたクロック異常検出システムは、多段接続された複数の遅延素子(ディレイセル)を用いて、基準クロック信号を遅延させ、各段の遅延素子から遅延信号を出力する。クロック異常検出システムは、出力された複数の遅延信号の中から、遅延前の基準クロック信号に同期する遅延信号を複数検出する。そして、クロック異常検出システムは、検出された複数の遅延信号に基づいて、基準クロック信号の一周期に係る遅延素子の段数を算出し、基準クロック信号の異常を検出する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】国際公開第2007/034540号

【特許文献2】特開2007−322235号公報

【特許文献3】特許第4617721号

【特許文献4】特開2004−362509号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献1に開示された方法は、ある程度の精度で測定を行うためには、十分な発振回数を確保できる測定時間が必要となる。

【0008】

また、特許文献2に開示された方法は、パルス遅延回路を起動するタイミングを決める起動用パルスと、ラッチ&エンコーダのラッチタイミングを決める計測用パルスと、の位相差が異なる。そのため、遅延特性を測定する際には、2つのパルスの位相差時間を把握しておく必要がある。同様に、特許文献3に開示された方法も、起動用パルスの位相と計測用パルスの位相とが異なるため、2つのパルスの位相差時間を把握しておく必要がある。

【0009】

特許文献4に開示されたクロック異常検出システムにおいては、多段接続された複数の遅延素子に入力される起動用パルスと、各遅延素子からの出力信号を保持するフリップフロップの保持タイミングを決める計測用パルスとは、同位相のクロック信号である。

【0010】

しかし、クロック信号の一周期に係る遅延素子の段数を計測するために、遅延前のクロック信号に同期する遅延後のクロック信号を複数検出し、検出された複数のクロック信号が経由した遅延素子の数の差を算出する遅延段数演算部が別途必要となる。

【0011】

つまり、特許文献1〜4に開示された遅延特性の測定方法は、いずれも処理が複雑であり、測定時間も長くなってしまうという問題があった。

【0012】

本発明は、このような問題を解決するためになされたものであり、簡易な処理によって遅延素子の遅延情報を検出する遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明にかかる遅延検出回路は、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期の間は前記第2のレベルが維持される基準信号を生成する基準信号生成手段と、多段接続された複数の遅延手段を有し、前記基準信号が入力される遅延チェーンと、前記クロック信号に同期して複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する保持手段と、を備えるものである。

【0014】

本発明にかかる電源電圧設定回路は、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期は前記第2のレベルが維持される基準信号を生成する基準信号生成手段と、電源から基準電圧が印加され、多段接続された複数の遅延手段を有し、前記基準信号が入力される遅延チェーンと、前記クロック信号に同期して、複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する保持手段と、前記遅延情報に基づいて、前記電源が出力する前記基準電圧を制御する制御手段と、を備えるものである。

【0015】

本発明にかかる遅延検出回路の制御方法は、多段接続された複数の遅延手段を有する遅延チェーンを備える遅延検出回路の制御方法であって、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期の間は前記第2のレベルが維持される基準信号を生成し、前記基準信号を前記遅延チェーンに入力し、前記クロック信号に同期して複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力するものである。

【発明の効果】

【0016】

本発明により、簡易な処理によって遅延素子の遅延情報を検出する遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法を提供することができる。

【図面の簡単な説明】

【0017】

【図1】実施の形態1にかかる半導体集積回路のブロック図である。

【図2】実施の形態1にかかる遅延検出回路のブロック図である。

【図3】実施の形態2にかかる遅延検出回路の回路図である。

【図4】実施の形態2にかかる遅延検出回路の動作を示すタイミングチャートである。

【図5】実施の形態2にかかる遅延検出回路の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0018】

<実施の形態1>

以下、図面を参照して本発明の実施の形態について説明する。本実施の形態にかかる半導体集積回路1のブロック図を図1に示す。半導体集積回路1は、遅延検出回路10と、論理回路30と、判定回路40と、を備える。遅延検出回路10と論理回路30とは外部の電源50と接続される。電源50は、遅延検出回路10と論理回路30とに基準電圧VDDを供給する。また、遅延検出回路10及び論理回路30にはクロック信号CLKが入力される。

【0019】

遅延検出回路10は、多段接続された遅延素子を有し、半導体集積回路1の遅延特性を測定する。具体的には、遅延検出回路10は、論理回路30において用いられている遅延素子の遅延情報を出力する。遅延検出回路10の詳細な構成については後述する。

【0020】

論理回路30は、複数の論理素子や遅延素子から構成され、入力信号(図示省略)に対して論理演算を行う。このとき、遅延検出回路10の遅延素子及び論理回路30の遅延素子を含む各素子には電源50からの基準電圧VDDが供給される。なお、論理回路30が有する遅延素子と遅延検出回路10が有する遅延素子とは、同じ遅延特性(基準電圧VDDに対する遅延値の変化量)を有する遅延素子である。そのため、遅延検出回路10における遅延素子の一段あたりの遅延値に基づいて、論理回路30における遅延素子の遅延値が測定できる。

【0021】

判定回路40(制御手段)は、遅延検出回路10から入力される遅延情報に基づいて、電源50が出力する基準電圧VDDを制御する制御信号を出力する。具体的には、判定回路40は、遅延情報に基づいて、遅延手段の遅延値を算出する。そして、遅延値が論理回路30において要求される所定の遅延値よりも短い場合、判定回路40は、基準電圧VDDを下げるように電源50に指示する。一方、遅延値が論理回路30において要求される所定の遅延値よりも長い場合、判定回路40は、基準電圧VDDを上げるように電源50に指示する。つまり、判定回路40は、遅延検出回路10から入力される遅延値が論理回路30において要求される所定の遅延値を超えない範囲で、基準電圧VDDがより低くなるように電源50を制御する。これにより、論理回路30の動作に影響を与えることなく、低電力化を図ることができる。なお、遅延検出回路10と判定回路40とが電源電圧設定回路を構成する。

【0022】

次に、遅延検出回路10の詳細な構成について、図2を参照して説明する。図2は、本実施の形態にかかる遅延検出回路10のブロック図である。遅延検出回路10は、基準信号生成部11と、遅延チェーン12と、保持部13と、を備える。なお、基準信号生成部11と保持部13とには、クロック信号CLKが入力される。

【0023】

基準信号生成部11は、入力されたクロック信号CLKに同期して第1のレベルから第2のレベルに変化し、少なくともクロック信号の一周期の間は第2のレベルが維持される基準信号を生成する。基準信号生成部11は、生成した基準信号を遅延チェーン12に出力する。

【0024】

このとき、第1のレベルとは、例えばL(Low)レベルを意味し、第2のレベルとは、例えばH(High)レベルを意味する。つまり、第1のレベルと第2のレベルが異なるレベルであればよい。また、クロック信号CLKに同期して第1のレベルから第2のレベルに変化するとは、例えば、クロック信号CLKの立ち上がりに同期して、LレベルからHレベルに変化することを意味する。さらに、少なくともクロック信号CLKの一周期の間は第2のレベルが維持されるとは、例えば、LレベルからHレベルに変化した後は、少なくともクロック信号CLKの一周期の間はHレベルから変化しないことを意味する。勿論、第1のレベルをHレベルとし、第2のレベルをLレベルとしてもよい。さらに、Lレベル及びHレベルに替えて、"0"及び"1"を用いてもよい。

【0025】

遅延チェーン12は、多段接続された複数の遅延ゲート(遅延手段)12−1〜12−nを有する。遅延チェーン12には、基準信号生成部11が生成した基準信号が入力される。基準信号は、各段に設けられた遅延ゲート12−1〜12−nの遅延値に応じて遅延しながら、遅延ゲート12−1〜12−nを伝搬する。なお、各遅延ゲート12−1〜12−nの遅延値は同一である。

【0026】

遅延ゲート12−1〜12−nの各段の出力信号は保持部13に入力される。各段の出力信号は、基準信号が経由した遅延ゲートの数に応じて遅延した信号である。より詳細には、各段の出力信号は、基準信号が経由した遅延ゲートの遅延値の合計時間だけ遅延した信号である。言い換えると、各段の出力信号は、遅延ゲート一つあたりの遅延値を、経由した遅延ゲートの数で乗じた時間だけ基準信号が遅延した信号である。

【0027】

保持部13は、クロック信号CLKに同期して複数の遅延ゲート12−1〜12−nの出力信号を保持する。保持部13は、例えばフリップフロップ等のラッチ回路から構成される。そして、保持部13は、保持した出力信号に応じた遅延情報として信号do1〜donを出力する。ここで、遅延情報とは、遅延ゲート12−1〜12−nの遅延に関する情報である。具体的には、所定の時間(例えば、クロック信号CLKの一周期)の間に、基準信号が伝搬した遅延ゲートの段数を示す情報である。

【0028】

続いて、本実施の形態にかかる遅延検出回路10及び判定回路40の動作について説明する。まず、基準信号生成部11は、第1のレベルの基準信号を遅延チェーン12に対して出力する。その後、基準信号生成部11は、クロック信号CLKに同期して、基準信号を第1のレベルから第2のレベルに変化させる。

【0029】

保持部13は、クロック信号CLKに同期して、遅延チェーン12の遅延ゲート12−1〜12−nから出力される出力信号を保持する。例えば、保持部13は、基準信号が第1のレベルから第2のレベルに変化してから、一周期経過後に、クロック信号CLKに同期して遅延ゲート12−1〜12−nから出力される出力信号を保持する。

【0030】

このとき、基準信号生成部11が第2のレベルの基準信号を出力してからクロック信号CLKの一周期の間に、第2のレベルの基準信号が伝搬した遅延ゲートの出力信号は第2のレベルとなる。一方、未だ第2のレベルの基準信号が伝搬していない遅延ゲートの出力信号は第1のレベルのままとなる。つまり、保持部13が保持する複数の出力信号のうち、遅延ゲート12−1から第2のレベルの基準信号が伝搬した遅延ゲート(例えば、遅延ゲート12−(m−1)とする)までの出力信号が連続して第2のレベルとなる。一方、第2のレベルの基準信号が伝搬した遅延ゲート(遅延ゲート12−(m−1))の次段の遅延ゲート(遅延ゲート12−m)から遅延ゲート12−nまでの出力信号が連続して第1のレベルとなる。

【0031】

保持部13は、保持した遅延ゲート12−1〜12−nの出力信号に応じた遅延情報を出力する。具体的には、保持部13は、保持した遅延ゲート12−1の出力信号を信号do1として出力する。同様に、保持部13は、保持した遅延ゲート12−2〜12−nの出力信号を信号do2〜donとして出力する。つまり、保持部13は、遅延情報として、第2のレベルの信号do1〜do(m−1)を出力し、第1のレベルの信号dom〜donを出力する。保持部13が出力した遅延情報のうち、第2のレベルの信号を計数することにより、クロック信号CLKの一周期の間に、第2のレベルの基準信号が伝搬した遅延ゲートの段数を検出できる。上記の例では、第2のレベルの信号はdo1〜do(m−1)の(m−1)であるため、第2のレベルの基準信号が伝搬した遅延ゲートの段数は(m−1)段となる。

【0032】

判定回路40は、保持部13から出力された遅延情報を参照し、クロック信号CLKの一周期の時間を、第2のレベルの基準信号が伝搬した遅延ゲートの段数で除することにより、遅延ゲート12−1〜12−nの一段あたりの遅延値を算出する。なお、遅延ゲート12−1〜12−nの一段あたりの遅延値を算出するためには、第2のレベルの基準信号が遅延チェーン12を伝搬した時間を、第2のレベルの基準信号が伝搬した遅延ゲートの段数で除すればよい。そのため、例えば、判定回路40は、クロック信号CLKの二周期の時間を、二周期の間に第2のレベルの基準信号が伝搬した遅延ゲートの段数で除してもよい。

【0033】

そして、判定回路40は、算出した遅延ゲート12−1〜12−nの一段あたりの遅延値に基づいて、電源50が出力する基準電圧VDDを制御する制御信号を出力する。

【0034】

以上のように、本実施の形態にかかる遅延検出回路10の構成によれば、基準信号生成部11が、クロック信号CLKに同期して第1のレベルから第2のレベルに変化し、少なくともクロック信号の一周期の間は第2のレベルが維持される基準信号を遅延チェーン12に出力する。そして、保持部13が、クロック信号CLKに同期して、遅延チェーン12の各遅延ゲート12−1〜12−nの出力信号を保持し、遅延ゲート12−1〜12−nの遅延情報を出力する。これにより、少なくとも一周期の間に第2のレベルの基準信号が伝搬した遅延ゲート12−1〜12−nの段数を検出することができる。さらに、判定回路40は、クロック信号CLKの周期のみを知っていればよく、複数の信号の位相差時間を把握する必要もない。

【0035】

加えて、第2のレベルの基準信号は、クロック信号CLKの一周期の間は、第2のレベルが維持される。そのため、複数の遅延ゲート12−1〜12−nの出力信号のうち、第2のレベルに変化した出力信号は、一周期の間は第2のレベルのまま維持される。したがって、遅延チェーン12の先頭から第2のレベルの基準信号が伝搬した遅延ゲートまでの遅延ゲート(遅延ゲート12−1〜12−(m−1))から、第2のレベルの出力信号が出力される。つまり、第2のレベルの出力信号を計数する際に、毎回遅延チェーン12の先頭(遅延ゲート12−1)から第2のレベルの出力信号の数を数えればよい。その結果、計数を始める遅延ゲートを毎回検出しなくて済むため、計数処理の負担が軽減される。

【0036】

言い換えると、遅延チェーン12において第1のレベルの出力信号と第2のレベルの出力信号との境界を複数検出して、検出された複数の境界の間の遅延ゲートの個数を算出する遅延段数演算部を別途設ける必要がない。このように、本実施の形態にかかる遅延検出回路10は、簡易な処理によって遅延ゲートの遅延値を算出することができる。

【0037】

<実施の形態2>

本発明にかかる実施の形態2について説明する。本実施の形態にかかる遅延検出回路20の構成例を図3に示す。遅延検出回路20は、遅延チェーン12と、遅延検出データ信号起動レジスタ21と、計測レジスタ22−1〜22−nと、セレクタ回路23−1〜23−nと、リセット回路24と、ホールド指示回路25と、を備える。なお、遅延チェーン12は、実施の形態1と同様の構成であるため、詳細な説明を省略する。

【0038】

遅延検出データ信号起動レジスタ21には、入力信号dinが入力される。遅延検出データ信号起動レジスタ21は、入力信号dinをクロック信号CLKに同期して取り込み、遅延検出データ信号dm(基準信号)として出力する。

【0039】

計測レジスタ22−1〜22−nは、セレクタ回路23−1〜23−nを介して、遅延チェーン12の遅延ゲート12−1〜12−nと接続される。計測レジスタ22−1〜22−nは、クロック信号CLKに同期して、遅延ゲート12−1〜12−nの出力信号又は計測レジスタ22−1〜22−nの出力信号を保持する。

【0040】

セレクタ回路23−1〜23−nは、リセット回路24の制御信号に応じて、遅延ゲート12−1〜12−nの出力信号又は計測レジスタ22−1〜22−nの出力信号のいずれか一方を選択し、計測レジスタ22−1〜22−nに出力する。具体的には、セレクタ回路23−1〜23−nは、制御信号が"0"(Lレベル)の場合は、遅延ゲート12−1〜12−nの出力信号を選択する。一方、セレクタ回路23−1〜23−nは、制御信号が"1"(Hレベル)の場合、計測レジスタ22−1〜22−nの出力信号を選択する。

【0041】

リセット回路24は、AND回路であり、イネーブル信号enと、ホールド指示回路25の出力信号とが入力される。リセット回路24は、イネーブル信号en及びホールド指示回路25の出力信号の双方が"0"である場合、又は、いずれか一方が"1"である場合に、セレクタ回路23−1〜23−nに対して"0"を出力する。このため、セレクタ回路23−1〜23−nは、遅延ゲート12−1〜12−nの出力信号を選択する。

【0042】

一方、リセット回路24は、イネーブル信号en及びホールド指示回路25の出力信号の双方が共に"1"である場合、セレクタ回路23−1〜23−nに対して"1"を出力する。このため、セレクタ回路23−1〜23−nは、計測レジスタ22−1〜22−nの出力信号を選択する。

【0043】

ホールド指示回路25は、OR回路であり、計測レジスタ22−1〜22−nが保持する全ての出力信号が入力される。ホールド指示回路25は、計測レジスタ22−1〜22−nが保持する出力信号に"0"と"1"との双方が含まれる場合、リセット回路24に対して"1"を出力する。言い換えると、ホールド指示回路25は、計測レジスタ22−1〜22−nが保持する信号のうち、少なくとも一つの出力信号が"1"であり、その他の計測レジスタの出力信号が"0"である場合、リセット回路24に対して"1"を出力する。

【0044】

続いて、本実施の形態にかかる遅延検出回路20の動作について、図4のタイミングチャートを参照して説明する。まず、イネーブル信号en及び入力信号dinを"0"にする。遅延検出データ信号起動レジスタ21及び計測レジスタ22−1〜22−nは、クロック信号CLKに同期して"0"を保持する。これにより、遅延検出データ信号起動レジスタ21及び計測レジスタ22−1〜22−nをリセットする。

【0045】

次に、イネーブル信号en及び入力信号dinを"0"から"1"に変化させる(図4の時刻t1)。すると、遅延検出データ信号起動レジスタ21は、クロック信号CLKに同期して、"1"に変化した入力信号dinを保持する。このため、遅延検出データ信号起動レジスタ21の出力信号である遅延検出データ信号dmが、"0"から"1"に変化する(図4の時刻t2)。遅延検出データ信号起動レジスタ21は、"1"を遅延チェーン12に対して出力する。

【0046】

遅延検出データ信号起動レジスタ21から遅延検出データ信号dmの"1"が出力されると、遅延検出データ信号dmは、遅延チェーン12の各遅延ゲートを伝搬していく。

【0047】

そして、遅延検出データ信号dmが"1"に変化してから、一周期経過後、計測レジスタ22−1〜22−nは、クロック信号CLKに同期して、遅延ゲート12−1〜12−nの出力信号を保持する(図4の時刻t3)。

【0048】

図4に示す例においては、計測レジスタ22−1〜22−(m−1)が、時刻t3において"1"を保持したため、計測レジスタ22−1〜22−(m−1)の出力信号do1〜do(m−1)は、"0"から"1"に変化している。

【0049】

一方、計測レジスタ22−m〜22−nは、時刻t3において"0"を保持したため、計測レジスタ22−m〜22−nの出力信号dom〜donは"0"のまま変化していない。

【0050】

つまり、時刻t2において、クロック信号CLKに同期して遅延チェーン12に出力された遅延検出データ信号"1"は、時刻t2から時刻t3までの間、つまりクロック信号CLKの一周期の間に、遅延ゲート12−1から12−(m−1)まで伝搬したことになる。

【0051】

このとき、計測レジスタ22−1〜22−(m−1)の出力信号do1〜do(m−1)は"1"であり、計測レジスタ22−m〜22−nの出力信号dom〜donは"0"である。そのため、ホールド指示回路25には、"1"及び"0"が入力される。その結果、ホールド指示回路25は、"1"をリセット回路24に出力する。

【0052】

上記したように、リセット回路24に入力されているイネーブル信号enは"1"であるため、リセット回路24の入力信号は共に"1"となる。そのため、リセット回路24の出力信号selは、"0"から"1"に変化する(図4の時刻t3)。これにより、セレクタ回路23−1〜23−nは、計測レジスタ22−1〜22−nの出力信号を選択する。つまり、計測レジスタ22−1〜22−nには、計測レジスタ22−1〜22−nが出力した信号が入力されることとなるため、計測レジスタ22−1〜22−nが保持した値がホールドされる。

【0053】

計測レジスタ22−1〜22−nによってホールドされた遅延ゲート12−1〜12−nの出力信号は、判定回路40に入力される。判定回路40は、入力された出力信号do1〜donのうち"1"の計数を行う。本実施の形態においては、出力信号do(m−1)までが"1"であるため、"1"の数は(m−1)個である。

【0054】

判定回路40は、クロック信号CLKの一周期の時間を(m−1)で除する。これにより、遅延ゲート12−1〜12−nの一段あたりの遅延値(遅延時間)が算出される。その後の処理については、実施の形態1と同様であるため、詳細な説明は省略する。

【0055】

上述した図4のタイミングチャートにおいては、入力信号dinを"0"から"1"に変化させた場合について説明したが、これに限られるものではない。図5のタイミングチャートに示すように、最初に"1"の入力信号dinを入力し、計測レジスタ22−1〜22−nに"1"を保持させてから、入力信号dinを"1"から"0"に変化させてもよい。

【0056】

この場合も、図4において説明した処理と同様に、遅延検出データ信号dmが"1"から"0"に変化してから、一周期の間に、"0"が遅延チェーン12のどこまで伝搬したのかを検出することにより、遅延値を算出できる。具体的には、判定回路40は、遅延検出データ信号dmが"1"から"0"に変化してから、一周期経過後に計測レジスタ22−1〜22−nが保持した値のうち、"0"の個数を数える(図5においては(m−1)個)。そして、判定回路40は、一周期の時間を"0"の個数で除することにより、遅延ゲート12−1〜12−nの一段あたりの遅延値を算出する。

【0057】

以上のように、本実施の形態にかかる遅延検出回路20の構成によれば、遅延検出データ信号起動レジスタ21が、入力信号dinに基づいて、クロック信号CLKに同期して"0"から"1"に変化し、少なくともクロック信号の一周期の間は"1"が維持される遅延検出データ信号dmを遅延チェーン12に出力する。そして、計測レジスタ22−1〜22−nが、クロック信号CLKに同期して、遅延チェーン12の各遅延ゲート12−1〜12−nの出力信号を保持し、遅延情報を出力する。これにより、少なくとも一周期の間に遅延検出データ信号dmが伝搬した遅延ゲート12−1〜12−nの段数を検出することができる。

【0058】

また、遅延検出データ信号dmは、"0"から"1"に変化した後はそのレベルが維持される。そのため、遅延ゲート12−1〜12−nの出力信号のうち、"1"に変化した出力信号は"1"のまま維持される。その結果、"1"の出力信号が、遅延チェーン12の先頭(遅延ゲート12−1)から"1"が伝搬した遅延ゲート(遅延ゲート12−(m−1))まで連続して出力される。したがって、計測レジスタ22−1〜22−nの先頭(計測レジスタ22−1)から連続する"1"の数を算出するだけで、一周期の間に遅延検出データ信号dmが伝搬した遅延ゲートの段数を検出できる。つまり、段数検出の処理負担が軽減される。

【0059】

さらに、本実施の形態にかかる遅延検出回路20は、全てのブロックがデジタル回路を用いて構成された単相クロック同期回路であり、容易に設計可能である。また、遅延検出データ信号dm(起動用パルス)と計測レジスタ22−1〜22−nに入力される計測用パルスとを同一のクロック信号CLKで同期させている。そのため、クロック信号CLKの一周期の間に遅延検出データ信号dmが伝搬した遅延ゲートの段数を正確に検出できると共に、起動用パルスと計測用パルスとの位相差時間を把握しておく必要もない。

【0060】

加えて、本実施の形態においては、図4及び図5に示すように、遅延検出データ信号dmを立ち上げ又は立ち下げてから(図4の時刻t2)、一周期後に計測レジスタ22−1〜22−nが保持した値を測定することにより、遅延検出データ信号dmが伝搬した段数を検出できる。つまり、計測を開始してから一周期後には、遅延検出データ信号dmが伝搬した段数を検出できるため、短時間で遅延値を算出できる。

【0061】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更及び組み合わせをすることが可能である。例えば、上述した実施の形態においては、遅延ゲート12−1〜12−nが同一の遅延値を有しているが、同一であることに限られない。また、遅延検出回路10、20は、遅延情報として、各遅延ゲート12−1〜12−nの出力信号の全てを出力しているが、第2のレベルの基準信号が伝搬した遅延ゲートのうちの一番後段側の遅延ゲートの番号のみを遅延情報として出力してもよい。

【符号の説明】

【0062】

1 半導体集積回路

10、20 遅延検出回路

11 基準信号生成部

12 遅延チェーン

12−1〜12−n 遅延ゲート

13 保持部

14 遅延値算出部

21 遅延検出データ信号起動レジスタ

22−1〜22−n 計測レジスタ

23−1〜23−n セレクタ回路

24 リセット回路

25 ホールド指示回路

30 論理回路

40 判定回路

50 電源

【特許請求の範囲】

【請求項1】

クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期の間は前記第2のレベルが維持される基準信号を生成する基準信号生成手段と、

多段接続された複数の遅延手段を有し、前記基準信号が入力される遅延チェーンと、

前記クロック信号に同期して複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する保持手段と、

を備える遅延検出回路。

【請求項2】

前記保持手段は、前記基準信号が前記クロック信号に同期して前記第1のレベルから前記第2のレベルに変化してから、前記クロック信号の一周期経過後に、複数の前記遅延手段の前記出力信号を保持する請求項1に記載の遅延検出回路。

【請求項3】

前記保持手段が保持した複数の前記遅延手段の前記出力信号に、前記第1及び第2のレベルの前記出力信号が含まれている場合、前記保持手段に入力される信号を前記遅延手段の前記出力信号から、前記保持手段の出力信号に切り換える選択手段をさらに備える請求項1又は2に記載の遅延検出回路。

【請求項4】

クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期は前記第2のレベルが維持される基準信号を生成する基準信号生成手段と、

電源から基準電圧が印加され、多段接続された複数の遅延手段を有し、前記基準信号が入力される遅延チェーンと、

前記クロック信号に同期して、複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する保持手段と、

前記遅延情報に基づいて、前記電源が出力する前記基準電圧を制御する制御手段と、

を備える電源電圧設定回路。

【請求項5】

前記制御手段は、前記基準信号が前記クロック信号に同期して前記第1のレベルから前記第2のレベルに変化してから、前記保持手段が前記クロック信号に同期して複数の前記出力信号を保持するまでの時間を、前記遅延情報に応じた前記遅延手段の段数で除することにより、前記遅延手段の遅延値を算出し、当該遅延値に基づいて、前記電源が出力する前記基準電圧を制御する請求項4に記載の電源電圧設定回路。

【請求項6】

多段接続された複数の遅延手段を有する遅延チェーンを備える遅延検出回路の制御方法であって、

クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期の間は前記第2のレベルが維持される基準信号を生成し、

前記基準信号を前記遅延チェーンに入力し、

前記クロック信号に同期して複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する遅延検出回路の制御方法。

【請求項1】

クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期の間は前記第2のレベルが維持される基準信号を生成する基準信号生成手段と、

多段接続された複数の遅延手段を有し、前記基準信号が入力される遅延チェーンと、

前記クロック信号に同期して複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する保持手段と、

を備える遅延検出回路。

【請求項2】

前記保持手段は、前記基準信号が前記クロック信号に同期して前記第1のレベルから前記第2のレベルに変化してから、前記クロック信号の一周期経過後に、複数の前記遅延手段の前記出力信号を保持する請求項1に記載の遅延検出回路。

【請求項3】

前記保持手段が保持した複数の前記遅延手段の前記出力信号に、前記第1及び第2のレベルの前記出力信号が含まれている場合、前記保持手段に入力される信号を前記遅延手段の前記出力信号から、前記保持手段の出力信号に切り換える選択手段をさらに備える請求項1又は2に記載の遅延検出回路。

【請求項4】

クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期は前記第2のレベルが維持される基準信号を生成する基準信号生成手段と、

電源から基準電圧が印加され、多段接続された複数の遅延手段を有し、前記基準信号が入力される遅延チェーンと、

前記クロック信号に同期して、複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する保持手段と、

前記遅延情報に基づいて、前記電源が出力する前記基準電圧を制御する制御手段と、

を備える電源電圧設定回路。

【請求項5】

前記制御手段は、前記基準信号が前記クロック信号に同期して前記第1のレベルから前記第2のレベルに変化してから、前記保持手段が前記クロック信号に同期して複数の前記出力信号を保持するまでの時間を、前記遅延情報に応じた前記遅延手段の段数で除することにより、前記遅延手段の遅延値を算出し、当該遅延値に基づいて、前記電源が出力する前記基準電圧を制御する請求項4に記載の電源電圧設定回路。

【請求項6】

多段接続された複数の遅延手段を有する遅延チェーンを備える遅延検出回路の制御方法であって、

クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくとも前記クロック信号の一周期の間は前記第2のレベルが維持される基準信号を生成し、

前記基準信号を前記遅延チェーンに入力し、

前記クロック信号に同期して複数の前記遅延手段の出力信号を保持し、前記遅延手段の遅延情報を出力する遅延検出回路の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−21494(P2013−21494A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2011−153037(P2011−153037)

【出願日】平成23年7月11日(2011.7.11)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成23年7月11日(2011.7.11)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]