遊技機

【課題】サブ制御装置のROM等の記憶媒体が交換されたことを、より確実に把握可能な遊技機を提供する。

【解決手段】認証用記憶媒体190は第1サブ記憶媒体150に記憶された所定の固有データに基づいて定められる基本認証データを予め記憶し、メインCPU110は、チェックコマンドを第2制御部102Bへ送信するとともに、メインCPU110が送信したチェックコマンドは、第2サブCPU170のみが受信可能とし、メインCPU110が送信したチェックコマンドを第2サブCPU170が受信したことを条件に、基本認証データと、当該時点で第1制御部102Aが備えている第1サブ記憶媒体150に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かを判断し、一致していない場合に異常と判定する。

【解決手段】認証用記憶媒体190は第1サブ記憶媒体150に記憶された所定の固有データに基づいて定められる基本認証データを予め記憶し、メインCPU110は、チェックコマンドを第2制御部102Bへ送信するとともに、メインCPU110が送信したチェックコマンドは、第2サブCPU170のみが受信可能とし、メインCPU110が送信したチェックコマンドを第2サブCPU170が受信したことを条件に、基本認証データと、当該時点で第1制御部102Aが備えている第1サブ記憶媒体150に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かを判断し、一致していない場合に異常と判定する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、遊技機に関し、詳しくは、CPU、ROM等の記憶媒体その他の電子部品が実装された基板を備えるとともに、この基板により構成される制御装置を備えた遊技機に関する。

【背景技術】

【0002】

従来、この種の遊技機、たとえばスロットマシンとしては、役の抽選、回転リールの回転及び停止制御等、主に遊技の進行を制御するメイン制御装置と、メイン制御装置が送信するコマンドやデータ等を受信することにより、所定の報知手段(たとえば、音声出力により報知を行うスピーカや、画像等の表示により報知を行う液晶表示装置等)を用いて行われる報知や演出を制御するサブ制御装置と、を備えているものが知られている。

このメイン制御装置及びサブ制御装置は、CPUやROM等の記憶媒体が実装された基板により構成されており、それぞれのROM(記憶媒体)に記憶されている遊技機に関するプログラムに基づいて、それぞれのCPUが当該プログラムに応じた遊技機に関する処理を実行するように形成されている。

【0003】

ここで、メイン制御装置のROMには、役抽選を実行するためのプログラムや、役の抽選確率を定めた役抽選テーブル等が記憶されており、また、サブ制御装置のROMには、役抽選の結果に関する報知を実行するためのプログラム等が記憶されている。各ROMに記憶されている上述のようなプログラムやデータは、スロットマシンの出玉に関して直接的に影響を及ぼすものであるため、不正に出玉を得ようと企むゴト師等により、正規のROMを上述やプログラムやデータを有利な内容に改竄した不正なROMに交換するという不正行為が行われるおそれが高かった。

そして、このような不正行為を抑止すべく、上述のような制御装置を構成する基板を収納するための基板ケースに収納した上で、当該基板ケースに封印シールを貼付したり、所定の封止具により基板ケースを封止したりすることにより、基板ケースが開放された場合の痕跡を残すことが可能なスロットマシンが考案されている。

【0004】

このようなスロットマシンは、下記の特許文献1に開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−19310号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、上述のようなスロットマシンにおいては、封印シールを特殊な薬品等を用いて痕跡が残らないように剥がした後、再度、この封印シールを接着剤等で貼付して、封印シールが貼付されているように見せかけるといった処理や、封止具を破壊後が目立たないように取り外した後、再度、この封止具を接着剤等で取り付けて、封止具により封印されているように見せかけるといった処理が行われると、基板ケースが開放された痕跡を即座に見つけることができず、不正行為の発見が遅れ、ホール等に大きな損害が発生するというおそれが生じていた。

また、各メーカーでは、遊技機の部品は汎用性や量産性が高められており、基板ケースの金型が複数機種について共通とすることが多いため、金型のデッドコピーによる偽物の基板ケースが製作されることにより、大規模に不正行為が行われるというおそれも生じていた。

【0007】

さらに、近年、所定期間の遊技中において、当選した所定の役を構成する図柄の組み合わせを所定の停止表示ラインに停止させるためのストップスイッチの操作態様を報知することにより、遊技者に対して利益を付与することが可能なアシスト遊技(ATゲーム)を備えたスロットマシンが増加している。そのため、特に、ストップスイッチの操作態様の報知を実行するためのプログラムが記憶されたサブ制御装置のROMについて、不正交換が行われるというおそれが顕著であった。

そこで、下記の発明は、上記した事情によりなされたものであり、サブ制御装置のROM等の記憶媒体が交換されたことを、より確実に把握可能な遊技機を提供することを目的とする。

【課題を解決するための手段】

【0008】

下記の発明は、上記した各目的を達成するためになされたものであり、各発明の特徴点を図面に示した発明の実施の形態を用いて、以下に説明する。

なお、符号は、発明の実施の形態において用いた符号を示し、本発明の技術的範囲を限定するものではない。

(第1の発明)

第1の発明は、遊技に関する処理を実行可能なメインCPU110を有するメイン制御装置101と、メインCPU110が送信するコマンドを受信可能であり、メインCPU110からのコマンドに応じた遊技に関する処理を実行するサブ制御装置102と、を備え、サブ制御装置102は、遊技に関するプログラムやデータを記憶した第1サブ記憶媒体150(サブ制御ROM151)、並びに、メインCPU110からのコマンド及び第1サブ記憶媒体150に記憶されたプログラムに基づき、実行する処理の内容を決定する第1サブCPU140を有する第1制御部102Aと、第1サブCPU140が送信するコマンドを受信可能であるとともに、第1サブCPU140により決定される処理内容を実行するためのプログラムやデータを記憶した第2サブ記憶媒体180(画像制御ROM181)、第1サブCPU140からのコマンド及び第2サブ記憶媒体180に記憶されたプログラムに基づき、前記処理内容を実行する装置の動作を制御する第2サブCPU170、並びに、データの読み書きが可能な認証用記憶媒体190(第2サブRAM191)を有する第2制御部102Bと、を備えた遊技機であって、認証用記憶媒体190は、第1サブ記憶媒体150に記憶された所定の固有データに基づいて定められる基本認証データを予め記憶しており、メインCPU110は、予め定められた所定のタイミングで、所定のチェックコマンドを第2制御部102Bへ送信するとともに、メインCPU110が送信した前記チェックコマンドは、第2サブCPU170のみが受信可能となっており、メインCPU110が送信した前記チェックコマンドを第2サブCPU170が受信したことを条件に、認証用記憶媒体190に記憶された基本認証データと、当該時点で第1制御部102Aが備えている第1サブ記憶媒体150に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かを判断し、一致していない場合に異常と判定するように形成されていることを特徴とする。

【0009】

ここで、遊技機としては、上述のようなメイン制御装置101及びサブ制御装置102等の構成を備えているものであれば、特に限定されるものではない。たとえば、遊技機には、遊技媒体として遊技球を用いて遊技が行われるパチンコ遊技機、遊技媒体として遊技メダルを用いて遊技が行われるスロットマシン、又は、遊技媒体として遊技球を用いてスロットマシンと同様の遊技が行われるパロット(登録商標)遊技機等が含まれる。

また、メイン制御装置101及びサブ制御装置102は、それぞれ、種々の電子部品を搭載した基板(メイン基板、サブ基板)により構成されるものであって、これらの基板を収納するための基板ケースに収納したものである。また、各制御装置は、1枚の基板により構成してもよいし、また、電気的に接続された複数枚の基板により構成してもよい。すなわち、1枚の基板により構成する場合には、当該基板上にすべての電子部品を搭載することができる。また、複数枚の基板により構成する場合には、これらの基板同士を電気的に接続した上で、それぞれの基板上に電子部品を搭載することができる。

【0010】

また、本発明における第1サブ記憶媒体150や第2サブ記憶媒体180は、基板上に搭載される記憶媒体であり、たとえば、ROM、RAM等のメモリー等が含まれる。

また、認証用記憶媒体190は、データの読み書きが可能な記憶媒体であり、たとえば、RAM等により構成することができる。また、遊技に関するデータを一時的に保存するために備えられる所定のRAMを、認証用記憶媒体190として共用してもよく、また、前記RAMとは別個に、認証用記憶媒体190として用いるRAMを備えていてもよい。

また、基本認証データは、第1サブ記憶媒体150に記憶された所定の固有データに基づいて定められるものであり、第1サブ記憶媒体150を認証するための認証データである。

【0011】

ここで、所定の固有データとは、第1サブ記憶媒体150ごとに特有のデータであり、すなわち、異なる第1サブ記憶媒体150においては互いに異なる内容(非同一の内容)となるデータである。そして、このような固有データにより定められる基本認証データも、第1サブ記憶媒体150ごとにそれぞれ異なる内容となる。したがって、複数の基本認証データを比較して内容が一致している場合には、これらの基本認証データは同一の第1サブ記憶媒体150に基づくものであると判断することができる。これに対して、複数の基本認証データが一致していない場合には、これらの基本認証データは異なる第1サブ記憶媒体150に基づくものであると判断することができる。すなわち、基本認証データが一致するか否かの判断結果により、データ元の第1サブ記憶媒体150が同一であるか否かを判断することができる。

【0012】

ここで、上述の固有データとしては、たとえば、遊技機ごとの抽選内容に関するデータ(スロットマシンであれば、たとえば、役のコード、役の当選となる乱数値、演出データのコード等、また、パチンコ遊技機であれば、たとえば、大当たりとなる乱数値、演出データのコード等)や、第1サブ記憶媒体150に記憶されているデータについてのチェックサムの値等を用いることができる。

また、本発明においては、1の固有データの内容をそのまま基本認証データとして定めることもできるし、複数の固有データを組み合わせた内容を基本認証データとして定めることもできる。また、1の固有データや複数の固有データについて所定の演算を行って得られた内容を基本認証データとして定めてもよい。

【0013】

また、本発明においては、メインCPU110が所定のチェックコマンドを第2制御部102Bへ送信するが、当該チェックコマンドは、第2サブCPU170のみが受信可能に形成されている。

たとえば、当該チェックコマンドの送受信を直接行うための特有の通信路を設け、この通信路により当該チェックコマンドを送信することで、当該チェックコマンドを第2サブCPU170のみが受信可能となるように形成することができる。

具体的には、本発明に係る遊技機では、一般的なコマンドやデータの通信路として、メインCPU110から第1制御部102Aへの通信路、及び、第1制御部102Aから第2制御部102Bへの通信路(送受信用ポート)を設けられるが、この他に、メインCPU110と第2制御部102Bとを直接接続することで、メインCPU110から第2制御部102Bへの直接的な通信が可能なチェックコマンド用の通信路を新設する。このように形成することで、一般的なコマンドやデータは、メインCPU110から第1制御部102Aを経由して第2制御部102Bへ送信されるものの、チェックコマンドは、メインCPU110から第2制御部102Bへ直接送信される。これにより、第2サブCPU170のみがチェックコマンドを受信可能となる。

【0014】

また、一般的なコマンドやデータの送受信を行うための通信路を共用して、この通信路によりチェックコマンドを送信するものの、当該チェックコマンドを送信する場合には、一般的なコマンドやデータの送受信時とは異なる固有のストローブ信号を送信し、これに基づいて、当該チェックコマンドを第2サブCPU170のみ受信可能となるように形成することもできる。

具体的には、一般的なコマンドやデータ、及び、チェックコマンドはいずれも、メインCPU110から第1制御部102Aを経由して第2制御部102Bへ送信されるようになっているものの、一般的なコマンドやデータを送信する場合には、所定のストローブ信号を送信し、また、チェックコマンドを送信する場合には、この所定のストローブ信号とは異なる固有のストローブ信号を送信するように設定しておく。そして、第1制御部102Aでは、固有のストローブ信号を受信しても、これに伴って送信されるチェックコマンドを受信しないように設定するとともに、第2制御部102Bでは、固有のストローブ信号を受信したときに、これに伴って送信されるチェックコマンドを受信するように設定しておく。これにより、第2サブCPU170のみがチェックコマンドを受信可能となる。

【0015】

また、上述のように固有のストローブ信号を設定するのではなく、第2制御部102Bの受信ポートがチェックコマンドを受信した場合のみ、当該受信が行われたと判断するように形成してもよい。

また、メインCPU110がチェックコマンドを送信する所定のタイミングは、特に限定されるものではなく、たとえば、電源断から復帰した時点、所定のリセット操作により異常状態が解除された時点、設定値の変更が完了した時点等とすることができる。換言すれば、第1サブ記憶媒体150の交換が行われた可能性が高いタイミングとすることができる。

【0016】

(作用・効果)

本発明に係る遊技機においては、第2制御部102Bに備えられた認証用記憶媒体190に、第1サブ記憶媒体150に記憶された所定の固有データに基づいて定められる基本認証データが記憶されている。また、メインCPU110から送信されるチェックコマンドは、第2制御部102Bにおける第2サブCPU170のみが受信するようになっている。そして、第2サブCPU170がチェックコマンドを受信したことを条件に、認証用記憶媒体190に記憶された基本認証データと、当該時点で第1制御部102Aが備えている第1サブ記憶媒体150に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かが判断される。そして、一致していない場合には異常と判断される。

【0017】

すなわち、本発明に係る遊技機によれば、第2サブCPU170がチェックコマンドを受信すると、この時点での第1サブ記憶媒体150に基づく認証データであるチェック用認証データと、認証用記憶媒体190に予め記憶されている基本認証データとが比較される。ここで、第1サブ記憶媒体150が交換されていなければ、チェック用認証データと予め記憶されている基本認証データとは一致することとなるが、第1サブ記憶媒体150が交換されていると、チェック用認証データと予め記憶されている基本認証データとは一致しないこととなる。

これにより、サブ制御装置102のROM等の記憶媒体(第1サブ記憶媒体150)が交換されたことを、より確実に把握することができるのである。

【0018】

また、本発明に係る遊技機によれば、第2サブCPU170のみが受信可能なチェックコマンドに基づいて、第2サブCPU170が上述のようなチェックを行うため、不正行為を行うゴト師等は、不正な交換を行うメリットの高い第1サブ記憶媒体150について解析を行ったのみでは、上述のようなチェックの存在に気付かない。したがって、ゴト師等にとっては、このようなチェックへの対応が困難となるため、効果的に不正交換を抑止することができるのである。

(第2の発明)

第2の発明は、上記した第1の発明の特徴に加え、メインCPU110は、前記所定のタイミングで、チェック用認証データを第2制御部102Bへ送信させるためのチェック用送信コマンドを第1サブCPU140へ送信し、第2サブCPU170は、第1サブCPU140が送信したチェック用認証データを受信したことを条件に、基本認証データとチェック用認証データとが一致しているか否かを判断するように形成されていることを特徴とする。

【0019】

(作用・効果)

本発明に係る遊技機によれば、第2サブCPU170は、第1サブCPU140によりチェック用認証データが送信されてくるのを待って、基本認証データとチェック用認証データとの一致を判断する。したがって、第2サブCPU170は、当該判断を行うにあたり、自発的にチェック用認証データを取得する必要が無くなるため、第2サブCPU170の処理負担を軽減することができるのである。

(第3の発明)

第3の発明は、上記した第2の発明の特徴に加え、メインCPU110が送信したチェックコマンドを第2サブCPU170が受信した後、予め定められた所定時間内に、第1サブCPU140が送信したチェック用認証データを第2サブCPU170が受信できなかった場合に異常と判定するように形成されていることを特徴とする。

【0020】

(作用・効果)

本発明に係る遊技機によれば、第1サブCPU140が送信したチェック用認証データを、所定時間内に第2サブCPU170が受信できないときには、異常と判定されるため、チェック用認証データの送信エラーの発生をも把握することができるのである。

(第4の発明)

第4の発明は、上記した第1、第2又は第3の発明の特徴に加え、認証用記憶媒体190に基本認証データが記憶されていない初期状態において、予め定められた所定の初期設定条件を満たすことを契機として、基本認証データを第2制御部102Bへ送信させるための基本認証データ送信コマンドを第1サブCPU140へ送信し、かつ、第1サブCPU140が送信した基本認証データを認証用記憶媒体190に記憶させるための基本認証データ記憶コマンドを第2サブCPU170へ送信し、基本認証データ記憶コマンドを第2サブCPU170が受信し、かつ、第1サブCPU140が送信した基本認証データを第2サブCPU170が受信した場合に、認証用記憶媒体190に基本認証データを記憶するように形成されていることを特徴とする。

【0021】

ここで、所定の初期設定条件としては、たとえば、最初の主電源投入時やリセット時のみに行われる所定のプログラムが実行されること、所定期間内に予め定められた操作態様や操作順序でスイッチ操作が行われること等が挙げられる。そして、これらの場合には、遊技機に備えられているメイン制御装置101が、基本認証データ送信コマンドを第1サブCPU140へ送信するように形成することができる。

また、所定の初期設定条件としては、たとえば、遊技機が工場から出荷される前に正常に動作するか否か等の出荷検査が行われる場合には、この検査中にのみ行われる所定の処理が実行されることを定めることもできる。なお、この場合には、検査のために用いられる検査用メイン制御装置が、基本認証データ送信コマンドを第1サブCPU140へ送信するように形成することもできる。

【0022】

(作用・効果)

本発明に係る遊技機においては、認証用記憶媒体190に基本認証データが記憶されていない初期状態において、第2サブCPU170が、基本認証データ記憶コマンドを受信し、かつ、第1サブCPU140が送信した基本認証データを受信した場合に、認証用記憶媒体190に基本認証データが記憶されるようになっている。

すなわち、本発明に係る遊技機によれば、上述の条件を満たさなければ、認証用記憶媒体190に基本認証データが記憶されないため、認証用記憶媒体190に記憶された基本認証データの改竄を極めて困難にすることができるのである。

【発明の効果】

【0023】

本発明は、以上のように構成されているので、以下に記載されるような効果を奏する。

すなわち、本発明によれば、サブ制御装置のROM等の記憶媒体が交換されたことを、より確実に把握可能な遊技機を提供することができる。

【図面の簡単な説明】

【0024】

【図1】本発明の形態であって、スロットマシンを示す外観正面図である。

【図2】本発明の形態であって、スロットマシンの制御装置の入力及び出力の概略を示すブロック図である。

【図3】本発明の形態であって、スロットマシンのメイン制御装置及びサブ制御装置の概略を示すブロック図である。

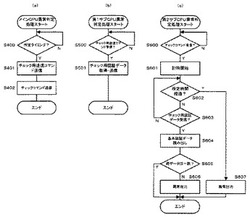

【図4】本発明の形態であって、基本認証データの初期設定処理の概略を示すフローである。

【図5】本発明の形態であって、基本認証データとチェック用認証データとが一致しているか否かを判定する異常判定処理の概略を示すフローである。

【発明を実施するための形態】

【0025】

以下、本発明を実施するための形態を図面を参照しつつ説明する。

(スロットマシン10)

本形態に係る遊技機は、遊技媒体として円板状の遊技メダルを使用するスロットマシン10である。

このスロットマシン10は、図1に示すように、正面側(スロットマシン10から見て、スロットマシン10と対向する遊技者の方向)に開口する箱状の筐体20と、この筐体20の正面開口を開閉可能に塞ぐ前扉30とから構成されている。

(筐体20)

筺体20には、特に図示していないが、スロットマシン10の作動を制御するための基板を備えたメイン基板ユニット、複数の回転リール25を備えたリールユニット21、遊技メダルを貯留するとともに役を構成する図柄51の組み合わせの停止表示時等に遊技メダルを払い出すためのホッパーユニット27、スロットマシン10に備えられた各種装置に電力を供給するための電源装置28(主電源)等が設置されている。

【0026】

メイン基板ユニットには、IC等の各種電子部品を搭載したメイン基板が収納されている。メイン基板は、スロットマシン10の作動を制御する制御装置100のうち、メイン制御装置101を構成するものであり、具体的には、スロットマシン10の遊技に関する制御を行うものとなっている。

リールユニット21は、スロットマシン10の遊技に用いられるメインの装置であり、枠体に固定された3個のステッピングモーター(図示しておらず)と、各ステッピングモーターの回転軸に固定された3個の回転リール25とから構成されている。具体的には、この回転リール25は、図1の向かって左側に位置する左リール22と、図1の向かって右側に位置する右リール24と、この左リール22及び右リール24の間に位置する中リール23とからなるものである。また、特に図示していないが、各回転リール25の周囲には、それぞれ21個の図柄51が付されている。また、これらの回転リール25は、前記ステッピングモーターの回転軸を中心として、後述する表示窓34内を回転リール25の図柄51が上側から下側へ向けて通過するように、回転する。

【0027】

(前扉30)

前扉30の前面上部には、図1に示すように、遊技状態に応じて点灯したり、消灯したりすることで各種演出や各種異常状態の報知を行うためのランプ52や、液晶表示装置53等を備えた装飾部31が設けられている。

また、前扉30の下部中央には、筐体20に設けられたホッパーユニット27から遊技メダルを払い出すためのメダル払出口40が設けられ、メダル払出口40の両側には、音声を出力するためのスピーカ54がそれぞれ1つずつ設けられている。

また、前扉30の裏面には、特に図示していないが、IC等の各種電子部品を搭載した基板であるサブ基板が収納されたサブ基板ユニットが設けられている。サブ基板は、スロットマシン10の作動を制御する制御装置100のうち、演出や報知に関する制御を行うためのサブ制御装置102を構成するものである。

【0028】

また、前扉30の前面の略中央には、正面側に突出する操作部33が備えられている。

この操作部33には、遊技を開始するにあたり遊技メダルをベットすべく、遊技メダルを投入するためのメダル投入口44、スロットマシン10に電子的に貯留されているメダルであるクレジットメダルを遊技メダルのベットに代えるためのベットスイッチ(遊技メダル1枚のベットが可能なシングルベットスイッチ36a、遊技を開始するためにベット可能な最大枚数である遊技メダル3枚のベットが可能なマックスベットスイッチ36b)、クレジットメダルを精算するための精算スイッチ39、3個すべての回転リール25の回転を開始させるためのレバー状のスタートスイッチ37、及び、各回転リール25に対応するとともに、各回転リール25の回転をそれぞれ別個に停止させるための3個のストップスイッチ38が設けられている。

【0029】

また、前扉30における装飾部31と操作部33との間には、筐体20に設けられた3個の回転リール25の図柄を視認可能な表示窓34が形成されている。

表示窓34は、3個の回転リール25の前方に設けられており、3個すべての回転リール25の回転が停止した際に、表示窓34内における、それぞれの回転リール25に対応する表示位置(上段、中段及び下段)にそれぞれ図柄が表示される。すなわち、表示窓34内に、縦3列横3行に配列した合計9個の図柄が表示されることとなる。

また、本形態に係るスロットマシン10は、特に図示していないが、左リール22、中リール23、及び、右リール24が停止した状態で、各回転リール25ごとの、表示窓34内におけるいずれか一の図柄の停止位置を一直線に結んで構成される計5本の停止表示ラインを有している。

【0030】

そして、1回の遊技を開始するために遊技メダルをベットすると、停止表示ラインが有効化される。そして、役抽選手段(特に図示しておらず)の抽選の結果、所定の役に当選するとともに、有効化された停止表示ラインのいずれかに、当該役を構成する図柄の組み合わせが停止すると、役に応じた利益(たとえば、所定枚数の遊技メダルの払い出しや特別遊技の実行等)が付与される。

また、図1に示すように、前扉30の裏面における、メダル投入口44の下部に対応する位置には、このメダル投入口44から投入された遊技メダルの正偽を判断するためのメダルセレクタ43、及び、このメダルセレクタ43により適正な遊技メダルであると判断された遊技メダルを検知するためのメダルセンサ35が設けられている。

【0031】

なお、本形態に係るスロットマシン10には、後述するサブ制御ROM151(第1サブ記憶媒体150)が交換されたことを報知するための異常報知装置55が接続されている。この異常報知装置55としては、スロットマシン10に直接的に設けられた装置(演出用のランプ52とは別個に設けられた警告灯(警告ランプ)、所定の警告音を出力するための警告音出力装置(警報スピーカ)等)を用いることができる。

また、この異常報知装置55としては、スロットマシン10に直接的に設けられた装置を用いるのではなく、スロットマシン10とは別体の装置(スロットマシン10が設置されるシマに設けられたランプや監視モニター、スロットマシン10の出玉状況等を管理するサーバー用のモニター等)を用いることができる。具体的には、これらの装置とスロットマシン10とを、所定の接続手段(通信ケーブル、無線通信装置等)により接続し、サブ制御ROM151が取り外されたと判定された場合にスロットマシン10から出力される信号等に基づいて、上述の装置において報知を行うように設定することができる。

【0032】

(制御装置100)

制御装置100は、上述の如く、スロットマシン10の作動を制御するためのものであり、メイン制御装置101及びサブ制御装置102から構成されるものとなっている。

また、メイン制御装置101及びサブ制御装置102には、これらの装置に対して各種信号等を入力可能な入力手段(メダルセンサ35、シングルベットスイッチ36a、マックスベットスイッチ36b、スタートスイッチ37、ストップスイッチ38、精算スイッチ39等)、入力手段による入力等に基づいた制御の結果を出力可能な出力手段(リールユニット21、ホッパーユニット27、ランプ52、液晶表示装置53、スピーカ54、異常報知装置55等)が接続されている。また、メイン制御装置101及びサブ制御装置102は、後述するCPUが後述するROMに記憶されたプログラムを読み込むことで、各種制御手段として機能する。

【0033】

また、メイン制御装置101とサブ制御装置102との間では、これらを構成する基板に設けられた後述の送信部及び受信部により、所定のコマンドやデータの送信及び受信ができるようになっているが、メイン制御装置101からサブ制御装置102への一方へ向けてのみコマンドやデータが送信され、サブ制御装置102からメイン制御装置101へ向けてはコマンドやデータが送信されないようになっている。

そして、メイン制御装置101は、スタートスイッチ37及びストップスイッチ38の操作により、役の抽選、回転リール25の回転及び停止の制御、並びに遊技メダルの払出し等、遊技の進行に関する制御等を行い、また、サブ制御装置102は、メイン制御装置101から送信されるコマンドやデータに基づき、これらの送信内容に対応した遊技に関する演出や報知の制御等を行う。

【0034】

また、本形態のサブ制御装置102においては、当該サブ制御装置102を構成する第1制御部102Aのサブ制御ROM151(第1サブ記憶媒体150)が交換されたことを検知できるように形成されている。当該検知については、後程、詳述する。

(メイン制御装置101)

メイン制御装置101は、上述の如く、メイン基板により構成されている。

そして、このメイン基板には、図3に示すように、遊技に関するプログラムやデータが記憶されたメインROM120、メインROM120に記憶されたプログラム等に基づいて遊技の進行に関する制御を行うメインCPU110、読み書き可能であって遊技の進行に関する制御を行うためのデータ等を一時的に記憶するメインRAM130等、種々の電子部品が備えられている。

【0035】

また、メインCPU110には、図3に示すように、後述するサブ制御装置102の第1制御部102Aにコマンドやデータ等を送信するための第1送信部111A、及び、後述するサブ制御装置102の第2制御部102Bに特定のコマンド(後述のチェックコマンド、基本認証データ記憶コマンド等)やデータ等を送信するための第2送信部111Bが設けられている。

なお、本形態においては、メインCPU110として、インターフェースポートが内臓されたCPUを採用することができ、この内臓されているインターフェースポートにより、上述の第1送信部111A及び第1送信部111bを構成することができる。また、メイン制御装置101内に別途インターフェース回路を形成し、このインターフェース回路により、上述の送信部の全部又は一部を構成してもよい。

【0036】

また、本形態においては、後述する如く、第1送信部111Aから第1制御部102Aへの通信路及び第2送信部111Bから第2制御部102Bへの通信路をそれぞれ別個独立に形成しているが、第1送信部111Aから第1制御部102Aへの通信路の一部及び第1制御部102Aから第2制御部102Bへの通信路により、第2送信部111Bを構成してもよい。

また、メインCPU110から第1制御部102Aを経由して第2制御部102Bまで至る通信路のみを形成し、第1送信部111A及び第2送信部111Bがこれを共通に利用して、データ等の内容により、第1制御部102A又は第2制御部102Bのいずれか一方のみに送信可能となるように形成してもよい。

【0037】

(サブ制御装置102)

サブ制御装置102は、メイン制御装置101から送信されるコマンドやデータ等を受信することで、これらのコマンドやデータ等に基づいて、報知や演出の内容を決定する第1制御部102Aと、この第1制御部102Aから送信されるコマンドに基づいて、第1制御部102Aで決定された報知や演出の内容を液晶表示装置53やスピーカ54に実行させる第2制御部102Bと、から構成されている(図2及び図3参照)。

また、サブ制御装置102は、上述の如く、サブ基板により構成されている。

そして、このサブ基板には、図3に示すように、上述の第1制御部102A及び第2制御部102Bを構成する種々の電子部品が備えられている。

【0038】

なお、本形態における第2制御部102Bの第2サブCPU170は、第1制御部102Aを構成する後述のサブ制御ROM151(第1サブ記憶媒体150)が交換されたか否かを検出できるように形成されている。当該検出については、後述する。

(第1制御部102A及び第2制御部102Bの構成)

(1)第1制御部102A

図3に示すように、サブ基板には、第1制御部102Aを構成する電子部品として、報知や演出の内容を決定するためのプログラムやデータが記憶された第1サブ記憶媒体150としてのサブ制御ROM151、メインCPU110からのコマンド及びサブ制御ROM151に記憶されたプログラム等に基づいて報知や演出の内容を決定する第1サブCPU140、及び、読み書き可能であって報知や演出に関するデータ等を一時的に記憶する第1サブRAM160等が備えられている。

【0039】

また、第1サブCPU140には、図3に示すように、ランプ52やLED等の演出装置が接続されており、第1サブCPU140は直接、これらの演出装置に報知や演出の内容を実行させることができるようになっている。

さらに、第1サブCPU140には、図3に示すように、メインCPU110の第1送信部111Aにより送信されるコマンド等を受信するための第1受信部141A、及び、後述するサブ制御装置102の第2制御部102Bとの間でコマンドやデータ等の送受信を行うための第1サブ間送受信部141Bが設けられている。

なお、本形態においては、第1サブCPU140として、インターフェースポートが内臓されたCPUを採用することができ、この内臓されているインターフェースポートにより、上述の第1受信部141A及び第1サブ間送受信部141Bを構成することができる。また、第1制御部102A内に別途インターフェース回路を形成し、このインターフェース回路により、上述の送受信部の全部又は一部を構成してもよい。

【0040】

(2)第2制御部102B

図3に示すように、サブ基板には、第2制御部102Bを構成する電子部品として、液晶表示装置53の動作を制御するためのプログラム等が記憶された第2サブ記憶媒体180としての画像制御ROM181、画像制御ROM181に記憶されたプログラム等に基づく液晶表示装置53の動作の制御(後述するVDP200の制御)や、後述するサウンドチップ220の制御を行う第2サブCPU170、読み書き可能であって液晶表示装置53等の制御に関するデータ等を一時的に記憶する第2サブRAM191(認証用記憶媒体190)、液晶表示装置53に表示する画像や文字のデータが記憶されたキャラクタROM210、液晶表示装置53における表示データ等を記憶するVRAM211、スピーカ54から出力する音声のデータが記憶されたサウンドROM230、及び、スピーカ54からの音声出力を実行するサウンドチップ220等が備えられている。

【0041】

そして、第2サブCPU170には、VDP200やサウンドチップ230を介して、液晶表示装置53やスピーカ54が接続されており、第2サブCPU170は、上述のVDP200やサウンドチップ230を制御することにより、液晶表示装置53やスピーカ54に報知や演出の内容を実行させることができるようになっている。

また、第2サブCPU170には、上述の異常報知装置55が接続されており、第2サブCPU170は、後述する如く、サブ制御ROM151(第1サブ記憶媒体150)が交換されたと判定された場合には、異常である旨を異常報知装置55に報知させることができるようになっている。

【0042】

さらに、第2サブCPU170には、図3に示すように、メインCPU110の第2送信部111Bにより送信される特定のコマンド(チェックコマンド、基本認証データ記憶コマンド)等を受信するための第2受信部171A、及び、サブ制御装置102の第1制御部102Aとの間でコマンドやデータ等の送受信を行うための第2サブ間送受信部171Bが設けられている。

なお、本形態においては、第2サブCPU170として、インターフェースポートが内臓されたCPUを採用することができ、この内臓されているインターフェースポートにより、上述の第2受信部171A及び第2サブ間送受信部171Bを構成することができる。また、第2制御部102B内に別途インターフェース回路を形成し、このインターフェース回路により、上述の送受信部の全部又は一部を構成してもよい。

【0043】

なお、本形態においては、特に図示していないが、第2サブRAM191は独立して電力供給が可能なバックアップ電源が接続されており、電源断によっても第2サブRAM191の内容は消去されないようになっている。また、この第2サブRAM191は、後述する如く、第1サブ記憶媒体150としてのサブ制御ROM151に記憶されている固有データに基づいて定められる基本認証データを記憶するための認証用記憶媒体190としても用いられる。

(3)メイン制御装置101、第1制御部102A及び第2制御部102B相互間の通信路

本形態においては、図3に示すように、メイン制御装置101のメインCPU110に設けられた第1送信部111Aと、サブ制御装置102の第1制御部102Aにおける第1サブCPU140に設けられた第1受信部141Aとが、互いに信号線により接続されることにより、通信路が形成されている。なお、この通信路においては、メインCPU110から第1サブCPU140の一方へ向けてのみ、コマンドやデータを送信できるようになっている。

【0044】

また、図3に示すように、メイン制御装置101のメインCPU110に設けられた第2送信部111Bと、サブ制御装置102の第2制御部102Bにおける第2サブCPU170に設けられた第2受信部171Aとが、互いに信号線により接続されることにより、通信路が形成されている。なお、この通信路においても、メインCPU110から第2サブCPU170の一方へ向けてのみ、コマンドやデータを送信できるようになっている。

また、図3に示すように、第1制御部102Aの第1サブ間送受信部141Bと、第2制御部102Bの第2サブ間送受信部171Bとが、互いに信号線により接続されることにより、通信路が形成されている。なお、この通信路においては、第1制御部102A及び第2制御部102B間で双方向に、コマンドやデータを送受信できるようになっている。

【0045】

本形態においては、これらの通信路は互いに独立して形成されている。

そして、メインCPU110及び第1サブCPU140間の通信路、並びに、第1制御部102A及び第2制御部102B間の通信路は、役抽選の結果を示すコマンドや報知内容を示すデータ等、一般的なコマンドやデータの送受信に用いられるようになっている。また、メインCPU110及び第2サブCPU170間の通信路は、サブ制御ROM151が交換されたか否かをチェックするためのチェックコマンド等、特定のコマンドやデータの送受信にのみ用いられるようになっている。換言すれば、メインCPU110及び第1サブCPU140間の通信路、並びに、第1制御部102A及び第2制御部102B間の通信路では、上述の特定のコマンド等は送信されないようになっており、また、メインCPU110及び第2サブCPU170間の通信路では、上述の一般的なコマンド等は送信されないようになっている。

【0046】

これにより、チェックコマンド等の特定のコマンドについては、第2サブCPU170のみが受信可能となっている。

(サブ制御ROM51が交換された旨の検出)

本形態においては、各CPUが所定の処理を実行することで、第1サブ記憶媒体150としてのサブ制御ROM151が交換されたか否かを検出できるように形成されている。

以下、各CPUが実行する所定の処理の内容について、説明する。

なお、当該処理は、各CPUが各ROMに記憶されている所定のプログラムを読み込むことで機能する各種制御手段により(すなわち、ソフトウェアにより)実行されるように形成することもできるし、CPUが有する演算器や比較器等の回路により(すなわち、ハードウェアにより)実行されるように形成することもできる。

【0047】

(1)基本認証データ送信要求処理

基本認証データ送信要求処理は、予め定められた所定の初期設定条件を満たしたことを契機として、メイン制御装置101のメインCPU110が、第1制御部102Aの第1サブCPU140に基本認証データを送信させるための基本認証データ送信コマンドを送信する処理である。

ここで、「基本認証データ」とは、第1制御部102Aのサブ制御ROM151(第1記憶媒体150)に記憶されている所定の固有データに基づいて定められるものであり、各サブ制御ROM151ごとに特有となるデータである。

【0048】

本形態においては、たとえば、サブ制御ROM151に記憶されている固有のデータである、所定の役(たとえば、遊技者に所定の利益を付与可能なBBゲームが開始されることとなるBBゲーム役)の抽選となる乱数値の範囲における最大値、及び、サブ制御ROM151のデータについてのチェックサムの値の合算値を基本認証データとして定めることができる。

なお、基本認証データを定めるための固有データとしては、上記のものに限定されず、たとえば、所定の役のコード、所定の演出データのコード等を用いることができる。また、基本認証データは、複数の固有データに基づいて定めるのではなく、1の固有データに基づいて定めることもできる。また、所定の演算を行うことにより得られる値を基本認証データとするのではなく、固有データそのものを基本認証データとして用いてもよい。

【0049】

また、「基本認証データ送信コマンド」は、基本認証データを、第2制御部102Bの第2サブCPU170へ送信する旨を指示するためのコマンドである。

すなわち、メインCPU110が、第1サブCPU140に基本認証データ送信コマンドを送信すると、当該コマンドを受信した第1サブCPU140は、基本認証データを第2サブCPU170へ送信する。

また、予め定められた所定の初期設定条件としては、たとえば、スロットマシン10に最初に主電源が投入されたときのみに行われる所定のプログラム(たとえば、ハードウェアやソフトウェアの異常があるか否かをチェックするための自己判定プログラム等)が実行されたこと等を設定することができる。

【0050】

このように設定した場合には、上記プログラムが実行されると、メインCPU110が、第1サブCPU140に基本認証データ送信コマンドを送信することとなる。

なお、初期設定条件としては、当該条件を満たすことが困難な内容となっていれば、上記の内容に限定されず、たとえば、スロットマシン10を所定のモード(たとえば、設定変更モード等)に切り替えてから、所定時間内に予め定められた操作態様や操作順序でスイッチ操作が行われること等を設定することもできる。

また、初期設定条件としては、スロットマシン10が出荷される前に正常に動作するか否か等の出荷検査が行われる場合には、この検査中にのみ行われる所定の処理が実行されることを定めることもできる。なお、検査用のメイン制御装置101を用いて前記検査が行われる場合には、この検査用のメイン制御装置101が、基本認証データ送信コマンドを第1サブCPU140へ送信するようにしてもよい。

【0051】

(2)基本認証データ記憶要求処理

基本認証データ記憶要求処理は、上述の初期設定条件を満たしたことを契機として、メインCPU110が、第2制御部102Bの第2サブCPU170に基本認証データ記憶コマンドを送信する処理である。

すなわち、メインCPU110は、上述の初期設定条件を満たしたことを契機として、基本認証データ送信コマンドとともに、基本認証データ記憶コマンドも送信する。

ここで、「基本認証データ記憶コマンド」は、基本認証データを記憶するための認証用記憶媒体190として用いられる第2サブRAM191に、第1サブCPU140により送信される基本認証データを記憶させる旨を指示するためのコマンドである。

【0052】

本形態においては、第2サブCPU170がこの基本認証データ記憶コマンドを受信すると、第2サブRAM191が書き込み可能状態となるように設定されている。そして、第2サブRAM191が書き込み可能状態となることにより、この第2サブRAM191にデータ等を書き込むことができるようになっている。

(3)基本認証データ送信処理

基本認証データ送信処理は、メインCPU110が送信した基本認証データ送信コマンドを第1サブCPU140が受信したことを契機として、当該第1サブCPU140が、第2サブCPU170に基本認証データを送信する処理である。

【0053】

なお、第1サブCPU140が基本認証データ送信コマンドを受信したときには、当該第1サブCPU140は、所定の書き込み手段により、第1サブRAM160に基本認証データを書き込むように設定してもよい。

(4)基本認証データ記憶処理

基本認証データ記憶処理は、第2サブRAM191に基本認証データが記憶されていない状態(初期状態)において、第2サブCPU170が基本認証データ記憶コマンドを受信し、かつ、第1サブCPU140が送信した基本認証データを受信した場合に、当該基本認証データを第2サブRAM191に記憶する処理である。すなわち、この基本認証データ記憶処理は、サブ制御ROM151が交換されたことをチェックするために用いる基本認証データを、スロットマシン10の初期状態において第2サブRAM191に記憶させるための処理である。

【0054】

そして、本形態においては、第2サブRAM191に基本認証データが記憶されている状態で、第2サブCPU170が基本認証データ記憶コマンド及び基本認証データを受信した場合には、第2サブRAM191に記憶されていた基本認証データを、受信した基本認証データに書き換えるように形成されている。

なお、第2サブRAM191に基本認証データが記憶されている状態で、第2サブCPU170が基本認証データ記憶コマンド及び基本認証データを受信した場合には、第2サブRAM191に記憶されていた基本認証データを、受信した基本認証データに書き換えないように形成することもできる。そして、このように形成した場合には、第2サブRAM191に記憶されていた基本認証データは、所定の操作態様でスイッチ操作を行う等、予め定められた消去条件を満たすことにより、第2サブRAM191から消去されるように設定することができる。

【0055】

(5)チェック用認証データ送信要求処理

チェック用認証データ送信要求処理は、予め定められた所定のタイミングで、メインCPU110が、第1制御部102Aの第1サブCPU140にチェック用認証データを送信させるためのチェック用送信コマンドを送信する処理である。

ここで、「チェック用認証データ」とは、当該時点で第1制御部102Aが備えているサブ制御ROM151(第1サブ記憶媒体150)に記憶された前記所定の固有データに基づいて定められるものであり、各サブ制御ROM151ごとに特有となるデータである。

そして、このチェック用認証データは基本認証データと同じ固有データに基づいて定められるものであるため、同一のサブ制御ROM151であれば、チェック用認証データ及び基本認証データは同一の内容となる。これに対して、異なるサブ制御ROM151であれば、チェック用認証データ及び基本認証データは異なる内容となる。

【0056】

また、「チェック用送信コマンド」は、チェック用認証データを、第2制御部102Bの第2サブCPU170へ送信する旨を指示するためのコマンドである。

すなわち、メインCPU110が、第1サブCPU140にチェック用送信コマンドを送信すると、当該コマンドを受信した第1サブCPU140は、チェック用認証データを第2サブCPU170へ送信する。

また、予め定められた所定のタイミングとしては、たとえば、電源断から復帰した時点、何らかの異常状態が発生した後、所定のリセット操作により当該異常状態が解除された時点、設定値の変更が完了した時点等、サブ制御ROM141の不正交換が行われる可能性が高い時点を設定することができる。

【0057】

(6)基本認証データチェック要求処理

基本認証データチェック要求処理は、上述の所定のタイミングで、メインCPU110が、第2制御部102Bの第2サブCPU170にチェックコマンドを送信する処理である。

すなわち、メインCPU110は、上述の所定のタイミングで、チェック用送信コマンドとともに、チェックコマンドも送信する。

ここで、「チェックコマンド」は、第2サブRAM191(認証用記憶媒体190)に記憶されている基本認証データと、第1サブCPU140により送信されるチェック用認証データとが一致しているか否かを判断させる旨を指示するためのコマンドである。

【0058】

本形態においては、このチェックコマンドに基づき第2サブCPU170に対して割込み入力が行われる。そして、第2サブCPU170がこのチェックコマンドを受信すると、第2サブCPU170が、第1サブCPU140により送信されるチェック用認証データの受信待ち状態となる。

なお、このチェックコマンドは特定のコマンドに該当するものであるため、第2送信部111B及び第2受信部171Aにより(すなわち、メインCPU110及び第2サブCPU170間の通信路により)、直接、メインCPU110から第2サブCPU170への送信が行われる。換言すれば、メインCPU110が送信するチェックコマンドは、第2サブCPU170のみが受信可能となっている。

【0059】

(7)チェック用認証データ送信処理

チェック用認証データ送信処理は、メインCPU110が送信したチェック用送信コマンドを第1サブCPU140が受信したことを契機として、当該第1サブCPU140が、第2サブCPU170にチェック用認証データを送信する処理である。

なお、第1サブRAM160が基本認証データを記憶するように設定していた場合には、第1サブCPU140がチェック用送信コマンドを受信したときに、チェック用認証データと、第1サブRAM160に記憶されている基本認証データとを、所定の比較手段により比較し、同一であれば第1サブRAM160に記憶されている基本認証データを第2サブCPU170に送信し、異なっていればチェック用認証データを第2サブCPU170に送信するようにしてもよい。

【0060】

(8)基本認証データ読み出し処理

基本認証データ読み出し処理は、第2サブCPU170がチェックコマンドを受信して上述の受信待ち状態となっているときに、第1サブCPU140により送信されるチェック用認証データを受信した場合に、第2サブCPU170が、第2サブRAM191(認証用記憶媒体190)に記憶されている基本認証データを、所定の読み出し手段により読み出す処理である。

また、本形態においては、第2サブCPU170がチェックコマンドを受信しておらず受信待ち状態となっていないときに、チェック用認証データを受信した場合には、第2サブCPU170は、第2サブRAM191に記憶されている基本認証データを読み出さないように設定されている。

【0061】

なお、この場合の処理としては、上記内容に限定されるものではない。たとえば、このチェック用認証データを一時的に所定の記憶手段(たとえば、第2サブRAM191)に記憶しておくとともに、予め定められた所定時間が経過するまでにチェックコマンドを受信したときには、第2サブCPU170が基本認証データを読み出し、前記所定時間が経過するまでにチェックコマンドを受信しなかったときには、第2サブCPU170が基本認証データを読み出さないように設定してもよい。

また、第2サブCPU170により基本認証データの読み出しが行われなかった場合には、異常と判定してその旨を報知してもよい。

【0062】

(9)データ比較判定処理

データ比較判定処理は、第2サブRAM191(認証用記憶媒体190)から読み出された基本認証データと、受信したチェック用認証データとを、所定の比較手段により比較し、第2サブCPU170が、基本認証データとチェック用認証データとが一致しているか否かを判定するものである。

上述の如く、同一のサブ制御ROM151であれば、基本認証データとチェック用認証データとは一致するものの、異なるサブ制御ROM151であれば、基本認証データとチェック用認証データとは一致しないこととなる。

【0063】

すなわち、基本認証データとチェック用認証データとが一致していれば、基本認証データが第2サブRAM191に記憶された時点において第1制御部102Aに備えられていたサブ制御ROM151と、チェック用認証データを送信する時点において第1制御部102Aに備えられていたサブ制御ROM151とが同一のものであると判断できる。これに対して、基本認証データとチェック用認証データとが一致していなければ、基本認証データが第2サブRAM191に記憶された時点において第1制御部102Aに備えられていたサブ制御ROM151と、チェック用認証データを送信する時点において第1制御部102Aに備えられていたサブ制御ROM151とが異なっている(すなわち、サブ制御ROM151が交換された)と判断できる。

【0064】

このように、基本認証データとチェック用認証データとが一致しているか否かを判断することにより、サブ制御ROM151が交換された旨を判定することができるようになっている。

(10)異常出力処理

異常出力処理は、上述のデータ比較判定処理において、基本認証データとチェック用認証データとが一致していないと判定された場合に、第2サブCPU170が、異常と判定するとともに、その旨を示すコマンドを液晶表示装置53や異常報知装置55等に送信する処理である。そして、液晶表示装置53や異常報知装置55が前記コマンドを受信すると、これらの装置において異常の報知が行われることとなる。

【0065】

すなわち、サブ制御ROM151が交換された場合、液晶表示装置53や異常放置装置55において異常の報知が行われることとなる。

また、本形態においては、メインCPU110が送信したチェックコマンドを第2サブCPU170が受信した後、予め定められた所定時間内(たとえば、5秒以内等)に、第1サブCPU140が送信したチェック用認証データを第2サブCPU170が受信できなかった場合(すなわち、通信エラーが発生したような場合)にも、第2サブCPU170が異常と判定し、液晶表示装置53や異常報知装置55において異常の報知が行われるようになっている。そして、この異常の報知は、サブ制御ROM151が交換されたことによる異常の報知とは異なる態様で報知されるようになっている。

【0066】

次に、上述のサブ制御ROM151が交換された旨の検出の概略について、図4及び図5に示したフローを用いて説明する。

まず、基本認証データを第2サブRAM191(認証用記憶媒体190)に記憶させるための初期時処理について、メインCPU110により行われる処理の概要を、図4(a)のフローを用いて説明する。

図4(a)に示すステップ100において、所定の初期設定条件(スロットマシン10に最初に主電源が投入されたときのみに行われる自己判定プログラムが実行されたこと)が満たされた場合、次のステップ101に進む。一方、満たされていない場合、ステップ100に戻る。

【0067】

ステップ101において、メインCPU110が、基本認証データ記憶コマンドを第2サブCPU170に送信する。そして、ステップ102に進む。

ステップ102において、メインCPU110が、基本認証データ送信コマンドを第1サブCPU140に送信する。そして、当該処理が終了する。

次に、第1サブCPU140により行われる処理の概要を、図4(b)のフローを用いて説明する。

図4(b)に示すステップ200において、メインCPU110が送信した基本認証データ送信コマンドを第1サブCPU140が受信した場合、次のステップ201に進む。一方、受信していない場合、ステップ200に戻る。

【0068】

ステップ201において、第1サブCPU140が、サブ制御ROM151(第1サブ記憶媒体150)に記憶された所定の固有データに基づく基本認証データを取得し(生成し)、この基本認証データを第2サブCPU170に送信する。そして、当該処理が終了する。

次に、第2サブCPU170により行われる処理の概要を、図4(c)のフローを用いて説明する。

図4(c)に示すステップ300において、メインCPU110が送信した基本認証データ記憶コマンドを第2サブCPU170が受信した場合、次のステップ301に進む。一方、受信していない場合、ステップ300に戻る。

【0069】

ステップ301において、所定のタイマーにより計時が開始される。そして、次のステップ302に進む。

ステップ302において、タイマーにより計時された時間が所定時間を超えた場合、当該処理が終了する。一方、所定時間を超えていない場合、次のステップ303に進む。

ステップ303において、第1サブCPU140が送信した基本認証データを受信した場合、次のステップ304に進む。一方、受信していない場合、ステップ302に進む。

ステップ304において、第2サブRAM191(認証用記憶媒体190)に既に基本認証データが記憶されている場合、ステップ306に進む。一方、基本認証データが記憶されていない場合、次のステップ305に進む。

【0070】

ステップ305において、基本認証データが、第2サブRAM191(認証用記憶媒体190)に記憶され、当該処理が終了する。

ステップ306において、第2サブRAM191(認証用記憶媒体190)に既に記憶されている基本認証データが、受信した基本認証データに書き換えられ、当該処理が終了する。

なお、初期設定条件として、スロットマシン10の出荷検査中にのみ行われる所定の処理の実行が定められており、検査用のメイン制御装置101が、基本認証データ送信コマンドを第1サブCPU140へ送信するように形成されている場合には、上述のステップ304の処理を行わず、基本認証データが第2サブRAM191(認証用記憶媒体190)に既に記憶されているか否かを問わず、第1サブCPU140が送信した基本認証データを、新たな基本認証データとして、常に、第2サブRAM191(認証用記憶媒体190)に設定(記憶)してもよい。

【0071】

これにより、管理者側が正規な手続きにより基本認証データを再設定する場合における作業を簡便なものとすることができる。

次に、チェック用認証データと基本認証データとが一致しているか否かを判定する異常判定処理について、メインCPU110により行われる処理の概要を、図5(a)のフローを用いて説明する。

図5(a)に示すステップ400において、当該遊技が予め定められた所定のタイミング(たとえば、電源断から復帰した時点等)である場合、次のステップ401に進む。一方、所定のタイミングで無い場合、ステップ400に戻る。

【0072】

ステップ401において、メインCPU110が、チェック用送信コマンドを第1サブCPU140に送信する。そして、ステップ402に進む。

ステップ402において、メインCPU110が、チェックコマンドを第2サブCPU170に送信する。そして、当該処理が終了する。

次に、第1サブCPU140により行われる処理の概要を、図5(b)のフローを用いて説明する。

図5(b)に示すステップ500において、メインCPU110が送信したチェック用送信コマンドを第1サブCPU140が受信した場合、次のステップ501に進む。一方、受信していない場合、ステップ200に戻る。

【0073】

ステップ501において、第1サブCPU140が、当該時点で第1制御部102Aに備えられているサブ制御ROM151(第1サブ記憶媒体150)に記憶された所定の固有データに基づくチェック用認証データを取得し(生成し)、このチェック用認証データを第2サブCPU170に送信する。そして、当該処理が終了する。

次に、第2サブCPU170により行われる処理の概要を、図5(c)のフローを用いて説明する。

図5(c)に示すステップ600において、メインCPU110が送信したチェックコマンドを第2サブCPU170が受信した場合、次のステップ601に進む。一方、受信していない場合、ステップ600に戻る。

【0074】

ステップ601において、所定のタイマーにより計時が開始される。そして、次のステップ602に進む。

ステップ602において、タイマーにより計時された時間が所定時間を超えた場合、ステップ607に進む。一方、所定時間を超えていない場合、次のステップ603に進む。

ステップ603において、第1サブCPU140が送信したチェック用認証データを受信した場合、次のステップ604に進む。一方、受信していない場合、ステップ602に進む。

ステップ604において、第2サブRAM191(認証用記憶媒体190)に既に記憶されている基本認証データが読み出される。そして、ステップ605に進む。

【0075】

ステップ605において、基本認証データとチェック用認証データとが一致しているか否か、すなわち、サブ制御ROM151が交換されたか否かを判定する。そして、一致していると判定された場合、当該処理が終了する。一方、一致していないと判定された場合、ステップ606に進む。

ステップ606において、基本認証データとチェック用認証データとが一致していない(サブ制御ROM151が交換された)旨を示す異常コマンドを出力する。そして、当該処理が終了する。

ステップ607において、第1サブCPU140が送信したチェック用認証データを所定時間内に第2サブCPU170が受信することができない旨を示す異常コマンドを出力する。そして、当該処理が終了する。

【0076】

(まとめ)

本形態に係るスロットマシン10では、第2制御部102Bに備えられた第2サブRAM191(認証用記憶媒体190)に、サブ制御ROM151(第1サブ記憶媒体150)に記憶された所定の固有データに基づいて定められる基本認証データが記憶されている。また、メインCPU110から送信されるチェックコマンドは、第2制御部102Bにおける第2サブCPU170のみが受信するようになっている。そして、第2サブCPU170がチェックコマンドを受信したことを条件に、第2サブRAM191に記憶された基本認証データと、当該時点で第1制御部102Aが備えているサブ制御ROM151に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かが判断される。そして、一致していない場合には異常と判断される。

【0077】

すなわち、本形態に係るスロットマシン10によれば、第2サブCPU170がチェックコマンドを受信すると、この時点でのサブ制御ROM151に基づく認証データであるチェック用認証データと、第2サブRAM191に予め記憶されている基本認証データとが比較される。ここで、サブ制御ROM151が交換されていなければ、チェック用認証データと予め記憶されている基本認証データとは一致することとなるが、サブ制御ROM151が交換されていると、チェック用認証データと予め記憶されている基本認証データとは一致しないこととなる。

これにより、サブ制御ROM151が交換された(取り外された)ことを、より確実に把握することができるのである。

【0078】

また、本形態に係るスロットマシン10によれば、第2サブCPU170のみが受信可能なチェックコマンドに基づいて、第2サブCPU170が上述のようなチェックを行うため、不正行為を行うゴト師等は、不正な交換を行うメリットの高いサブ制御ROM151について解析を行ったのみでは、上述のようなチェックの存在に気付かない。したがって、ゴト師等にとっては、このようなチェックへの対応が困難となるため、効果的に不正交換を抑止することができるのである。

また、本形態に係るスロットマシン10においては、第2サブCPU170は、第1サブCPU140によりチェック用認証データが送信されてくるのを待って、基本認証データとチェック用認証データとが一致するか否かを判断する。したがって、第2サブCPU170は、当該判断を行うにあたり、自発的にチェック用認証データを取得する必要が無くなるため、第2サブCPU170の処理負担を軽減することができるのである。

【0079】

また、本形態に係るスロットマシン10によれば、第1サブCPU140が送信したチェック用認証データを、所定時間内に第2サブCPU170が受信できないときには、異常と判定されるため、チェック用認証データの送信エラーの発生をも把握することができるのである。

また、本形態に係るスロットマシン10においては、第2サブRAM191に基本認証データが記憶されていない初期状態において、第2サブCPU170が、基本認証データ記憶コマンドを受信し、かつ、第1サブCPU140が送信した基本認証データを受信した場合に、第2サブRAM191に基本認証データが記憶されるようになっている。

【0080】

すなわち、本形態に係るスロットマシン10によれば、上述の条件を満たさなければ、第2サブRAM191に基本認証データが記憶されないため、第2サブRAM191に記憶された基本認証データの改竄を極めて困難にすることができるのである。

なお、上述の形態は、同様の構成の制御装置100を備えていれば、スロットマシン10以外の遊技機にも応用できる。たとえば、遊技媒体として遊技球を用いて遊技を行わせるパチンコ遊技機や、遊技媒体として遊技球を用いてスロットマシン10と同様の遊技を行わせるパロット(登録商標)遊技機、アレンジボール遊技機、雀球遊技機、カジノマシン等に使用してもよいものである。

【0081】

(変形例1)

上述の形態においては、メインCPU110及び第2サブCPU170間を直接的に通信可能な独立した通信路により、チェックコマンド等の特定のコマンドを送受信することで、第2サブCPU170のみがチェックコマンドを受信可能となるように形成されていたが、独立した通信路を設けるのではなく、一般的なコマンドやデータの送受信を行うための通信路を共通に利用して、第2サブCPU170のみがチェックコマンドを受信可能とすることもできる。

具体的には、一般的なコマンドやデータ、及び、チェックコマンドはいずれも、メインCPU110から第1制御部102Aを経由して第2制御部102Bへ至る通信路により、送信されるようになっているものの、一般的なコマンドやデータを送信する場合には、所定のストローブ信号を送信し、また、チェックコマンドを送信する場合には、この所定のストローブ信号とは異なる固有のストローブ信号を送信するように設定しておく。そして、第1制御部102Aでは、固有のストローブ信号を受信しても、これに伴って送信されるチェックコマンドを受信しないように設定するとともに、第2制御部102Bでは、固有のストローブ信号を受信したときに、これに伴って送信されるチェックコマンドを受信するように設定しておく。これにより、第2サブCPU170のみがチェックコマンドを受信可能とすることができる。

【0082】

また、上述のように固有のストローブ信号を設定するのではなく、たとえば、第1サブCPU140では利用されない所定のコマンド(送信準備コマンド)を設けておくとともに、メインCPU110がチェックコマンドを送信する場合には、その直前に送信準備コマンドを送信するように設定しておく。これにより、第2サブCPU170のみが送信準備コマンドを受信可能となる。そして、第2サブCPU170が送信準備コマンドを受信したときにのみ、その後に送信されるチェックコマンドを受信できるようにしてもよい。

このように形成した場合にも、上述の形態と同様の作用効果を奏するとともに、別個に通信路を設ける必要が無くなるため、ハードウェア資源を有効に利用することができることとなる。

【0083】

(変形例2)

上述の形態においては、メインCPU110が、チェック用認証データを第2サブCPU170へ送信する旨を指示するチェック用送信コマンドを、第1サブCPU140へ送信するようになっていたが、第2サブCPU170自ら、チェック用送信コマンドを第1サブCPU140へ送信するようにしてもよい。

なお、この場合には、第2サブCPU170は、初期時において備えられていたサブ制御ROM151のみが解読可能な暗号化データを付加したチェック用送信コマンドを、第1サブCPU140へ送信するように形成することが望ましい。これにより、サブ制御ROM151が交換された場合には、このチェック用送信コマンドを解読することができないこととなるため、チェック用認証データが第2サブCPU170へ送信されず、サブ制御ROM151の交換を確実に検知することができることとなる。

【符号の説明】

【0084】

10 スロットマシン

20 筐体 21 リールユニット

22 左リール 23 中リール

24 右リール 25 回転リール

27 ホッパーユニット 28 電源装置

30 前扉 31 装飾部

33 操作部 34 表示窓

35 メダルセンサ 36a シングルベットスイッチ

36b マックスベットスイッチ 37 スタートスイッチ

38 ストップスイッチ 39 精算スイッチ

40 メダル払出口 43 メダルセレクタ

44 メダル投入口 52 ランプ

53 液晶表示装置 54 スピーカ

55 異常報知装置

100 制御装置 101 メイン制御装置

102 サブ制御装置 102A 第1制御部

102B 第2制御部

110 メインCPU 111A 第1送信部

111B第2送信部 120 メインROM

130 メインRAM

140 第1サブCPU 141A 第1受信部

141B 第1サブ間送受信部 150 第1サブ記憶媒体

151 サブ制御ROM 160 第1サブRAM

170 第2サブCPU 171A 第2受信部

171B 第2サブ間送受信部 180 第2サブ記憶媒体

181 画像制御ROM 190 認証用記憶媒体

191 第2サブRAM 200 VDP

210 キャラクタROM 211 VRAM

220 サウンドチップ 230 サウンドROM

【技術分野】

【0001】

この発明は、遊技機に関し、詳しくは、CPU、ROM等の記憶媒体その他の電子部品が実装された基板を備えるとともに、この基板により構成される制御装置を備えた遊技機に関する。

【背景技術】

【0002】

従来、この種の遊技機、たとえばスロットマシンとしては、役の抽選、回転リールの回転及び停止制御等、主に遊技の進行を制御するメイン制御装置と、メイン制御装置が送信するコマンドやデータ等を受信することにより、所定の報知手段(たとえば、音声出力により報知を行うスピーカや、画像等の表示により報知を行う液晶表示装置等)を用いて行われる報知や演出を制御するサブ制御装置と、を備えているものが知られている。

このメイン制御装置及びサブ制御装置は、CPUやROM等の記憶媒体が実装された基板により構成されており、それぞれのROM(記憶媒体)に記憶されている遊技機に関するプログラムに基づいて、それぞれのCPUが当該プログラムに応じた遊技機に関する処理を実行するように形成されている。

【0003】

ここで、メイン制御装置のROMには、役抽選を実行するためのプログラムや、役の抽選確率を定めた役抽選テーブル等が記憶されており、また、サブ制御装置のROMには、役抽選の結果に関する報知を実行するためのプログラム等が記憶されている。各ROMに記憶されている上述のようなプログラムやデータは、スロットマシンの出玉に関して直接的に影響を及ぼすものであるため、不正に出玉を得ようと企むゴト師等により、正規のROMを上述やプログラムやデータを有利な内容に改竄した不正なROMに交換するという不正行為が行われるおそれが高かった。

そして、このような不正行為を抑止すべく、上述のような制御装置を構成する基板を収納するための基板ケースに収納した上で、当該基板ケースに封印シールを貼付したり、所定の封止具により基板ケースを封止したりすることにより、基板ケースが開放された場合の痕跡を残すことが可能なスロットマシンが考案されている。

【0004】

このようなスロットマシンは、下記の特許文献1に開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−19310号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、上述のようなスロットマシンにおいては、封印シールを特殊な薬品等を用いて痕跡が残らないように剥がした後、再度、この封印シールを接着剤等で貼付して、封印シールが貼付されているように見せかけるといった処理や、封止具を破壊後が目立たないように取り外した後、再度、この封止具を接着剤等で取り付けて、封止具により封印されているように見せかけるといった処理が行われると、基板ケースが開放された痕跡を即座に見つけることができず、不正行為の発見が遅れ、ホール等に大きな損害が発生するというおそれが生じていた。

また、各メーカーでは、遊技機の部品は汎用性や量産性が高められており、基板ケースの金型が複数機種について共通とすることが多いため、金型のデッドコピーによる偽物の基板ケースが製作されることにより、大規模に不正行為が行われるというおそれも生じていた。

【0007】

さらに、近年、所定期間の遊技中において、当選した所定の役を構成する図柄の組み合わせを所定の停止表示ラインに停止させるためのストップスイッチの操作態様を報知することにより、遊技者に対して利益を付与することが可能なアシスト遊技(ATゲーム)を備えたスロットマシンが増加している。そのため、特に、ストップスイッチの操作態様の報知を実行するためのプログラムが記憶されたサブ制御装置のROMについて、不正交換が行われるというおそれが顕著であった。

そこで、下記の発明は、上記した事情によりなされたものであり、サブ制御装置のROM等の記憶媒体が交換されたことを、より確実に把握可能な遊技機を提供することを目的とする。

【課題を解決するための手段】

【0008】

下記の発明は、上記した各目的を達成するためになされたものであり、各発明の特徴点を図面に示した発明の実施の形態を用いて、以下に説明する。

なお、符号は、発明の実施の形態において用いた符号を示し、本発明の技術的範囲を限定するものではない。

(第1の発明)

第1の発明は、遊技に関する処理を実行可能なメインCPU110を有するメイン制御装置101と、メインCPU110が送信するコマンドを受信可能であり、メインCPU110からのコマンドに応じた遊技に関する処理を実行するサブ制御装置102と、を備え、サブ制御装置102は、遊技に関するプログラムやデータを記憶した第1サブ記憶媒体150(サブ制御ROM151)、並びに、メインCPU110からのコマンド及び第1サブ記憶媒体150に記憶されたプログラムに基づき、実行する処理の内容を決定する第1サブCPU140を有する第1制御部102Aと、第1サブCPU140が送信するコマンドを受信可能であるとともに、第1サブCPU140により決定される処理内容を実行するためのプログラムやデータを記憶した第2サブ記憶媒体180(画像制御ROM181)、第1サブCPU140からのコマンド及び第2サブ記憶媒体180に記憶されたプログラムに基づき、前記処理内容を実行する装置の動作を制御する第2サブCPU170、並びに、データの読み書きが可能な認証用記憶媒体190(第2サブRAM191)を有する第2制御部102Bと、を備えた遊技機であって、認証用記憶媒体190は、第1サブ記憶媒体150に記憶された所定の固有データに基づいて定められる基本認証データを予め記憶しており、メインCPU110は、予め定められた所定のタイミングで、所定のチェックコマンドを第2制御部102Bへ送信するとともに、メインCPU110が送信した前記チェックコマンドは、第2サブCPU170のみが受信可能となっており、メインCPU110が送信した前記チェックコマンドを第2サブCPU170が受信したことを条件に、認証用記憶媒体190に記憶された基本認証データと、当該時点で第1制御部102Aが備えている第1サブ記憶媒体150に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かを判断し、一致していない場合に異常と判定するように形成されていることを特徴とする。

【0009】

ここで、遊技機としては、上述のようなメイン制御装置101及びサブ制御装置102等の構成を備えているものであれば、特に限定されるものではない。たとえば、遊技機には、遊技媒体として遊技球を用いて遊技が行われるパチンコ遊技機、遊技媒体として遊技メダルを用いて遊技が行われるスロットマシン、又は、遊技媒体として遊技球を用いてスロットマシンと同様の遊技が行われるパロット(登録商標)遊技機等が含まれる。

また、メイン制御装置101及びサブ制御装置102は、それぞれ、種々の電子部品を搭載した基板(メイン基板、サブ基板)により構成されるものであって、これらの基板を収納するための基板ケースに収納したものである。また、各制御装置は、1枚の基板により構成してもよいし、また、電気的に接続された複数枚の基板により構成してもよい。すなわち、1枚の基板により構成する場合には、当該基板上にすべての電子部品を搭載することができる。また、複数枚の基板により構成する場合には、これらの基板同士を電気的に接続した上で、それぞれの基板上に電子部品を搭載することができる。

【0010】

また、本発明における第1サブ記憶媒体150や第2サブ記憶媒体180は、基板上に搭載される記憶媒体であり、たとえば、ROM、RAM等のメモリー等が含まれる。

また、認証用記憶媒体190は、データの読み書きが可能な記憶媒体であり、たとえば、RAM等により構成することができる。また、遊技に関するデータを一時的に保存するために備えられる所定のRAMを、認証用記憶媒体190として共用してもよく、また、前記RAMとは別個に、認証用記憶媒体190として用いるRAMを備えていてもよい。

また、基本認証データは、第1サブ記憶媒体150に記憶された所定の固有データに基づいて定められるものであり、第1サブ記憶媒体150を認証するための認証データである。

【0011】

ここで、所定の固有データとは、第1サブ記憶媒体150ごとに特有のデータであり、すなわち、異なる第1サブ記憶媒体150においては互いに異なる内容(非同一の内容)となるデータである。そして、このような固有データにより定められる基本認証データも、第1サブ記憶媒体150ごとにそれぞれ異なる内容となる。したがって、複数の基本認証データを比較して内容が一致している場合には、これらの基本認証データは同一の第1サブ記憶媒体150に基づくものであると判断することができる。これに対して、複数の基本認証データが一致していない場合には、これらの基本認証データは異なる第1サブ記憶媒体150に基づくものであると判断することができる。すなわち、基本認証データが一致するか否かの判断結果により、データ元の第1サブ記憶媒体150が同一であるか否かを判断することができる。

【0012】

ここで、上述の固有データとしては、たとえば、遊技機ごとの抽選内容に関するデータ(スロットマシンであれば、たとえば、役のコード、役の当選となる乱数値、演出データのコード等、また、パチンコ遊技機であれば、たとえば、大当たりとなる乱数値、演出データのコード等)や、第1サブ記憶媒体150に記憶されているデータについてのチェックサムの値等を用いることができる。

また、本発明においては、1の固有データの内容をそのまま基本認証データとして定めることもできるし、複数の固有データを組み合わせた内容を基本認証データとして定めることもできる。また、1の固有データや複数の固有データについて所定の演算を行って得られた内容を基本認証データとして定めてもよい。

【0013】

また、本発明においては、メインCPU110が所定のチェックコマンドを第2制御部102Bへ送信するが、当該チェックコマンドは、第2サブCPU170のみが受信可能に形成されている。

たとえば、当該チェックコマンドの送受信を直接行うための特有の通信路を設け、この通信路により当該チェックコマンドを送信することで、当該チェックコマンドを第2サブCPU170のみが受信可能となるように形成することができる。

具体的には、本発明に係る遊技機では、一般的なコマンドやデータの通信路として、メインCPU110から第1制御部102Aへの通信路、及び、第1制御部102Aから第2制御部102Bへの通信路(送受信用ポート)を設けられるが、この他に、メインCPU110と第2制御部102Bとを直接接続することで、メインCPU110から第2制御部102Bへの直接的な通信が可能なチェックコマンド用の通信路を新設する。このように形成することで、一般的なコマンドやデータは、メインCPU110から第1制御部102Aを経由して第2制御部102Bへ送信されるものの、チェックコマンドは、メインCPU110から第2制御部102Bへ直接送信される。これにより、第2サブCPU170のみがチェックコマンドを受信可能となる。

【0014】

また、一般的なコマンドやデータの送受信を行うための通信路を共用して、この通信路によりチェックコマンドを送信するものの、当該チェックコマンドを送信する場合には、一般的なコマンドやデータの送受信時とは異なる固有のストローブ信号を送信し、これに基づいて、当該チェックコマンドを第2サブCPU170のみ受信可能となるように形成することもできる。

具体的には、一般的なコマンドやデータ、及び、チェックコマンドはいずれも、メインCPU110から第1制御部102Aを経由して第2制御部102Bへ送信されるようになっているものの、一般的なコマンドやデータを送信する場合には、所定のストローブ信号を送信し、また、チェックコマンドを送信する場合には、この所定のストローブ信号とは異なる固有のストローブ信号を送信するように設定しておく。そして、第1制御部102Aでは、固有のストローブ信号を受信しても、これに伴って送信されるチェックコマンドを受信しないように設定するとともに、第2制御部102Bでは、固有のストローブ信号を受信したときに、これに伴って送信されるチェックコマンドを受信するように設定しておく。これにより、第2サブCPU170のみがチェックコマンドを受信可能となる。

【0015】

また、上述のように固有のストローブ信号を設定するのではなく、第2制御部102Bの受信ポートがチェックコマンドを受信した場合のみ、当該受信が行われたと判断するように形成してもよい。

また、メインCPU110がチェックコマンドを送信する所定のタイミングは、特に限定されるものではなく、たとえば、電源断から復帰した時点、所定のリセット操作により異常状態が解除された時点、設定値の変更が完了した時点等とすることができる。換言すれば、第1サブ記憶媒体150の交換が行われた可能性が高いタイミングとすることができる。

【0016】

(作用・効果)

本発明に係る遊技機においては、第2制御部102Bに備えられた認証用記憶媒体190に、第1サブ記憶媒体150に記憶された所定の固有データに基づいて定められる基本認証データが記憶されている。また、メインCPU110から送信されるチェックコマンドは、第2制御部102Bにおける第2サブCPU170のみが受信するようになっている。そして、第2サブCPU170がチェックコマンドを受信したことを条件に、認証用記憶媒体190に記憶された基本認証データと、当該時点で第1制御部102Aが備えている第1サブ記憶媒体150に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かが判断される。そして、一致していない場合には異常と判断される。

【0017】

すなわち、本発明に係る遊技機によれば、第2サブCPU170がチェックコマンドを受信すると、この時点での第1サブ記憶媒体150に基づく認証データであるチェック用認証データと、認証用記憶媒体190に予め記憶されている基本認証データとが比較される。ここで、第1サブ記憶媒体150が交換されていなければ、チェック用認証データと予め記憶されている基本認証データとは一致することとなるが、第1サブ記憶媒体150が交換されていると、チェック用認証データと予め記憶されている基本認証データとは一致しないこととなる。

これにより、サブ制御装置102のROM等の記憶媒体(第1サブ記憶媒体150)が交換されたことを、より確実に把握することができるのである。

【0018】

また、本発明に係る遊技機によれば、第2サブCPU170のみが受信可能なチェックコマンドに基づいて、第2サブCPU170が上述のようなチェックを行うため、不正行為を行うゴト師等は、不正な交換を行うメリットの高い第1サブ記憶媒体150について解析を行ったのみでは、上述のようなチェックの存在に気付かない。したがって、ゴト師等にとっては、このようなチェックへの対応が困難となるため、効果的に不正交換を抑止することができるのである。

(第2の発明)

第2の発明は、上記した第1の発明の特徴に加え、メインCPU110は、前記所定のタイミングで、チェック用認証データを第2制御部102Bへ送信させるためのチェック用送信コマンドを第1サブCPU140へ送信し、第2サブCPU170は、第1サブCPU140が送信したチェック用認証データを受信したことを条件に、基本認証データとチェック用認証データとが一致しているか否かを判断するように形成されていることを特徴とする。

【0019】

(作用・効果)

本発明に係る遊技機によれば、第2サブCPU170は、第1サブCPU140によりチェック用認証データが送信されてくるのを待って、基本認証データとチェック用認証データとの一致を判断する。したがって、第2サブCPU170は、当該判断を行うにあたり、自発的にチェック用認証データを取得する必要が無くなるため、第2サブCPU170の処理負担を軽減することができるのである。

(第3の発明)

第3の発明は、上記した第2の発明の特徴に加え、メインCPU110が送信したチェックコマンドを第2サブCPU170が受信した後、予め定められた所定時間内に、第1サブCPU140が送信したチェック用認証データを第2サブCPU170が受信できなかった場合に異常と判定するように形成されていることを特徴とする。

【0020】

(作用・効果)

本発明に係る遊技機によれば、第1サブCPU140が送信したチェック用認証データを、所定時間内に第2サブCPU170が受信できないときには、異常と判定されるため、チェック用認証データの送信エラーの発生をも把握することができるのである。

(第4の発明)

第4の発明は、上記した第1、第2又は第3の発明の特徴に加え、認証用記憶媒体190に基本認証データが記憶されていない初期状態において、予め定められた所定の初期設定条件を満たすことを契機として、基本認証データを第2制御部102Bへ送信させるための基本認証データ送信コマンドを第1サブCPU140へ送信し、かつ、第1サブCPU140が送信した基本認証データを認証用記憶媒体190に記憶させるための基本認証データ記憶コマンドを第2サブCPU170へ送信し、基本認証データ記憶コマンドを第2サブCPU170が受信し、かつ、第1サブCPU140が送信した基本認証データを第2サブCPU170が受信した場合に、認証用記憶媒体190に基本認証データを記憶するように形成されていることを特徴とする。

【0021】

ここで、所定の初期設定条件としては、たとえば、最初の主電源投入時やリセット時のみに行われる所定のプログラムが実行されること、所定期間内に予め定められた操作態様や操作順序でスイッチ操作が行われること等が挙げられる。そして、これらの場合には、遊技機に備えられているメイン制御装置101が、基本認証データ送信コマンドを第1サブCPU140へ送信するように形成することができる。

また、所定の初期設定条件としては、たとえば、遊技機が工場から出荷される前に正常に動作するか否か等の出荷検査が行われる場合には、この検査中にのみ行われる所定の処理が実行されることを定めることもできる。なお、この場合には、検査のために用いられる検査用メイン制御装置が、基本認証データ送信コマンドを第1サブCPU140へ送信するように形成することもできる。

【0022】

(作用・効果)

本発明に係る遊技機においては、認証用記憶媒体190に基本認証データが記憶されていない初期状態において、第2サブCPU170が、基本認証データ記憶コマンドを受信し、かつ、第1サブCPU140が送信した基本認証データを受信した場合に、認証用記憶媒体190に基本認証データが記憶されるようになっている。

すなわち、本発明に係る遊技機によれば、上述の条件を満たさなければ、認証用記憶媒体190に基本認証データが記憶されないため、認証用記憶媒体190に記憶された基本認証データの改竄を極めて困難にすることができるのである。

【発明の効果】

【0023】

本発明は、以上のように構成されているので、以下に記載されるような効果を奏する。

すなわち、本発明によれば、サブ制御装置のROM等の記憶媒体が交換されたことを、より確実に把握可能な遊技機を提供することができる。

【図面の簡単な説明】

【0024】

【図1】本発明の形態であって、スロットマシンを示す外観正面図である。

【図2】本発明の形態であって、スロットマシンの制御装置の入力及び出力の概略を示すブロック図である。

【図3】本発明の形態であって、スロットマシンのメイン制御装置及びサブ制御装置の概略を示すブロック図である。

【図4】本発明の形態であって、基本認証データの初期設定処理の概略を示すフローである。

【図5】本発明の形態であって、基本認証データとチェック用認証データとが一致しているか否かを判定する異常判定処理の概略を示すフローである。

【発明を実施するための形態】

【0025】

以下、本発明を実施するための形態を図面を参照しつつ説明する。

(スロットマシン10)

本形態に係る遊技機は、遊技媒体として円板状の遊技メダルを使用するスロットマシン10である。

このスロットマシン10は、図1に示すように、正面側(スロットマシン10から見て、スロットマシン10と対向する遊技者の方向)に開口する箱状の筐体20と、この筐体20の正面開口を開閉可能に塞ぐ前扉30とから構成されている。

(筐体20)

筺体20には、特に図示していないが、スロットマシン10の作動を制御するための基板を備えたメイン基板ユニット、複数の回転リール25を備えたリールユニット21、遊技メダルを貯留するとともに役を構成する図柄51の組み合わせの停止表示時等に遊技メダルを払い出すためのホッパーユニット27、スロットマシン10に備えられた各種装置に電力を供給するための電源装置28(主電源)等が設置されている。

【0026】

メイン基板ユニットには、IC等の各種電子部品を搭載したメイン基板が収納されている。メイン基板は、スロットマシン10の作動を制御する制御装置100のうち、メイン制御装置101を構成するものであり、具体的には、スロットマシン10の遊技に関する制御を行うものとなっている。

リールユニット21は、スロットマシン10の遊技に用いられるメインの装置であり、枠体に固定された3個のステッピングモーター(図示しておらず)と、各ステッピングモーターの回転軸に固定された3個の回転リール25とから構成されている。具体的には、この回転リール25は、図1の向かって左側に位置する左リール22と、図1の向かって右側に位置する右リール24と、この左リール22及び右リール24の間に位置する中リール23とからなるものである。また、特に図示していないが、各回転リール25の周囲には、それぞれ21個の図柄51が付されている。また、これらの回転リール25は、前記ステッピングモーターの回転軸を中心として、後述する表示窓34内を回転リール25の図柄51が上側から下側へ向けて通過するように、回転する。

【0027】

(前扉30)

前扉30の前面上部には、図1に示すように、遊技状態に応じて点灯したり、消灯したりすることで各種演出や各種異常状態の報知を行うためのランプ52や、液晶表示装置53等を備えた装飾部31が設けられている。

また、前扉30の下部中央には、筐体20に設けられたホッパーユニット27から遊技メダルを払い出すためのメダル払出口40が設けられ、メダル払出口40の両側には、音声を出力するためのスピーカ54がそれぞれ1つずつ設けられている。

また、前扉30の裏面には、特に図示していないが、IC等の各種電子部品を搭載した基板であるサブ基板が収納されたサブ基板ユニットが設けられている。サブ基板は、スロットマシン10の作動を制御する制御装置100のうち、演出や報知に関する制御を行うためのサブ制御装置102を構成するものである。

【0028】

また、前扉30の前面の略中央には、正面側に突出する操作部33が備えられている。

この操作部33には、遊技を開始するにあたり遊技メダルをベットすべく、遊技メダルを投入するためのメダル投入口44、スロットマシン10に電子的に貯留されているメダルであるクレジットメダルを遊技メダルのベットに代えるためのベットスイッチ(遊技メダル1枚のベットが可能なシングルベットスイッチ36a、遊技を開始するためにベット可能な最大枚数である遊技メダル3枚のベットが可能なマックスベットスイッチ36b)、クレジットメダルを精算するための精算スイッチ39、3個すべての回転リール25の回転を開始させるためのレバー状のスタートスイッチ37、及び、各回転リール25に対応するとともに、各回転リール25の回転をそれぞれ別個に停止させるための3個のストップスイッチ38が設けられている。

【0029】

また、前扉30における装飾部31と操作部33との間には、筐体20に設けられた3個の回転リール25の図柄を視認可能な表示窓34が形成されている。

表示窓34は、3個の回転リール25の前方に設けられており、3個すべての回転リール25の回転が停止した際に、表示窓34内における、それぞれの回転リール25に対応する表示位置(上段、中段及び下段)にそれぞれ図柄が表示される。すなわち、表示窓34内に、縦3列横3行に配列した合計9個の図柄が表示されることとなる。

また、本形態に係るスロットマシン10は、特に図示していないが、左リール22、中リール23、及び、右リール24が停止した状態で、各回転リール25ごとの、表示窓34内におけるいずれか一の図柄の停止位置を一直線に結んで構成される計5本の停止表示ラインを有している。

【0030】

そして、1回の遊技を開始するために遊技メダルをベットすると、停止表示ラインが有効化される。そして、役抽選手段(特に図示しておらず)の抽選の結果、所定の役に当選するとともに、有効化された停止表示ラインのいずれかに、当該役を構成する図柄の組み合わせが停止すると、役に応じた利益(たとえば、所定枚数の遊技メダルの払い出しや特別遊技の実行等)が付与される。

また、図1に示すように、前扉30の裏面における、メダル投入口44の下部に対応する位置には、このメダル投入口44から投入された遊技メダルの正偽を判断するためのメダルセレクタ43、及び、このメダルセレクタ43により適正な遊技メダルであると判断された遊技メダルを検知するためのメダルセンサ35が設けられている。

【0031】

なお、本形態に係るスロットマシン10には、後述するサブ制御ROM151(第1サブ記憶媒体150)が交換されたことを報知するための異常報知装置55が接続されている。この異常報知装置55としては、スロットマシン10に直接的に設けられた装置(演出用のランプ52とは別個に設けられた警告灯(警告ランプ)、所定の警告音を出力するための警告音出力装置(警報スピーカ)等)を用いることができる。

また、この異常報知装置55としては、スロットマシン10に直接的に設けられた装置を用いるのではなく、スロットマシン10とは別体の装置(スロットマシン10が設置されるシマに設けられたランプや監視モニター、スロットマシン10の出玉状況等を管理するサーバー用のモニター等)を用いることができる。具体的には、これらの装置とスロットマシン10とを、所定の接続手段(通信ケーブル、無線通信装置等)により接続し、サブ制御ROM151が取り外されたと判定された場合にスロットマシン10から出力される信号等に基づいて、上述の装置において報知を行うように設定することができる。

【0032】

(制御装置100)

制御装置100は、上述の如く、スロットマシン10の作動を制御するためのものであり、メイン制御装置101及びサブ制御装置102から構成されるものとなっている。

また、メイン制御装置101及びサブ制御装置102には、これらの装置に対して各種信号等を入力可能な入力手段(メダルセンサ35、シングルベットスイッチ36a、マックスベットスイッチ36b、スタートスイッチ37、ストップスイッチ38、精算スイッチ39等)、入力手段による入力等に基づいた制御の結果を出力可能な出力手段(リールユニット21、ホッパーユニット27、ランプ52、液晶表示装置53、スピーカ54、異常報知装置55等)が接続されている。また、メイン制御装置101及びサブ制御装置102は、後述するCPUが後述するROMに記憶されたプログラムを読み込むことで、各種制御手段として機能する。

【0033】

また、メイン制御装置101とサブ制御装置102との間では、これらを構成する基板に設けられた後述の送信部及び受信部により、所定のコマンドやデータの送信及び受信ができるようになっているが、メイン制御装置101からサブ制御装置102への一方へ向けてのみコマンドやデータが送信され、サブ制御装置102からメイン制御装置101へ向けてはコマンドやデータが送信されないようになっている。

そして、メイン制御装置101は、スタートスイッチ37及びストップスイッチ38の操作により、役の抽選、回転リール25の回転及び停止の制御、並びに遊技メダルの払出し等、遊技の進行に関する制御等を行い、また、サブ制御装置102は、メイン制御装置101から送信されるコマンドやデータに基づき、これらの送信内容に対応した遊技に関する演出や報知の制御等を行う。

【0034】

また、本形態のサブ制御装置102においては、当該サブ制御装置102を構成する第1制御部102Aのサブ制御ROM151(第1サブ記憶媒体150)が交換されたことを検知できるように形成されている。当該検知については、後程、詳述する。

(メイン制御装置101)

メイン制御装置101は、上述の如く、メイン基板により構成されている。

そして、このメイン基板には、図3に示すように、遊技に関するプログラムやデータが記憶されたメインROM120、メインROM120に記憶されたプログラム等に基づいて遊技の進行に関する制御を行うメインCPU110、読み書き可能であって遊技の進行に関する制御を行うためのデータ等を一時的に記憶するメインRAM130等、種々の電子部品が備えられている。

【0035】

また、メインCPU110には、図3に示すように、後述するサブ制御装置102の第1制御部102Aにコマンドやデータ等を送信するための第1送信部111A、及び、後述するサブ制御装置102の第2制御部102Bに特定のコマンド(後述のチェックコマンド、基本認証データ記憶コマンド等)やデータ等を送信するための第2送信部111Bが設けられている。

なお、本形態においては、メインCPU110として、インターフェースポートが内臓されたCPUを採用することができ、この内臓されているインターフェースポートにより、上述の第1送信部111A及び第1送信部111bを構成することができる。また、メイン制御装置101内に別途インターフェース回路を形成し、このインターフェース回路により、上述の送信部の全部又は一部を構成してもよい。

【0036】

また、本形態においては、後述する如く、第1送信部111Aから第1制御部102Aへの通信路及び第2送信部111Bから第2制御部102Bへの通信路をそれぞれ別個独立に形成しているが、第1送信部111Aから第1制御部102Aへの通信路の一部及び第1制御部102Aから第2制御部102Bへの通信路により、第2送信部111Bを構成してもよい。

また、メインCPU110から第1制御部102Aを経由して第2制御部102Bまで至る通信路のみを形成し、第1送信部111A及び第2送信部111Bがこれを共通に利用して、データ等の内容により、第1制御部102A又は第2制御部102Bのいずれか一方のみに送信可能となるように形成してもよい。

【0037】

(サブ制御装置102)

サブ制御装置102は、メイン制御装置101から送信されるコマンドやデータ等を受信することで、これらのコマンドやデータ等に基づいて、報知や演出の内容を決定する第1制御部102Aと、この第1制御部102Aから送信されるコマンドに基づいて、第1制御部102Aで決定された報知や演出の内容を液晶表示装置53やスピーカ54に実行させる第2制御部102Bと、から構成されている(図2及び図3参照)。

また、サブ制御装置102は、上述の如く、サブ基板により構成されている。

そして、このサブ基板には、図3に示すように、上述の第1制御部102A及び第2制御部102Bを構成する種々の電子部品が備えられている。

【0038】

なお、本形態における第2制御部102Bの第2サブCPU170は、第1制御部102Aを構成する後述のサブ制御ROM151(第1サブ記憶媒体150)が交換されたか否かを検出できるように形成されている。当該検出については、後述する。

(第1制御部102A及び第2制御部102Bの構成)

(1)第1制御部102A

図3に示すように、サブ基板には、第1制御部102Aを構成する電子部品として、報知や演出の内容を決定するためのプログラムやデータが記憶された第1サブ記憶媒体150としてのサブ制御ROM151、メインCPU110からのコマンド及びサブ制御ROM151に記憶されたプログラム等に基づいて報知や演出の内容を決定する第1サブCPU140、及び、読み書き可能であって報知や演出に関するデータ等を一時的に記憶する第1サブRAM160等が備えられている。

【0039】

また、第1サブCPU140には、図3に示すように、ランプ52やLED等の演出装置が接続されており、第1サブCPU140は直接、これらの演出装置に報知や演出の内容を実行させることができるようになっている。

さらに、第1サブCPU140には、図3に示すように、メインCPU110の第1送信部111Aにより送信されるコマンド等を受信するための第1受信部141A、及び、後述するサブ制御装置102の第2制御部102Bとの間でコマンドやデータ等の送受信を行うための第1サブ間送受信部141Bが設けられている。

なお、本形態においては、第1サブCPU140として、インターフェースポートが内臓されたCPUを採用することができ、この内臓されているインターフェースポートにより、上述の第1受信部141A及び第1サブ間送受信部141Bを構成することができる。また、第1制御部102A内に別途インターフェース回路を形成し、このインターフェース回路により、上述の送受信部の全部又は一部を構成してもよい。

【0040】

(2)第2制御部102B

図3に示すように、サブ基板には、第2制御部102Bを構成する電子部品として、液晶表示装置53の動作を制御するためのプログラム等が記憶された第2サブ記憶媒体180としての画像制御ROM181、画像制御ROM181に記憶されたプログラム等に基づく液晶表示装置53の動作の制御(後述するVDP200の制御)や、後述するサウンドチップ220の制御を行う第2サブCPU170、読み書き可能であって液晶表示装置53等の制御に関するデータ等を一時的に記憶する第2サブRAM191(認証用記憶媒体190)、液晶表示装置53に表示する画像や文字のデータが記憶されたキャラクタROM210、液晶表示装置53における表示データ等を記憶するVRAM211、スピーカ54から出力する音声のデータが記憶されたサウンドROM230、及び、スピーカ54からの音声出力を実行するサウンドチップ220等が備えられている。

【0041】

そして、第2サブCPU170には、VDP200やサウンドチップ230を介して、液晶表示装置53やスピーカ54が接続されており、第2サブCPU170は、上述のVDP200やサウンドチップ230を制御することにより、液晶表示装置53やスピーカ54に報知や演出の内容を実行させることができるようになっている。

また、第2サブCPU170には、上述の異常報知装置55が接続されており、第2サブCPU170は、後述する如く、サブ制御ROM151(第1サブ記憶媒体150)が交換されたと判定された場合には、異常である旨を異常報知装置55に報知させることができるようになっている。

【0042】

さらに、第2サブCPU170には、図3に示すように、メインCPU110の第2送信部111Bにより送信される特定のコマンド(チェックコマンド、基本認証データ記憶コマンド)等を受信するための第2受信部171A、及び、サブ制御装置102の第1制御部102Aとの間でコマンドやデータ等の送受信を行うための第2サブ間送受信部171Bが設けられている。

なお、本形態においては、第2サブCPU170として、インターフェースポートが内臓されたCPUを採用することができ、この内臓されているインターフェースポートにより、上述の第2受信部171A及び第2サブ間送受信部171Bを構成することができる。また、第2制御部102B内に別途インターフェース回路を形成し、このインターフェース回路により、上述の送受信部の全部又は一部を構成してもよい。

【0043】

なお、本形態においては、特に図示していないが、第2サブRAM191は独立して電力供給が可能なバックアップ電源が接続されており、電源断によっても第2サブRAM191の内容は消去されないようになっている。また、この第2サブRAM191は、後述する如く、第1サブ記憶媒体150としてのサブ制御ROM151に記憶されている固有データに基づいて定められる基本認証データを記憶するための認証用記憶媒体190としても用いられる。

(3)メイン制御装置101、第1制御部102A及び第2制御部102B相互間の通信路

本形態においては、図3に示すように、メイン制御装置101のメインCPU110に設けられた第1送信部111Aと、サブ制御装置102の第1制御部102Aにおける第1サブCPU140に設けられた第1受信部141Aとが、互いに信号線により接続されることにより、通信路が形成されている。なお、この通信路においては、メインCPU110から第1サブCPU140の一方へ向けてのみ、コマンドやデータを送信できるようになっている。

【0044】

また、図3に示すように、メイン制御装置101のメインCPU110に設けられた第2送信部111Bと、サブ制御装置102の第2制御部102Bにおける第2サブCPU170に設けられた第2受信部171Aとが、互いに信号線により接続されることにより、通信路が形成されている。なお、この通信路においても、メインCPU110から第2サブCPU170の一方へ向けてのみ、コマンドやデータを送信できるようになっている。

また、図3に示すように、第1制御部102Aの第1サブ間送受信部141Bと、第2制御部102Bの第2サブ間送受信部171Bとが、互いに信号線により接続されることにより、通信路が形成されている。なお、この通信路においては、第1制御部102A及び第2制御部102B間で双方向に、コマンドやデータを送受信できるようになっている。

【0045】

本形態においては、これらの通信路は互いに独立して形成されている。

そして、メインCPU110及び第1サブCPU140間の通信路、並びに、第1制御部102A及び第2制御部102B間の通信路は、役抽選の結果を示すコマンドや報知内容を示すデータ等、一般的なコマンドやデータの送受信に用いられるようになっている。また、メインCPU110及び第2サブCPU170間の通信路は、サブ制御ROM151が交換されたか否かをチェックするためのチェックコマンド等、特定のコマンドやデータの送受信にのみ用いられるようになっている。換言すれば、メインCPU110及び第1サブCPU140間の通信路、並びに、第1制御部102A及び第2制御部102B間の通信路では、上述の特定のコマンド等は送信されないようになっており、また、メインCPU110及び第2サブCPU170間の通信路では、上述の一般的なコマンド等は送信されないようになっている。

【0046】

これにより、チェックコマンド等の特定のコマンドについては、第2サブCPU170のみが受信可能となっている。

(サブ制御ROM51が交換された旨の検出)

本形態においては、各CPUが所定の処理を実行することで、第1サブ記憶媒体150としてのサブ制御ROM151が交換されたか否かを検出できるように形成されている。

以下、各CPUが実行する所定の処理の内容について、説明する。

なお、当該処理は、各CPUが各ROMに記憶されている所定のプログラムを読み込むことで機能する各種制御手段により(すなわち、ソフトウェアにより)実行されるように形成することもできるし、CPUが有する演算器や比較器等の回路により(すなわち、ハードウェアにより)実行されるように形成することもできる。

【0047】

(1)基本認証データ送信要求処理

基本認証データ送信要求処理は、予め定められた所定の初期設定条件を満たしたことを契機として、メイン制御装置101のメインCPU110が、第1制御部102Aの第1サブCPU140に基本認証データを送信させるための基本認証データ送信コマンドを送信する処理である。

ここで、「基本認証データ」とは、第1制御部102Aのサブ制御ROM151(第1記憶媒体150)に記憶されている所定の固有データに基づいて定められるものであり、各サブ制御ROM151ごとに特有となるデータである。

【0048】

本形態においては、たとえば、サブ制御ROM151に記憶されている固有のデータである、所定の役(たとえば、遊技者に所定の利益を付与可能なBBゲームが開始されることとなるBBゲーム役)の抽選となる乱数値の範囲における最大値、及び、サブ制御ROM151のデータについてのチェックサムの値の合算値を基本認証データとして定めることができる。

なお、基本認証データを定めるための固有データとしては、上記のものに限定されず、たとえば、所定の役のコード、所定の演出データのコード等を用いることができる。また、基本認証データは、複数の固有データに基づいて定めるのではなく、1の固有データに基づいて定めることもできる。また、所定の演算を行うことにより得られる値を基本認証データとするのではなく、固有データそのものを基本認証データとして用いてもよい。

【0049】

また、「基本認証データ送信コマンド」は、基本認証データを、第2制御部102Bの第2サブCPU170へ送信する旨を指示するためのコマンドである。

すなわち、メインCPU110が、第1サブCPU140に基本認証データ送信コマンドを送信すると、当該コマンドを受信した第1サブCPU140は、基本認証データを第2サブCPU170へ送信する。

また、予め定められた所定の初期設定条件としては、たとえば、スロットマシン10に最初に主電源が投入されたときのみに行われる所定のプログラム(たとえば、ハードウェアやソフトウェアの異常があるか否かをチェックするための自己判定プログラム等)が実行されたこと等を設定することができる。

【0050】

このように設定した場合には、上記プログラムが実行されると、メインCPU110が、第1サブCPU140に基本認証データ送信コマンドを送信することとなる。

なお、初期設定条件としては、当該条件を満たすことが困難な内容となっていれば、上記の内容に限定されず、たとえば、スロットマシン10を所定のモード(たとえば、設定変更モード等)に切り替えてから、所定時間内に予め定められた操作態様や操作順序でスイッチ操作が行われること等を設定することもできる。

また、初期設定条件としては、スロットマシン10が出荷される前に正常に動作するか否か等の出荷検査が行われる場合には、この検査中にのみ行われる所定の処理が実行されることを定めることもできる。なお、検査用のメイン制御装置101を用いて前記検査が行われる場合には、この検査用のメイン制御装置101が、基本認証データ送信コマンドを第1サブCPU140へ送信するようにしてもよい。

【0051】

(2)基本認証データ記憶要求処理

基本認証データ記憶要求処理は、上述の初期設定条件を満たしたことを契機として、メインCPU110が、第2制御部102Bの第2サブCPU170に基本認証データ記憶コマンドを送信する処理である。

すなわち、メインCPU110は、上述の初期設定条件を満たしたことを契機として、基本認証データ送信コマンドとともに、基本認証データ記憶コマンドも送信する。

ここで、「基本認証データ記憶コマンド」は、基本認証データを記憶するための認証用記憶媒体190として用いられる第2サブRAM191に、第1サブCPU140により送信される基本認証データを記憶させる旨を指示するためのコマンドである。

【0052】

本形態においては、第2サブCPU170がこの基本認証データ記憶コマンドを受信すると、第2サブRAM191が書き込み可能状態となるように設定されている。そして、第2サブRAM191が書き込み可能状態となることにより、この第2サブRAM191にデータ等を書き込むことができるようになっている。

(3)基本認証データ送信処理

基本認証データ送信処理は、メインCPU110が送信した基本認証データ送信コマンドを第1サブCPU140が受信したことを契機として、当該第1サブCPU140が、第2サブCPU170に基本認証データを送信する処理である。

【0053】

なお、第1サブCPU140が基本認証データ送信コマンドを受信したときには、当該第1サブCPU140は、所定の書き込み手段により、第1サブRAM160に基本認証データを書き込むように設定してもよい。

(4)基本認証データ記憶処理

基本認証データ記憶処理は、第2サブRAM191に基本認証データが記憶されていない状態(初期状態)において、第2サブCPU170が基本認証データ記憶コマンドを受信し、かつ、第1サブCPU140が送信した基本認証データを受信した場合に、当該基本認証データを第2サブRAM191に記憶する処理である。すなわち、この基本認証データ記憶処理は、サブ制御ROM151が交換されたことをチェックするために用いる基本認証データを、スロットマシン10の初期状態において第2サブRAM191に記憶させるための処理である。

【0054】

そして、本形態においては、第2サブRAM191に基本認証データが記憶されている状態で、第2サブCPU170が基本認証データ記憶コマンド及び基本認証データを受信した場合には、第2サブRAM191に記憶されていた基本認証データを、受信した基本認証データに書き換えるように形成されている。

なお、第2サブRAM191に基本認証データが記憶されている状態で、第2サブCPU170が基本認証データ記憶コマンド及び基本認証データを受信した場合には、第2サブRAM191に記憶されていた基本認証データを、受信した基本認証データに書き換えないように形成することもできる。そして、このように形成した場合には、第2サブRAM191に記憶されていた基本認証データは、所定の操作態様でスイッチ操作を行う等、予め定められた消去条件を満たすことにより、第2サブRAM191から消去されるように設定することができる。

【0055】

(5)チェック用認証データ送信要求処理

チェック用認証データ送信要求処理は、予め定められた所定のタイミングで、メインCPU110が、第1制御部102Aの第1サブCPU140にチェック用認証データを送信させるためのチェック用送信コマンドを送信する処理である。

ここで、「チェック用認証データ」とは、当該時点で第1制御部102Aが備えているサブ制御ROM151(第1サブ記憶媒体150)に記憶された前記所定の固有データに基づいて定められるものであり、各サブ制御ROM151ごとに特有となるデータである。

そして、このチェック用認証データは基本認証データと同じ固有データに基づいて定められるものであるため、同一のサブ制御ROM151であれば、チェック用認証データ及び基本認証データは同一の内容となる。これに対して、異なるサブ制御ROM151であれば、チェック用認証データ及び基本認証データは異なる内容となる。

【0056】

また、「チェック用送信コマンド」は、チェック用認証データを、第2制御部102Bの第2サブCPU170へ送信する旨を指示するためのコマンドである。

すなわち、メインCPU110が、第1サブCPU140にチェック用送信コマンドを送信すると、当該コマンドを受信した第1サブCPU140は、チェック用認証データを第2サブCPU170へ送信する。

また、予め定められた所定のタイミングとしては、たとえば、電源断から復帰した時点、何らかの異常状態が発生した後、所定のリセット操作により当該異常状態が解除された時点、設定値の変更が完了した時点等、サブ制御ROM141の不正交換が行われる可能性が高い時点を設定することができる。

【0057】

(6)基本認証データチェック要求処理

基本認証データチェック要求処理は、上述の所定のタイミングで、メインCPU110が、第2制御部102Bの第2サブCPU170にチェックコマンドを送信する処理である。

すなわち、メインCPU110は、上述の所定のタイミングで、チェック用送信コマンドとともに、チェックコマンドも送信する。

ここで、「チェックコマンド」は、第2サブRAM191(認証用記憶媒体190)に記憶されている基本認証データと、第1サブCPU140により送信されるチェック用認証データとが一致しているか否かを判断させる旨を指示するためのコマンドである。

【0058】

本形態においては、このチェックコマンドに基づき第2サブCPU170に対して割込み入力が行われる。そして、第2サブCPU170がこのチェックコマンドを受信すると、第2サブCPU170が、第1サブCPU140により送信されるチェック用認証データの受信待ち状態となる。

なお、このチェックコマンドは特定のコマンドに該当するものであるため、第2送信部111B及び第2受信部171Aにより(すなわち、メインCPU110及び第2サブCPU170間の通信路により)、直接、メインCPU110から第2サブCPU170への送信が行われる。換言すれば、メインCPU110が送信するチェックコマンドは、第2サブCPU170のみが受信可能となっている。

【0059】

(7)チェック用認証データ送信処理

チェック用認証データ送信処理は、メインCPU110が送信したチェック用送信コマンドを第1サブCPU140が受信したことを契機として、当該第1サブCPU140が、第2サブCPU170にチェック用認証データを送信する処理である。

なお、第1サブRAM160が基本認証データを記憶するように設定していた場合には、第1サブCPU140がチェック用送信コマンドを受信したときに、チェック用認証データと、第1サブRAM160に記憶されている基本認証データとを、所定の比較手段により比較し、同一であれば第1サブRAM160に記憶されている基本認証データを第2サブCPU170に送信し、異なっていればチェック用認証データを第2サブCPU170に送信するようにしてもよい。

【0060】

(8)基本認証データ読み出し処理

基本認証データ読み出し処理は、第2サブCPU170がチェックコマンドを受信して上述の受信待ち状態となっているときに、第1サブCPU140により送信されるチェック用認証データを受信した場合に、第2サブCPU170が、第2サブRAM191(認証用記憶媒体190)に記憶されている基本認証データを、所定の読み出し手段により読み出す処理である。

また、本形態においては、第2サブCPU170がチェックコマンドを受信しておらず受信待ち状態となっていないときに、チェック用認証データを受信した場合には、第2サブCPU170は、第2サブRAM191に記憶されている基本認証データを読み出さないように設定されている。

【0061】

なお、この場合の処理としては、上記内容に限定されるものではない。たとえば、このチェック用認証データを一時的に所定の記憶手段(たとえば、第2サブRAM191)に記憶しておくとともに、予め定められた所定時間が経過するまでにチェックコマンドを受信したときには、第2サブCPU170が基本認証データを読み出し、前記所定時間が経過するまでにチェックコマンドを受信しなかったときには、第2サブCPU170が基本認証データを読み出さないように設定してもよい。

また、第2サブCPU170により基本認証データの読み出しが行われなかった場合には、異常と判定してその旨を報知してもよい。

【0062】

(9)データ比較判定処理

データ比較判定処理は、第2サブRAM191(認証用記憶媒体190)から読み出された基本認証データと、受信したチェック用認証データとを、所定の比較手段により比較し、第2サブCPU170が、基本認証データとチェック用認証データとが一致しているか否かを判定するものである。

上述の如く、同一のサブ制御ROM151であれば、基本認証データとチェック用認証データとは一致するものの、異なるサブ制御ROM151であれば、基本認証データとチェック用認証データとは一致しないこととなる。

【0063】

すなわち、基本認証データとチェック用認証データとが一致していれば、基本認証データが第2サブRAM191に記憶された時点において第1制御部102Aに備えられていたサブ制御ROM151と、チェック用認証データを送信する時点において第1制御部102Aに備えられていたサブ制御ROM151とが同一のものであると判断できる。これに対して、基本認証データとチェック用認証データとが一致していなければ、基本認証データが第2サブRAM191に記憶された時点において第1制御部102Aに備えられていたサブ制御ROM151と、チェック用認証データを送信する時点において第1制御部102Aに備えられていたサブ制御ROM151とが異なっている(すなわち、サブ制御ROM151が交換された)と判断できる。

【0064】

このように、基本認証データとチェック用認証データとが一致しているか否かを判断することにより、サブ制御ROM151が交換された旨を判定することができるようになっている。

(10)異常出力処理

異常出力処理は、上述のデータ比較判定処理において、基本認証データとチェック用認証データとが一致していないと判定された場合に、第2サブCPU170が、異常と判定するとともに、その旨を示すコマンドを液晶表示装置53や異常報知装置55等に送信する処理である。そして、液晶表示装置53や異常報知装置55が前記コマンドを受信すると、これらの装置において異常の報知が行われることとなる。

【0065】

すなわち、サブ制御ROM151が交換された場合、液晶表示装置53や異常放置装置55において異常の報知が行われることとなる。

また、本形態においては、メインCPU110が送信したチェックコマンドを第2サブCPU170が受信した後、予め定められた所定時間内(たとえば、5秒以内等)に、第1サブCPU140が送信したチェック用認証データを第2サブCPU170が受信できなかった場合(すなわち、通信エラーが発生したような場合)にも、第2サブCPU170が異常と判定し、液晶表示装置53や異常報知装置55において異常の報知が行われるようになっている。そして、この異常の報知は、サブ制御ROM151が交換されたことによる異常の報知とは異なる態様で報知されるようになっている。

【0066】

次に、上述のサブ制御ROM151が交換された旨の検出の概略について、図4及び図5に示したフローを用いて説明する。

まず、基本認証データを第2サブRAM191(認証用記憶媒体190)に記憶させるための初期時処理について、メインCPU110により行われる処理の概要を、図4(a)のフローを用いて説明する。

図4(a)に示すステップ100において、所定の初期設定条件(スロットマシン10に最初に主電源が投入されたときのみに行われる自己判定プログラムが実行されたこと)が満たされた場合、次のステップ101に進む。一方、満たされていない場合、ステップ100に戻る。

【0067】

ステップ101において、メインCPU110が、基本認証データ記憶コマンドを第2サブCPU170に送信する。そして、ステップ102に進む。

ステップ102において、メインCPU110が、基本認証データ送信コマンドを第1サブCPU140に送信する。そして、当該処理が終了する。

次に、第1サブCPU140により行われる処理の概要を、図4(b)のフローを用いて説明する。

図4(b)に示すステップ200において、メインCPU110が送信した基本認証データ送信コマンドを第1サブCPU140が受信した場合、次のステップ201に進む。一方、受信していない場合、ステップ200に戻る。

【0068】

ステップ201において、第1サブCPU140が、サブ制御ROM151(第1サブ記憶媒体150)に記憶された所定の固有データに基づく基本認証データを取得し(生成し)、この基本認証データを第2サブCPU170に送信する。そして、当該処理が終了する。

次に、第2サブCPU170により行われる処理の概要を、図4(c)のフローを用いて説明する。

図4(c)に示すステップ300において、メインCPU110が送信した基本認証データ記憶コマンドを第2サブCPU170が受信した場合、次のステップ301に進む。一方、受信していない場合、ステップ300に戻る。

【0069】

ステップ301において、所定のタイマーにより計時が開始される。そして、次のステップ302に進む。

ステップ302において、タイマーにより計時された時間が所定時間を超えた場合、当該処理が終了する。一方、所定時間を超えていない場合、次のステップ303に進む。

ステップ303において、第1サブCPU140が送信した基本認証データを受信した場合、次のステップ304に進む。一方、受信していない場合、ステップ302に進む。

ステップ304において、第2サブRAM191(認証用記憶媒体190)に既に基本認証データが記憶されている場合、ステップ306に進む。一方、基本認証データが記憶されていない場合、次のステップ305に進む。

【0070】

ステップ305において、基本認証データが、第2サブRAM191(認証用記憶媒体190)に記憶され、当該処理が終了する。

ステップ306において、第2サブRAM191(認証用記憶媒体190)に既に記憶されている基本認証データが、受信した基本認証データに書き換えられ、当該処理が終了する。

なお、初期設定条件として、スロットマシン10の出荷検査中にのみ行われる所定の処理の実行が定められており、検査用のメイン制御装置101が、基本認証データ送信コマンドを第1サブCPU140へ送信するように形成されている場合には、上述のステップ304の処理を行わず、基本認証データが第2サブRAM191(認証用記憶媒体190)に既に記憶されているか否かを問わず、第1サブCPU140が送信した基本認証データを、新たな基本認証データとして、常に、第2サブRAM191(認証用記憶媒体190)に設定(記憶)してもよい。

【0071】

これにより、管理者側が正規な手続きにより基本認証データを再設定する場合における作業を簡便なものとすることができる。

次に、チェック用認証データと基本認証データとが一致しているか否かを判定する異常判定処理について、メインCPU110により行われる処理の概要を、図5(a)のフローを用いて説明する。

図5(a)に示すステップ400において、当該遊技が予め定められた所定のタイミング(たとえば、電源断から復帰した時点等)である場合、次のステップ401に進む。一方、所定のタイミングで無い場合、ステップ400に戻る。

【0072】

ステップ401において、メインCPU110が、チェック用送信コマンドを第1サブCPU140に送信する。そして、ステップ402に進む。

ステップ402において、メインCPU110が、チェックコマンドを第2サブCPU170に送信する。そして、当該処理が終了する。

次に、第1サブCPU140により行われる処理の概要を、図5(b)のフローを用いて説明する。

図5(b)に示すステップ500において、メインCPU110が送信したチェック用送信コマンドを第1サブCPU140が受信した場合、次のステップ501に進む。一方、受信していない場合、ステップ200に戻る。

【0073】

ステップ501において、第1サブCPU140が、当該時点で第1制御部102Aに備えられているサブ制御ROM151(第1サブ記憶媒体150)に記憶された所定の固有データに基づくチェック用認証データを取得し(生成し)、このチェック用認証データを第2サブCPU170に送信する。そして、当該処理が終了する。

次に、第2サブCPU170により行われる処理の概要を、図5(c)のフローを用いて説明する。

図5(c)に示すステップ600において、メインCPU110が送信したチェックコマンドを第2サブCPU170が受信した場合、次のステップ601に進む。一方、受信していない場合、ステップ600に戻る。

【0074】

ステップ601において、所定のタイマーにより計時が開始される。そして、次のステップ602に進む。

ステップ602において、タイマーにより計時された時間が所定時間を超えた場合、ステップ607に進む。一方、所定時間を超えていない場合、次のステップ603に進む。

ステップ603において、第1サブCPU140が送信したチェック用認証データを受信した場合、次のステップ604に進む。一方、受信していない場合、ステップ602に進む。

ステップ604において、第2サブRAM191(認証用記憶媒体190)に既に記憶されている基本認証データが読み出される。そして、ステップ605に進む。

【0075】

ステップ605において、基本認証データとチェック用認証データとが一致しているか否か、すなわち、サブ制御ROM151が交換されたか否かを判定する。そして、一致していると判定された場合、当該処理が終了する。一方、一致していないと判定された場合、ステップ606に進む。

ステップ606において、基本認証データとチェック用認証データとが一致していない(サブ制御ROM151が交換された)旨を示す異常コマンドを出力する。そして、当該処理が終了する。

ステップ607において、第1サブCPU140が送信したチェック用認証データを所定時間内に第2サブCPU170が受信することができない旨を示す異常コマンドを出力する。そして、当該処理が終了する。

【0076】

(まとめ)

本形態に係るスロットマシン10では、第2制御部102Bに備えられた第2サブRAM191(認証用記憶媒体190)に、サブ制御ROM151(第1サブ記憶媒体150)に記憶された所定の固有データに基づいて定められる基本認証データが記憶されている。また、メインCPU110から送信されるチェックコマンドは、第2制御部102Bにおける第2サブCPU170のみが受信するようになっている。そして、第2サブCPU170がチェックコマンドを受信したことを条件に、第2サブRAM191に記憶された基本認証データと、当該時点で第1制御部102Aが備えているサブ制御ROM151に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かが判断される。そして、一致していない場合には異常と判断される。

【0077】

すなわち、本形態に係るスロットマシン10によれば、第2サブCPU170がチェックコマンドを受信すると、この時点でのサブ制御ROM151に基づく認証データであるチェック用認証データと、第2サブRAM191に予め記憶されている基本認証データとが比較される。ここで、サブ制御ROM151が交換されていなければ、チェック用認証データと予め記憶されている基本認証データとは一致することとなるが、サブ制御ROM151が交換されていると、チェック用認証データと予め記憶されている基本認証データとは一致しないこととなる。

これにより、サブ制御ROM151が交換された(取り外された)ことを、より確実に把握することができるのである。

【0078】

また、本形態に係るスロットマシン10によれば、第2サブCPU170のみが受信可能なチェックコマンドに基づいて、第2サブCPU170が上述のようなチェックを行うため、不正行為を行うゴト師等は、不正な交換を行うメリットの高いサブ制御ROM151について解析を行ったのみでは、上述のようなチェックの存在に気付かない。したがって、ゴト師等にとっては、このようなチェックへの対応が困難となるため、効果的に不正交換を抑止することができるのである。

また、本形態に係るスロットマシン10においては、第2サブCPU170は、第1サブCPU140によりチェック用認証データが送信されてくるのを待って、基本認証データとチェック用認証データとが一致するか否かを判断する。したがって、第2サブCPU170は、当該判断を行うにあたり、自発的にチェック用認証データを取得する必要が無くなるため、第2サブCPU170の処理負担を軽減することができるのである。

【0079】

また、本形態に係るスロットマシン10によれば、第1サブCPU140が送信したチェック用認証データを、所定時間内に第2サブCPU170が受信できないときには、異常と判定されるため、チェック用認証データの送信エラーの発生をも把握することができるのである。

また、本形態に係るスロットマシン10においては、第2サブRAM191に基本認証データが記憶されていない初期状態において、第2サブCPU170が、基本認証データ記憶コマンドを受信し、かつ、第1サブCPU140が送信した基本認証データを受信した場合に、第2サブRAM191に基本認証データが記憶されるようになっている。

【0080】

すなわち、本形態に係るスロットマシン10によれば、上述の条件を満たさなければ、第2サブRAM191に基本認証データが記憶されないため、第2サブRAM191に記憶された基本認証データの改竄を極めて困難にすることができるのである。

なお、上述の形態は、同様の構成の制御装置100を備えていれば、スロットマシン10以外の遊技機にも応用できる。たとえば、遊技媒体として遊技球を用いて遊技を行わせるパチンコ遊技機や、遊技媒体として遊技球を用いてスロットマシン10と同様の遊技を行わせるパロット(登録商標)遊技機、アレンジボール遊技機、雀球遊技機、カジノマシン等に使用してもよいものである。

【0081】

(変形例1)

上述の形態においては、メインCPU110及び第2サブCPU170間を直接的に通信可能な独立した通信路により、チェックコマンド等の特定のコマンドを送受信することで、第2サブCPU170のみがチェックコマンドを受信可能となるように形成されていたが、独立した通信路を設けるのではなく、一般的なコマンドやデータの送受信を行うための通信路を共通に利用して、第2サブCPU170のみがチェックコマンドを受信可能とすることもできる。

具体的には、一般的なコマンドやデータ、及び、チェックコマンドはいずれも、メインCPU110から第1制御部102Aを経由して第2制御部102Bへ至る通信路により、送信されるようになっているものの、一般的なコマンドやデータを送信する場合には、所定のストローブ信号を送信し、また、チェックコマンドを送信する場合には、この所定のストローブ信号とは異なる固有のストローブ信号を送信するように設定しておく。そして、第1制御部102Aでは、固有のストローブ信号を受信しても、これに伴って送信されるチェックコマンドを受信しないように設定するとともに、第2制御部102Bでは、固有のストローブ信号を受信したときに、これに伴って送信されるチェックコマンドを受信するように設定しておく。これにより、第2サブCPU170のみがチェックコマンドを受信可能とすることができる。

【0082】

また、上述のように固有のストローブ信号を設定するのではなく、たとえば、第1サブCPU140では利用されない所定のコマンド(送信準備コマンド)を設けておくとともに、メインCPU110がチェックコマンドを送信する場合には、その直前に送信準備コマンドを送信するように設定しておく。これにより、第2サブCPU170のみが送信準備コマンドを受信可能となる。そして、第2サブCPU170が送信準備コマンドを受信したときにのみ、その後に送信されるチェックコマンドを受信できるようにしてもよい。

このように形成した場合にも、上述の形態と同様の作用効果を奏するとともに、別個に通信路を設ける必要が無くなるため、ハードウェア資源を有効に利用することができることとなる。

【0083】

(変形例2)

上述の形態においては、メインCPU110が、チェック用認証データを第2サブCPU170へ送信する旨を指示するチェック用送信コマンドを、第1サブCPU140へ送信するようになっていたが、第2サブCPU170自ら、チェック用送信コマンドを第1サブCPU140へ送信するようにしてもよい。

なお、この場合には、第2サブCPU170は、初期時において備えられていたサブ制御ROM151のみが解読可能な暗号化データを付加したチェック用送信コマンドを、第1サブCPU140へ送信するように形成することが望ましい。これにより、サブ制御ROM151が交換された場合には、このチェック用送信コマンドを解読することができないこととなるため、チェック用認証データが第2サブCPU170へ送信されず、サブ制御ROM151の交換を確実に検知することができることとなる。

【符号の説明】

【0084】

10 スロットマシン

20 筐体 21 リールユニット

22 左リール 23 中リール

24 右リール 25 回転リール

27 ホッパーユニット 28 電源装置

30 前扉 31 装飾部

33 操作部 34 表示窓

35 メダルセンサ 36a シングルベットスイッチ

36b マックスベットスイッチ 37 スタートスイッチ

38 ストップスイッチ 39 精算スイッチ

40 メダル払出口 43 メダルセレクタ

44 メダル投入口 52 ランプ

53 液晶表示装置 54 スピーカ

55 異常報知装置

100 制御装置 101 メイン制御装置

102 サブ制御装置 102A 第1制御部

102B 第2制御部

110 メインCPU 111A 第1送信部

111B第2送信部 120 メインROM

130 メインRAM

140 第1サブCPU 141A 第1受信部

141B 第1サブ間送受信部 150 第1サブ記憶媒体

151 サブ制御ROM 160 第1サブRAM

170 第2サブCPU 171A 第2受信部

171B 第2サブ間送受信部 180 第2サブ記憶媒体

181 画像制御ROM 190 認証用記憶媒体

191 第2サブRAM 200 VDP

210 キャラクタROM 211 VRAM

220 サウンドチップ 230 サウンドROM

【特許請求の範囲】

【請求項1】

遊技に関する処理を実行可能なメインCPUを有するメイン制御装置と、

メインCPUが送信するコマンドを受信可能であり、メインCPUからのコマンドに応じた遊技に関する処理を実行するサブ制御装置と、を備え、

サブ制御装置は、

遊技に関するプログラムやデータを記憶した第1サブ記憶媒体、並びに、メインCPUからのコマンド及び第1サブ記憶媒体に記憶されたプログラムに基づき、実行する処理の内容を決定する第1サブCPUを有する第1制御部と、

第1サブCPUが送信するコマンドを受信可能であるとともに、第1サブCPUにより決定される処理内容を実行するためのプログラムやデータを記憶した第2サブ記憶媒体、第1サブCPUからのコマンド及び第2サブ記憶媒体に記憶されたプログラムに基づき、前記処理内容を実行する装置の動作を制御する第2サブCPU、並びに、データの読み書きが可能な認証用記憶媒体を有する第2制御部と、を備えた遊技機であって、

認証用記憶媒体は、第1サブ記憶媒体に記憶された所定の固有データに基づいて定められる基本認証データを予め記憶しており、

メインCPUは、予め定められた所定のタイミングで、所定のチェックコマンドを第2制御部へ送信するとともに、メインCPUが送信した前記チェックコマンドは、第2サブCPUのみが受信可能となっており、

メインCPUが送信した前記チェックコマンドを第2サブCPUが受信したことを条件に、認証用記憶媒体に記憶された基本認証データと、当該時点で第1制御部が備えている第1サブ記憶媒体に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かを判断し、一致していない場合に異常と判定するように形成されていることを特徴とする遊技機。

【請求項2】

メインCPUは、前記所定のタイミングで、チェック用認証データを第2制御部へ送信させるためのチェック用送信コマンドを第1サブCPUへ送信し、

第2サブCPUは、第1サブCPUが送信したチェック用認証データを受信したことを条件に、基本認証データとチェック用認証データとが一致しているか否かを判断するように形成されていることを特徴とする請求項1記載の遊技機。

【請求項3】

メインCPUが送信したチェックコマンドを第2サブCPUが受信した後、予め定められた所定時間内に、第1サブCPUが送信したチェック用認証データを第2サブCPUが受信できなかった場合に異常と判定するように形成されていることを特徴とする請求項2記載の遊技機。

【請求項4】

認証用記憶媒体に基本認証データが記憶されていない初期状態において、予め定められた所定の初期設定条件を満たすことを契機として、基本認証データを第2制御部へ送信させるための基本認証データ送信コマンドを第1サブCPUへ送信し、かつ、第1サブCPUが送信した基本認証データを認証用記憶媒体に記憶させるための基本認証データ記憶コマンドを第2サブCPUへ送信し、

基本認証データ記憶コマンドを第2サブCPUが受信し、かつ、第1サブCPUが送信した基本認証データを第2サブCPUが受信した場合に、認証用記憶媒体に基本認証データを記憶するように形成されていることを特徴とする請求項1、2又は3記載の遊技機。

【請求項1】

遊技に関する処理を実行可能なメインCPUを有するメイン制御装置と、

メインCPUが送信するコマンドを受信可能であり、メインCPUからのコマンドに応じた遊技に関する処理を実行するサブ制御装置と、を備え、

サブ制御装置は、

遊技に関するプログラムやデータを記憶した第1サブ記憶媒体、並びに、メインCPUからのコマンド及び第1サブ記憶媒体に記憶されたプログラムに基づき、実行する処理の内容を決定する第1サブCPUを有する第1制御部と、

第1サブCPUが送信するコマンドを受信可能であるとともに、第1サブCPUにより決定される処理内容を実行するためのプログラムやデータを記憶した第2サブ記憶媒体、第1サブCPUからのコマンド及び第2サブ記憶媒体に記憶されたプログラムに基づき、前記処理内容を実行する装置の動作を制御する第2サブCPU、並びに、データの読み書きが可能な認証用記憶媒体を有する第2制御部と、を備えた遊技機であって、

認証用記憶媒体は、第1サブ記憶媒体に記憶された所定の固有データに基づいて定められる基本認証データを予め記憶しており、

メインCPUは、予め定められた所定のタイミングで、所定のチェックコマンドを第2制御部へ送信するとともに、メインCPUが送信した前記チェックコマンドは、第2サブCPUのみが受信可能となっており、

メインCPUが送信した前記チェックコマンドを第2サブCPUが受信したことを条件に、認証用記憶媒体に記憶された基本認証データと、当該時点で第1制御部が備えている第1サブ記憶媒体に記憶された前記所定の固有データに基づいて定められるチェック用認証データとが一致しているか否かを判断し、一致していない場合に異常と判定するように形成されていることを特徴とする遊技機。

【請求項2】

メインCPUは、前記所定のタイミングで、チェック用認証データを第2制御部へ送信させるためのチェック用送信コマンドを第1サブCPUへ送信し、

第2サブCPUは、第1サブCPUが送信したチェック用認証データを受信したことを条件に、基本認証データとチェック用認証データとが一致しているか否かを判断するように形成されていることを特徴とする請求項1記載の遊技機。

【請求項3】

メインCPUが送信したチェックコマンドを第2サブCPUが受信した後、予め定められた所定時間内に、第1サブCPUが送信したチェック用認証データを第2サブCPUが受信できなかった場合に異常と判定するように形成されていることを特徴とする請求項2記載の遊技機。

【請求項4】

認証用記憶媒体に基本認証データが記憶されていない初期状態において、予め定められた所定の初期設定条件を満たすことを契機として、基本認証データを第2制御部へ送信させるための基本認証データ送信コマンドを第1サブCPUへ送信し、かつ、第1サブCPUが送信した基本認証データを認証用記憶媒体に記憶させるための基本認証データ記憶コマンドを第2サブCPUへ送信し、

基本認証データ記憶コマンドを第2サブCPUが受信し、かつ、第1サブCPUが送信した基本認証データを第2サブCPUが受信した場合に、認証用記憶媒体に基本認証データを記憶するように形成されていることを特徴とする請求項1、2又は3記載の遊技機。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−106690(P2013−106690A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−252400(P2011−252400)

【出願日】平成23年11月18日(2011.11.18)

【出願人】(390031783)サミー株式会社 (5,279)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月18日(2011.11.18)

【出願人】(390031783)サミー株式会社 (5,279)

【Fターム(参考)】

[ Back to top ]