過渡エラー制約を受ける電子システムのためのメモリアクセス監視装置

【課題】過渡エラー制約を受ける電子システム用の処理手法を提案し、過渡エラーの様相を検出し、それらを修正することである。

【解決手段】本発明は、過渡エラー制約を受ける電子システムの処理手順に関し、単一物理チャネルにある二つの仮想チャネルが所定のリアルタイムサイクルでタイミングよく多重化され(使用の前に票決できるように、仮想チャネルの各実行から生じるデータは記憶されている)、エラーが検出された場合には、処理中のリアルタイムサイクルは禁止され、再ロードされたコンテキスト始まる次のサイクルの仮実行からなる再開始を行うように異常のないコンテキストが再ロードされる。本発明は、また、メモリアクセスの監視装置にも関する。

【解決手段】本発明は、過渡エラー制約を受ける電子システムの処理手順に関し、単一物理チャネルにある二つの仮想チャネルが所定のリアルタイムサイクルでタイミングよく多重化され(使用の前に票決できるように、仮想チャネルの各実行から生じるデータは記憶されている)、エラーが検出された場合には、処理中のリアルタイムサイクルは禁止され、再ロードされたコンテキスト始まる次のサイクルの仮実行からなる再開始を行うように異常のないコンテキストが再ロードされる。本発明は、また、メモリアクセスの監視装置にも関する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、過渡エラー制約を受ける電子システムの処理手順及び、例えば、宇宙関係に使用されるメモリーアクセス監視装置に関する。

【背景技術】

【0002】

本発明による方法は、過渡エラーを受ける全てのコンピュータアーキテクチャに関する。例えば、以下の分野では、この種のエラーを発生する、電子部品に対する妨害環境(放射線、電磁外乱)の影響を受けるコンピュータを使用している。

−周囲環境に重イオンが含まれる、宇宙、原子及び航空産業

−重大な電磁環境の影響を受ける自動車産業

【0003】

宇宙産業は、以下の説明で例として使用する。その理由は、電子部品に発生するランダム過渡エラーは極めて代表的なものであり、またこの理由は、この分野で、最初に本発明による処理方法が開発され、評価されたからである。

【0004】

衛星用のコンピュータ構造の設計者は、宇宙に存在するが、大気によって濾過される放射線の問題に直面している。この放射線には、マイクロプロセッサの内部レジスタ内で、または他の集積部品において、メモリ部品のビットの一時的な状態変化を起こす「特異イベント」効果がある。例えば、これらの特異イベントによって発生するエラーは、データを不正確にする場合がある。その例としては、衛星アクチュエータの制御不良、またはソフトウェアチャネルへの重大な外乱などがあり、これらは例えばマイクロプロセッサのクラッシュによって発生する。

【0005】

現在まで、特異イベントタイプのエラーに対する解決方法は、この現象の影響が極めて少ない「放射線耐性」技術、またはこの現象の影響を受けない「対放射線強化」技術といわれる集積回路技術を使用することであった。産業用マイクロエレクトロニクスの分野では使用されていないこの種の技術は、特に軍事及び宇宙の用途に開発されたものであった。

【0006】

このマイクロエレクトロニクス技術を維持し、この技術を使用した部品を開発する全体的なコスト、つまりこれらの部品の市販コストはかなり高くなっている。強化型回路と市販回路とのコストの比率は、100またはそれ以上の場合がある。

【0007】

「高信頼性」軍事部品の市場占有率は、1960年代の80%から1995年には1%以下へと急激に落ち込んだ。1994年から、米国国防総省は軍事用途への軍事用電子部品の使用を控え始めて、一般市販仕様/規格/部品を軍事用途への使用を拡大加速し始めた。

【0008】

本明細書の最後で参考文献〔1〕に説明されているように、市販電子部品の使用は、宇宙産業が直面しなければならない試練となった。

【0009】

宇宙産業用途に市販部品を使用することは、全ての新規勃興プロジェクトが直面する問題である。解決すべき主な問題は、部品の放射線、特に重イオンに対する感度である。この問題は、以前には「部品」レベルで扱われたが、「構造」レベル、「システム」レベルで解決すべき問題となっている。二つの参考文献〔2〕と〔3〕で説明したように、衛星及びその搭載電子部品は、異なった粒子(電子、重イオン、陽子)で構成される放射線環境の影響を受ける。これらの粒子は大気によって濾過されるので、地上のシステムには適用されない。

【0010】

これらの粒子は、以下の理由によると考えられる。すなわち:

−一部は銀河系の外から発生する宇宙放射線、また一部は非常に高いエネルギーイオンからなる銀河系内の宇宙放射線

−地球大気と太陽粒子との間の相互作用に続いて発生した閉じこみ電子と陽子で構成される放射線帯

−陽子と重イオンを放出する太陽の爆発

−コロナプラズマの蒸発により発生する太陽風であって、これにより、低エネルギー陽子とイオンが太陽の引力から抜け出せるようになる、である。

【0011】

これら高エネルギー粒子が、電子部品にぶつかり、通過して、粒子のエネルギーの一部を電子部品に伝えて、通常の作動を乱すようになる。これらの問題は、重イオンと陽子によって発生する「特異イベント」といわれる。

【0012】

これら特異イベントは、2進値を記憶するセル内のエラーの発生に対応していて、ビットエラーを引き起こす。一般的に、単一ビットは重イオンによって変更される。これらの現象は重大ではなく、新しいデータがその後に書き込まれる。同じセル内で他の特異イベントが発生しない限り、新しいデータはエラーなく記憶される。これは、本明細書のこれ以後で、これらの現象により発生するエラーを特徴づけるために使用される用語「過渡不良」のためである。

【0013】

前述したように、衛星への搭載電子部品の製造は、一般には、放射線の影響を受けない部品を使って行なわれる。その理由は、その部品は特にこの目的のために製作されていること、または特にこの目的のために製作されていない部品の選定によるためである。

【0014】

大規模に、宇宙用途に市販部品を使用するためにある最初の可能性は、系統的な放射線のもとで市販部品を試験することにより選定することである。選定に関して、まずこの方法は大変な費用がかかるばかりでなく、効率が悪い。その理由は、望ましいことではあるが、広範な産業規格を必ずしも使うことができないからである。

【0015】

他の経済的にさらに好ましい可能性は、部品選定の制約を緩和することである。これには、放射線によって発生する現象の許容、特に過渡エラーの許容を拡大する方法を探ることが含まれる。つまり、エラーを検出し、修正するアーキテクチャを規定することである。過渡不良を、「部品」レベルではなく、「構造」及び「システム」レベルで考慮することである。

【0016】

参考文献〔4〕、〔5〕と〔6〕では、一連の不良検出、分離及び再生機構について説明されている。機構によっては、単にエラー検出するためだけに使われていて、またエラーを検出しそれにマスクをするもの、エラーを修正するものがある。さらにこれらの機構は、一時的なエラー処理、パラメータ不良またはその両方に適用されている。

【0017】

一般の機構を、特に宇宙産業に適用される数例を挙げて、簡単に説明する。

−不良回避:実際に使用される前に、静的データの系統的更新;部品が使用される前に、部品不良を検出するために、「オフ−ライン」自己試験(標準作動中ではない)

【0018】

−エラー検出または検出/主として、アプリケーション特定集積回路(ASICs)、または集積コントロール装備フィールド・プログラマブル・ゲート・アレー(FPGA)製造用メモリー、通信及び可能であれば論理に適用可能な修正コード。エラー検出及び修正(EDAC)回路は、系統的にメモリー用途に宇宙産業で使用されている。全体メモリーの系統的リロード(または「スクラビング」)機能はこれらの回路に関連していて、実質的に検出/修正を不可能にする休止エラーの集積を回避するために、スクラブタスクとして動作する。

【0019】

−二重及び比較、三重及び多数決(「N モジュラ冗長性」、オーダーNのモジュラ冗長性)。これらの機構には、悪性コマンドは発生しないが、最初の不良で停止するフェールセーフが得られる構造(二重)、不良中に作動可能の状態(「フェイルオペレーショナル」)で、リアルタイムで単一エラーをマスクすることができ、「セーフ」のままで継続する構造(三重)がある。この分類には、また、マイクロプロセッサだけが複製され、「マスター」からのデータ出力は「コントローラー」によって検証される、マスター/コントローラー構造が含まれる。MHS S.A.社により製作されたERC−32マイクロプロセッサはこのような構造を含んでいる。

【0020】

−Nオーダーのモジュラ冗長性構造に関連したマルチプルプログラミング法(「N−バージョンプログラミング」、)、これはまたソフトウェア設計エラーを検出可能である。各コンピュータは、特に共通仕様から始まって開発されたソフトウェアバージョンを備えている。

【0021】

−時間冗長性;その目的は、比較に続く二つの連続実行を使用こと、またはコマンドレジスタをロードすることに続いて単一実行を使用することであり、例えば火器エレメントの引き金を引く極めて重要なコマンドに宇宙で使用される「装填 発射」メカニズムなどの比較と検証をするためにリロードする。

【0022】

−実行時間の確認:「ウオッチドッグ(監視者)」(プログラムが制限時間内で実行されていることを確認するタイムカウンター)は全ての宇宙用コンピュータに使用される。実行時間に関してこれらさらに詳細な確認装置は、ソフトウェアに組み込まれる場合がある。つまり、タスクの時間、通信エレメントからの回答を得るための最大許容時間を確認する。ソフトウェアはまたタスク実行時間にチェックを設定するために使われる。

【0023】

−コントロールフローの検証、例えば、マイクロプロセッサのシーケンスの確認。監視できるのは粗いチェック。ハードディスククラッシュを検出可能である。インストラクションフローチェックは多少複雑な監視プロセッサで終わる。シグナチャ分析を使うチェックは、特に有効で多くの電子装置を必要としない。このコンセプトはMHS S.A.社により製作されたERC−32に盛り込まれているが、参照シグナチャを計算してコードに組み込む特定コンパイラーは、ユーザーに見えるようにするために必要である。

【0024】

−ページ/セグメントによってアクセス権から始まるマイクロプロセッサアドレスの正当性をチェックする。

【0025】

−確率チェック;この原理は、衛星用に姿勢軌道制御システム(SCAO)に使用され、何種類かのセンサーからのデータが不一致を検出するために比較され、またはデータの1項目が前の値についての推定フィルタを使って推定された基準と比較され、またはデータの1項目が予め定義された範囲と比較される。「演算処理に基づいた不良公差」法は確立チェックの一分野であり、その検証は第二演算の実行に基づく。例えば、逆演算は、エラーが発生しない場合に得られる結果から始まる最初の結果を再生する。

【0026】

−比較的複雑なデータ構造を必要とするデータの構造的または語義のチェック

【0027】

−補助誤再生コンセプト、主に、上記で説明した機構が修正できない点で再開する、つまり定期的にコンテクストをバックアップし、最後にセーブされたコンテクストから再開する。

【0028】

−エラー再生の他の手段は、初期検出/修正能力を回復するために、不良コンピュータに正常なコンテクストを移入することにより不良があるリソースを再挿入することである。

【0029】

従来の文書には、また時間冗長性の説明が含まれている。

【0030】

参考文献〔5〕には、連続的にタスクを3回実行して、結果を「票決」する可能性が説明されている。

【0031】

ソフトウェアによりオーダーNモジュラ冗長性型操作の実行の可能性は、また参考文献〔6〕に理論的に説明されている。

【0032】

この文献では、パラメータ不良から過渡不良を区別し、不良を修正でき得る別の方法が説明されている。検出は時間冗長性法ではないが、例えばデータ符号化を含む場合がある。検出が行なわれると、処理は2回行なわれる。2回目の実行でエラーのない結果が得られると、エラーは過渡的であってシステムを再構成する必要はない。それでも、パーマネントな不良である場合は、再構成が必要である。

【0033】

両文献においては、理論的に可能であるので、時間冗長性は測定されるが、実際にこれが実行できる可能性について、何ら記載されていないし、特に進展は説明されていない。検討すらされていない問題がある。特にマイクロプロセッサ自身によって票決される場合、またはマイクロプロセッサと独立した外部装置により決定される場合である。決定の結果は変更できないものとする必要がある。その理由は、マイクロプロセッサ内にデータエラー、シーケンスのクラッシュなどの機能不全が発生する可能性があるが、結果は意思決定の要素だからである。従がって、マイクロプロセッサによって行なわれる票決は、検討されない主な要素となる。さらに、検出が行なわれる粒度は定義されていない。

【0034】

参考文献〔7〕は、僅かながらさらに詳しく記載されている。この文献では、二つのエラー検出方法の比較評価が説明されている。そのうちの一つは、「モジュラ・トリプル・ソフトウェア冗長性」といわれる。通常、モジュラ・トリプル冗長性はハードウェア内で正常に実行される。本文で評価される方法は、ソフトウェアと全てのモジュールの、特に票決モジュールの連続実行による時間冗長性を使い、特にソフトウェアにより行なわれ、同じマイクロプロセッサ上で実行される。従って、これは純粋にソフトウェアの手法になる。本文における図1に対応する図1は、どのように検出が行われるかを示す。つまり、各三つの決定モジュール1,2、と3は三つの手法4,5、と6の実行の結果を比較し、三つの処理ステップの同一性を確認する各決定モジュールからの結果の出力を比較する意思決定段階7が続く。モジュラ・トリプル・ソフトウェア冗長性はMC6800マイクロプロセッサ上でプログラムされる。このソフトウェアを評価するために、1500のエラーが注入された。メモリーはエラー検出と修正回路により、エラーから保護されていない。本書では、検出されないエラーのみが処理されると他を乱すエラーであると結論している。さらに、プログラム間の通信に悪影響を及ぼす全てのエラーは許容されない。

【0035】

本文では、処理が連続して3回実行され(時間冗長性)、決定モジュールが3回実行され決定モジュールの結果はそれ自身で決定される構造の特定例について説明する。結果は固定されていなくて、何故三重化されるかを理解することができる。最終決定は図に示されている最後の段階により行なわれ、間接的にそれは必ず小さくなる(データの数行のみがデータの項目を決定するのに必要である)ことから確実になる。統計的に、直接このモジュールに影響する特異事象は無視できるものであるが、これはマイクロプロセッサシーケンスエラーに対してセキュリティーは与えていない。

【0036】

参考文献〔8〕は、また、LAPX432タイプ、マイクロプロセッサ上での「トリプル・ソフトウェア・モジュラ冗長性」の実行を示している。これは参考文献〔7〕に示されているものと同じ実施形態である。各ソフトウェアサブタスクは連続的に3回実施され、ソフトウェア決定モジュールは3回実施され、その結果、これらタスクは同じマイクロプロセッサ上で非同期的に実行されるので、安全ではない。エラーの注入段階によりサブタスク間のエラーの伝播が示された、これは異なるサブタスク間のエラーに対するバリアがないことを示す傾向にある。

【0037】

特異事象の割合の推定は、宇宙で使用される一般的なコンピュータ用に行なわれた。明らかに、この割合は、メモリーセルの数や使用されるユニットセルの感度の値などの仮定に依存している。限界のシミュレーション。

参考文献〔9〕は、トランジットエラーに依存する電子或いはデジタルシステムに対する処理手順の一般的概要を示し,且つ処理手段として,空間的冗長度と時間的冗長度を記述している。

参考文献〔10〕は、エラーに依存する電子システムに対する処理手順を公表している。このシステムは,冗長シーケンスの使用を回避するために単一の物理的チャネルの使用を支援する。

参考文献〔11〕は、メモリ管理及び仮想メモリをイネーブルにするためいに最近のマイクロプロセッサに適用されるプロセスを記述している。情報に対して制限されるアクセス原則が考察される。頁或いはその一部へのあるアクセス権は、各処理毎に与えられ、これらのアクセス権は,リアルタイムで制御される。衛星の挙動に管理に関するエラーについても、例えば,リアクションホイールのような、挙動及びオービット制御システムにおける媒体臨界アクチュエータで発生された悪いコマンドが考えられた。次に、単一事象が低いが,十分には低くないことが判ると,この現象は,二つのタイプの制御に関して無視され得る。

−最大限界制御:火器推進ユニット、バッテリー管理など。一年に数回衛星を失う危険は認められない。

−中間限界制御:リアクションホイール、電磁カプラーなど。飛行、特に商業衛星飛行(観測、電気通信)は、これらのエラー、エラーが限界に近いものであっても、によって発生する姿勢の乱れは認められない。

【0038】

さらに、特異事象の周波数はコンピュータのリアルタイムサイクルよりもきわめて大きい。

【発明の概要】

【発明が解決しようとする課題】

【0039】

本発明の目的は、特異事象に対する感度に関わらず市販部品を使用するために、過渡エラー制約を受ける電子システム用の処理手法を提案し、過渡エラーの様相を検出し、それらを修正することである。

【課題を解決するための手段】

【0040】

本発明は、例えば、宇宙産業において、単一の物理的チャネルにインストールされる2つの仮想チャネルが1つの所定のリアルタイムサイクルで多重化され(仮想チャネルの各実行から生じるデータが使用前に票決できるように記憶される)、かつエラーが検出される場合、進行中のリアルタイムサイクルが禁止され、異常のないコンテキストが再ロードされるコンテキストから始まる次のサイクルの仮実行からなる再開始を行うように再ロードされることを特徴とする、過渡エラー閉じ込みを受ける電子システムのための処理手順に関するものである。

【0041】

したがって、エラー修正は、異常のないコンテキスト、換言するとエラーが検出されたサイクルに先行するリアルタイムサイクル中計算されたコンテキストを再ロードすることによって、次に復元されたコンテキストから始まる、エラーが検出されたサイクルに続くサイクルの仮実行(換言すると新しい捕捉を繰り返すこと)によって行われる。この種の修正は、ソフトウェア(エラーが検出される)の実行におけるリアルタイムサイクルの「穴」の出現によって特徴付けられる。

【0042】

有利なことには、下記の特徴も可能である。

【0043】

3つのエラー制約領域(時間、ソフトウェアおよびハードウェア)がある。すなわち、エラーの時間制約は、一方のリアルタイムサイクルから他方のリアルタイムサイクルに伝達できない。エラーのソフトウェア制約は、一方のソフトウェアタスクから他方のソフトウェアタスクにあるいは一方の仮想チャネルから他方のチャネルに伝達できない。エラーのハードウェア制約は、捕捉エレクトロニクスあるいは制御装置で生じるエラーが制御エレクトロニクスに伝達されることを防止する(誤ったコマンドの生成が全くない)。

【0044】

エラー検出/修正コードによって特異イベントから保護される制御装置のメモリプレーンも使用できる。

【0045】

選択された検出/訂正細分性は,コンピュータで実行されるソフトウエアタスクの動作サイクルであっても良く、それは、コンテキストに属する変数の数が二つのリアルタイムサイクル間の境界で完全に最小に減少される主題におけるエキスパートに知られている通常の解決策に比較して、定期的に起動される“バックアップコンテキスト”機能及びエラー訂正時起動される“回復コンテキスト”機能によって付加される制約を減少出来る。

【0046】

「バックアップコンテキスト」機能は、規則的に作動され、インデックス変更によって得られてもよく、この機能がソフトウェアの開発費用あるいはマイクロプロセッサによるこの機能の実行時間に殆ど影響を及ぼさない長所がある。唯一の影響は、検出/修正粒度、すなわちリアルタイムサイクルを超える寿命でコンテキスト変数をコピーするこの機能の使用にある。

【0047】

エラー訂正の間に起動される“回復コンテキスト”機能は,ヘルシーであると考えられているコンテキストを指示するインデックス、換言すれば、前のリアルタイムサイクルにおける“エラーのないこと”がスワップされる必要がないが,通常(換言すれば、エラーが検出されない時)、それはスワップされるという事実を使用することによって達成されてもよい。この“ノースワップ(スワップをしないこと)”は,エラーが検出されるリアルタイムサイクルの禁止に固有であり,従って、この機能は、ソフトウエアの開発コストやマイクロプロセッサによってこの機能の実行時間には影響を与えないという利点を提供し、このことは、この主題におけるエキスパートには典型的に公知の解決策ではない。

【0048】

特定のアクセス権検査装置に関連したメモリのセグメンテーションを使用でき、この装置は、異なる任意のセグメントサイズを可能にする。アクセス権を検査するこのハードウェア装置は、いくつかのアクセス構成を可能にでき、各構成は、1つあるいはいくつかの非隣接セグメントへのアクセスを可能にする。アクセス権を検査するこのハードウェア装置は、1つあるいはいくつかのキーの論理組み合わせによるアクセス構成の選択も可能にする。

【0049】

票決される変数/データは、異なる用途で再使用できる簡単な票決モジュールを得るために均一に広がる。この場合、票決モジュールはソフトウェア開発費用にごくわずかな影響を及ぼす。

【0050】

特に、ソフトウェア監視プロセッサおよびハードウエアを含む一貫性がソフトウェア検査によって得られるソフトウェア票決を使用できる。エラーが全く検出されない場合、票決は制御エレクトロニクスへの転送の許可も作動させる。

【0051】

最後に、アクセス権を満たし、この転送のバリディティ時間(時間バリディティウィンドウ)を制限するハードウェア装置によって制御エレクトロニクスへの転送の検査をできるので、ハードウェアエラー制約領域の境界を定める。

【0052】

したがって、本発明による方法は、

−タイミングよくタスクの実行の複製および生成されたテーブル票決と、

−テーブル票決による全データエラーの検出と、

−アクセス権の票決および検査のためのハードウェアおよびソフトウェアセキュリティ装置によるエラーの順序付の検出と、

−アプリケーションに透過である修正とを含み、あらゆることはリアルタイムサイクルに「穴」があるかのように行われる。

【0053】

特定の開発の最小化は、本発明による方法の長所の中の1つであり、すなわち:

−ソフトウェアの場合:

・表で票決される変数のグルーピング、

・通常異なるアプリケーションで再使用可能である「コマンドの票決および生成」モジュール、

・本発明による方法の管理(時間重複、メモリアクセスおよび時間バリデーションウィンドウを監視するハードウェア装置、およびエラー修正の管理)。

−ハードウェアの場合:

・メモリアクセスおよび時間バリデーションの監視;これらは、FPGA回路、あるいは(さらによい)マイクロプロセッサ(アドレス復号化等)に通常関連したASIC回路に統合されねばならない普通の部品であり、これらは異なる用途でも再使用可能である。

・通常のフォールトトレラント機構による重要なコマンドのエレクトロニクスの保護(例えば、計装)。

【0054】

したがって、本発明による方法は下記の長所:

−非常に小さいハードウェアの開発、

−非常に小さいソフトウェアの開発、

−他のフォールトトレラントアーキテクチャと比較される周期的に起きる費用(唯一つのコンピュータ)の最少化、

を有し、これらの特徴はフォールトトレラントアプリケーションでしばしば見つけられるものではない。

【0055】

さらに、宇宙産業の「市販」部品の使用は下記の主要な長所を有する:

−主要なサプライヤーはもはやこの市場に供給しないために、この使用は「高信頼性」部品の有効性の確認された減少の問題を解決する。

−コストの減少、バジェットコンテキストによって刺激される様相。「高信頼性部品」項目は装置の全開発費用で無視できなく、その周期的に起こる費用において無視する。

−エレクトロニクスの容積の減少および/または機能性の増加のためにより高い実行機能/部品の使用。

−宇宙に反動的なアクセスを与えるためにプロジェクトの開発時間を減少させ、一般的には「高信頼性」部品に対する調達時間は1年あるいは2年である。

【0056】

有利なことには、本発明による方法は、一般的な目的を有し、これらのエラー(宇宙放射線、電磁パルス等)の発生源とは無関係に過渡エラー制約を受ける全ての型式のコンピュータで使用されてもよいが、宇宙分野に当然応用可能である。

【0057】

本発明は、特にマイクロプロセッサの周辺に製造される制御装置を含むコンピュータのメモリアクセス監視装置(SAM)、およびセグメントに分割され、各セグメントがこの装置に利用可能なキーの全部あるいはいくつかの論理機能によって規定されるアクセス権を有することを特徴とするメモリにも関連し、各セグメントへのアクセス権はリアルタイムで制御される。幾つかのセグメントは,マイクロプロセッサが良好な動作状態にあるという非常に良好な可能性がある時にのみ、アクセスを許可した。従って、重要なデータ(例えば,コンテキストデータ)の安全な記憶が可能となる。

【0058】

有利なことは、デバイスにおける利用できるキーのプログラミングに依存して、一セットの非連続セグメントがあるセグメントに対しては読み出し時において、及び他のセグメントに対しては読み出し/書き込み時にアクセス可能である。

【0059】

有利なことには、セグメントのサイズは、所定のアプリケーションに対して最適化できるように任意である。

【0060】

利用できるキーのセットの定義、これらのキーの組み合わせのための論理機能、及びキーのプログラミングの関数としてアクセス可能なセグメントの構成が指定される。

キーの固有定義に関連するこの装置の固有機能を規定することも可能である:例えば、

−セグメントの中の1つが、コンピュータの例外状態の機能としアクセスできる書き込み許可を有するので、重要なデータ(例えば、コード)の確実な記憶を可能にする、

−重要なデータの確実な記憶を可能にするセグメントが対(「旧」セグメントおよび「新」セグメント)(フリップフロップで作動する)でグループ化される。

【図面の簡単な説明】

【0061】

【図1】公知の技術によるソフトウェアモジュール三重冗長性を示す。

【図2】この説明で参考として使用されるハードウェアアーキテクチャのためのブロック図を示している。

【図3】参考ソフトウェアアーキテクチャの時間図を示している。

【図4】参考アーキテクチャの順序付けを示している。

【図5】グローバルオペレーティングシーケンスを示す:図5Aはグローバルオペレーティングシーケンスなしの手順を示す;図5Bは本発明による処理を使用する手順を示す。

【図6】本発明による処理の機能的説明を示す。

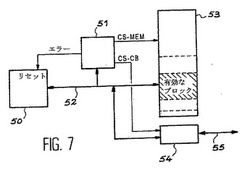

【図7】本発明による全処理のブロック図を示す。

【図8】ハードウェアレベルのエラー閉じ込み領域を示す。

【図9】本発明による処理のシーケンスおよびコンテキストテーブルのスワッピングを示す。

【図10】データの票決を示す。

【図11A】異なる「ソフトクラッシュ」形式の順序付けエラーおよび票決/コマンド生成手順の構造を含む、本発明による処理のための票決の構造を示す。

【図11B】異なる「ソフトクラッシュ」形式の順序付けエラーおよび票決/コマンド生成手順の構造を含む、本発明による処理のための票決の構造を示す。

【発明を実施するための形態】

【0062】

宇宙アプリケーションのための本発明による方法が、この説明の残りを通じて実施例として考慮されている。

【0063】

宇宙に使用されるコンピュータの代表的な、そして包括的なアプリケーションが下記に提供され、図のハードウェアおよびソフトウェアのポイントを考慮している。図2に示される参照アーキテクチャは、本発明による方法の説明のための根本原理として使用されている。

【0064】

図2に示される搭載管理ユニット10は、

−マイクロプロセッサ周辺に作られる制御装置11と、

−マスメモリ12と、

−パワーインターフェイス13、ペイロードインターフェイス15、パイロテクニクスインターフェイス16、サーマルインターフェイス17、姿勢および軌道制御システムインターフェイス18と、

−データバス19を介して連結されることと、

−リモートコントロール−リモート測定インターフェイス14と、

−監視および再構成エレクトロニクス20と、

−交換パワーを生成するDC−DCコンバータ21は、ACを供給し、パーマネントパワーは、APを供給することと、を備えている。

【0065】

パワーインターフェイス13は、太陽熱発電機25とバッテリ26とに連結されている。

【0066】

リモートコントロール−リモート測定インターフェイス14は、トランスミッタ/レシーバに連結され、デュプレクサ27は、アンテナ28、29に連結されている。

【0067】

ペイロード31は、アビオニクスバス32を介して制御装置11に、マスメモリ12に、高速シリアルリンク33を介してリモートコントロール/リモート測定インターフェイス14に、そしてペイロードインターフェイス15に連結されている。

【0068】

パイロテクニクスインターフェイス16は、展開可能なシステム35に連結されている。

【0069】

サーマルインターフェイス17は、ヒータおよびサーミスタンス36に連結されている。

【0070】

姿勢および軌道制御システムインターフェイスは、センサC1、C2、・・Cnに、アクチュエータA1、A2、・・Amに、そしてリザーバ圧力センサ37に連結されている。

【0071】

その結果、このタイプのアーキテクチャは、異なる処理モジュール(制御装置モジュール)と、入出力モジュール(捕捉モジュール、制御モジュール)とで構成されている。入出力モジュールは、低レベルエレクトロニクス(アナログ/デジタルコンバータ、あるいはデジタル/アナログコンバータ、デジタルまたはアナログチャネルマルチプレクサ、リレーなど)を含んでいる。

【0072】

モジュールは、無関係に、バックパネルバスによって連結されるボード、あるいはアビオニクスバスを介して連結される完全なボックスであってよい。2つの場合、バスへのインターフェイスは、マスタBus Coupler(バスカプラー)(CB)を介して制御装置モジュールに、また加入者バスカプラーによって他のモジュールに作られる。

【0073】

図3に示されるような参照ソフトウェアアーキテクチャは、処理タスク(たとえば、姿勢および軌道制御システムタスク、サーマル制御タスク、リアルタイムクロックタスク、搭載管理タスクなど)で構成され、各タスクは、コンピュータから出力される結果(制御、あるいはコマンド)を生成し、そして計算されるとき、これらの結果は、生成される(すなわち、コンピュータからの出力)。Acquisitions(捕捉)(あるいはAcq)は、時間一貫性(たとえば、姿勢および軌道制御システム)により、リアルタイムサイクルの開始時に分類される。

【0074】

図3において、タスクA、BおよびCは、説明を明瞭にするために、同一周波数で示されている。

【0075】

これらのタスクのアクティビティは、サイクルReal Time Interrupt(リアルタイム割り込み)(IT−TR)によって誘発されるリアルタイムサイクルレートで実行される。このサイクルは、周期的にいくつかのタスクを開始し、そしてこれらのタスクは、リアルタイムサイクルと同一の周波数か、あるいはリアルタイムサイクルのサブ周波数かのいずれかで作動する。他のタスクは、非同期であり、イベントに基づいて初期化される。

【0076】

この図は、参照ハードウェアおよびソフトウェアアーキテクチャを示し、図4において供給されている。この図は、制御装置40と、センサ42に連結される捕捉エレクトロニクス41と、アクチュエータ44に連結される制御エレクトロニクス43とを示し、これら2つのエレクトロニクス41、43および制御装置は、データバス45に連結されている。

【0077】

3つのメイン位相Ph1、Ph2、Ph3(すなわち、データ捕捉、データ処理、コマンドの生成)の順序付けは、エレクトロニクス40、41、43の3つの独立した部分を含み、位相Ph2,Ph3は、ネストされている。

【0078】

このアーキテクチャのハードウェア部分は、機能ブロックだけに基づいており、そのため、特別な部品の特有の性質およびエラー検出/修正におけるそれらの能力(あれば)を無視する。その結果、本発明による方法は、自制的である。とはいえ、所定のアプリケーションに使用される部品に一体化されるフォールトトレラント構造の使用により、本発明だけによる方法と比べてエラー適用範囲比率を改善することが可能である。

【0079】

特異イベントを受けやすい参照アーキテクチャのポテンシャルエラーシグネチャが測定された。その結果は、エラーが、2つの重要なクラスに分類されることが可能であるということであった:

−データエラーと、

−サブクラスにも共有される順序付けエラー:

・「ソフトクラッシュ」:不正な接続だが、マイクロプロセッサは、指示により位相に戻り、多少不安定で、指示の順序付けを続行することが可能である;

・「ハードクラッシュ」:マイクロプロセッサは、操作可能でなく、たとえば、マイクロプロセッサは、指示と位相が同じでなく、マイクロプロセッサは、データを指示レジスタにロードし、スタックポインタが妨害されて、指示順序付けがブロックされ、不可能なイベント、無限ループなどを待つ。

【0080】

これら2つのクラスは、それら自体いくつかのサブクラスに再分され、最も重要なものは、アドレスエラーに関する。

【0081】

「ソフトクラッシュ」と「ハードクラッシュ」との間の識別が重要である。マイクロプロセッサの外側のハードウェア装置は、通常、「ハードクラッシュ」を検出する必要がある(すなわち、ウォッチドッグ)が、ソフトウェア装置は、たとえ不安定であるとしても、マイクロプロセッサが、ソフトウェアクラッシュの場合、コードを実行し続けるので、「ソフトクラッシュ」を検出するのに十分である。

【0082】

そのうえ、「抑制されていないマイクロプロセッサ」は、宇宙ミッションのための破局的結果を有することができるアクションが可能なので、マイクロプロセッサクラッシュは、クリティカルエラークラスを形成し、そのため、短い待ち時間でそれらを検出するために、あらゆる試みを行い、および/または検出されていないエラーに続く不良コマンドの確率を最小にするために、エラー制約領域を生成することが重要である。

【0083】

ここでは、本発明に自体による方法のオペレーションについて記述する。

【0084】

全体的に、検出/修正に使用される粒度は、コンピュータの基本リアルタイムサイクル、たとえば、プラットフォームコンピュータにおける姿勢および軌道制御システムタスクのサイクルである。

【0085】

本発明による方法(構造的デュプレックスにおけるような)の目的は、コンピュータが、監視されることなく作業し、次に、コンピュータから出力されるデータ(コマンド)、あるいは修正のために使用されるデータ(コンテキスト)だけを選択することか、あるいは「票決する」ことを可能とする。

【0086】

粒度のためにリアルタイムサイクルを選択することにはいくつかの利点がある:

−これは、捕捉がアクセスされ、あるいは大部分のセンサ/アクチュエータが制御される周波数であること、

−かなり制限された数の「アクティブ」データが、リアルタイムサイクルの終りに使用可能である;多量の中間データがなく、そしてローカル変数が使用されていないこと、

・検出のために、それらは、票決される一連のテーブルに格納されていることと、

・単純で、良好に配置された再開始コンテキストが修正のために使用可能であること。

【0087】

特に、票決がタスクの終りで行われるので、所定タスクのための検出/修正粒度が、このタスクの周波数である。その結果として、姿勢および軌道制御システムタスクが10Hzで、そしてサーマルタスクが1Hzで考慮されると、粒度は、姿勢および軌道制御システムのためには10Hzであり、サーマルタスクのためには1Hzである。明瞭にするために、リアルタイムサイクルによる「粒度」は、「タスクによって」よりはむしろ本文書の残りに使用されている。

【0088】

構造的冗長性を削除すると同時に、タイプに関係なく、例外なく、すべてのエラー(データエラー、アドレスエラー、順序付けエラー、構成エラーなど)を検出する手段であるデュプレックス(出力と比較すれば同一のソフトウェアを実行する並列の2つの同一システム)の効率から利益を得るために、本発明による方法は、単一の物理的チャネルに基づきデュプレックスオペレーションを設置することから成る。所定のリアルタイムサイクルにおいて、同一の物理的チャネルに位置される2つの仮想チャネルは、タイミングよく多重化され、仮想チャネルの各実行から生成されるデータは、「時間多重化されたデュプレックステーブル」(たとえば、コマンド、コンテキスト)に格納され、そのため、それらは使用前に票決されることが可能である。

【0089】

検出後、修正は、現在のリアルタイムサイクルを禁止することと、再ロードされたコンテキストから開始する次のサイクルの仮実行から成る再開始を行うために、異常のないコンテキストを再ロードすることとから成る;リアルタイムサイクルに「穴」があるかのように、すべてのことが生ずる。

【0090】

本発明による方法は、特異イベントによって生成されるエラーが一時的のものであるという事実に基づいている;第1の仮想チャネルの実行中に生ずるこのタイプのエラーは、第2のシステム実行中再生成されない(逆もまた同じである)。これに対し、本発明による方法は、静的エラー、たとえば、部品の故障(故障したビットなど)、あるいは特異イベントによるいくつかのエラーでさえを検出することができず、それは、永久エラー(たとえば、シーケンサのブロッキング)を生ずる。

【0091】

票決モジュールの出力側のアクション、換言すれば、制御エレクトロニクスへのデータ転送(すなわち、データバス)および制御エレクトロニクス自体は、本発明による方法によって保護されない。ユーザは、エラーのないようにする必要があるこれらクリティカルコマンドを決定し、そして当業者に周知である構造によって、それらを保護するために、システム分析を行う;データの符号化、自己検査回路、制御エレクトロニクスの計装など。

【0092】

図6は、本発明による方法の機能の説明を含んでいる。

【0093】

この図は、データフロー(太い線)を示し、それによると、仮想チャネル♯1 47は、捕捉♯1を受信し、仮想チャネル♯2 48は、捕捉♯2を受信し、確実な票決者49は、これら2つのチャネル47、48から出力を受信して、コマンドを発行する。修正のための再開始を初期化するべく、再ロードされたコンテキストリクエストをするために、確実な票決モジュール49を2つの仮想チャネル47、48に連結するエラー信号(細い線)もある。

【0094】

本発明による方法のグローバルシーケンスは、図5Aおよび図5Bに示されている:

−図5A:本発明による方法を有さないシーケンスであり、コマンドは、それにもかかわらず、処理の終りに分類されている、

−図5B:本発明による方法を有するシーケンス。

【0095】

図5Aは、2つのリアルタイムサイクルN、N+1と、サイクルN+2の開始を示している。

【0096】

各リアルタイムサイクルは、時間において異なる4つの位相から構成されている:

−データ捕捉、

−コマンドの計算で処理、

−コマンドの送信、

−タスクの取り消しおよび待機、この場合、「Scrub+Standby(取り消し+待機)」と呼ばれる。

【0097】

図5Bは、各リアルタイムサイクルが構成される本発明による方法を示している:

−仮想チャネル♯1(ChV ♯1)の捕捉、

−仮想チャネル♯1の処理;結果は、テーブルTAB ♯1に格納される、

−仮想チャネル♯2(ChV ♯2)の捕捉、

−仮想チャネル♯2の処理;結果は、テーブルTAB ♯2に格納される、

−テーブルTAB ♯1およびTAB ♯2の票決、

−コマンドの生成、

−タスクの取り消しおよび待機。

【0098】

図7は、本発明による全体の方法の模倣図を示し、本発明の実施形態に必要なすべての回路を表わしている。

【0099】

第1のマイクロプロセッサモジュール50は、すべてのソフトウェア構造を、特に、

−タスクの時間複写、

−テーブルへの変数の配置、

−確実な票決、

−再開始による修正、

−ハードウェア構造の管理、

を管理する。

【0100】

メモリアクセス監視および時間バリデーションウインドウモジュール51は、マイクロプロセッサ50のバス52と、エラー検出および修正メモリ53と、バスカプラー54とに連結されている。

【0101】

モジュール51は、マイクロプロセッサ50の「Reset(リセット)」ターミナルでエラー信号を、メモリ53で選択信号(「チップ−選択」、CS)を、そしてバスカプラー54で選択信号を生成する。

【0102】

メモリ53は、セグメントにおいて共有され、各セグメントは、特定のアクセス権(キーによるバリデーション)を有している。アクセスを他のコンピュータ機能(捕捉エレクトロニクス、制御エレクトロニクスなど)に供給するデータバス55に連結されるバスカプラー54は、「時間ウインドウ」タイプの信号によって妥当性が検査される。

【0103】

本発明による方法は、下記の特徴に基づいている:

−3つのエラー制約領域(時間、ソフトウェアおよびハードウェア)、

−テーブルに変数/データを配置、

−処理の時間複写、

−各処理の結果の比較によるエラー検出を可能にするユニークな確実なソフトウェア票決モジュール、その票決モジュールは、さらに、コマンドを生成する、

−票決の完全性をチェックするのに関係するソフトウェア監視プロセッサ、

−エラー検出および修正コードによる特異イベントに対して保護される制御装置メモリプレーン、

−前のエレメントを有して、再開始コンテキストを確実にバックアップし、かつアドレスエラーを検出するのに使用されるハードウェアアクセス権制御装置に関連するメモリセグメンテーション、

−アクセス権を制御するハードウェア装置を介して、データバスを通って制御エレクトロニクスに転送することをチェックし、エラー制約領域の境界を画定すること、

−エラーが生ずる場合、再開始による修正。

【0104】

ここでは、順番に、これらの特徴のそれぞれについて記述する。

【0105】

制約領域

最大エラー制約領域60は、図8に示されるように、捕捉エレクトロニクス41と、制御装置40とから構成される;この図は、図4と同一参照符号を使用している。したがって、エラーが、捕捉あるいは処理を妨害する場合、このエラーは、制御エレクトロニクス43に通過させることができない。この結果、捕捉エレクトロニクス41において、あるいは制御装置40において、特異イベントに続いて生ずるエラーは、不良な衛星用コマンドを生成しないし、またミッションを妨害しない。

【0106】

票決によるこの制約領域60は、票決モジュールが検出することが可能なエラーに効果的である。この制約領域は、さらに、アクセス権チェックの存在により、ほとんど他のエラーに不浸透性である;時間バリデーションウインドウにおけるハードウェア装置が、バスのコマンドの認可されていない発生をブロックする。

【0107】

さらに、他の制約領域は、本発明による方法において画定される:

−修正がリアルタイムサイクルの粒度に基づいているので、リアルタイムサイクルによるエラーの時間制約、

−メモリアクセス監視装置により、ソフトウェアタスクによる、そしてメモリアクセスの監視により、仮想チャネルによるエラー制約。

【0108】

プロセステーブル

本発明による方法のオペレーションは、特に、票決されるデータを含む一連のテーブルに基づく(その結果、これらのテーブルは、複写され、1つのセットは、ChV ♯1によって管理され、もう1つのセットは、ChV ♯2によって管理される)。これらのテーブルは、通常のソフトウェアテーブルとは異なり、デュプレックスオペレーションに特有なので、「時間多重化されたデュプレックステーブル」と呼ばれる。たとえば、

−捕捉テーブル(TAB−Acq)、

−制御テーブル(TAB−Cde)、

−コンテキストテーブル(TAB−Ctxt)。

【0109】

コンテキストテーブルTAB−Ctxt ♯1、TAB−Ctxt ♯2のそれぞれは、実際には、再開始による修正を行うとき、コンテキストを再格納することを可能にするために、タスクの終りに(すなわち、票決の終りに)、2つごとに1つのサイクルをスワッピングすることによって作業する一連の2つのテーブルから構成されている。一連の2つのインデックス(「Old(古いインデックス)」と「New(新しいインデックス)」)は、メモリに格納されて、それらと関連される。

【0110】

このように、たとえば、仮想シーケンス1について、タスクKのサイクル♯Nの間、第1のテーブルは、「New(新しい)」と考慮され、TAB−Ctxt−New ♯1と示され、第2のテーブルは、「Old(古い)」と考慮され、TAB−Ctxt−Old ♯1と示される。タスクKの票決が、何らエラーを検出しない場合、スワッピングは、票決の終りに役割を逆転し、第1のテーブルは、次に、TAB−Ctxt−Old ♯1になり、そして第2のテーブルは、TAB−Ctxt−New ♯1となる。

【0111】

「Old(古い)」の領域は、たとえば、票決されて、異常がないと判断されると、マイクロプロセッサクラッシュからコンテキストの再開始を保護するために、メモリアクセス監視装置による書き込みを禁じられている。

【0112】

順序付け−時間複写

上記に定義される参照ソフトウェアアーキテクチャと比較すれば、本発明による方法は、コマンドが、図3に示されるように、計算されるとき生成されないことを強要するが、むしろどちらかと言えば、それらは、票決を待つテーブルに格納される(図5Bを参照)。処理が2つの仮想チャネルのために終了されるとき、テーブルは票決されて、そして不一致が検出されない場合だけ、票決モジュールがコマンドを生成する;この場合、2つのコマンドテーブルの1つは、バス45を介して制御エレクトロニクス43を通って、制御装置40に送信される。

【0113】

所定のタスクについて、タイプ複写の態様を含む本発明による方法のグローバルシーケンスは、図9を参照として下記に記述されている。

【0114】

この図は、本発明による時間多重化されたデュプレックスのシーケンスと、コンテキストテーブルのスワッピングとを示している。

【0115】

リアルタイムサイクルは、リアルタイム割り込みIT−TRによって初期化される。

【0116】

各リアルタイムサイクルは、下記の位相から構成される:

−シーケンサ/リアルタイムエグゼクティブ(ETR)、

−タスクA、

−シーケンサ/リアルタイムエグゼクティブ、

−タスクB、

−シーケンサ/リアルタイムエグゼクティブ、

−タスクC,

−シーケンサ/リアルタイムエグゼクティブ、

−タスクの取り消しおよび待機。

【0117】

タスクA、タスクBおよびタスクCは、図5Bに示されるように下記のことから構成されている:

−仮想チャネルNo.1 捕捉、

−仮想チャネルNo.1 処理、

−仮想チャネルNo.2 捕捉、

−仮想チャネルNo.2 処理、

−票決およびコマンドの生成。

【0118】

下記のステップがある:

・仮想チャネル No.1(ChV♯1)のための「処理」モジュールの間:

−ChV♯1のデータの捕捉およびTAB−Acq♯11への格納、

−TAB−Acq♯1およびTAB−Ctxt−Old♯1から開始するChV♯1と関連する処理の実行;この処理の結果は、TAB−Cde♯1テーブルおよびTAB−Ctxt−New♯1テーブルに格納される;コマンドは、アクチュエータに送信される制御装置によって生成されない。

【0119】

・仮想チャネルNo.2(ChV♯2)のための「処理」モジュールの間:

−ChV♯2のデータの捕捉およびTAB−Acq♯2への格納、

−TAB−Acq♯2およびTAB−Ctxt−Old♯2から開始するChV♯2に関連する処理の実行;この処理の結果は、TAB−Cde♯2テーブルおよびTAB−Ctxt−New♯2テーブルに格納される;コンピュータは、なんら出力を生成しない。

【0120】

・「票決およびコマンドの生成」モジュール、換言すれば、テーブルの比較およびテーブルに関連するアクションの実行の間:

−逐語的にTAB−Cde♯1とTAB−Cde♯2の比較、

−逐語的にTAB−Ctxt−New No.1とNo.2との比較、

−エラーが検出されない場合、方法は続行し、さもなければ、待機に配置、

−インデックスを変更することによってコンテキストテーブルをスワッピングする:TAB−Ctxt−NewとTAB−Ctxt−oldとを置き換えて、次のリアルタイムサイクルのためのコンテキストとして使用される、

−コマンドの生成、2つのTAB−Cdeテーブルの1つが、データバスを介してコマンドエレクトロニクスにコマンドリクエストを転送するために、連続して空にされる、

−時間多重化されたデュプレックスパラメータの初期化(時間多重化されたデュプレックステーブル、時間多重化されたデュプレックス管理変数)。

【0121】

したがって、図9において、リアルタイムサイクルN+1の間、エラーが、リアルタイムサイクルNの間検出されない場合、タスクAへのエントリコンテキストは、TAB−Ctext−Old(N)であり、このテーブルは、実際には、スワッピングによりTAB−Ctxt−New(N)からのデータを含んでいる;エラーが検出される場合、タスクAへのエントリコンテキストは、TAB−Ctxt−Old(N−1)であり、このテーブルは、コンテキスト交換がエラーの場合に起こらないので、リアルタイムサイクルNにおけるテーブルTAB−Ctxt−Old(N−1)と同一である。

【0122】

モジュール処理の間、チェックサムコードは、票決に提起されるテーブルのそれぞれのために計算され、票決の徹底性(完全性)をチェックすることに関係している。

【0123】

確実なソフトウェア票決

最小として、票決されるのに必要とするデータは、図10に示されるような処理モジュールからの様々な出力である、すなわち:

−不正な動作を生成しないために、コンピュータ(コマンド)から出力されるデータ65、

−再開始コンテキストは異常がないであることを必要とするので、再開始のために使用されるデータ66(コンテキスト−サイクルNが障害状態である場合、異常のないデータN−1は、再開始のために格納される)。

【0124】

このように、処理モジュールから出力されるすべてのデータは、票決される。所定のタスクと関連する票決は、検出/修正の粒度によって定義されるように、このタスクの終りに行われる。

【0125】

票決モジュールに関して、本発明による方法は、下記の特徴を与えることが可能である:

−票決保全装置が画定される場合、特異イベントに耐性のある外部部品を使用する必要がない;アーキテクチャは、したがって、簡素化される;票決は、本発明による方法における他の場所で必要な少数のハードウェア装置からのサポートで、ソフトウェア全体においてマイクロプロセッサ自体によって行われることが可能である。

−ソフトウェア票決は、複写されない。

【0126】

本発明による方法は、デュプレックスアーキテクチャの検出能力の最良使用に基づいており、換言すれば、検出が最も難しく、さらに、潜在的に最も重大な結果を有する順序付けエラーを含むすべてのエラータイプを検出することが可能である。これらのエラーは、時間多重化されたデュプレックステーブルの一貫性に影響を有し、その結果、それらは、ソフトウェア票決が確実であるとすれば、換言すれば、不正に作動するマイクロプロセッサによって誘発されることができないとすれば、それらはソフトウェア票決によって検出される。したがって、適切な装置は、票決が正しいことを確実にするために備えられる必要がある。

【0127】

2つの中央要素は、票決が確実であることを確実にするために備えられる:

−マイクロプロセッサおよび制御装置モジュールが、票決の開始に異常のない状態であることをチェックすること、

−コマンドの生成を認可するために、票決が行われている間に票決が完結することをチェックすること。

【0128】

票決ストラクチャは、「ソフト」クラッシュによって影響を及ぼされるマイクロプロセッサの不良修正の可能性の分析の機能として画定されている:図11Aは、様々な起こり得る「ソフトクラッシュ」タイプの順序付けエラーを示している。

【0129】

「ハードクラッシュ」は、当業者によって通常使用されている方法であるウォッチドッグによって処理される。

【0130】

下記のストラクチャは、タスクKに関連する「Software(ソフトウェア)票決およびコマンド生成」モジュールに使用され、図11Bに示されている:

a)票決の開始時に連結されるマイクロプロセッサの状態と、制御装置モジュールの状態とをチェックすること:スタックポインタが認可された領域内にあることをチェックすること、マイクロプロセッサおよび制御装置カード構成レジスタをチェックすること、

b)票決の間のエラーの確率を最小にするために、可能な場合、キャッシュを禁止すること、

【0131】

c)Vote−Key(票決−キー)変数が、0に等しいことをチェックし、次に、それを1にセットすること(すなわち、票決):この変数は、Software Monitoring(ソフトウェア監視)方法を使用して、マイクロプロセッサの正しい順序付けを全体的にチェックするのに使用されるキーである、

d)票決することが行われることを表示し、そして2つのメモリ領域ChV♯1、ChV♯2への同時アクセスを認可するメモリアクセス監視装置のためのキーを活動化する、

【0132】

e)時間多重化されたデュプレックスによって生成されるすべてのテーブルで票決し、そして票決が、各テーブル:TAB−Ctxt、TAB−Ctxt−Newのために行われるとき、CRC−V票決の間に計算される巡回冗長コードを計算すること、

f)Vote−Key(票決−キー)が、1に等しいことをチェックし、次に、それを2にセットすること(すなわち、コマンド生成)、

【0133】

g)CRC−VをCRC−T処理の間に計算される巡回冗長コードと比較すること、

h)票決が行われることを表示するメモリアクセス監視装置キーを禁止すること、

i)テストe、f、gの結果が正しい場合、次に、時間バリデーションウインドウシステムを使用して、バスカプラー時間バリデーションウインドウを開くこと、

j)コマンドカード構成レジスタを再初期化すること、

【0134】

k)バスカプラーにコマンドを生成すること、

l)コマンドカード構成レジスタをチェックし、そして、検出されるエラータイプの関数としてアクションを行う(通常コマンド再送信);

時間ウインドウは終了されるか、あるいは終了するかである。

m)Vote−Key(票決−キー)が、2に等しいことをチェックし、次に、それを3にセットすること(すなわち、交換および初期化)、

n)メモリに格納される一対の「old(古い)」と「New(新しい)」インデックスを逆転することによって、タスクKのためのコンテキストテーブルをスワッピングすること、

【0135】

o)ChV♯1とChV♯2との間の1の補数値で、「Old(古い)」テーブルは別としてタスクKのすべてのテーブルを初期化すること、

p)「Old(古い)」テーブルを「New(新しい)」テーブルに転送し、そして、この転送をチェックするために票決すること;この転送は、タスクが実行されるたびに、変数が組織的に更新されない場合、変数が長期間有効であることを確かめるために必要である、

q)Vote−Key(票決−キー)が3に等しいことをチェックし、次に、0にセットすること(すなわち、禁止されている)、

r)キャッシュの妥当性を検査すること。

【0136】

「票決/コマンド生成/スイッチ/時間多重化されたデュプレックステーブルの初期化」手順は、割り込まれることができない、すなわち、それは、より優先度の高いタスクによって止められることがない(それは、初期化されると、終了される)。とはいえ、割り込みは、このモジュールに一時的に割り込むことが可能である。

【0137】

ソフトウェア監視プロセッサ

当業者に周知であるSoftware Monitoring Prosess(ソフトウェア監視方法)は、ソフトウェア自体へのマイクロプロセッサ指示の正しいなシーケンスの制御を受け渡す手段である。ソフトウェアは、リニア基本セグメント、換言すれば、2つの結合間のセグメントに分割される。リニアセグメントは、それ自体、分岐指示を含んでいないので、マイクロプロセッサが、このセグメントの第1の指示を実行すると、それは、このセグメントの最後の指示が実行されるまで続行する必要がある。

【0138】

エントリポイントでキーをテストし、かつそれを出口ポイントでチェックすることによって、マイクロプロセッサが、他の場所ではなく、正しいエントリポイントでリニアセグメントを実際に実行したことがチェックされる。

【0139】

票決保全は、このSoftware Monitoring(ソフトウェア監視)方法を含むいくつかの手段を使用する;「Vote−Key(票決−キー)」ソフトウェア変数は、この方法と関連するキーである。この票決モジュールは、アプリケーションソフトウェアの残りが第4のセグメントを表わす方法で、3つの機能セグメント(票決、コマンド生成、交換と初期化)に分割される:

−マイクロプロセッサが、他の場所でなく、出口ポイントで正しく、前のセグメントから実際に出たことを確認するために、Software Monitoring(ソフトウェア監視)方法キーの値は、各セグメントの開始にチェックされ、そして、さらに、そのセグメントが、互いに次々と正しく連鎖されることがチェックされること、

−次に、Software Monitoring(ソフトウェア監視)方法キーが、セグメントの開始でのこのチェック直後、現在のセグメントに対応する値にセットされること、

−マイクロプロセッサが、各セグメントの終りに、他の場所でなく、正しいエントリポイントで現在のセグメントを実際に実行したことがチェックされること。

【0140】

メモリプレーンの保護

メモリプレーンは、従来、休止エラーを検出して、修正するべくメモリプレーン全体を読み取るために、修正コード(EDAC)と、取り消しタスクとによって特異イベントに対して保護されている。これは、同一ワードの多重エラーが検出されること、および/または修正されることができないので必要である。

【0141】

本発明による方法は、

−修正コード(EDAC)の使用による特異イベントに関係する信頼性メモリと、

−アクセス権を監視することによって、アドレスエラー、指示エラー、マイクロプロセッサクラッシュなどに続く不正な書き込みのための信頼性メモリと、に基づいている。

【0142】

メモリアクセス監視装置

Memory Access Monitoring(メモリアクセス監視)(SAM)装置は、従来のブロックメモリ保護ユニットから導出されるハードウェア装置である。それは、境界が画定されたメモリ領域にアクセスしようとするマイクロプロセッサが、実際に、この領域へのアクセス権を有していることをチェックするのに使用される。

【0143】

メモリアクセス監視装置は、最も多くアドレスエラーを検出することが可能である。特に、それは、多数のマイクロプロセッサクラッシュを極めて迅速に検出することが可能である。マイクロプロセッサは、「ソフト」クラッシュ後、たびたび、許容可能なアドレス領域の外側に行くことが可能である。

【0144】

メモリアクセス監視装置は、従来のブロックメモリ保護ユニットと比べるといくつかの特有の特色を有している:

−セグメントのサイズは、任意であり、アプリケーションの関数として画定されること、

−アクセス認可は、メモリアクセス監視装置の内部のレジスタに記憶されるキーをプログラミングすることによって行われ、これらのキーの定義および組合せが、本発明による方法に特有である。

【0145】

下述のことは、メモリアクセス監視装置に一体化されるキーのリストである:

−コードエラーは、2つの仮想チャネルに共通のエラーモードであり、そして票決によって検出されないので、コードを記憶する領域への書き込みアクセスを防止するキーであって、このキーは、メモリだけを読み取るコードがRAMに転送されるとき、コンピュータの初期化の間だけメモリへの書き込みを認可する、

−仮想シーケンスが現在の ChV♯1、あるいはChV♯2であることを表示し、そして、ChV♯1が実行されるとき、マイクロプロセッサが、ChV♯2テーブルを含むメモリ領域にアクセスすることを防止するキー(逆もまた同じ)であって、このキーは、1つの仮想シーケンスが別のものに生ずるエラーに不浸透性になることを可能にする、

【0146】

−票決が現在行われていることを表示するキーであって、このキーが、アクティブであるとき、それは、例外的に、マイクロプロセッサが、2つの領域ChV♯1、ChV♯2に同時にアクセスすることを可能にし、そのため、票決が行われることが可能である、

−現在のタスクを表示し、そしてマイクロプロセッサが、現在実行されるこのソフトウェアタスクのためのテーブルを含むメモリ領域だけにアクセスすることを可能とするキーであって、このキーは、1つのタスクが、別のタスクに生ずるエラーに不浸透性になることを可能にする、

−スワッピングで作業する2つの「Old(古い)」/「New(新しい)」テーブルセットが、「Old(古い)」領域と、「New(新しい)」領域とであることを表示するキーであって、書き込みは、「Old(古い)」領域において禁じられている。

【0147】

時間バリデーションウインドウシステム

Time Validation Window(時間バリデーションウインドウ)(FVT)システムは、革新的なハードウェア装置である。それは、従来の時間カウンタを使用して行われる。それは、ハードウェアエラーを制約る。それは、

−コマンドエレクトロニクス管理コードを実行するクラッシュしたマイクロプロセッサが、アクセス権を正しく肯定応答することなく、コマンドを生成することを防止するように、

−不正な「コマンドに対応するアドレスに書き込む」タイプの指示を実行するマイクロプロセッサが、偶然にコマンドを生成することを禁ずるように、構成されている。

【0148】

その結果、時間バリデーションウインドウ装置は、それらがアプリケーションのために有する潜在的な破局的結果を帯びて、偶然のコマンドからシステムを保護する。それは、制御されたエレクトロニクスへのアクセスを認可するように予め準備されている;時間アクセスバリデーションウインドウが開かれる。

【0149】

上述のエラーの場合、マイクロプロセッサは、インターフェイス手順を徹底的に実行することによって、コマンドエレクトロニクスにアクセスしない;その結果として、認可されないアクセスは、マイクロプロセッサが、時間バリデーションウインドウを予め開かないので、このシステムによって直ちに検出される。

【0150】

時間バリデーションウインドウ装置は、存在するエラーがないという決定をした後準備される。この決定は、第一に、マイクロプロセッサと制御装置との異常のない状態をチェックする(票決の開始時に、その時、「Vote−Key(票決−キー)」変数で、そして票決の間に、「Checksum(チェックサム)」で)ことに基づき、第二に、票決の結果に基づく。

【0151】

修正

修正は、下記のシーケンスに従って実行される:

−エラーが検出されるとき、現在のリアルタイムサイクル(♯N)は、禁止され、そしてコマンドは生成されない;マイクロプロセッサは、待機モードに進み、次のリアルタイムサイクルを待つ、

−次のリアルタイムサイクルN+1は、前のコンテキストN−1から実行され、信頼性のないコンテキストNからは実行されず、そして現在のサイクルN+1のための捕捉から実行される。

【0152】

不正なリアルタイムサイクルは、リプレイされず、行われるすべては、現在のリアルタイムサイクルを禁止し、かつ前のサイクルのコンテキストを再格納することである。エラーが生ずると、マイクロプロセッサは、それが待機状態に置かれるので、現在のリアルタイムサイクルのためのコマンドを生成しない。すべてのことは、リアルタイムサイクルに「穴」があるかのように生ずる。

【0153】

修正は、特別のアクションを必要としない;マイクロプロセッサは、検出後待機状態に置かれ、その結果として、それは、票決モジュールの実行を続行しない。これは、当然のことながら、票決モジュールの終りに起こる「Old(古い)」コンテキストと「New(新しい)」コンテキストとのスワッピングを防止する。

【0154】

方法によって検出される一時的な性質のエラーとすれば、単一の再開始の試みが行われる。この試みが成功しない場合、コンピュータは、完全に再初期化される必要がある。

【0155】

シーケンサ−リアルタイムエグゼクティブ

ソフトウェアタスクの順序付けを可能にするシーケンサ、あるいはリアルタイムエグゼクティブは、直接に保護されない。対象は、市販のエグゼクティブを使用し、そのため、フォールトトレラント構造を含むように、それに何らかの変更をすることがない。

【0156】

これに反して、総実行時間と比べてこれらのタスクに専用の実行時間は極めて少ない。その結果として、タスクスケジューリングエラーは、2つの仮想チャネルに共通のモードであり、検出不可能であるが、適用範囲比率で極めて小さな影響を有している。

【0157】

さらに、制約領域は、不良コマンドが初期化される前にいくつかの検出されないエラーをブロックすることが可能であり、スケジューラから起こるエラーの影響を減少する。

【0158】

変形実施形態

本発明による方法に対する変形は、特に、その特徴のいくつかを簡素化することによって可能であり、たとえば、

−票決保全構造の簡素化:チェックサム計算の削除、十分であると考慮されるソフトウェア監視方法によるチェック、

−メモリアクセス監視装置の簡素化:2つのシーケンス間の同一エラーの可能性が、極めて少ないので、ChV♯1とChV♯2との間の不浸透性仕切りが不要(現在の仮想シーケンスを表示するキーの削除)。

【0159】

本発明による方法の開発および実施形態

本発明による方法は、最も包括的で、最も徹底的な可能性のあるバリデーションを生成し、かつ最大に可能性のあるエラー適用範囲比率を測定するために、開発された。

【0160】

目的

目的は、これを最後にこの方法を有効にするために、代表的な宇宙アプリケーションを表わすハードウェアおよびソフトウェア実施形態(モックアップ)を有することである。宇宙プロジェクトは、実際には、予備段階における様々な可能性のある解決法を分析している。新しい解決法について、モックアップが、正しいオペレーションと、プロジェクトチームがその使用について決定する前に、かなりの遅延を生ずる必要性への適合とを説明する試みにおいて使用されている。

【0161】

その結果として、この段階の前に、包括的なバリデーションが、要求仕様書、施行仕様書、施行ファイル、バリデーション結果、回復率測定などを含む完全なファイルを興味あるプロジェクトに供給するために企てられている。

【0162】

このように、予備段階において、すべてのプロジェクトは、モックアップを再開発する必要性がなく、この方法のための完全な開発/バリデーションファイルを有することが可能である。その結果として、(たとえば、監査により)、プロジェクトの必要性を満たす方法の適合が、選択についての決定をするために、迅速に決められることが可能である。

【0163】

バリデーション方法

方法は、障害の注入によって妥当性が検査される。したがって、独立した対象で2つのタイプの注入がある。

−第1の段階において、確定的エラーがソフトウェアによって注入される。この注入は同期であるので、エラーシナリオは、方法が障害状態であるとき、再プレイされることが可能である。この段階は、このように、方法の妥当性を検査するのに、かつ可能な場合、エラー検出/修正パフォーマンスを改善するために、それを修正するのに使用されることが可能である。

−第2の段階において、ランダムエラーは、粒子加速器を使用することによって、粒子ビームを本実施形態のメイン部品に印加して注入される(重イオン、プロトン)。この段階は、前の段階に相補的であり、注入されたエラースペクトルがより広いので、端から端にバリデーションを可能にする。さらに、エラーの分布が、リアルアプリケーション環境を表わすので、それは、方法のエラー適用範囲比率を精密に測定することが可能である。

【0164】

ハードウェア実施形態

開発されたハードウェア実施形態は、主として、処理ユニット、捕捉ユニットおよび可観測性ユニットの3つの部分から構成されている。

【0165】

処理ユニットは、Power(パワー) PC 603eタイプのマイクロプロセッサとそのメモリ、および方法のすべてのハードウェア構造を一体化するプログラム可能な部品周りで開発されている。

【0166】

捕捉ユニットは、マイクロプロセッサのためのいくつかの捕捉チャネルを模擬実験し、これらのチャネルのそれぞれは、特別の特徴を有している:マイクロプロセッサの要求で作られる捕捉(簡単なセンサのシミュレーション)、周期的に作られ、そしてマイクロプロセッサは、それらが到達するときに読み取る必要がある捕捉(衛星センサ、あるいはGPSなどのインテリジェントセンサのシミュレーション)、リモートコマンドの受信など。これらの捕捉チャネルは、PIC 16C73Aタイプのナノコントローラの周りに作られている。

【0167】

可観測性ユニットは、本実施形態の制御計装(ソフトウェア、マイクロプロセッサの可観測性をロードなど)およびマイクロプロセッサによって作られる動作のシミュレーションを可能にするチャネルを一体化する。このチャネルの出力は、それが一時的なエラーによって影響を及ぼされるという事実にもかかわらず、コンピュータによって生成される障害動作がないことを立証するために、組織的にチェックされる。

【0168】

ハードウェア実施形態

開発されたソフトウェアアプリケーション(すなわち、ソフトウェア実施形態)は、宇宙において、あるいは他のアプリケーションにおいて、搭載リアルタイムアプリケーションをできるだけ表わすために、下記の特徴を有している:

−後で、市販用リアルタイムエグゼクティブと置き換えられる周期シーケンサに基づく順序付け、

−異なるプライオリティを有するいくつかのメインアプリケーションタスク(たとえば、6個)、それらのいくつかは、周期的であり、その他は、非同期であり、非周期的である;それらのタスクの1つは、宇宙機の姿勢制御プログラムのコアである、

−アプリケーションは、リアルタイムクロックの制御のもとに実行されるリアルタイムサイクルに基づき、アプリケーションタスクは、異なる間隔を有している、

−いくつかのアプリケーションタスク、たとえば、3つのアプリケーションは、より優先度の高いタスクによって割り込まれる、

−ソフトウェアは、捕捉チャネルから生ずる外部非同期イベントに対してリアルタイムで作用する。

【0169】

〔参考文献〕

【表1】

【表2】

【符号の説明】

【0170】

A1 A3 Am アクチュエータ

C1 C2 Cn センサ

Ph1 Ph2 Ph3 メイン位相

1 仮想チャネル

10 搭載管理ユニット

11 制御装置

12 マスメモリ

13 パワーインターフェイス

14 リモートコントロール−リモート測定インターフェイス

15 ペイロードインターフェイス

16 パイロテクニクスインターフェイス

17 サーマルインターフェイス

18 姿勢および軌道制御システムインターフェイス

19 データバス

20 監視および再構成エレクトロニクス

21 DC−DCコンバータ

25 太陽熱発電機

26 バッテリ

27 デュプレクサ

28 29 アンテナ

31 ペイロード

32 アビオニクスバス

33 高速シリアルリンク

35 展開可能なシステム

36 ヒータおよびサーミスタンス

37 リザーバ圧力センサ

40 制御装置

41 捕捉エレクトロニクス

42 センサ

43 制御エレクトロニクス

44 アクチュエータ

45 データバス

47 仮想チャネル

48 仮想チャネル

49 確実な票決モジュール

50 第1のマイクロプロセッサモジュール

51 メモリアクセス監視および時間バリデーションウインドウモジュール

52 バス

53 エラー検出および修正メモリ

54 バスカプラー

55 データバス

60 最大エラー制約領域

65 データ

66 データ

【技術分野】

【0001】

本発明は、過渡エラー制約を受ける電子システムの処理手順及び、例えば、宇宙関係に使用されるメモリーアクセス監視装置に関する。

【背景技術】

【0002】

本発明による方法は、過渡エラーを受ける全てのコンピュータアーキテクチャに関する。例えば、以下の分野では、この種のエラーを発生する、電子部品に対する妨害環境(放射線、電磁外乱)の影響を受けるコンピュータを使用している。

−周囲環境に重イオンが含まれる、宇宙、原子及び航空産業

−重大な電磁環境の影響を受ける自動車産業

【0003】

宇宙産業は、以下の説明で例として使用する。その理由は、電子部品に発生するランダム過渡エラーは極めて代表的なものであり、またこの理由は、この分野で、最初に本発明による処理方法が開発され、評価されたからである。

【0004】

衛星用のコンピュータ構造の設計者は、宇宙に存在するが、大気によって濾過される放射線の問題に直面している。この放射線には、マイクロプロセッサの内部レジスタ内で、または他の集積部品において、メモリ部品のビットの一時的な状態変化を起こす「特異イベント」効果がある。例えば、これらの特異イベントによって発生するエラーは、データを不正確にする場合がある。その例としては、衛星アクチュエータの制御不良、またはソフトウェアチャネルへの重大な外乱などがあり、これらは例えばマイクロプロセッサのクラッシュによって発生する。

【0005】

現在まで、特異イベントタイプのエラーに対する解決方法は、この現象の影響が極めて少ない「放射線耐性」技術、またはこの現象の影響を受けない「対放射線強化」技術といわれる集積回路技術を使用することであった。産業用マイクロエレクトロニクスの分野では使用されていないこの種の技術は、特に軍事及び宇宙の用途に開発されたものであった。

【0006】

このマイクロエレクトロニクス技術を維持し、この技術を使用した部品を開発する全体的なコスト、つまりこれらの部品の市販コストはかなり高くなっている。強化型回路と市販回路とのコストの比率は、100またはそれ以上の場合がある。

【0007】

「高信頼性」軍事部品の市場占有率は、1960年代の80%から1995年には1%以下へと急激に落ち込んだ。1994年から、米国国防総省は軍事用途への軍事用電子部品の使用を控え始めて、一般市販仕様/規格/部品を軍事用途への使用を拡大加速し始めた。

【0008】

本明細書の最後で参考文献〔1〕に説明されているように、市販電子部品の使用は、宇宙産業が直面しなければならない試練となった。

【0009】

宇宙産業用途に市販部品を使用することは、全ての新規勃興プロジェクトが直面する問題である。解決すべき主な問題は、部品の放射線、特に重イオンに対する感度である。この問題は、以前には「部品」レベルで扱われたが、「構造」レベル、「システム」レベルで解決すべき問題となっている。二つの参考文献〔2〕と〔3〕で説明したように、衛星及びその搭載電子部品は、異なった粒子(電子、重イオン、陽子)で構成される放射線環境の影響を受ける。これらの粒子は大気によって濾過されるので、地上のシステムには適用されない。

【0010】

これらの粒子は、以下の理由によると考えられる。すなわち:

−一部は銀河系の外から発生する宇宙放射線、また一部は非常に高いエネルギーイオンからなる銀河系内の宇宙放射線

−地球大気と太陽粒子との間の相互作用に続いて発生した閉じこみ電子と陽子で構成される放射線帯

−陽子と重イオンを放出する太陽の爆発

−コロナプラズマの蒸発により発生する太陽風であって、これにより、低エネルギー陽子とイオンが太陽の引力から抜け出せるようになる、である。

【0011】

これら高エネルギー粒子が、電子部品にぶつかり、通過して、粒子のエネルギーの一部を電子部品に伝えて、通常の作動を乱すようになる。これらの問題は、重イオンと陽子によって発生する「特異イベント」といわれる。

【0012】

これら特異イベントは、2進値を記憶するセル内のエラーの発生に対応していて、ビットエラーを引き起こす。一般的に、単一ビットは重イオンによって変更される。これらの現象は重大ではなく、新しいデータがその後に書き込まれる。同じセル内で他の特異イベントが発生しない限り、新しいデータはエラーなく記憶される。これは、本明細書のこれ以後で、これらの現象により発生するエラーを特徴づけるために使用される用語「過渡不良」のためである。

【0013】

前述したように、衛星への搭載電子部品の製造は、一般には、放射線の影響を受けない部品を使って行なわれる。その理由は、その部品は特にこの目的のために製作されていること、または特にこの目的のために製作されていない部品の選定によるためである。

【0014】

大規模に、宇宙用途に市販部品を使用するためにある最初の可能性は、系統的な放射線のもとで市販部品を試験することにより選定することである。選定に関して、まずこの方法は大変な費用がかかるばかりでなく、効率が悪い。その理由は、望ましいことではあるが、広範な産業規格を必ずしも使うことができないからである。

【0015】

他の経済的にさらに好ましい可能性は、部品選定の制約を緩和することである。これには、放射線によって発生する現象の許容、特に過渡エラーの許容を拡大する方法を探ることが含まれる。つまり、エラーを検出し、修正するアーキテクチャを規定することである。過渡不良を、「部品」レベルではなく、「構造」及び「システム」レベルで考慮することである。

【0016】

参考文献〔4〕、〔5〕と〔6〕では、一連の不良検出、分離及び再生機構について説明されている。機構によっては、単にエラー検出するためだけに使われていて、またエラーを検出しそれにマスクをするもの、エラーを修正するものがある。さらにこれらの機構は、一時的なエラー処理、パラメータ不良またはその両方に適用されている。

【0017】

一般の機構を、特に宇宙産業に適用される数例を挙げて、簡単に説明する。

−不良回避:実際に使用される前に、静的データの系統的更新;部品が使用される前に、部品不良を検出するために、「オフ−ライン」自己試験(標準作動中ではない)

【0018】

−エラー検出または検出/主として、アプリケーション特定集積回路(ASICs)、または集積コントロール装備フィールド・プログラマブル・ゲート・アレー(FPGA)製造用メモリー、通信及び可能であれば論理に適用可能な修正コード。エラー検出及び修正(EDAC)回路は、系統的にメモリー用途に宇宙産業で使用されている。全体メモリーの系統的リロード(または「スクラビング」)機能はこれらの回路に関連していて、実質的に検出/修正を不可能にする休止エラーの集積を回避するために、スクラブタスクとして動作する。

【0019】

−二重及び比較、三重及び多数決(「N モジュラ冗長性」、オーダーNのモジュラ冗長性)。これらの機構には、悪性コマンドは発生しないが、最初の不良で停止するフェールセーフが得られる構造(二重)、不良中に作動可能の状態(「フェイルオペレーショナル」)で、リアルタイムで単一エラーをマスクすることができ、「セーフ」のままで継続する構造(三重)がある。この分類には、また、マイクロプロセッサだけが複製され、「マスター」からのデータ出力は「コントローラー」によって検証される、マスター/コントローラー構造が含まれる。MHS S.A.社により製作されたERC−32マイクロプロセッサはこのような構造を含んでいる。

【0020】

−Nオーダーのモジュラ冗長性構造に関連したマルチプルプログラミング法(「N−バージョンプログラミング」、)、これはまたソフトウェア設計エラーを検出可能である。各コンピュータは、特に共通仕様から始まって開発されたソフトウェアバージョンを備えている。

【0021】

−時間冗長性;その目的は、比較に続く二つの連続実行を使用こと、またはコマンドレジスタをロードすることに続いて単一実行を使用することであり、例えば火器エレメントの引き金を引く極めて重要なコマンドに宇宙で使用される「装填 発射」メカニズムなどの比較と検証をするためにリロードする。

【0022】

−実行時間の確認:「ウオッチドッグ(監視者)」(プログラムが制限時間内で実行されていることを確認するタイムカウンター)は全ての宇宙用コンピュータに使用される。実行時間に関してこれらさらに詳細な確認装置は、ソフトウェアに組み込まれる場合がある。つまり、タスクの時間、通信エレメントからの回答を得るための最大許容時間を確認する。ソフトウェアはまたタスク実行時間にチェックを設定するために使われる。

【0023】

−コントロールフローの検証、例えば、マイクロプロセッサのシーケンスの確認。監視できるのは粗いチェック。ハードディスククラッシュを検出可能である。インストラクションフローチェックは多少複雑な監視プロセッサで終わる。シグナチャ分析を使うチェックは、特に有効で多くの電子装置を必要としない。このコンセプトはMHS S.A.社により製作されたERC−32に盛り込まれているが、参照シグナチャを計算してコードに組み込む特定コンパイラーは、ユーザーに見えるようにするために必要である。

【0024】

−ページ/セグメントによってアクセス権から始まるマイクロプロセッサアドレスの正当性をチェックする。

【0025】

−確率チェック;この原理は、衛星用に姿勢軌道制御システム(SCAO)に使用され、何種類かのセンサーからのデータが不一致を検出するために比較され、またはデータの1項目が前の値についての推定フィルタを使って推定された基準と比較され、またはデータの1項目が予め定義された範囲と比較される。「演算処理に基づいた不良公差」法は確立チェックの一分野であり、その検証は第二演算の実行に基づく。例えば、逆演算は、エラーが発生しない場合に得られる結果から始まる最初の結果を再生する。

【0026】

−比較的複雑なデータ構造を必要とするデータの構造的または語義のチェック

【0027】

−補助誤再生コンセプト、主に、上記で説明した機構が修正できない点で再開する、つまり定期的にコンテクストをバックアップし、最後にセーブされたコンテクストから再開する。

【0028】

−エラー再生の他の手段は、初期検出/修正能力を回復するために、不良コンピュータに正常なコンテクストを移入することにより不良があるリソースを再挿入することである。

【0029】

従来の文書には、また時間冗長性の説明が含まれている。

【0030】

参考文献〔5〕には、連続的にタスクを3回実行して、結果を「票決」する可能性が説明されている。

【0031】

ソフトウェアによりオーダーNモジュラ冗長性型操作の実行の可能性は、また参考文献〔6〕に理論的に説明されている。

【0032】

この文献では、パラメータ不良から過渡不良を区別し、不良を修正でき得る別の方法が説明されている。検出は時間冗長性法ではないが、例えばデータ符号化を含む場合がある。検出が行なわれると、処理は2回行なわれる。2回目の実行でエラーのない結果が得られると、エラーは過渡的であってシステムを再構成する必要はない。それでも、パーマネントな不良である場合は、再構成が必要である。

【0033】

両文献においては、理論的に可能であるので、時間冗長性は測定されるが、実際にこれが実行できる可能性について、何ら記載されていないし、特に進展は説明されていない。検討すらされていない問題がある。特にマイクロプロセッサ自身によって票決される場合、またはマイクロプロセッサと独立した外部装置により決定される場合である。決定の結果は変更できないものとする必要がある。その理由は、マイクロプロセッサ内にデータエラー、シーケンスのクラッシュなどの機能不全が発生する可能性があるが、結果は意思決定の要素だからである。従がって、マイクロプロセッサによって行なわれる票決は、検討されない主な要素となる。さらに、検出が行なわれる粒度は定義されていない。

【0034】

参考文献〔7〕は、僅かながらさらに詳しく記載されている。この文献では、二つのエラー検出方法の比較評価が説明されている。そのうちの一つは、「モジュラ・トリプル・ソフトウェア冗長性」といわれる。通常、モジュラ・トリプル冗長性はハードウェア内で正常に実行される。本文で評価される方法は、ソフトウェアと全てのモジュールの、特に票決モジュールの連続実行による時間冗長性を使い、特にソフトウェアにより行なわれ、同じマイクロプロセッサ上で実行される。従って、これは純粋にソフトウェアの手法になる。本文における図1に対応する図1は、どのように検出が行われるかを示す。つまり、各三つの決定モジュール1,2、と3は三つの手法4,5、と6の実行の結果を比較し、三つの処理ステップの同一性を確認する各決定モジュールからの結果の出力を比較する意思決定段階7が続く。モジュラ・トリプル・ソフトウェア冗長性はMC6800マイクロプロセッサ上でプログラムされる。このソフトウェアを評価するために、1500のエラーが注入された。メモリーはエラー検出と修正回路により、エラーから保護されていない。本書では、検出されないエラーのみが処理されると他を乱すエラーであると結論している。さらに、プログラム間の通信に悪影響を及ぼす全てのエラーは許容されない。

【0035】

本文では、処理が連続して3回実行され(時間冗長性)、決定モジュールが3回実行され決定モジュールの結果はそれ自身で決定される構造の特定例について説明する。結果は固定されていなくて、何故三重化されるかを理解することができる。最終決定は図に示されている最後の段階により行なわれ、間接的にそれは必ず小さくなる(データの数行のみがデータの項目を決定するのに必要である)ことから確実になる。統計的に、直接このモジュールに影響する特異事象は無視できるものであるが、これはマイクロプロセッサシーケンスエラーに対してセキュリティーは与えていない。

【0036】

参考文献〔8〕は、また、LAPX432タイプ、マイクロプロセッサ上での「トリプル・ソフトウェア・モジュラ冗長性」の実行を示している。これは参考文献〔7〕に示されているものと同じ実施形態である。各ソフトウェアサブタスクは連続的に3回実施され、ソフトウェア決定モジュールは3回実施され、その結果、これらタスクは同じマイクロプロセッサ上で非同期的に実行されるので、安全ではない。エラーの注入段階によりサブタスク間のエラーの伝播が示された、これは異なるサブタスク間のエラーに対するバリアがないことを示す傾向にある。

【0037】

特異事象の割合の推定は、宇宙で使用される一般的なコンピュータ用に行なわれた。明らかに、この割合は、メモリーセルの数や使用されるユニットセルの感度の値などの仮定に依存している。限界のシミュレーション。

参考文献〔9〕は、トランジットエラーに依存する電子或いはデジタルシステムに対する処理手順の一般的概要を示し,且つ処理手段として,空間的冗長度と時間的冗長度を記述している。

参考文献〔10〕は、エラーに依存する電子システムに対する処理手順を公表している。このシステムは,冗長シーケンスの使用を回避するために単一の物理的チャネルの使用を支援する。

参考文献〔11〕は、メモリ管理及び仮想メモリをイネーブルにするためいに最近のマイクロプロセッサに適用されるプロセスを記述している。情報に対して制限されるアクセス原則が考察される。頁或いはその一部へのあるアクセス権は、各処理毎に与えられ、これらのアクセス権は,リアルタイムで制御される。衛星の挙動に管理に関するエラーについても、例えば,リアクションホイールのような、挙動及びオービット制御システムにおける媒体臨界アクチュエータで発生された悪いコマンドが考えられた。次に、単一事象が低いが,十分には低くないことが判ると,この現象は,二つのタイプの制御に関して無視され得る。

−最大限界制御:火器推進ユニット、バッテリー管理など。一年に数回衛星を失う危険は認められない。

−中間限界制御:リアクションホイール、電磁カプラーなど。飛行、特に商業衛星飛行(観測、電気通信)は、これらのエラー、エラーが限界に近いものであっても、によって発生する姿勢の乱れは認められない。

【0038】

さらに、特異事象の周波数はコンピュータのリアルタイムサイクルよりもきわめて大きい。

【発明の概要】

【発明が解決しようとする課題】

【0039】

本発明の目的は、特異事象に対する感度に関わらず市販部品を使用するために、過渡エラー制約を受ける電子システム用の処理手法を提案し、過渡エラーの様相を検出し、それらを修正することである。

【課題を解決するための手段】

【0040】

本発明は、例えば、宇宙産業において、単一の物理的チャネルにインストールされる2つの仮想チャネルが1つの所定のリアルタイムサイクルで多重化され(仮想チャネルの各実行から生じるデータが使用前に票決できるように記憶される)、かつエラーが検出される場合、進行中のリアルタイムサイクルが禁止され、異常のないコンテキストが再ロードされるコンテキストから始まる次のサイクルの仮実行からなる再開始を行うように再ロードされることを特徴とする、過渡エラー閉じ込みを受ける電子システムのための処理手順に関するものである。

【0041】

したがって、エラー修正は、異常のないコンテキスト、換言するとエラーが検出されたサイクルに先行するリアルタイムサイクル中計算されたコンテキストを再ロードすることによって、次に復元されたコンテキストから始まる、エラーが検出されたサイクルに続くサイクルの仮実行(換言すると新しい捕捉を繰り返すこと)によって行われる。この種の修正は、ソフトウェア(エラーが検出される)の実行におけるリアルタイムサイクルの「穴」の出現によって特徴付けられる。

【0042】

有利なことには、下記の特徴も可能である。

【0043】

3つのエラー制約領域(時間、ソフトウェアおよびハードウェア)がある。すなわち、エラーの時間制約は、一方のリアルタイムサイクルから他方のリアルタイムサイクルに伝達できない。エラーのソフトウェア制約は、一方のソフトウェアタスクから他方のソフトウェアタスクにあるいは一方の仮想チャネルから他方のチャネルに伝達できない。エラーのハードウェア制約は、捕捉エレクトロニクスあるいは制御装置で生じるエラーが制御エレクトロニクスに伝達されることを防止する(誤ったコマンドの生成が全くない)。

【0044】

エラー検出/修正コードによって特異イベントから保護される制御装置のメモリプレーンも使用できる。

【0045】

選択された検出/訂正細分性は,コンピュータで実行されるソフトウエアタスクの動作サイクルであっても良く、それは、コンテキストに属する変数の数が二つのリアルタイムサイクル間の境界で完全に最小に減少される主題におけるエキスパートに知られている通常の解決策に比較して、定期的に起動される“バックアップコンテキスト”機能及びエラー訂正時起動される“回復コンテキスト”機能によって付加される制約を減少出来る。

【0046】

「バックアップコンテキスト」機能は、規則的に作動され、インデックス変更によって得られてもよく、この機能がソフトウェアの開発費用あるいはマイクロプロセッサによるこの機能の実行時間に殆ど影響を及ぼさない長所がある。唯一の影響は、検出/修正粒度、すなわちリアルタイムサイクルを超える寿命でコンテキスト変数をコピーするこの機能の使用にある。

【0047】

エラー訂正の間に起動される“回復コンテキスト”機能は,ヘルシーであると考えられているコンテキストを指示するインデックス、換言すれば、前のリアルタイムサイクルにおける“エラーのないこと”がスワップされる必要がないが,通常(換言すれば、エラーが検出されない時)、それはスワップされるという事実を使用することによって達成されてもよい。この“ノースワップ(スワップをしないこと)”は,エラーが検出されるリアルタイムサイクルの禁止に固有であり,従って、この機能は、ソフトウエアの開発コストやマイクロプロセッサによってこの機能の実行時間には影響を与えないという利点を提供し、このことは、この主題におけるエキスパートには典型的に公知の解決策ではない。

【0048】

特定のアクセス権検査装置に関連したメモリのセグメンテーションを使用でき、この装置は、異なる任意のセグメントサイズを可能にする。アクセス権を検査するこのハードウェア装置は、いくつかのアクセス構成を可能にでき、各構成は、1つあるいはいくつかの非隣接セグメントへのアクセスを可能にする。アクセス権を検査するこのハードウェア装置は、1つあるいはいくつかのキーの論理組み合わせによるアクセス構成の選択も可能にする。

【0049】

票決される変数/データは、異なる用途で再使用できる簡単な票決モジュールを得るために均一に広がる。この場合、票決モジュールはソフトウェア開発費用にごくわずかな影響を及ぼす。

【0050】

特に、ソフトウェア監視プロセッサおよびハードウエアを含む一貫性がソフトウェア検査によって得られるソフトウェア票決を使用できる。エラーが全く検出されない場合、票決は制御エレクトロニクスへの転送の許可も作動させる。

【0051】

最後に、アクセス権を満たし、この転送のバリディティ時間(時間バリディティウィンドウ)を制限するハードウェア装置によって制御エレクトロニクスへの転送の検査をできるので、ハードウェアエラー制約領域の境界を定める。

【0052】

したがって、本発明による方法は、

−タイミングよくタスクの実行の複製および生成されたテーブル票決と、

−テーブル票決による全データエラーの検出と、

−アクセス権の票決および検査のためのハードウェアおよびソフトウェアセキュリティ装置によるエラーの順序付の検出と、

−アプリケーションに透過である修正とを含み、あらゆることはリアルタイムサイクルに「穴」があるかのように行われる。

【0053】

特定の開発の最小化は、本発明による方法の長所の中の1つであり、すなわち:

−ソフトウェアの場合:

・表で票決される変数のグルーピング、

・通常異なるアプリケーションで再使用可能である「コマンドの票決および生成」モジュール、

・本発明による方法の管理(時間重複、メモリアクセスおよび時間バリデーションウィンドウを監視するハードウェア装置、およびエラー修正の管理)。

−ハードウェアの場合:

・メモリアクセスおよび時間バリデーションの監視;これらは、FPGA回路、あるいは(さらによい)マイクロプロセッサ(アドレス復号化等)に通常関連したASIC回路に統合されねばならない普通の部品であり、これらは異なる用途でも再使用可能である。

・通常のフォールトトレラント機構による重要なコマンドのエレクトロニクスの保護(例えば、計装)。

【0054】

したがって、本発明による方法は下記の長所:

−非常に小さいハードウェアの開発、

−非常に小さいソフトウェアの開発、

−他のフォールトトレラントアーキテクチャと比較される周期的に起きる費用(唯一つのコンピュータ)の最少化、

を有し、これらの特徴はフォールトトレラントアプリケーションでしばしば見つけられるものではない。

【0055】

さらに、宇宙産業の「市販」部品の使用は下記の主要な長所を有する:

−主要なサプライヤーはもはやこの市場に供給しないために、この使用は「高信頼性」部品の有効性の確認された減少の問題を解決する。

−コストの減少、バジェットコンテキストによって刺激される様相。「高信頼性部品」項目は装置の全開発費用で無視できなく、その周期的に起こる費用において無視する。

−エレクトロニクスの容積の減少および/または機能性の増加のためにより高い実行機能/部品の使用。

−宇宙に反動的なアクセスを与えるためにプロジェクトの開発時間を減少させ、一般的には「高信頼性」部品に対する調達時間は1年あるいは2年である。

【0056】

有利なことには、本発明による方法は、一般的な目的を有し、これらのエラー(宇宙放射線、電磁パルス等)の発生源とは無関係に過渡エラー制約を受ける全ての型式のコンピュータで使用されてもよいが、宇宙分野に当然応用可能である。

【0057】

本発明は、特にマイクロプロセッサの周辺に製造される制御装置を含むコンピュータのメモリアクセス監視装置(SAM)、およびセグメントに分割され、各セグメントがこの装置に利用可能なキーの全部あるいはいくつかの論理機能によって規定されるアクセス権を有することを特徴とするメモリにも関連し、各セグメントへのアクセス権はリアルタイムで制御される。幾つかのセグメントは,マイクロプロセッサが良好な動作状態にあるという非常に良好な可能性がある時にのみ、アクセスを許可した。従って、重要なデータ(例えば,コンテキストデータ)の安全な記憶が可能となる。

【0058】

有利なことは、デバイスにおける利用できるキーのプログラミングに依存して、一セットの非連続セグメントがあるセグメントに対しては読み出し時において、及び他のセグメントに対しては読み出し/書き込み時にアクセス可能である。

【0059】

有利なことには、セグメントのサイズは、所定のアプリケーションに対して最適化できるように任意である。

【0060】

利用できるキーのセットの定義、これらのキーの組み合わせのための論理機能、及びキーのプログラミングの関数としてアクセス可能なセグメントの構成が指定される。

キーの固有定義に関連するこの装置の固有機能を規定することも可能である:例えば、

−セグメントの中の1つが、コンピュータの例外状態の機能としアクセスできる書き込み許可を有するので、重要なデータ(例えば、コード)の確実な記憶を可能にする、

−重要なデータの確実な記憶を可能にするセグメントが対(「旧」セグメントおよび「新」セグメント)(フリップフロップで作動する)でグループ化される。

【図面の簡単な説明】

【0061】

【図1】公知の技術によるソフトウェアモジュール三重冗長性を示す。

【図2】この説明で参考として使用されるハードウェアアーキテクチャのためのブロック図を示している。

【図3】参考ソフトウェアアーキテクチャの時間図を示している。

【図4】参考アーキテクチャの順序付けを示している。

【図5】グローバルオペレーティングシーケンスを示す:図5Aはグローバルオペレーティングシーケンスなしの手順を示す;図5Bは本発明による処理を使用する手順を示す。

【図6】本発明による処理の機能的説明を示す。

【図7】本発明による全処理のブロック図を示す。

【図8】ハードウェアレベルのエラー閉じ込み領域を示す。

【図9】本発明による処理のシーケンスおよびコンテキストテーブルのスワッピングを示す。

【図10】データの票決を示す。

【図11A】異なる「ソフトクラッシュ」形式の順序付けエラーおよび票決/コマンド生成手順の構造を含む、本発明による処理のための票決の構造を示す。

【図11B】異なる「ソフトクラッシュ」形式の順序付けエラーおよび票決/コマンド生成手順の構造を含む、本発明による処理のための票決の構造を示す。

【発明を実施するための形態】

【0062】

宇宙アプリケーションのための本発明による方法が、この説明の残りを通じて実施例として考慮されている。

【0063】

宇宙に使用されるコンピュータの代表的な、そして包括的なアプリケーションが下記に提供され、図のハードウェアおよびソフトウェアのポイントを考慮している。図2に示される参照アーキテクチャは、本発明による方法の説明のための根本原理として使用されている。

【0064】

図2に示される搭載管理ユニット10は、

−マイクロプロセッサ周辺に作られる制御装置11と、

−マスメモリ12と、

−パワーインターフェイス13、ペイロードインターフェイス15、パイロテクニクスインターフェイス16、サーマルインターフェイス17、姿勢および軌道制御システムインターフェイス18と、

−データバス19を介して連結されることと、

−リモートコントロール−リモート測定インターフェイス14と、

−監視および再構成エレクトロニクス20と、

−交換パワーを生成するDC−DCコンバータ21は、ACを供給し、パーマネントパワーは、APを供給することと、を備えている。

【0065】

パワーインターフェイス13は、太陽熱発電機25とバッテリ26とに連結されている。

【0066】

リモートコントロール−リモート測定インターフェイス14は、トランスミッタ/レシーバに連結され、デュプレクサ27は、アンテナ28、29に連結されている。

【0067】

ペイロード31は、アビオニクスバス32を介して制御装置11に、マスメモリ12に、高速シリアルリンク33を介してリモートコントロール/リモート測定インターフェイス14に、そしてペイロードインターフェイス15に連結されている。

【0068】

パイロテクニクスインターフェイス16は、展開可能なシステム35に連結されている。

【0069】

サーマルインターフェイス17は、ヒータおよびサーミスタンス36に連結されている。

【0070】

姿勢および軌道制御システムインターフェイスは、センサC1、C2、・・Cnに、アクチュエータA1、A2、・・Amに、そしてリザーバ圧力センサ37に連結されている。

【0071】

その結果、このタイプのアーキテクチャは、異なる処理モジュール(制御装置モジュール)と、入出力モジュール(捕捉モジュール、制御モジュール)とで構成されている。入出力モジュールは、低レベルエレクトロニクス(アナログ/デジタルコンバータ、あるいはデジタル/アナログコンバータ、デジタルまたはアナログチャネルマルチプレクサ、リレーなど)を含んでいる。

【0072】

モジュールは、無関係に、バックパネルバスによって連結されるボード、あるいはアビオニクスバスを介して連結される完全なボックスであってよい。2つの場合、バスへのインターフェイスは、マスタBus Coupler(バスカプラー)(CB)を介して制御装置モジュールに、また加入者バスカプラーによって他のモジュールに作られる。

【0073】

図3に示されるような参照ソフトウェアアーキテクチャは、処理タスク(たとえば、姿勢および軌道制御システムタスク、サーマル制御タスク、リアルタイムクロックタスク、搭載管理タスクなど)で構成され、各タスクは、コンピュータから出力される結果(制御、あるいはコマンド)を生成し、そして計算されるとき、これらの結果は、生成される(すなわち、コンピュータからの出力)。Acquisitions(捕捉)(あるいはAcq)は、時間一貫性(たとえば、姿勢および軌道制御システム)により、リアルタイムサイクルの開始時に分類される。

【0074】

図3において、タスクA、BおよびCは、説明を明瞭にするために、同一周波数で示されている。

【0075】

これらのタスクのアクティビティは、サイクルReal Time Interrupt(リアルタイム割り込み)(IT−TR)によって誘発されるリアルタイムサイクルレートで実行される。このサイクルは、周期的にいくつかのタスクを開始し、そしてこれらのタスクは、リアルタイムサイクルと同一の周波数か、あるいはリアルタイムサイクルのサブ周波数かのいずれかで作動する。他のタスクは、非同期であり、イベントに基づいて初期化される。

【0076】

この図は、参照ハードウェアおよびソフトウェアアーキテクチャを示し、図4において供給されている。この図は、制御装置40と、センサ42に連結される捕捉エレクトロニクス41と、アクチュエータ44に連結される制御エレクトロニクス43とを示し、これら2つのエレクトロニクス41、43および制御装置は、データバス45に連結されている。

【0077】

3つのメイン位相Ph1、Ph2、Ph3(すなわち、データ捕捉、データ処理、コマンドの生成)の順序付けは、エレクトロニクス40、41、43の3つの独立した部分を含み、位相Ph2,Ph3は、ネストされている。

【0078】

このアーキテクチャのハードウェア部分は、機能ブロックだけに基づいており、そのため、特別な部品の特有の性質およびエラー検出/修正におけるそれらの能力(あれば)を無視する。その結果、本発明による方法は、自制的である。とはいえ、所定のアプリケーションに使用される部品に一体化されるフォールトトレラント構造の使用により、本発明だけによる方法と比べてエラー適用範囲比率を改善することが可能である。

【0079】

特異イベントを受けやすい参照アーキテクチャのポテンシャルエラーシグネチャが測定された。その結果は、エラーが、2つの重要なクラスに分類されることが可能であるということであった:

−データエラーと、

−サブクラスにも共有される順序付けエラー:

・「ソフトクラッシュ」:不正な接続だが、マイクロプロセッサは、指示により位相に戻り、多少不安定で、指示の順序付けを続行することが可能である;

・「ハードクラッシュ」:マイクロプロセッサは、操作可能でなく、たとえば、マイクロプロセッサは、指示と位相が同じでなく、マイクロプロセッサは、データを指示レジスタにロードし、スタックポインタが妨害されて、指示順序付けがブロックされ、不可能なイベント、無限ループなどを待つ。

【0080】

これら2つのクラスは、それら自体いくつかのサブクラスに再分され、最も重要なものは、アドレスエラーに関する。

【0081】

「ソフトクラッシュ」と「ハードクラッシュ」との間の識別が重要である。マイクロプロセッサの外側のハードウェア装置は、通常、「ハードクラッシュ」を検出する必要がある(すなわち、ウォッチドッグ)が、ソフトウェア装置は、たとえ不安定であるとしても、マイクロプロセッサが、ソフトウェアクラッシュの場合、コードを実行し続けるので、「ソフトクラッシュ」を検出するのに十分である。

【0082】

そのうえ、「抑制されていないマイクロプロセッサ」は、宇宙ミッションのための破局的結果を有することができるアクションが可能なので、マイクロプロセッサクラッシュは、クリティカルエラークラスを形成し、そのため、短い待ち時間でそれらを検出するために、あらゆる試みを行い、および/または検出されていないエラーに続く不良コマンドの確率を最小にするために、エラー制約領域を生成することが重要である。

【0083】

ここでは、本発明に自体による方法のオペレーションについて記述する。

【0084】

全体的に、検出/修正に使用される粒度は、コンピュータの基本リアルタイムサイクル、たとえば、プラットフォームコンピュータにおける姿勢および軌道制御システムタスクのサイクルである。

【0085】

本発明による方法(構造的デュプレックスにおけるような)の目的は、コンピュータが、監視されることなく作業し、次に、コンピュータから出力されるデータ(コマンド)、あるいは修正のために使用されるデータ(コンテキスト)だけを選択することか、あるいは「票決する」ことを可能とする。

【0086】

粒度のためにリアルタイムサイクルを選択することにはいくつかの利点がある:

−これは、捕捉がアクセスされ、あるいは大部分のセンサ/アクチュエータが制御される周波数であること、

−かなり制限された数の「アクティブ」データが、リアルタイムサイクルの終りに使用可能である;多量の中間データがなく、そしてローカル変数が使用されていないこと、

・検出のために、それらは、票決される一連のテーブルに格納されていることと、

・単純で、良好に配置された再開始コンテキストが修正のために使用可能であること。

【0087】

特に、票決がタスクの終りで行われるので、所定タスクのための検出/修正粒度が、このタスクの周波数である。その結果として、姿勢および軌道制御システムタスクが10Hzで、そしてサーマルタスクが1Hzで考慮されると、粒度は、姿勢および軌道制御システムのためには10Hzであり、サーマルタスクのためには1Hzである。明瞭にするために、リアルタイムサイクルによる「粒度」は、「タスクによって」よりはむしろ本文書の残りに使用されている。

【0088】

構造的冗長性を削除すると同時に、タイプに関係なく、例外なく、すべてのエラー(データエラー、アドレスエラー、順序付けエラー、構成エラーなど)を検出する手段であるデュプレックス(出力と比較すれば同一のソフトウェアを実行する並列の2つの同一システム)の効率から利益を得るために、本発明による方法は、単一の物理的チャネルに基づきデュプレックスオペレーションを設置することから成る。所定のリアルタイムサイクルにおいて、同一の物理的チャネルに位置される2つの仮想チャネルは、タイミングよく多重化され、仮想チャネルの各実行から生成されるデータは、「時間多重化されたデュプレックステーブル」(たとえば、コマンド、コンテキスト)に格納され、そのため、それらは使用前に票決されることが可能である。

【0089】

検出後、修正は、現在のリアルタイムサイクルを禁止することと、再ロードされたコンテキストから開始する次のサイクルの仮実行から成る再開始を行うために、異常のないコンテキストを再ロードすることとから成る;リアルタイムサイクルに「穴」があるかのように、すべてのことが生ずる。

【0090】

本発明による方法は、特異イベントによって生成されるエラーが一時的のものであるという事実に基づいている;第1の仮想チャネルの実行中に生ずるこのタイプのエラーは、第2のシステム実行中再生成されない(逆もまた同じである)。これに対し、本発明による方法は、静的エラー、たとえば、部品の故障(故障したビットなど)、あるいは特異イベントによるいくつかのエラーでさえを検出することができず、それは、永久エラー(たとえば、シーケンサのブロッキング)を生ずる。

【0091】

票決モジュールの出力側のアクション、換言すれば、制御エレクトロニクスへのデータ転送(すなわち、データバス)および制御エレクトロニクス自体は、本発明による方法によって保護されない。ユーザは、エラーのないようにする必要があるこれらクリティカルコマンドを決定し、そして当業者に周知である構造によって、それらを保護するために、システム分析を行う;データの符号化、自己検査回路、制御エレクトロニクスの計装など。

【0092】

図6は、本発明による方法の機能の説明を含んでいる。

【0093】

この図は、データフロー(太い線)を示し、それによると、仮想チャネル♯1 47は、捕捉♯1を受信し、仮想チャネル♯2 48は、捕捉♯2を受信し、確実な票決者49は、これら2つのチャネル47、48から出力を受信して、コマンドを発行する。修正のための再開始を初期化するべく、再ロードされたコンテキストリクエストをするために、確実な票決モジュール49を2つの仮想チャネル47、48に連結するエラー信号(細い線)もある。

【0094】

本発明による方法のグローバルシーケンスは、図5Aおよび図5Bに示されている:

−図5A:本発明による方法を有さないシーケンスであり、コマンドは、それにもかかわらず、処理の終りに分類されている、

−図5B:本発明による方法を有するシーケンス。

【0095】

図5Aは、2つのリアルタイムサイクルN、N+1と、サイクルN+2の開始を示している。

【0096】

各リアルタイムサイクルは、時間において異なる4つの位相から構成されている:

−データ捕捉、

−コマンドの計算で処理、

−コマンドの送信、

−タスクの取り消しおよび待機、この場合、「Scrub+Standby(取り消し+待機)」と呼ばれる。

【0097】

図5Bは、各リアルタイムサイクルが構成される本発明による方法を示している:

−仮想チャネル♯1(ChV ♯1)の捕捉、

−仮想チャネル♯1の処理;結果は、テーブルTAB ♯1に格納される、

−仮想チャネル♯2(ChV ♯2)の捕捉、

−仮想チャネル♯2の処理;結果は、テーブルTAB ♯2に格納される、

−テーブルTAB ♯1およびTAB ♯2の票決、

−コマンドの生成、

−タスクの取り消しおよび待機。

【0098】

図7は、本発明による全体の方法の模倣図を示し、本発明の実施形態に必要なすべての回路を表わしている。

【0099】

第1のマイクロプロセッサモジュール50は、すべてのソフトウェア構造を、特に、

−タスクの時間複写、

−テーブルへの変数の配置、

−確実な票決、

−再開始による修正、

−ハードウェア構造の管理、

を管理する。

【0100】

メモリアクセス監視および時間バリデーションウインドウモジュール51は、マイクロプロセッサ50のバス52と、エラー検出および修正メモリ53と、バスカプラー54とに連結されている。

【0101】

モジュール51は、マイクロプロセッサ50の「Reset(リセット)」ターミナルでエラー信号を、メモリ53で選択信号(「チップ−選択」、CS)を、そしてバスカプラー54で選択信号を生成する。

【0102】

メモリ53は、セグメントにおいて共有され、各セグメントは、特定のアクセス権(キーによるバリデーション)を有している。アクセスを他のコンピュータ機能(捕捉エレクトロニクス、制御エレクトロニクスなど)に供給するデータバス55に連結されるバスカプラー54は、「時間ウインドウ」タイプの信号によって妥当性が検査される。

【0103】

本発明による方法は、下記の特徴に基づいている:

−3つのエラー制約領域(時間、ソフトウェアおよびハードウェア)、

−テーブルに変数/データを配置、

−処理の時間複写、

−各処理の結果の比較によるエラー検出を可能にするユニークな確実なソフトウェア票決モジュール、その票決モジュールは、さらに、コマンドを生成する、

−票決の完全性をチェックするのに関係するソフトウェア監視プロセッサ、

−エラー検出および修正コードによる特異イベントに対して保護される制御装置メモリプレーン、

−前のエレメントを有して、再開始コンテキストを確実にバックアップし、かつアドレスエラーを検出するのに使用されるハードウェアアクセス権制御装置に関連するメモリセグメンテーション、

−アクセス権を制御するハードウェア装置を介して、データバスを通って制御エレクトロニクスに転送することをチェックし、エラー制約領域の境界を画定すること、

−エラーが生ずる場合、再開始による修正。

【0104】

ここでは、順番に、これらの特徴のそれぞれについて記述する。

【0105】

制約領域

最大エラー制約領域60は、図8に示されるように、捕捉エレクトロニクス41と、制御装置40とから構成される;この図は、図4と同一参照符号を使用している。したがって、エラーが、捕捉あるいは処理を妨害する場合、このエラーは、制御エレクトロニクス43に通過させることができない。この結果、捕捉エレクトロニクス41において、あるいは制御装置40において、特異イベントに続いて生ずるエラーは、不良な衛星用コマンドを生成しないし、またミッションを妨害しない。

【0106】

票決によるこの制約領域60は、票決モジュールが検出することが可能なエラーに効果的である。この制約領域は、さらに、アクセス権チェックの存在により、ほとんど他のエラーに不浸透性である;時間バリデーションウインドウにおけるハードウェア装置が、バスのコマンドの認可されていない発生をブロックする。

【0107】

さらに、他の制約領域は、本発明による方法において画定される:

−修正がリアルタイムサイクルの粒度に基づいているので、リアルタイムサイクルによるエラーの時間制約、

−メモリアクセス監視装置により、ソフトウェアタスクによる、そしてメモリアクセスの監視により、仮想チャネルによるエラー制約。

【0108】

プロセステーブル

本発明による方法のオペレーションは、特に、票決されるデータを含む一連のテーブルに基づく(その結果、これらのテーブルは、複写され、1つのセットは、ChV ♯1によって管理され、もう1つのセットは、ChV ♯2によって管理される)。これらのテーブルは、通常のソフトウェアテーブルとは異なり、デュプレックスオペレーションに特有なので、「時間多重化されたデュプレックステーブル」と呼ばれる。たとえば、

−捕捉テーブル(TAB−Acq)、

−制御テーブル(TAB−Cde)、

−コンテキストテーブル(TAB−Ctxt)。

【0109】

コンテキストテーブルTAB−Ctxt ♯1、TAB−Ctxt ♯2のそれぞれは、実際には、再開始による修正を行うとき、コンテキストを再格納することを可能にするために、タスクの終りに(すなわち、票決の終りに)、2つごとに1つのサイクルをスワッピングすることによって作業する一連の2つのテーブルから構成されている。一連の2つのインデックス(「Old(古いインデックス)」と「New(新しいインデックス)」)は、メモリに格納されて、それらと関連される。

【0110】

このように、たとえば、仮想シーケンス1について、タスクKのサイクル♯Nの間、第1のテーブルは、「New(新しい)」と考慮され、TAB−Ctxt−New ♯1と示され、第2のテーブルは、「Old(古い)」と考慮され、TAB−Ctxt−Old ♯1と示される。タスクKの票決が、何らエラーを検出しない場合、スワッピングは、票決の終りに役割を逆転し、第1のテーブルは、次に、TAB−Ctxt−Old ♯1になり、そして第2のテーブルは、TAB−Ctxt−New ♯1となる。

【0111】

「Old(古い)」の領域は、たとえば、票決されて、異常がないと判断されると、マイクロプロセッサクラッシュからコンテキストの再開始を保護するために、メモリアクセス監視装置による書き込みを禁じられている。

【0112】

順序付け−時間複写

上記に定義される参照ソフトウェアアーキテクチャと比較すれば、本発明による方法は、コマンドが、図3に示されるように、計算されるとき生成されないことを強要するが、むしろどちらかと言えば、それらは、票決を待つテーブルに格納される(図5Bを参照)。処理が2つの仮想チャネルのために終了されるとき、テーブルは票決されて、そして不一致が検出されない場合だけ、票決モジュールがコマンドを生成する;この場合、2つのコマンドテーブルの1つは、バス45を介して制御エレクトロニクス43を通って、制御装置40に送信される。

【0113】

所定のタスクについて、タイプ複写の態様を含む本発明による方法のグローバルシーケンスは、図9を参照として下記に記述されている。

【0114】

この図は、本発明による時間多重化されたデュプレックスのシーケンスと、コンテキストテーブルのスワッピングとを示している。

【0115】

リアルタイムサイクルは、リアルタイム割り込みIT−TRによって初期化される。

【0116】

各リアルタイムサイクルは、下記の位相から構成される:

−シーケンサ/リアルタイムエグゼクティブ(ETR)、

−タスクA、

−シーケンサ/リアルタイムエグゼクティブ、

−タスクB、

−シーケンサ/リアルタイムエグゼクティブ、

−タスクC,

−シーケンサ/リアルタイムエグゼクティブ、

−タスクの取り消しおよび待機。

【0117】

タスクA、タスクBおよびタスクCは、図5Bに示されるように下記のことから構成されている:

−仮想チャネルNo.1 捕捉、

−仮想チャネルNo.1 処理、

−仮想チャネルNo.2 捕捉、

−仮想チャネルNo.2 処理、

−票決およびコマンドの生成。

【0118】

下記のステップがある:

・仮想チャネル No.1(ChV♯1)のための「処理」モジュールの間:

−ChV♯1のデータの捕捉およびTAB−Acq♯11への格納、

−TAB−Acq♯1およびTAB−Ctxt−Old♯1から開始するChV♯1と関連する処理の実行;この処理の結果は、TAB−Cde♯1テーブルおよびTAB−Ctxt−New♯1テーブルに格納される;コマンドは、アクチュエータに送信される制御装置によって生成されない。

【0119】

・仮想チャネルNo.2(ChV♯2)のための「処理」モジュールの間:

−ChV♯2のデータの捕捉およびTAB−Acq♯2への格納、

−TAB−Acq♯2およびTAB−Ctxt−Old♯2から開始するChV♯2に関連する処理の実行;この処理の結果は、TAB−Cde♯2テーブルおよびTAB−Ctxt−New♯2テーブルに格納される;コンピュータは、なんら出力を生成しない。

【0120】

・「票決およびコマンドの生成」モジュール、換言すれば、テーブルの比較およびテーブルに関連するアクションの実行の間:

−逐語的にTAB−Cde♯1とTAB−Cde♯2の比較、

−逐語的にTAB−Ctxt−New No.1とNo.2との比較、

−エラーが検出されない場合、方法は続行し、さもなければ、待機に配置、

−インデックスを変更することによってコンテキストテーブルをスワッピングする:TAB−Ctxt−NewとTAB−Ctxt−oldとを置き換えて、次のリアルタイムサイクルのためのコンテキストとして使用される、

−コマンドの生成、2つのTAB−Cdeテーブルの1つが、データバスを介してコマンドエレクトロニクスにコマンドリクエストを転送するために、連続して空にされる、

−時間多重化されたデュプレックスパラメータの初期化(時間多重化されたデュプレックステーブル、時間多重化されたデュプレックス管理変数)。

【0121】

したがって、図9において、リアルタイムサイクルN+1の間、エラーが、リアルタイムサイクルNの間検出されない場合、タスクAへのエントリコンテキストは、TAB−Ctext−Old(N)であり、このテーブルは、実際には、スワッピングによりTAB−Ctxt−New(N)からのデータを含んでいる;エラーが検出される場合、タスクAへのエントリコンテキストは、TAB−Ctxt−Old(N−1)であり、このテーブルは、コンテキスト交換がエラーの場合に起こらないので、リアルタイムサイクルNにおけるテーブルTAB−Ctxt−Old(N−1)と同一である。

【0122】

モジュール処理の間、チェックサムコードは、票決に提起されるテーブルのそれぞれのために計算され、票決の徹底性(完全性)をチェックすることに関係している。

【0123】

確実なソフトウェア票決

最小として、票決されるのに必要とするデータは、図10に示されるような処理モジュールからの様々な出力である、すなわち:

−不正な動作を生成しないために、コンピュータ(コマンド)から出力されるデータ65、

−再開始コンテキストは異常がないであることを必要とするので、再開始のために使用されるデータ66(コンテキスト−サイクルNが障害状態である場合、異常のないデータN−1は、再開始のために格納される)。

【0124】

このように、処理モジュールから出力されるすべてのデータは、票決される。所定のタスクと関連する票決は、検出/修正の粒度によって定義されるように、このタスクの終りに行われる。

【0125】

票決モジュールに関して、本発明による方法は、下記の特徴を与えることが可能である:

−票決保全装置が画定される場合、特異イベントに耐性のある外部部品を使用する必要がない;アーキテクチャは、したがって、簡素化される;票決は、本発明による方法における他の場所で必要な少数のハードウェア装置からのサポートで、ソフトウェア全体においてマイクロプロセッサ自体によって行われることが可能である。

−ソフトウェア票決は、複写されない。

【0126】

本発明による方法は、デュプレックスアーキテクチャの検出能力の最良使用に基づいており、換言すれば、検出が最も難しく、さらに、潜在的に最も重大な結果を有する順序付けエラーを含むすべてのエラータイプを検出することが可能である。これらのエラーは、時間多重化されたデュプレックステーブルの一貫性に影響を有し、その結果、それらは、ソフトウェア票決が確実であるとすれば、換言すれば、不正に作動するマイクロプロセッサによって誘発されることができないとすれば、それらはソフトウェア票決によって検出される。したがって、適切な装置は、票決が正しいことを確実にするために備えられる必要がある。

【0127】

2つの中央要素は、票決が確実であることを確実にするために備えられる:

−マイクロプロセッサおよび制御装置モジュールが、票決の開始に異常のない状態であることをチェックすること、

−コマンドの生成を認可するために、票決が行われている間に票決が完結することをチェックすること。

【0128】

票決ストラクチャは、「ソフト」クラッシュによって影響を及ぼされるマイクロプロセッサの不良修正の可能性の分析の機能として画定されている:図11Aは、様々な起こり得る「ソフトクラッシュ」タイプの順序付けエラーを示している。

【0129】

「ハードクラッシュ」は、当業者によって通常使用されている方法であるウォッチドッグによって処理される。

【0130】

下記のストラクチャは、タスクKに関連する「Software(ソフトウェア)票決およびコマンド生成」モジュールに使用され、図11Bに示されている:

a)票決の開始時に連結されるマイクロプロセッサの状態と、制御装置モジュールの状態とをチェックすること:スタックポインタが認可された領域内にあることをチェックすること、マイクロプロセッサおよび制御装置カード構成レジスタをチェックすること、

b)票決の間のエラーの確率を最小にするために、可能な場合、キャッシュを禁止すること、

【0131】

c)Vote−Key(票決−キー)変数が、0に等しいことをチェックし、次に、それを1にセットすること(すなわち、票決):この変数は、Software Monitoring(ソフトウェア監視)方法を使用して、マイクロプロセッサの正しい順序付けを全体的にチェックするのに使用されるキーである、

d)票決することが行われることを表示し、そして2つのメモリ領域ChV♯1、ChV♯2への同時アクセスを認可するメモリアクセス監視装置のためのキーを活動化する、

【0132】

e)時間多重化されたデュプレックスによって生成されるすべてのテーブルで票決し、そして票決が、各テーブル:TAB−Ctxt、TAB−Ctxt−Newのために行われるとき、CRC−V票決の間に計算される巡回冗長コードを計算すること、

f)Vote−Key(票決−キー)が、1に等しいことをチェックし、次に、それを2にセットすること(すなわち、コマンド生成)、

【0133】

g)CRC−VをCRC−T処理の間に計算される巡回冗長コードと比較すること、

h)票決が行われることを表示するメモリアクセス監視装置キーを禁止すること、

i)テストe、f、gの結果が正しい場合、次に、時間バリデーションウインドウシステムを使用して、バスカプラー時間バリデーションウインドウを開くこと、

j)コマンドカード構成レジスタを再初期化すること、

【0134】

k)バスカプラーにコマンドを生成すること、

l)コマンドカード構成レジスタをチェックし、そして、検出されるエラータイプの関数としてアクションを行う(通常コマンド再送信);

時間ウインドウは終了されるか、あるいは終了するかである。

m)Vote−Key(票決−キー)が、2に等しいことをチェックし、次に、それを3にセットすること(すなわち、交換および初期化)、

n)メモリに格納される一対の「old(古い)」と「New(新しい)」インデックスを逆転することによって、タスクKのためのコンテキストテーブルをスワッピングすること、

【0135】

o)ChV♯1とChV♯2との間の1の補数値で、「Old(古い)」テーブルは別としてタスクKのすべてのテーブルを初期化すること、

p)「Old(古い)」テーブルを「New(新しい)」テーブルに転送し、そして、この転送をチェックするために票決すること;この転送は、タスクが実行されるたびに、変数が組織的に更新されない場合、変数が長期間有効であることを確かめるために必要である、

q)Vote−Key(票決−キー)が3に等しいことをチェックし、次に、0にセットすること(すなわち、禁止されている)、

r)キャッシュの妥当性を検査すること。

【0136】

「票決/コマンド生成/スイッチ/時間多重化されたデュプレックステーブルの初期化」手順は、割り込まれることができない、すなわち、それは、より優先度の高いタスクによって止められることがない(それは、初期化されると、終了される)。とはいえ、割り込みは、このモジュールに一時的に割り込むことが可能である。

【0137】

ソフトウェア監視プロセッサ

当業者に周知であるSoftware Monitoring Prosess(ソフトウェア監視方法)は、ソフトウェア自体へのマイクロプロセッサ指示の正しいなシーケンスの制御を受け渡す手段である。ソフトウェアは、リニア基本セグメント、換言すれば、2つの結合間のセグメントに分割される。リニアセグメントは、それ自体、分岐指示を含んでいないので、マイクロプロセッサが、このセグメントの第1の指示を実行すると、それは、このセグメントの最後の指示が実行されるまで続行する必要がある。

【0138】

エントリポイントでキーをテストし、かつそれを出口ポイントでチェックすることによって、マイクロプロセッサが、他の場所ではなく、正しいエントリポイントでリニアセグメントを実際に実行したことがチェックされる。

【0139】

票決保全は、このSoftware Monitoring(ソフトウェア監視)方法を含むいくつかの手段を使用する;「Vote−Key(票決−キー)」ソフトウェア変数は、この方法と関連するキーである。この票決モジュールは、アプリケーションソフトウェアの残りが第4のセグメントを表わす方法で、3つの機能セグメント(票決、コマンド生成、交換と初期化)に分割される:

−マイクロプロセッサが、他の場所でなく、出口ポイントで正しく、前のセグメントから実際に出たことを確認するために、Software Monitoring(ソフトウェア監視)方法キーの値は、各セグメントの開始にチェックされ、そして、さらに、そのセグメントが、互いに次々と正しく連鎖されることがチェックされること、

−次に、Software Monitoring(ソフトウェア監視)方法キーが、セグメントの開始でのこのチェック直後、現在のセグメントに対応する値にセットされること、

−マイクロプロセッサが、各セグメントの終りに、他の場所でなく、正しいエントリポイントで現在のセグメントを実際に実行したことがチェックされること。

【0140】

メモリプレーンの保護

メモリプレーンは、従来、休止エラーを検出して、修正するべくメモリプレーン全体を読み取るために、修正コード(EDAC)と、取り消しタスクとによって特異イベントに対して保護されている。これは、同一ワードの多重エラーが検出されること、および/または修正されることができないので必要である。

【0141】

本発明による方法は、

−修正コード(EDAC)の使用による特異イベントに関係する信頼性メモリと、

−アクセス権を監視することによって、アドレスエラー、指示エラー、マイクロプロセッサクラッシュなどに続く不正な書き込みのための信頼性メモリと、に基づいている。

【0142】

メモリアクセス監視装置

Memory Access Monitoring(メモリアクセス監視)(SAM)装置は、従来のブロックメモリ保護ユニットから導出されるハードウェア装置である。それは、境界が画定されたメモリ領域にアクセスしようとするマイクロプロセッサが、実際に、この領域へのアクセス権を有していることをチェックするのに使用される。

【0143】

メモリアクセス監視装置は、最も多くアドレスエラーを検出することが可能である。特に、それは、多数のマイクロプロセッサクラッシュを極めて迅速に検出することが可能である。マイクロプロセッサは、「ソフト」クラッシュ後、たびたび、許容可能なアドレス領域の外側に行くことが可能である。

【0144】

メモリアクセス監視装置は、従来のブロックメモリ保護ユニットと比べるといくつかの特有の特色を有している:

−セグメントのサイズは、任意であり、アプリケーションの関数として画定されること、

−アクセス認可は、メモリアクセス監視装置の内部のレジスタに記憶されるキーをプログラミングすることによって行われ、これらのキーの定義および組合せが、本発明による方法に特有である。

【0145】

下述のことは、メモリアクセス監視装置に一体化されるキーのリストである:

−コードエラーは、2つの仮想チャネルに共通のエラーモードであり、そして票決によって検出されないので、コードを記憶する領域への書き込みアクセスを防止するキーであって、このキーは、メモリだけを読み取るコードがRAMに転送されるとき、コンピュータの初期化の間だけメモリへの書き込みを認可する、

−仮想シーケンスが現在の ChV♯1、あるいはChV♯2であることを表示し、そして、ChV♯1が実行されるとき、マイクロプロセッサが、ChV♯2テーブルを含むメモリ領域にアクセスすることを防止するキー(逆もまた同じ)であって、このキーは、1つの仮想シーケンスが別のものに生ずるエラーに不浸透性になることを可能にする、

【0146】

−票決が現在行われていることを表示するキーであって、このキーが、アクティブであるとき、それは、例外的に、マイクロプロセッサが、2つの領域ChV♯1、ChV♯2に同時にアクセスすることを可能にし、そのため、票決が行われることが可能である、

−現在のタスクを表示し、そしてマイクロプロセッサが、現在実行されるこのソフトウェアタスクのためのテーブルを含むメモリ領域だけにアクセスすることを可能とするキーであって、このキーは、1つのタスクが、別のタスクに生ずるエラーに不浸透性になることを可能にする、

−スワッピングで作業する2つの「Old(古い)」/「New(新しい)」テーブルセットが、「Old(古い)」領域と、「New(新しい)」領域とであることを表示するキーであって、書き込みは、「Old(古い)」領域において禁じられている。

【0147】

時間バリデーションウインドウシステム

Time Validation Window(時間バリデーションウインドウ)(FVT)システムは、革新的なハードウェア装置である。それは、従来の時間カウンタを使用して行われる。それは、ハードウェアエラーを制約る。それは、

−コマンドエレクトロニクス管理コードを実行するクラッシュしたマイクロプロセッサが、アクセス権を正しく肯定応答することなく、コマンドを生成することを防止するように、

−不正な「コマンドに対応するアドレスに書き込む」タイプの指示を実行するマイクロプロセッサが、偶然にコマンドを生成することを禁ずるように、構成されている。

【0148】

その結果、時間バリデーションウインドウ装置は、それらがアプリケーションのために有する潜在的な破局的結果を帯びて、偶然のコマンドからシステムを保護する。それは、制御されたエレクトロニクスへのアクセスを認可するように予め準備されている;時間アクセスバリデーションウインドウが開かれる。

【0149】

上述のエラーの場合、マイクロプロセッサは、インターフェイス手順を徹底的に実行することによって、コマンドエレクトロニクスにアクセスしない;その結果として、認可されないアクセスは、マイクロプロセッサが、時間バリデーションウインドウを予め開かないので、このシステムによって直ちに検出される。

【0150】

時間バリデーションウインドウ装置は、存在するエラーがないという決定をした後準備される。この決定は、第一に、マイクロプロセッサと制御装置との異常のない状態をチェックする(票決の開始時に、その時、「Vote−Key(票決−キー)」変数で、そして票決の間に、「Checksum(チェックサム)」で)ことに基づき、第二に、票決の結果に基づく。

【0151】

修正

修正は、下記のシーケンスに従って実行される:

−エラーが検出されるとき、現在のリアルタイムサイクル(♯N)は、禁止され、そしてコマンドは生成されない;マイクロプロセッサは、待機モードに進み、次のリアルタイムサイクルを待つ、

−次のリアルタイムサイクルN+1は、前のコンテキストN−1から実行され、信頼性のないコンテキストNからは実行されず、そして現在のサイクルN+1のための捕捉から実行される。

【0152】

不正なリアルタイムサイクルは、リプレイされず、行われるすべては、現在のリアルタイムサイクルを禁止し、かつ前のサイクルのコンテキストを再格納することである。エラーが生ずると、マイクロプロセッサは、それが待機状態に置かれるので、現在のリアルタイムサイクルのためのコマンドを生成しない。すべてのことは、リアルタイムサイクルに「穴」があるかのように生ずる。

【0153】

修正は、特別のアクションを必要としない;マイクロプロセッサは、検出後待機状態に置かれ、その結果として、それは、票決モジュールの実行を続行しない。これは、当然のことながら、票決モジュールの終りに起こる「Old(古い)」コンテキストと「New(新しい)」コンテキストとのスワッピングを防止する。

【0154】

方法によって検出される一時的な性質のエラーとすれば、単一の再開始の試みが行われる。この試みが成功しない場合、コンピュータは、完全に再初期化される必要がある。

【0155】

シーケンサ−リアルタイムエグゼクティブ

ソフトウェアタスクの順序付けを可能にするシーケンサ、あるいはリアルタイムエグゼクティブは、直接に保護されない。対象は、市販のエグゼクティブを使用し、そのため、フォールトトレラント構造を含むように、それに何らかの変更をすることがない。

【0156】

これに反して、総実行時間と比べてこれらのタスクに専用の実行時間は極めて少ない。その結果として、タスクスケジューリングエラーは、2つの仮想チャネルに共通のモードであり、検出不可能であるが、適用範囲比率で極めて小さな影響を有している。

【0157】

さらに、制約領域は、不良コマンドが初期化される前にいくつかの検出されないエラーをブロックすることが可能であり、スケジューラから起こるエラーの影響を減少する。

【0158】

変形実施形態

本発明による方法に対する変形は、特に、その特徴のいくつかを簡素化することによって可能であり、たとえば、

−票決保全構造の簡素化:チェックサム計算の削除、十分であると考慮されるソフトウェア監視方法によるチェック、

−メモリアクセス監視装置の簡素化:2つのシーケンス間の同一エラーの可能性が、極めて少ないので、ChV♯1とChV♯2との間の不浸透性仕切りが不要(現在の仮想シーケンスを表示するキーの削除)。

【0159】

本発明による方法の開発および実施形態

本発明による方法は、最も包括的で、最も徹底的な可能性のあるバリデーションを生成し、かつ最大に可能性のあるエラー適用範囲比率を測定するために、開発された。

【0160】

目的

目的は、これを最後にこの方法を有効にするために、代表的な宇宙アプリケーションを表わすハードウェアおよびソフトウェア実施形態(モックアップ)を有することである。宇宙プロジェクトは、実際には、予備段階における様々な可能性のある解決法を分析している。新しい解決法について、モックアップが、正しいオペレーションと、プロジェクトチームがその使用について決定する前に、かなりの遅延を生ずる必要性への適合とを説明する試みにおいて使用されている。

【0161】

その結果として、この段階の前に、包括的なバリデーションが、要求仕様書、施行仕様書、施行ファイル、バリデーション結果、回復率測定などを含む完全なファイルを興味あるプロジェクトに供給するために企てられている。

【0162】

このように、予備段階において、すべてのプロジェクトは、モックアップを再開発する必要性がなく、この方法のための完全な開発/バリデーションファイルを有することが可能である。その結果として、(たとえば、監査により)、プロジェクトの必要性を満たす方法の適合が、選択についての決定をするために、迅速に決められることが可能である。

【0163】

バリデーション方法

方法は、障害の注入によって妥当性が検査される。したがって、独立した対象で2つのタイプの注入がある。

−第1の段階において、確定的エラーがソフトウェアによって注入される。この注入は同期であるので、エラーシナリオは、方法が障害状態であるとき、再プレイされることが可能である。この段階は、このように、方法の妥当性を検査するのに、かつ可能な場合、エラー検出/修正パフォーマンスを改善するために、それを修正するのに使用されることが可能である。

−第2の段階において、ランダムエラーは、粒子加速器を使用することによって、粒子ビームを本実施形態のメイン部品に印加して注入される(重イオン、プロトン)。この段階は、前の段階に相補的であり、注入されたエラースペクトルがより広いので、端から端にバリデーションを可能にする。さらに、エラーの分布が、リアルアプリケーション環境を表わすので、それは、方法のエラー適用範囲比率を精密に測定することが可能である。

【0164】

ハードウェア実施形態

開発されたハードウェア実施形態は、主として、処理ユニット、捕捉ユニットおよび可観測性ユニットの3つの部分から構成されている。

【0165】

処理ユニットは、Power(パワー) PC 603eタイプのマイクロプロセッサとそのメモリ、および方法のすべてのハードウェア構造を一体化するプログラム可能な部品周りで開発されている。

【0166】

捕捉ユニットは、マイクロプロセッサのためのいくつかの捕捉チャネルを模擬実験し、これらのチャネルのそれぞれは、特別の特徴を有している:マイクロプロセッサの要求で作られる捕捉(簡単なセンサのシミュレーション)、周期的に作られ、そしてマイクロプロセッサは、それらが到達するときに読み取る必要がある捕捉(衛星センサ、あるいはGPSなどのインテリジェントセンサのシミュレーション)、リモートコマンドの受信など。これらの捕捉チャネルは、PIC 16C73Aタイプのナノコントローラの周りに作られている。

【0167】

可観測性ユニットは、本実施形態の制御計装(ソフトウェア、マイクロプロセッサの可観測性をロードなど)およびマイクロプロセッサによって作られる動作のシミュレーションを可能にするチャネルを一体化する。このチャネルの出力は、それが一時的なエラーによって影響を及ぼされるという事実にもかかわらず、コンピュータによって生成される障害動作がないことを立証するために、組織的にチェックされる。

【0168】

ハードウェア実施形態

開発されたソフトウェアアプリケーション(すなわち、ソフトウェア実施形態)は、宇宙において、あるいは他のアプリケーションにおいて、搭載リアルタイムアプリケーションをできるだけ表わすために、下記の特徴を有している:

−後で、市販用リアルタイムエグゼクティブと置き換えられる周期シーケンサに基づく順序付け、

−異なるプライオリティを有するいくつかのメインアプリケーションタスク(たとえば、6個)、それらのいくつかは、周期的であり、その他は、非同期であり、非周期的である;それらのタスクの1つは、宇宙機の姿勢制御プログラムのコアである、

−アプリケーションは、リアルタイムクロックの制御のもとに実行されるリアルタイムサイクルに基づき、アプリケーションタスクは、異なる間隔を有している、

−いくつかのアプリケーションタスク、たとえば、3つのアプリケーションは、より優先度の高いタスクによって割り込まれる、

−ソフトウェアは、捕捉チャネルから生ずる外部非同期イベントに対してリアルタイムで作用する。

【0169】

〔参考文献〕

【表1】

【表2】

【符号の説明】

【0170】

A1 A3 Am アクチュエータ

C1 C2 Cn センサ

Ph1 Ph2 Ph3 メイン位相

1 仮想チャネル

10 搭載管理ユニット

11 制御装置

12 マスメモリ

13 パワーインターフェイス

14 リモートコントロール−リモート測定インターフェイス

15 ペイロードインターフェイス

16 パイロテクニクスインターフェイス

17 サーマルインターフェイス

18 姿勢および軌道制御システムインターフェイス

19 データバス

20 監視および再構成エレクトロニクス

21 DC−DCコンバータ

25 太陽熱発電機

26 バッテリ

27 デュプレクサ

28 29 アンテナ

31 ペイロード

32 アビオニクスバス

33 高速シリアルリンク

35 展開可能なシステム

36 ヒータおよびサーミスタンス

37 リザーバ圧力センサ

40 制御装置

41 捕捉エレクトロニクス

42 センサ

43 制御エレクトロニクス

44 アクチュエータ

45 データバス

47 仮想チャネル

48 仮想チャネル

49 確実な票決モジュール

50 第1のマイクロプロセッサモジュール

51 メモリアクセス監視および時間バリデーションウインドウモジュール

52 バス

53 エラー検出および修正メモリ

54 バスカプラー

55 データバス

60 最大エラー制約領域

65 データ

66 データ

【特許請求の範囲】

【請求項1】

マイクロプロセッサの周りに形成された制御装置およびメモリを含むコンピュータのメモリアクセスを監視する装置であって、前記メモリが、セグメントに分割され、各セグメントが前記装置で利用可能なキーの全部あるいはいくつかの論理機能によって規定されるアクセス権を有し、各セグメントへの前記アクセス権がリアルタイムで検査され、いくつかのセグメントに対するアクセスが、マイクロプロセッサが適切な作動状態にあるという非常に高い可能性がある場合に許可されるだけであり、したがって重要なデータの確実な記憶を可能にすることを特徴とする装置。

【請求項2】

非隣接セグメントのセットが、前記装置にあるキーのプログラミングに応じて、いくつかのセグメントに対して読み出し専用でおよび他のセグメントに対して読み出し/書き込みでアクセス可能である請求項1に記載の装置。

【請求項3】

セグメントサイズが、所定の用途に対して最適化できるように任意である請求項1に記載の装置。

【請求項4】

利用可能なキーのセットの定義、これらのキーに対する論理的組合せ機能および前記キーのプログラミングの機能としての前記アクセス可能なセグメントの構成が固有である請求項1に記載の装置。

【請求項5】

前記セグメントの中の1つが前記コンピュータの例外状態でアクセス可能な書き込み許可を有し、したがって重要なデータの確実な記憶を可能にする請求項1に記載の装置。

【請求項6】

重要なデータの確実な記憶を可能にするセグメントがフリップフロップで作動する対で記憶される請求項1に記載の装置。

【請求項1】

マイクロプロセッサの周りに形成された制御装置およびメモリを含むコンピュータのメモリアクセスを監視する装置であって、前記メモリが、セグメントに分割され、各セグメントが前記装置で利用可能なキーの全部あるいはいくつかの論理機能によって規定されるアクセス権を有し、各セグメントへの前記アクセス権がリアルタイムで検査され、いくつかのセグメントに対するアクセスが、マイクロプロセッサが適切な作動状態にあるという非常に高い可能性がある場合に許可されるだけであり、したがって重要なデータの確実な記憶を可能にすることを特徴とする装置。

【請求項2】

非隣接セグメントのセットが、前記装置にあるキーのプログラミングに応じて、いくつかのセグメントに対して読み出し専用でおよび他のセグメントに対して読み出し/書き込みでアクセス可能である請求項1に記載の装置。

【請求項3】

セグメントサイズが、所定の用途に対して最適化できるように任意である請求項1に記載の装置。

【請求項4】

利用可能なキーのセットの定義、これらのキーに対する論理的組合せ機能および前記キーのプログラミングの機能としての前記アクセス可能なセグメントの構成が固有である請求項1に記載の装置。

【請求項5】

前記セグメントの中の1つが前記コンピュータの例外状態でアクセス可能な書き込み許可を有し、したがって重要なデータの確実な記憶を可能にする請求項1に記載の装置。

【請求項6】

重要なデータの確実な記憶を可能にするセグメントがフリップフロップで作動する対で記憶される請求項1に記載の装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【公開番号】特開2010−134967(P2010−134967A)

【公開日】平成22年6月17日(2010.6.17)

【国際特許分類】

【出願番号】特願2010−57535(P2010−57535)

【出願日】平成22年3月15日(2010.3.15)

【分割の表示】特願2000−576368(P2000−576368)の分割

【原出願日】平成11年10月11日(1999.10.11)

【出願人】(500201613)センタ・ナショナル・デチュード・スパティアレ (5)

【Fターム(参考)】

【公開日】平成22年6月17日(2010.6.17)

【国際特許分類】

【出願日】平成22年3月15日(2010.3.15)

【分割の表示】特願2000−576368(P2000−576368)の分割

【原出願日】平成11年10月11日(1999.10.11)

【出願人】(500201613)センタ・ナショナル・デチュード・スパティアレ (5)

【Fターム(参考)】

[ Back to top ]