過渡電圧抑制器のための方法およびシステム

【課題】炭化シリコン過渡電圧抑制器(TVS)アセンブリを形成する方法および過渡電圧抑制器(TVS)アセンブリのためのシステムを提供する。

【解決手段】TVSアセンブリは、第1の極性の導電性を有する第1の広バンドギャップ半導体の第1の層306と、第1の層と電気的に接触して結合された第2の極性の導電性を有する第1または第2の広バンドギャップ半導体の第2の層308であって、第2の極性は第1の極性と異なる、第2の層とを含むメサ構造の半導体ダイ302を含む。TVSアセンブリはまた、第2の層と電気的に接触して結合された第1の極性の導電性を有する第1、第2、または第3の広バンドギャップ半導体の第3の層312も含む。第2の極性の導電性を有する層は、第1の極性の導電性を有する層に比して低濃度にドープされる。

【解決手段】TVSアセンブリは、第1の極性の導電性を有する第1の広バンドギャップ半導体の第1の層306と、第1の層と電気的に接触して結合された第2の極性の導電性を有する第1または第2の広バンドギャップ半導体の第2の層308であって、第2の極性は第1の極性と異なる、第2の層とを含むメサ構造の半導体ダイ302を含む。TVSアセンブリはまた、第2の層と電気的に接触して結合された第1の極性の導電性を有する第1、第2、または第3の広バンドギャップ半導体の第3の層312も含む。第2の極性の導電性を有する層は、第1の極性の導電性を有する層に比して低濃度にドープされる。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、一般に高温半導体デバイスに関し、より具体的には、高温環境での過渡電圧抑制のための半導体デバイスに関する。

【背景技術】

【0002】

シリコンデバイスは、TVSデバイスに並列に結合された高感度電子機器が例えば落雷で生じる電圧スパイクにさらされ、損傷を受けるのを防止するために使用されてきたけれども、それらは、高温動作に適していない。シリコンデバイスは、温度が上昇するにつれてより高い電流を漏えいする傾向があり、その電流は、約150℃よりも大きい周囲温度では容認できないほど高い値に達し、それは、分散エンジン制御などのコアエンジン搭載電子機器を必要とする航空用途に必要な225℃以上の周囲温度でのそれらの使用を不適切にする。その上、周知のTVSデバイスは典型的には、エポキシ封入材を使用してパッケージ化される。エポキシパッケージ化は、約185℃より上でTVSデバイス構造内に大きな熱歪みを誘起し、分解し始める傾向がある。

【0003】

航空および発電の両方の用途のためのタービンエンジン機器類はしばしば、高価な冷却、または電子機器をセンサーおよびアクチュエータからさらに遠くに移動させることを必要とし、据え付けおよび配線の複雑さの増加ならびにノイズに起因するセンサー性能の低下をもたらす。航空機で分散制御に使用する電子機器は、落雷および電磁妨害(EMI)で生じる電圧サージから損傷を受けやすい。少なくともいくつかの周知の用途は、過渡電圧抑制(TVS)デバイスを使用し、それは、ツェナーダイオードに似た特徴を含むこともある。シリコンでできた市販のTVSデバイスは、それらがさらされることになる高い周囲温度に起因してエンジンコアの近くに置いた分散電子機器を保護するために使用することができない。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国特許出願公開第2011/0058299号明細書

【発明の概要】

【0005】

一実施形態では、過渡電圧抑制器(TVS)アセンブリは、第1の極性の導電性を有する第1の広バンドギャップ半導体の層を含む基板と、基板と電気的に接触して結合された第2の極性の導電性を有する第1または第2の広バンドギャップ半導体の第2の層であって、第2の極性は第1の極性と異なる、第2の層と、第2の層と電気的に接触して結合された第1の極性の導電性を有する第1、第2、または第3の広バンドギャップ半導体の第3の層とを含むメサ構造の半導体ダイを含む。第2の極性の導電性を有する層は、第1の極性の導電性を有する層に比して低濃度にドープされる。TVSアセンブリはまた、基板と電気的に接触して結合された第1の電極および第3の層と電気的に接触して結合された第2の電極も含む。所定の大きさよりも大きい電圧が、第1および第2の電極間に印加されるとき、TVSアセンブリは、比較的大量の電流がTVSアセンブリを通って流れることを可能にするパンチスルーモードで動作する。

【0006】

別の実施形態では、炭化ケイ素過渡電圧抑制器(TVS)アセンブリを形成する方法は、第1の側面および反対側の第2の側面を含むパンチスルー炭化ケイ素半導体過渡電圧抑制器ダイを提供するステップと、ダイを少なくとも部分的に取り囲むガラス筐体にダイを封入するステップと、第1および第2の側面の各々と電気的に接続してそれぞれの電極を結合するステップとを含み、各電極は、ガラス筐体の熱膨張係数と実質的に一致する熱膨張係数を有する。

【0007】

なお別の実施形態では、高温電子システムは、約150.0℃よりも大きい温度を有する環境にさらすように構成された電子機器ユニットを含み、遠隔電子機器ユニットは、電子機器ユニットの少なくともいくつかの電子部品と動作可能に結合された過渡電圧抑制器(TVS)アセンブリを含み、TVSは、ダイを少なくとも部分的に取り囲むガラス筐体に封入され、熱圧着接合、過渡的液相はんだ接合、拡散接合、および合金化層の少なくとも1つを使用して電極に結合されたパンチスルー炭化シリコン半導体TVSダイを含む。

【0008】

本技術のこれらのかつ他の特徴、態様、および利点は、類似の文字が図面全体にわたって類似の部分を表す添付の図面を参照して次の詳細な説明を読むときより良く理解されることになろう。

【図面の簡単な説明】

【0009】

【図1】本発明の例となる実施形態による電力および通信分配システムのアーキテクチャの概略ブロック図である。

【図2】本システムの例となる実施形態による図1で示す電子機器ユニットの例となる1つの概略ブロック図である。

【図3】本発明の例となる実施形態によるTVS218を使用して利用できる電圧抑制保護のさまざまな構成の概略ブロック図である。

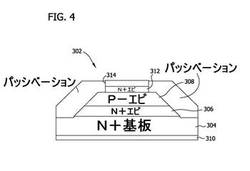

【図4】本システムの例となる実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの半導体ダイ部分の側面図である。

【図5】本システムの別の実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの半導体ダイ部分の側面図である。

【図6】本システムの別の実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの半導体ダイ部分の側面図である。

【図7】本発明の例となる実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの側面図である。

【図8】本システムの例となる実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの別の図である。

【図9】TVSアセンブリの雷試験波形の結果を例示するグラフ800である。

【図10】TVSアセンブリのDC試験の結果を例示するグラフ900である。

【図11】TVSアセンブリの図10で示すDC試験の結果を例示するグラフ1000である。

【発明を実施するための形態】

【0010】

次の詳細な説明は、システムの実施形態を例としてであって制限する目的ではなく例示する。システムおよび方法は、パワーエレクトロニクス、信号エレクトロニクス、ならびに工業、商業、および住宅用途での電磁妨害(EMI)保護の電子部品製造およびパッケージ化への一般的応用を有すると熟考される。

【0011】

本明細書で使用するように、単数形で列挙され、単語「a」または「an」が先行する要素またはステップは、そのような排除が明確に列挙されない限り、複数形の要素またはステップを排除しないと理解すべきである。さらにその上、本発明の「一実施形態」への言及は、列挙する特徴もまた組み込む追加の実施形態の存在を排除すると解釈されることを意図していない。

【0012】

本開示の実施形態は、300℃で確実に動作する半導体ベースのTVSデバイスを実証する。一実施形態では、デバイスは、炭化シリコン(SiC)から製作される。他の実施形態では、デバイスは、窒化ガリウム(GaN)、ダイヤモンド、窒化アルミニウム(AlN)、窒化ホウ素(BN)、およびそれらの組合せなどだが限定されない、他の広バンドギャップ材料から製作される。広バンドギャップ半導体TVSデバイスは、約500℃に至るまで確実に動作可能であるが、しかしながら、TVSパッケージ類などの他の部品は、例の実施形態ではより制限的なこともある。TVSは、クランプデバイスであり、それの降伏電圧より上のほぼすべての過電圧を抑制する。TVSデバイスは典型的には、3つのSiC層(N−P−N)を含む。他の実施形態では、3つの層は、P−N−P層を含む。N−P−N型デバイスでは、デバイスが2つのN層を横切る電位を受けるとき、P層のドーピングは2つのN層と比較してはるかにより低いので、空乏層は、P層中に(大部分)形成される。例えば、N層のドーパント濃度よりも大きさが1から5桁低い、またはN層のドーパント濃度の1/10から1/10000である。さらなる例については、もしN層でのドーピング濃度が、約1018/cm3であるならば、P層でのドーピング濃度は、約1015/cm3であることになる。デバイスを横切る電圧が増加するにつれて、空乏領域は、P層をすべて横切って延び、もう一方の側のN層に接触する。これは、「パンチスルー」として周知の条件をもたらし、大量の電流が、デバイスに流れ始める。デバイスは、それを横切る電圧の変化が最小の状態でこの条件を維持することができる。同様の説明は、層の極性がP−N−Pに変更されるときの動作も述べる。

【0013】

パッケージは、一例では、高速の電気的応答を提供するために低いインダクタンスおよび静電容量を有し、熱パルスを管理するために熱キャパシタンスを有するように設計される。低いインダクタンスおよび静電容量は、ダイから回路に接合される終端までの短い伝導経路を使用することによって達成される。ガラスまたはセラミック封入材は、ダイを環境での汚染から保護し、デバイスを横切る電気的絶縁の改善を提供するために使用されてもよい。ホウケイ酸ガラス封入材は、600℃に至るまでの試験で低い漏れ電流を有することが見いだされた。終端材料は、セラミックと金属との密封およびガラスと金属との密封にそれぞれ適合するように選択される。終端材料は、タングステン、モリブデン、またはKovar(登録商標)を含んでもよいが限定されない。ダイは、例えば熱圧着接合、過渡的液相はんだ接合、拡散接合、または合金化層を使用してそれぞれの終端に両側で接合される。一実施形態では、金熱圧着接合が、より低い熱抵抗経路を提供し、高温中で酸化しない。金はまた、大きな塑性域も有して特に高温で低応力界面を提供する。

【0014】

TVSデバイスは、TVSデバイスに並列に結合された高感度電子機器が例えば落雷で生じる電圧スパイクにさらされ、損傷を受けるのを防止することを容易にする。さまざまな実施形態では、2つ以上のTVSデバイスが、TVSデバイスの並列、直列、および/または直列並列構成を含むTVSアセンブリに接続されてTVSアセンブリの強化された電気的保護特徴、例えばより大きな電圧または電流能力を可能にしてもよい。高温パッケージでのSiCデバイスは、例えば約150℃よりも大きい、比較的高い周囲温度の環境にそれを配置することを可能にする。その上、SiCデバイスは、極めて強固なクランプを提供する。本明細書では高温用途での使用に適していると述べるけれども、広バンドギャップ材料はまた、温度が比較的高くない、例えば室温である用途にもよく適している。

【0015】

図1は、本発明の例となる実施形態による電力および通信分配システム100のアーキテクチャの概略ブロック図である。例となる実施形態では、分配システム100は、電力供給分配バス102および通信チャネル104を含む。電力供給分配バス102は、例となる実施形態では、エンジン110の周囲に位置する複数の電子機器ユニット106に電力を分配する。例となる実施形態では、エンジン110は、ファン112およびコアエンジン114を含むガスタービンエンジンである。さまざまな他の実施形態では、エンジン110は、ピストン駆動内燃エンジン、圧縮機、発電機、およびポンプなどだが限定されない、別の1台の機械であってもよい。例となる実施形態では、複数の電子機器ユニット106は、例えばガスタービンエンジン(GTE)110のファン112に隣接した比較的冷たい環境に取り付けられているように例示される電子機器ユニット(EU)116および118を含む。分配システム100はまた、高温電子機器ユニット(HT−EU)120、122、および124も含む。HT−EU120、122、および124の各々は、ガスタービンエンジン110のコアエンジン114に取り付けられているように例示され、それは、比較的熱い環境の場所である。例えば、コア筐体114の近辺での温度は、約150.0°セ氏(C)から約300.0℃のこともある。

【0016】

EU116は、電力供給装置126から電力を受け取る。受け取った電力は、EU116によって分配システム100内に分配するために管理される。管理された電力は、電力供給分配バス102を通ってEU118、HT−EU120、122および124を含むさまざまなそれぞれの負荷に送られる。同様に、さまざまな電子機器ユニット間の通信は、通信チャネル104を通って送られる。

【0017】

動作中は、航空機への電磁妨害および/または落雷が、バス102および/または104に大きな過渡電圧スパイクを誘起することもある。そのような大きな電圧スパイクは、もし修正しないならば、EU116、118、ならびにHT−EU120、122、および124を含む、バスに結合された電気部品および電子部品に損傷を引き起こすこともある。そのような損傷を避けるために、過渡電圧抑制器が、選択した部品および/または部品内の回路と直列にかつ/または並列に使用されてそのようなスパイクを低減しかつ/または除去することを容易にすることができる。一方法は、バスの電圧を所定のレベルにクランプする。

【0018】

図2は、本システムの例となる実施形態によるEU116、118、ならびにHT−EU120、122、および124の例となる1つの概略ブロック図である。例となる実施形態では、HT−EU120は例えば、プロセッサ202、プロセッサ202に通信可能に結合されたメモリ204、ROMメモリ206、またプロセッサ202に通信可能に結合もされた、入力セクション208、駆動モジュール210、および出力モジュール212を含む。HT−EU120はまた、通信バス104およびプロセッサ202に通信可能に結合された通信モジュール214も含む。HT−EU120はさらに、電力供給分配バス102に電気的に結合され、HT−EU120全体にわたってさまざまな電圧で電力を分配するように構成された電力モジュール216を含む。それぞれのバスに結合されていると、通信モジュール214および電力モジュール216は、EMIおよび/または雷誘起スパイクの影響を受けやすい。そのような妨害およびスパイクが通信モジュール214および電力モジュール216ならびに下流の部品に到達するのを防止するために、1つまたは複数の過渡電圧抑制(TVS)アセンブリ218および220が、それぞれのバスと通信モジュール214および電力モジュール216との間に結合される。

【0019】

図3A〜3Cは、本発明の例となる実施形態によるTVSアセンブリ218を使用して利用できる電圧抑制保護のさまざまな構成の概略ブロック図である。図3Aの実施形態では、TVSアセンブリ218は、直列構成の2つの過渡電圧抑制器を含む。図3Bの実施形態では、TVSアセンブリ218は、第3の過渡電圧抑制器と並列に直列構成の2つの過渡電圧抑制器を含む。図3Cの実施形態では、TVSアセンブリ218は、第3の過渡電圧抑制器と直列に並列構成の2つの過渡電圧抑制器を含む。個々の過渡電圧抑制器のさまざまな他の組合せが、多くの異なる用途にとって十分な電流運送能力および所定の電圧性能を提供するように組み立てられてもよい。

【0020】

図4は、本システムの例となる実施形態による過渡電圧抑制(TVS)アセンブリ218または220(図2で示す)の半導体ダイ302部分の側面図である。例となる実施形態では、ダイ302は、例えばn+型導電性を有する炭化シリコンの基板304ならびにエピタキシャル成長のn+型導電性層306、層306と電気的に接触して結合されたエピタキシャル成長のp−層308、およびp−層308と電気的に接触して結合されたエピタキシャル成長のn+層312で形成されるメサ構造を含む。例となる実施形態では、p−層308は、n+層306および312に比して比較的低濃度にドープされる。基板304ならびに層306、308、および312の均一なドーピング濃度は、空乏領域での電場分布の均一性を改善し、それによって降伏電圧特性を改善する。その上、メサ構造は、隣接接触層間の界面に関して約5度から約80度の角を成す傾斜側壁を有してダイの表面での最大電場プロファイルを低減する。第1の電気接点310は、基板304と電気的に接触して結合される。第2の電気接点314は、エピタキシャル成長のn+層312と電気的に接触して結合される。過渡電圧抑制(TVS)アセンブリ218または220の半導体ダイ302部分は、ダイ302を横切る電圧が増加するにつれて、空乏領域がp−層308をすべて横切って延び、n+層306および312に接触するような「パンチスルー」または「リーチスルー」としてもまた周知の物理的過程を使用して動作する。これは、「パンチスルー」として周知の条件をもたらし、大量の電流が、ダイ302を通って流れることができる。ダイ302は、それを横切る電圧の変化が最小の状態でこの条件を維持することができる。

【0021】

さまざまな実施形態では、TVSアセンブリ218は、ダイ302の半導体材料内部の最大電場が1センチメートル当たり2メガボルト未満に維持されることを確実にするような大きさおよび形にされる。加えて、TVSアセンブリ218は、約1.0ナノアンペア未満から約1.0ミリアンペアの範囲の電流について5%未満の阻止電圧の増加を維持するように構成される。本明細書で使用するように、阻止電圧は、TVSアセンブリ218が電気を通さないまたはなお「オフ」状態にある最高電圧のことである。その上、TVSアセンブリ218は、室温ではTVSアセンブリ218のほぼパンチスルー電圧に至るまで約1.0マイクロアンペア未満および225°セ氏に至るまでの動作温度ではほぼパンチスルー電圧に至るまで1.0マイクロアンペア未満の漏れ電流を維持するように構成される。

【0022】

さまざまな実施形態では、TVSアセンブリ218は、約5.0ボルトから約75.0ボルトの間でパンチスルー特性を示すように構成される。さまざまな他の実施形態では、TVSアセンブリ218は、約75.0ボルトから約200.0ボルトの間でパンチスルー特性を示すように構成される。なお他の実施形態では、TVSアセンブリ218は、約200ボルトよりも大きいところでパンチスルー特性を示すように構成される。

【0023】

図5は、本システムの別の実施形態による過渡電圧抑制(TVS)アセンブリ218または220(図2で示す)の半導体ダイ302部分の側面図である。例となる実施形態では、ダイ302は、第1の円錐台構造402および第2の実質的に円柱状の構造404を含む。第1の円錐台構造402は、エピタキシャル成長のn+型導電性層306およびエピタキシャル成長のp−層308の少なくとも一部分で形成される。円柱状構造404は、エピタキシャル成長のp−層308の少なくとも一部分およびエピタキシャル成長のn+層312で形成される。例となる実施形態では、p−層308は、n+層306および312に比して比較的低濃度にドープされる。基板304ならびに層306、308、および312の均一なドーピング濃度は、空乏領域での電場分布の均一性を改善し、それによって降伏電圧特性を改善する。第1の電気接点310は、基板304と電気的に接触して結合される。第2の電気接点314は、エピタキシャル成長のn+層312と電気的に接触して結合される。

【0024】

図6は、本システムの別の実施形態による過渡電圧抑制(TVS)アセンブリ218または220(図2で示す)の半導体ダイ302部分の側面図である。例となる実施形態では、ダイ302は、第1の円錐台構造602および第2の円錐台構造604を含む。第1の円錐台構造602は、エピタキシャル成長のn+型導電性層306およびエピタキシャル成長のp−層308の少なくとも一部分で形成される。第2の円錐台構造604は、エピタキシャル成長のp−層308の少なくとも一部分およびエピタキシャル成長のn+層312で形成される。例となる実施形態では、p−層308は、n+層306および312に比して比較的低濃度にドープされる。基板304ならびに層306、308、および312の均一なドーピング濃度は、空乏領域での電場分布の均一性を改善し、それによって降伏電圧特性を改善する。第1の電気接点310は、基板304と電気的に接触して結合される。第2の電気接点314は、エピタキシャル成長のn+層312と電気的に接触して結合される。

【0025】

図7は、本発明の例となる実施形態による過渡電圧抑制(TVS)アセンブリ218(図2で示す)の側面図である。例となる実施形態では、第1および第2の電気接点310および314はそれぞれ、拡散接合または合金化層702および704ならびにそれぞれのヘッダーピン406および408を含む。さまざまな実施形態では、層702および704は、銅(Cu)、金(Au)、アルミニウム(Al)、白金(Pt)およびそれらの組合せで形成される。他の実施形態では、層702および704は、他の材料、組合せまたは合金で形成されてもよい。さまざまな実施形態では、第1および第2の電気接点310および314は、例えば熱圧着接合、過渡的液相はんだ接合、拡散接合、または合金化層だが限定されないそれらを使用する層702および704を使用してダイ302に結合される。表面実装接点410および412は、第1および第2の電気接点310および314と電気的に接触して結合され、典型的にはヘッダーピン406および408にそれぞれ結合される。ガラス封入材414は、ダイ302ならびに第1および第2の電気接点310および314を少なくとも部分的に取り囲む。さまざまな実施形態では、ガラス封入材414は、ホウケイ酸ガラスまたはアルミナセラミックを含む。ヘッダーピン406および408は、ガラス封入材414の熱膨張係数と実質的に一致する熱膨張係数を有するように選択した材料から形成される。そのような材料は、タングステン、モリブデン、鉄−ニッケル−コバルト、時にはKovar(登録商標)と呼ばれる低膨張合金およびそれらの組合せの少なくとも1つを含んでもよい。Kovar(登録商標)合金は、真空溶解した鉄−ニッケル−コバルトの低いまたは制御された膨張合金であり、その化学組成は、正確な均一熱膨張特性を確保するために狭い制限内に制御される。例となる実施形態では、ヘッダーピン406および408は、約29%ニッケル(Ni)、17%コバルト(Co)を含み、残余は実質的に鉄(Fe)である材料から形成される。

【0026】

図8は、本システムの例となる実施形態による過渡電圧抑制(TVS)アセンブリ218(図2で示す)の別の図である。例となる実施形態では、ヘッダーピン406および408は、ガラス封入材414と一緒になり、例えばはんだ接続を受けてTVSアセンブリ218を回路に電気的に結合するように構成されたフランジ502および504を有して形成される。

【0027】

図9は、TVSアセンブリ218の雷試験波形を例示するグラフ800である。例となる実施形態では、グラフ800は、時間の単位で目盛の付いたx軸802ならびに電圧および電流の単位で目盛の付いたy軸804を含む。トレース806は、TVSアセンブリ218にかける電圧を表し、それのピークは、TVSアセンブリ218のクランプ電圧を指し示す。例となる実施形態では、それは、約100.0ボルトである。トレース808は、TVSアセンブリ218を通って流れる電流を表し、それは、約134アンペアである。

【0028】

図10は、DC試験を例示するグラフ900である。例となる実施形態では、グラフ900は、電圧の単位で目盛の付いたx軸902および対数尺度を使用して電流の単位で目盛の付いたy軸904を含む。トレース906は、第1および第2の電気接点310および312を横切って電圧を与え、対応する電流を測定するときのTVSアセンブリ218の応答を表す。DC試験は、TVSアセンブリ218の高温能力を決定するために約200°セ氏でのTVSアセンブリ218について行われる。例となる実施形態では、TVSアセンブリ218は、約65.0ボルトでオンになり、そこではトレース906は、平坦になる。65.0ボルト未満の電圧では、TVSアセンブリ218は、「オフ」条件にある。TVSアセンブリ218がオフであるときに流れる電流は、漏れ電流である。TVSアセンブリ218を通る漏れ電流値は、TVSアセンブリ218が高温でオフであり低い漏れ電流を示すときは、極めて小さく、例えばピコアンペアの範囲であることがわかる。

【0029】

図11は、TVS218のDC試験を例示するグラフ1000である。例となる実施形態では、グラフ1000は、電圧の単位で目盛の付いたx軸1002および線形尺度を使用して電流の単位で目盛の付いたy軸1004を含む。トレース1006は、第1および第2の電気接点310および312を横切って電圧を与え、対応する電流を測定するときのTVSアセンブリ218の応答を表す。DC試験は、TVSアセンブリ218の高温能力を決定するために約200°セ氏でのTVSアセンブリ218について行われる。例となる実施形態では、TVSアセンブリ218は、約65.0ボルトでオンになり、そこではトレース1006は、鋭く急上昇する。

【0030】

過渡電圧抑制の方法およびシステムの上述の実施形態は、EMIおよび/または落雷などから電気システムに誘起される電圧スパイクを低減しかつ/または除去するためのコスト効率の良い、信頼性のある手段を提供する。より具体的には、本明細書で述べる方法およびシステムは、比較的高い環境温度にさらされる電子装置の動作を容易にする。加えて、上述の方法およびシステムは、追加の冷却支援なしで高密度筐体中の電子部品を動作させることを容易にする。結果として、本明細書で述べる方法およびシステムは、航空機などの乗り物をコスト効率の良い、信頼性のある方法で動作させることを容易にする。

【0031】

この書面による明細は、例を使用してベストモードを含む本発明を開示し、また当業者ならだれでも任意のデバイスまたはシステムを作りかつ使用することおよび任意の組み込まれた方法を行うことを含み、本発明を実施することも可能にする。本発明の特許可能な範囲は、特許請求の範囲によって定義され、当業者には思い付く他の例を含んでもよい。そのような他の例は、もしそれらがクレームの文字通りの言葉と異ならない構造要素を有するならば、またはもしそれらがクレームの文字通りの言葉と実質的に異ならない等価な構成要素を含むならば、クレームの範囲内であることを意図している。

【符号の説明】

【0032】

100 分配システム

102 電力供給分配バス

104 通信チャネル

106 電子機器ユニット(EU)

110 エンジン

112 ファン

114 コアエンジン

116 EU

118 EU

120 HT−EU

122 HT−EU

124 HT−EU

126 電力供給装置

202 プロセッサ

206 メモリ

208 入力セクション

210 駆動モジュール

212 出力モジュール

214 通信モジュール

216 電力モジュール

218 TVSアセンブリ

220 TVSアセンブリ

302 半導体ダイ

304 基板

306 層

308 層

310 電気接点

312 層

314 電気接点

402 円錐台構造

404 円柱状構造

406 ヘッダーピン

408 ヘッダーピン

410 表面実装接点

412 表面実装接点

414 封入材

502 フランジ

504 フランジ

602 円錐台構造

604 円錐台構造

800 グラフ

802 x軸

804 y軸

806 トレース

808 トレース

900 グラフ

902 x軸

904 y軸

906 トレース

1000 グラフ

1002 x軸

1004 y軸

1006 トレース

【技術分野】

【0001】

本開示は、一般に高温半導体デバイスに関し、より具体的には、高温環境での過渡電圧抑制のための半導体デバイスに関する。

【背景技術】

【0002】

シリコンデバイスは、TVSデバイスに並列に結合された高感度電子機器が例えば落雷で生じる電圧スパイクにさらされ、損傷を受けるのを防止するために使用されてきたけれども、それらは、高温動作に適していない。シリコンデバイスは、温度が上昇するにつれてより高い電流を漏えいする傾向があり、その電流は、約150℃よりも大きい周囲温度では容認できないほど高い値に達し、それは、分散エンジン制御などのコアエンジン搭載電子機器を必要とする航空用途に必要な225℃以上の周囲温度でのそれらの使用を不適切にする。その上、周知のTVSデバイスは典型的には、エポキシ封入材を使用してパッケージ化される。エポキシパッケージ化は、約185℃より上でTVSデバイス構造内に大きな熱歪みを誘起し、分解し始める傾向がある。

【0003】

航空および発電の両方の用途のためのタービンエンジン機器類はしばしば、高価な冷却、または電子機器をセンサーおよびアクチュエータからさらに遠くに移動させることを必要とし、据え付けおよび配線の複雑さの増加ならびにノイズに起因するセンサー性能の低下をもたらす。航空機で分散制御に使用する電子機器は、落雷および電磁妨害(EMI)で生じる電圧サージから損傷を受けやすい。少なくともいくつかの周知の用途は、過渡電圧抑制(TVS)デバイスを使用し、それは、ツェナーダイオードに似た特徴を含むこともある。シリコンでできた市販のTVSデバイスは、それらがさらされることになる高い周囲温度に起因してエンジンコアの近くに置いた分散電子機器を保護するために使用することができない。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国特許出願公開第2011/0058299号明細書

【発明の概要】

【0005】

一実施形態では、過渡電圧抑制器(TVS)アセンブリは、第1の極性の導電性を有する第1の広バンドギャップ半導体の層を含む基板と、基板と電気的に接触して結合された第2の極性の導電性を有する第1または第2の広バンドギャップ半導体の第2の層であって、第2の極性は第1の極性と異なる、第2の層と、第2の層と電気的に接触して結合された第1の極性の導電性を有する第1、第2、または第3の広バンドギャップ半導体の第3の層とを含むメサ構造の半導体ダイを含む。第2の極性の導電性を有する層は、第1の極性の導電性を有する層に比して低濃度にドープされる。TVSアセンブリはまた、基板と電気的に接触して結合された第1の電極および第3の層と電気的に接触して結合された第2の電極も含む。所定の大きさよりも大きい電圧が、第1および第2の電極間に印加されるとき、TVSアセンブリは、比較的大量の電流がTVSアセンブリを通って流れることを可能にするパンチスルーモードで動作する。

【0006】

別の実施形態では、炭化ケイ素過渡電圧抑制器(TVS)アセンブリを形成する方法は、第1の側面および反対側の第2の側面を含むパンチスルー炭化ケイ素半導体過渡電圧抑制器ダイを提供するステップと、ダイを少なくとも部分的に取り囲むガラス筐体にダイを封入するステップと、第1および第2の側面の各々と電気的に接続してそれぞれの電極を結合するステップとを含み、各電極は、ガラス筐体の熱膨張係数と実質的に一致する熱膨張係数を有する。

【0007】

なお別の実施形態では、高温電子システムは、約150.0℃よりも大きい温度を有する環境にさらすように構成された電子機器ユニットを含み、遠隔電子機器ユニットは、電子機器ユニットの少なくともいくつかの電子部品と動作可能に結合された過渡電圧抑制器(TVS)アセンブリを含み、TVSは、ダイを少なくとも部分的に取り囲むガラス筐体に封入され、熱圧着接合、過渡的液相はんだ接合、拡散接合、および合金化層の少なくとも1つを使用して電極に結合されたパンチスルー炭化シリコン半導体TVSダイを含む。

【0008】

本技術のこれらのかつ他の特徴、態様、および利点は、類似の文字が図面全体にわたって類似の部分を表す添付の図面を参照して次の詳細な説明を読むときより良く理解されることになろう。

【図面の簡単な説明】

【0009】

【図1】本発明の例となる実施形態による電力および通信分配システムのアーキテクチャの概略ブロック図である。

【図2】本システムの例となる実施形態による図1で示す電子機器ユニットの例となる1つの概略ブロック図である。

【図3】本発明の例となる実施形態によるTVS218を使用して利用できる電圧抑制保護のさまざまな構成の概略ブロック図である。

【図4】本システムの例となる実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの半導体ダイ部分の側面図である。

【図5】本システムの別の実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの半導体ダイ部分の側面図である。

【図6】本システムの別の実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの半導体ダイ部分の側面図である。

【図7】本発明の例となる実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの側面図である。

【図8】本システムの例となる実施形態による図2で示す過渡電圧抑制(TVS)アセンブリの別の図である。

【図9】TVSアセンブリの雷試験波形の結果を例示するグラフ800である。

【図10】TVSアセンブリのDC試験の結果を例示するグラフ900である。

【図11】TVSアセンブリの図10で示すDC試験の結果を例示するグラフ1000である。

【発明を実施するための形態】

【0010】

次の詳細な説明は、システムの実施形態を例としてであって制限する目的ではなく例示する。システムおよび方法は、パワーエレクトロニクス、信号エレクトロニクス、ならびに工業、商業、および住宅用途での電磁妨害(EMI)保護の電子部品製造およびパッケージ化への一般的応用を有すると熟考される。

【0011】

本明細書で使用するように、単数形で列挙され、単語「a」または「an」が先行する要素またはステップは、そのような排除が明確に列挙されない限り、複数形の要素またはステップを排除しないと理解すべきである。さらにその上、本発明の「一実施形態」への言及は、列挙する特徴もまた組み込む追加の実施形態の存在を排除すると解釈されることを意図していない。

【0012】

本開示の実施形態は、300℃で確実に動作する半導体ベースのTVSデバイスを実証する。一実施形態では、デバイスは、炭化シリコン(SiC)から製作される。他の実施形態では、デバイスは、窒化ガリウム(GaN)、ダイヤモンド、窒化アルミニウム(AlN)、窒化ホウ素(BN)、およびそれらの組合せなどだが限定されない、他の広バンドギャップ材料から製作される。広バンドギャップ半導体TVSデバイスは、約500℃に至るまで確実に動作可能であるが、しかしながら、TVSパッケージ類などの他の部品は、例の実施形態ではより制限的なこともある。TVSは、クランプデバイスであり、それの降伏電圧より上のほぼすべての過電圧を抑制する。TVSデバイスは典型的には、3つのSiC層(N−P−N)を含む。他の実施形態では、3つの層は、P−N−P層を含む。N−P−N型デバイスでは、デバイスが2つのN層を横切る電位を受けるとき、P層のドーピングは2つのN層と比較してはるかにより低いので、空乏層は、P層中に(大部分)形成される。例えば、N層のドーパント濃度よりも大きさが1から5桁低い、またはN層のドーパント濃度の1/10から1/10000である。さらなる例については、もしN層でのドーピング濃度が、約1018/cm3であるならば、P層でのドーピング濃度は、約1015/cm3であることになる。デバイスを横切る電圧が増加するにつれて、空乏領域は、P層をすべて横切って延び、もう一方の側のN層に接触する。これは、「パンチスルー」として周知の条件をもたらし、大量の電流が、デバイスに流れ始める。デバイスは、それを横切る電圧の変化が最小の状態でこの条件を維持することができる。同様の説明は、層の極性がP−N−Pに変更されるときの動作も述べる。

【0013】

パッケージは、一例では、高速の電気的応答を提供するために低いインダクタンスおよび静電容量を有し、熱パルスを管理するために熱キャパシタンスを有するように設計される。低いインダクタンスおよび静電容量は、ダイから回路に接合される終端までの短い伝導経路を使用することによって達成される。ガラスまたはセラミック封入材は、ダイを環境での汚染から保護し、デバイスを横切る電気的絶縁の改善を提供するために使用されてもよい。ホウケイ酸ガラス封入材は、600℃に至るまでの試験で低い漏れ電流を有することが見いだされた。終端材料は、セラミックと金属との密封およびガラスと金属との密封にそれぞれ適合するように選択される。終端材料は、タングステン、モリブデン、またはKovar(登録商標)を含んでもよいが限定されない。ダイは、例えば熱圧着接合、過渡的液相はんだ接合、拡散接合、または合金化層を使用してそれぞれの終端に両側で接合される。一実施形態では、金熱圧着接合が、より低い熱抵抗経路を提供し、高温中で酸化しない。金はまた、大きな塑性域も有して特に高温で低応力界面を提供する。

【0014】

TVSデバイスは、TVSデバイスに並列に結合された高感度電子機器が例えば落雷で生じる電圧スパイクにさらされ、損傷を受けるのを防止することを容易にする。さまざまな実施形態では、2つ以上のTVSデバイスが、TVSデバイスの並列、直列、および/または直列並列構成を含むTVSアセンブリに接続されてTVSアセンブリの強化された電気的保護特徴、例えばより大きな電圧または電流能力を可能にしてもよい。高温パッケージでのSiCデバイスは、例えば約150℃よりも大きい、比較的高い周囲温度の環境にそれを配置することを可能にする。その上、SiCデバイスは、極めて強固なクランプを提供する。本明細書では高温用途での使用に適していると述べるけれども、広バンドギャップ材料はまた、温度が比較的高くない、例えば室温である用途にもよく適している。

【0015】

図1は、本発明の例となる実施形態による電力および通信分配システム100のアーキテクチャの概略ブロック図である。例となる実施形態では、分配システム100は、電力供給分配バス102および通信チャネル104を含む。電力供給分配バス102は、例となる実施形態では、エンジン110の周囲に位置する複数の電子機器ユニット106に電力を分配する。例となる実施形態では、エンジン110は、ファン112およびコアエンジン114を含むガスタービンエンジンである。さまざまな他の実施形態では、エンジン110は、ピストン駆動内燃エンジン、圧縮機、発電機、およびポンプなどだが限定されない、別の1台の機械であってもよい。例となる実施形態では、複数の電子機器ユニット106は、例えばガスタービンエンジン(GTE)110のファン112に隣接した比較的冷たい環境に取り付けられているように例示される電子機器ユニット(EU)116および118を含む。分配システム100はまた、高温電子機器ユニット(HT−EU)120、122、および124も含む。HT−EU120、122、および124の各々は、ガスタービンエンジン110のコアエンジン114に取り付けられているように例示され、それは、比較的熱い環境の場所である。例えば、コア筐体114の近辺での温度は、約150.0°セ氏(C)から約300.0℃のこともある。

【0016】

EU116は、電力供給装置126から電力を受け取る。受け取った電力は、EU116によって分配システム100内に分配するために管理される。管理された電力は、電力供給分配バス102を通ってEU118、HT−EU120、122および124を含むさまざまなそれぞれの負荷に送られる。同様に、さまざまな電子機器ユニット間の通信は、通信チャネル104を通って送られる。

【0017】

動作中は、航空機への電磁妨害および/または落雷が、バス102および/または104に大きな過渡電圧スパイクを誘起することもある。そのような大きな電圧スパイクは、もし修正しないならば、EU116、118、ならびにHT−EU120、122、および124を含む、バスに結合された電気部品および電子部品に損傷を引き起こすこともある。そのような損傷を避けるために、過渡電圧抑制器が、選択した部品および/または部品内の回路と直列にかつ/または並列に使用されてそのようなスパイクを低減しかつ/または除去することを容易にすることができる。一方法は、バスの電圧を所定のレベルにクランプする。

【0018】

図2は、本システムの例となる実施形態によるEU116、118、ならびにHT−EU120、122、および124の例となる1つの概略ブロック図である。例となる実施形態では、HT−EU120は例えば、プロセッサ202、プロセッサ202に通信可能に結合されたメモリ204、ROMメモリ206、またプロセッサ202に通信可能に結合もされた、入力セクション208、駆動モジュール210、および出力モジュール212を含む。HT−EU120はまた、通信バス104およびプロセッサ202に通信可能に結合された通信モジュール214も含む。HT−EU120はさらに、電力供給分配バス102に電気的に結合され、HT−EU120全体にわたってさまざまな電圧で電力を分配するように構成された電力モジュール216を含む。それぞれのバスに結合されていると、通信モジュール214および電力モジュール216は、EMIおよび/または雷誘起スパイクの影響を受けやすい。そのような妨害およびスパイクが通信モジュール214および電力モジュール216ならびに下流の部品に到達するのを防止するために、1つまたは複数の過渡電圧抑制(TVS)アセンブリ218および220が、それぞれのバスと通信モジュール214および電力モジュール216との間に結合される。

【0019】

図3A〜3Cは、本発明の例となる実施形態によるTVSアセンブリ218を使用して利用できる電圧抑制保護のさまざまな構成の概略ブロック図である。図3Aの実施形態では、TVSアセンブリ218は、直列構成の2つの過渡電圧抑制器を含む。図3Bの実施形態では、TVSアセンブリ218は、第3の過渡電圧抑制器と並列に直列構成の2つの過渡電圧抑制器を含む。図3Cの実施形態では、TVSアセンブリ218は、第3の過渡電圧抑制器と直列に並列構成の2つの過渡電圧抑制器を含む。個々の過渡電圧抑制器のさまざまな他の組合せが、多くの異なる用途にとって十分な電流運送能力および所定の電圧性能を提供するように組み立てられてもよい。

【0020】

図4は、本システムの例となる実施形態による過渡電圧抑制(TVS)アセンブリ218または220(図2で示す)の半導体ダイ302部分の側面図である。例となる実施形態では、ダイ302は、例えばn+型導電性を有する炭化シリコンの基板304ならびにエピタキシャル成長のn+型導電性層306、層306と電気的に接触して結合されたエピタキシャル成長のp−層308、およびp−層308と電気的に接触して結合されたエピタキシャル成長のn+層312で形成されるメサ構造を含む。例となる実施形態では、p−層308は、n+層306および312に比して比較的低濃度にドープされる。基板304ならびに層306、308、および312の均一なドーピング濃度は、空乏領域での電場分布の均一性を改善し、それによって降伏電圧特性を改善する。その上、メサ構造は、隣接接触層間の界面に関して約5度から約80度の角を成す傾斜側壁を有してダイの表面での最大電場プロファイルを低減する。第1の電気接点310は、基板304と電気的に接触して結合される。第2の電気接点314は、エピタキシャル成長のn+層312と電気的に接触して結合される。過渡電圧抑制(TVS)アセンブリ218または220の半導体ダイ302部分は、ダイ302を横切る電圧が増加するにつれて、空乏領域がp−層308をすべて横切って延び、n+層306および312に接触するような「パンチスルー」または「リーチスルー」としてもまた周知の物理的過程を使用して動作する。これは、「パンチスルー」として周知の条件をもたらし、大量の電流が、ダイ302を通って流れることができる。ダイ302は、それを横切る電圧の変化が最小の状態でこの条件を維持することができる。

【0021】

さまざまな実施形態では、TVSアセンブリ218は、ダイ302の半導体材料内部の最大電場が1センチメートル当たり2メガボルト未満に維持されることを確実にするような大きさおよび形にされる。加えて、TVSアセンブリ218は、約1.0ナノアンペア未満から約1.0ミリアンペアの範囲の電流について5%未満の阻止電圧の増加を維持するように構成される。本明細書で使用するように、阻止電圧は、TVSアセンブリ218が電気を通さないまたはなお「オフ」状態にある最高電圧のことである。その上、TVSアセンブリ218は、室温ではTVSアセンブリ218のほぼパンチスルー電圧に至るまで約1.0マイクロアンペア未満および225°セ氏に至るまでの動作温度ではほぼパンチスルー電圧に至るまで1.0マイクロアンペア未満の漏れ電流を維持するように構成される。

【0022】

さまざまな実施形態では、TVSアセンブリ218は、約5.0ボルトから約75.0ボルトの間でパンチスルー特性を示すように構成される。さまざまな他の実施形態では、TVSアセンブリ218は、約75.0ボルトから約200.0ボルトの間でパンチスルー特性を示すように構成される。なお他の実施形態では、TVSアセンブリ218は、約200ボルトよりも大きいところでパンチスルー特性を示すように構成される。

【0023】

図5は、本システムの別の実施形態による過渡電圧抑制(TVS)アセンブリ218または220(図2で示す)の半導体ダイ302部分の側面図である。例となる実施形態では、ダイ302は、第1の円錐台構造402および第2の実質的に円柱状の構造404を含む。第1の円錐台構造402は、エピタキシャル成長のn+型導電性層306およびエピタキシャル成長のp−層308の少なくとも一部分で形成される。円柱状構造404は、エピタキシャル成長のp−層308の少なくとも一部分およびエピタキシャル成長のn+層312で形成される。例となる実施形態では、p−層308は、n+層306および312に比して比較的低濃度にドープされる。基板304ならびに層306、308、および312の均一なドーピング濃度は、空乏領域での電場分布の均一性を改善し、それによって降伏電圧特性を改善する。第1の電気接点310は、基板304と電気的に接触して結合される。第2の電気接点314は、エピタキシャル成長のn+層312と電気的に接触して結合される。

【0024】

図6は、本システムの別の実施形態による過渡電圧抑制(TVS)アセンブリ218または220(図2で示す)の半導体ダイ302部分の側面図である。例となる実施形態では、ダイ302は、第1の円錐台構造602および第2の円錐台構造604を含む。第1の円錐台構造602は、エピタキシャル成長のn+型導電性層306およびエピタキシャル成長のp−層308の少なくとも一部分で形成される。第2の円錐台構造604は、エピタキシャル成長のp−層308の少なくとも一部分およびエピタキシャル成長のn+層312で形成される。例となる実施形態では、p−層308は、n+層306および312に比して比較的低濃度にドープされる。基板304ならびに層306、308、および312の均一なドーピング濃度は、空乏領域での電場分布の均一性を改善し、それによって降伏電圧特性を改善する。第1の電気接点310は、基板304と電気的に接触して結合される。第2の電気接点314は、エピタキシャル成長のn+層312と電気的に接触して結合される。

【0025】

図7は、本発明の例となる実施形態による過渡電圧抑制(TVS)アセンブリ218(図2で示す)の側面図である。例となる実施形態では、第1および第2の電気接点310および314はそれぞれ、拡散接合または合金化層702および704ならびにそれぞれのヘッダーピン406および408を含む。さまざまな実施形態では、層702および704は、銅(Cu)、金(Au)、アルミニウム(Al)、白金(Pt)およびそれらの組合せで形成される。他の実施形態では、層702および704は、他の材料、組合せまたは合金で形成されてもよい。さまざまな実施形態では、第1および第2の電気接点310および314は、例えば熱圧着接合、過渡的液相はんだ接合、拡散接合、または合金化層だが限定されないそれらを使用する層702および704を使用してダイ302に結合される。表面実装接点410および412は、第1および第2の電気接点310および314と電気的に接触して結合され、典型的にはヘッダーピン406および408にそれぞれ結合される。ガラス封入材414は、ダイ302ならびに第1および第2の電気接点310および314を少なくとも部分的に取り囲む。さまざまな実施形態では、ガラス封入材414は、ホウケイ酸ガラスまたはアルミナセラミックを含む。ヘッダーピン406および408は、ガラス封入材414の熱膨張係数と実質的に一致する熱膨張係数を有するように選択した材料から形成される。そのような材料は、タングステン、モリブデン、鉄−ニッケル−コバルト、時にはKovar(登録商標)と呼ばれる低膨張合金およびそれらの組合せの少なくとも1つを含んでもよい。Kovar(登録商標)合金は、真空溶解した鉄−ニッケル−コバルトの低いまたは制御された膨張合金であり、その化学組成は、正確な均一熱膨張特性を確保するために狭い制限内に制御される。例となる実施形態では、ヘッダーピン406および408は、約29%ニッケル(Ni)、17%コバルト(Co)を含み、残余は実質的に鉄(Fe)である材料から形成される。

【0026】

図8は、本システムの例となる実施形態による過渡電圧抑制(TVS)アセンブリ218(図2で示す)の別の図である。例となる実施形態では、ヘッダーピン406および408は、ガラス封入材414と一緒になり、例えばはんだ接続を受けてTVSアセンブリ218を回路に電気的に結合するように構成されたフランジ502および504を有して形成される。

【0027】

図9は、TVSアセンブリ218の雷試験波形を例示するグラフ800である。例となる実施形態では、グラフ800は、時間の単位で目盛の付いたx軸802ならびに電圧および電流の単位で目盛の付いたy軸804を含む。トレース806は、TVSアセンブリ218にかける電圧を表し、それのピークは、TVSアセンブリ218のクランプ電圧を指し示す。例となる実施形態では、それは、約100.0ボルトである。トレース808は、TVSアセンブリ218を通って流れる電流を表し、それは、約134アンペアである。

【0028】

図10は、DC試験を例示するグラフ900である。例となる実施形態では、グラフ900は、電圧の単位で目盛の付いたx軸902および対数尺度を使用して電流の単位で目盛の付いたy軸904を含む。トレース906は、第1および第2の電気接点310および312を横切って電圧を与え、対応する電流を測定するときのTVSアセンブリ218の応答を表す。DC試験は、TVSアセンブリ218の高温能力を決定するために約200°セ氏でのTVSアセンブリ218について行われる。例となる実施形態では、TVSアセンブリ218は、約65.0ボルトでオンになり、そこではトレース906は、平坦になる。65.0ボルト未満の電圧では、TVSアセンブリ218は、「オフ」条件にある。TVSアセンブリ218がオフであるときに流れる電流は、漏れ電流である。TVSアセンブリ218を通る漏れ電流値は、TVSアセンブリ218が高温でオフであり低い漏れ電流を示すときは、極めて小さく、例えばピコアンペアの範囲であることがわかる。

【0029】

図11は、TVS218のDC試験を例示するグラフ1000である。例となる実施形態では、グラフ1000は、電圧の単位で目盛の付いたx軸1002および線形尺度を使用して電流の単位で目盛の付いたy軸1004を含む。トレース1006は、第1および第2の電気接点310および312を横切って電圧を与え、対応する電流を測定するときのTVSアセンブリ218の応答を表す。DC試験は、TVSアセンブリ218の高温能力を決定するために約200°セ氏でのTVSアセンブリ218について行われる。例となる実施形態では、TVSアセンブリ218は、約65.0ボルトでオンになり、そこではトレース1006は、鋭く急上昇する。

【0030】

過渡電圧抑制の方法およびシステムの上述の実施形態は、EMIおよび/または落雷などから電気システムに誘起される電圧スパイクを低減しかつ/または除去するためのコスト効率の良い、信頼性のある手段を提供する。より具体的には、本明細書で述べる方法およびシステムは、比較的高い環境温度にさらされる電子装置の動作を容易にする。加えて、上述の方法およびシステムは、追加の冷却支援なしで高密度筐体中の電子部品を動作させることを容易にする。結果として、本明細書で述べる方法およびシステムは、航空機などの乗り物をコスト効率の良い、信頼性のある方法で動作させることを容易にする。

【0031】

この書面による明細は、例を使用してベストモードを含む本発明を開示し、また当業者ならだれでも任意のデバイスまたはシステムを作りかつ使用することおよび任意の組み込まれた方法を行うことを含み、本発明を実施することも可能にする。本発明の特許可能な範囲は、特許請求の範囲によって定義され、当業者には思い付く他の例を含んでもよい。そのような他の例は、もしそれらがクレームの文字通りの言葉と異ならない構造要素を有するならば、またはもしそれらがクレームの文字通りの言葉と実質的に異ならない等価な構成要素を含むならば、クレームの範囲内であることを意図している。

【符号の説明】

【0032】

100 分配システム

102 電力供給分配バス

104 通信チャネル

106 電子機器ユニット(EU)

110 エンジン

112 ファン

114 コアエンジン

116 EU

118 EU

120 HT−EU

122 HT−EU

124 HT−EU

126 電力供給装置

202 プロセッサ

206 メモリ

208 入力セクション

210 駆動モジュール

212 出力モジュール

214 通信モジュール

216 電力モジュール

218 TVSアセンブリ

220 TVSアセンブリ

302 半導体ダイ

304 基板

306 層

308 層

310 電気接点

312 層

314 電気接点

402 円錐台構造

404 円柱状構造

406 ヘッダーピン

408 ヘッダーピン

410 表面実装接点

412 表面実装接点

414 封入材

502 フランジ

504 フランジ

602 円錐台構造

604 円錐台構造

800 グラフ

802 x軸

804 y軸

806 トレース

808 トレース

900 グラフ

902 x軸

904 y軸

906 トレース

1000 グラフ

1002 x軸

1004 y軸

1006 トレース

【特許請求の範囲】

【請求項1】

第1の極性の導電性を有する第1の広バンドギャップ半導体の層を含む基板(306)と、

前記基板と電気的に接触して結合された第2の極性の導電性を有する前記第1または第2の広バンドギャップ半導体の第2の層(308)であって、前記第2の極性は前記第1の極性と異なる、第2の層と、

前記第2の層と電気的に接触して結合された前記第1の極性の導電性を有する前記第1、前記第2、または第3の広バンドギャップ半導体の第3の層(312)とを含み、

前記第2の極性の導電性を有する前記層は、前記第1の極性の導電性を有する前記層に比して低濃度にドープされる、メサ構造の半導体ダイ(302)と、

前記基板と電気的に接触して結合された第1の電極(310)と、

前記第3の層と電気的に接触して結合された第2の電極(314)とを含む過渡電圧抑制器(TVS)アセンブリ(218)であって、

所定の大きさよりも大きい電圧が、前記第1および第2の電極を横切って印加されるとき、前記TVSアセンブリは、比較的大量の電流が前記TVSアセンブリを通って流れることを可能にするパンチスルーモードで動作する、TVSアセンブリ。

【請求項2】

前記ダイならびに前記第1および第2の電極を少なくとも部分的に取り囲むガラスまたはセラミック封入材(414)さらに含む、請求項1記載のTVSアセンブリ。

【請求項3】

第1の極性の導電性を有する前記層は、n+型導電性層を含み、第2の極性の導電性を有する前記層は、p−型導電性層を含む、請求項1記載のTVSアセンブリ。

【請求項4】

第1の極性の導電性を有する前記層は、p+型導電性層を含み、第2の極性の導電性を有する前記層は、n−型導電性層を含む、請求項1記載のTVSアセンブリ。

【請求項5】

前記基板および前記層は、炭化シリコン(SiC)、窒化ガリウム(GaN)、ダイヤモンド、窒化アルミニウム(AlN)、窒化ホウ素(BN)、およびそれらの組合せの少なくとも1つを含む、請求項1記載のTVSアセンブリ。

【請求項6】

SiCを含む第2の極性の導電性を有する層について、ドーパント濃度は、第1の極性の導電性を有する前記層のドーパント濃度よりも大きさが約1から5桁小さい、請求項1記載のTVSアセンブリ。

【請求項7】

SiCを含む第2の極性の導電性を有する層について、ドーパント濃度は、第1の極性の導電性を有する前記層のドーパント濃度の約1/1000である、請求項6記載のTVSアセンブリ。

【請求項8】

前記第1および前記第2の電極の各々と前記ダイとの間に位置する拡散接合または合金化接触層(702、704)をさらに含む、請求項1記載のTVSアセンブリ。

【請求項9】

前記拡散接合または合金化接触層は、銅(Cu)、金(Au)、アルミニウム(Al)、白金(Pt)およびそれらの組合せを含む、請求項8記載のTVSアセンブリ。

【請求項10】

前記第1および前記第2の電極は、前記ガラス封入材の熱膨張係数と実質的に一致する熱膨張係数を含む、請求項1記載のTVSアセンブリ。

【請求項1】

第1の極性の導電性を有する第1の広バンドギャップ半導体の層を含む基板(306)と、

前記基板と電気的に接触して結合された第2の極性の導電性を有する前記第1または第2の広バンドギャップ半導体の第2の層(308)であって、前記第2の極性は前記第1の極性と異なる、第2の層と、

前記第2の層と電気的に接触して結合された前記第1の極性の導電性を有する前記第1、前記第2、または第3の広バンドギャップ半導体の第3の層(312)とを含み、

前記第2の極性の導電性を有する前記層は、前記第1の極性の導電性を有する前記層に比して低濃度にドープされる、メサ構造の半導体ダイ(302)と、

前記基板と電気的に接触して結合された第1の電極(310)と、

前記第3の層と電気的に接触して結合された第2の電極(314)とを含む過渡電圧抑制器(TVS)アセンブリ(218)であって、

所定の大きさよりも大きい電圧が、前記第1および第2の電極を横切って印加されるとき、前記TVSアセンブリは、比較的大量の電流が前記TVSアセンブリを通って流れることを可能にするパンチスルーモードで動作する、TVSアセンブリ。

【請求項2】

前記ダイならびに前記第1および第2の電極を少なくとも部分的に取り囲むガラスまたはセラミック封入材(414)さらに含む、請求項1記載のTVSアセンブリ。

【請求項3】

第1の極性の導電性を有する前記層は、n+型導電性層を含み、第2の極性の導電性を有する前記層は、p−型導電性層を含む、請求項1記載のTVSアセンブリ。

【請求項4】

第1の極性の導電性を有する前記層は、p+型導電性層を含み、第2の極性の導電性を有する前記層は、n−型導電性層を含む、請求項1記載のTVSアセンブリ。

【請求項5】

前記基板および前記層は、炭化シリコン(SiC)、窒化ガリウム(GaN)、ダイヤモンド、窒化アルミニウム(AlN)、窒化ホウ素(BN)、およびそれらの組合せの少なくとも1つを含む、請求項1記載のTVSアセンブリ。

【請求項6】

SiCを含む第2の極性の導電性を有する層について、ドーパント濃度は、第1の極性の導電性を有する前記層のドーパント濃度よりも大きさが約1から5桁小さい、請求項1記載のTVSアセンブリ。

【請求項7】

SiCを含む第2の極性の導電性を有する層について、ドーパント濃度は、第1の極性の導電性を有する前記層のドーパント濃度の約1/1000である、請求項6記載のTVSアセンブリ。

【請求項8】

前記第1および前記第2の電極の各々と前記ダイとの間に位置する拡散接合または合金化接触層(702、704)をさらに含む、請求項1記載のTVSアセンブリ。

【請求項9】

前記拡散接合または合金化接触層は、銅(Cu)、金(Au)、アルミニウム(Al)、白金(Pt)およびそれらの組合せを含む、請求項8記載のTVSアセンブリ。

【請求項10】

前記第1および前記第2の電極は、前記ガラス封入材の熱膨張係数と実質的に一致する熱膨張係数を含む、請求項1記載のTVSアセンブリ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−93574(P2013−93574A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−228503(P2012−228503)

【出願日】平成24年10月16日(2012.10.16)

【出願人】(390041542)ゼネラル・エレクトリック・カンパニイ (6,332)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2012−228503(P2012−228503)

【出願日】平成24年10月16日(2012.10.16)

【出願人】(390041542)ゼネラル・エレクトリック・カンパニイ (6,332)

【Fターム(参考)】

[ Back to top ]