過電圧保護回路

【課題】製造し易い高耐圧素子を使用し、且つ、インピーダンスのバラツキを考慮しなくても良い過電圧保護回路。

【解決手段】制御信号によりスイッチング素子Q1を駆動する駆動部10と、スイッチング素子のドレインとソースとの間に接続され、コンデンサC2と抵抗R1とが直列に接続された微分回路と、抵抗R1の両端に接続され、抵抗R2とコンデンサC3とが直列に接続された積分回路と、コンデンサC3の電圧が基準電圧以上となった場合にドレイン及びソース間の電圧が所定電圧以上になったと判定し、スイッチング素子をオンさせてドレイン及びソース間の電圧をクランプさせる過電圧保護部A1,R3,C4とを備える。

【解決手段】制御信号によりスイッチング素子Q1を駆動する駆動部10と、スイッチング素子のドレインとソースとの間に接続され、コンデンサC2と抵抗R1とが直列に接続された微分回路と、抵抗R1の両端に接続され、抵抗R2とコンデンサC3とが直列に接続された積分回路と、コンデンサC3の電圧が基準電圧以上となった場合にドレイン及びソース間の電圧が所定電圧以上になったと判定し、スイッチング素子をオンさせてドレイン及びソース間の電圧をクランプさせる過電圧保護部A1,R3,C4とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、サージ電圧からトランジスタを保護するための過電圧保護回路に関し、特にスイッチング素子のゲートを駆動するゲート駆動回路に用いられる。

【背景技術】

【0002】

近年、スイッチング電源等に用いられる出力用のトランジスタによるスイッチング動作の高速化が進み、スイッチの切り替え時においてソレノイド等を用いた負荷回路のインダクタンスにより発生する逆起電圧が大きくなる。このため、ターンオフ時に開放状態となったトランジスタのドレイン−ソース間にサージ電圧が印加されてブレークダウンが引き起こされる場合がある。このため、サージ電圧からトランジスタを保護するための過電圧保護回路が必要である。

【0003】

特許文献1には、誘導性負荷を高速遮断することを目的とするハイサイドスイッチ用の半導体装置が記載され、ハイサイドスイッチのドレイン−ソース間電圧を抑制する方法が記載されている。特に、ハイサイドスイッチのドレイン−ゲート端子間にツェナーダイオードとダイオードとを直列に接続した能動クランプ回路(アクティブクランプ回路)がドレイン−ソース間電圧を抑制してハイサイドスイッチを保護する方法が開示されている。

【0004】

特許文献2には、IGBTやMOSFETの高速スイッチング時に発生する過大サージ電圧を低い値に抑制することを目的とする電力変換装置が記載されている。この電力変換装置は、ハイサイドスイッチ及びローサイドスイッチのいずれにも適用できる能動クランプ回路を採用している。特許文献2における能動クランプ回路は、その構成中におけるダイオードにコンデンサを並列接続させることにより、負帰還パスを迅速に形成して過電圧をクランプすることができる。

【0005】

このように、従来の過電圧保護回路では、ツェナーダイオードや抵抗、コンデンサを用いて過電圧を検出していた。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平8−288817号公報

【特許文献2】特開2001−245466号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、ツェナーダイオードで過電圧を検出する場合には、高耐圧のツェナーダイオードを製造する必要があった。また、2個以上の抵抗を分割して過電圧を検出する場合には、抵抗に常に電流が流れているため、損失が多くなる。さらに、2個以上のコンデンサを分割して過電圧を検出する場合には、インピーダンスのバラツキにより検出電圧精度が低下していた。

【0008】

本発明の課題は、製造し易い高耐圧素子を使用し、且つ、インピーダンスのバラツキを考慮しなくても良い過電圧保護回路を提供することにある。

【課題を解決するための手段】

【0009】

上記の課題を解決するために、本発明に係る過電圧保護回路は、スイッチング素子のゲートを駆動するゲート駆動回路であって、制御信号により前記スイッチング素子を駆動する駆動部と、前記スイッチング素子の第1主端子と第2主端子との間に接続され、第1コンデンサと第1抵抗とが直列に接続された微分回路と、前記第1抵抗の両端に接続され、第2抵抗と第2コンデンサとが直列に接続された積分回路と、前記第2コンデンサの電圧が基準電圧以上となった場合に前記第1主端子及び前記第2主端子間の電圧が所定電圧以上になったと判定し、前記スイッチング素子をオンさせて前記第1主端子及び前記第2主端子間の電圧をクランプさせる過電圧保護部とを備えることを特徴とする。

【発明の効果】

【0010】

本発明に係る過電圧保護回路によれば、第1コンデンサと第1抵抗とからなる微分回路によりスイッチング素子の第1主端子に印加された電圧のdV/dtを検出し、dV/dtに比例する第1抵抗の両端電圧を第2抵抗と第2コンデンサとからなる積分回路により積分すると、第2コンデンサには、スイッチング素子の第1主端子と第2主端子間の電圧に比例した電圧が発生する。

【0011】

過電圧保護部は、第2コンデンサの電圧が基準電圧以上となった場合に第1主端子及び第2主端子間の電圧が所定電圧以上になったと判定し、スイッチング素子をオンさせて第1主端子及び前記第2主端子間の電圧をクランプさせるので、過電圧を防止できる。従って、製造し易い高耐圧素子で構成でき、且つ、インピーダンスのバラツキを考慮しなくても良い

【図面の簡単な説明】

【0012】

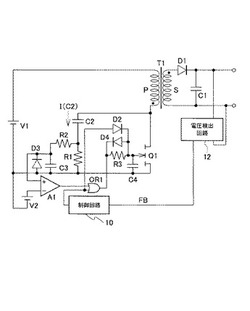

【図1】本発明の実施例1に係る過電圧保護回路の構成を示す図である。

【図2】本発明の実施例1に係る過電圧保護回路の動作を示すタイミングチャートである。

【図3】本発明の実施例2に係る過電圧保護回路の構成を示す図である。

【図4】本発明の実施例3に係る過電圧保護回路の構成を示す図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態に係る過電圧保護回路について、図面を参照しながら詳細に説明する。

【実施例1】

【0014】

図1は、本発明の実施例1に係る過電圧保護回路の構成を示す図である。図1に示す実施例1に係る過電圧保護回路において、直流電源V1の両端には、トランスT1の一次巻線Pとスイッチング素子Q1との直列回路が接続される。

【0015】

スイッチング素子Q1は、GaN HEMT(High Electron Mobility Transistor)からなる。あるいは、スイッチング素子Q1は、バイポーラトランジスタ、IGBT(絶縁ゲートトランジスタ)であっても良い。スイッチング素子Q1は、制御回路10からの制御信号によりオン/オフされる。

【0016】

トランスT1の二次巻線Sの両端にはダイオードD1とコンデンサC1との直列回路が接続される。ダイオードD1とコンデンサC1とは、整流平滑回路を構成し、トランスT1の二次巻線Sの両端に発生した電圧を整流平滑して直流電圧を図示しない負荷に供給する。

【0017】

電圧検出回路12は、コンデンサC1の両端電圧を検出し、検出された電圧をフィードバック信号FBとして制御回路10に出力する。制御回路10は、電圧検出回路12からのフィードバック信号FBに応じてスイッチング素子Q1のオンオフを制御する。

【0018】

スイッチング素子Q1のドレイン(第1主端子)−ソース(第2主端子)の間には、抵抗R1(第1抵抗)とコンデンサC2(第1コンデンサ)とが直列に接続された微分回路が接続される。微分回路は、スイッチング素子Q1のドレインに印加された電圧のdV/dtを検出する。

【0019】

抵抗R1の両端には、抵抗R2(第2抵抗)とコンデンサC3(第2コンデンサ)とが直列に接続された積分回路が接続される。積分回路は、検出されたdV/dtに比例する抵抗R1の両端電圧を積分することにより、コンデンサC3の両端に、スイッチング素子Q1のドレイン−ソース間の電圧Vdsに比例した電圧を発生させる。

【0020】

コンデンサC3の両端にはダイオードD3のアノードとカソードとが接続される。ダイオードD3はコンパレータA1を保護するために設けられている。

【0021】

コンデンサC3と抵抗R2との接続点とダイオードD3のカソードとにはコンパレータA1の非反転入力端子(+)が接続され、コンパレータA1の反転入力端子(−)には基準電源V2の正極が接続される。基準電源V2の負極は、直流電源V1の負極とダイオードD3のアノードとコンデンサC3の一端と抵抗R1の一端とコンデンサC4の一端とスイッチング素子Q1のソースとが接続される。

【0022】

コンパレータA1は、コンデンサC3の電圧と基準電源V2の基準電圧とを比較し、コンデンサC3の電圧が基準電源V2の基準電圧以上になったときにHレベルをオア回路OR1の一方の入力端子に出力する。

【0023】

オア回路OR1の他方の入力端子には、制御回路10の出力端子とダイオードD2のアノードとが接続され、ダイオードD2のカソードはスイッチング素子Q1のゲートに接続される。ダイオードD2は、制御回路10からの制御信号を直接スイッチング素子Q1のゲートに印加するために設けられる。

【0024】

オア回路OR1は、コンパレータA1からの出力と制御回路10からの出力との論理和とを取る。オア回路OR1の出力端子には、ダイオードD4のカソードと抵抗R3の一端が接続され、ダイオードD4のアノードと抵抗R3の他端とはスイッチング素子Q1のゲートに接続される。スイッチング素子Q1のゲート−ソース間にはコンデンサC4が接続される。抵抗R3とコンデンサC4とは、オア回路OR1からの保護信号に対して抵抗R3とコンデンサC4とによる時定数だけ遅延する遅延回路を構成する。

【0025】

コンパレータA1、オア回路OR1、抵抗R3、コンデンサC4は過電圧保護部を構成する。

【0026】

次にこのように構成された実施例1に係る過電圧保護回路の動作を図2に示す各部のタイミングチャートを参照しながら詳細に説明する。図2において、Vds(Q1)はスイッチング素子Q1のドレイン−ソース間の電圧、V(R1)は抵抗R1の両端電圧、V(C3)はコンデンサC3の両端電圧、A1outはコンパレータA1の出力、Vgs(Q1)はスイッチング素子Q1のゲート−ソース間の電圧、Id(Q1)はスイッチング素子Q1のドレイン電流である。

【0027】

まず、時刻t0において、スイッチング素子Q1がターンオフすると、スイッチング素子Q1のドレイン−ソース間の電圧Vds(Q1)が時刻t0〜t2まで上昇する。時刻t0〜t2の時間は、抵抗R1とコンデンサC2との時定数により決定される。

【0028】

また、コンデンサC2と抵抗R1とからなる微分回路は、スイッチング素子Q1のドレインに印加された電圧Vds(Q1)のdV/dtを検出する。このため、電圧Vds(Q1)のdV/dtに比例する抵抗R1の両端電圧V(R1)は、図2に示すように変化する。

【0029】

次に、抵抗R2とコンデンサC3とからなる積分回路により積分すると、コンデンサC3には、スイッチング素子Q1の電圧Vds(Q1)に比例した電圧V(C3)が発生する。電圧V(C3)は、図2に示すように、直線的に増加していく。

【0030】

時刻t1において、コンデンサC3の電圧V(C3)が基準電圧V2に達すると、コンパレータA1の出力A1outは、Hレベルとなり、オア回路OR1を介して、抵抗R3に供給される。抵抗R2とコンデンサC4とは、オア回路OR1からのHレベルを抵抗R2とコンデンサC4とによる時定数だけ、即ち、時刻t1〜t2の時間だけ遅延して、スイッチング素子Q1のゲートに印加する。

【0031】

すると、時刻t1〜t2において、スイッチング素子Q1のゲート−ソース間の電圧Vgs(Q1)が直線的に上昇して、時刻t2において、オン開始電圧Vthに達すると、スイッチング素子Q1がオンする。

【0032】

すると、スイッチング素子Q1のドレイン−ソース間に電流Id(Q1)が流れる。このため、スイッチング素子Q1の電圧Vds(Q1)の上昇が抑えられて、下降するため、電圧V(R1)は負電圧となる。これに伴って、コンデンサC3の電圧V(C3)も低下して、時刻t3において、電圧V(C3)が基準電圧V2未満となると、コンパレータA1のA1outは、Lレベルとなるので、電流Id(Q1)がゼロとなる。

【0033】

すると、スイッチング素子Q1の電圧Vds(Q1)が上昇して基準電圧V2に達すると、コンパレータA1の出力A1outは、Hレベルとなるので、上述したように、スイッチング素子Q1の間欠オン動作が時刻t4まで繰り返し行われる。時刻t5〜t7では、電圧Vds(Q1)が電圧VPよりも充分に低い電圧に下がっているので、スイッチング素子Q1の間欠オン動作は行われない。

【0034】

このように、コンパレータA1とオア回路OR1と抵抗R3とコンデンサC4とからなる過電圧保護部は、コンデンサC3の電圧が基準電圧V2以上となった場合に電圧Vds(Q1)が所定電圧VP以上になったと判定し、スイッチング素子Q1をオンさせて電圧Vds(Q1)を所定電圧VPにクランプさせるので、過電圧を防止できる。

【0035】

また、時刻t0〜t2の時間、時刻t4〜t8の時間においては、電流Id(Q1)が流れないので、損失が少なくなる。従って、製造し易い高耐圧素子を使用でき、且つ、インピーダンスのバラツキを考慮しなくても良い。

【実施例2】

【0036】

図3は、本発明の実施例2に係る過電圧保護回路の構成を示す図である。図3に示す実施例2に係る過電圧保護回路は、図1に示す実施例1に係る過電圧保護回路のコンデンサC2に代えて、ツェナーダイオードZDを設けたことを特徴とする。

【0037】

ツェナーダイオードZDのカソードをスイッチング素子Q1のドレインに接続し、ツェナーダイオードZDのアノードを抵抗R1の一端に接続している。即ち、ツェナーダイオードZDを逆バイアス状態にすることで、ツェナーダイオードZDの接合容量がコンデンサC2の役割を果すので、実施例2に係る過電圧保護回路においても実施例1に係る過電圧保護回路の効果と同様な効果が得られる。

【実施例3】

【0038】

図4は、本発明の実施例3に係る過電圧保護回路の構成を示す図である。図4に示す実施例3に係る過電圧保護回路は、図3に示す実施例2に係る過電圧保護回路のツェナーダイオードZDに並列にコンデンサC5を接続したことを特徴とする。

【0039】

ツェナーダイオードZDの接合容量では所望のコンデンサ値が足りない場合には、ツェナーダイオードZDに並列にコンデンサC5を接続することで、微分回路を構成することができる。これによって、実施例3に係る過電圧保護回路においても実施例1に係る過電圧保護回路の効果と同様な効果が得られる。

【産業上の利用可能性】

【0040】

本発明は、ゲート駆動回路に利用可能である。

【符号の説明】

【0041】

V1 直流電源

V2 基準電源

T1 トランス

D1〜D4 ダイオード

C1〜C5 コンデンサ

R1〜R3 抵抗

ZD ツェナーダイオード

A1 コンパレータ

Q1 スイッチング素子

OR1 オア回路

10 制御回路

12 電圧検出回路

【技術分野】

【0001】

本発明は、サージ電圧からトランジスタを保護するための過電圧保護回路に関し、特にスイッチング素子のゲートを駆動するゲート駆動回路に用いられる。

【背景技術】

【0002】

近年、スイッチング電源等に用いられる出力用のトランジスタによるスイッチング動作の高速化が進み、スイッチの切り替え時においてソレノイド等を用いた負荷回路のインダクタンスにより発生する逆起電圧が大きくなる。このため、ターンオフ時に開放状態となったトランジスタのドレイン−ソース間にサージ電圧が印加されてブレークダウンが引き起こされる場合がある。このため、サージ電圧からトランジスタを保護するための過電圧保護回路が必要である。

【0003】

特許文献1には、誘導性負荷を高速遮断することを目的とするハイサイドスイッチ用の半導体装置が記載され、ハイサイドスイッチのドレイン−ソース間電圧を抑制する方法が記載されている。特に、ハイサイドスイッチのドレイン−ゲート端子間にツェナーダイオードとダイオードとを直列に接続した能動クランプ回路(アクティブクランプ回路)がドレイン−ソース間電圧を抑制してハイサイドスイッチを保護する方法が開示されている。

【0004】

特許文献2には、IGBTやMOSFETの高速スイッチング時に発生する過大サージ電圧を低い値に抑制することを目的とする電力変換装置が記載されている。この電力変換装置は、ハイサイドスイッチ及びローサイドスイッチのいずれにも適用できる能動クランプ回路を採用している。特許文献2における能動クランプ回路は、その構成中におけるダイオードにコンデンサを並列接続させることにより、負帰還パスを迅速に形成して過電圧をクランプすることができる。

【0005】

このように、従来の過電圧保護回路では、ツェナーダイオードや抵抗、コンデンサを用いて過電圧を検出していた。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平8−288817号公報

【特許文献2】特開2001−245466号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、ツェナーダイオードで過電圧を検出する場合には、高耐圧のツェナーダイオードを製造する必要があった。また、2個以上の抵抗を分割して過電圧を検出する場合には、抵抗に常に電流が流れているため、損失が多くなる。さらに、2個以上のコンデンサを分割して過電圧を検出する場合には、インピーダンスのバラツキにより検出電圧精度が低下していた。

【0008】

本発明の課題は、製造し易い高耐圧素子を使用し、且つ、インピーダンスのバラツキを考慮しなくても良い過電圧保護回路を提供することにある。

【課題を解決するための手段】

【0009】

上記の課題を解決するために、本発明に係る過電圧保護回路は、スイッチング素子のゲートを駆動するゲート駆動回路であって、制御信号により前記スイッチング素子を駆動する駆動部と、前記スイッチング素子の第1主端子と第2主端子との間に接続され、第1コンデンサと第1抵抗とが直列に接続された微分回路と、前記第1抵抗の両端に接続され、第2抵抗と第2コンデンサとが直列に接続された積分回路と、前記第2コンデンサの電圧が基準電圧以上となった場合に前記第1主端子及び前記第2主端子間の電圧が所定電圧以上になったと判定し、前記スイッチング素子をオンさせて前記第1主端子及び前記第2主端子間の電圧をクランプさせる過電圧保護部とを備えることを特徴とする。

【発明の効果】

【0010】

本発明に係る過電圧保護回路によれば、第1コンデンサと第1抵抗とからなる微分回路によりスイッチング素子の第1主端子に印加された電圧のdV/dtを検出し、dV/dtに比例する第1抵抗の両端電圧を第2抵抗と第2コンデンサとからなる積分回路により積分すると、第2コンデンサには、スイッチング素子の第1主端子と第2主端子間の電圧に比例した電圧が発生する。

【0011】

過電圧保護部は、第2コンデンサの電圧が基準電圧以上となった場合に第1主端子及び第2主端子間の電圧が所定電圧以上になったと判定し、スイッチング素子をオンさせて第1主端子及び前記第2主端子間の電圧をクランプさせるので、過電圧を防止できる。従って、製造し易い高耐圧素子で構成でき、且つ、インピーダンスのバラツキを考慮しなくても良い

【図面の簡単な説明】

【0012】

【図1】本発明の実施例1に係る過電圧保護回路の構成を示す図である。

【図2】本発明の実施例1に係る過電圧保護回路の動作を示すタイミングチャートである。

【図3】本発明の実施例2に係る過電圧保護回路の構成を示す図である。

【図4】本発明の実施例3に係る過電圧保護回路の構成を示す図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態に係る過電圧保護回路について、図面を参照しながら詳細に説明する。

【実施例1】

【0014】

図1は、本発明の実施例1に係る過電圧保護回路の構成を示す図である。図1に示す実施例1に係る過電圧保護回路において、直流電源V1の両端には、トランスT1の一次巻線Pとスイッチング素子Q1との直列回路が接続される。

【0015】

スイッチング素子Q1は、GaN HEMT(High Electron Mobility Transistor)からなる。あるいは、スイッチング素子Q1は、バイポーラトランジスタ、IGBT(絶縁ゲートトランジスタ)であっても良い。スイッチング素子Q1は、制御回路10からの制御信号によりオン/オフされる。

【0016】

トランスT1の二次巻線Sの両端にはダイオードD1とコンデンサC1との直列回路が接続される。ダイオードD1とコンデンサC1とは、整流平滑回路を構成し、トランスT1の二次巻線Sの両端に発生した電圧を整流平滑して直流電圧を図示しない負荷に供給する。

【0017】

電圧検出回路12は、コンデンサC1の両端電圧を検出し、検出された電圧をフィードバック信号FBとして制御回路10に出力する。制御回路10は、電圧検出回路12からのフィードバック信号FBに応じてスイッチング素子Q1のオンオフを制御する。

【0018】

スイッチング素子Q1のドレイン(第1主端子)−ソース(第2主端子)の間には、抵抗R1(第1抵抗)とコンデンサC2(第1コンデンサ)とが直列に接続された微分回路が接続される。微分回路は、スイッチング素子Q1のドレインに印加された電圧のdV/dtを検出する。

【0019】

抵抗R1の両端には、抵抗R2(第2抵抗)とコンデンサC3(第2コンデンサ)とが直列に接続された積分回路が接続される。積分回路は、検出されたdV/dtに比例する抵抗R1の両端電圧を積分することにより、コンデンサC3の両端に、スイッチング素子Q1のドレイン−ソース間の電圧Vdsに比例した電圧を発生させる。

【0020】

コンデンサC3の両端にはダイオードD3のアノードとカソードとが接続される。ダイオードD3はコンパレータA1を保護するために設けられている。

【0021】

コンデンサC3と抵抗R2との接続点とダイオードD3のカソードとにはコンパレータA1の非反転入力端子(+)が接続され、コンパレータA1の反転入力端子(−)には基準電源V2の正極が接続される。基準電源V2の負極は、直流電源V1の負極とダイオードD3のアノードとコンデンサC3の一端と抵抗R1の一端とコンデンサC4の一端とスイッチング素子Q1のソースとが接続される。

【0022】

コンパレータA1は、コンデンサC3の電圧と基準電源V2の基準電圧とを比較し、コンデンサC3の電圧が基準電源V2の基準電圧以上になったときにHレベルをオア回路OR1の一方の入力端子に出力する。

【0023】

オア回路OR1の他方の入力端子には、制御回路10の出力端子とダイオードD2のアノードとが接続され、ダイオードD2のカソードはスイッチング素子Q1のゲートに接続される。ダイオードD2は、制御回路10からの制御信号を直接スイッチング素子Q1のゲートに印加するために設けられる。

【0024】

オア回路OR1は、コンパレータA1からの出力と制御回路10からの出力との論理和とを取る。オア回路OR1の出力端子には、ダイオードD4のカソードと抵抗R3の一端が接続され、ダイオードD4のアノードと抵抗R3の他端とはスイッチング素子Q1のゲートに接続される。スイッチング素子Q1のゲート−ソース間にはコンデンサC4が接続される。抵抗R3とコンデンサC4とは、オア回路OR1からの保護信号に対して抵抗R3とコンデンサC4とによる時定数だけ遅延する遅延回路を構成する。

【0025】

コンパレータA1、オア回路OR1、抵抗R3、コンデンサC4は過電圧保護部を構成する。

【0026】

次にこのように構成された実施例1に係る過電圧保護回路の動作を図2に示す各部のタイミングチャートを参照しながら詳細に説明する。図2において、Vds(Q1)はスイッチング素子Q1のドレイン−ソース間の電圧、V(R1)は抵抗R1の両端電圧、V(C3)はコンデンサC3の両端電圧、A1outはコンパレータA1の出力、Vgs(Q1)はスイッチング素子Q1のゲート−ソース間の電圧、Id(Q1)はスイッチング素子Q1のドレイン電流である。

【0027】

まず、時刻t0において、スイッチング素子Q1がターンオフすると、スイッチング素子Q1のドレイン−ソース間の電圧Vds(Q1)が時刻t0〜t2まで上昇する。時刻t0〜t2の時間は、抵抗R1とコンデンサC2との時定数により決定される。

【0028】

また、コンデンサC2と抵抗R1とからなる微分回路は、スイッチング素子Q1のドレインに印加された電圧Vds(Q1)のdV/dtを検出する。このため、電圧Vds(Q1)のdV/dtに比例する抵抗R1の両端電圧V(R1)は、図2に示すように変化する。

【0029】

次に、抵抗R2とコンデンサC3とからなる積分回路により積分すると、コンデンサC3には、スイッチング素子Q1の電圧Vds(Q1)に比例した電圧V(C3)が発生する。電圧V(C3)は、図2に示すように、直線的に増加していく。

【0030】

時刻t1において、コンデンサC3の電圧V(C3)が基準電圧V2に達すると、コンパレータA1の出力A1outは、Hレベルとなり、オア回路OR1を介して、抵抗R3に供給される。抵抗R2とコンデンサC4とは、オア回路OR1からのHレベルを抵抗R2とコンデンサC4とによる時定数だけ、即ち、時刻t1〜t2の時間だけ遅延して、スイッチング素子Q1のゲートに印加する。

【0031】

すると、時刻t1〜t2において、スイッチング素子Q1のゲート−ソース間の電圧Vgs(Q1)が直線的に上昇して、時刻t2において、オン開始電圧Vthに達すると、スイッチング素子Q1がオンする。

【0032】

すると、スイッチング素子Q1のドレイン−ソース間に電流Id(Q1)が流れる。このため、スイッチング素子Q1の電圧Vds(Q1)の上昇が抑えられて、下降するため、電圧V(R1)は負電圧となる。これに伴って、コンデンサC3の電圧V(C3)も低下して、時刻t3において、電圧V(C3)が基準電圧V2未満となると、コンパレータA1のA1outは、Lレベルとなるので、電流Id(Q1)がゼロとなる。

【0033】

すると、スイッチング素子Q1の電圧Vds(Q1)が上昇して基準電圧V2に達すると、コンパレータA1の出力A1outは、Hレベルとなるので、上述したように、スイッチング素子Q1の間欠オン動作が時刻t4まで繰り返し行われる。時刻t5〜t7では、電圧Vds(Q1)が電圧VPよりも充分に低い電圧に下がっているので、スイッチング素子Q1の間欠オン動作は行われない。

【0034】

このように、コンパレータA1とオア回路OR1と抵抗R3とコンデンサC4とからなる過電圧保護部は、コンデンサC3の電圧が基準電圧V2以上となった場合に電圧Vds(Q1)が所定電圧VP以上になったと判定し、スイッチング素子Q1をオンさせて電圧Vds(Q1)を所定電圧VPにクランプさせるので、過電圧を防止できる。

【0035】

また、時刻t0〜t2の時間、時刻t4〜t8の時間においては、電流Id(Q1)が流れないので、損失が少なくなる。従って、製造し易い高耐圧素子を使用でき、且つ、インピーダンスのバラツキを考慮しなくても良い。

【実施例2】

【0036】

図3は、本発明の実施例2に係る過電圧保護回路の構成を示す図である。図3に示す実施例2に係る過電圧保護回路は、図1に示す実施例1に係る過電圧保護回路のコンデンサC2に代えて、ツェナーダイオードZDを設けたことを特徴とする。

【0037】

ツェナーダイオードZDのカソードをスイッチング素子Q1のドレインに接続し、ツェナーダイオードZDのアノードを抵抗R1の一端に接続している。即ち、ツェナーダイオードZDを逆バイアス状態にすることで、ツェナーダイオードZDの接合容量がコンデンサC2の役割を果すので、実施例2に係る過電圧保護回路においても実施例1に係る過電圧保護回路の効果と同様な効果が得られる。

【実施例3】

【0038】

図4は、本発明の実施例3に係る過電圧保護回路の構成を示す図である。図4に示す実施例3に係る過電圧保護回路は、図3に示す実施例2に係る過電圧保護回路のツェナーダイオードZDに並列にコンデンサC5を接続したことを特徴とする。

【0039】

ツェナーダイオードZDの接合容量では所望のコンデンサ値が足りない場合には、ツェナーダイオードZDに並列にコンデンサC5を接続することで、微分回路を構成することができる。これによって、実施例3に係る過電圧保護回路においても実施例1に係る過電圧保護回路の効果と同様な効果が得られる。

【産業上の利用可能性】

【0040】

本発明は、ゲート駆動回路に利用可能である。

【符号の説明】

【0041】

V1 直流電源

V2 基準電源

T1 トランス

D1〜D4 ダイオード

C1〜C5 コンデンサ

R1〜R3 抵抗

ZD ツェナーダイオード

A1 コンパレータ

Q1 スイッチング素子

OR1 オア回路

10 制御回路

12 電圧検出回路

【特許請求の範囲】

【請求項1】

スイッチング素子のゲートを駆動するゲート駆動回路であって、

制御信号により前記スイッチング素子を駆動する駆動部と、

前記スイッチング素子の第1主端子と第2主端子との間に接続され、第1コンデンサと第1抵抗とが直列に接続された微分回路と、

前記第1抵抗の両端に接続され、第2抵抗と第2コンデンサとが直列に接続された積分回路と、

前記第2コンデンサの電圧が基準電圧以上となった場合に前記第1主端子及び前記第2主端子間の電圧が所定電圧以上になったと判定し、前記スイッチング素子をオンさせて前記第1主端子及び前記第2主端子間の電圧をクランプさせる過電圧保護部と、

を備えることを特徴とする過電圧保護回路。

【請求項2】

前記過電圧保護部は、前記第2コンデンサの電圧と基準電圧とを比較して前記第2コンデンサの電圧が基準電圧以上となった場合に保護信号を出力する比較部と、

前記比較部からの保護信号を所定時間だけ遅延させて前記スイッチング素子の制御端子に印加する遅延回路と、

を備えることを特徴とする請求項1記載の過電圧保護回路。

【請求項3】

前記スイッチング素子は、GaN HEMTであることを特徴とする請求項1又は請求項2記載の過電圧保護回路。

【請求項4】

前記第1コンデンサは、ツェナーダイオードの接合容量からなることを特徴とする請求項1乃至請求項3のいずれか1項記載の過電圧保護回路。

【請求項1】

スイッチング素子のゲートを駆動するゲート駆動回路であって、

制御信号により前記スイッチング素子を駆動する駆動部と、

前記スイッチング素子の第1主端子と第2主端子との間に接続され、第1コンデンサと第1抵抗とが直列に接続された微分回路と、

前記第1抵抗の両端に接続され、第2抵抗と第2コンデンサとが直列に接続された積分回路と、

前記第2コンデンサの電圧が基準電圧以上となった場合に前記第1主端子及び前記第2主端子間の電圧が所定電圧以上になったと判定し、前記スイッチング素子をオンさせて前記第1主端子及び前記第2主端子間の電圧をクランプさせる過電圧保護部と、

を備えることを特徴とする過電圧保護回路。

【請求項2】

前記過電圧保護部は、前記第2コンデンサの電圧と基準電圧とを比較して前記第2コンデンサの電圧が基準電圧以上となった場合に保護信号を出力する比較部と、

前記比較部からの保護信号を所定時間だけ遅延させて前記スイッチング素子の制御端子に印加する遅延回路と、

を備えることを特徴とする請求項1記載の過電圧保護回路。

【請求項3】

前記スイッチング素子は、GaN HEMTであることを特徴とする請求項1又は請求項2記載の過電圧保護回路。

【請求項4】

前記第1コンデンサは、ツェナーダイオードの接合容量からなることを特徴とする請求項1乃至請求項3のいずれか1項記載の過電圧保護回路。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−115852(P2013−115852A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−257291(P2011−257291)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

[ Back to top ]