過電流検出回路および半導体装置

【課題】過電流検出において精度の高い温度補償を行う。

【解決手段】制御回路20は、NMOSトランジスタNM0と出力端子OUT間を接続するワイヤ17に流れる負荷電流Iaとワイヤ17の抵抗分とによってワイヤ17の両端に生じる電位差を検出し、電位差が所定値より大きくなった場合に負過電流Iaを制限するようにNMOSトランジスタNM0を制御する。制御回路20は、一端から電流源I1によって電流を順方向に流すと共に他端をワイヤ17の一端に接続するダイオード群21と、一端から電流源I2によって電流を順方向に流すと共に他端をワイヤ17の他端に接続するダイオード群22と、を備え、ワイヤ17の抵抗分の温度変化によって生じる出力電流制限値の変化が少なくなるように、ダイオード群21、22の一端間の電位差に基づいて所定値を補正する。

【解決手段】制御回路20は、NMOSトランジスタNM0と出力端子OUT間を接続するワイヤ17に流れる負荷電流Iaとワイヤ17の抵抗分とによってワイヤ17の両端に生じる電位差を検出し、電位差が所定値より大きくなった場合に負過電流Iaを制限するようにNMOSトランジスタNM0を制御する。制御回路20は、一端から電流源I1によって電流を順方向に流すと共に他端をワイヤ17の一端に接続するダイオード群21と、一端から電流源I2によって電流を順方向に流すと共に他端をワイヤ17の他端に接続するダイオード群22と、を備え、ワイヤ17の抵抗分の温度変化によって生じる出力電流制限値の変化が少なくなるように、ダイオード群21、22の一端間の電位差に基づいて所定値を補正する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、過電流検出回路および半導体装置に係り、特に、出力電流が流れる配線の抵抗成分における電位の変化に応じて過電流を検出する技術に係る。

【背景技術】

【0002】

一般に、自動車等の車両では、車体(シャーシ)がGND電位のため、ランプやモータ等の負荷がロウサイド側に設置される場合が多い。そこで、負荷がスイッチとGND間に接続されるハイサイドスイッチが多用され、低オン抵抗、低コストのために、スイッチ素子として、ソースフォロワ動作するNチャネル型MOSFETが多用される。

【0003】

このようなハイサイドスイッチ等にあっては、負荷に過電流が流れると、スイッチ素子であるNチャネル型MOSFETや配線材料が損傷を受ける虞がある。そこで、過電流を検出して、Nチャネル型MOSFETに流れる電流を制御する過電流検出回路を設けるのが一般的である。このような過電流検出回路において、Nチャネル型MOSFETを流れる電流の検出素子として半導体装置を構成する配線(ワイヤ)を用いる技術が、特許文献1、2、3において開示されている。

【0004】

なお、関連する技術として、特許文献4には、2つのダイオード間に発生する電圧差の温度係数が入力電流によって異なることを利用して、電圧差から温度を検出する温度検出回路が記載されている。

【0005】

【特許文献1】特開平11−121683号公報

【特許文献2】特開2004−80087号公報

【特許文献3】特開平6−216307号公報

【特許文献4】特開2000−213992号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

車載用の半導体装置は、その使用環境からかなり広い温度範囲において使用される。したがって、広い温度範囲に亘って要求される条件を満たす必要がある。ハイサイドスイッチもその例外ではなく、過電流の検出値も広い温度範囲に亘って変化が少ないことが求められる。ところで、電流の検出素子として用いられる配線における金属の電気抵抗率の温度係数は、常温において、約0.4%/℃である。例えば、銅(Cu)の温度係数は、0.00393/℃である。図6に銅のワイヤ抵抗の温度変化の例を示す。今、使用温度範囲を100℃とすると、配線の抵抗値は、使用温度範囲において約40%変化し、これに伴い過電流の検出値も約40%も変化してしまうことになる。

【0007】

このため、過電流検出回路において、広い温度範囲に亘って変動の少ない過電流検出を行うことができない虞があった。ところで、特許文献1には、「ボンディングワイヤ(配線)の抵抗の温度係数を考慮して、基準電圧回路に温度係数を持たせるように設計すれば、過電流の検出電流値の温度特性を補償することも可能である」との記載がなされている。しかしながら、具体的な温度特性の補償方法は何ら記載されていないため、車載用の過電流検出回路において簡単な回路構成によって精度の高い温度補償回路を設計することが困難であった。

【課題を解決するための手段】

【0008】

本発明者は、鋭意検討の結果、定電流を流した2組のダイオード群の電位差における温度係数が、金属の電気抵抗率の温度係数と同程度であることを見出した。そこで、2組のダイオード群の電位差に基づいて金属配線に流れる過電流の電流制限値を補正するように構成することで、温度特性に優れた過電流検出が行うことができると考え、本発明を創案するに至った。

【0009】

本発明の1つのアスペクトに係る過電流検出回路は、出力端子と、出力端子を介して負荷に出力電流を流すトランジスタと、トランジスタに接続され出力電流が流れる金属配線と、金属配線に流れる出力電流と金属配線の抵抗とによって金属配線の両端に生じる電位差を検出し、電位差が所定値より大きくなった場合に出力電流を制限するようにトランジスタを制御する制御回路と、を備え、制御回路は、第1および第2の電流源と、一端から第1の電流源によって第1の電流を順方向に流すと共に、他端を金属配線の一端に接続する第1のダイオード群と、一端から第2の電流源によって第2の電流を順方向に流すと共に、他端を金属配線の他端に接続する第2のダイオード群と、を備えると共に、配線の抵抗の温度変化によって生じる出力電流制限値の変化が少なくなるように、第1および第2のダイオード群の一端間の電位差に基づいて所定値を補正する構成とされる。

【発明の効果】

【0010】

本発明によれば、2組のダイオード群の電位差における温度係数が、金属の電気抵抗率の温度係数と同程度であることを用いて、出力電流制限値の変化が少なくなるように出力電流制限値の検出電圧が補正される。したがって、過電流検出回路において簡単な回路構成で精度の高い温度補償がなされる。

【発明を実施するための最良の形態】

【0011】

本発明の実施形態に係る過電流検出回路は、出力端子(図1のOUT)と、出力端子を介して負荷(図1の12)に出力電流(図1のIa)を流す出力トランジスタ(図1のNM0)と、出力トランジスタに接続され出力電流が流れる金属配線(図1の17)と、金属配線に流れる出力電流と金属配線の抵抗とによって金属配線の両端に生じる電位差を検出し、電位差が所定値より大きくなった場合に出力電流を制限するように出力トランジスタを制御する制御回路(図1の20)と、を備える。ここで、制御回路(図1の20)は、第1および第2の電流源(図1のI1、I2)と、一端から第1の電流源によって電流を順方向に流すと共に、他端を金属配線の一端に接続する第1のダイオード群(図1の21)と、一端から第2の電流源によって電流を順方向に流すと共に、他端を金属配線の他端に接続する第2のダイオード群(図1の22)と、を備え、金属配線の抵抗の温度変化によって生じる出力電流制限値の変化が少なくなるように、第1および第2のダイオード群の一端間の電位差に基づいて所定値を補正する構成とされる。

【0012】

また、第1のダイオード群は、アノードおよびカソードをそれぞれ共通に並列接続したX(Xは1以上の整数)個のダイオードを一組としてL(Lは1以上の整数)組を順方向に直列に接続すると共に、カソード端を金属配線の一端に接続し、第2のダイオード群は、アノードおよびカソードをそれぞれ共通に並列接続したY(Yは1以上の整数)個のダイオードを一組としてL組を順方向に直列に接続すると共に、カソード端を金属配線の他端に接続し、金属配線の他端の電位が金属配線の一端の電位よりも高く、第1および第2の電流源の電流値比をM:N(M、Nは正数)とする場合、M・Y/N/X>1を満たすように構成することが好ましい。

【0013】

さらに、制御回路は、第1のダイオード群のアノード端にソースを接続し、第1の電流源にドレインおよびゲートを接続する第1のMOSトランジスタ(図4のNM1)と、第2のダイオード群のアノード端にソースを接続し、第2の電流源にドレインを接続し、ゲートを第1のMOSトランジスタのゲートと接続する第2のMOSトランジスタ(図4のNM2)と、ゲートを第2のMOSトランジスタのドレインと接続し、ソースを金属配線の一端または他端に接続し、ドレインを出力トランジスタ(図4のNM0)の制御端に接続する第3のMOSトランジスタ(図4のNM3)と、を備え、第1、第2および第3のMOSトランジスタは、同一の導電型であって、第3のMOSトランジスタは、電位差が所定値より大きくなった場合に出力電流を制限するように出力トランジスタを制御するようにすることが好ましい。

【0014】

ここで、出力トランジスタは、ハイサイドスイッチまたはローサイドスイッチとして機能するNMOSトランジスタであってもよい。

【0015】

本発明の実施形態に係る半導体装置は、以上のような過電流検出回路を含む。この半導体装置において、第1および第2のダイオード群と金属配線とは、近接して配設されることが好ましい。また、金属配線は、銅、銀、金、アルミニウム、およびこれらの少なくとも一つを主成分とする合金のいずれかで構成されるボンディングワイヤであって、出力端子は、ボンディングワイヤが接続されるリードフレームとして構成されるようにしてもよい。

【0016】

以下、実施例に即し、図面を参照して詳しく説明する。

【実施例1】

【0017】

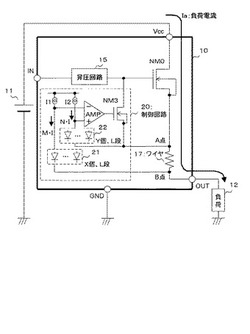

図1は、本発明の第1の実施例に係る半導体装置の回路図である。図1において、半導体装置10は、端子Vcc、IN、GND、OUT、NMOSトランジスタNM0、昇圧回路15、ワイヤ17、制御回路20、を備える。昇圧回路15は、端子INにオン信号が与えられると、昇圧電圧をNMOSトランジスタNM0のゲートに与える。ゲートに昇圧電圧が与えられたNMOSトランジスタNM0は、オンとなって、バッテリ11から供給される負荷電流(出力電流)Iaを、端子Vcc、NMOSトランジスタNM0のドレインおよびソース、さらにワイヤ17を介して端子OUTから出力して負荷12に供給する。

【0018】

制御回路20は、ダイオード群21、22、電流源I1、I2、増幅器AMP、NMOSトランジスタNM3を備える。ダイオード群21は、一端(アノード側)から電流源I1によって電流を順方向に流すと共に、他端(カソード側)をワイヤ17の一端(B点)に接続する。ダイオード群22は、一端(アノード側)から電流源I2によって電流を順方向に流すと共に、他端(カソード側)をワイヤ17の他端(A点)に接続する。ここで、電流源I1、I2における電流値は、負荷電流Iaの電流値に比べて無視できるほど小さいものとする。増幅器AMPは、反転入力端子(−)をダイオード群21の一端(アノード側)に接続し、非反転入力端子(+)をダイオード群22の一端(アノード側)に接続し、出力端子をNMOSトランジスタNM3のゲートに接続する。NMOSトランジスタNM3は、ドレインをNMOSトランジスタNM0のゲートに接続し、ソースをワイヤ17の他端(A点)、すなわちNMOSトランジスタNM0のソースに接続する。

【0019】

以上のような構成の半導体装置において、負荷電流Iaの値が通常の範囲内にある場合、ワイヤ17の両端(A点、B点)間の電位差は、小さく、ダイオード群22の一端(アノード側)すなわち増幅器AMPの非反転入力端子の電位がダイオード群21の一端(アノード側)すなわち増幅器AMPの反転入力端子の電位より低い。したがって、増幅器AMPの出力の電位が低下し、NMOSトランジスタNM3がオフとなって、NMOSトランジスタNM0の動作に影響を与えることがない。

【0020】

一方、負荷電流Iaが出力電流制限値を超えると、ワイヤ17の両端(A点、B点)間の電位差が所定値を超える。制御回路20は、この電位差が所定値より大きくなった場合に負荷電流Iaを制限するようにNMOSトランジスタNM0のゲートを制御する。すなわち、ダイオード群22の一端(アノード側)の電位がダイオード群21の一端(アノード側)の電位より高くなると、増幅器AMPの出力端子の電位が上昇する。この結果、NMOSトランジスタNM3のゲート・ソース間の電位差が大きくなって、NMOSトランジスタNM3のドレインの電位すなわちNMOSトランジスタNM0のゲートの電位が下り、NMOSトランジスタNM0を流れる負荷電流Iaが制限されるように動作する。

【0021】

次に、ダイオード群21、22によって、ワイヤ17の抵抗の温度変化によって生じる出力電流制限値の変化が補償される点について説明する。今、ダイオード群21は、アノードおよびカソードをそれぞれ共通に並列接続したX(Xは1以上の整数)個のダイオードを一組としてL(Lは1以上の整数)組を順方向に直列に接続した構成とする。また、ダイオード群22は、アノードおよびカソードをそれぞれ共通に並列接続したY(Yは1以上の整数)個のダイオードを一組としてL組を順方向に直列に接続した構成とする。さらに、電流源I1、I2における電流値比をM:N(M、Nは正数)とする。さらに、ワイヤ17の抵抗値をRとする。

【0022】

ここで、負荷電流Iaが出力電流制限値に一致する時、以下の式が成り立つ。

L・k/q・(T+273)・ln(M・I/X/Is)−L・k/q・(T+273)・ln(N・I/Y/Is)=Ia・R・{1+tc・(T−25)} −−−−−式(1)

ただし、kはボルツマン定数、qは電子運動エネルギー、Tは摂氏温度、Isはダイオードの飽和電流、tcはワイヤ17を構成する金属の温度係数である。

【0023】

式(1)から負荷電流Iaを求めると、以下の式のように表される。

Ia=L・k/q・(T+273)・ln(M・Y/N/X)/R/{1+tc・(T−25)} −−−−−式(2)

【0024】

式(2)において、Ia>0でなければならないため、M・Y/N/X>1を満たす必要がある。

【0025】

式(2)に対して、具体的な数値を当てはめ、負荷電流Iaの出力電流制限値の温度係数を求めると、図2に示すようになる。図2は、ワイヤ17を構成する金属が銅であって、ワイヤ17の抵抗値が1mΩ、温度を−40℃、25℃、125℃と変化させた場合の例である。図2(A)は、L=1、M/N=1、Y/X=2、図2(B)は、L=1、M/N=3、Y/X=2、図2(C)は、L=2、M/N=3、Y/X=2に設定している。図2(A)、(B)、(C)のいずれの場合であっても、温度が25℃〜125℃と変化した時の負荷電流Iaの出力電流制限値の温度係数は、−0.00041/℃である。すなわち、100℃変化した場合、出力電流制限値は、4%程度の変動に収まることが示される。

【0026】

図3(A)は、温度を変化させた時のダイオード群21、22の電位差ΔVFの変化を示す図である。図3(B)は、温度を変化させた時の検出電流(出力電流制限値)の変化を示す図である。ここでは、L=1、M/N=1とし、Y/Xを2〜30まで変化させている。ダイオード群21、22の電位差の温度係数が、図6に示した銅のワイヤの温度係数と近い値となって、図3(B)に示すように、出力電流制限値(検出電流)の温度変化が低く抑えられることが分かる。また、Y/Xを2〜30まで変えた場合、温度係数の小さい電流検出特性が、十数A〜90A程度まで調整可能であることが示される。なお、ここでは、L=1、M/N=1としたが、L、M/Nを変更することで、出力電流制限値に対し、さらに広範囲できめ細かい調整も可能である。

【0027】

なお、以上の説明では、端子OUTと接地間に負荷12が接続され、NMOSトランジスタNM0がハイサイドスイッチとして機能する例を示した。これに対し、端子OUTを接地すると共に、端子Vccとバッテリ11との間に負荷12を接続し、NMOSトランジスタNM0がローサイドスイッチとして機能するように構成することも可能である。

【実施例2】

【0028】

図4は、本発明の第2の実施例に係る過電流検出回路の回路図である。図4において、図1と同じ符号は同じものを表し、その説明を省略する。図4に示す過電流検出回路は、図1における増幅器AMPの替わりにNMOSトランジスタNM1、NM2からなるカレントミラーを制御回路20aに組み込んでいる。

【0029】

MOSトランジスタNM1は、ダイオード群21のアノード端にソースを接続し、電流源I1にドレインおよびゲートを接続する。また、MOSトランジスタNM2は、ダイオード群21のアノード端にソースを接続し、電流源I2にドレインを接続し、ゲートをMOSトランジスタNM1のゲートと接続する。MOSトランジスタNM3は、ゲートをMOSトランジスタNM2のドレインと接続し、ソースをワイヤ17の他端(A点)に接続し、ドレインをMOSトランジスタNM0のゲート(制御端)に接続する。なお、NMOSトランジスタNM1、NM2のサイズ比は、電流源I1、I2の電流比に一致するように構成されるものとする。

【0030】

以上のような構成の過電流検出回路において、負荷電流Iaの値が通常の範囲内にある場合、ワイヤ17の両端(A点、B点)間の電位差は、小さく、ダイオード群22の一端(アノード側)すなわちNMOSトランジスタNM2のソースの電位がダイオード群21の一端(アノード側)すなわちNMOSトランジスタNM1のソースの電位より低い。したがって、NMOSトランジスタNM2はオンとなって、NMOSトランジスタNM3のゲートの電位が低下する。このため、NMOSトランジスタNM3がオフとなって、NMOSトランジスタNM0の動作に影響を与えることがない。なお、NMOSトランジスタNM3は、オンとなったNMOSトランジスタNM2およびダイオード群22の電圧降下によってオンとはならないようにサイズが設定されるものとする。

【0031】

一方、負荷電流Iaが出力電流制限値を超えると、ワイヤ17の両端(A点、B点)間の電位差が所定値を超える。この場合、ダイオード群22の一端(アノード側)の電位がダイオード群21の一端(アノード側)の電位より高くなり、NMOSトランジスタNM2はオフとなる。したがって、電流源I2から流れ出る電流によってNMOSトランジスタNM3のゲートの電位が上昇する。この結果、NMOSトランジスタNM3のゲート・ソース間の電位差が大きくなって、NMOSトランジスタNM3のドレインの電位すなわちNMOSトランジスタNM0のゲートの電位が下り、NMOSトランジスタNM0を流れる負荷電流Iaが制限されるように動作する。

【0032】

以上のような過電流検出回路によれば、簡単な構成の回路によって過電流検出を行うことができると共に、出力電流制限値(検出電流)の温度変化が低く抑えられる。

【実施例3】

【0033】

図5は、本発明の第3の実施例に係る半導体装置の構造を表す図である。図5において、図1と同一の符号は同一物を表す。図5において、半導体装置は、IPDチップ30、端子Vcc、IN、GND、OUT、ワイヤ17、18a、18b、19を備える。また、IPDチップ30は、端子Vccが接続されるリードフレーム上に配設され、NMOSトランジスタNM0、昇圧回路15、制御回路20等を備える。

【0034】

昇圧回路15、制御回路20等の配置部は、端子IN、GNDとそれぞれワイヤ(ボンディングワイヤ)18a、18bによって接続され、NMOSトランジスタNM0と表面メタルで配線され(A点に相当)、端子OUTであるリードフレームとワイヤ(ボンディングワイヤ)19によって接続される。また、NMOSトランジスタNM0は、ドレインが端子Vcc(IPDチップ30のマウントされたリードフレーム)に接続され、ソースがワイヤ17によって端子OUTであるリードフレームと接続される。また、ゲートは図示されない配線によって制御回路20に配線される。

【0035】

ここでワイヤ17は、銅、銀、金、アルミニウム等の金属およびこれらの少なくとも一つを主成分とする合金で構成されるボンディングワイヤであることが好ましい。また、図示されないが、制御回路20中のダイオード群21、22とワイヤ17とは、ダイオード群21、22とワイヤ17との温度差が少なくなるように近接して配設されることが好ましい。

【0036】

以上のような構造の半導体装置によれば、ダイオード群21、22とワイヤ17との温度差が少なくなり、2組のダイオード群の電位差における温度係数が、ワイヤ17の電気抵抗率の温度係数と同程度であることを用いて、出力電流制限値の変化が少なくなるように出力電流制限値の検出電圧が補正される。

【0037】

このような半導体装置において、ボンディングワイヤ17の抵抗値Rのバラツキは、材質、径、長さのバラツキに起因するが、一例として3σ(σは標準偏差)で概算±5%程度となる。また、ダイオードの電位差ΔVFは、相対値でありばらつきが小さく、一例として3σで概算±3%程度となる。すなわち、抵抗値の精度、参照電圧値の精度とも高く電流検出の精度が良好である。

【0038】

また、電位差ΔVFの温度係数は、先に示したX、Yに関係なく、0.00336(/℃)であり、温度特性グラフは、先に示した図3(A)に示す通りになる。一方、ボンディングワイヤの抵抗値Rの温度係数(1℃あたりの増加率)は、材質で決まり、一例として銅(Cu)ワイヤの場合の温度係数は、0.00393(/℃)であり、温度特性グラフは、先の図6に示す通りである。また、銀、金、アルミニウムのそれぞれの抵抗温度係数は、0.0038(/℃)、0.0034(/℃)、0.0039(/℃)であって、銅の抵抗温度係数とほぼ同じで、電位差ΔVFの温度係数と近い。

【0039】

今、仮に、25℃〜125℃まで100℃上昇した場合に、ΔVFは、+33.6%、Cuワイヤの抵抗値は、+39.3%変化する。この変化に対し、温度補償の結果、Y/X=2において、25℃で電流検出値=17.8Aであった場合には、125℃では17.1A(0.959倍)となり、温度特性グラフは、先の図3(B)に示す通りになる。ここで、−0.00041(/℃)と小さい温度係数の電流検出特性が得られていることがわかる。さらに、25℃で1mΩの抵抗値をもつワイヤに対して、ダイオードの比(Y/X)を2〜30まで変えた場合も同様に、上記の通り温度係数の小さい電流検出特性が得られる。すなわち、十数A〜90A程度まで調節できていることがわかる。

【0040】

以上のような半導体装置は、車載用のハイサイドスイッチとして好適であり、過電流検出回路において精度の高い温度補償がなされる。

【0041】

以上本発明を上記実施例に即して説明したが、本発明は、上記実施例にのみ限定されるものではなく、本願特許請求の範囲の各請求項の発明の範囲内で当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【図面の簡単な説明】

【0042】

【図1】本発明の第1の実施例に係る半導体装置の回路図である。

【図2】負荷電流Iaの出力電流制限値の温度変化を示す表である。

【図3】温度を変化させた時の2組のダイオード群の電位差の変化および検出電流の変化を示す図である。

【図4】本発明の第2の実施例に係る過電流検出回路の回路図である。

【図5】本発明の第3の実施例に係る半導体装置の構造を表す図である。

【図6】銅のワイヤ抵抗の温度変化の例を示す図である。

【符号の説明】

【0043】

10 半導体装置

11 バッテリ

12 負荷

15 昇圧回路

17、18a、18b、19 ワイヤ

20、20a 制御回路

21、22 ダイオード群

30 IPDチップ

AMP 増幅器

I1、I2 電流源

Ia 負荷電流

GND、IN、OUT、Vcc 端子

MN0、NM1、NM2、MN3 NMOSトランジスタ

【技術分野】

【0001】

本発明は、過電流検出回路および半導体装置に係り、特に、出力電流が流れる配線の抵抗成分における電位の変化に応じて過電流を検出する技術に係る。

【背景技術】

【0002】

一般に、自動車等の車両では、車体(シャーシ)がGND電位のため、ランプやモータ等の負荷がロウサイド側に設置される場合が多い。そこで、負荷がスイッチとGND間に接続されるハイサイドスイッチが多用され、低オン抵抗、低コストのために、スイッチ素子として、ソースフォロワ動作するNチャネル型MOSFETが多用される。

【0003】

このようなハイサイドスイッチ等にあっては、負荷に過電流が流れると、スイッチ素子であるNチャネル型MOSFETや配線材料が損傷を受ける虞がある。そこで、過電流を検出して、Nチャネル型MOSFETに流れる電流を制御する過電流検出回路を設けるのが一般的である。このような過電流検出回路において、Nチャネル型MOSFETを流れる電流の検出素子として半導体装置を構成する配線(ワイヤ)を用いる技術が、特許文献1、2、3において開示されている。

【0004】

なお、関連する技術として、特許文献4には、2つのダイオード間に発生する電圧差の温度係数が入力電流によって異なることを利用して、電圧差から温度を検出する温度検出回路が記載されている。

【0005】

【特許文献1】特開平11−121683号公報

【特許文献2】特開2004−80087号公報

【特許文献3】特開平6−216307号公報

【特許文献4】特開2000−213992号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

車載用の半導体装置は、その使用環境からかなり広い温度範囲において使用される。したがって、広い温度範囲に亘って要求される条件を満たす必要がある。ハイサイドスイッチもその例外ではなく、過電流の検出値も広い温度範囲に亘って変化が少ないことが求められる。ところで、電流の検出素子として用いられる配線における金属の電気抵抗率の温度係数は、常温において、約0.4%/℃である。例えば、銅(Cu)の温度係数は、0.00393/℃である。図6に銅のワイヤ抵抗の温度変化の例を示す。今、使用温度範囲を100℃とすると、配線の抵抗値は、使用温度範囲において約40%変化し、これに伴い過電流の検出値も約40%も変化してしまうことになる。

【0007】

このため、過電流検出回路において、広い温度範囲に亘って変動の少ない過電流検出を行うことができない虞があった。ところで、特許文献1には、「ボンディングワイヤ(配線)の抵抗の温度係数を考慮して、基準電圧回路に温度係数を持たせるように設計すれば、過電流の検出電流値の温度特性を補償することも可能である」との記載がなされている。しかしながら、具体的な温度特性の補償方法は何ら記載されていないため、車載用の過電流検出回路において簡単な回路構成によって精度の高い温度補償回路を設計することが困難であった。

【課題を解決するための手段】

【0008】

本発明者は、鋭意検討の結果、定電流を流した2組のダイオード群の電位差における温度係数が、金属の電気抵抗率の温度係数と同程度であることを見出した。そこで、2組のダイオード群の電位差に基づいて金属配線に流れる過電流の電流制限値を補正するように構成することで、温度特性に優れた過電流検出が行うことができると考え、本発明を創案するに至った。

【0009】

本発明の1つのアスペクトに係る過電流検出回路は、出力端子と、出力端子を介して負荷に出力電流を流すトランジスタと、トランジスタに接続され出力電流が流れる金属配線と、金属配線に流れる出力電流と金属配線の抵抗とによって金属配線の両端に生じる電位差を検出し、電位差が所定値より大きくなった場合に出力電流を制限するようにトランジスタを制御する制御回路と、を備え、制御回路は、第1および第2の電流源と、一端から第1の電流源によって第1の電流を順方向に流すと共に、他端を金属配線の一端に接続する第1のダイオード群と、一端から第2の電流源によって第2の電流を順方向に流すと共に、他端を金属配線の他端に接続する第2のダイオード群と、を備えると共に、配線の抵抗の温度変化によって生じる出力電流制限値の変化が少なくなるように、第1および第2のダイオード群の一端間の電位差に基づいて所定値を補正する構成とされる。

【発明の効果】

【0010】

本発明によれば、2組のダイオード群の電位差における温度係数が、金属の電気抵抗率の温度係数と同程度であることを用いて、出力電流制限値の変化が少なくなるように出力電流制限値の検出電圧が補正される。したがって、過電流検出回路において簡単な回路構成で精度の高い温度補償がなされる。

【発明を実施するための最良の形態】

【0011】

本発明の実施形態に係る過電流検出回路は、出力端子(図1のOUT)と、出力端子を介して負荷(図1の12)に出力電流(図1のIa)を流す出力トランジスタ(図1のNM0)と、出力トランジスタに接続され出力電流が流れる金属配線(図1の17)と、金属配線に流れる出力電流と金属配線の抵抗とによって金属配線の両端に生じる電位差を検出し、電位差が所定値より大きくなった場合に出力電流を制限するように出力トランジスタを制御する制御回路(図1の20)と、を備える。ここで、制御回路(図1の20)は、第1および第2の電流源(図1のI1、I2)と、一端から第1の電流源によって電流を順方向に流すと共に、他端を金属配線の一端に接続する第1のダイオード群(図1の21)と、一端から第2の電流源によって電流を順方向に流すと共に、他端を金属配線の他端に接続する第2のダイオード群(図1の22)と、を備え、金属配線の抵抗の温度変化によって生じる出力電流制限値の変化が少なくなるように、第1および第2のダイオード群の一端間の電位差に基づいて所定値を補正する構成とされる。

【0012】

また、第1のダイオード群は、アノードおよびカソードをそれぞれ共通に並列接続したX(Xは1以上の整数)個のダイオードを一組としてL(Lは1以上の整数)組を順方向に直列に接続すると共に、カソード端を金属配線の一端に接続し、第2のダイオード群は、アノードおよびカソードをそれぞれ共通に並列接続したY(Yは1以上の整数)個のダイオードを一組としてL組を順方向に直列に接続すると共に、カソード端を金属配線の他端に接続し、金属配線の他端の電位が金属配線の一端の電位よりも高く、第1および第2の電流源の電流値比をM:N(M、Nは正数)とする場合、M・Y/N/X>1を満たすように構成することが好ましい。

【0013】

さらに、制御回路は、第1のダイオード群のアノード端にソースを接続し、第1の電流源にドレインおよびゲートを接続する第1のMOSトランジスタ(図4のNM1)と、第2のダイオード群のアノード端にソースを接続し、第2の電流源にドレインを接続し、ゲートを第1のMOSトランジスタのゲートと接続する第2のMOSトランジスタ(図4のNM2)と、ゲートを第2のMOSトランジスタのドレインと接続し、ソースを金属配線の一端または他端に接続し、ドレインを出力トランジスタ(図4のNM0)の制御端に接続する第3のMOSトランジスタ(図4のNM3)と、を備え、第1、第2および第3のMOSトランジスタは、同一の導電型であって、第3のMOSトランジスタは、電位差が所定値より大きくなった場合に出力電流を制限するように出力トランジスタを制御するようにすることが好ましい。

【0014】

ここで、出力トランジスタは、ハイサイドスイッチまたはローサイドスイッチとして機能するNMOSトランジスタであってもよい。

【0015】

本発明の実施形態に係る半導体装置は、以上のような過電流検出回路を含む。この半導体装置において、第1および第2のダイオード群と金属配線とは、近接して配設されることが好ましい。また、金属配線は、銅、銀、金、アルミニウム、およびこれらの少なくとも一つを主成分とする合金のいずれかで構成されるボンディングワイヤであって、出力端子は、ボンディングワイヤが接続されるリードフレームとして構成されるようにしてもよい。

【0016】

以下、実施例に即し、図面を参照して詳しく説明する。

【実施例1】

【0017】

図1は、本発明の第1の実施例に係る半導体装置の回路図である。図1において、半導体装置10は、端子Vcc、IN、GND、OUT、NMOSトランジスタNM0、昇圧回路15、ワイヤ17、制御回路20、を備える。昇圧回路15は、端子INにオン信号が与えられると、昇圧電圧をNMOSトランジスタNM0のゲートに与える。ゲートに昇圧電圧が与えられたNMOSトランジスタNM0は、オンとなって、バッテリ11から供給される負荷電流(出力電流)Iaを、端子Vcc、NMOSトランジスタNM0のドレインおよびソース、さらにワイヤ17を介して端子OUTから出力して負荷12に供給する。

【0018】

制御回路20は、ダイオード群21、22、電流源I1、I2、増幅器AMP、NMOSトランジスタNM3を備える。ダイオード群21は、一端(アノード側)から電流源I1によって電流を順方向に流すと共に、他端(カソード側)をワイヤ17の一端(B点)に接続する。ダイオード群22は、一端(アノード側)から電流源I2によって電流を順方向に流すと共に、他端(カソード側)をワイヤ17の他端(A点)に接続する。ここで、電流源I1、I2における電流値は、負荷電流Iaの電流値に比べて無視できるほど小さいものとする。増幅器AMPは、反転入力端子(−)をダイオード群21の一端(アノード側)に接続し、非反転入力端子(+)をダイオード群22の一端(アノード側)に接続し、出力端子をNMOSトランジスタNM3のゲートに接続する。NMOSトランジスタNM3は、ドレインをNMOSトランジスタNM0のゲートに接続し、ソースをワイヤ17の他端(A点)、すなわちNMOSトランジスタNM0のソースに接続する。

【0019】

以上のような構成の半導体装置において、負荷電流Iaの値が通常の範囲内にある場合、ワイヤ17の両端(A点、B点)間の電位差は、小さく、ダイオード群22の一端(アノード側)すなわち増幅器AMPの非反転入力端子の電位がダイオード群21の一端(アノード側)すなわち増幅器AMPの反転入力端子の電位より低い。したがって、増幅器AMPの出力の電位が低下し、NMOSトランジスタNM3がオフとなって、NMOSトランジスタNM0の動作に影響を与えることがない。

【0020】

一方、負荷電流Iaが出力電流制限値を超えると、ワイヤ17の両端(A点、B点)間の電位差が所定値を超える。制御回路20は、この電位差が所定値より大きくなった場合に負荷電流Iaを制限するようにNMOSトランジスタNM0のゲートを制御する。すなわち、ダイオード群22の一端(アノード側)の電位がダイオード群21の一端(アノード側)の電位より高くなると、増幅器AMPの出力端子の電位が上昇する。この結果、NMOSトランジスタNM3のゲート・ソース間の電位差が大きくなって、NMOSトランジスタNM3のドレインの電位すなわちNMOSトランジスタNM0のゲートの電位が下り、NMOSトランジスタNM0を流れる負荷電流Iaが制限されるように動作する。

【0021】

次に、ダイオード群21、22によって、ワイヤ17の抵抗の温度変化によって生じる出力電流制限値の変化が補償される点について説明する。今、ダイオード群21は、アノードおよびカソードをそれぞれ共通に並列接続したX(Xは1以上の整数)個のダイオードを一組としてL(Lは1以上の整数)組を順方向に直列に接続した構成とする。また、ダイオード群22は、アノードおよびカソードをそれぞれ共通に並列接続したY(Yは1以上の整数)個のダイオードを一組としてL組を順方向に直列に接続した構成とする。さらに、電流源I1、I2における電流値比をM:N(M、Nは正数)とする。さらに、ワイヤ17の抵抗値をRとする。

【0022】

ここで、負荷電流Iaが出力電流制限値に一致する時、以下の式が成り立つ。

L・k/q・(T+273)・ln(M・I/X/Is)−L・k/q・(T+273)・ln(N・I/Y/Is)=Ia・R・{1+tc・(T−25)} −−−−−式(1)

ただし、kはボルツマン定数、qは電子運動エネルギー、Tは摂氏温度、Isはダイオードの飽和電流、tcはワイヤ17を構成する金属の温度係数である。

【0023】

式(1)から負荷電流Iaを求めると、以下の式のように表される。

Ia=L・k/q・(T+273)・ln(M・Y/N/X)/R/{1+tc・(T−25)} −−−−−式(2)

【0024】

式(2)において、Ia>0でなければならないため、M・Y/N/X>1を満たす必要がある。

【0025】

式(2)に対して、具体的な数値を当てはめ、負荷電流Iaの出力電流制限値の温度係数を求めると、図2に示すようになる。図2は、ワイヤ17を構成する金属が銅であって、ワイヤ17の抵抗値が1mΩ、温度を−40℃、25℃、125℃と変化させた場合の例である。図2(A)は、L=1、M/N=1、Y/X=2、図2(B)は、L=1、M/N=3、Y/X=2、図2(C)は、L=2、M/N=3、Y/X=2に設定している。図2(A)、(B)、(C)のいずれの場合であっても、温度が25℃〜125℃と変化した時の負荷電流Iaの出力電流制限値の温度係数は、−0.00041/℃である。すなわち、100℃変化した場合、出力電流制限値は、4%程度の変動に収まることが示される。

【0026】

図3(A)は、温度を変化させた時のダイオード群21、22の電位差ΔVFの変化を示す図である。図3(B)は、温度を変化させた時の検出電流(出力電流制限値)の変化を示す図である。ここでは、L=1、M/N=1とし、Y/Xを2〜30まで変化させている。ダイオード群21、22の電位差の温度係数が、図6に示した銅のワイヤの温度係数と近い値となって、図3(B)に示すように、出力電流制限値(検出電流)の温度変化が低く抑えられることが分かる。また、Y/Xを2〜30まで変えた場合、温度係数の小さい電流検出特性が、十数A〜90A程度まで調整可能であることが示される。なお、ここでは、L=1、M/N=1としたが、L、M/Nを変更することで、出力電流制限値に対し、さらに広範囲できめ細かい調整も可能である。

【0027】

なお、以上の説明では、端子OUTと接地間に負荷12が接続され、NMOSトランジスタNM0がハイサイドスイッチとして機能する例を示した。これに対し、端子OUTを接地すると共に、端子Vccとバッテリ11との間に負荷12を接続し、NMOSトランジスタNM0がローサイドスイッチとして機能するように構成することも可能である。

【実施例2】

【0028】

図4は、本発明の第2の実施例に係る過電流検出回路の回路図である。図4において、図1と同じ符号は同じものを表し、その説明を省略する。図4に示す過電流検出回路は、図1における増幅器AMPの替わりにNMOSトランジスタNM1、NM2からなるカレントミラーを制御回路20aに組み込んでいる。

【0029】

MOSトランジスタNM1は、ダイオード群21のアノード端にソースを接続し、電流源I1にドレインおよびゲートを接続する。また、MOSトランジスタNM2は、ダイオード群21のアノード端にソースを接続し、電流源I2にドレインを接続し、ゲートをMOSトランジスタNM1のゲートと接続する。MOSトランジスタNM3は、ゲートをMOSトランジスタNM2のドレインと接続し、ソースをワイヤ17の他端(A点)に接続し、ドレインをMOSトランジスタNM0のゲート(制御端)に接続する。なお、NMOSトランジスタNM1、NM2のサイズ比は、電流源I1、I2の電流比に一致するように構成されるものとする。

【0030】

以上のような構成の過電流検出回路において、負荷電流Iaの値が通常の範囲内にある場合、ワイヤ17の両端(A点、B点)間の電位差は、小さく、ダイオード群22の一端(アノード側)すなわちNMOSトランジスタNM2のソースの電位がダイオード群21の一端(アノード側)すなわちNMOSトランジスタNM1のソースの電位より低い。したがって、NMOSトランジスタNM2はオンとなって、NMOSトランジスタNM3のゲートの電位が低下する。このため、NMOSトランジスタNM3がオフとなって、NMOSトランジスタNM0の動作に影響を与えることがない。なお、NMOSトランジスタNM3は、オンとなったNMOSトランジスタNM2およびダイオード群22の電圧降下によってオンとはならないようにサイズが設定されるものとする。

【0031】

一方、負荷電流Iaが出力電流制限値を超えると、ワイヤ17の両端(A点、B点)間の電位差が所定値を超える。この場合、ダイオード群22の一端(アノード側)の電位がダイオード群21の一端(アノード側)の電位より高くなり、NMOSトランジスタNM2はオフとなる。したがって、電流源I2から流れ出る電流によってNMOSトランジスタNM3のゲートの電位が上昇する。この結果、NMOSトランジスタNM3のゲート・ソース間の電位差が大きくなって、NMOSトランジスタNM3のドレインの電位すなわちNMOSトランジスタNM0のゲートの電位が下り、NMOSトランジスタNM0を流れる負荷電流Iaが制限されるように動作する。

【0032】

以上のような過電流検出回路によれば、簡単な構成の回路によって過電流検出を行うことができると共に、出力電流制限値(検出電流)の温度変化が低く抑えられる。

【実施例3】

【0033】

図5は、本発明の第3の実施例に係る半導体装置の構造を表す図である。図5において、図1と同一の符号は同一物を表す。図5において、半導体装置は、IPDチップ30、端子Vcc、IN、GND、OUT、ワイヤ17、18a、18b、19を備える。また、IPDチップ30は、端子Vccが接続されるリードフレーム上に配設され、NMOSトランジスタNM0、昇圧回路15、制御回路20等を備える。

【0034】

昇圧回路15、制御回路20等の配置部は、端子IN、GNDとそれぞれワイヤ(ボンディングワイヤ)18a、18bによって接続され、NMOSトランジスタNM0と表面メタルで配線され(A点に相当)、端子OUTであるリードフレームとワイヤ(ボンディングワイヤ)19によって接続される。また、NMOSトランジスタNM0は、ドレインが端子Vcc(IPDチップ30のマウントされたリードフレーム)に接続され、ソースがワイヤ17によって端子OUTであるリードフレームと接続される。また、ゲートは図示されない配線によって制御回路20に配線される。

【0035】

ここでワイヤ17は、銅、銀、金、アルミニウム等の金属およびこれらの少なくとも一つを主成分とする合金で構成されるボンディングワイヤであることが好ましい。また、図示されないが、制御回路20中のダイオード群21、22とワイヤ17とは、ダイオード群21、22とワイヤ17との温度差が少なくなるように近接して配設されることが好ましい。

【0036】

以上のような構造の半導体装置によれば、ダイオード群21、22とワイヤ17との温度差が少なくなり、2組のダイオード群の電位差における温度係数が、ワイヤ17の電気抵抗率の温度係数と同程度であることを用いて、出力電流制限値の変化が少なくなるように出力電流制限値の検出電圧が補正される。

【0037】

このような半導体装置において、ボンディングワイヤ17の抵抗値Rのバラツキは、材質、径、長さのバラツキに起因するが、一例として3σ(σは標準偏差)で概算±5%程度となる。また、ダイオードの電位差ΔVFは、相対値でありばらつきが小さく、一例として3σで概算±3%程度となる。すなわち、抵抗値の精度、参照電圧値の精度とも高く電流検出の精度が良好である。

【0038】

また、電位差ΔVFの温度係数は、先に示したX、Yに関係なく、0.00336(/℃)であり、温度特性グラフは、先に示した図3(A)に示す通りになる。一方、ボンディングワイヤの抵抗値Rの温度係数(1℃あたりの増加率)は、材質で決まり、一例として銅(Cu)ワイヤの場合の温度係数は、0.00393(/℃)であり、温度特性グラフは、先の図6に示す通りである。また、銀、金、アルミニウムのそれぞれの抵抗温度係数は、0.0038(/℃)、0.0034(/℃)、0.0039(/℃)であって、銅の抵抗温度係数とほぼ同じで、電位差ΔVFの温度係数と近い。

【0039】

今、仮に、25℃〜125℃まで100℃上昇した場合に、ΔVFは、+33.6%、Cuワイヤの抵抗値は、+39.3%変化する。この変化に対し、温度補償の結果、Y/X=2において、25℃で電流検出値=17.8Aであった場合には、125℃では17.1A(0.959倍)となり、温度特性グラフは、先の図3(B)に示す通りになる。ここで、−0.00041(/℃)と小さい温度係数の電流検出特性が得られていることがわかる。さらに、25℃で1mΩの抵抗値をもつワイヤに対して、ダイオードの比(Y/X)を2〜30まで変えた場合も同様に、上記の通り温度係数の小さい電流検出特性が得られる。すなわち、十数A〜90A程度まで調節できていることがわかる。

【0040】

以上のような半導体装置は、車載用のハイサイドスイッチとして好適であり、過電流検出回路において精度の高い温度補償がなされる。

【0041】

以上本発明を上記実施例に即して説明したが、本発明は、上記実施例にのみ限定されるものではなく、本願特許請求の範囲の各請求項の発明の範囲内で当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【図面の簡単な説明】

【0042】

【図1】本発明の第1の実施例に係る半導体装置の回路図である。

【図2】負荷電流Iaの出力電流制限値の温度変化を示す表である。

【図3】温度を変化させた時の2組のダイオード群の電位差の変化および検出電流の変化を示す図である。

【図4】本発明の第2の実施例に係る過電流検出回路の回路図である。

【図5】本発明の第3の実施例に係る半導体装置の構造を表す図である。

【図6】銅のワイヤ抵抗の温度変化の例を示す図である。

【符号の説明】

【0043】

10 半導体装置

11 バッテリ

12 負荷

15 昇圧回路

17、18a、18b、19 ワイヤ

20、20a 制御回路

21、22 ダイオード群

30 IPDチップ

AMP 増幅器

I1、I2 電流源

Ia 負荷電流

GND、IN、OUT、Vcc 端子

MN0、NM1、NM2、MN3 NMOSトランジスタ

【特許請求の範囲】

【請求項1】

出力端子と、

前記出力端子を介して負荷に出力電流を流す出力トランジスタと、

前記出力トランジスタに接続され前記出力電流が流れる金属配線と、

前記金属配線に流れる前記出力電流と前記金属配線の抵抗とによって前記金属配線の両端に生じる電位差を検出し、該電位差が所定値より大きくなった場合に前記出力電流を制限するように出力トランジスタを制御する制御回路と、

を備え、

前記制御回路は、

第1および第2の電流源と、

一端から前記第1の電流源によって電流を順方向に流すと共に、他端を前記金属配線の一端に接続する第1のダイオード群と、

一端から前記第2の電流源によって電流を順方向に流すと共に、他端を前記金属配線の他端に接続する第2のダイオード群と、

を備えると共に、前記金属配線の抵抗の温度変化によって生じる出力電流制限値の変化が少なくなるように、前記第1および第2のダイオード群の一端間の電位差に基づいて前記所定値を補正する構成とされることを特徴とする過電流検出回路。

【請求項2】

前記第1のダイオード群は、アノードおよびカソードをそれぞれ共通に並列接続したX(Xは1以上の整数)個のダイオードを一組としてL(Lは1以上の整数)組を順方向に直列に接続すると共に、カソード端を前記金属配線の一端に接続し、

前記第2のダイオード群は、アノードおよびカソードをそれぞれ共通に並列接続したY(Yは1以上の整数)個のダイオードを一組としてL組を順方向に直列に接続すると共に、カソード端を前記金属配線の他端に接続し、

前記金属配線の他端の電位が前記金属配線の一端の電位よりも高く、前記第1および第2の電流源の電流値比をM:N(M、Nは正数)とする場合、M・Y/N/X>1を満たすように構成することを特徴とする請求項1記載の過電流検出回路。

【請求項3】

前記制御回路は、

前記第1のダイオード群のアノード端にソースを接続し、前記第1の電流源にドレインおよびゲートを接続する第1のMOSトランジスタと、

前記第2のダイオード群のアノード端にソースを接続し、前記第2の電流源にドレインを接続し、ゲートを前記第1のMOSトランジスタのゲートと接続する第2のMOSトランジスタと、

ゲートを前記第2のMOSトランジスタのドレインと接続し、ソースを前記金属配線の一端または他端に接続し、ドレインを前記出力トランジスタの制御端に接続する第3のMOSトランジスタと、

を備え、

前記第1、第2および第3のMOSトランジスタは、同一の導電型であって、

前記第3のMOSトランジスタは、前記電位差が前記所定値より大きくなった場合に前記出力電流を制限するように前記出力トランジスタを制御することを特徴とする請求項2記載の過電流検出回路。

【請求項4】

前記出力トランジスタは、ハイサイドスイッチまたはローサイドスイッチとして機能するNMOSトランジスタであることを特徴とする請求項1または3記載の過電流検出回路。

【請求項5】

請求項1乃至4のいずれか一記載の過電流検出回路を含むことを特徴とする半導体装置。

【請求項6】

前記第1および第2のダイオード群と前記金属配線とは、近接して配設されることを特徴とする請求項5記載の半導体装置。

【請求項7】

前記金属配線は、銅、銀、金、アルミニウム、およびこれらの少なくとも一つを主成分とする合金のいずれかで構成されるボンディングワイヤであって、前記出力端子は、該ボンディングワイヤが接続されるリードフレームとして構成されることを特徴とする請求項5または6記載の半導体装置。

【請求項1】

出力端子と、

前記出力端子を介して負荷に出力電流を流す出力トランジスタと、

前記出力トランジスタに接続され前記出力電流が流れる金属配線と、

前記金属配線に流れる前記出力電流と前記金属配線の抵抗とによって前記金属配線の両端に生じる電位差を検出し、該電位差が所定値より大きくなった場合に前記出力電流を制限するように出力トランジスタを制御する制御回路と、

を備え、

前記制御回路は、

第1および第2の電流源と、

一端から前記第1の電流源によって電流を順方向に流すと共に、他端を前記金属配線の一端に接続する第1のダイオード群と、

一端から前記第2の電流源によって電流を順方向に流すと共に、他端を前記金属配線の他端に接続する第2のダイオード群と、

を備えると共に、前記金属配線の抵抗の温度変化によって生じる出力電流制限値の変化が少なくなるように、前記第1および第2のダイオード群の一端間の電位差に基づいて前記所定値を補正する構成とされることを特徴とする過電流検出回路。

【請求項2】

前記第1のダイオード群は、アノードおよびカソードをそれぞれ共通に並列接続したX(Xは1以上の整数)個のダイオードを一組としてL(Lは1以上の整数)組を順方向に直列に接続すると共に、カソード端を前記金属配線の一端に接続し、

前記第2のダイオード群は、アノードおよびカソードをそれぞれ共通に並列接続したY(Yは1以上の整数)個のダイオードを一組としてL組を順方向に直列に接続すると共に、カソード端を前記金属配線の他端に接続し、

前記金属配線の他端の電位が前記金属配線の一端の電位よりも高く、前記第1および第2の電流源の電流値比をM:N(M、Nは正数)とする場合、M・Y/N/X>1を満たすように構成することを特徴とする請求項1記載の過電流検出回路。

【請求項3】

前記制御回路は、

前記第1のダイオード群のアノード端にソースを接続し、前記第1の電流源にドレインおよびゲートを接続する第1のMOSトランジスタと、

前記第2のダイオード群のアノード端にソースを接続し、前記第2の電流源にドレインを接続し、ゲートを前記第1のMOSトランジスタのゲートと接続する第2のMOSトランジスタと、

ゲートを前記第2のMOSトランジスタのドレインと接続し、ソースを前記金属配線の一端または他端に接続し、ドレインを前記出力トランジスタの制御端に接続する第3のMOSトランジスタと、

を備え、

前記第1、第2および第3のMOSトランジスタは、同一の導電型であって、

前記第3のMOSトランジスタは、前記電位差が前記所定値より大きくなった場合に前記出力電流を制限するように前記出力トランジスタを制御することを特徴とする請求項2記載の過電流検出回路。

【請求項4】

前記出力トランジスタは、ハイサイドスイッチまたはローサイドスイッチとして機能するNMOSトランジスタであることを特徴とする請求項1または3記載の過電流検出回路。

【請求項5】

請求項1乃至4のいずれか一記載の過電流検出回路を含むことを特徴とする半導体装置。

【請求項6】

前記第1および第2のダイオード群と前記金属配線とは、近接して配設されることを特徴とする請求項5記載の半導体装置。

【請求項7】

前記金属配線は、銅、銀、金、アルミニウム、およびこれらの少なくとも一つを主成分とする合金のいずれかで構成されるボンディングワイヤであって、前記出力端子は、該ボンディングワイヤが接続されるリードフレームとして構成されることを特徴とする請求項5または6記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2008−236528(P2008−236528A)

【公開日】平成20年10月2日(2008.10.2)

【国際特許分類】

【出願番号】特願2007−74943(P2007−74943)

【出願日】平成19年3月22日(2007.3.22)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成20年10月2日(2008.10.2)

【国際特許分類】

【出願日】平成19年3月22日(2007.3.22)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]