選択可能な副精度に対して、低減された電力要求を有する浮動小数点プロセッサ

【課題】所定の精度を有する浮動小数点プロセッサにより、必要以上の電力を消費せずに浮動小数点演算を実行する。

【解決手段】1つ以上の浮動小数点数に関して、浮動小数点演算に対する副精度が選択される。副精度の選択は、1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらす。さもなければ1つ以上の過剰ビットを記憶または処理するために使用される、浮動小数点プロセッサ中の1つ以上のコンポーネントから、電力を取り除くことができ、浮動小数点演算は、1つ以上のコンポーネントから電力を取り除いた状態で実行される。

【解決手段】1つ以上の浮動小数点数に関して、浮動小数点演算に対する副精度が選択される。副精度の選択は、1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらす。さもなければ1つ以上の過剰ビットを記憶または処理するために使用される、浮動小数点プロセッサ中の1つ以上のコンポーネントから、電力を取り除くことができ、浮動小数点演算は、1つ以上のコンポーネントから電力を取り除いた状態で実行される。

【発明の詳細な説明】

【背景】

【0001】

浮動小数点プロセッサは、例えば、乗算や、除算や、三角関数や、指数関数のような、ある数学的演算を高速で実行する、専門の計算ユニットである。それゆえに、強力な計算システムは、メインプロセッサの一部分として、またはコプロセッサとして、浮動小数点プロセッサを組み込んでいることが多い。ある数の浮動小数点の表現は、一般に、符号部と、指数と、仮数とを含んでいる。浮動小数点数の値を見つけるために、基数(一般にコンピュータにおいては2)の指数乗を仮数に掛ける。符号は、結果として生じる値に適用される。

【0002】

浮動小数点プロセッサの精度は、仮数を表現するために使用されるビット数により規定される。仮数におけるビットが増えるほど、精度はより高くなる。浮動小数点プロセッサの精度は一般的に、特定のアプリケーションに左右される。例えば、(一般に最近のコンピュータにより採用される)ANSI/IEEE−754規格は、1ビットの符号と、8ビットの指数と、23ビットの仮数とを有する、32ビットの単フォーマットを指定する。仮数の23の小数部ビットだけが、32ビットのエンコーディングで記憶され、2進小数点のすぐ左側に、整数ビットが示される。IEEE−754はまた、1ビットの符号と、11ビットの指数と、53ビットの仮数とを有する、64ビットの倍フォーマットを指定する。単一エンコーディングに類似して、仮数の52の小数部ビットだけが、64ビットのエンコーディングで記憶され、2進小数点のすぐ左側に整数ビットが示される。より高い精度は、より高い正確さをもたらすが、一般に、電力消費の増加をもたらす。

【0003】

浮動小数点プロセッサは、一般に、単フォーマット、または、単フォーマットおよび倍フォーマットの両方、のいずれかにより提供された精度に制限されるため、浮動小数点算術演算の実行は、計算の非能率を必然的に伴うことがある。いくつかのアプリケーションは、これらのタイプの精度を必要とするかもしれないが、他のアプリケーションは、必要としないかもしれない。例えば、いくつかのグラフィックアプリケーションは、16ビットの仮数を必要とするだけであるかもしれない。これらのグラフィックアプリケーションに対して、16ビットの精度を超える何らかの正確さは、不必要な電力消費をもたらす傾向がある。少し挙げてみただけでも、ワイヤレス電話機や、パーソナルデジタルアシスタント(PDA)や、ラップトップや、ゲームコンソールや、ページャーや、カメラなどがある、電力の発生に限りがあるバッテリー駆動のデバイスにおいて、これは、特に問題である。アプリケーションが常に、ある低減された精度を必要とすることが知られている場合、その低減された精度に対して、浮動小数点プロセッサを設計および構築できる。しかしながら、汎用目的のプロセッサに対して、例えば、3Dグラフィックを発生させるような、あるアプリケーションに対しては、低減された精度が受け入れられるかもしれないが、例えば、全地球測位システム(GPS)機能を実現するような、他のアプリケーションに対しては、より高い精度が必要とされるかもしれないということが、共通の状況である。したがって、浮動小数点フォーマットの、低減された精度すなわち副精度が選択可能である浮動小数点プロセッサに対する技術的必要性がある。電力管理技術を用いて、浮動小数点プロセッサが、選択された精度をサポートするために必要以上の電力を確実に消費しないようにすることもできる。

【概要】

【0004】

精度フォーマットを有する浮動小数点プロセッサにより、浮動小数点演算を実行する方法の観点を開示する。方法は、1つ以上の浮動小数点数に関して、浮動小数点演算に対する副精度を選択することを含み、副精度の選択は、1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらす。方法は、さもなければ1つ以上の過剰ビットを記憶または処理するために使用される、浮動小数点プロセッサ中の1つ以上のコンポーネントから電力を取り除くことと、1つ以上のコンポーネントから電力を取り除いた状態で、浮動小数点演算を実行することとをさらに含む。

【0005】

精度フォーマットを有する浮動小数点プロセッサの1つの観点を開示する。浮動小数点プロセッサは、1つ以上の浮動小数点数に関して、浮動小数点演算に対する副精度を選択するように構成された浮動小数点制御装置を含み、副精度の選択は、1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらし、浮動小数点制御装置は、さもなければ1つ以上の過剰ビットを記憶または処理するために使用される、浮動小数点プロセッサ中の1つ以上のコンポーネントから電力を取り除くようにさらに構成されている。浮動小数点プロセッサは、浮動小数点演算を実行するように構成された浮動小数点演算器をさらに含む。

【0006】

精度フォーマットを有する浮動小数点プロセッサの別の観点を開示する。浮動小数点プロセッサは、複数の浮動小数点数を記憶するように構成された複数の記憶素子を有する浮動小数点レジスタと、浮動小数点レジスタ中に記憶された浮動小数点数のうちの1つ以上に関して浮動小数点演算を実行するように構成された浮動小数点演算器とを含む。浮動小数点プロセッサは、浮動小数点数のうちの1つ以上に関して、浮動小数点演算に対する副精度を選択するように構成された浮動小数点制御装置をさらに含み、副精度の選択は、浮動小数点数のうちの1つ以上のそれぞれに対して、1つ以上の過剰ビットをもたらし、1つ以上の過剰ビットは、浮動小数点レジスタの記憶素子のうちの1つ以上の中に記憶されており、浮動小数点制御装置は、1つ以上の過剰ビットに対する記憶素子から電力を取り除くようにさらに構成されている。

【0007】

精度フォーマットを有する浮動小数点プロセッサのさらなる観点を開示する。浮動小数点プロセッサは、複数の浮動小数点数を記憶するように構成された浮動小数点レジスタと、浮動小数点レジスタ中に記憶された浮動小数点数のうちの1つ以上に関して、浮動小数点演算を実行するように構成されたロジックを有する浮動小数点演算器とを含む。浮動小数点プロセッサは、浮動小数点数のうちの1つ以上に関して、浮動小数点演算に対する副精度を選択するように構成された浮動小数点制御装置をさらに含み、副精度の選択は、浮動小数点数のうちの1つ以上のそれぞれに対して、1つ以上の過剰ビットをもたらし、浮動小数点制御装置は、さもなければ1つ以上の過剰ビットを処理するために使用される、ロジックの一部から電力を取り除くようにさらに構成されている。

【0008】

浮動小数点プロセッサの、および浮動小数点演算を実行する方法の、他の実施形態は、浮動小数点プロセッサの、および浮動小数点演算を実行する方法の、さまざまな実施形態を実例として示し、記述している以下の詳細な説明から、当業者に容易に明らかになることを理解すべきである。理解されるように、浮動小数点プロセッサの、および浮動小数点演算を実行する方法の、他のおよび異なる実施形態が可能であり、これらの実施形態を記述するために使用される記述は、多くの点において修正できる。したがって、図面および詳細な説明は、本質的に例示であると考えるべきであり、限定的であると考えるべきでない。

【図面の簡単な説明】

【0009】

【図1】図1は、選択可能な副精度を有する浮動小数点プロセッサの例を図示する機能ブロック図である。

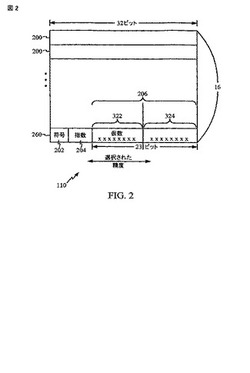

【図2】図2は、選択可能な副精度を有する浮動小数点プロセッサ中で使用される、浮動小数点レジスタの例のグラフィカルな説明図である。

【図3A】図3Aは、選択可能な副精度を有する浮動小数点プロセッサを使用して実行される、浮動小数点加算の例を図示する概念図である。

【図3B】図3Bは、選択可能な副精度を有する浮動小数点プロセッサを使用して実行される、浮動小数点乗算の例を図示する概念図である。

【詳細な説明】

【0010】

添付図面に関連して以下で示される詳細な説明は、本開示のさまざまな実施形態を記述するように向けられているが、本開示を実施する実施形態だけを表すように向けられていない。詳細な説明は、本開示の完全な理解を可能にするために、特定の詳細を含んでいる。しかしながら、これらの特定の詳細なしで本開示を実施できることが、当業者により理解されるだろう。いくつかの例において、本開示の概念をより明瞭に図示するために、よく知られている構造およびコンポーネントが、ブロック図の形態で示されている。

【0011】

浮動小数点プロセッサの少なくとも1つの実施形態において、1つ以上の浮動小数点演算に対する精度は、指定のフォーマットの精度から低減されてもよい。さらに、電力管理技術を用いて、浮動小数点プロセッサが、選択された副精度をサポートするために必要以上の電力を確実に消費しないようにすることもできる。数学的演算を実行するために浮動小数点プロセッサに提供される命令は、プログラム可能な制御フィールドを含んでいる。制御フィールドは、浮動小数点フォーマットの副精度を選択し、電力消費を管理するために使用される。特定の演算に対して必要とされる浮動小数点フォーマットの副精度を選択することにより、結果として、選択された副精度をサポートするための浮動小数点プロセッサの電力消費を低減させ、より高い効率だけでなく、かなりの電力節減を達成することができる。

【0012】

図1は、選択可能な副精度を有する浮動小数点プロセッサ(FPP)の例を図示する機能ブロック図である。浮動小数点プロセッサ100は、浮動小数点レジスタファイル(FPR)110と、浮動小数点制御装置(CTL)130と、浮動小数点数学的演算器(FPO)140とを含んでいる。浮動小数点プロセッサ100は、メインプロセッサの一部分や、コプロセッサや、あるいは、バスまたは他のチャネルを通してメインプロセッサに接続された別個のエンティティとして実現してもよい。

【0013】

浮動小数点レジスタファイル110は、何らかの適切な記憶媒体である。図1中で示した実施形態において、浮動小数点レジスタファイル110は、いくつかのアドレス可能レジスタ位置115−1(REG1)、115−2(REG2)、...115−N(REG N)を含み、それぞれは、浮動小数点演算に対するオペランドを記憶するように構成されている。オペランドは、例えば、メモリからのデータおよび/または以前の浮動小数点演算の結果を含んでいてもよい。浮動小数点プロセッサに提供される命令を使用して、メインメモリに、およびメインメモリから、オペランドを移動できる。

【0014】

図2は、図1に関して記述した、選択可能な副精度を有する浮動小数点プロセッサ100中で使用される、浮動小数点レジスタファイル110に対するデータ構造の例を概略的に図示する。図2中で図示した実施形態において、浮動小数点レジスタファイル110は、16個のアドレス可能レジスタ位置を含み、それぞれのレジスタ位置は、便宜上、図2中の参照数字200により参照されている。各レジスタ位置200は、IEEE−754の32ビット単フォーマットで、32ビットのバイナリの浮動小数点数を記憶するように構成されている。特に、各レジスタ位置200は、1ビットの符号202と、8ビットの指数204と、24ビットの小数部206とを含む。しかしながら、浮動小数点プロセッサ100の他の実施形態は、IEEE32ビット単フォーマットとは異なってフォーマットされている(限定されないが、IEEE64ビット倍フォーマットを含む)浮動小数点レジスタ110を含んでいてもよく、および/または異なる数のレジスタ位置を含んでいてもよいことを当然理解すべきである。

【0015】

図1を再度参照すると、浮動小数点制御装置130は、制御信号133を使用して、浮動小数点演算の副精度を選択するために使用される。制御レジスタ(CRG)137には、例えば、1つ以上の命令の制御フィールド中で送信される副精度選択ビットがロードされてもよい。後に、より詳細に記述する方法において、浮動小数点制御装置130により副精度選択ビットを使用して、オペランドの精度を低減させてもよい。副精度選択ビットを使用して、浮動小数点プロセッサ100の一部の電源を切ってもよい。一例として、副精度選択ビットを使用して、選択された副精度に対して必要とされないビットに対する浮動小数点レジスタ素子から電力を取り除いてもよい。選択された副精度が低減されるとき、副精度選択ビットを使用して、使用されない浮動小数点演算器FPO140中のロジックから電力を取り除いてもよい。一連のスイッチを使用して、浮動小数点演算器140中の浮動小数点レジスタ素子およびロジックから電力を取り除いてもよく、それらに対して電力を加えてもよい。浮動小数点レジスタ110および浮動小数点演算器140に対して内部または外部にあってもよいスイッチは、電界効果トランジスタまたは他の何らかのタイプのスイッチであってもよい。

【0016】

浮動小数点演算器140は、浮動小数点演算を実行するように構成された1つ以上のコンポーネントを含んでいてもよい。これらのコンポーネントは、浮動小数点の加算および減算命令を実行するように構成された浮動小数点加算器(ADD)142や、浮動小数点乗算命令を実行するように構成された浮動小数点乗算器(MUL)144のような計算ユニットを含んでいてもよいが、それらに限定されない。図1中で見られるように、浮動小数点演算器140中の計算ユニットADD142およびMUL144のそれぞれは、互いに結合されており、そして、計算ユニットの間だけでなく、各計算ユニットと浮動小数点レジスタファイル110との間でも、オペランドが転送されることを可能にする方法で、浮動小数点レジスタファイル110に結合されている。浮動小数点演算器は、図示したような個々の接続134、135、136、137、138、および139を通して浮動小数点レジスタに結合されていてもよく、バスまたは他の何らかの適切な結合を介して結合されていてもよい。浮動小数点プロセッサ100の少なくとも1つの実施形態において、計算ユニット(ADD142およびMUL144)のうちのいずれか1つの出力は、他の何らかの計算ユニットの入力であってもよい。浮動小数点レジスタファイル110は、中間結果だけでなく、浮動小数点演算器140からの出力である結果を記憶するために使用してもよい。

【0017】

加算器142は、浮動小数点フォーマットで標準算術演算を実行するように構成された、通常の浮動小数点加算器であってもよい。乗算器144は、浮動小数点乗算を実行するように構成された、通常の浮動小数点乗算器であってもよい。乗算器144は、一例として、ブースアルゴリズムまたは修正されたブースアルゴリズムにより実現してもよく、部分積を発生させる部分積発生ロジックと、部分積を累計する多数のキャリー保存加算器とを含んでいてもよい。

【0018】

簡単にするために、加算器142と乗算器144だけを図1中で示しているが、技術的に既知であり、他のタイプの浮動小数点数学的演算を実行するように構成されている、(示していない)他の計算ユニットを、浮動小数点演算器140が含んでいてもよい。これらの計算ユニットは、浮動小数点の除算命令を実行するように構成された浮動小数点除算器や、浮動小数点の平方根を開く命令を実行するように構成された浮動小数点平方根開器や、浮動小数点の指数命令を実行するように構成された浮動小数点指数演算器や、対数関数を計算する命令を実行するように構成された浮動小数点対数演算器や、三角関数を計算する命令を実行するように構成された浮動小数点三角演算器を含んでいてもよいが、これらに限定されない。

【0019】

浮動小数点プロセッサ100の異なる実施形態は、上でリスト表示した計算ユニットのうちの、1つだけを、またはいくつかを、またはすべてを含んでいてもよい。例えば、加算器142および乗算器144は、それぞれ、入力オペランドを整列させるアライナーや、結果を標準フォーマットにシフトするノーマライザや、指定の丸めモードに基づいて、結果を丸めるラウンダのような、1つ以上のよく知られている通常のサブユニットを含んでいてもよい。ビットインバータや、マルチプレクサや、カウンタや、組み合わせロジック回路のような、よく知られている回路素子が、さらに、加算器142および乗算器144中に含まれている。

【0020】

図1中で図示したように、浮動小数点演算器140は、浮動小数点レジスタファイル110に結合されており、それにより、要求された浮動小数点演算の各命令に対して、関連した計算ユニット、すなわち、加算器142または乗算器144は、レジスタ位置REG1、...、REG Nのうちの1つ以上の中に記憶された1つ以上のオペランドを、浮動小数点レジスタファイル110から受け取ることができる。

【0021】

浮動小数点レジスタファイル110からオペランドを受け取り次第、浮動小数点演算器140中の1つ以上の計算ユニットは、浮動小数点制御装置130により選択された副精度で、受け取られたオペランドに関して、要求された浮動小数点演算の命令を実行してもよい。図1中で示したように、出力は、記憶のために浮動小数点レジスタ110に返送されてもよい。

【0022】

浮動小数点プロセッサ100の1つの実施形態において、ソフトウェアの選択可能なモードを使用して、プログラム制御の下で、浮動小数点演算の精度を低減させてもよく、または、上で説明したように、浮動小数点プロセッサ100に提供される命令は、副精度選択ビットを含んでいる、プログラム可能な制御フィールドを含んでいてもよい。副精度選択ビットは、制御レジスタ137に書き込まれ、副精度選択ビットは次に、浮動小数点演算の間に、各オペランドに対する仮数のビット長を制御する。代わりに、副精度選択ビットは、例えば、図1中で示した、モニタスクリーン/キーボードまたはマウス150を含むが、これらに限定されない何らかの適切なユーザインターフェースから、直接に制御レジスタ137に書き込まれてもよい。浮動小数点プロセッサ100の別の実施形態において、副精度選択ビットは、メインプロセッサ、またはそのオペレーティングシステムから、直接に制御レジスタ137に書き込まれてもよい。浮動小数点制御装置130中で示されている制御レジスタ137は、別のエンティティに組み込まれた、または、複数のエンティティにわたって分散された、独立型のエンティティとして、どこかの場所に存在していてもよい。

【0023】

副精度選択ビットを使用して、浮動小数点演算の精度を低減させてもよい。これは、さまざまな方法で達成できる。1つの実施形態において、副精度選択ビットにより指定された精度を満たすことが要求されない小数部の過剰ビットに対する浮動小数点レジスタ素子から、浮動小数点制御装置130により、電力が取り除かれてもよい。一例として、浮動小数点レジスタファイル中のそれぞれの位置が、23ビットの小数部を含み、そして、浮動小数点演算に対して必要とされる副精度が10ビットである場合、小数部のうちの9個の上位ビットだけが必要とされ、隠れた、または整数ビットが、10番目になる。残りの14個の小数部ビットに対する浮動小数点レジスタ素子から、電力を取り除くことができる。1つ以上の命令に対する副精度が、16ビットに増加される場合、仮数の15個のMSBが必要とされる。後者のケースにおいて、小数部の8個の下位ビット(LSB)に対する浮動小数点レジスタ素子から、電力を取り除くことができる。

【0024】

さらに、過剰の仮数ビットに対応する、浮動小数点演算器140中のロジックは、電力を必要としない。したがって、選択された副精度の結果として、使用されずにとどまっている、浮動小数点演算器140中のロジックに対する電力を取り除くことにより、電力節減を達成できる。

【0025】

図3Aは、浮動小数点演算器中のロジックに対して電力が選択的に加えられている状態での、浮動小数点の加算の例を図示する概念図である。特に、図3Aは、2つの入力浮動小数点数302と304による浮動小数点の加算を概念的に図示する。浮動小数点数302と304は、それぞれ、選択された副精度により特徴付けられ、ともに加算される。簡単にするために、2つの数302と304は、すでに整列しており、それにより、シフトする必要がないと仮定する。フル精度モードにおける浮動小数点の加算は、図3A中で参照される、参照数字3101、3102、...、310i、...、310nによる連続のステージを通して実行される。標準の規則にしたがうと、浮動小数点レジスタは、最も右側のLSBから最も左側のMSBまでの範囲にわたる、各数を構成するビットを順番に記憶する。図3Aにわたって、右から左に移動する、それぞれの連続するステージのうちの1つは、前のステージに含まれるビットと比較して、増加した有効桁数を有するビットを含む。

【0026】

図3A中で図示した例において、選択された副精度は、ライン305により表されている。ライン305の右側に対する各ステージを実現するために使用されるロジックから、電力を取り除くことができる。最後に電源を切られたステージ310iからの桁上がりCは、強制的にゼロにされる。電力は、ライン305の左側に対する各ステージを実現するために使用されるロジックに対してのみ供給される。図3Aにおいて、浮動小数点演算器のアクティブなステージに対して提供される、電力供給されたビットは、参照数字322を使用して、Xとして示されており、一方、電力が取り除かれたステージに対して提供される、電力供給されないビットは、参照数字324を使用して、円として示されている。

【0027】

図3Bは、浮動小数点演算器中のロジックに対して電力が選択的に加えられている状態での、浮動小数点の乗算の例を図示する概念図である。浮動小数点の乗算は、図1中で示した、参照数字144による浮動小数点乗算器MULにおいて実行される。乗算器において、相当な量のロジックは、電源を切ることができ、かなりの電力の節減を提供する。図3B中で図示したバイナリ乗算は、基本的に、シフトされた浮動小数点数の一連の加算である。図示した実施形態において、バイナリ乗算は、桁送りおよび加算技術を使用して、kビットの被乗数402とkビットの乗数404との間で実行される。桁送りおよび加算技術は、ブースアルゴリズムの、または修正されたブースアルゴリズムの乗算器に取って代えてもよい。

【0028】

浮動小数点の加算のケースと同様に、浮動小数点乗算は、410−1、...、410−mとして図3B中で図示される、一連のステージにおいて実行される。簡単にするために、ブースアルゴリズムが使用されると仮定すると、1つの部分積が、乗数404中のすべてのビットに対して発生され、部分積420−iが、対応するステージ410−iの間に発生される。乗数の値が0である場合は、その対応する部分積は0だけで構成され、ビットの値が1である場合は、その対応する部分積は、被乗数のコピーである。演算が次のステージに移行した後、各部分積420−iは、それが関係付けられる乗数ビットの関数として、左にシフトされる。各部分積は、このように、シフトされた数としてとらえることができる。乗数中のビット0に関係付けられた部分積は、左にシフトされたゼロのビットであり、ビット1に関係付けられた部分積は、左にシフトされた1のビットである。部分積すなわちシフトされた浮動小数点数420−iは、ともに加算されて、乗算に対する出力値430を発生させる。

【0029】

図3B中で図示した実施形態において、制御装置130による所望の低減精度の選択が、ライン405により示されている。図3Aに関して記述した、浮動小数点の加算のケースと同様に、ライン405の右側に対するステージを実現するために使用されるロジックから、電力を取り除くことができる。選択された副精度をサポートするために実際に必要とされるステージ、すなわち、ライン405の左側に対するステージに対して、電力が加えられるだけである。図3Bにおいて、電源投入されたロジックに提供されるビットは、Xとして示されており、一方、電源を切られたステージに提供されるビットは、円として示されている。

【0030】

図3Bから分かるように、1番目の部分積420−1に対して、参照数字402を使用して示した、N個のビットに対するロジックは、電力供給されない。2番目の部分積に対して、N−1個のビットに対するロジックは、電力供給されない、などである。m番目の部分積すなわちシフトされた浮動小数点数420−mに対して、参照数字414を使用して示した(N−m+1)個のビットに対するロジックは、電力供給されない。残りのステージの精度に悪影響を及ぼさないように、ビット数Nが選ばれる。

【0031】

上述した浮動小数点乗算から結果として生じる出力値は、互いに乗算されている2つの入力値402と404との幅(すなわち、ビット数)の合計に等しい幅を有する。出力値430は、選択された副精度に切り捨てられてもよく、すなわち、選択された精度よりも低い出力値430のビットのいくつかを切り捨てて、選択された精度により特徴付けられた、切り捨てられた出力の数を発生させてもよい。代わりに、出力値430を選択された精度に四捨五入してもよい。いずれのケースにおいても、選択された精度よりも下位の出力ビットは、電力供給されなくてもよい。

【0032】

汎用目的のプロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラム可能ゲートアレイ(FPGA)または他のプログラム可能ロジックコンポーネント、ディスクリートゲートまたはトランジスタロジック、ディスクリートハードウェアコンポーネント、あるいはここで記述した機能を実行するために設計された、これらの任意の組み合わせ、の一部分である浮動小数点プロセッサ中で、ここで開示した実施形態に関して記述した、さまざまな実例となるロジックユニット、ブロック、モジュール、回路、素子、および/またはコンポーネントを実現または実行してもよい。汎用目的のプロセッサはマイクロプロセッサでもよいが、代わりに、プロセッサは任意の従来のプロセッサ、制御装置、マイクロ制御装置、または状態遷移機械であってもよい。プロセッサは、例えば、DSPとマイクロプロセッサとの組み合わせや、複数のマイクロプロセッサや、DSPコアに関連した1つ以上のマイクロプロセッサや、または他の任意のこのような構成のような、計算コンポーネントの組み合わせとして実現してもよい。

【0033】

ここで開示した実施形態に関して記述した方法またはアルゴリズムのステップを、ハードウェア中で直接、プロセッサにより実行されるソフトウェアモジュール中で、またはその2つの組み合わせ中で具体化してもよい。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバルディスク、CD−ROM,または技術的に知られている他の任意の形態の記憶媒体中に存在してもよい。プロセッサが記憶媒体から情報を読み取ることができ、記憶媒体に情報を書き込むことができるように、記憶媒体はプロセッサに結合されている。代わりに、記憶媒体はプロセッサと一体化されていてもよい。

【0034】

いかなる当業者であっても本開示を作成または使用できるように、開示した実施形態の記述をこれまでに提供している。これらの実施形態に対してさまざまな修正が当業者に容易に明らかとなり、本開示の精神または範囲から逸脱することなく、ここで規定した一般的な原理を他の実施形態に適用してもよい。したがって、本開示は、ここで示した実施形態に限定されるように意図されていないが、特許請求の範囲に矛盾しない全範囲に一致すべきであり、ここで単一の要素に対する参照は、特にそう述べられていない限り、“1つおよびただ1つ”を意味するように意図されておらず、むしろ“1つまたはそれ以上”を意味するように意図されている。当業者に知られている、または後に知られるようになる、本開示全体を通して記述したさまざまな実施形態の要素に対するすべての構造的および機能的な均等物は、明白に、参照によりここに組み込まれ、特許請求の範囲により包含されるように意図されている。さらに、ここで開示したものは、そのような開示が特許請求の範囲中で明示的に記載されているかどうかにかかわらず、公開専用のものであるように意図されていない。要素がフレーズ“手段”を使用して明白に記載されていない限り、または方法の請求項のケースにおいて、要素がフレーズ“ステップ”を使用して記載されていない限り、請求項の要素は、合衆国法典第35部112条第6項のもとで解釈すべきでない。

【背景】

【0001】

浮動小数点プロセッサは、例えば、乗算や、除算や、三角関数や、指数関数のような、ある数学的演算を高速で実行する、専門の計算ユニットである。それゆえに、強力な計算システムは、メインプロセッサの一部分として、またはコプロセッサとして、浮動小数点プロセッサを組み込んでいることが多い。ある数の浮動小数点の表現は、一般に、符号部と、指数と、仮数とを含んでいる。浮動小数点数の値を見つけるために、基数(一般にコンピュータにおいては2)の指数乗を仮数に掛ける。符号は、結果として生じる値に適用される。

【0002】

浮動小数点プロセッサの精度は、仮数を表現するために使用されるビット数により規定される。仮数におけるビットが増えるほど、精度はより高くなる。浮動小数点プロセッサの精度は一般的に、特定のアプリケーションに左右される。例えば、(一般に最近のコンピュータにより採用される)ANSI/IEEE−754規格は、1ビットの符号と、8ビットの指数と、23ビットの仮数とを有する、32ビットの単フォーマットを指定する。仮数の23の小数部ビットだけが、32ビットのエンコーディングで記憶され、2進小数点のすぐ左側に、整数ビットが示される。IEEE−754はまた、1ビットの符号と、11ビットの指数と、53ビットの仮数とを有する、64ビットの倍フォーマットを指定する。単一エンコーディングに類似して、仮数の52の小数部ビットだけが、64ビットのエンコーディングで記憶され、2進小数点のすぐ左側に整数ビットが示される。より高い精度は、より高い正確さをもたらすが、一般に、電力消費の増加をもたらす。

【0003】

浮動小数点プロセッサは、一般に、単フォーマット、または、単フォーマットおよび倍フォーマットの両方、のいずれかにより提供された精度に制限されるため、浮動小数点算術演算の実行は、計算の非能率を必然的に伴うことがある。いくつかのアプリケーションは、これらのタイプの精度を必要とするかもしれないが、他のアプリケーションは、必要としないかもしれない。例えば、いくつかのグラフィックアプリケーションは、16ビットの仮数を必要とするだけであるかもしれない。これらのグラフィックアプリケーションに対して、16ビットの精度を超える何らかの正確さは、不必要な電力消費をもたらす傾向がある。少し挙げてみただけでも、ワイヤレス電話機や、パーソナルデジタルアシスタント(PDA)や、ラップトップや、ゲームコンソールや、ページャーや、カメラなどがある、電力の発生に限りがあるバッテリー駆動のデバイスにおいて、これは、特に問題である。アプリケーションが常に、ある低減された精度を必要とすることが知られている場合、その低減された精度に対して、浮動小数点プロセッサを設計および構築できる。しかしながら、汎用目的のプロセッサに対して、例えば、3Dグラフィックを発生させるような、あるアプリケーションに対しては、低減された精度が受け入れられるかもしれないが、例えば、全地球測位システム(GPS)機能を実現するような、他のアプリケーションに対しては、より高い精度が必要とされるかもしれないということが、共通の状況である。したがって、浮動小数点フォーマットの、低減された精度すなわち副精度が選択可能である浮動小数点プロセッサに対する技術的必要性がある。電力管理技術を用いて、浮動小数点プロセッサが、選択された精度をサポートするために必要以上の電力を確実に消費しないようにすることもできる。

【概要】

【0004】

精度フォーマットを有する浮動小数点プロセッサにより、浮動小数点演算を実行する方法の観点を開示する。方法は、1つ以上の浮動小数点数に関して、浮動小数点演算に対する副精度を選択することを含み、副精度の選択は、1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらす。方法は、さもなければ1つ以上の過剰ビットを記憶または処理するために使用される、浮動小数点プロセッサ中の1つ以上のコンポーネントから電力を取り除くことと、1つ以上のコンポーネントから電力を取り除いた状態で、浮動小数点演算を実行することとをさらに含む。

【0005】

精度フォーマットを有する浮動小数点プロセッサの1つの観点を開示する。浮動小数点プロセッサは、1つ以上の浮動小数点数に関して、浮動小数点演算に対する副精度を選択するように構成された浮動小数点制御装置を含み、副精度の選択は、1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらし、浮動小数点制御装置は、さもなければ1つ以上の過剰ビットを記憶または処理するために使用される、浮動小数点プロセッサ中の1つ以上のコンポーネントから電力を取り除くようにさらに構成されている。浮動小数点プロセッサは、浮動小数点演算を実行するように構成された浮動小数点演算器をさらに含む。

【0006】

精度フォーマットを有する浮動小数点プロセッサの別の観点を開示する。浮動小数点プロセッサは、複数の浮動小数点数を記憶するように構成された複数の記憶素子を有する浮動小数点レジスタと、浮動小数点レジスタ中に記憶された浮動小数点数のうちの1つ以上に関して浮動小数点演算を実行するように構成された浮動小数点演算器とを含む。浮動小数点プロセッサは、浮動小数点数のうちの1つ以上に関して、浮動小数点演算に対する副精度を選択するように構成された浮動小数点制御装置をさらに含み、副精度の選択は、浮動小数点数のうちの1つ以上のそれぞれに対して、1つ以上の過剰ビットをもたらし、1つ以上の過剰ビットは、浮動小数点レジスタの記憶素子のうちの1つ以上の中に記憶されており、浮動小数点制御装置は、1つ以上の過剰ビットに対する記憶素子から電力を取り除くようにさらに構成されている。

【0007】

精度フォーマットを有する浮動小数点プロセッサのさらなる観点を開示する。浮動小数点プロセッサは、複数の浮動小数点数を記憶するように構成された浮動小数点レジスタと、浮動小数点レジスタ中に記憶された浮動小数点数のうちの1つ以上に関して、浮動小数点演算を実行するように構成されたロジックを有する浮動小数点演算器とを含む。浮動小数点プロセッサは、浮動小数点数のうちの1つ以上に関して、浮動小数点演算に対する副精度を選択するように構成された浮動小数点制御装置をさらに含み、副精度の選択は、浮動小数点数のうちの1つ以上のそれぞれに対して、1つ以上の過剰ビットをもたらし、浮動小数点制御装置は、さもなければ1つ以上の過剰ビットを処理するために使用される、ロジックの一部から電力を取り除くようにさらに構成されている。

【0008】

浮動小数点プロセッサの、および浮動小数点演算を実行する方法の、他の実施形態は、浮動小数点プロセッサの、および浮動小数点演算を実行する方法の、さまざまな実施形態を実例として示し、記述している以下の詳細な説明から、当業者に容易に明らかになることを理解すべきである。理解されるように、浮動小数点プロセッサの、および浮動小数点演算を実行する方法の、他のおよび異なる実施形態が可能であり、これらの実施形態を記述するために使用される記述は、多くの点において修正できる。したがって、図面および詳細な説明は、本質的に例示であると考えるべきであり、限定的であると考えるべきでない。

【図面の簡単な説明】

【0009】

【図1】図1は、選択可能な副精度を有する浮動小数点プロセッサの例を図示する機能ブロック図である。

【図2】図2は、選択可能な副精度を有する浮動小数点プロセッサ中で使用される、浮動小数点レジスタの例のグラフィカルな説明図である。

【図3A】図3Aは、選択可能な副精度を有する浮動小数点プロセッサを使用して実行される、浮動小数点加算の例を図示する概念図である。

【図3B】図3Bは、選択可能な副精度を有する浮動小数点プロセッサを使用して実行される、浮動小数点乗算の例を図示する概念図である。

【詳細な説明】

【0010】

添付図面に関連して以下で示される詳細な説明は、本開示のさまざまな実施形態を記述するように向けられているが、本開示を実施する実施形態だけを表すように向けられていない。詳細な説明は、本開示の完全な理解を可能にするために、特定の詳細を含んでいる。しかしながら、これらの特定の詳細なしで本開示を実施できることが、当業者により理解されるだろう。いくつかの例において、本開示の概念をより明瞭に図示するために、よく知られている構造およびコンポーネントが、ブロック図の形態で示されている。

【0011】

浮動小数点プロセッサの少なくとも1つの実施形態において、1つ以上の浮動小数点演算に対する精度は、指定のフォーマットの精度から低減されてもよい。さらに、電力管理技術を用いて、浮動小数点プロセッサが、選択された副精度をサポートするために必要以上の電力を確実に消費しないようにすることもできる。数学的演算を実行するために浮動小数点プロセッサに提供される命令は、プログラム可能な制御フィールドを含んでいる。制御フィールドは、浮動小数点フォーマットの副精度を選択し、電力消費を管理するために使用される。特定の演算に対して必要とされる浮動小数点フォーマットの副精度を選択することにより、結果として、選択された副精度をサポートするための浮動小数点プロセッサの電力消費を低減させ、より高い効率だけでなく、かなりの電力節減を達成することができる。

【0012】

図1は、選択可能な副精度を有する浮動小数点プロセッサ(FPP)の例を図示する機能ブロック図である。浮動小数点プロセッサ100は、浮動小数点レジスタファイル(FPR)110と、浮動小数点制御装置(CTL)130と、浮動小数点数学的演算器(FPO)140とを含んでいる。浮動小数点プロセッサ100は、メインプロセッサの一部分や、コプロセッサや、あるいは、バスまたは他のチャネルを通してメインプロセッサに接続された別個のエンティティとして実現してもよい。

【0013】

浮動小数点レジスタファイル110は、何らかの適切な記憶媒体である。図1中で示した実施形態において、浮動小数点レジスタファイル110は、いくつかのアドレス可能レジスタ位置115−1(REG1)、115−2(REG2)、...115−N(REG N)を含み、それぞれは、浮動小数点演算に対するオペランドを記憶するように構成されている。オペランドは、例えば、メモリからのデータおよび/または以前の浮動小数点演算の結果を含んでいてもよい。浮動小数点プロセッサに提供される命令を使用して、メインメモリに、およびメインメモリから、オペランドを移動できる。

【0014】

図2は、図1に関して記述した、選択可能な副精度を有する浮動小数点プロセッサ100中で使用される、浮動小数点レジスタファイル110に対するデータ構造の例を概略的に図示する。図2中で図示した実施形態において、浮動小数点レジスタファイル110は、16個のアドレス可能レジスタ位置を含み、それぞれのレジスタ位置は、便宜上、図2中の参照数字200により参照されている。各レジスタ位置200は、IEEE−754の32ビット単フォーマットで、32ビットのバイナリの浮動小数点数を記憶するように構成されている。特に、各レジスタ位置200は、1ビットの符号202と、8ビットの指数204と、24ビットの小数部206とを含む。しかしながら、浮動小数点プロセッサ100の他の実施形態は、IEEE32ビット単フォーマットとは異なってフォーマットされている(限定されないが、IEEE64ビット倍フォーマットを含む)浮動小数点レジスタ110を含んでいてもよく、および/または異なる数のレジスタ位置を含んでいてもよいことを当然理解すべきである。

【0015】

図1を再度参照すると、浮動小数点制御装置130は、制御信号133を使用して、浮動小数点演算の副精度を選択するために使用される。制御レジスタ(CRG)137には、例えば、1つ以上の命令の制御フィールド中で送信される副精度選択ビットがロードされてもよい。後に、より詳細に記述する方法において、浮動小数点制御装置130により副精度選択ビットを使用して、オペランドの精度を低減させてもよい。副精度選択ビットを使用して、浮動小数点プロセッサ100の一部の電源を切ってもよい。一例として、副精度選択ビットを使用して、選択された副精度に対して必要とされないビットに対する浮動小数点レジスタ素子から電力を取り除いてもよい。選択された副精度が低減されるとき、副精度選択ビットを使用して、使用されない浮動小数点演算器FPO140中のロジックから電力を取り除いてもよい。一連のスイッチを使用して、浮動小数点演算器140中の浮動小数点レジスタ素子およびロジックから電力を取り除いてもよく、それらに対して電力を加えてもよい。浮動小数点レジスタ110および浮動小数点演算器140に対して内部または外部にあってもよいスイッチは、電界効果トランジスタまたは他の何らかのタイプのスイッチであってもよい。

【0016】

浮動小数点演算器140は、浮動小数点演算を実行するように構成された1つ以上のコンポーネントを含んでいてもよい。これらのコンポーネントは、浮動小数点の加算および減算命令を実行するように構成された浮動小数点加算器(ADD)142や、浮動小数点乗算命令を実行するように構成された浮動小数点乗算器(MUL)144のような計算ユニットを含んでいてもよいが、それらに限定されない。図1中で見られるように、浮動小数点演算器140中の計算ユニットADD142およびMUL144のそれぞれは、互いに結合されており、そして、計算ユニットの間だけでなく、各計算ユニットと浮動小数点レジスタファイル110との間でも、オペランドが転送されることを可能にする方法で、浮動小数点レジスタファイル110に結合されている。浮動小数点演算器は、図示したような個々の接続134、135、136、137、138、および139を通して浮動小数点レジスタに結合されていてもよく、バスまたは他の何らかの適切な結合を介して結合されていてもよい。浮動小数点プロセッサ100の少なくとも1つの実施形態において、計算ユニット(ADD142およびMUL144)のうちのいずれか1つの出力は、他の何らかの計算ユニットの入力であってもよい。浮動小数点レジスタファイル110は、中間結果だけでなく、浮動小数点演算器140からの出力である結果を記憶するために使用してもよい。

【0017】

加算器142は、浮動小数点フォーマットで標準算術演算を実行するように構成された、通常の浮動小数点加算器であってもよい。乗算器144は、浮動小数点乗算を実行するように構成された、通常の浮動小数点乗算器であってもよい。乗算器144は、一例として、ブースアルゴリズムまたは修正されたブースアルゴリズムにより実現してもよく、部分積を発生させる部分積発生ロジックと、部分積を累計する多数のキャリー保存加算器とを含んでいてもよい。

【0018】

簡単にするために、加算器142と乗算器144だけを図1中で示しているが、技術的に既知であり、他のタイプの浮動小数点数学的演算を実行するように構成されている、(示していない)他の計算ユニットを、浮動小数点演算器140が含んでいてもよい。これらの計算ユニットは、浮動小数点の除算命令を実行するように構成された浮動小数点除算器や、浮動小数点の平方根を開く命令を実行するように構成された浮動小数点平方根開器や、浮動小数点の指数命令を実行するように構成された浮動小数点指数演算器や、対数関数を計算する命令を実行するように構成された浮動小数点対数演算器や、三角関数を計算する命令を実行するように構成された浮動小数点三角演算器を含んでいてもよいが、これらに限定されない。

【0019】

浮動小数点プロセッサ100の異なる実施形態は、上でリスト表示した計算ユニットのうちの、1つだけを、またはいくつかを、またはすべてを含んでいてもよい。例えば、加算器142および乗算器144は、それぞれ、入力オペランドを整列させるアライナーや、結果を標準フォーマットにシフトするノーマライザや、指定の丸めモードに基づいて、結果を丸めるラウンダのような、1つ以上のよく知られている通常のサブユニットを含んでいてもよい。ビットインバータや、マルチプレクサや、カウンタや、組み合わせロジック回路のような、よく知られている回路素子が、さらに、加算器142および乗算器144中に含まれている。

【0020】

図1中で図示したように、浮動小数点演算器140は、浮動小数点レジスタファイル110に結合されており、それにより、要求された浮動小数点演算の各命令に対して、関連した計算ユニット、すなわち、加算器142または乗算器144は、レジスタ位置REG1、...、REG Nのうちの1つ以上の中に記憶された1つ以上のオペランドを、浮動小数点レジスタファイル110から受け取ることができる。

【0021】

浮動小数点レジスタファイル110からオペランドを受け取り次第、浮動小数点演算器140中の1つ以上の計算ユニットは、浮動小数点制御装置130により選択された副精度で、受け取られたオペランドに関して、要求された浮動小数点演算の命令を実行してもよい。図1中で示したように、出力は、記憶のために浮動小数点レジスタ110に返送されてもよい。

【0022】

浮動小数点プロセッサ100の1つの実施形態において、ソフトウェアの選択可能なモードを使用して、プログラム制御の下で、浮動小数点演算の精度を低減させてもよく、または、上で説明したように、浮動小数点プロセッサ100に提供される命令は、副精度選択ビットを含んでいる、プログラム可能な制御フィールドを含んでいてもよい。副精度選択ビットは、制御レジスタ137に書き込まれ、副精度選択ビットは次に、浮動小数点演算の間に、各オペランドに対する仮数のビット長を制御する。代わりに、副精度選択ビットは、例えば、図1中で示した、モニタスクリーン/キーボードまたはマウス150を含むが、これらに限定されない何らかの適切なユーザインターフェースから、直接に制御レジスタ137に書き込まれてもよい。浮動小数点プロセッサ100の別の実施形態において、副精度選択ビットは、メインプロセッサ、またはそのオペレーティングシステムから、直接に制御レジスタ137に書き込まれてもよい。浮動小数点制御装置130中で示されている制御レジスタ137は、別のエンティティに組み込まれた、または、複数のエンティティにわたって分散された、独立型のエンティティとして、どこかの場所に存在していてもよい。

【0023】

副精度選択ビットを使用して、浮動小数点演算の精度を低減させてもよい。これは、さまざまな方法で達成できる。1つの実施形態において、副精度選択ビットにより指定された精度を満たすことが要求されない小数部の過剰ビットに対する浮動小数点レジスタ素子から、浮動小数点制御装置130により、電力が取り除かれてもよい。一例として、浮動小数点レジスタファイル中のそれぞれの位置が、23ビットの小数部を含み、そして、浮動小数点演算に対して必要とされる副精度が10ビットである場合、小数部のうちの9個の上位ビットだけが必要とされ、隠れた、または整数ビットが、10番目になる。残りの14個の小数部ビットに対する浮動小数点レジスタ素子から、電力を取り除くことができる。1つ以上の命令に対する副精度が、16ビットに増加される場合、仮数の15個のMSBが必要とされる。後者のケースにおいて、小数部の8個の下位ビット(LSB)に対する浮動小数点レジスタ素子から、電力を取り除くことができる。

【0024】

さらに、過剰の仮数ビットに対応する、浮動小数点演算器140中のロジックは、電力を必要としない。したがって、選択された副精度の結果として、使用されずにとどまっている、浮動小数点演算器140中のロジックに対する電力を取り除くことにより、電力節減を達成できる。

【0025】

図3Aは、浮動小数点演算器中のロジックに対して電力が選択的に加えられている状態での、浮動小数点の加算の例を図示する概念図である。特に、図3Aは、2つの入力浮動小数点数302と304による浮動小数点の加算を概念的に図示する。浮動小数点数302と304は、それぞれ、選択された副精度により特徴付けられ、ともに加算される。簡単にするために、2つの数302と304は、すでに整列しており、それにより、シフトする必要がないと仮定する。フル精度モードにおける浮動小数点の加算は、図3A中で参照される、参照数字3101、3102、...、310i、...、310nによる連続のステージを通して実行される。標準の規則にしたがうと、浮動小数点レジスタは、最も右側のLSBから最も左側のMSBまでの範囲にわたる、各数を構成するビットを順番に記憶する。図3Aにわたって、右から左に移動する、それぞれの連続するステージのうちの1つは、前のステージに含まれるビットと比較して、増加した有効桁数を有するビットを含む。

【0026】

図3A中で図示した例において、選択された副精度は、ライン305により表されている。ライン305の右側に対する各ステージを実現するために使用されるロジックから、電力を取り除くことができる。最後に電源を切られたステージ310iからの桁上がりCは、強制的にゼロにされる。電力は、ライン305の左側に対する各ステージを実現するために使用されるロジックに対してのみ供給される。図3Aにおいて、浮動小数点演算器のアクティブなステージに対して提供される、電力供給されたビットは、参照数字322を使用して、Xとして示されており、一方、電力が取り除かれたステージに対して提供される、電力供給されないビットは、参照数字324を使用して、円として示されている。

【0027】

図3Bは、浮動小数点演算器中のロジックに対して電力が選択的に加えられている状態での、浮動小数点の乗算の例を図示する概念図である。浮動小数点の乗算は、図1中で示した、参照数字144による浮動小数点乗算器MULにおいて実行される。乗算器において、相当な量のロジックは、電源を切ることができ、かなりの電力の節減を提供する。図3B中で図示したバイナリ乗算は、基本的に、シフトされた浮動小数点数の一連の加算である。図示した実施形態において、バイナリ乗算は、桁送りおよび加算技術を使用して、kビットの被乗数402とkビットの乗数404との間で実行される。桁送りおよび加算技術は、ブースアルゴリズムの、または修正されたブースアルゴリズムの乗算器に取って代えてもよい。

【0028】

浮動小数点の加算のケースと同様に、浮動小数点乗算は、410−1、...、410−mとして図3B中で図示される、一連のステージにおいて実行される。簡単にするために、ブースアルゴリズムが使用されると仮定すると、1つの部分積が、乗数404中のすべてのビットに対して発生され、部分積420−iが、対応するステージ410−iの間に発生される。乗数の値が0である場合は、その対応する部分積は0だけで構成され、ビットの値が1である場合は、その対応する部分積は、被乗数のコピーである。演算が次のステージに移行した後、各部分積420−iは、それが関係付けられる乗数ビットの関数として、左にシフトされる。各部分積は、このように、シフトされた数としてとらえることができる。乗数中のビット0に関係付けられた部分積は、左にシフトされたゼロのビットであり、ビット1に関係付けられた部分積は、左にシフトされた1のビットである。部分積すなわちシフトされた浮動小数点数420−iは、ともに加算されて、乗算に対する出力値430を発生させる。

【0029】

図3B中で図示した実施形態において、制御装置130による所望の低減精度の選択が、ライン405により示されている。図3Aに関して記述した、浮動小数点の加算のケースと同様に、ライン405の右側に対するステージを実現するために使用されるロジックから、電力を取り除くことができる。選択された副精度をサポートするために実際に必要とされるステージ、すなわち、ライン405の左側に対するステージに対して、電力が加えられるだけである。図3Bにおいて、電源投入されたロジックに提供されるビットは、Xとして示されており、一方、電源を切られたステージに提供されるビットは、円として示されている。

【0030】

図3Bから分かるように、1番目の部分積420−1に対して、参照数字402を使用して示した、N個のビットに対するロジックは、電力供給されない。2番目の部分積に対して、N−1個のビットに対するロジックは、電力供給されない、などである。m番目の部分積すなわちシフトされた浮動小数点数420−mに対して、参照数字414を使用して示した(N−m+1)個のビットに対するロジックは、電力供給されない。残りのステージの精度に悪影響を及ぼさないように、ビット数Nが選ばれる。

【0031】

上述した浮動小数点乗算から結果として生じる出力値は、互いに乗算されている2つの入力値402と404との幅(すなわち、ビット数)の合計に等しい幅を有する。出力値430は、選択された副精度に切り捨てられてもよく、すなわち、選択された精度よりも低い出力値430のビットのいくつかを切り捨てて、選択された精度により特徴付けられた、切り捨てられた出力の数を発生させてもよい。代わりに、出力値430を選択された精度に四捨五入してもよい。いずれのケースにおいても、選択された精度よりも下位の出力ビットは、電力供給されなくてもよい。

【0032】

汎用目的のプロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラム可能ゲートアレイ(FPGA)または他のプログラム可能ロジックコンポーネント、ディスクリートゲートまたはトランジスタロジック、ディスクリートハードウェアコンポーネント、あるいはここで記述した機能を実行するために設計された、これらの任意の組み合わせ、の一部分である浮動小数点プロセッサ中で、ここで開示した実施形態に関して記述した、さまざまな実例となるロジックユニット、ブロック、モジュール、回路、素子、および/またはコンポーネントを実現または実行してもよい。汎用目的のプロセッサはマイクロプロセッサでもよいが、代わりに、プロセッサは任意の従来のプロセッサ、制御装置、マイクロ制御装置、または状態遷移機械であってもよい。プロセッサは、例えば、DSPとマイクロプロセッサとの組み合わせや、複数のマイクロプロセッサや、DSPコアに関連した1つ以上のマイクロプロセッサや、または他の任意のこのような構成のような、計算コンポーネントの組み合わせとして実現してもよい。

【0033】

ここで開示した実施形態に関して記述した方法またはアルゴリズムのステップを、ハードウェア中で直接、プロセッサにより実行されるソフトウェアモジュール中で、またはその2つの組み合わせ中で具体化してもよい。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバルディスク、CD−ROM,または技術的に知られている他の任意の形態の記憶媒体中に存在してもよい。プロセッサが記憶媒体から情報を読み取ることができ、記憶媒体に情報を書き込むことができるように、記憶媒体はプロセッサに結合されている。代わりに、記憶媒体はプロセッサと一体化されていてもよい。

【0034】

いかなる当業者であっても本開示を作成または使用できるように、開示した実施形態の記述をこれまでに提供している。これらの実施形態に対してさまざまな修正が当業者に容易に明らかとなり、本開示の精神または範囲から逸脱することなく、ここで規定した一般的な原理を他の実施形態に適用してもよい。したがって、本開示は、ここで示した実施形態に限定されるように意図されていないが、特許請求の範囲に矛盾しない全範囲に一致すべきであり、ここで単一の要素に対する参照は、特にそう述べられていない限り、“1つおよびただ1つ”を意味するように意図されておらず、むしろ“1つまたはそれ以上”を意味するように意図されている。当業者に知られている、または後に知られるようになる、本開示全体を通して記述したさまざまな実施形態の要素に対するすべての構造的および機能的な均等物は、明白に、参照によりここに組み込まれ、特許請求の範囲により包含されるように意図されている。さらに、ここで開示したものは、そのような開示が特許請求の範囲中で明示的に記載されているかどうかにかかわらず、公開専用のものであるように意図されていない。要素がフレーズ“手段”を使用して明白に記載されていない限り、または方法の請求項のケースにおいて、要素がフレーズ“ステップ”を使用して記載されていない限り、請求項の要素は、合衆国法典第35部112条第6項のもとで解釈すべきでない。

【特許請求の範囲】

【請求項1】

最大精度を有する浮動小数点プロセッサにより、浮動小数点演算を実行する方法において、

1つ以上の浮動小数点数に関する前記浮動小数点演算に対して、前記最大精度よりも小さい副精度を選択し、前記副精度の選択は、前記1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらすことと、

さもなければ前記1つ以上の過剰ビットを記憶または処理するために使用される、前記浮動小数点プロセッサ中の1つ以上のコンポーネントから電力を取り除くことと、

前記1つ以上のコンポーネントから電力を取り除いた状態で、前記浮動小数点演算を実行することとを含む方法。

【請求項2】

複数の記憶素子を有する浮動小数点レジスタを使用することをさらに含み、前記1つ以上の過剰ビットは、前記記憶素子のうちの1つ以上の中に記憶されており、

前記電力が取り除かれる1つ以上のコンポーネントは、前記1つ以上の過剰ビットに対する前記記憶素子を含む請求項1記載の方法。

【請求項3】

前記浮動小数点演算を実行するためのロジックを有する浮動小数点演算器を使用することをさらに含み、

前記電力が取り除かれる1つ以上のコンポーネントは、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部を含む請求項2記載の方法。

【請求項4】

前記浮動小数点演算を実行するロジックを有する浮動小数点演算器を使用することをさらに含み、

前記電力が取り除かれる1つ以上のコンポーネントは、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部を含む請求項1記載の方法。

【請求項5】

前記浮動小数点演算は、加算を含む請求項4記載の方法。

【請求項6】

前記ロジックの一部からの桁上がりを強制的にゼロにすることをさらに含む請求項5記載の方法。

【請求項7】

前記浮動小数点演算は、乗算を含む請求項4記載の方法。

【請求項8】

最大精度を有する浮動小数点プロセッサにおいて、

1つ以上の浮動小数点数に関する浮動小数点演算に対して、前記最大精度よりも小さい副精度を選択するように構成された浮動小数点制御装置と、

前記浮動小数点演算を実行するように構成された浮動小数点演算器とを具備し、

前記副精度の選択は、前記1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらし、

前記浮動小数点制御装置は、さもなければ前記1つ以上の過剰ビットを記憶または処理するために使用される、前記浮動小数点プロセッサ中の1つ以上のコンポーネントから電力を取り除くようにさらに構成されている浮動小数点プロセッサ。

【請求項9】

複数の記憶素子を有する浮動小数点レジスタをさらに具備し、前記1つ以上の過剰ビットは、前記記憶素子のうちの1つ以上の中に記憶されており、

前記電力を取り除くことができる1つ以上のコンポーネントは、前記1つ以上の過剰ビットに対する前記記憶素子を含む請求項8記載の浮動小数点プロセッサ。

【請求項10】

前記浮動小数点演算器は、前記浮動小数点演算を実行するためのロジックを備え、

前記電力を取り除くことができる1つ以上のコンポーネントは、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部を含む請求項9記載の浮動小数点プロセッサ。

【請求項11】

前記浮動小数点演算器は、前記浮動小数点演算を実行するためのロジックを備え、

前記電力を取り除くことができる1つ以上のコンポーネントは、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部を含む請求項8記載の浮動小数点プロセッサ。

【請求項12】

前記浮動小数点演算器は、浮動小数点加算器を含む請求項11記載の浮動小数点プロセッサ。

【請求項13】

前記電力が取り除かれるとき、前記浮動小数点演算器は、前記ロジックの一部からの桁上がりを強制的にゼロにするようにさらに構成されている請求項12記載の浮動小数点プロセッサ。

【請求項14】

前記浮動小数点演算器は、浮動小数点乗算器を含む請求項11記載の浮動小数点プロセッサ。

【請求項15】

最大精度を有する浮動小数点プロセッサにおいて、

複数の浮動小数点数を記憶するように構成された複数の記憶素子を有する浮動小数点レジスタと、

前記浮動小数点レジスタ中に記憶された前記浮動小数点数のうちの1つ以上に関して、浮動小数点演算を実行するように構成された浮動小数点演算器と、

前記浮動小数点数のうちの1つ以上に関する浮動小数点演算に対して、前記最大精度よりも小さい副精度を選択するように構成された浮動小数点制御装置とを具備し、

前記副精度の選択は、前記浮動小数点数のうちの1つ以上のそれぞれに対して、1つ以上の過剰ビットをもたらし、

前記1つ以上の過剰ビットは、前記浮動小数点レジスタの前記記憶素子のうちの1つ以上の中に記憶されており、

前記浮動小数点制御装置は、前記1つ以上の過剰ビットに対する前記記憶素子から電力を取り除くようにさらに構成されている浮動小数点プロセッサ。

【請求項16】

前記浮動小数点演算器は、前記浮動小数点演算を実行するように構成されたロジックを備え、

前記浮動小数点制御装置は、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部から電力を取り除くようにさらに構成されている請求項15記載の浮動小数点プロセッサ。

【請求項17】

前記浮動小数点演算器は、浮動小数点加算器を含む請求項16記載の浮動小数点プロセッサ。

【請求項18】

前記電力が取り除かれるとき、前記浮動小数点演算器は、前記ロジックの一部からの桁上がりを強制的にゼロにするようにさらに構成されている請求項17記載の浮動小数点プロセッサ。

【請求項19】

前記浮動小数点演算器は、浮動小数点乗算器を含む請求項16記載の浮動小数点プロセッサ。

【請求項20】

最大精度を有する浮動小数点プロセッサにおいて、

複数の浮動小数点数を記憶するように構成された浮動小数点レジスタと、

前記浮動小数点レジスタ中に記憶された前記浮動小数点数のうちの1つ以上に関して、浮動小数点演算を実行するように構成されたロジックを有する浮動小数点演算器と、

前記浮動小数点数のうちの1つ以上に関する浮動小数点演算に対して、前記最大精度よりも小さい副精度を選択するように構成された浮動小数点制御装置とを具備し、

前記副精度の選択は、前記浮動小数点数のうちの1つ以上のそれぞれに対して、1つ以上の過剰ビットをもたらし、

前記浮動小数点制御装置は、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記回路の一部から電力を取り除くようにさらに構成されている浮動小数点プロセッサ。

【請求項21】

前記浮動小数点レジスタは、前記浮動小数点数を記憶するように構成された複数の記憶素子を備え、前記1つ以上の過剰ビットは、前記記憶素子のうちの1つ以上の中に記憶されており、

前記浮動小数点制御装置は、前記1つ以上の過剰ビットに対する前記記憶素子から電力を取り除くようにさらに構成されている請求項20記載の浮動小数点プロセッサ。

【請求項22】

前記浮動小数点演算器は、浮動小数点加算器を含む請求項20記載の浮動小数点プロセッサ。

【請求項23】

前記電力が取り除かれるとき、前記浮動小数点演算器は、前記ロジックの一部からの桁上がりを強制的にゼロにするようにさらに構成されている請求項22記載の浮動小数点プロセッサ。

【請求項24】

前記浮動小数点演算器は、浮動小数点乗算器を含み、前記浮動小数点乗算器内の、部分積を構成する素子の一部から、電力が取り除かれる請求項20記載の浮動小数点プロセッサ。

【請求項1】

最大精度を有する浮動小数点プロセッサにより、浮動小数点演算を実行する方法において、

1つ以上の浮動小数点数に関する前記浮動小数点演算に対して、前記最大精度よりも小さい副精度を選択し、前記副精度の選択は、前記1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらすことと、

さもなければ前記1つ以上の過剰ビットを記憶または処理するために使用される、前記浮動小数点プロセッサ中の1つ以上のコンポーネントから電力を取り除くことと、

前記1つ以上のコンポーネントから電力を取り除いた状態で、前記浮動小数点演算を実行することとを含む方法。

【請求項2】

複数の記憶素子を有する浮動小数点レジスタを使用することをさらに含み、前記1つ以上の過剰ビットは、前記記憶素子のうちの1つ以上の中に記憶されており、

前記電力が取り除かれる1つ以上のコンポーネントは、前記1つ以上の過剰ビットに対する前記記憶素子を含む請求項1記載の方法。

【請求項3】

前記浮動小数点演算を実行するためのロジックを有する浮動小数点演算器を使用することをさらに含み、

前記電力が取り除かれる1つ以上のコンポーネントは、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部を含む請求項2記載の方法。

【請求項4】

前記浮動小数点演算を実行するロジックを有する浮動小数点演算器を使用することをさらに含み、

前記電力が取り除かれる1つ以上のコンポーネントは、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部を含む請求項1記載の方法。

【請求項5】

前記浮動小数点演算は、加算を含む請求項4記載の方法。

【請求項6】

前記ロジックの一部からの桁上がりを強制的にゼロにすることをさらに含む請求項5記載の方法。

【請求項7】

前記浮動小数点演算は、乗算を含む請求項4記載の方法。

【請求項8】

最大精度を有する浮動小数点プロセッサにおいて、

1つ以上の浮動小数点数に関する浮動小数点演算に対して、前記最大精度よりも小さい副精度を選択するように構成された浮動小数点制御装置と、

前記浮動小数点演算を実行するように構成された浮動小数点演算器とを具備し、

前記副精度の選択は、前記1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらし、

前記浮動小数点制御装置は、さもなければ前記1つ以上の過剰ビットを記憶または処理するために使用される、前記浮動小数点プロセッサ中の1つ以上のコンポーネントから電力を取り除くようにさらに構成されている浮動小数点プロセッサ。

【請求項9】

複数の記憶素子を有する浮動小数点レジスタをさらに具備し、前記1つ以上の過剰ビットは、前記記憶素子のうちの1つ以上の中に記憶されており、

前記電力を取り除くことができる1つ以上のコンポーネントは、前記1つ以上の過剰ビットに対する前記記憶素子を含む請求項8記載の浮動小数点プロセッサ。

【請求項10】

前記浮動小数点演算器は、前記浮動小数点演算を実行するためのロジックを備え、

前記電力を取り除くことができる1つ以上のコンポーネントは、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部を含む請求項9記載の浮動小数点プロセッサ。

【請求項11】

前記浮動小数点演算器は、前記浮動小数点演算を実行するためのロジックを備え、

前記電力を取り除くことができる1つ以上のコンポーネントは、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部を含む請求項8記載の浮動小数点プロセッサ。

【請求項12】

前記浮動小数点演算器は、浮動小数点加算器を含む請求項11記載の浮動小数点プロセッサ。

【請求項13】

前記電力が取り除かれるとき、前記浮動小数点演算器は、前記ロジックの一部からの桁上がりを強制的にゼロにするようにさらに構成されている請求項12記載の浮動小数点プロセッサ。

【請求項14】

前記浮動小数点演算器は、浮動小数点乗算器を含む請求項11記載の浮動小数点プロセッサ。

【請求項15】

最大精度を有する浮動小数点プロセッサにおいて、

複数の浮動小数点数を記憶するように構成された複数の記憶素子を有する浮動小数点レジスタと、

前記浮動小数点レジスタ中に記憶された前記浮動小数点数のうちの1つ以上に関して、浮動小数点演算を実行するように構成された浮動小数点演算器と、

前記浮動小数点数のうちの1つ以上に関する浮動小数点演算に対して、前記最大精度よりも小さい副精度を選択するように構成された浮動小数点制御装置とを具備し、

前記副精度の選択は、前記浮動小数点数のうちの1つ以上のそれぞれに対して、1つ以上の過剰ビットをもたらし、

前記1つ以上の過剰ビットは、前記浮動小数点レジスタの前記記憶素子のうちの1つ以上の中に記憶されており、

前記浮動小数点制御装置は、前記1つ以上の過剰ビットに対する前記記憶素子から電力を取り除くようにさらに構成されている浮動小数点プロセッサ。

【請求項16】

前記浮動小数点演算器は、前記浮動小数点演算を実行するように構成されたロジックを備え、

前記浮動小数点制御装置は、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記ロジックの一部から電力を取り除くようにさらに構成されている請求項15記載の浮動小数点プロセッサ。

【請求項17】

前記浮動小数点演算器は、浮動小数点加算器を含む請求項16記載の浮動小数点プロセッサ。

【請求項18】

前記電力が取り除かれるとき、前記浮動小数点演算器は、前記ロジックの一部からの桁上がりを強制的にゼロにするようにさらに構成されている請求項17記載の浮動小数点プロセッサ。

【請求項19】

前記浮動小数点演算器は、浮動小数点乗算器を含む請求項16記載の浮動小数点プロセッサ。

【請求項20】

最大精度を有する浮動小数点プロセッサにおいて、

複数の浮動小数点数を記憶するように構成された浮動小数点レジスタと、

前記浮動小数点レジスタ中に記憶された前記浮動小数点数のうちの1つ以上に関して、浮動小数点演算を実行するように構成されたロジックを有する浮動小数点演算器と、

前記浮動小数点数のうちの1つ以上に関する浮動小数点演算に対して、前記最大精度よりも小さい副精度を選択するように構成された浮動小数点制御装置とを具備し、

前記副精度の選択は、前記浮動小数点数のうちの1つ以上のそれぞれに対して、1つ以上の過剰ビットをもたらし、

前記浮動小数点制御装置は、さもなければ前記1つ以上の過剰ビットを処理するために使用される、前記回路の一部から電力を取り除くようにさらに構成されている浮動小数点プロセッサ。

【請求項21】

前記浮動小数点レジスタは、前記浮動小数点数を記憶するように構成された複数の記憶素子を備え、前記1つ以上の過剰ビットは、前記記憶素子のうちの1つ以上の中に記憶されており、

前記浮動小数点制御装置は、前記1つ以上の過剰ビットに対する前記記憶素子から電力を取り除くようにさらに構成されている請求項20記載の浮動小数点プロセッサ。

【請求項22】

前記浮動小数点演算器は、浮動小数点加算器を含む請求項20記載の浮動小数点プロセッサ。

【請求項23】

前記電力が取り除かれるとき、前記浮動小数点演算器は、前記ロジックの一部からの桁上がりを強制的にゼロにするようにさらに構成されている請求項22記載の浮動小数点プロセッサ。

【請求項24】

前記浮動小数点演算器は、浮動小数点乗算器を含み、前記浮動小数点乗算器内の、部分積を構成する素子の一部から、電力が取り除かれる請求項20記載の浮動小数点プロセッサ。

【図1】

【図2】

【図3A】

【図3B】

【図2】

【図3A】

【図3B】

【公開番号】特開2012−230684(P2012−230684A)

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−130000(P2012−130000)

【出願日】平成24年6月7日(2012.6.7)

【分割の表示】特願2008−557471(P2008−557471)の分割

【原出願日】平成19年2月27日(2007.2.27)

【出願人】(595020643)クゥアルコム・インコーポレイテッド (7,166)

【氏名又は名称原語表記】QUALCOMM INCORPORATED

【Fターム(参考)】

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願番号】特願2012−130000(P2012−130000)

【出願日】平成24年6月7日(2012.6.7)

【分割の表示】特願2008−557471(P2008−557471)の分割

【原出願日】平成19年2月27日(2007.2.27)

【出願人】(595020643)クゥアルコム・インコーポレイテッド (7,166)

【氏名又は名称原語表記】QUALCOMM INCORPORATED

【Fターム(参考)】

[ Back to top ]