配線基板の製造方法

【課題】半田バンプ上に半導体素子の電極を安定した状態で載せて半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することが可能な配線基板の製造方法を提供する。

【解決手段】絶縁基板に半導体素子接続パッド及びソルダーレジスト層5bを形成する工程と、前記半導体素子接続パッド上にソルダーレジスト層5bの上面より高い半田バンプB1を溶着する工程と、ソルダーレジスト層5b及び半田バンプB1上にソルダーレジスト層5bを弾性変形で凹ませつつ半田バンプB1を塑性変形で押潰す様に押圧ローラーRを転動させて半田バンプB1の頭頂部をソルダーレジスト層5bの上面より低い位置となるように平坦化する工程とを行なう。

【解決手段】絶縁基板に半導体素子接続パッド及びソルダーレジスト層5bを形成する工程と、前記半導体素子接続パッド上にソルダーレジスト層5bの上面より高い半田バンプB1を溶着する工程と、ソルダーレジスト層5b及び半田バンプB1上にソルダーレジスト層5bを弾性変形で凹ませつつ半田バンプB1を塑性変形で押潰す様に押圧ローラーRを転動させて半田バンプB1の頭頂部をソルダーレジスト層5bの上面より低い位置となるように平坦化する工程とを行なう。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路素子等の半導体素子を搭載するための高密度配線基板の製造方法に関するものである。

【背景技術】

【0002】

近年、携帯型のゲーム機や通信機器に代表される電子機器の小型、高機能化が進む中、それらに使用される配線基板にも小型、高機能化が要求されるようになっている。このような要求に対し、例えば半導体集積回路素子等の半導体素子を搭載する配線基板の上面に、さらに別の電気基板が半導体素子を覆うようにして積載された、いわゆるPoP(Package on Package)とよばれる複合構造の電子部品がある。

【0003】

このような電子部品において、半導体素子を搭載するための下側の配線基板は、その上面中央部に半導体素子を搭載するための半導体素子搭載部が形成されているとともに、この半導体素子搭載部を取り囲む上面外周部に上側の電気基板が搭載される電気基板搭載部を有している。そして、半導体素子搭載部には半導体素子の下面に設けた電極が半田バンプを介して接続される半導体素子接続パッドが、例えば縦横の並びの格子状の配列で形成されている。また、電気基板搭載部には電気基板の下面外周部に設けた接続端子が半田ボールを介して接続される電気基板接続パッドが、例えば枠状に並ぶ格子状の配列で形成されている。さらに、配線基板の上面には半導体素子接続パッドおよび電気基板接続パッドを露出させる開口部を有するソルダーレジスト層が被着されている。

【0004】

このような電子部品に用いられる配線基板上面に半導体素子を搭載するときには、半導体素子接続パッド上に、半田バンプを予め溶着しておき、その半田バンプ上に半導体素子の電極を載せた後、リフロー処理により接続する周知のフリップチップ法が好適に用いられる。なお、半田バンプ上に半導体素子の電極を載せる際には、半田バンプの頭頂部を例えば配線基板よりも大きな平坦なプレス面を有する平坦化装置によりプレスして予め平坦化しておくことが一般的に行なわれている。半田バンプの頭頂部を予め平坦化しておくことによって、半導体素子の電極を半田バンプ上に載せた際に電極が半田バンプ上から滑り落ちることを有効に防止して安定した状態で載せることができる。また半導体素子を搭載した後は、半導体素子と配線基板との隙間にアンダーフィルと呼ばれる封止樹脂を注入する。さらに、半導体素子が搭載された配線基板に電気基板を搭載するときには、電気基板の下面の接続パッドに半田ボールを予め溶着させておくとともに、配線基板の電気基板接続パッド上に、電気基板に溶着させた半田ボールを載せた後、リフロー処理により接続する方法が用いられる。

【0005】

ところで、上述したように、半導体素子の電極と半導体素子接続パッドとを接続した後は、半導体素子と配線基板との間に樹脂を注入して封止することで半導体素子の電極や接続パッドを保護する。このとき、封止用の樹脂は注入の際に流動性を有することから、一部が搭載部からはみ出して配線基板上の周囲に広がった後に固着することがある。しかし、この樹脂が、搭載部周囲の電気基板接続パッドにまで到達して固着すると、電気基板の接続に支障をきたしてしまう。そこで、そのような支障を回避するため、電気基板搭載部におけるソルダーレジスト層の厚みを半導体素子搭載部におけるソルダーレジスト層の厚みよりも10〜30μm程度厚くして半導体素子搭載部を厚みの厚いソルダーレジスト層で囲繞することによりアンダーフィル樹脂の半導体素子搭載部の外側への広がりを防止する構造をとる場合がある。

【0006】

ところが、上述のように半導体素子搭載部を厚みの厚いソルダーレジスト層で囲繞すると、半導体素子接続パッドに半田バンプを溶着させた際に、半田バンプの頭頂部が半導体素子搭載部周囲のソルダーレジスト層の上面から突出する高さがその分、低くなってしまう。すると半田バンプの頭頂部を平坦化する際に、平坦化装置の平坦なプレス面が半導体素子搭載部周囲の厚みの厚いソルダーレジスト層の上面に当ってしまい、半田バンプの頭頂部を十分に平坦化することが困難となる。半田バンプの頭頂部における平坦化が不十分であると、半導体素子の電極を半田バンプ上に載せた際に電極が半田バンプ上から滑り落ちる危険性が高くなり安定した状態で載せることができなくなる。その結果、半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することができないおそれがあった。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平6−224547号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、半導体素子を搭載する半導体素子搭載部の周囲が厚みの厚いソルダーレジスト層で囲繞されている場合であっても、半導体素子接続パッドに溶着された半田バンプの頭頂部を十分に平坦化することができ、それにより半田バンプ上に半導体素子の電極を安定した状態で載せて半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することが可能な配線基板の製造方法を提供することを課題とする。

【課題を解決するための手段】

【0009】

本発明における配線基板の製造方法は、上面中央部に半導体素子が搭載される半導体素子搭載部を有する絶縁基板と、半導体素子搭載部に配設された複数の半導体素子接続パッドと、絶縁基板の上面に半導体素子搭載部を囲繞するようにして被着されており、半導体素子接続パッドの上面より高い上面を有するソルダーレジスト層と、半導体素子接続パッド上に溶着されており、頭頂部が平坦化された半田バンプとを備える配線基板の製造方法であって、絶縁基板の上面に半導体素子接続パッドおよびソルダーレジスト層を形成する工程と、半導体素子接続パッド上にソルダーレジスト層の上面よりも突出する高さの半田バンプを溶着する工程と、ソルダーレジスト層上および半田バンプ上に、ソルダーレジスト層を弾性変形で凹ませつつ半田バンプの頭頂部を塑性変形で押し潰すように押圧ローラーを転動させることにより頭頂部をソルダーレジスト層の上面より低い位置となるように平坦化する工程とを行なうことを特徴とするものである。

【発明の効果】

【0010】

本発明の配線基板の製造方法によれば、押圧ローラーが半導体素子搭載部を囲繞するソルダーレジスト層を弾性変形で凹ませつつ半田バンプの頭頂部を塑性変形で押し潰すように転動させることから、押圧ローラーが転動した後のソルダーレジスト層は弾性力により転動前の高さに復元するとともに、半田バンプの頭頂部は平坦に塑性変形される。これにより、半田バンプの頭頂部を安定的に平坦化することができ、その結果、半田バンプ上に半導体素子の電極を安定した状態で載せて半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することが可能な配線基板の製造方法を提供することができる。

【図面の簡単な説明】

【0011】

【図1】図1は、本発明の配線基板の実施の形態の一例を示す概略断面図である。

【図2】図2(a)〜(d)は、本発明の配線基板の製造方法の実施形態の一例を示す概略断面図である。

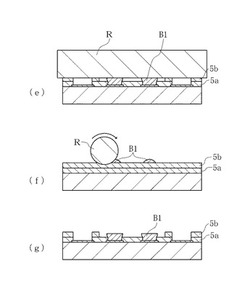

【図3】図3(e)〜(g)は、本発明の配線基板の製造方法の実施形態の一例を示す概略断面図および概略側面図である。

【発明を実施するための形態】

【0012】

次に、本発明の配線基板の製造方法の実施形態の一例を図1〜図3を基にして詳細に説明する。

【0013】

図1に本発明配線基板の製造方法により接続された配線基板10を用いた電子部品の概略断面図を示す。配線基板10は、コア用の絶縁層1の両主面にビルドアップ用の絶縁層3が複数層ずつ積層されて成る絶縁基板Sの内部および表面にコア用の配線導体2とビルドアップ用の配線導体4を配設して成る。コア用の絶縁層1は例えばガラスクロスにエポキシ樹脂やビスマレイミドトリアジン樹脂等の熱硬化性樹脂を含浸させた電気絶縁材料から成り、コア用の配線導体2は例えば銅箔や銅めっき層から成る。またビルドアップ用の絶縁層3は例えばエポキシ樹脂やポリイミド樹脂などの熱硬化性樹脂を含有する電気絶縁材料から成り、ビルドアップ用の配線導体4は例えば銅めっき層から成る。

【0014】

配線基板10の上面中央部には、半導体素子Eがフリップチップ接続により搭載される半導体素子搭載部10aが形成されている。半導体素子搭載部10aには、半導体素子Eの電極T1に接続される半導体素子接続パッド6が形成されている。また、配線基板10の上面外周部には、電気基板Cが搭載される電気基板搭載部10bが形成されている。電気基板搭載部10bには電気基板Cの接続端子T2が接続される電気基板接続パッド7が形成されている。これらの半導体素子接続パッド6および電気基板接続パッド7は、最表層に形成された配線導体4の一部から形成されている。

【0015】

さらに配線基板10の上面には、半導体素子接続パッド6および電気基板接続パッド7を露出させる開口部を有するようにしてソルダーレジスト層5が形成されている。ソルダーレジスト層5は、半導体素子搭載部10aから電気基板搭載部10bを含む領域にわたり形成された第1のソルダーレジスト層5aと、この第1のソルダーレジスト5a上の電気基板搭載部10bに半導体素子搭載部10aを囲繞するように形成された第2のソルダーレジスト層5bとを積層した2層構造を有しており、それにより半導体素子搭載部10aで薄く、その周囲で厚くなっている。なお、第1のソルダーレジスト層5aの厚みは5〜20μm程度である。また第2のソルダーレジスト層5bの厚みは10〜30μm程度である。このようなソルダーレジスト層5は、エポキシ樹脂やポリイミド樹脂などの熱硬化性樹脂を含有する電気絶縁材料から成り、好ましくは3〜6GPaの弾性率を有する。

【0016】

そして、半導体素子搭載部10aには半導体素子Eが半田バンプB1を介して搭載される。また、電気基板搭載部10bには電気基板Cが半田ボールB2を介して搭載される。なお、半導体素子搭載部10aに半導体素子Eを搭載するには、半導体素子接続パッド6上に半田バンプB1を予め溶着しておくとともにその頭頂部を平坦化した後、半田バンプB1上に半導体素子Eの電極T1を載せてリフロー処理する方法が採用される。また電気基板搭載部10bに電気基板Cを搭載するには、電気基板Cの接続端子T2に半田ボールB2を予め溶着しておくとともにその半田ボールB2を電気基板接続パッド7上に載せてリフロー処理する方法が採用される。なお半導体素子Eを搭載した後は、半導体素子Eと配線基板10との間にアンダーフィルと呼ばれる封止樹脂Gを注入する。このとき、半導体素子搭載部10aは厚みの厚い第2のソルダーレジスト層5bで囲繞されているので、封止樹脂Gの広がりは第2のソルダーレジスト5bの内周面でせき止められて電気基板接続パッド7に到達することはない。したがって、封止樹脂Gが配線基板10と電気基板Cとの接続に支障をきたすようなことはない。

【0017】

次に、本発明の配線基板の製造方法の一例について、図2(a)〜(d)および図3(e)〜(g)を基にして詳細に説明する。なお、本説明においては、半田バンプの平坦化方法を中心に説明する。また、図1と同様の個所には同様の符号を付して説明する。

【0018】

まず、図2(a)に示すように、絶縁基板Sの上面に半導体素子接続パッド6および電気基板接続パッド7を形成する。このような半導体素子接続パッド6および電気基板接続パッド7は、例えば周知のセミアディティブ法を用いることにより形成できる。

【0019】

次に、図2(b)に示すように、絶縁基板Sの表面に半導体素子接続パッド6および電気基板接続パッド7の中央部を露出させる開口部を有する第1のソルダーレジスト層5aを形成する。第1のソルダーレジスト層5aの形成は、絶縁基板Sの表面にソルダーレジスト用の感光性の樹脂フィルムを貼着するとともに、これを周知のフォトリソグラフィ技術を用いて所定のパターンに露光および現像した後、硬化させることにより行なう。なお絶縁基板Sの上面中央部に配設された接続パッド6の形成領域は、半導体素子Eが搭載される半導体素子搭載部10aとなり、電気基板接続パッド7の形成領域は電気基板Cが搭載される電気回路搭載部10bとなる。

【0020】

次に、図2(c)に示すように、電気基板搭載部10bにおける第1のソルダーレジスト層5aの上面に、電気基板接続パッド7を露出させる開口部を有するとともに半導体素子搭載部10aを囲繞する第2のソルダーレジスト層5bを形成する。ソルダーレジスト5bの形成は、ソルダーレジスト5aの場合と同様の方法により行なえばよい。

【0021】

次に、図2(d)に示すように、第1のソルダーレジスト層5aの開口部から露出した接続パッド6上に半田バンプB1を溶着する。このとき、半田バンプB1の頭頂部が第2のソルダーレジスト層5bの上面よりも若干高く形成されるようにする。半田バンプB1は、周知の印刷技術により接続パッド6上に半田ペーストを塗布した後に、リフロー処理することにより形成される。

【0022】

次に、図3(e)および図3(f)に示すように、第2のソルダーレジスト層5b上および半田バンプB1上に押圧ローラーRを上方から押さえながら転動させて、図3(g)に示すように半田バンプB1の頭頂部を平坦化する。押圧ローラーRは、例えば直径が10〜30mm程度の円柱状のステンレスから成る。なお、押圧ローラーRが転動している方向の前面から見た状態を図3(e)に示し、側面から見た状態を図3(f)に示している。押圧ローラーRは、第2のソルダーレジスト層5bおよび半田バンプB1を上方から押さえながら矢印の方向に転動しているが、このとき、押圧ローラーRが第2のソルダーレジスト層5bを弾性変形で凹ませつつ半田バンプB1の頭頂部を塑性変形で押し潰すようにする。第2のソルダーレジスト層5bを弾性変形で凹ませながら押圧ローラーRを転動させることにより、半導体素子搭載部10a内の半田バンプB1の頭頂部をソルダーレジスト層5aの上面よりも低い位置まで押しつぶして良好に平坦化することが可能となる。押圧ローラーRが転動した後は、第2のソルダーレジスト層5bは弾性力により元の高さに復元するが、半田バンプB1の頭頂部は第2のソルダーレジスト層5bの上面よりも低い位置で平坦に塑性変形されたままとなる。したがって本発明によれば、半導体素子接続パッドに溶着された半田バンプの頭頂部を十分に平坦化することができ、それにより半田バンプ上に半導体素子の電極を安定した状態で載せて半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することが可能な配線基板の製造方法を提供することができる。

【0023】

なお、押圧ローラーRの直径が10mmを未満であると、押圧ローラーR自体が転動に伴い撓んで半田バンプB1を良好に平坦化できなくなる危険性が高くなり、逆に30mmを超えると、ソルダーレジスト層5b上を上方から押さえながら転動する際にソルダーレジスト層5bを弾性変形で良好に凹ますことが困難となる。したがって、押圧ローラーRの直径は10〜30mmの範囲が好ましい。

【符号の説明】

【0024】

5 ソルダーレジスト層

6 半導体素子接続パッド

10 配線基板

10a 半導体素子搭載部

B1 半田バンプ

E 半導体素子

R 押圧ローラー

S 絶縁基板

【技術分野】

【0001】

本発明は、半導体集積回路素子等の半導体素子を搭載するための高密度配線基板の製造方法に関するものである。

【背景技術】

【0002】

近年、携帯型のゲーム機や通信機器に代表される電子機器の小型、高機能化が進む中、それらに使用される配線基板にも小型、高機能化が要求されるようになっている。このような要求に対し、例えば半導体集積回路素子等の半導体素子を搭載する配線基板の上面に、さらに別の電気基板が半導体素子を覆うようにして積載された、いわゆるPoP(Package on Package)とよばれる複合構造の電子部品がある。

【0003】

このような電子部品において、半導体素子を搭載するための下側の配線基板は、その上面中央部に半導体素子を搭載するための半導体素子搭載部が形成されているとともに、この半導体素子搭載部を取り囲む上面外周部に上側の電気基板が搭載される電気基板搭載部を有している。そして、半導体素子搭載部には半導体素子の下面に設けた電極が半田バンプを介して接続される半導体素子接続パッドが、例えば縦横の並びの格子状の配列で形成されている。また、電気基板搭載部には電気基板の下面外周部に設けた接続端子が半田ボールを介して接続される電気基板接続パッドが、例えば枠状に並ぶ格子状の配列で形成されている。さらに、配線基板の上面には半導体素子接続パッドおよび電気基板接続パッドを露出させる開口部を有するソルダーレジスト層が被着されている。

【0004】

このような電子部品に用いられる配線基板上面に半導体素子を搭載するときには、半導体素子接続パッド上に、半田バンプを予め溶着しておき、その半田バンプ上に半導体素子の電極を載せた後、リフロー処理により接続する周知のフリップチップ法が好適に用いられる。なお、半田バンプ上に半導体素子の電極を載せる際には、半田バンプの頭頂部を例えば配線基板よりも大きな平坦なプレス面を有する平坦化装置によりプレスして予め平坦化しておくことが一般的に行なわれている。半田バンプの頭頂部を予め平坦化しておくことによって、半導体素子の電極を半田バンプ上に載せた際に電極が半田バンプ上から滑り落ちることを有効に防止して安定した状態で載せることができる。また半導体素子を搭載した後は、半導体素子と配線基板との隙間にアンダーフィルと呼ばれる封止樹脂を注入する。さらに、半導体素子が搭載された配線基板に電気基板を搭載するときには、電気基板の下面の接続パッドに半田ボールを予め溶着させておくとともに、配線基板の電気基板接続パッド上に、電気基板に溶着させた半田ボールを載せた後、リフロー処理により接続する方法が用いられる。

【0005】

ところで、上述したように、半導体素子の電極と半導体素子接続パッドとを接続した後は、半導体素子と配線基板との間に樹脂を注入して封止することで半導体素子の電極や接続パッドを保護する。このとき、封止用の樹脂は注入の際に流動性を有することから、一部が搭載部からはみ出して配線基板上の周囲に広がった後に固着することがある。しかし、この樹脂が、搭載部周囲の電気基板接続パッドにまで到達して固着すると、電気基板の接続に支障をきたしてしまう。そこで、そのような支障を回避するため、電気基板搭載部におけるソルダーレジスト層の厚みを半導体素子搭載部におけるソルダーレジスト層の厚みよりも10〜30μm程度厚くして半導体素子搭載部を厚みの厚いソルダーレジスト層で囲繞することによりアンダーフィル樹脂の半導体素子搭載部の外側への広がりを防止する構造をとる場合がある。

【0006】

ところが、上述のように半導体素子搭載部を厚みの厚いソルダーレジスト層で囲繞すると、半導体素子接続パッドに半田バンプを溶着させた際に、半田バンプの頭頂部が半導体素子搭載部周囲のソルダーレジスト層の上面から突出する高さがその分、低くなってしまう。すると半田バンプの頭頂部を平坦化する際に、平坦化装置の平坦なプレス面が半導体素子搭載部周囲の厚みの厚いソルダーレジスト層の上面に当ってしまい、半田バンプの頭頂部を十分に平坦化することが困難となる。半田バンプの頭頂部における平坦化が不十分であると、半導体素子の電極を半田バンプ上に載せた際に電極が半田バンプ上から滑り落ちる危険性が高くなり安定した状態で載せることができなくなる。その結果、半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することができないおそれがあった。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平6−224547号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、半導体素子を搭載する半導体素子搭載部の周囲が厚みの厚いソルダーレジスト層で囲繞されている場合であっても、半導体素子接続パッドに溶着された半田バンプの頭頂部を十分に平坦化することができ、それにより半田バンプ上に半導体素子の電極を安定した状態で載せて半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することが可能な配線基板の製造方法を提供することを課題とする。

【課題を解決するための手段】

【0009】

本発明における配線基板の製造方法は、上面中央部に半導体素子が搭載される半導体素子搭載部を有する絶縁基板と、半導体素子搭載部に配設された複数の半導体素子接続パッドと、絶縁基板の上面に半導体素子搭載部を囲繞するようにして被着されており、半導体素子接続パッドの上面より高い上面を有するソルダーレジスト層と、半導体素子接続パッド上に溶着されており、頭頂部が平坦化された半田バンプとを備える配線基板の製造方法であって、絶縁基板の上面に半導体素子接続パッドおよびソルダーレジスト層を形成する工程と、半導体素子接続パッド上にソルダーレジスト層の上面よりも突出する高さの半田バンプを溶着する工程と、ソルダーレジスト層上および半田バンプ上に、ソルダーレジスト層を弾性変形で凹ませつつ半田バンプの頭頂部を塑性変形で押し潰すように押圧ローラーを転動させることにより頭頂部をソルダーレジスト層の上面より低い位置となるように平坦化する工程とを行なうことを特徴とするものである。

【発明の効果】

【0010】

本発明の配線基板の製造方法によれば、押圧ローラーが半導体素子搭載部を囲繞するソルダーレジスト層を弾性変形で凹ませつつ半田バンプの頭頂部を塑性変形で押し潰すように転動させることから、押圧ローラーが転動した後のソルダーレジスト層は弾性力により転動前の高さに復元するとともに、半田バンプの頭頂部は平坦に塑性変形される。これにより、半田バンプの頭頂部を安定的に平坦化することができ、その結果、半田バンプ上に半導体素子の電極を安定した状態で載せて半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することが可能な配線基板の製造方法を提供することができる。

【図面の簡単な説明】

【0011】

【図1】図1は、本発明の配線基板の実施の形態の一例を示す概略断面図である。

【図2】図2(a)〜(d)は、本発明の配線基板の製造方法の実施形態の一例を示す概略断面図である。

【図3】図3(e)〜(g)は、本発明の配線基板の製造方法の実施形態の一例を示す概略断面図および概略側面図である。

【発明を実施するための形態】

【0012】

次に、本発明の配線基板の製造方法の実施形態の一例を図1〜図3を基にして詳細に説明する。

【0013】

図1に本発明配線基板の製造方法により接続された配線基板10を用いた電子部品の概略断面図を示す。配線基板10は、コア用の絶縁層1の両主面にビルドアップ用の絶縁層3が複数層ずつ積層されて成る絶縁基板Sの内部および表面にコア用の配線導体2とビルドアップ用の配線導体4を配設して成る。コア用の絶縁層1は例えばガラスクロスにエポキシ樹脂やビスマレイミドトリアジン樹脂等の熱硬化性樹脂を含浸させた電気絶縁材料から成り、コア用の配線導体2は例えば銅箔や銅めっき層から成る。またビルドアップ用の絶縁層3は例えばエポキシ樹脂やポリイミド樹脂などの熱硬化性樹脂を含有する電気絶縁材料から成り、ビルドアップ用の配線導体4は例えば銅めっき層から成る。

【0014】

配線基板10の上面中央部には、半導体素子Eがフリップチップ接続により搭載される半導体素子搭載部10aが形成されている。半導体素子搭載部10aには、半導体素子Eの電極T1に接続される半導体素子接続パッド6が形成されている。また、配線基板10の上面外周部には、電気基板Cが搭載される電気基板搭載部10bが形成されている。電気基板搭載部10bには電気基板Cの接続端子T2が接続される電気基板接続パッド7が形成されている。これらの半導体素子接続パッド6および電気基板接続パッド7は、最表層に形成された配線導体4の一部から形成されている。

【0015】

さらに配線基板10の上面には、半導体素子接続パッド6および電気基板接続パッド7を露出させる開口部を有するようにしてソルダーレジスト層5が形成されている。ソルダーレジスト層5は、半導体素子搭載部10aから電気基板搭載部10bを含む領域にわたり形成された第1のソルダーレジスト層5aと、この第1のソルダーレジスト5a上の電気基板搭載部10bに半導体素子搭載部10aを囲繞するように形成された第2のソルダーレジスト層5bとを積層した2層構造を有しており、それにより半導体素子搭載部10aで薄く、その周囲で厚くなっている。なお、第1のソルダーレジスト層5aの厚みは5〜20μm程度である。また第2のソルダーレジスト層5bの厚みは10〜30μm程度である。このようなソルダーレジスト層5は、エポキシ樹脂やポリイミド樹脂などの熱硬化性樹脂を含有する電気絶縁材料から成り、好ましくは3〜6GPaの弾性率を有する。

【0016】

そして、半導体素子搭載部10aには半導体素子Eが半田バンプB1を介して搭載される。また、電気基板搭載部10bには電気基板Cが半田ボールB2を介して搭載される。なお、半導体素子搭載部10aに半導体素子Eを搭載するには、半導体素子接続パッド6上に半田バンプB1を予め溶着しておくとともにその頭頂部を平坦化した後、半田バンプB1上に半導体素子Eの電極T1を載せてリフロー処理する方法が採用される。また電気基板搭載部10bに電気基板Cを搭載するには、電気基板Cの接続端子T2に半田ボールB2を予め溶着しておくとともにその半田ボールB2を電気基板接続パッド7上に載せてリフロー処理する方法が採用される。なお半導体素子Eを搭載した後は、半導体素子Eと配線基板10との間にアンダーフィルと呼ばれる封止樹脂Gを注入する。このとき、半導体素子搭載部10aは厚みの厚い第2のソルダーレジスト層5bで囲繞されているので、封止樹脂Gの広がりは第2のソルダーレジスト5bの内周面でせき止められて電気基板接続パッド7に到達することはない。したがって、封止樹脂Gが配線基板10と電気基板Cとの接続に支障をきたすようなことはない。

【0017】

次に、本発明の配線基板の製造方法の一例について、図2(a)〜(d)および図3(e)〜(g)を基にして詳細に説明する。なお、本説明においては、半田バンプの平坦化方法を中心に説明する。また、図1と同様の個所には同様の符号を付して説明する。

【0018】

まず、図2(a)に示すように、絶縁基板Sの上面に半導体素子接続パッド6および電気基板接続パッド7を形成する。このような半導体素子接続パッド6および電気基板接続パッド7は、例えば周知のセミアディティブ法を用いることにより形成できる。

【0019】

次に、図2(b)に示すように、絶縁基板Sの表面に半導体素子接続パッド6および電気基板接続パッド7の中央部を露出させる開口部を有する第1のソルダーレジスト層5aを形成する。第1のソルダーレジスト層5aの形成は、絶縁基板Sの表面にソルダーレジスト用の感光性の樹脂フィルムを貼着するとともに、これを周知のフォトリソグラフィ技術を用いて所定のパターンに露光および現像した後、硬化させることにより行なう。なお絶縁基板Sの上面中央部に配設された接続パッド6の形成領域は、半導体素子Eが搭載される半導体素子搭載部10aとなり、電気基板接続パッド7の形成領域は電気基板Cが搭載される電気回路搭載部10bとなる。

【0020】

次に、図2(c)に示すように、電気基板搭載部10bにおける第1のソルダーレジスト層5aの上面に、電気基板接続パッド7を露出させる開口部を有するとともに半導体素子搭載部10aを囲繞する第2のソルダーレジスト層5bを形成する。ソルダーレジスト5bの形成は、ソルダーレジスト5aの場合と同様の方法により行なえばよい。

【0021】

次に、図2(d)に示すように、第1のソルダーレジスト層5aの開口部から露出した接続パッド6上に半田バンプB1を溶着する。このとき、半田バンプB1の頭頂部が第2のソルダーレジスト層5bの上面よりも若干高く形成されるようにする。半田バンプB1は、周知の印刷技術により接続パッド6上に半田ペーストを塗布した後に、リフロー処理することにより形成される。

【0022】

次に、図3(e)および図3(f)に示すように、第2のソルダーレジスト層5b上および半田バンプB1上に押圧ローラーRを上方から押さえながら転動させて、図3(g)に示すように半田バンプB1の頭頂部を平坦化する。押圧ローラーRは、例えば直径が10〜30mm程度の円柱状のステンレスから成る。なお、押圧ローラーRが転動している方向の前面から見た状態を図3(e)に示し、側面から見た状態を図3(f)に示している。押圧ローラーRは、第2のソルダーレジスト層5bおよび半田バンプB1を上方から押さえながら矢印の方向に転動しているが、このとき、押圧ローラーRが第2のソルダーレジスト層5bを弾性変形で凹ませつつ半田バンプB1の頭頂部を塑性変形で押し潰すようにする。第2のソルダーレジスト層5bを弾性変形で凹ませながら押圧ローラーRを転動させることにより、半導体素子搭載部10a内の半田バンプB1の頭頂部をソルダーレジスト層5aの上面よりも低い位置まで押しつぶして良好に平坦化することが可能となる。押圧ローラーRが転動した後は、第2のソルダーレジスト層5bは弾性力により元の高さに復元するが、半田バンプB1の頭頂部は第2のソルダーレジスト層5bの上面よりも低い位置で平坦に塑性変形されたままとなる。したがって本発明によれば、半導体素子接続パッドに溶着された半田バンプの頭頂部を十分に平坦化することができ、それにより半田バンプ上に半導体素子の電極を安定した状態で載せて半導体素子の電極と半導体素子接続パッドとを電気的に良好に接続することが可能な配線基板の製造方法を提供することができる。

【0023】

なお、押圧ローラーRの直径が10mmを未満であると、押圧ローラーR自体が転動に伴い撓んで半田バンプB1を良好に平坦化できなくなる危険性が高くなり、逆に30mmを超えると、ソルダーレジスト層5b上を上方から押さえながら転動する際にソルダーレジスト層5bを弾性変形で良好に凹ますことが困難となる。したがって、押圧ローラーRの直径は10〜30mmの範囲が好ましい。

【符号の説明】

【0024】

5 ソルダーレジスト層

6 半導体素子接続パッド

10 配線基板

10a 半導体素子搭載部

B1 半田バンプ

E 半導体素子

R 押圧ローラー

S 絶縁基板

【特許請求の範囲】

【請求項1】

上面中央部に半導体素子が搭載される半導体素子搭載部を有する絶縁基板と、前記半導体素子搭載部に配設された複数の半導体素子接続パッドと、前記絶縁基板の上面に前記半導体素子搭載部を囲繞するようにして被着されており、前記半導体素子接続パッドの上面より高い上面を有するソルダーレジスト層と、前記半導体素子接続パッド上に溶着されており、頭頂部が平坦化された半田バンプとを備える配線基板の製造方法であって、前記絶縁基板の上面に前記半導体素子接続パッドおよび前記ソルダーレジスト層を形成する工程と、前記半導体素子接続パッド上に前記ソルダーレジスト層の上面よりも突出する高さの半田バンプを溶着する工程と、前記ソルダーレジスト層上および前記半田バンプ上に、前記ソルダーレジスト層を弾性変形で凹ませつつ前記半田バンプの頭頂部を塑性変形で押し潰すように押圧ローラーを転動させることにより前記頭頂部を前記ソルダーレジスト層の上面より低い位置となるようなに平坦化する工程とを行なうことを特徴とする配線基板の製造方法。

【請求項1】

上面中央部に半導体素子が搭載される半導体素子搭載部を有する絶縁基板と、前記半導体素子搭載部に配設された複数の半導体素子接続パッドと、前記絶縁基板の上面に前記半導体素子搭載部を囲繞するようにして被着されており、前記半導体素子接続パッドの上面より高い上面を有するソルダーレジスト層と、前記半導体素子接続パッド上に溶着されており、頭頂部が平坦化された半田バンプとを備える配線基板の製造方法であって、前記絶縁基板の上面に前記半導体素子接続パッドおよび前記ソルダーレジスト層を形成する工程と、前記半導体素子接続パッド上に前記ソルダーレジスト層の上面よりも突出する高さの半田バンプを溶着する工程と、前記ソルダーレジスト層上および前記半田バンプ上に、前記ソルダーレジスト層を弾性変形で凹ませつつ前記半田バンプの頭頂部を塑性変形で押し潰すように押圧ローラーを転動させることにより前記頭頂部を前記ソルダーレジスト層の上面より低い位置となるようなに平坦化する工程とを行なうことを特徴とする配線基板の製造方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−115145(P2013−115145A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−258116(P2011−258116)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(304024898)京セラSLCテクノロジー株式会社 (213)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(304024898)京セラSLCテクノロジー株式会社 (213)

【Fターム(参考)】

[ Back to top ]