配線基板及びその製造方法

【課題】ピンとの接合に適した突起電極を備えることにより、信頼性を向上させることが可能な配線基板を提供すること。

【解決手段】本発明の配線基板101は、基板裏面103上の電極形成領域内に複数の突起電極11が配置され、複数の突起電極11上に母基板搭載用の複数のピン21がはんだ部31を介して接合された構造を有する。複数のピン21は、軸部22と、軸部22よりも外径が大きい頭部23とを有する。複数の突起電極11は、外径B1が頭部23の外径A2よりも大きく設定されるとともに、基板裏面103からの突出量B2が最大となる最突出部13が中心軸C1上に位置している。なお、頭部23は、突起電極11の中心軸C1とピン21の中心軸C2とが一致するように、はんだ部31を介して突起電極11上に接合される。

【解決手段】本発明の配線基板101は、基板裏面103上の電極形成領域内に複数の突起電極11が配置され、複数の突起電極11上に母基板搭載用の複数のピン21がはんだ部31を介して接合された構造を有する。複数のピン21は、軸部22と、軸部22よりも外径が大きい頭部23とを有する。複数の突起電極11は、外径B1が頭部23の外径A2よりも大きく設定されるとともに、基板裏面103からの突出量B2が最大となる最突出部13が中心軸C1上に位置している。なお、頭部23は、突起電極11の中心軸C1とピン21の中心軸C2とが一致するように、はんだ部31を介して突起電極11上に接合される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基板裏面上の電極形成領域内に複数の突起電極が配置され、複数の突起電極上に母基板搭載用の複数のピンがはんだ部を介して接合された配線基板及びその製造方法に関するものである。

【背景技術】

【0002】

コンピュータのマイクロプロセッサ等として使用される半導体集積回路素子(ICチップ)は、近年ますます高速化、高機能化しており、これに付随して端子数が増え、端子間ピッチも狭くなる傾向にある。一般的にICチップの底面には多数の端子が密集してアレイ状に配置されており、このような端子群はマザーボード(母基板)側の端子群に対してフリップチップの形態で接続される。但し、ICチップ側の端子群とマザーボード側の端子群とでは端子間ピッチに大きな差があることから、ICチップをマザーボード上に直接的に接続することは困難である。そのため、通常は、ICチップを搭載してなる配線基板(いわゆる半導体パッケージ)を作製し、その配線基板をマザーボード上に搭載するという手法が採用される。

【0003】

ここで、配線基板とマザーボードとの電気的な接続を図るための構造としては、配線基板の基板裏面上に配置された複数のパッド(突起電極)上にはんだバンプを形成した、いわゆるボールグリッドアレイ(BGA)が提案されている。また、配線基板とマザーボードとの電気的な接続を図るための他の構造として、複数のパッド上にはんだ部を介してピンを接合した、いわゆるピングリッドアレイ(PGA)も提案されている(例えば特許文献1参照)。以下、上記の配線基板におけるピンの接合方法について簡単に説明する。まず、基板裏面上に複数のパッドが形成された配線基板を準備する。また、複数のピンを専用の位置決め治具のピン挿入孔にセットした後、配線基板の下方に配置する。そして、各ピンの頭部を各パッドにはんだ付けすることにより、各ピンが配線基板に接合される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第3378550号公報(図2など)

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、一般的なパッドとしては、特許文献1に記載の平板状をなす「ピン接合部111」に加えて、表面に凹みを有するものも提案されている。なお、パッド上には、通常フラックスが印刷塗布されており、フラックスは、ピンをパッドにはんだ付けする際(リフロー時)に気化して、外部に放出されるようになっている。

【0006】

ところが、パッドが平板状であったり凹みを有する形状であったりすると、フラックスは、外部に放出されずにはんだ部内に溜まりやすくなる。この場合、はんだ部内にボイドが発生してしまい、それに起因してパッドとピンとの接合強度が低下する可能性がある。ゆえに、製造される配線基板が不良品となるため、配線基板の信頼性が低下するおそれがある。

【0007】

本発明は上記の課題に鑑みてなされたものであり、その第1の目的は、ピンとの接合に適した突起電極を備えることにより、信頼性を向上させることが可能な配線基板を提供することにある。また、第2の目的は、上記の優れた配線基板を得るのに好適な製造方法を提供することにある。

【課題を解決するための手段】

【0008】

上記課題を解決するための手段(手段1)としては、基板裏面上の電極形成領域内に複数の突起電極が配置され、前記複数の突起電極上に母基板搭載用の複数のピンがはんだ部を介して接合された配線基板であって、前記複数のピンは、軸部と、前記軸部よりも外径が大きい頭部とを有し、前記複数の突起電極は、外径が前記頭部の外径よりも大きく設定されるとともに、前記基板裏面からの突出量が最大となる最突出部が前記突起電極の中心軸上に位置しており、前記突起電極の中心軸と前記ピンの中心軸とが一致するように、前記頭部が前記はんだ部を介して前記突起電極上に接合されていることを特徴とする配線基板がある。

【0009】

従って、手段1の配線基板によると、複数の突起電極が、基板裏面からの突出量が最大となる最突出部を有している。即ち、各突起電極の表面は凸状をなしているため、はんだ部を介してピンを接合した際に、はんだ部内における突起電極の表面付近にフラックスが溜まりにくくなる。その結果、気化したフラックスがはんだ部内に溜まることに起因したボイドの発生が防止されるため、突起電極とピンとの接合強度の低下を防止することができる。即ち、ピンとの接合に適した突起電極を備えることにより、配線基板の信頼性を向上させることが可能となる。

【0010】

また、突起電極の外径がピンの頭部の外径よりも大きく設定されているため、突起電極と頭部とをはんだ部を介して接触させやすくなる。その結果、突起電極とピンとをより確実に接合させることができるため、配線基板の信頼性をよりいっそう向上させることができる。しかも、最突出部は突起電極の中心軸上に位置しているため、最突出部と向かい合うようにピンの頭部を配置するだけで、突起電極の中心軸とピンの中心軸とを容易に一致させることができる。よって、ピンを正確に位置決めすることができる。

【0011】

上記配線基板を形成する材料は特に限定されず任意であるが、例えば、樹脂基板などが好適である。好適な樹脂基板としては、EP樹脂(エポキシ樹脂)、PI樹脂(ポリイミド樹脂)、BT樹脂(ビスマレイミド−トリアジン樹脂)、PPE樹脂(ポリフェニレンエーテル樹脂)等からなる基板が挙げられる。そのほか、これらの樹脂とガラス繊維(ガラス織布やガラス不織布)との複合材料からなる基板を使用してもよい。その具体例としては、ガラス−BT複合基板、高Tgガラス−エポキシ複合基板(FR−4、FR−5等)等の高耐熱性積層板などがある。また、これらの樹脂とポリアミド繊維等の有機繊維との複合材料からなる基板を使用してもよい。あるいは、連続多孔質PTFE等の三次元網目状フッ素系樹脂基材にエポキシ樹脂などの熱硬化性樹脂を含浸させた樹脂−樹脂複合材料からなる基板等を使用してもよい。他の材料として、例えば各種のセラミックなどを選択することもできる。なお、かかる配線基板の構造としては特に限定されないが、例えばコア基板の片面または両面にビルドアップ層を有するビルドアップ多層配線基板や、コア基板を有さないコアレス配線基板などを挙げることができる。

【0012】

上記基板裏面上の電極形成領域の位置及び数は特に限定されず任意であるが、例えばいわゆる多数個取り基板の場合には配線基板の取り数に相当する数だけ電極形成領域が存在している。電極形成領域は基板裏面のみに存在していてもよいが、基板主面及び基板裏面の両方に存在していてもよい。

【0013】

また、複数の突起電極は、導電性の金属材料などによって形成することが可能である。突起電極を構成する金属材料としては、例えば銅、銀、鉄、コバルト、ニッケルなどが挙げられる。特に、突起電極は、導電性が高く安価な銅からなることが好ましい。また、突起電極は、めっきによって形成されることがよい。このようにすれば、突起電極を高精度かつ均一に形成することができる。仮に、突起電極を金属ペーストのリフローによって形成すると、突起電極を高精度かつ均一に形成することが困難になるため、個々の突起電極の高さにバラツキが生じてしまうおそれがある。

【0014】

さらに、複数のピンは、軸部と、軸部よりも外径が大きい頭部とを有している。ピンの形状は特に限定されず任意であるが、例えば、ピンは、頭部の上面が球面となっていることが好ましい。このようにすれば、はんだ部を介して突起電極上にピンを接合した際に、はんだ部内における頭部の上面付近にフラックスが溜まりにくくなる。その結果、気化したフラックスに起因するボイドがよりいっそう発生しにくくなるため、突起電極とピンとの接合強度の低下をより確実に防止することができる。

【0015】

なお、複数の突起電極及び複数のピンは、はんだ部を介して互いに接合される。はんだ部(及びはんだフィレット)に使用されるはんだ材料としては特に限定されないが、90Pb−10Sn、95Pb−5Sn、40Pb−60SnなどのPb−Sn系はんだ、Sn−Sb系はんだ、Sn−Ag系はんだ、Sn−Ag−Cu系はんだ、Au−Ge系はんだ、Au−Sn系はんだ、Au−Si系はんだなどが挙げられる。特に、はんだ部は鉛フリーはんだからなることが好ましい。このようにすれば、はんだ部に鉛が含まれないため、配線基板の環境への負荷を低くすることができる。また、鉛フリーはんだは、鉛を含有するはんだよりも濡れ性が悪く、ボイドの発生量が多くなる傾向にあるため、突起電極に最突出部を設けてフラックスを放出しやすくすれば、ボイドの発生をより効果的に防止できる。ここで、鉛フリーはんだとしては、Sn−Sb系はんだ、Sn−Ag系はんだ、Sn−Ag−Cu系はんだ、Au−Ge系はんだ、Au−Sn系はんだ、Au−Si系はんだなどが挙げられる。

【0016】

なお、ピンの頭部の上面と突起電極の表面とは互いに離間していることが好ましい。このようにすれば、頭部の上面と突起電極の表面との間に対してはんだ部を確実に充填することができる。その結果、頭部とはんだ部との接触面積や、突起電極とはんだ部との接触面積が大きくなるため、突起電極とピンとの接合強度を向上させることができる。また、はんだ部を構成するはんだフィレットの最大径は、突起電極の外径よりも大きく設定されることが好ましい。このようにした場合、はんだ部が突起電極の表面全体に接触するようになるため、突起電極とはんだ部との接合強度が向上する。

【0017】

上記課題を解決するための別の手段(手段2)としては、上記手段1のいずれか1項に記載の配線基板を製造する方法であって、複数の層間絶縁層を積層してなる積層部を準備する積層部準備工程と、前記基板裏面を有する最下層の前記層間絶縁層上に前記突起電極を形成する突起電極形成工程と、前記複数のピンを前記積層部よりも下方に配置した状態で、前記頭部を前記突起電極にはんだ付けするはんだ付け工程とを含むことを特徴とする配線基板の製造方法がある。

【0018】

従って、手段2の配線基板の製造方法によれば、最突出部を有する突起電極を形成すれば、はんだ付け工程を行ってはんだ部を介してピンの頭部を突起電極にはんだ付けした際に、はんだ部内における突起電極の表面付近にフラックスが溜まりにくくなる。その結果、気化したフラックスがはんだ部内に溜まることに起因したボイドの発生が防止されるため、突起電極とピンとの接合強度の低下を防止することができる。即ち、ピンとの接合に適した突起電極を備える配線基板を製造できるため、配線基板の信頼性を向上させることが可能となる。

【0019】

以下、手段2にかかる配線基板の製造方法について説明する。

【0020】

積層部準備工程では、複数の層間絶縁層を積層してなる積層部を準備する。層間絶縁層は、絶縁性、耐熱性、耐湿性等を考慮して適宜選択することができる。層間絶縁層の形成材料の好適例としては、エポキシ樹脂、フェノール樹脂、ウレタン樹脂、シリコーン樹脂、ポリイミド樹脂などの熱硬化性樹脂、ポリカーボネート樹脂、アクリル樹脂、ポリアセタール樹脂、ポリプロピレン樹脂などの熱可塑性樹脂等が挙げられる。そのほか、これらの樹脂とガラス繊維(ガラス織布やガラス不織布)やポリアミド繊維等の有機繊維との複合材料、あるいは、連続多孔質PTFE等の三次元網目状フッ素系樹脂基材にエポキシ樹脂などの熱硬化性樹脂を含浸させた樹脂−樹脂複合材料等を使用してもよい。なお、層間絶縁層には、層間接続のためのビア導体を形成するために、あらかじめビア穴が形成されていてもよい。

【0021】

次に、突起電極形成工程を行い、基板裏面を有する最下層の層間絶縁層上に突起電極を形成する。さらに、はんだ付け工程を行い、複数のピンを積層部よりも下方に配置した状態で、頭部を突起電極にはんだ付けする。以上のプロセスを経て、配線基板が製造される。

【0022】

なお、突起電極形成工程後かつはんだ付け工程前に、突起電極に対してエッチングを行うことにより、中心軸上に最突出部が位置する形状に突起電極を成形する突起電極成形工程を行うことが好ましい。このようにした場合、突起電極成形工程において突起電極に対してエッチングを行っているため、最突出部を高精度に形成することが可能となる。しかも、突起電極成形工程において最突出部を突起電極の中心軸上に位置させているため、最突出部と向かい合うようにピンの頭部を配置するだけで、突起電極の中心軸とピンの中心軸とを容易に一致させることができる。よって、ピンを正確に位置決めすることができる。

【図面の簡単な説明】

【0023】

【図1】本実施形態におけるコアレス配線基板の構成を示す概略断面図。

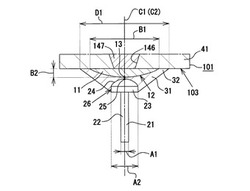

【図2】コアレス配線基板の要部断面図。

【図3】コアレス配線基板の製造方法を示す説明図。

【図4】コアレス配線基板の製造方法を示す説明図。

【図5】コアレス配線基板の製造方法を示す説明図。

【図6】コアレス配線基板の製造方法を示す説明図。

【図7】コアレス配線基板の製造方法を示す説明図。

【図8】コアレス配線基板の製造方法を示す説明図。

【図9】コアレス配線基板の製造方法を示す説明図。

【図10】コアレス配線基板の製造方法を示す説明図。

【図11】コアレス配線基板の製造方法を示す説明図。

【図12】コアレス配線基板の製造方法を示す説明図。

【発明を実施するための形態】

【0024】

以下、本発明を具体化した一実施形態を図面に基づき詳細に説明する。

【0025】

図1は、本実施形態のコアレス配線基板101(配線基板)を示す概略断面図である。コアレス配線基板101は、コア基板を有さず、エポキシ樹脂からなる4層の樹脂絶縁層41,42,43,44と銅からなる導体層51とを交互に積層した構造を有する配線基板である。樹脂絶縁層41〜44は、同一の厚さ及び材料からなる層間絶縁層である。

【0026】

さらに、各樹脂絶縁層41〜44には、それぞれビア穴146及びビア導体147が設けられている。各ビア穴146は、逆円錐台形状をなし、各樹脂絶縁層41〜44に対してYAGレーザーまたは炭酸ガスレーザーを用いた穴あけ加工を施すことにより形成される。各ビア導体147は、同一方向(図1では上方向)に拡径した導体であって、各導体層51を相互に電気的に接続している。なお、各ビア導体147の上端における外径は50μm以上120μm以下(本実施形態では80μm)に設定され、各ビア導体147の下端における外径は30μm以上100μm以下(本実施形態では60μm)に設定されている。

【0027】

図1に示されるように、コアレス配線基板101の基板主面102上(第4層の樹脂絶縁層44の表面上)には、ビア導体147を介して導体層51に電気的に接続される端子パッド52がアレイ状に形成されている。また、各端子パッド52は、はんだバンプ130を介して、矩形平板状をなすICチップ131の底面に配置された接続端子132に接続されるようになっている。即ち、はんだバンプ130は、ICチップ131の接続端子132とのフリップチップ接続に用いられる、いわゆるC4用のバンプである。なお、各端子パッド52からなる領域は、ICチップ131を搭載可能なICチップ搭載領域133である。ICチップ搭載領域133は、コアレス配線基板101の基板主面102に設定されている。

【0028】

そして、基板主面102とICチップ131との隙間には、アンダーフィル134が充填されている。その結果、コアレス配線基板101とICチップ131とが、隙間が封止された状態で互いに固定される。なお、本実施形態のアンダーフィル134は、熱膨張係数が20〜60ppm/℃程度(具体的には34ppm/℃)のエポキシ樹脂からなる。

【0029】

一方、図1に示されるように、コアレス配線基板101の基板裏面103上(第1層の樹脂絶縁層41の下面上)には、平面視矩形状の電極形成領域10が設定されている。そして、電極形成領域10内には、複数の突起電極11が基板裏面103の面方向に沿ってアレイ状に配置されている。なお本実施形態では、電極形成領域10内に存在する電極の全てが突起電極11となっている。

【0030】

また、各突起電極11は、基板裏面103を有する最下層の樹脂絶縁層41に設けられたビア導体147を介して導体層51に電気的に接続されている。図2に示されるように、各突起電極11は、平面視円形状をなし、ビア導体147の上端における外径(80μm)、及び、ビア導体147の下端における外径(60μm)よりも大きい外径B1(本実施形態では1.05mm)を有している。さらに、突起電極11は、高さ方向に切断した断面を平面方向から見たときの外形線が円弧状をなす表面12を有している。また、突起電極11の表面12の曲率半径は、本実施形態では0.5mmに設定されている。そして、突起電極11は、基板裏面103からの突出量が最大となる最突出部13を有している。最突出部13は、突起電極11の中心軸C1上に位置するとともに、突起電極11に接するビア導体147の中心軸上に位置している。なお、最突出部13の基板裏面103からの突出量B2は、本実施形態では50μmに設定されている。

【0031】

なお、各突起電極11は、銅層、ニッケル層、パラジウム層及び金層によって構成されている。銅層は、銅箔73(図7参照)に対してエッチングによるパターンニングを行うことにより、形成された金属層である。ニッケル層は、銅層の上面を無電解ニッケルめっきで被覆することによって形成されためっき層である。パラジウム層は、ニッケル層の表面を無電解パラジウムめっきで被覆することによって形成されためっき層である。金層は、パラジウム層の表面を無電解金めっきで被覆することによって形成されためっき層である。

【0032】

図1に示されるように、各突起電極11上には、図示しないマザーボード(母基板)側の端子との電気的な接続に用いられる複数のピン21がはんだ部31を介して接合されている。即ち、本実施形態のコアレス配線基板101は、ピングリッドアレイ(PGA)タイプの半導体パッケージである。なお、各ピン21は、基板主面102側のはんだバンプ130よりも高融点のはんだを用いてはんだ付けされている。

【0033】

図2に示されるように、各ピン21は、コバールや42アロイ等の鉄ニッケル系合金または銅合金からなり、表面がニッケルめっき及び金めっきによって被覆されている。また、各ピン21は、断面円形状をなす軸部22と、同じく断面円形状をなす頭部23とを有している。本実施形態において、軸部22の外径A1は0.3mmに設定され、軸部22の長さは2.0mmに設定されている。一方、頭部23の外径A2は、軸部22の外径A1よりも大きく、本実施形態では0.7mmに設定されている。即ち、上記した突起電極11の外径B1(1.05mm)は、頭部23の外径A2よりも大きく設定されている。さらに、頭部23の上面24は球面となっている。頭部23の上面24の曲率半径は約0.4mmに設定されている。即ち、突起電極11の表面12の曲率半径(0.5mm)は、頭部23の上面24の曲率半径よりも大きくなっている。仮に、突起電極11の表面12の曲率半径を頭部23の上面24の曲率半径よりも大きくすると、突起電極11の最突出部13の突出量B2が大きくなるため、ピン21の接合に多量のはんだが必要になってしまう。また、頭部23の上面24から基板裏面103までの距離が長くなるため、はんだ部31を構成するはんだフィレット32を基板裏面103に接触させることが困難になる。そして、頭部23は、軸部22と頭部23との接続部分からの突出量が最大となる最突出部25を有している。なお、軸部22と頭部23との接続部分からの最突出部25の突出量は、本実施形態では0.1mmに設定されている。また、最突出部25は、ピン21の中心軸C2上に位置している。中心軸C2は、上記した突起電極11の中心軸C1と一致している。

【0034】

図2に示されるように、頭部23は、はんだ部31を介して突起電極11上に接合されている。そして、頭部23の上面24は、突起電極11の表面12から離間した状態で、表面12と向かい合うように配置されている。なお、突起電極11の表面12と頭部23の上面24との隙間の大きさ(即ち、突起電極11の最突出部13と頭部23の最突出部25との距離)は、本実施形態において0.05mmに設定されている。よって、突起電極11の表面12と頭部23の上面24との隙間の大きさは、最突出部13の基板裏面103からの突出量B2(40μm)、及び、軸部22と頭部23との接続部分からの最突出部25の突出量(0.1mm)よりも小さくなっている。また、はんだ部31は、突起電極11の上面12全体を覆うとともに、頭部23の上面24全体及び側面26全体を覆っている。さらに、はんだフィレット32は、基板裏面103に接触している。従って、はんだフィレット32(はんだ部31)の最大径D1は、突起電極11の外径B1(1.05mm)よりも大きく、本実施形態では1.07mmに設定されている。

【0035】

次に、コアレス配線基板101の製造方法について説明する。

【0036】

積層部準備工程では、コアレス配線基板101の中間製品を作製し、あらかじめ準備しておく。なお、コアレス配線基板101の中間製品は、コアレス配線基板101となるべき製品部を平面方向に沿って複数配列した構造を有している。コアレス配線基板101の中間製品は以下のように作製される。まず、ガラスエポキシ基板などの十分な強度を有する支持基板70を準備する(図3参照)。次に、支持基板70上に、エポキシ樹脂からなるシート状の絶縁樹脂基材を半硬化の状態で貼り付けて下地樹脂絶縁層71を形成することにより、支持基板70及び下地樹脂絶縁層71からなる基材69を得る(図3参照)。そして、基材69の片面(具体的には下地樹脂絶縁層71の上面)に、積層金属シート体72を配置する(図3参照)。ここでは、半硬化の状態の下地樹脂絶縁層71上に積層金属シート体72を配置することにより、以降の製造工程で積層金属シート体72が下地樹脂絶縁層71から剥れない程度の密着性が確保される。積層金属シート体72は、2枚の銅箔73,74を剥離可能な状態で密着させる。具体的には、金属めっき(例えば、クロムめっき)を介して各銅箔73,74を積層することで積層金属シート体72が形成されている。

【0037】

その後、積層金属シート体72上にシート状の絶縁樹脂基材40を積層し、真空圧着熱プレス機(図示略)を用いて真空下にて加熱加圧することにより、絶縁樹脂基材40を硬化させて第1層の樹脂絶縁層41を形成する(図3参照)。そして、図4に示されるように、レーザー加工を施すことによって樹脂絶縁層41の所定の位置にビア穴146を形成し、次いで各ビア穴146内のスミアを除去するデスミア処理を行う。その後、従来公知の手法に従って無電解銅めっき及び電解銅めっきを行うことにより、各ビア穴146内にビア導体147を形成する。さらに、従来公知の手法(例えばセミアディティブ法)によってエッチングを行うことにより、樹脂絶縁層41上に導体層51をパターン形成する(図5参照)。

【0038】

また、第2層〜第4層の樹脂絶縁層42〜44及び導体層51についても、上述した樹脂絶縁層41及び導体層51と同様の手法によって形成し、樹脂絶縁層41上に積層していく。以上の製造工程によって、支持基板70上に積層金属シート体72、樹脂絶縁層41〜44及び導体層51を積層してなる積層部80を形成する(図6参照)。なお図6に示されるように、積層金属シート体72上に位置する領域が、コアレス配線基板101の中間製品となるべき積層部80となる。

【0039】

次に、基材69を除去して銅箔73を露出させる。具体的に言うと、積層金属シート体72における2枚の銅箔73,74の界面で剥離して、積層部80を支持基板70から分離する(図7参照)。

【0040】

続く突起電極形成工程では、最下層の樹脂絶縁層41上に突起電極11を形成する。具体的には、積層部80(樹脂絶縁層41)の基板裏面103(下面)上にある銅箔73に対してエッチングによるパターニングを行うことにより、樹脂絶縁層41における基板裏面103上の領域に突起電極11を形成する(図8参照)。さらに、突起電極形成工程後の突起電極成形工程では、突起電極11に対してソフトエッチングを行う。その結果、中心軸C1上に最突出部13が位置する形状に突起電極11が成形される(図9参照)。

【0041】

その後、無電解ニッケルめっきを行い、突起電極11となる銅層(銅箔73の一部)の表面にニッケル層を形成する。さらに、無電解パラジウムめっきを行い、ニッケル層上にパラジウム層を形成する。そして、無電解金めっきを行い、パラジウム層上に金層を形成する。ここで、銅層の厚さ(最大厚さ)は50μm程度に設定され、ニッケル層、パラジウム層及び金層の厚さは、それぞれ0.01μm以上15μm以下に設定されている。なお、本実施形態のニッケル層、パラジウム層及び金層は、無電解めっき法によって形成されているが、電解めっき法、スパッタ法、CVD等の他の方法により形成することも可能である。

【0042】

続くはんだ付け工程では、複数のピン21をコアレス配線基板101となる積層部80よりも下方に配置した状態で、ピン21の頭部23を突起電極11にはんだ付けする。詳述すると、まず、突起電極11に対してはんだペースト30を印刷する(図10参照)。また、各ピン21の位置決めに用いられる位置決め治具151を準備する(図10参照)。なお、位置決め治具151には、上方に向けて開口する複数のピン挿入孔152が、ピン21と等しいピッチで格子状に配列されている。本実施形態のピン挿入孔152は、開口部よりも深い部分が等断面形状に形成されている。一方、ピン挿入孔152の開口部は、面取りが施されており、開口部より深い部分よりも断面積が大きく形成されている。また、これらのピン挿入孔152の開口部は、ピン21の頭部23を収容可能な大きさの穴径を有している。なお、位置決め治具151は、機械的強度の高い金属材料によって形成されることが好ましく、例えば、タングステン・カーバイド(WC)とコバルト(Co)などからなる超硬合金を用いて形成される。

【0043】

次に、ピン21の軸部22をピン挿入孔152に挿入した後、複数のピン21が挿入された位置決め治具151を積層部80の下方に配置する。そして、各突起電極11にピン21の頭部23を当接させた状態ではんだペースト30を加熱溶融することにより、複数のピン21が複数の突起電極11に対して同時にはんだ付けされる(図11参照)。なお、この時点で、コアレス配線基板101の中間製品が完成する。

【0044】

続く分離工程では、従来周知の切断装置などを用いてコアレス配線基板101の中間製品を分割する。その結果、製品部同士が分割され、個々の製品であるコアレス配線基板101が多数個同時に得られる(図1参照)。

【0045】

その後、ICチップ搭載工程を実施する。具体的に言うと、まず、コアレス配線基板101のICチップ搭載領域133にICチップ131を載置する。このとき、ICチップ131の底面側に配置されたはんだバンプ130を、コアレス配線基板101側に配置された端子パッド52上に載置するようにする(図12参照)。そして、230℃〜260℃程度の温度に加熱して各はんだバンプ130をリフローすることにより、端子パッド52が接続端子132に対してフリップチップ接続され、コアレス配線基板101にICチップ131が搭載される。さらに、コアレス配線基板101の基板主面102とICチップ131との隙間にアンダーフィル134を充填して硬化処理を行い、隙間を封止する。

【0046】

従って、本実施形態によれば以下の効果を得ることができる。

【0047】

(1)本実施形態のコアレス配線基板101では、電極形成領域10に存在する電極の全てが、基板裏面103からの突出量B2が最大となる最突出部13を備えた突起電極11となっている。即ち、各突起電極11の表面12は凸状をなしているため、はんだ部31を介してピン21を接合した際に、はんだ部31内における突起電極11の表面12付近にフラックスが溜まりにくくなる。その結果、気化したフラックスがはんだ部31内に溜まることに起因したボイドの発生が防止されるため、突起電極11とピン21との接合強度の低下を防止することができる。即ち、ピン21との接合に適した突起電極11を備えることにより、コアレス配線基板101の信頼性を向上させることが可能となる。

【0048】

(2)本実施形態では、突起電極11の外径B1がピン21の頭部23の外径A2よりも大きく設定されているため、突起電極11と頭部23とをはんだ部31を介して接触させやすくなる。その結果、突起電極11とピン21とをより確実に接合させることができるため、コアレス配線基板101の信頼性をよりいっそう向上させることができる。しかも、最突出部13は突起電極11の中心軸C1上に位置しているため、最突出部13と向かい合うようにピン21の頭部23を配置するだけで、突起電極11の中心軸C1とピン21の中心軸C2とを容易に一致させることができる。よって、ピン21を正確に位置決めすることができる。

【0049】

なお、本実施形態を以下のように変更してもよい。

【0050】

・上記実施形態の突起電極形成工程では、銅箔73に対してエッチングによるパターンニングを行うことにより、最下層の樹脂絶縁層41上に突起電極11を形成していた(図7,図8参照)。しかし、他の方法を用いて突起電極11を形成するようにしてもよい。

【0051】

例えば、エッチングによって銅箔73を完全に除去した後、レジスト形成工程、開口部形成工程及びめっき形成工程を順番に行うことにより、突起電極11を形成してもよい。詳述すると、銅箔73を除去した後、レジスト形成工程を行い、基板裏面103を有する最下層の樹脂絶縁層41上にドライフィルムをラミネートして、めっきレジストを形成する。続く開口部形成工程では、めっきレジストに対して、内径がピン21の頭部23の外径A2よりも大きく設定された開口部を形成する。開口部を形成する方法としては、めっきレジストに対するドリル加工を行って開口部を形成する方法、めっきレジストに対するレーザー加工を行って開口部を形成する方法、感光及び現像を行って開口部を形成する方法、打ち抜き金型を用いてめっきレジストを打ち抜くことにより、めっきレジストに開口部を形成する方法などが挙げられる。続くめっき形成工程では、開口部の内面に対してめっきを行うことにより、開口部に突起電極11を形成する。具体的に言うと、無電解銅めっき及び電解銅めっきを行い、開口部の内面、及び、基板裏面103に露出したビア導体147の下端面に対して突起電極11を形成する。その後、めっきレジストを剥離する。さらに、突起電極成形工程において突起電極11に対してエッチングを行い、中心軸C1上に最突出部13が位置する形状に突起電極11を成形する。

【0052】

なお、上記した突起電極の形成方法は、コア基板の片面または両面にビルドアップ層を有するビルドアップ多層配線基板にも好適に用いることができる。この場合、ビルドアップ層は、層間絶縁層を形成する層間絶縁層形成工程と、層間絶縁層上に導体層を形成する導体層形成工程とを交互に行うことによって形成される。また、突起電極は、ビルドアップ層の表面(下面)に対して、レジスト形成工程、開口部形成工程及びめっき形成工程を順番に行うことによって形成される。即ち、ビルドアップ層の表面には上記実施形態のような銅箔73が存在しないため、レジスト形成工程、開口部形成工程及びめっき形成工程を経て突起電極を形成することが好適である。

【0053】

・上記実施形態の突起電極成形工程では、突起電極11に対してソフトエッチングを行うことにより、中心軸C1上に最突出部13が位置する形状に突起電極11を成形するようになっていた。

【0054】

しかし、突起電極成形工程において、突起電極11を他の方法を用いて成形するようにしてもよい。例えば、突起電極11の基端部分(基板裏面103側の部分)を通常のめっき条件で形成した後、通常とは異なるめっき条件に変更した状態で突起電極11の先端部分(ピン21側の部分)を形成することにより、突起電極11を成形してもよい。ここで、めっき条件を変更する方法としては、例えば、めっき浴におけるめっきの撹拌量を減らすことや、めっきに含まれる光沢剤の分量を増加または減少させることや、めっきに弱酸(例えば、次亜塩素酸ナトリウムなど)を添加することなどが挙げられる。即ち、めっき条件を、ピットやザラツキなどのはんだ不良が発生する条件に敢えて変更することが考えられる。

【0055】

また、突起電極成形工程において、突起電極11を機械的な方法を用いて成形するようにしても勿論よい。例えば、治具を用いて複数の突起電極11の表面12をプレスすることにより、突起電極11を成形してもよい。また、サンドブラストや研磨によって突起電極11を成形してもよい。

【0056】

・上記実施形態において、突起電極成形工程後かつはんだ付け工程前に、突起電極11の表面12を粗化させる粗化工程を行ってもよい。このようにすれば、はんだ部31を介して突起電極11上にピン21の頭部23を接合した際に、突起電極11とはんだ部31との密着強度が高くなる。その結果、突起電極11とピン21との接合強度の低下をより確実に防止できるため、コアレス配線基板101の信頼性がよりいっそう向上する。

【0057】

・上記実施形態において、コアレス配線基板101を構成する最下層の樹脂絶縁層41の下面(基板裏面103)を、ソルダーレジスト(裏面側ソルダーレジスト)によって覆ってもよい。この場合、ソルダーレジストには、突起電極11全体、はんだ部31全体及びピン21を露出させる開口部(裏面側開口部)が形成されるようになる。同様に、コアレス配線基板101を構成する最上層の樹脂絶縁層44の上面(基板主面102)を、ソルダーレジスト(主面側ソルダーレジスト)によって覆ってもよい。この場合、ソルダーレジストには、端子パッド52の少なくとも一部を露出させる開口部(主面側開口部)が形成されるようになる。

【0058】

次に、前述した実施形態によって把握される技術的思想を以下に列挙する。

【0059】

(1)上記手段1において、前記頭部の前記上面の最突出部は、前記ピンの中心軸上に位置していることを特徴とする配線基板。

【0060】

(2)上記手段1において、前記頭部の前記上面の曲率半径は、前記突起電極の表面の曲率半径よりも小さいことを特徴とする配線基板。

【0061】

(3)上記手段1において、前記頭部の上面と前記突起電極の表面とが互いに離間しており、前記頭部の上面と前記突起電極の表面との隙間の大きさは、前記突起電極に設けられた最突出部の前記基板裏面からの突出量、及び、前記頭部に設けられた最突出部の前記軸部との接続部分からの突出量よりも小さいことを特徴とする配線基板。

【0062】

(4)上記手段1において、前記配線基板は、基板主面及び基板裏面を有するとともに複数の層間絶縁層を積層してなる積層部を有し、前記層間絶縁層に設けられたビア導体が前記基板主面側に行くに従って拡径し、前記突起電極の外径は、前記ビア導体の前記基板主面側における外径よりも大きく設定されていることを特徴とする配線基板。従って、技術的思想(4)によれば、ビア導体のピン側における外径が小さくなるため、ピンを引っ張る方向に応力が加わった際に、ビア導体がピンに引っ張られて抜けることを防止できる。

【0063】

(5)上記手段1において、前記配線基板は、コア基板を有さず、基板主面及び基板裏面を有するとともに複数の層間絶縁層を積層してなる積層部を有し、前記層間絶縁層に設けられたビア導体が前記基板主面側に行くに従って拡径し、前記基板主面上の半導体集積回路素子搭載領域内に配置された電極が、半導体集積回路素子とのフリップチップ接続に用いられる端子パッドとなり、前記基板裏面上の前記電極形成領域内に配置された前記突起電極上に、前記ピンが前記はんだ部を介して接合されるコアレス配線基板であることを特徴とする配線基板。

【0064】

(6)上記手段2において、前記突起電極形成工程は、前記基板裏面を有する最下層の前記層間絶縁層上にめっきレジストを形成するレジスト形成工程と、前記めっきレジストに、内径が前記頭部の外径よりも大きく設定された開口部を形成する開口部形成工程と、前記開口部の内面に対してめっきを行うことにより、前記開口部に前記突起電極を形成するめっき形成工程とを含むことを特徴とする配線基板の製造方法。

【0065】

(7)上記手段2において、前記はんだ付け工程では、前記複数のピンの前記軸部を位置決め治具のピン挿入孔に挿入することにより、前記複数のピンを前記積層部よりも下方に配置することを特徴とする配線基板の製造方法。

【符号の説明】

【0066】

10…電極形成領域

11…突起電極

12…突起電極の表面

13…最突出部

21…ピン

22…軸部

23…頭部

24…頭部の上面

31…はんだ部

32…はんだフィレット

41,42,43,44…層間絶縁層としての樹脂絶縁層

80…積層部

101…配線基板としてのコアレス配線基板

103…基板裏面

A2…頭部の外径

B1…突起電極の外径

B2…突出量

C1…突起電極の中心軸

C2…ピンの中心軸

D1…はんだフィレットの最大径

【技術分野】

【0001】

本発明は、基板裏面上の電極形成領域内に複数の突起電極が配置され、複数の突起電極上に母基板搭載用の複数のピンがはんだ部を介して接合された配線基板及びその製造方法に関するものである。

【背景技術】

【0002】

コンピュータのマイクロプロセッサ等として使用される半導体集積回路素子(ICチップ)は、近年ますます高速化、高機能化しており、これに付随して端子数が増え、端子間ピッチも狭くなる傾向にある。一般的にICチップの底面には多数の端子が密集してアレイ状に配置されており、このような端子群はマザーボード(母基板)側の端子群に対してフリップチップの形態で接続される。但し、ICチップ側の端子群とマザーボード側の端子群とでは端子間ピッチに大きな差があることから、ICチップをマザーボード上に直接的に接続することは困難である。そのため、通常は、ICチップを搭載してなる配線基板(いわゆる半導体パッケージ)を作製し、その配線基板をマザーボード上に搭載するという手法が採用される。

【0003】

ここで、配線基板とマザーボードとの電気的な接続を図るための構造としては、配線基板の基板裏面上に配置された複数のパッド(突起電極)上にはんだバンプを形成した、いわゆるボールグリッドアレイ(BGA)が提案されている。また、配線基板とマザーボードとの電気的な接続を図るための他の構造として、複数のパッド上にはんだ部を介してピンを接合した、いわゆるピングリッドアレイ(PGA)も提案されている(例えば特許文献1参照)。以下、上記の配線基板におけるピンの接合方法について簡単に説明する。まず、基板裏面上に複数のパッドが形成された配線基板を準備する。また、複数のピンを専用の位置決め治具のピン挿入孔にセットした後、配線基板の下方に配置する。そして、各ピンの頭部を各パッドにはんだ付けすることにより、各ピンが配線基板に接合される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第3378550号公報(図2など)

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、一般的なパッドとしては、特許文献1に記載の平板状をなす「ピン接合部111」に加えて、表面に凹みを有するものも提案されている。なお、パッド上には、通常フラックスが印刷塗布されており、フラックスは、ピンをパッドにはんだ付けする際(リフロー時)に気化して、外部に放出されるようになっている。

【0006】

ところが、パッドが平板状であったり凹みを有する形状であったりすると、フラックスは、外部に放出されずにはんだ部内に溜まりやすくなる。この場合、はんだ部内にボイドが発生してしまい、それに起因してパッドとピンとの接合強度が低下する可能性がある。ゆえに、製造される配線基板が不良品となるため、配線基板の信頼性が低下するおそれがある。

【0007】

本発明は上記の課題に鑑みてなされたものであり、その第1の目的は、ピンとの接合に適した突起電極を備えることにより、信頼性を向上させることが可能な配線基板を提供することにある。また、第2の目的は、上記の優れた配線基板を得るのに好適な製造方法を提供することにある。

【課題を解決するための手段】

【0008】

上記課題を解決するための手段(手段1)としては、基板裏面上の電極形成領域内に複数の突起電極が配置され、前記複数の突起電極上に母基板搭載用の複数のピンがはんだ部を介して接合された配線基板であって、前記複数のピンは、軸部と、前記軸部よりも外径が大きい頭部とを有し、前記複数の突起電極は、外径が前記頭部の外径よりも大きく設定されるとともに、前記基板裏面からの突出量が最大となる最突出部が前記突起電極の中心軸上に位置しており、前記突起電極の中心軸と前記ピンの中心軸とが一致するように、前記頭部が前記はんだ部を介して前記突起電極上に接合されていることを特徴とする配線基板がある。

【0009】

従って、手段1の配線基板によると、複数の突起電極が、基板裏面からの突出量が最大となる最突出部を有している。即ち、各突起電極の表面は凸状をなしているため、はんだ部を介してピンを接合した際に、はんだ部内における突起電極の表面付近にフラックスが溜まりにくくなる。その結果、気化したフラックスがはんだ部内に溜まることに起因したボイドの発生が防止されるため、突起電極とピンとの接合強度の低下を防止することができる。即ち、ピンとの接合に適した突起電極を備えることにより、配線基板の信頼性を向上させることが可能となる。

【0010】

また、突起電極の外径がピンの頭部の外径よりも大きく設定されているため、突起電極と頭部とをはんだ部を介して接触させやすくなる。その結果、突起電極とピンとをより確実に接合させることができるため、配線基板の信頼性をよりいっそう向上させることができる。しかも、最突出部は突起電極の中心軸上に位置しているため、最突出部と向かい合うようにピンの頭部を配置するだけで、突起電極の中心軸とピンの中心軸とを容易に一致させることができる。よって、ピンを正確に位置決めすることができる。

【0011】

上記配線基板を形成する材料は特に限定されず任意であるが、例えば、樹脂基板などが好適である。好適な樹脂基板としては、EP樹脂(エポキシ樹脂)、PI樹脂(ポリイミド樹脂)、BT樹脂(ビスマレイミド−トリアジン樹脂)、PPE樹脂(ポリフェニレンエーテル樹脂)等からなる基板が挙げられる。そのほか、これらの樹脂とガラス繊維(ガラス織布やガラス不織布)との複合材料からなる基板を使用してもよい。その具体例としては、ガラス−BT複合基板、高Tgガラス−エポキシ複合基板(FR−4、FR−5等)等の高耐熱性積層板などがある。また、これらの樹脂とポリアミド繊維等の有機繊維との複合材料からなる基板を使用してもよい。あるいは、連続多孔質PTFE等の三次元網目状フッ素系樹脂基材にエポキシ樹脂などの熱硬化性樹脂を含浸させた樹脂−樹脂複合材料からなる基板等を使用してもよい。他の材料として、例えば各種のセラミックなどを選択することもできる。なお、かかる配線基板の構造としては特に限定されないが、例えばコア基板の片面または両面にビルドアップ層を有するビルドアップ多層配線基板や、コア基板を有さないコアレス配線基板などを挙げることができる。

【0012】

上記基板裏面上の電極形成領域の位置及び数は特に限定されず任意であるが、例えばいわゆる多数個取り基板の場合には配線基板の取り数に相当する数だけ電極形成領域が存在している。電極形成領域は基板裏面のみに存在していてもよいが、基板主面及び基板裏面の両方に存在していてもよい。

【0013】

また、複数の突起電極は、導電性の金属材料などによって形成することが可能である。突起電極を構成する金属材料としては、例えば銅、銀、鉄、コバルト、ニッケルなどが挙げられる。特に、突起電極は、導電性が高く安価な銅からなることが好ましい。また、突起電極は、めっきによって形成されることがよい。このようにすれば、突起電極を高精度かつ均一に形成することができる。仮に、突起電極を金属ペーストのリフローによって形成すると、突起電極を高精度かつ均一に形成することが困難になるため、個々の突起電極の高さにバラツキが生じてしまうおそれがある。

【0014】

さらに、複数のピンは、軸部と、軸部よりも外径が大きい頭部とを有している。ピンの形状は特に限定されず任意であるが、例えば、ピンは、頭部の上面が球面となっていることが好ましい。このようにすれば、はんだ部を介して突起電極上にピンを接合した際に、はんだ部内における頭部の上面付近にフラックスが溜まりにくくなる。その結果、気化したフラックスに起因するボイドがよりいっそう発生しにくくなるため、突起電極とピンとの接合強度の低下をより確実に防止することができる。

【0015】

なお、複数の突起電極及び複数のピンは、はんだ部を介して互いに接合される。はんだ部(及びはんだフィレット)に使用されるはんだ材料としては特に限定されないが、90Pb−10Sn、95Pb−5Sn、40Pb−60SnなどのPb−Sn系はんだ、Sn−Sb系はんだ、Sn−Ag系はんだ、Sn−Ag−Cu系はんだ、Au−Ge系はんだ、Au−Sn系はんだ、Au−Si系はんだなどが挙げられる。特に、はんだ部は鉛フリーはんだからなることが好ましい。このようにすれば、はんだ部に鉛が含まれないため、配線基板の環境への負荷を低くすることができる。また、鉛フリーはんだは、鉛を含有するはんだよりも濡れ性が悪く、ボイドの発生量が多くなる傾向にあるため、突起電極に最突出部を設けてフラックスを放出しやすくすれば、ボイドの発生をより効果的に防止できる。ここで、鉛フリーはんだとしては、Sn−Sb系はんだ、Sn−Ag系はんだ、Sn−Ag−Cu系はんだ、Au−Ge系はんだ、Au−Sn系はんだ、Au−Si系はんだなどが挙げられる。

【0016】

なお、ピンの頭部の上面と突起電極の表面とは互いに離間していることが好ましい。このようにすれば、頭部の上面と突起電極の表面との間に対してはんだ部を確実に充填することができる。その結果、頭部とはんだ部との接触面積や、突起電極とはんだ部との接触面積が大きくなるため、突起電極とピンとの接合強度を向上させることができる。また、はんだ部を構成するはんだフィレットの最大径は、突起電極の外径よりも大きく設定されることが好ましい。このようにした場合、はんだ部が突起電極の表面全体に接触するようになるため、突起電極とはんだ部との接合強度が向上する。

【0017】

上記課題を解決するための別の手段(手段2)としては、上記手段1のいずれか1項に記載の配線基板を製造する方法であって、複数の層間絶縁層を積層してなる積層部を準備する積層部準備工程と、前記基板裏面を有する最下層の前記層間絶縁層上に前記突起電極を形成する突起電極形成工程と、前記複数のピンを前記積層部よりも下方に配置した状態で、前記頭部を前記突起電極にはんだ付けするはんだ付け工程とを含むことを特徴とする配線基板の製造方法がある。

【0018】

従って、手段2の配線基板の製造方法によれば、最突出部を有する突起電極を形成すれば、はんだ付け工程を行ってはんだ部を介してピンの頭部を突起電極にはんだ付けした際に、はんだ部内における突起電極の表面付近にフラックスが溜まりにくくなる。その結果、気化したフラックスがはんだ部内に溜まることに起因したボイドの発生が防止されるため、突起電極とピンとの接合強度の低下を防止することができる。即ち、ピンとの接合に適した突起電極を備える配線基板を製造できるため、配線基板の信頼性を向上させることが可能となる。

【0019】

以下、手段2にかかる配線基板の製造方法について説明する。

【0020】

積層部準備工程では、複数の層間絶縁層を積層してなる積層部を準備する。層間絶縁層は、絶縁性、耐熱性、耐湿性等を考慮して適宜選択することができる。層間絶縁層の形成材料の好適例としては、エポキシ樹脂、フェノール樹脂、ウレタン樹脂、シリコーン樹脂、ポリイミド樹脂などの熱硬化性樹脂、ポリカーボネート樹脂、アクリル樹脂、ポリアセタール樹脂、ポリプロピレン樹脂などの熱可塑性樹脂等が挙げられる。そのほか、これらの樹脂とガラス繊維(ガラス織布やガラス不織布)やポリアミド繊維等の有機繊維との複合材料、あるいは、連続多孔質PTFE等の三次元網目状フッ素系樹脂基材にエポキシ樹脂などの熱硬化性樹脂を含浸させた樹脂−樹脂複合材料等を使用してもよい。なお、層間絶縁層には、層間接続のためのビア導体を形成するために、あらかじめビア穴が形成されていてもよい。

【0021】

次に、突起電極形成工程を行い、基板裏面を有する最下層の層間絶縁層上に突起電極を形成する。さらに、はんだ付け工程を行い、複数のピンを積層部よりも下方に配置した状態で、頭部を突起電極にはんだ付けする。以上のプロセスを経て、配線基板が製造される。

【0022】

なお、突起電極形成工程後かつはんだ付け工程前に、突起電極に対してエッチングを行うことにより、中心軸上に最突出部が位置する形状に突起電極を成形する突起電極成形工程を行うことが好ましい。このようにした場合、突起電極成形工程において突起電極に対してエッチングを行っているため、最突出部を高精度に形成することが可能となる。しかも、突起電極成形工程において最突出部を突起電極の中心軸上に位置させているため、最突出部と向かい合うようにピンの頭部を配置するだけで、突起電極の中心軸とピンの中心軸とを容易に一致させることができる。よって、ピンを正確に位置決めすることができる。

【図面の簡単な説明】

【0023】

【図1】本実施形態におけるコアレス配線基板の構成を示す概略断面図。

【図2】コアレス配線基板の要部断面図。

【図3】コアレス配線基板の製造方法を示す説明図。

【図4】コアレス配線基板の製造方法を示す説明図。

【図5】コアレス配線基板の製造方法を示す説明図。

【図6】コアレス配線基板の製造方法を示す説明図。

【図7】コアレス配線基板の製造方法を示す説明図。

【図8】コアレス配線基板の製造方法を示す説明図。

【図9】コアレス配線基板の製造方法を示す説明図。

【図10】コアレス配線基板の製造方法を示す説明図。

【図11】コアレス配線基板の製造方法を示す説明図。

【図12】コアレス配線基板の製造方法を示す説明図。

【発明を実施するための形態】

【0024】

以下、本発明を具体化した一実施形態を図面に基づき詳細に説明する。

【0025】

図1は、本実施形態のコアレス配線基板101(配線基板)を示す概略断面図である。コアレス配線基板101は、コア基板を有さず、エポキシ樹脂からなる4層の樹脂絶縁層41,42,43,44と銅からなる導体層51とを交互に積層した構造を有する配線基板である。樹脂絶縁層41〜44は、同一の厚さ及び材料からなる層間絶縁層である。

【0026】

さらに、各樹脂絶縁層41〜44には、それぞれビア穴146及びビア導体147が設けられている。各ビア穴146は、逆円錐台形状をなし、各樹脂絶縁層41〜44に対してYAGレーザーまたは炭酸ガスレーザーを用いた穴あけ加工を施すことにより形成される。各ビア導体147は、同一方向(図1では上方向)に拡径した導体であって、各導体層51を相互に電気的に接続している。なお、各ビア導体147の上端における外径は50μm以上120μm以下(本実施形態では80μm)に設定され、各ビア導体147の下端における外径は30μm以上100μm以下(本実施形態では60μm)に設定されている。

【0027】

図1に示されるように、コアレス配線基板101の基板主面102上(第4層の樹脂絶縁層44の表面上)には、ビア導体147を介して導体層51に電気的に接続される端子パッド52がアレイ状に形成されている。また、各端子パッド52は、はんだバンプ130を介して、矩形平板状をなすICチップ131の底面に配置された接続端子132に接続されるようになっている。即ち、はんだバンプ130は、ICチップ131の接続端子132とのフリップチップ接続に用いられる、いわゆるC4用のバンプである。なお、各端子パッド52からなる領域は、ICチップ131を搭載可能なICチップ搭載領域133である。ICチップ搭載領域133は、コアレス配線基板101の基板主面102に設定されている。

【0028】

そして、基板主面102とICチップ131との隙間には、アンダーフィル134が充填されている。その結果、コアレス配線基板101とICチップ131とが、隙間が封止された状態で互いに固定される。なお、本実施形態のアンダーフィル134は、熱膨張係数が20〜60ppm/℃程度(具体的には34ppm/℃)のエポキシ樹脂からなる。

【0029】

一方、図1に示されるように、コアレス配線基板101の基板裏面103上(第1層の樹脂絶縁層41の下面上)には、平面視矩形状の電極形成領域10が設定されている。そして、電極形成領域10内には、複数の突起電極11が基板裏面103の面方向に沿ってアレイ状に配置されている。なお本実施形態では、電極形成領域10内に存在する電極の全てが突起電極11となっている。

【0030】

また、各突起電極11は、基板裏面103を有する最下層の樹脂絶縁層41に設けられたビア導体147を介して導体層51に電気的に接続されている。図2に示されるように、各突起電極11は、平面視円形状をなし、ビア導体147の上端における外径(80μm)、及び、ビア導体147の下端における外径(60μm)よりも大きい外径B1(本実施形態では1.05mm)を有している。さらに、突起電極11は、高さ方向に切断した断面を平面方向から見たときの外形線が円弧状をなす表面12を有している。また、突起電極11の表面12の曲率半径は、本実施形態では0.5mmに設定されている。そして、突起電極11は、基板裏面103からの突出量が最大となる最突出部13を有している。最突出部13は、突起電極11の中心軸C1上に位置するとともに、突起電極11に接するビア導体147の中心軸上に位置している。なお、最突出部13の基板裏面103からの突出量B2は、本実施形態では50μmに設定されている。

【0031】

なお、各突起電極11は、銅層、ニッケル層、パラジウム層及び金層によって構成されている。銅層は、銅箔73(図7参照)に対してエッチングによるパターンニングを行うことにより、形成された金属層である。ニッケル層は、銅層の上面を無電解ニッケルめっきで被覆することによって形成されためっき層である。パラジウム層は、ニッケル層の表面を無電解パラジウムめっきで被覆することによって形成されためっき層である。金層は、パラジウム層の表面を無電解金めっきで被覆することによって形成されためっき層である。

【0032】

図1に示されるように、各突起電極11上には、図示しないマザーボード(母基板)側の端子との電気的な接続に用いられる複数のピン21がはんだ部31を介して接合されている。即ち、本実施形態のコアレス配線基板101は、ピングリッドアレイ(PGA)タイプの半導体パッケージである。なお、各ピン21は、基板主面102側のはんだバンプ130よりも高融点のはんだを用いてはんだ付けされている。

【0033】

図2に示されるように、各ピン21は、コバールや42アロイ等の鉄ニッケル系合金または銅合金からなり、表面がニッケルめっき及び金めっきによって被覆されている。また、各ピン21は、断面円形状をなす軸部22と、同じく断面円形状をなす頭部23とを有している。本実施形態において、軸部22の外径A1は0.3mmに設定され、軸部22の長さは2.0mmに設定されている。一方、頭部23の外径A2は、軸部22の外径A1よりも大きく、本実施形態では0.7mmに設定されている。即ち、上記した突起電極11の外径B1(1.05mm)は、頭部23の外径A2よりも大きく設定されている。さらに、頭部23の上面24は球面となっている。頭部23の上面24の曲率半径は約0.4mmに設定されている。即ち、突起電極11の表面12の曲率半径(0.5mm)は、頭部23の上面24の曲率半径よりも大きくなっている。仮に、突起電極11の表面12の曲率半径を頭部23の上面24の曲率半径よりも大きくすると、突起電極11の最突出部13の突出量B2が大きくなるため、ピン21の接合に多量のはんだが必要になってしまう。また、頭部23の上面24から基板裏面103までの距離が長くなるため、はんだ部31を構成するはんだフィレット32を基板裏面103に接触させることが困難になる。そして、頭部23は、軸部22と頭部23との接続部分からの突出量が最大となる最突出部25を有している。なお、軸部22と頭部23との接続部分からの最突出部25の突出量は、本実施形態では0.1mmに設定されている。また、最突出部25は、ピン21の中心軸C2上に位置している。中心軸C2は、上記した突起電極11の中心軸C1と一致している。

【0034】

図2に示されるように、頭部23は、はんだ部31を介して突起電極11上に接合されている。そして、頭部23の上面24は、突起電極11の表面12から離間した状態で、表面12と向かい合うように配置されている。なお、突起電極11の表面12と頭部23の上面24との隙間の大きさ(即ち、突起電極11の最突出部13と頭部23の最突出部25との距離)は、本実施形態において0.05mmに設定されている。よって、突起電極11の表面12と頭部23の上面24との隙間の大きさは、最突出部13の基板裏面103からの突出量B2(40μm)、及び、軸部22と頭部23との接続部分からの最突出部25の突出量(0.1mm)よりも小さくなっている。また、はんだ部31は、突起電極11の上面12全体を覆うとともに、頭部23の上面24全体及び側面26全体を覆っている。さらに、はんだフィレット32は、基板裏面103に接触している。従って、はんだフィレット32(はんだ部31)の最大径D1は、突起電極11の外径B1(1.05mm)よりも大きく、本実施形態では1.07mmに設定されている。

【0035】

次に、コアレス配線基板101の製造方法について説明する。

【0036】

積層部準備工程では、コアレス配線基板101の中間製品を作製し、あらかじめ準備しておく。なお、コアレス配線基板101の中間製品は、コアレス配線基板101となるべき製品部を平面方向に沿って複数配列した構造を有している。コアレス配線基板101の中間製品は以下のように作製される。まず、ガラスエポキシ基板などの十分な強度を有する支持基板70を準備する(図3参照)。次に、支持基板70上に、エポキシ樹脂からなるシート状の絶縁樹脂基材を半硬化の状態で貼り付けて下地樹脂絶縁層71を形成することにより、支持基板70及び下地樹脂絶縁層71からなる基材69を得る(図3参照)。そして、基材69の片面(具体的には下地樹脂絶縁層71の上面)に、積層金属シート体72を配置する(図3参照)。ここでは、半硬化の状態の下地樹脂絶縁層71上に積層金属シート体72を配置することにより、以降の製造工程で積層金属シート体72が下地樹脂絶縁層71から剥れない程度の密着性が確保される。積層金属シート体72は、2枚の銅箔73,74を剥離可能な状態で密着させる。具体的には、金属めっき(例えば、クロムめっき)を介して各銅箔73,74を積層することで積層金属シート体72が形成されている。

【0037】

その後、積層金属シート体72上にシート状の絶縁樹脂基材40を積層し、真空圧着熱プレス機(図示略)を用いて真空下にて加熱加圧することにより、絶縁樹脂基材40を硬化させて第1層の樹脂絶縁層41を形成する(図3参照)。そして、図4に示されるように、レーザー加工を施すことによって樹脂絶縁層41の所定の位置にビア穴146を形成し、次いで各ビア穴146内のスミアを除去するデスミア処理を行う。その後、従来公知の手法に従って無電解銅めっき及び電解銅めっきを行うことにより、各ビア穴146内にビア導体147を形成する。さらに、従来公知の手法(例えばセミアディティブ法)によってエッチングを行うことにより、樹脂絶縁層41上に導体層51をパターン形成する(図5参照)。

【0038】

また、第2層〜第4層の樹脂絶縁層42〜44及び導体層51についても、上述した樹脂絶縁層41及び導体層51と同様の手法によって形成し、樹脂絶縁層41上に積層していく。以上の製造工程によって、支持基板70上に積層金属シート体72、樹脂絶縁層41〜44及び導体層51を積層してなる積層部80を形成する(図6参照)。なお図6に示されるように、積層金属シート体72上に位置する領域が、コアレス配線基板101の中間製品となるべき積層部80となる。

【0039】

次に、基材69を除去して銅箔73を露出させる。具体的に言うと、積層金属シート体72における2枚の銅箔73,74の界面で剥離して、積層部80を支持基板70から分離する(図7参照)。

【0040】

続く突起電極形成工程では、最下層の樹脂絶縁層41上に突起電極11を形成する。具体的には、積層部80(樹脂絶縁層41)の基板裏面103(下面)上にある銅箔73に対してエッチングによるパターニングを行うことにより、樹脂絶縁層41における基板裏面103上の領域に突起電極11を形成する(図8参照)。さらに、突起電極形成工程後の突起電極成形工程では、突起電極11に対してソフトエッチングを行う。その結果、中心軸C1上に最突出部13が位置する形状に突起電極11が成形される(図9参照)。

【0041】

その後、無電解ニッケルめっきを行い、突起電極11となる銅層(銅箔73の一部)の表面にニッケル層を形成する。さらに、無電解パラジウムめっきを行い、ニッケル層上にパラジウム層を形成する。そして、無電解金めっきを行い、パラジウム層上に金層を形成する。ここで、銅層の厚さ(最大厚さ)は50μm程度に設定され、ニッケル層、パラジウム層及び金層の厚さは、それぞれ0.01μm以上15μm以下に設定されている。なお、本実施形態のニッケル層、パラジウム層及び金層は、無電解めっき法によって形成されているが、電解めっき法、スパッタ法、CVD等の他の方法により形成することも可能である。

【0042】

続くはんだ付け工程では、複数のピン21をコアレス配線基板101となる積層部80よりも下方に配置した状態で、ピン21の頭部23を突起電極11にはんだ付けする。詳述すると、まず、突起電極11に対してはんだペースト30を印刷する(図10参照)。また、各ピン21の位置決めに用いられる位置決め治具151を準備する(図10参照)。なお、位置決め治具151には、上方に向けて開口する複数のピン挿入孔152が、ピン21と等しいピッチで格子状に配列されている。本実施形態のピン挿入孔152は、開口部よりも深い部分が等断面形状に形成されている。一方、ピン挿入孔152の開口部は、面取りが施されており、開口部より深い部分よりも断面積が大きく形成されている。また、これらのピン挿入孔152の開口部は、ピン21の頭部23を収容可能な大きさの穴径を有している。なお、位置決め治具151は、機械的強度の高い金属材料によって形成されることが好ましく、例えば、タングステン・カーバイド(WC)とコバルト(Co)などからなる超硬合金を用いて形成される。

【0043】

次に、ピン21の軸部22をピン挿入孔152に挿入した後、複数のピン21が挿入された位置決め治具151を積層部80の下方に配置する。そして、各突起電極11にピン21の頭部23を当接させた状態ではんだペースト30を加熱溶融することにより、複数のピン21が複数の突起電極11に対して同時にはんだ付けされる(図11参照)。なお、この時点で、コアレス配線基板101の中間製品が完成する。

【0044】

続く分離工程では、従来周知の切断装置などを用いてコアレス配線基板101の中間製品を分割する。その結果、製品部同士が分割され、個々の製品であるコアレス配線基板101が多数個同時に得られる(図1参照)。

【0045】

その後、ICチップ搭載工程を実施する。具体的に言うと、まず、コアレス配線基板101のICチップ搭載領域133にICチップ131を載置する。このとき、ICチップ131の底面側に配置されたはんだバンプ130を、コアレス配線基板101側に配置された端子パッド52上に載置するようにする(図12参照)。そして、230℃〜260℃程度の温度に加熱して各はんだバンプ130をリフローすることにより、端子パッド52が接続端子132に対してフリップチップ接続され、コアレス配線基板101にICチップ131が搭載される。さらに、コアレス配線基板101の基板主面102とICチップ131との隙間にアンダーフィル134を充填して硬化処理を行い、隙間を封止する。

【0046】

従って、本実施形態によれば以下の効果を得ることができる。

【0047】

(1)本実施形態のコアレス配線基板101では、電極形成領域10に存在する電極の全てが、基板裏面103からの突出量B2が最大となる最突出部13を備えた突起電極11となっている。即ち、各突起電極11の表面12は凸状をなしているため、はんだ部31を介してピン21を接合した際に、はんだ部31内における突起電極11の表面12付近にフラックスが溜まりにくくなる。その結果、気化したフラックスがはんだ部31内に溜まることに起因したボイドの発生が防止されるため、突起電極11とピン21との接合強度の低下を防止することができる。即ち、ピン21との接合に適した突起電極11を備えることにより、コアレス配線基板101の信頼性を向上させることが可能となる。

【0048】

(2)本実施形態では、突起電極11の外径B1がピン21の頭部23の外径A2よりも大きく設定されているため、突起電極11と頭部23とをはんだ部31を介して接触させやすくなる。その結果、突起電極11とピン21とをより確実に接合させることができるため、コアレス配線基板101の信頼性をよりいっそう向上させることができる。しかも、最突出部13は突起電極11の中心軸C1上に位置しているため、最突出部13と向かい合うようにピン21の頭部23を配置するだけで、突起電極11の中心軸C1とピン21の中心軸C2とを容易に一致させることができる。よって、ピン21を正確に位置決めすることができる。

【0049】

なお、本実施形態を以下のように変更してもよい。

【0050】

・上記実施形態の突起電極形成工程では、銅箔73に対してエッチングによるパターンニングを行うことにより、最下層の樹脂絶縁層41上に突起電極11を形成していた(図7,図8参照)。しかし、他の方法を用いて突起電極11を形成するようにしてもよい。

【0051】

例えば、エッチングによって銅箔73を完全に除去した後、レジスト形成工程、開口部形成工程及びめっき形成工程を順番に行うことにより、突起電極11を形成してもよい。詳述すると、銅箔73を除去した後、レジスト形成工程を行い、基板裏面103を有する最下層の樹脂絶縁層41上にドライフィルムをラミネートして、めっきレジストを形成する。続く開口部形成工程では、めっきレジストに対して、内径がピン21の頭部23の外径A2よりも大きく設定された開口部を形成する。開口部を形成する方法としては、めっきレジストに対するドリル加工を行って開口部を形成する方法、めっきレジストに対するレーザー加工を行って開口部を形成する方法、感光及び現像を行って開口部を形成する方法、打ち抜き金型を用いてめっきレジストを打ち抜くことにより、めっきレジストに開口部を形成する方法などが挙げられる。続くめっき形成工程では、開口部の内面に対してめっきを行うことにより、開口部に突起電極11を形成する。具体的に言うと、無電解銅めっき及び電解銅めっきを行い、開口部の内面、及び、基板裏面103に露出したビア導体147の下端面に対して突起電極11を形成する。その後、めっきレジストを剥離する。さらに、突起電極成形工程において突起電極11に対してエッチングを行い、中心軸C1上に最突出部13が位置する形状に突起電極11を成形する。

【0052】

なお、上記した突起電極の形成方法は、コア基板の片面または両面にビルドアップ層を有するビルドアップ多層配線基板にも好適に用いることができる。この場合、ビルドアップ層は、層間絶縁層を形成する層間絶縁層形成工程と、層間絶縁層上に導体層を形成する導体層形成工程とを交互に行うことによって形成される。また、突起電極は、ビルドアップ層の表面(下面)に対して、レジスト形成工程、開口部形成工程及びめっき形成工程を順番に行うことによって形成される。即ち、ビルドアップ層の表面には上記実施形態のような銅箔73が存在しないため、レジスト形成工程、開口部形成工程及びめっき形成工程を経て突起電極を形成することが好適である。

【0053】

・上記実施形態の突起電極成形工程では、突起電極11に対してソフトエッチングを行うことにより、中心軸C1上に最突出部13が位置する形状に突起電極11を成形するようになっていた。

【0054】

しかし、突起電極成形工程において、突起電極11を他の方法を用いて成形するようにしてもよい。例えば、突起電極11の基端部分(基板裏面103側の部分)を通常のめっき条件で形成した後、通常とは異なるめっき条件に変更した状態で突起電極11の先端部分(ピン21側の部分)を形成することにより、突起電極11を成形してもよい。ここで、めっき条件を変更する方法としては、例えば、めっき浴におけるめっきの撹拌量を減らすことや、めっきに含まれる光沢剤の分量を増加または減少させることや、めっきに弱酸(例えば、次亜塩素酸ナトリウムなど)を添加することなどが挙げられる。即ち、めっき条件を、ピットやザラツキなどのはんだ不良が発生する条件に敢えて変更することが考えられる。

【0055】

また、突起電極成形工程において、突起電極11を機械的な方法を用いて成形するようにしても勿論よい。例えば、治具を用いて複数の突起電極11の表面12をプレスすることにより、突起電極11を成形してもよい。また、サンドブラストや研磨によって突起電極11を成形してもよい。

【0056】

・上記実施形態において、突起電極成形工程後かつはんだ付け工程前に、突起電極11の表面12を粗化させる粗化工程を行ってもよい。このようにすれば、はんだ部31を介して突起電極11上にピン21の頭部23を接合した際に、突起電極11とはんだ部31との密着強度が高くなる。その結果、突起電極11とピン21との接合強度の低下をより確実に防止できるため、コアレス配線基板101の信頼性がよりいっそう向上する。

【0057】

・上記実施形態において、コアレス配線基板101を構成する最下層の樹脂絶縁層41の下面(基板裏面103)を、ソルダーレジスト(裏面側ソルダーレジスト)によって覆ってもよい。この場合、ソルダーレジストには、突起電極11全体、はんだ部31全体及びピン21を露出させる開口部(裏面側開口部)が形成されるようになる。同様に、コアレス配線基板101を構成する最上層の樹脂絶縁層44の上面(基板主面102)を、ソルダーレジスト(主面側ソルダーレジスト)によって覆ってもよい。この場合、ソルダーレジストには、端子パッド52の少なくとも一部を露出させる開口部(主面側開口部)が形成されるようになる。

【0058】

次に、前述した実施形態によって把握される技術的思想を以下に列挙する。

【0059】

(1)上記手段1において、前記頭部の前記上面の最突出部は、前記ピンの中心軸上に位置していることを特徴とする配線基板。

【0060】

(2)上記手段1において、前記頭部の前記上面の曲率半径は、前記突起電極の表面の曲率半径よりも小さいことを特徴とする配線基板。

【0061】

(3)上記手段1において、前記頭部の上面と前記突起電極の表面とが互いに離間しており、前記頭部の上面と前記突起電極の表面との隙間の大きさは、前記突起電極に設けられた最突出部の前記基板裏面からの突出量、及び、前記頭部に設けられた最突出部の前記軸部との接続部分からの突出量よりも小さいことを特徴とする配線基板。

【0062】

(4)上記手段1において、前記配線基板は、基板主面及び基板裏面を有するとともに複数の層間絶縁層を積層してなる積層部を有し、前記層間絶縁層に設けられたビア導体が前記基板主面側に行くに従って拡径し、前記突起電極の外径は、前記ビア導体の前記基板主面側における外径よりも大きく設定されていることを特徴とする配線基板。従って、技術的思想(4)によれば、ビア導体のピン側における外径が小さくなるため、ピンを引っ張る方向に応力が加わった際に、ビア導体がピンに引っ張られて抜けることを防止できる。

【0063】

(5)上記手段1において、前記配線基板は、コア基板を有さず、基板主面及び基板裏面を有するとともに複数の層間絶縁層を積層してなる積層部を有し、前記層間絶縁層に設けられたビア導体が前記基板主面側に行くに従って拡径し、前記基板主面上の半導体集積回路素子搭載領域内に配置された電極が、半導体集積回路素子とのフリップチップ接続に用いられる端子パッドとなり、前記基板裏面上の前記電極形成領域内に配置された前記突起電極上に、前記ピンが前記はんだ部を介して接合されるコアレス配線基板であることを特徴とする配線基板。

【0064】

(6)上記手段2において、前記突起電極形成工程は、前記基板裏面を有する最下層の前記層間絶縁層上にめっきレジストを形成するレジスト形成工程と、前記めっきレジストに、内径が前記頭部の外径よりも大きく設定された開口部を形成する開口部形成工程と、前記開口部の内面に対してめっきを行うことにより、前記開口部に前記突起電極を形成するめっき形成工程とを含むことを特徴とする配線基板の製造方法。

【0065】

(7)上記手段2において、前記はんだ付け工程では、前記複数のピンの前記軸部を位置決め治具のピン挿入孔に挿入することにより、前記複数のピンを前記積層部よりも下方に配置することを特徴とする配線基板の製造方法。

【符号の説明】

【0066】

10…電極形成領域

11…突起電極

12…突起電極の表面

13…最突出部

21…ピン

22…軸部

23…頭部

24…頭部の上面

31…はんだ部

32…はんだフィレット

41,42,43,44…層間絶縁層としての樹脂絶縁層

80…積層部

101…配線基板としてのコアレス配線基板

103…基板裏面

A2…頭部の外径

B1…突起電極の外径

B2…突出量

C1…突起電極の中心軸

C2…ピンの中心軸

D1…はんだフィレットの最大径

【特許請求の範囲】

【請求項1】

基板裏面上の電極形成領域内に複数の突起電極が配置され、前記複数の突起電極上に母基板搭載用の複数のピンがはんだ部を介して接合された配線基板であって、

前記複数のピンは、軸部と、前記軸部よりも外径が大きい頭部とを有し、

前記複数の突起電極は、外径が前記頭部の外径よりも大きく設定されるとともに、前記基板裏面からの突出量が最大となる最突出部が前記突起電極の中心軸上に位置しており、

前記突起電極の中心軸と前記ピンの中心軸とが一致するように、前記頭部が前記はんだ部を介して前記突起電極上に接合されている

ことを特徴とする配線基板。

【請求項2】

前記ピンは、前記頭部の上面が球面となっていることを特徴とする請求項1に記載の配線基板。

【請求項3】

前記頭部の上面と前記突起電極の表面とが互いに離間していることを特徴とする請求項1または2に記載の配線基板。

【請求項4】

前記はんだ部を構成するはんだフィレットの最大径が、前記突起電極の外径よりも大きく設定されることを特徴とする請求項1乃至3のいずれか1項に記載の配線基板。

【請求項5】

請求項1乃至4のいずれか1項に記載の配線基板を製造する方法であって、

複数の層間絶縁層を積層してなる積層部を準備する積層部準備工程と、

前記基板裏面を有する最下層の前記層間絶縁層上に前記突起電極を形成する突起電極形成工程と、

前記複数のピンを前記積層部よりも下方に配置した状態で、前記頭部を前記突起電極にはんだ付けするはんだ付け工程と

を含むことを特徴とする配線基板の製造方法。

【請求項6】

前記突起電極形成工程後かつ前記はんだ付け工程前に、前記突起電極に対してエッチングを行うことにより、前記中心軸上に前記最突出部が位置する形状に前記突起電極を成形する突起電極成形工程を行うことを特徴とする請求項5に記載の配線基板の製造方法。

【請求項1】

基板裏面上の電極形成領域内に複数の突起電極が配置され、前記複数の突起電極上に母基板搭載用の複数のピンがはんだ部を介して接合された配線基板であって、

前記複数のピンは、軸部と、前記軸部よりも外径が大きい頭部とを有し、

前記複数の突起電極は、外径が前記頭部の外径よりも大きく設定されるとともに、前記基板裏面からの突出量が最大となる最突出部が前記突起電極の中心軸上に位置しており、

前記突起電極の中心軸と前記ピンの中心軸とが一致するように、前記頭部が前記はんだ部を介して前記突起電極上に接合されている

ことを特徴とする配線基板。

【請求項2】

前記ピンは、前記頭部の上面が球面となっていることを特徴とする請求項1に記載の配線基板。

【請求項3】

前記頭部の上面と前記突起電極の表面とが互いに離間していることを特徴とする請求項1または2に記載の配線基板。

【請求項4】

前記はんだ部を構成するはんだフィレットの最大径が、前記突起電極の外径よりも大きく設定されることを特徴とする請求項1乃至3のいずれか1項に記載の配線基板。

【請求項5】

請求項1乃至4のいずれか1項に記載の配線基板を製造する方法であって、

複数の層間絶縁層を積層してなる積層部を準備する積層部準備工程と、

前記基板裏面を有する最下層の前記層間絶縁層上に前記突起電極を形成する突起電極形成工程と、

前記複数のピンを前記積層部よりも下方に配置した状態で、前記頭部を前記突起電極にはんだ付けするはんだ付け工程と

を含むことを特徴とする配線基板の製造方法。

【請求項6】

前記突起電極形成工程後かつ前記はんだ付け工程前に、前記突起電極に対してエッチングを行うことにより、前記中心軸上に前記最突出部が位置する形状に前記突起電極を成形する突起電極成形工程を行うことを特徴とする請求項5に記載の配線基板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−102096(P2013−102096A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−245840(P2011−245840)

【出願日】平成23年11月9日(2011.11.9)

【出願人】(000004547)日本特殊陶業株式会社 (2,912)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月9日(2011.11.9)

【出願人】(000004547)日本特殊陶業株式会社 (2,912)

【Fターム(参考)】

[ Back to top ]