配線基板及び電子部品の実装構造

【課題】導電部材を介して半導体素子等の電子部品が実装される配線基板及び前記電子部品の当該配線基板への実装構造であって、前記電子部品の凸状の外部接続端子と配線基板の導電層との接合安定性(歩留まり)を向上させた信頼性の高い実装構造を実現する配線基板及び電子部品実装構造を提供する。

【解決手段】一方の主面に、電子部品12の外部接続端子14が接続される電極端子16が複数個、列状に配設された配線基板11は、前記電極端子16が、それぞれ、第1の直線状部16−1と、当該第1の直線状部16−1の端部に於いて当該第1の直線状部16−1とは異なる方向に延びる第2の直線状部16−2と、前記第1の直線状部16−1と前記第2の直線状部16−2とが連続する部位に於ける屈曲部16−3とを有することを特徴とする。

【解決手段】一方の主面に、電子部品12の外部接続端子14が接続される電極端子16が複数個、列状に配設された配線基板11は、前記電極端子16が、それぞれ、第1の直線状部16−1と、当該第1の直線状部16−1の端部に於いて当該第1の直線状部16−1とは異なる方向に延びる第2の直線状部16−2と、前記第1の直線状部16−1と前記第2の直線状部16−2とが連続する部位に於ける屈曲部16−3とを有することを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板及び電子部品の実装構造に関し、より具体的には、導電部材を介して半導体素子等の電子部品が実装される配線基板及び前記電子部品の配線基板への実装構造に関する。

【背景技術】

【0002】

ガラスエポキシ樹脂等の絶縁性樹脂を基材とし、一方の主面に銅(Cu)等からなる導電層が選択的に配設された配線基板を用い、前記導電層に、半導体集積回路素子(以下、半導体素子と称する)の主面に配設された凸状(突起状)の外部接続端子が接続され、一方、前記配線基板の他方の主面には選択的に形成された電極の表面に球状電極端子等の外部接続端子が配設されてなる半導体装置がある。即ち、半導体素子は所謂フリップチップ(フェイスダウン)状態で、配線基板に搭載されている。

【0003】

このようなフリップチップ実装構造に於いて、ワイヤバンプとも称される凸状外部接続端子は、前記半導体素子の主面の外部接続端子用の電極パッド上にワイヤボンディング技術を用いた所謂ボールボンディング法によって形成される。

【0004】

かかる凸状外部接続端子は、前記配線基板上の導電層に対して、半田等の導電性部材をもって接続固着される。

【0005】

このような実装構造においては、半導体素子の配線基板への実装の際、当該半導体素子の凸状外部接続端子と配線基板の導電層との間に、電気的接続の安定性を十分確保する必要があり、そのため、例えば配線基板の導電層に選択的に幅広の部位を設け、当該幅広部に導電部材を厚く配設する方法が提案されている。

【0006】

即ち、導電層であるパッド上に半田層が配設された回路基板において、前記パッドの幅をその長手方向の一部で広くし、その幅広部に他の部分より半田層の厚さが厚い半田盛り上がり部を形成した構造(特許文献1参照)、或いはパッドの幅をその中間部において広くし、パッド幅広部の長さ方向の中心を部品リードの平坦部の長さの範囲内に位置させ、パッド幅広部の長さを部品リードの平坦部の長さより長くして、パッド幅広部に他の部分より大きな厚さを有するはんだ盛り上がり部を形成した構造(特許文献2参照)が提案されている。

【0007】

また、配線パターンをソルダーレジストにより選択的に被覆し、露出する配線パターンの領域を電極とした回路パターンにおいて、電極が、左右の長さ方向に沿って最大幅の箇所を1箇所だけ存在するように形成された回路パターン(特許文献3参照)、或いは回路基板上に、半田を介して半導体素子に設けられたバンプがフリップチップ実装される導体パターンを形成してなるフリップチップ実装基板において、導体パターンを配線パターンと、バンプが接合される接続パッドとにより構成し、前記配線パターンの幅寸法に対し、接続パッドの幅寸法を大きくした構造(特許文献4参照)が提案されている。

【0008】

更に、基板上に複数の配線パターンが列状に配設され、それぞれの配線パターンの第1の直線状部が互いに平行又は非平行に形成され、配線パターンの第2の直線状部が同一直線上に形成された構造(特許文献5参照)も提案されている。かかる構造にあっては、各配線パターンにおいて、第2の直線状部が、第1の直線状部と第2の直線状部とが連続する箇所に位置する各屈曲部がなす各配線パターンの列方向に、第1の直線状部から延在している。

【特許文献1】特開平5−308184号公報

【特許文献2】特開平6−216507号公報

【特許文献3】実用新案登録第3115062号公報

【特許文献4】特開2000−77471号公報

【特許文献5】特開2004−40056号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、近年、配線基板に実装される半導体素子は小型化・多端子化しており、また、このような半導体素子の配線基板に対する高密度実装が要求されている。

【0010】

従って、このような要求に対応するために半導体素子の凸状外部接続端子のピッチを微細化すると、上述の各特許文献中に開示されている態様では、配線基板の、隣接して設けられた電極(導電層)の幅広部間の間隙は狭くなる。

【0011】

そのため、半導体素子を配線基板に実装する際に、半導体素子の凸状外部接続端子と配線基板の導電層とにより形成され隣接して設けられた接続部の間に於いて、幅広部に設けられた導電部材がはみ出してしまう恐れがある。その結果、当該接続部間に於いて、ショート(短絡)或いは電流リークが発生して、半導体素子の凸状外部接続端子と配線基板の電極(導電層)との電気的接続の信頼生が低下してしまう。

【0012】

また、特許文献5に示される構造に於いては、隣接する配線パターンのそれぞれの第2の直線状部が、各配線パターンの列方向に同一直線上に配置されているため、配線パターン間のピッチを微細化することは困難である。

【0013】

そこで、本発明は、上記の点に鑑みてなされたものであって、導電部材を介して半導体素子等の電子部品が実装される配線基板及び前記電子部品の当該配線基板への実装構造であって、前記電子部品の凸状外部接続端子と配線基板の導電層との接合安定性(歩留まり)を向上させた信頼性の高い実装構造を実現する配線基板及び電子部品実装構造を提供することを本発明の目的とする。

【課題を解決するための手段】

【0014】

本発明の一観点によれば、一方の主面に、電子部品の外部接続端子が接続される電極端子が複数個、列状に配設された配線基板であって、前記電極端子は、それぞれ、第1の直線状部と、当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部と、を有することを特徴とする配線基板が提供される。

【0015】

本発明の別の観点によれば、電子部品が、導電部材を介して配線基板上の電極端子に実装される電子部品の実装構造であって、一方の主面に、それぞれ、第1の直線状部と、当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部とを具備してなる前記電極端子が、複数個、列状に配設された前記配線基板の、前記電極端子の前記屈曲部に、導電部材を介して、前記電子部品の外部接続端子が接続されてなることを特徴とする電子部品の実装構造が提供される。

【発明の効果】

【0016】

本発明によれば、導電部材を介して半導体素子等の電子部品が実装される配線基板及び前記電子部品の当該配線基板への実装構造であって、前記電子部品の凸状外部接続端子と配線基板の導電層との接合安定性(歩留まり)を向上させた信頼性の高い実装構造を実現する配線基板及び電子部品実装構造を提供することができる。

【発明を実施するための最良の形態】

【0017】

以下、本発明の実施の形態について説明する。

【0018】

なお、以下では、本発明の実施の形態に係る配線基板に実装される電子部品として、半導体素子を例にして説明するが、当該電子部品は、半導体素子に限定されるものではなく、半導体素子を樹脂封止した半導体装置、或いは受動素子等であってもよい。

【0019】

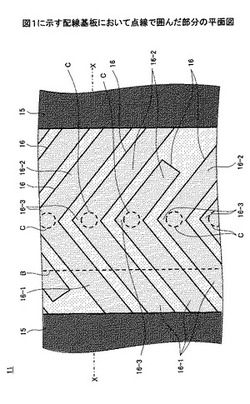

本発明の実施の形態に係る配線基板上に、半導体素子が実装された半導体装置の実装構造を、図1に示す。これを半導体装置10とする。

【0020】

同図において、当該半導体装置10にあっては、配線基板11の一方の主面(上面)上に、半導体集積回路素子(以下、半導体素子と称する)12がフリップチップ(フェイスダウン)方式をもって搭載・固着されている。

【0021】

ここで配線基板11は、ガラスエポキシ樹脂、ガラス−BT(ビスマレイミドトリアジン)、或いはポリイミド等の有機材絶縁性樹脂、又はセラミック,ガラス等の無機材料を基材とし、その表面及び/或いは内部に銅(Cu)等からなる配線層が選択的に配設されている。当該配線基板11は、インターポーザー又は支持基板と称される場合もある。

【0022】

当該配線基板11の一方の主面であって、半導体素子が搭載される主面上には、前記配線層に接続された導電層13が選択的に配設されている。

【0023】

そして、当該導電層13を選択的に覆って、即ち、半導体素子12の外部接続端子14が接続される部位及びその周囲を除いて、ソルダーレジスト層(絶縁樹脂膜)15が選択的に被覆されている。当該ソルダーレジストは、エポキシ系、アクリル系、ポリイミド系等の樹脂又はこれらの混合樹脂等からなる。

【0024】

この結果、当該ソルダーレジスト層15に設けられた開口部において、導電層13の一部が電極端子16として表出している。ソルダーレジスト層15は、導電層13に於ける半導体素子12との接続領域、即ち電極端子16の表出部を画定している。

【0025】

尚、配線基板11の他方の主面(裏面)にも、選択的に導電層が設けられ、当該導電層には、半田を主体とする球状電極端子等の外部接続端子が複数配設されるが、本実施の形態にあっては図示しない。

【0026】

一方、半導体素子12にあっては、周知の半導体製造プロセスが適用されて、シリコン(Si)等の半導体、或いはガリウム砒素(GaAs)等の化合物半導体からなる半導体基板17の一方の主面に電子回路が形成されている。

【0027】

ここでは、当該半導体素子12にあって、半導体基板17に形成されたトランジスタ等の能動素子及び/或いは容量素子等の受動素子、並びに一方の主面上に形成された多層配線層及び/或いは再配線層を図示することを省略している。

【0028】

当該半導体基板17の一方の主面には、電子回路部の周囲に位置して、外部接続用端子パッド18が列状に配設され、当該外部接続用端子パッド18それぞれの上には凸状外部接続端子14が配設されている。

【0029】

前記外部接続用端子パッド18は、アルミニウム(Al)、銅(Cu)、又はこれらの合金等をもって形成され、一方、凸状外部接続端子14は、例えば所謂ボールボンディング法によって金(Au)ボールが固着・接続されて台座部が形成され、更に当該台座部上に突出する部位からなる凸状部が一体に形成される。尚、凸状外部接続端子14の頂部は、必要に応じて平坦化処理が施される。

【0030】

また、外部接続端子パッド18の露出表面(最上層)には、予め電解めっき法又は蒸着法等により金(Au)層が形成されてもよい。

【0031】

そして、凸状外部接続端子14は、例えば銅(Cu)、銅(Cu)と金(Au)の合金、又は半田等から構成されてもよい。

【0032】

かかる半導体素子12の凸状外部接続端子14の少なくとも凸状部と、これに対応する前記配線基板11上の電極端子16は、再溶融性を有する導電部材19によって共通に被覆され、機械的・電気的に接続されている。

【0033】

当該導電部材19としては、半田からなる導電部材が効果的である。半田は再溶融性を有するが、導電性樹脂接着剤の如き他の再溶融性を有する導電材料に比べ、加熱溶融時の流動性が高く、導電部材19の材料として好適である。また、導電部材19として半田を用いる場合、配線基板11のプリコート用の半田材料を使用でき、半田プリコート技術を適用できるため便利であり、また、材料コストも安く抑えることができる。

【0034】

このように、配線基板11の一方の主面上に、フリップチップ(フェイスダウン)方式をもって搭載・固着された半導体素子12と当該配線基板11の一方の主面との間には、エポキシ系樹脂、ポリイミド系樹脂、又はアクリル系樹脂等からなる熱硬化性接着剤等の、アンダーフィル材20が充填されている。

【0035】

この様な半導体素子の実装形態が採られる半導体装置10の、前記配線基板11に於ける、電極端子16の形態について、図2乃至図4をもって説明する。

【0036】

ここでは、図1に示した構成に於いて点線により囲まれた部位Aに於ける、配線基板11の一方の主面に於ける電極端子の配設形態を図2に示す。尚、同図にあっては、半導体素子12並びにアンダーフィル材20の図示を省略している。また、当該図2に示す配線基板11に於けるX−X断面を、図3に示す。

【0037】

図2に示される様に、配線基板11の一方の主面上に配設された複数配設された導電層13を選択的に覆ってソルダーレジスト層15が配設され、当該ソルダーレジスト層15により被覆されない導電層13の一部が電極端子16として表出している。

【0038】

尚、同図に於いて、配線基板11上にフリップチップ実装される半導体素子12の外周縁部を破線Bにて示し、当該半導体素子12の凸状外部接続端子14が接続される電極端子16の接続部位を破線円Cにて示している。即ち、破線Bより右側に半導体素子が位置する。

【0039】

即ち、本実施の形態にあっては、配線基板11の一方の主面にあって、半導体素子12の凸状外部接続端子14が接続される導電層13は、電極端子16部分に於いて、第1の直線状部16−1と、当該第1の直線状部16−1の端部に於いて当該第1の直線状部16−1とは異なる方向に延びる第2の直線状部16−2と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部16−3とを具備している。

【0040】

また、隣り合う電極端子16間にあっては、第1の直線状部16−1相互間のそれぞれ、並びに第2の直線状部16−2相互間のそれぞれが平行に配設されている。

【0041】

電極端子16に於ける、第1の直線状部16−1と第2の直線状部16−2が連続する屈曲部16−3にあっては、第1の直線状部16−1と第2の直線状部16−2との間は、所定の角度(本実施の形態にあっては鈍角)をもって、略「くの字」状に屈曲している。

【0042】

当該屈曲部16−3に、半導体素子12の凸状外部接続端子14が接続される。

【0043】

そして、各電極端子16の屈曲部16−3は、接続される半導体素子12の外部接続用端子パッド18の配置に対応して、同一線上に並んで配設されている。

【0044】

この様な構造を有する電極端子16に、導電部材19を被覆した状態を図4に示す。

【0045】

前述の如く、電極端子16の表面には、再溶融性を有する導電部材19が配設され、当該導電部材19を介して、半導体素子12の凸状外部接続端子14が固着・接続される。

【0046】

本実施の形態の形態にあっては、図4に示されるように、電極端子16の屈曲部16−3に被着された導電部材19の厚さは、第1の直線状部16−1並びに第2の直線状部16−2上に被着された導電部材19の厚さよりも大きい。

【0047】

この様に、一つの電極端子16に於いて、導電部材19の厚さの差異を生ずる理由について、図5を参照して説明する。ここで、図5(a)は、電極端子16の1つを示し、図5(b)は当該電極端子16の屈曲部16−3に於ける断面(図5(a)の線a−aに於ける断面)を示し、また図5(c)は当該電極端子16の一方の直線状部16−2の断面(図5(a)の線b−b)を示している。なお、図5(c)では、一方の直線状部16−2の断面を示しているが、他方の直線状部16−1も同様の断面構造を有する。

【0048】

ここで、導電部材19の表面張力をγ、外気圧力をPoとし、電極端子16の屈曲部16−3の、図5(a)の線a−aに沿う断面に於ける導電部材19の内部圧力をPa、電極端子6の第2の直線状部16−2の、図5(a)の線b−bに沿う断面に於ける導電部材19の内部圧力をPb、電極端子16の屈曲部16−3の、図5(a)の線a−aに沿う断面に於ける導電部材19の曲率半径をRaとし、更に電極端子16の第2の直線状部16−2の図5(a)の線b−bに沿う断面に於ける導電部材19の曲率半径をRbとする。

【0049】

表面張力に関するラプラス(Laplace)の定理より、式(1)及び(2)が成立する。

【0050】

ΔPa=Po−Pa=2γ/Ra ・・・式(1)

ΔPb=Po−Pb=2γ/Rb ・・・式(2)

前記導電部材19が溶融し、その表面張力が作用して平衡状態にある時には、電極端子16の屈曲部16−3に於ける導電部材19の内部圧力Paと、電極端子16の第2の直線状部16−2に於ける導電部材19の内部圧力Pbとは等しくなり、式(1)及び式(2)より、式(3)が得られる。

【0051】

Rb=Ra ・・・式(3)

一方、前記屈曲部16−3に於ける屈曲角θと、当該屈曲部16−3の幅(最大幅)Da、及び第2の直線状部15−2の幅Dbとの間には、次の関係式(4)が成り立つ。

【0052】

Da=[1/{sin(0.5θ)}]×Db ・・・式(4)

このとき、屈曲部16−3の屈曲角θは、0度<θ<180度であり、この範囲に於いては、式(4)より、次の関係式(5)が得られる。

【0053】

Da>Db ・・・式(5)

かかる式(3)及び式(5)より、導電部材19が平衡状態及び溶融状態にあるとき、電極端子16の屈曲部16−3に於ける断面(図5(a)の線A−Aに沿う断面)上の導電部材19の厚さHa、及び電極端子16の第2の直線状部16−2に於ける断面(図5(a)の線B−Bに沿う断面)上の導電部材19の厚さHbについて、以下の関係式(6)が得られる。

【0054】

Ha>Hb ・・・式(6)

この様に、電極端子16の屈曲部16−3に於いては、第1の直線状部16−1並びに第2の直線状部16−2に比し、大なる高さ(厚さ)をもって導電部材19が配設される。

【0055】

尚、電極端子16が微細になるほど重力の影響は小さくなることから、作用原理の理解を容易にする為、式(1)乃至式(6)の説明に於いては、導電部材19に作用する重力の影響を無視し、また導電部材19は電極端子16の上面部のみに於いて濡れ形成され、曲率半径が一定であるモデルを用いている。

【0056】

この様に、電極端子16の実効的な幅が異なることにより、その表面に被着される導電部材19の厚さ(高さ)が異なる。即ち、前記図4に示すように、電極端子16上に導電部材19を被着した後、加熱してその流動性を高めると、液状になった導電部材19はその表面張力により、屈曲部16−3においてその厚みが最大となる。

【0057】

この状態に於いて導電部材19を、降温又は固化することにより、当該導電部材19は屈曲部16−3に於いて、第1の直線状部16−1並びに第2の直線状部16−2に比べ大なる厚さをもって形成される。

【0058】

即ち、電極端子16上に導電部材19を被覆形成する際、当該電極端子16に於いて、半導体素子13の凸状外部接続端子14が接続される部位である屈曲部16−3に於ける導電部材19の被覆厚さ(高さ)を厚く(高く)形成することができる。

【0059】

この様に、本実施の形態にあっては、半導体素子12の凸状外部接続端子14を配線基板11上の電極端子16へ接続する際、十分な量(厚さ)をもって導電部材19を配置することができ、半導体素子12の凸状外部接続端子14の高さの不均一性及び/或いは配線基板11の反りを吸収することができる。これにより、配線基板11上に半導体素子12をフリップチップ実装する際に、その接続安定性(歩留まり)を高めることができる。

【0060】

尚、電極端子16の屈曲部16−3の屈曲角を鋭角とすることにより、当該電極端子16に導電部材19を被覆形成する際に、当該局部的16−3に於ける被着高さをより大とすることができるが、当該屈曲角は電極端子の幅、相互の間隔などにより適宜選択される。

【0061】

この様に、導電部材19は、電極端子16の屈曲部16−3に於いて大なる厚さをもって形成される。従って、半導体素子12の凸状外部接続端子14のピッチが微細化され、これに対応して配線基板11の各電極端子16の幅が微細化された場合であっても、当該凸状外部接続端子14を大きな接続強度をもって接続することができる。

【0062】

また、半導体素子12の凸状外部接続端子14の高さのバラツキ、或いは配線基板11の反りが吸収されて、半導体素子12の凸状外部接続端子14と配線基板11のボンディング電極15との電気的接続を確実ならしめることができる。

【0063】

一方、前記複数個の電極端子16は、第1の直線状部16−1が互いに並行となる様配設され、一方第2の直線状部16−2も互いに並行となるよう配設されることから、配線基板11上に於ける当該電極端子16の高い配置密度を得ることができる。

【0064】

また、半導体素子12の凸状外部接続端子14の配設ピッチが微細化され、これに対応して配線基板11上の電極端子16の幅が微細化される場合にあっても、当該配線基板11上に半導体素子12をフリップチップ実装する際、電極端子間の短絡或いは電流リークの発生を抑制することができ、もって高い信頼性を有する実装構造を実現することができる。

【0065】

次に、図6及び図7を参照して、前記配線基板11への半導体素子12の実装工程を説明する。

【0066】

先ず、ボンディングステージ(図示せず)上に載置・固定された配線基板11と、吸着用治具21に吸着・保持された半導体素子12とを対向せしめる。(図6(a)参照)

配線基板11は、前述の如く、ガラスエポキシ樹脂、ガラス−BT(ビスマレイミドトリアジン)、或いはポリイミド等の有機材絶縁性樹脂、又はセラミック、ガラス等の無機材料を基材とし、その表面及び/或いは内部に、銅(Cu)等からなる配線層が選択的に配設されている。

【0067】

かかる配線基板11の一方の主面(上面)には、前記配線層に接続された導電層13が配設されている。当該導電層13は、ソルダーレジスト層(絶縁樹脂膜)15により選択的に被覆され、当該ソルダーレジスト層15の開口部に於いて、複数の電極端子16が露出している。

【0068】

当該電極端子16は、所謂フォトエッチング法、選択メッキ法等により形成され、前記図2に示すところの、本発明思想に従ったパターン形状に形成される。即ち、当該電極端子16は、第1の直線状部16−1と第2の直線状部16−2により構成され、当該第1の直線状部16−1と第2の直線状部16−2は、所定の角度を有する屈曲部16−3を介して連続している。

【0069】

一方、半導体素子12は、シリコン(Si)半導体基板16の主面上に配設された外部接続用端子パッド18上に、凸状外部接続端子14が配設されている。

【0070】

外部接続用端子パッド18は、通常アルミニウム(Al)、銅(Cu)或いはこれらの合金から形成され、また凸状外部接続端子14は、外部接続用端子パッド17の表面に、例えば所謂ボールボンディング法によって金(Au)ボールが固着・接続されて台座部が形成され、更に当該台座部上に突出する部位からなる凸状部をもって一体に形成されている。

【0071】

尚、当該凸状外部接続端子14の頂部に対しては、平坦化処理が施されてもよい。

【0072】

また、当該外部接続用端子パッド18表面への凸状外部接続端子14の形成法として、電解めっき法又は無電解めっき法により、金(Au)、銅(Cu)、ニッケル(Ni)等を被着させる方法を適用してもよい。

【0073】

更に、当該外部接続用端子パッド18の露出表面(最上層)には、電解めっき法又は蒸着法等により、金(Au)層を形成してもよい。

【0074】

一方、前記配線基板11の電極端子16には、予め例えば錫(Sn)を主体とする半田からなる導電部材19が、印刷法、メッキ法或いは蒸着・リフロー法等により、被覆・形成されている。

【0075】

このとき、電極端子16の屈曲部16−3に配設された導電部材19の厚さ(鉛直方向の高さ)は、前述の如く、第1の直線状部16−1並びに第2の直線状部16−2上に配設された導電部材19の厚さよりも厚い。

【0076】

この様な電極構造を有する半導体素子12の外部接続端子14を、配線基板11の電極端子16の屈曲部16−3に位置合わせし、対向させる。

【0077】

尚、前記吸着用治具21は、加熱樹段(図示せず)により、前記導電部材19の融点以上の温度(例えば180℃乃至260℃)に予め加熱しておく。

【0078】

かかる状態に於いて、半導体素子12を吸着保持する吸着用治具21を降下させ、半導体素子12の凸状外部接続端子14を配線基板11の電極端子16の表面を覆う導電部材19に接触させ、更に吸着用治具21により加重を付加して導電部材19を溶融せしめる。

【0079】

この結果、半導体素子12の凸状外部接続端子14は、少なくともその突出部が導電部材19により被覆され、半導体素子12の凸状外部接続端子14と配線基板11の電極端子16は導電部材19を介して接続される。(図6(b)参照)

尚、前記ボンディングステージを、予め50℃乃至100℃程の温度に加熱して、配線基板11を余熱しておき、導電部材19をより短時間で昇温させることもできる。

【0080】

このようにして、配線基板11上の電極端子16の屈曲部16−3に、半導体素子12の凸状外部接続端子14が接続・固着され、当該配線基板11に半導体素子12を搭載した後、当該配線基板11と半導体素子12との間に、エポキシ系樹脂、ポリイミド系樹脂、又はアクリル系樹脂等からなる熱硬化性接着剤等のアンダーフィル材20を充填する。(図7(c)参照)

当該アンダーフィル材20は、ノズル22を介して供給される。

【0081】

このようにして、配線基板11の一方の主面上に、半導体素子12がフリップチップ(フェイスダウン)方式をもって搭載・固着され、当該半導体素子12の凸状外部接続端子14と、これに対応する前記配線基板11上の電極端子16とが、導電部材19を介して機械的・電気的に接続される。(図7(d)参照)

しかる後、配線基板11の他方の主面(下面)に、半田を主体とする球状電極端子等の外部接続端子を配設(図示せず)し、半導体装置10を形成する。

【0082】

尚、本発明思想によれば、配線基板上の電極端子の形状、並びに半導体素子の外部接続端子の配設構造は、前記図2に示す形態に限られず、以下に示す変形例の如き形態を採ることもできる。

【0083】

[変形例1]

本発明の実施の形態の変形例1に係る、配線基板の電極端子形状を、図8に示す。同図に於いて、配線基板81上に搭載される半導体素子の外周端部を破線Bにて示し、当該配線基板上の電極端子に半導体素子の凸状外部接続端子が接続される部位を破線円Cにて示す。

即ち、破線Bより右側に半導体素子が位置する。

【0084】

本変形例1にあっても、配線基板81に配設される複数の電極端子85は、一定の幅を有し互いに繋がっている第1の直線状部85−1と第2の直線状部85−2とを具備する。当該第1の直線状部85−1と第2の直線状部85−2は、鈍角をなす屈曲部85−3を介して連続し、且つ互いに異なる方向に延在している。

【0085】

かかる構成にあって、当該電極端子85の第1の直線状部85−1は、比較的短い直線状(短冊状)を有し、前記半導体素子の外周端部に沿う方向に複数個、且つ互いに並行に並べられて配設されている。

【0086】

一方、第2の直線状部85−2は、第1の直線状部85−1の一方の端部に屈曲部85−3を介して連続して配設されるが、その屈曲部85−3は複数の第1の直線状部85−1に於いて交互に選択・配置され、結果として、第2の直線状部85−2は、第1の直線状部85−1の一つ置きに、異なる方向(図示される形態では左下方、右上方)に延在される。

【0087】

即ち、前記半導体素子の外周端部に沿う方向に並ぶ複数の第1の直線状部85−1に対し、その両端の一方が交互に選択されて、第2の直線状部85−2が導出されている。

【0088】

従って、屈曲部85−3、即ち半導体素子の外部接続端子が接続される部位は、半導体素子の外周端部から異なる距離をもって交互に設定されている。これにより、近接する屈曲部85−3相互の距離を実質的に大きくすることができ、当該屈曲部85−3に接続される半導体素子に於ける外部接続端子の、当該半導体素子の外周端部に沿う方向に於ける相互の間隔を、実質的に大きくすることができる。そして、同一方向に延在する第2の直線状部85−2は、相互に平行となるよう配設されている。

【0089】

[変形例2]

本発明の実施の形態の変形例2に係る配線基板の電極端子形状を、図9に示す。同図に於いて、配線基板91上に搭載される半導体素子の外周端部を、破線Bにて示す。即ち、破線Bより右側に半導体素子が位置する。また、当該配線基板上の電極端子に半導体素子の凸状外部接続端子が接続される部位を破線円にて示す。

【0090】

本変形例2にあっても、配線基板91に配設される複数の電極端子95は、一定の幅を有し互いに繋がっている第1の直線状部95−1と第2の直線状部95−2とを具備する。当該第1の直線状部95−1と第2の直線状部95−2は、鈍角をなす屈曲部95−3を介して連続し、且つ互いに異なる方向に延在している。

【0091】

かかる構成にあって、電極端子95の第1の直線状部95−1は、前記変形例1と同様に比較的短い直線状(短冊状)を有する。そして半導体素子の外周端部に沿う方向に、傾斜して2列に配設され、且つ一つの列にあっては、互いに並行に並べられて配設されている。

【0092】

そして、2列に並ぶ電極端子95の第1の直線状部95−1間にあっては、その傾斜方向が異なり、一方の列を構成する電極端子95の第1の直線状部95−1の端部が、当該他方の列を構成する電極端子95の第1の直線状部95−1の端部に近接して配設されている。

【0093】

一方、第2の直線状部95−2は、第1の直線状部95−1の他方の端部、即ち他方の列から遠い側の端部に、屈曲部95−3を介して連続して配設される。そして、当該第2の直線状部95−2は、前記列から遠ざかる方向に延在される。

【0094】

即ち、前記半導体素子の外周端部に沿う方向に、傾斜して2列に並ぶ複数の第1の直線状部95−1に対し、その一方の端部(他方の列からは遠い端部)に於いて第2の直線状部95−2が導出されている。

【0095】

従って、屈曲部95−3、即ち半導体素子の凸状外部接続端子が接続される部位は、半導体素子の外周端部から異なる寸法(距離)をもって交互に設定されている。

【0096】

このため、近接する屈曲部95−3相互の距離を実質的に大きくすることができ、当該屈曲部95−3に接続される半導体素子に於ける外部接続端子の、当該半導体素子の外周端部に沿う方向に於ける相互の間隔を、実質的に大きくすることができる。

【0097】

一方、同一方向に延在する第2の直線状部95−2は、相互に平行となるよう配設されている。

【0098】

この様な電極端子の配置構造を有する配線基板(変形例1、変形例2)に対して実装される半導体素子の外部接続用端子パッド及び凸状外部接続端子の配設構造を、図10(a)及び図10(b)に示す。当該図10(a)、図10(b)にあっては、それぞれ半導体素子の一つの隅部(コーナー部)を例示している。

【0099】

図10(a)に示す例にあっては、複数個の外部接続用端子パッド117が、半導体素子110の直線状外周縁部に沿って、且つ当該外周縁部からの距離が異なる状態をもって2列に配設されている。

【0100】

そして、外部接続用端子パッド117のそれぞれには、凸状外部接続端子114が配設されている。即ち、当該半導体素子100に於いては、その外周縁部に沿って、互いに平行な凸状外部接続端子114の列が二つ形成されている。

【0101】

一方、図10(b)に示す例にあっては、半導体素子110の外周縁部から内側に向かって延びる長方形の外部接続用端子パッド117が、当該半導体素子の直線状外周縁部に沿って、列状に配設されている。

【0102】

そして、隣接する長方形状の外部接続用端子パッド117間に於いては、長方形の長さ方向の異なる端部、即ち前記半導体素子の直線状外周縁部に近い端部、或いは遠い側の端部に、交互に、凸状外部接続端子124が配設される。即ち、当該半導体素子110にあっても、その外周縁部に沿って、互いに平行な凸状外部接続端子124の列が二つ形成されている。

【0103】

この様な凸状外部接続端子の配設形態を有する半導体素子を、前記図8或いは図9に示される配線基板(81、91)上にフリップチップ実装する際には、当該半導体素子の直線状外周縁部に沿って2列に配設された凸状外部接続端子が、配線基板上に於いて2列に配設された電極端子の屈曲部(85−3、95−3)に接続される。

【0104】

この時、2列の屈曲部のそれぞれに於いて、凸状外部接続端子は、厚く被着された(多量の)導電部材をもって、屈曲部に対して強固に接続・固着される。また、同時に当該凸状外部接続端子の高さのバラツキ、或いは配線基板の反りが吸収される。これにより、半導体素子と配線基板上の電極端子は、高い接続安定性(歩留り)及び高い接続信頼性をもって接続される。

【0105】

尚、前述の如く、配線基板上に列状に配設される電極端子の屈曲部、即ち半導体素子の外部接続端子が接続される部位は、近接する相互間に於いて、半導体素子の外周端部から異なる寸法(距離)をもって交互に設定されている。

【0106】

従って、近接する屈曲部相互の距離は実質的に大きく、当該屈曲部に接続される半導体素子に於ける外部接続端子の間隔を実質的に大きくすることができる。これにより、外部接続端子間の絶縁耐圧が確保され、もって、外部接続端子を高密度に備えた半導体素子のフリップチップ実装を行うことができる。

【0107】

[変形例3]

本発明の実施の形態の変形例3に係る配線基板の電極端子形状を、図11に示す。同図に於いて、配線基板131上に搭載される半導体素子の外周端部を破線Bにて示す。即ち、破線Bより右側に半導体素子が位置する。また、当該配線基板上の電極端子に半導体素子の凸状外部接続端子が接続される部位を破線円にて示す。

【0108】

本変形例3にあっては、配線基板131上に配設される複数の電極端子135は、一定の幅を有する第1の直線状部135−1と、当該第1の直線状部135−1の両端部から延在される第2の直線状部135−2A,135−2Bとを具備する。

【0109】

そして、第1の直線状部135−1は、半導体素子の外周端部に沿う方向に複数個配設され、二つの第2の直線状部135−2A,135−2Bは、当該第1の直線状部135−1の両端部に於いて、鈍角をなす屈曲部135−3A,135−3Bを介して連続し、且つ互いに異なる方向に延在している。かかる構成によれば、一つの電極配線135に於いて、2つの屈曲部、即ち半導体素子の凸状外部接続端子の接続部が設定される。

【0110】

この時、半導体素子の外周端部に沿って並ぶ第1の直線状部135−1は、その長さが互いに等しいことから、2つの屈曲部135−3A,135−3Bはそれぞれ半導体素子の外周端部に沿って並行に位置して配設され、列状を呈する。

【0111】

尚、図において、15はソルダーレジスト層を指す。

【0112】

この様な電極端子の配設構造を有する配線基板131に対してフリップチップ実装される半導体素子の外部接続用丹治パッド及び凸状外部接続端子の配設構造を、図12に示す。当該図12に於いても、半導体素子の一つの隅部(コーナー部)を例示している。即ち、半導体素子132の一つの直線状外周縁部に沿って、当該外周縁部から内側に延びる長方形状の外部接続用端子パッド137が複数個、列状に且つ互いに並行に配設されている。

【0113】

そして、一つの長方形状の外部接続用端子パッド137に於いては、長方形の長手方向に並んで二つの凸状外部接続端子134A,134Bが配設される。即ち、当該半導体素子132にあっても、その一つの直線状外周縁部に沿って、互いに平行な凸状外部接続端子134が、2列に配設される。

【0114】

この様な凸状外部接続端子の配設構造を有する半導体素子132を、前記配線基板131上にフリップチップ実装した状態を、図13に示す。

【0115】

即ち、配線基板131の一方の主面上に、半導体素子132がフリップチップ(フェイスダウン)方式をもって搭載され、当該半導体素子132の凸状外部接続端子134と、これに対応する前記配線基板131上の電極端子135とが、導電部材19を介して機械的・電気的に接続される。

【0116】

ここで、半導体素子132の電極端子パッド137に配設された二つの凸状外部接続端子134A、134Bは、配線基板131上の電極端子135−1の両端屈曲部135−3A,135−3Bに対して導電部材19を介して接続される。

【0117】

即ち、半導体素子132の凸状外部接続端子134は、一つの電極端子135に対して、2箇所に於いて接続され、且つ二つの凸状外部接続端子134A,134Bはそれぞれ、厚く被着された(多量の)導電部材19をもって、対応する屈曲部に接続・固着される。

【0118】

また、この時、当該凸状外部接続端子134の高さのバラツキ、或いは配線基板131の反りが吸収され、半導体素子132と配線基板上の電極端子134は、高い接続安定性(歩留り)及び高い接続信頼性をもって接続される。

【0119】

尚、図において、20はアンダーフィル材を指す。

【0120】

[変形例4]

本発明の実施の形態の変形例4に係る配線基板の電極端子形状を、図14に示す。同図に於いて、配線基板151上に搭載される半導体素子の外周端部を破線Bにて示す。即ち、破線Bより右側に半導体素子が位置する。また、当該配線基板上の電極端子に半導体素子の凸状外部接続端子が接続される部位を破線円にて示す。

【0121】

本変形例4にあっては、配線基板151上に配設される複数の電極端子155は、一定の幅を有する第1の直線状部155−1と、当該第1の直線状部155−1の両端部から延在される第2の直線状部155−2A,155−2Bとを具備する。

【0122】

そして、当該第1の直線状部155−1は、搭載される半導体素子の外周端部に沿う方向に対して傾斜し、且つ当該半導体素子の外周端部に沿う方向に、複数個互いに並行に配設される。

【0123】

一方、第2の直線状部155−2A及び155−2Bは、前記第1の直線状部155−1の両端部に於いて、ほぼ直角をなす屈曲部155−3A,155−3Bを介して連続し、且つ互いに反対方向に延在している。そして、当該第2の直線状部155−2A、第2の直線状部155−2Bもそれぞれ、半導体素子の外周端部に沿う方向に、複数個互いに並行に配設される。

【0124】

かかる構成に於いても、一つの電極端子155に於いて、2つの屈曲部、即ち半導体素子の凸状外部接続端子の接続部が設定される。この時、半導体素子の外周端部に沿って隣接する第1の直線状部155−1は、その長さが互いに等しいことから、2つの屈曲部155−3A,155−3Bはそれぞれ半導体素子の外周端部に沿って並行に位置して配設され、列状を呈する。

【0125】

尚、図において、15はソルダーレジスト層を指す。

【0126】

この様な電極端子の配設構造を有する配線基板151にフリップチップ実装される半導体素子152の外部接続用丹治パッド及び凸状外部接続端子の配設構造を、図15に示す。当該図15に於いても、半導体素子の一つの隅部(コーナー部)を例示している。

【0127】

即ち、半導体素子152の直線状外周縁部に沿って、矩形形状を有する外部接続用端子パッド157が、列状に配設されている。そして、当該外部接続用端子パッド157に於いては、矩形形状の対角線にほぼ沿って、凸状外部接続端子154A,154Bが並び配設されている。即ち、当該半導体素子152にあっても、その一つの外周縁部に沿って、凸状外部接続端子154が2列に、ほぼ平行に配設される。

【0128】

この様な凸状外部接続端子の配設形態を有する半導体素子152を、前記配線基板131上にフリップチップ実装した状態を、図16に示す。

【0129】

即ち、配線基板151の一方の主面上に、半導体素子152がフリップチップ(フェイスダウン)方式をもって搭載され、当該半導体素子152の凸状外部接続端子154と、これに対応する前記配線基板151上の電極端子154とが、導電部材19を介して機械的・電気的に接続される。ここで、半導体素子152の凸状外部接続端子154A、154Bは、対応する電極端子155−1の屈曲部155−3A,155−3Bに於いて、導電部材19を介して接続される。

【0130】

即ち、半導体素子152の一つの凸状外部接続用端子パッド157は、配線基板上の一つの電極端子155に対して、2箇所に於いて接続され、且つ二つの凸状外部接続端子154A,154Bはそれぞれ、厚く被着された(多量の)導電部材19をもって、対応する屈曲部位に於いて電極端子155に接続・固着される。

【0131】

また、この時、当該凸状外部接続端子154の高さのバラツキ、或いは配線基板151の反りが吸収され、半導体素子152と配線基板上の電極端子155は、高い接続安定性(歩留り)及び高い接続信頼性をもって接続される。

【0132】

尚、図において、20はアンダーフィル材を指す。

【0133】

以上、本発明の実施の形態及びその変形例について詳述したが、本発明は特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形及び変更が可能である。

【0134】

以上の説明に関し、更に以下の項を開示する。

(付記1)

一方の主面に、電子部品の外部接続端子が接続される電極端子が複数個、列状に配設された配線基板であって、

前記電極端子は、それぞれ、

第1の直線状部と、

当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、

前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部と

を有することを特徴とする配線基板。

(付記2)

付記1記載の配線基板であって、

前記複数個の電極端子は、前記第1の直線状部が互いに並行となる様配設されてなることを特徴とする配線基板。

(付記3)

付記1又は2記載の配線基板であって、

前記複数個の電極端子は、前記第2の直線状部が互いに並行となるよう配設されてなることを特徴とする配線基板。

(付記4)

付記1乃至3記載の配線基板であって、

前記複数個の電極端子は、前記屈曲部が列状に配設されてなることを特徴とする配線基板。

(付記5)

付記4記載の配線基板であって、

前記主面において、複数の前記電極端子から構成される列が、互いに平行に複数形成されており、

一の列を構成する電極端子の屈曲部と、他の列を構成する電極端子の屈曲部とは、前記列の形成方向においてずれて位置していることを特徴とする配線基板。

(付記6)

付記1記載の配線基板であって、

前記複数個の電極端子は、前記屈曲部が複数の列状に配設され、当該複数の列は互いに並行であることを特徴とする配線基板。

(付記7)

付記1記載の配線基板であって、

前記複数個の電極端子は、それぞれ前記第1の直線状部の両端部に前記屈曲部が配設されてなること特徴とする配線基板。

(付記8)

付記7記載の配線基板であって、

前記第1の直線状部の一の端部に配設された屈曲部と、前記第1の直線状部の他の端部に配設された屈曲部は、前記電極端子の配列方向と略垂直の方向に並んで配設されてなることを特徴とする配線基板。

(付記9)

付記7記載の配線基板であって、

前記第1の直線状部の一の端部に配設された屈曲部と、前記第1の直線状部の他の端部に配設された屈曲部は、前記電極端子の配列方向においてずれて配設されてなることを特徴とする配線基板。

(付記10)

付記1乃至9いずれか一項記載の配線基板であって、

前記第2の直線状部は、前記第1の直線状部の端部に於いて前記第1の直線状部に対して鋭角を為して延びていることを特徴とする配線基板。

(付記11)

電子部品が、導電部材を介して配線基板上の電極端子に実装される電子部品の実装構造であって、

一方の主面に、それぞれ、第1の直線状部と、当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部とを具備してなる前記電極端子が、複数個、列状に配設された前記配線基板の、前記電極端子の前記屈曲部に、導電部材を介して、前記電子部品の外部接続端子が接続されてなることを特徴とする電子部品の実装構造。

(付記12)

付記11記載の電子部品の実装構造であって、

前記電子部品の前記外部接続端子は、凸状を有することを特徴とする電子部品の実装構造。

(付記13)

付記11記載の電子部品の実装構造であって、

前記電子部品の前記外部接続端子は、互いに並行する複数の列状をもって、前記配線基板上の前記電極端子に接続されてなることを特徴とする電子部品の実装構造。

(付記14)

付記11記載の電子部品の実装構造であって、

前記電子部品の電極パッドに於ける前記外部接続端子の形態に対応して、前記配線基板上の前記電極端子の前記屈曲部が配設され、前記電子部品の前記外部接続端子と前記電極端子の前記屈曲部は、前記導電部材を介して接続されてなることを特徴とする電子部品の実装構造。

(付記15)

付記11乃至14いずれか一項記載の電子部品の実装構造であって、

前記導電部材は、半田を含む材料から構成されることを特徴とする電子部品の実装構造。

【図面の簡単な説明】

【0135】

【図1】本発明の実施の形態に係る配線基板上への半導体素子の実装構造の要部を示す図である。

【図2】図1に示す配線基板に於いて、点線Aで囲んだ部分の平面形状を示す平面図である。

【図3】図2に示す配線基板に於ける線X−X断面を示す図である。

【図4】図3に示す配線基板に於いて電極端子上に導電部材を被覆した状態を示す断面図である。

【図5】配線基板上の電極端子の屈曲部に設けられた導電部材の厚みと、第1の直線状部と第2の直線状部に設けられた導電部材の厚みとを説明するための図である。

【図6】図1に示す配線基板への半導体素子の実装工程を説明するための断面図(その1)である。

【図7】図1に示す配線基板への半導体素子の実装工程を説明するための断面図(その2)である。

【図8】本発明の実施の形態の変形例1に係る配線基板の電極端子を示す部分平面図である。

【図9】本発明の実施の形態の変形例2に係る配線基板の電極端子を示す部分平面図である。

【図10】図8又は図9に示す配線基板に実装される半導体素子の外部接続用端子パッド及び凸状外部接続端子の配設構造を示す部分平面図である。

【図11】本発明の実施の形態の変形例3に係る配線基板の電極端子を示す部分平面図である。

【図12】図11に示す配線基板に実装される半導体素子の、外部接続用端子パッド及び凸状外部接続端子の配設構造を示す部分平面図である。

【図13】図11に示す配線基板上に図12に示す半導体素子を実装した構造を示す断面図である。

【図14】本発明の実施の形態の変形例4に係る配線基板の電極端子を示す部分平面図である。

【図15】図14に示す配線基板に実装される半導体素子の、外部接続用端子パッド及び凸状外部接続端子の配設構造を示す部分平面図である。

【図16】図14に示す配線基板上に図15に示す半導体素子を実装した構造を示す断面図である。

【符号の説明】

【0136】

10、130、150 半導体装置

11、81、91、131、151 配線基板

12、100、110、132、152 半導体素子

14、114、124、134、154 凸状外部接続端子

16、85、95、135、155 電極端子

16−1、85−1、95−1、135−1、155−1 第1の直線状部

16−2、85−2、95−2、135−2、155−2 第2の直線状部

16−3、85−3、95−3、135−3、155−3 屈曲部

18、117、127、137、157 外部接続用端子パッド

19 導電部材

【技術分野】

【0001】

本発明は、配線基板及び電子部品の実装構造に関し、より具体的には、導電部材を介して半導体素子等の電子部品が実装される配線基板及び前記電子部品の配線基板への実装構造に関する。

【背景技術】

【0002】

ガラスエポキシ樹脂等の絶縁性樹脂を基材とし、一方の主面に銅(Cu)等からなる導電層が選択的に配設された配線基板を用い、前記導電層に、半導体集積回路素子(以下、半導体素子と称する)の主面に配設された凸状(突起状)の外部接続端子が接続され、一方、前記配線基板の他方の主面には選択的に形成された電極の表面に球状電極端子等の外部接続端子が配設されてなる半導体装置がある。即ち、半導体素子は所謂フリップチップ(フェイスダウン)状態で、配線基板に搭載されている。

【0003】

このようなフリップチップ実装構造に於いて、ワイヤバンプとも称される凸状外部接続端子は、前記半導体素子の主面の外部接続端子用の電極パッド上にワイヤボンディング技術を用いた所謂ボールボンディング法によって形成される。

【0004】

かかる凸状外部接続端子は、前記配線基板上の導電層に対して、半田等の導電性部材をもって接続固着される。

【0005】

このような実装構造においては、半導体素子の配線基板への実装の際、当該半導体素子の凸状外部接続端子と配線基板の導電層との間に、電気的接続の安定性を十分確保する必要があり、そのため、例えば配線基板の導電層に選択的に幅広の部位を設け、当該幅広部に導電部材を厚く配設する方法が提案されている。

【0006】

即ち、導電層であるパッド上に半田層が配設された回路基板において、前記パッドの幅をその長手方向の一部で広くし、その幅広部に他の部分より半田層の厚さが厚い半田盛り上がり部を形成した構造(特許文献1参照)、或いはパッドの幅をその中間部において広くし、パッド幅広部の長さ方向の中心を部品リードの平坦部の長さの範囲内に位置させ、パッド幅広部の長さを部品リードの平坦部の長さより長くして、パッド幅広部に他の部分より大きな厚さを有するはんだ盛り上がり部を形成した構造(特許文献2参照)が提案されている。

【0007】

また、配線パターンをソルダーレジストにより選択的に被覆し、露出する配線パターンの領域を電極とした回路パターンにおいて、電極が、左右の長さ方向に沿って最大幅の箇所を1箇所だけ存在するように形成された回路パターン(特許文献3参照)、或いは回路基板上に、半田を介して半導体素子に設けられたバンプがフリップチップ実装される導体パターンを形成してなるフリップチップ実装基板において、導体パターンを配線パターンと、バンプが接合される接続パッドとにより構成し、前記配線パターンの幅寸法に対し、接続パッドの幅寸法を大きくした構造(特許文献4参照)が提案されている。

【0008】

更に、基板上に複数の配線パターンが列状に配設され、それぞれの配線パターンの第1の直線状部が互いに平行又は非平行に形成され、配線パターンの第2の直線状部が同一直線上に形成された構造(特許文献5参照)も提案されている。かかる構造にあっては、各配線パターンにおいて、第2の直線状部が、第1の直線状部と第2の直線状部とが連続する箇所に位置する各屈曲部がなす各配線パターンの列方向に、第1の直線状部から延在している。

【特許文献1】特開平5−308184号公報

【特許文献2】特開平6−216507号公報

【特許文献3】実用新案登録第3115062号公報

【特許文献4】特開2000−77471号公報

【特許文献5】特開2004−40056号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、近年、配線基板に実装される半導体素子は小型化・多端子化しており、また、このような半導体素子の配線基板に対する高密度実装が要求されている。

【0010】

従って、このような要求に対応するために半導体素子の凸状外部接続端子のピッチを微細化すると、上述の各特許文献中に開示されている態様では、配線基板の、隣接して設けられた電極(導電層)の幅広部間の間隙は狭くなる。

【0011】

そのため、半導体素子を配線基板に実装する際に、半導体素子の凸状外部接続端子と配線基板の導電層とにより形成され隣接して設けられた接続部の間に於いて、幅広部に設けられた導電部材がはみ出してしまう恐れがある。その結果、当該接続部間に於いて、ショート(短絡)或いは電流リークが発生して、半導体素子の凸状外部接続端子と配線基板の電極(導電層)との電気的接続の信頼生が低下してしまう。

【0012】

また、特許文献5に示される構造に於いては、隣接する配線パターンのそれぞれの第2の直線状部が、各配線パターンの列方向に同一直線上に配置されているため、配線パターン間のピッチを微細化することは困難である。

【0013】

そこで、本発明は、上記の点に鑑みてなされたものであって、導電部材を介して半導体素子等の電子部品が実装される配線基板及び前記電子部品の当該配線基板への実装構造であって、前記電子部品の凸状外部接続端子と配線基板の導電層との接合安定性(歩留まり)を向上させた信頼性の高い実装構造を実現する配線基板及び電子部品実装構造を提供することを本発明の目的とする。

【課題を解決するための手段】

【0014】

本発明の一観点によれば、一方の主面に、電子部品の外部接続端子が接続される電極端子が複数個、列状に配設された配線基板であって、前記電極端子は、それぞれ、第1の直線状部と、当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部と、を有することを特徴とする配線基板が提供される。

【0015】

本発明の別の観点によれば、電子部品が、導電部材を介して配線基板上の電極端子に実装される電子部品の実装構造であって、一方の主面に、それぞれ、第1の直線状部と、当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部とを具備してなる前記電極端子が、複数個、列状に配設された前記配線基板の、前記電極端子の前記屈曲部に、導電部材を介して、前記電子部品の外部接続端子が接続されてなることを特徴とする電子部品の実装構造が提供される。

【発明の効果】

【0016】

本発明によれば、導電部材を介して半導体素子等の電子部品が実装される配線基板及び前記電子部品の当該配線基板への実装構造であって、前記電子部品の凸状外部接続端子と配線基板の導電層との接合安定性(歩留まり)を向上させた信頼性の高い実装構造を実現する配線基板及び電子部品実装構造を提供することができる。

【発明を実施するための最良の形態】

【0017】

以下、本発明の実施の形態について説明する。

【0018】

なお、以下では、本発明の実施の形態に係る配線基板に実装される電子部品として、半導体素子を例にして説明するが、当該電子部品は、半導体素子に限定されるものではなく、半導体素子を樹脂封止した半導体装置、或いは受動素子等であってもよい。

【0019】

本発明の実施の形態に係る配線基板上に、半導体素子が実装された半導体装置の実装構造を、図1に示す。これを半導体装置10とする。

【0020】

同図において、当該半導体装置10にあっては、配線基板11の一方の主面(上面)上に、半導体集積回路素子(以下、半導体素子と称する)12がフリップチップ(フェイスダウン)方式をもって搭載・固着されている。

【0021】

ここで配線基板11は、ガラスエポキシ樹脂、ガラス−BT(ビスマレイミドトリアジン)、或いはポリイミド等の有機材絶縁性樹脂、又はセラミック,ガラス等の無機材料を基材とし、その表面及び/或いは内部に銅(Cu)等からなる配線層が選択的に配設されている。当該配線基板11は、インターポーザー又は支持基板と称される場合もある。

【0022】

当該配線基板11の一方の主面であって、半導体素子が搭載される主面上には、前記配線層に接続された導電層13が選択的に配設されている。

【0023】

そして、当該導電層13を選択的に覆って、即ち、半導体素子12の外部接続端子14が接続される部位及びその周囲を除いて、ソルダーレジスト層(絶縁樹脂膜)15が選択的に被覆されている。当該ソルダーレジストは、エポキシ系、アクリル系、ポリイミド系等の樹脂又はこれらの混合樹脂等からなる。

【0024】

この結果、当該ソルダーレジスト層15に設けられた開口部において、導電層13の一部が電極端子16として表出している。ソルダーレジスト層15は、導電層13に於ける半導体素子12との接続領域、即ち電極端子16の表出部を画定している。

【0025】

尚、配線基板11の他方の主面(裏面)にも、選択的に導電層が設けられ、当該導電層には、半田を主体とする球状電極端子等の外部接続端子が複数配設されるが、本実施の形態にあっては図示しない。

【0026】

一方、半導体素子12にあっては、周知の半導体製造プロセスが適用されて、シリコン(Si)等の半導体、或いはガリウム砒素(GaAs)等の化合物半導体からなる半導体基板17の一方の主面に電子回路が形成されている。

【0027】

ここでは、当該半導体素子12にあって、半導体基板17に形成されたトランジスタ等の能動素子及び/或いは容量素子等の受動素子、並びに一方の主面上に形成された多層配線層及び/或いは再配線層を図示することを省略している。

【0028】

当該半導体基板17の一方の主面には、電子回路部の周囲に位置して、外部接続用端子パッド18が列状に配設され、当該外部接続用端子パッド18それぞれの上には凸状外部接続端子14が配設されている。

【0029】

前記外部接続用端子パッド18は、アルミニウム(Al)、銅(Cu)、又はこれらの合金等をもって形成され、一方、凸状外部接続端子14は、例えば所謂ボールボンディング法によって金(Au)ボールが固着・接続されて台座部が形成され、更に当該台座部上に突出する部位からなる凸状部が一体に形成される。尚、凸状外部接続端子14の頂部は、必要に応じて平坦化処理が施される。

【0030】

また、外部接続端子パッド18の露出表面(最上層)には、予め電解めっき法又は蒸着法等により金(Au)層が形成されてもよい。

【0031】

そして、凸状外部接続端子14は、例えば銅(Cu)、銅(Cu)と金(Au)の合金、又は半田等から構成されてもよい。

【0032】

かかる半導体素子12の凸状外部接続端子14の少なくとも凸状部と、これに対応する前記配線基板11上の電極端子16は、再溶融性を有する導電部材19によって共通に被覆され、機械的・電気的に接続されている。

【0033】

当該導電部材19としては、半田からなる導電部材が効果的である。半田は再溶融性を有するが、導電性樹脂接着剤の如き他の再溶融性を有する導電材料に比べ、加熱溶融時の流動性が高く、導電部材19の材料として好適である。また、導電部材19として半田を用いる場合、配線基板11のプリコート用の半田材料を使用でき、半田プリコート技術を適用できるため便利であり、また、材料コストも安く抑えることができる。

【0034】

このように、配線基板11の一方の主面上に、フリップチップ(フェイスダウン)方式をもって搭載・固着された半導体素子12と当該配線基板11の一方の主面との間には、エポキシ系樹脂、ポリイミド系樹脂、又はアクリル系樹脂等からなる熱硬化性接着剤等の、アンダーフィル材20が充填されている。

【0035】

この様な半導体素子の実装形態が採られる半導体装置10の、前記配線基板11に於ける、電極端子16の形態について、図2乃至図4をもって説明する。

【0036】

ここでは、図1に示した構成に於いて点線により囲まれた部位Aに於ける、配線基板11の一方の主面に於ける電極端子の配設形態を図2に示す。尚、同図にあっては、半導体素子12並びにアンダーフィル材20の図示を省略している。また、当該図2に示す配線基板11に於けるX−X断面を、図3に示す。

【0037】

図2に示される様に、配線基板11の一方の主面上に配設された複数配設された導電層13を選択的に覆ってソルダーレジスト層15が配設され、当該ソルダーレジスト層15により被覆されない導電層13の一部が電極端子16として表出している。

【0038】

尚、同図に於いて、配線基板11上にフリップチップ実装される半導体素子12の外周縁部を破線Bにて示し、当該半導体素子12の凸状外部接続端子14が接続される電極端子16の接続部位を破線円Cにて示している。即ち、破線Bより右側に半導体素子が位置する。

【0039】

即ち、本実施の形態にあっては、配線基板11の一方の主面にあって、半導体素子12の凸状外部接続端子14が接続される導電層13は、電極端子16部分に於いて、第1の直線状部16−1と、当該第1の直線状部16−1の端部に於いて当該第1の直線状部16−1とは異なる方向に延びる第2の直線状部16−2と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部16−3とを具備している。

【0040】

また、隣り合う電極端子16間にあっては、第1の直線状部16−1相互間のそれぞれ、並びに第2の直線状部16−2相互間のそれぞれが平行に配設されている。

【0041】

電極端子16に於ける、第1の直線状部16−1と第2の直線状部16−2が連続する屈曲部16−3にあっては、第1の直線状部16−1と第2の直線状部16−2との間は、所定の角度(本実施の形態にあっては鈍角)をもって、略「くの字」状に屈曲している。

【0042】

当該屈曲部16−3に、半導体素子12の凸状外部接続端子14が接続される。

【0043】

そして、各電極端子16の屈曲部16−3は、接続される半導体素子12の外部接続用端子パッド18の配置に対応して、同一線上に並んで配設されている。

【0044】

この様な構造を有する電極端子16に、導電部材19を被覆した状態を図4に示す。

【0045】

前述の如く、電極端子16の表面には、再溶融性を有する導電部材19が配設され、当該導電部材19を介して、半導体素子12の凸状外部接続端子14が固着・接続される。

【0046】

本実施の形態の形態にあっては、図4に示されるように、電極端子16の屈曲部16−3に被着された導電部材19の厚さは、第1の直線状部16−1並びに第2の直線状部16−2上に被着された導電部材19の厚さよりも大きい。

【0047】

この様に、一つの電極端子16に於いて、導電部材19の厚さの差異を生ずる理由について、図5を参照して説明する。ここで、図5(a)は、電極端子16の1つを示し、図5(b)は当該電極端子16の屈曲部16−3に於ける断面(図5(a)の線a−aに於ける断面)を示し、また図5(c)は当該電極端子16の一方の直線状部16−2の断面(図5(a)の線b−b)を示している。なお、図5(c)では、一方の直線状部16−2の断面を示しているが、他方の直線状部16−1も同様の断面構造を有する。

【0048】

ここで、導電部材19の表面張力をγ、外気圧力をPoとし、電極端子16の屈曲部16−3の、図5(a)の線a−aに沿う断面に於ける導電部材19の内部圧力をPa、電極端子6の第2の直線状部16−2の、図5(a)の線b−bに沿う断面に於ける導電部材19の内部圧力をPb、電極端子16の屈曲部16−3の、図5(a)の線a−aに沿う断面に於ける導電部材19の曲率半径をRaとし、更に電極端子16の第2の直線状部16−2の図5(a)の線b−bに沿う断面に於ける導電部材19の曲率半径をRbとする。

【0049】

表面張力に関するラプラス(Laplace)の定理より、式(1)及び(2)が成立する。

【0050】

ΔPa=Po−Pa=2γ/Ra ・・・式(1)

ΔPb=Po−Pb=2γ/Rb ・・・式(2)

前記導電部材19が溶融し、その表面張力が作用して平衡状態にある時には、電極端子16の屈曲部16−3に於ける導電部材19の内部圧力Paと、電極端子16の第2の直線状部16−2に於ける導電部材19の内部圧力Pbとは等しくなり、式(1)及び式(2)より、式(3)が得られる。

【0051】

Rb=Ra ・・・式(3)

一方、前記屈曲部16−3に於ける屈曲角θと、当該屈曲部16−3の幅(最大幅)Da、及び第2の直線状部15−2の幅Dbとの間には、次の関係式(4)が成り立つ。

【0052】

Da=[1/{sin(0.5θ)}]×Db ・・・式(4)

このとき、屈曲部16−3の屈曲角θは、0度<θ<180度であり、この範囲に於いては、式(4)より、次の関係式(5)が得られる。

【0053】

Da>Db ・・・式(5)

かかる式(3)及び式(5)より、導電部材19が平衡状態及び溶融状態にあるとき、電極端子16の屈曲部16−3に於ける断面(図5(a)の線A−Aに沿う断面)上の導電部材19の厚さHa、及び電極端子16の第2の直線状部16−2に於ける断面(図5(a)の線B−Bに沿う断面)上の導電部材19の厚さHbについて、以下の関係式(6)が得られる。

【0054】

Ha>Hb ・・・式(6)

この様に、電極端子16の屈曲部16−3に於いては、第1の直線状部16−1並びに第2の直線状部16−2に比し、大なる高さ(厚さ)をもって導電部材19が配設される。

【0055】

尚、電極端子16が微細になるほど重力の影響は小さくなることから、作用原理の理解を容易にする為、式(1)乃至式(6)の説明に於いては、導電部材19に作用する重力の影響を無視し、また導電部材19は電極端子16の上面部のみに於いて濡れ形成され、曲率半径が一定であるモデルを用いている。

【0056】

この様に、電極端子16の実効的な幅が異なることにより、その表面に被着される導電部材19の厚さ(高さ)が異なる。即ち、前記図4に示すように、電極端子16上に導電部材19を被着した後、加熱してその流動性を高めると、液状になった導電部材19はその表面張力により、屈曲部16−3においてその厚みが最大となる。

【0057】

この状態に於いて導電部材19を、降温又は固化することにより、当該導電部材19は屈曲部16−3に於いて、第1の直線状部16−1並びに第2の直線状部16−2に比べ大なる厚さをもって形成される。

【0058】

即ち、電極端子16上に導電部材19を被覆形成する際、当該電極端子16に於いて、半導体素子13の凸状外部接続端子14が接続される部位である屈曲部16−3に於ける導電部材19の被覆厚さ(高さ)を厚く(高く)形成することができる。

【0059】

この様に、本実施の形態にあっては、半導体素子12の凸状外部接続端子14を配線基板11上の電極端子16へ接続する際、十分な量(厚さ)をもって導電部材19を配置することができ、半導体素子12の凸状外部接続端子14の高さの不均一性及び/或いは配線基板11の反りを吸収することができる。これにより、配線基板11上に半導体素子12をフリップチップ実装する際に、その接続安定性(歩留まり)を高めることができる。

【0060】

尚、電極端子16の屈曲部16−3の屈曲角を鋭角とすることにより、当該電極端子16に導電部材19を被覆形成する際に、当該局部的16−3に於ける被着高さをより大とすることができるが、当該屈曲角は電極端子の幅、相互の間隔などにより適宜選択される。

【0061】

この様に、導電部材19は、電極端子16の屈曲部16−3に於いて大なる厚さをもって形成される。従って、半導体素子12の凸状外部接続端子14のピッチが微細化され、これに対応して配線基板11の各電極端子16の幅が微細化された場合であっても、当該凸状外部接続端子14を大きな接続強度をもって接続することができる。

【0062】

また、半導体素子12の凸状外部接続端子14の高さのバラツキ、或いは配線基板11の反りが吸収されて、半導体素子12の凸状外部接続端子14と配線基板11のボンディング電極15との電気的接続を確実ならしめることができる。

【0063】

一方、前記複数個の電極端子16は、第1の直線状部16−1が互いに並行となる様配設され、一方第2の直線状部16−2も互いに並行となるよう配設されることから、配線基板11上に於ける当該電極端子16の高い配置密度を得ることができる。

【0064】

また、半導体素子12の凸状外部接続端子14の配設ピッチが微細化され、これに対応して配線基板11上の電極端子16の幅が微細化される場合にあっても、当該配線基板11上に半導体素子12をフリップチップ実装する際、電極端子間の短絡或いは電流リークの発生を抑制することができ、もって高い信頼性を有する実装構造を実現することができる。

【0065】

次に、図6及び図7を参照して、前記配線基板11への半導体素子12の実装工程を説明する。

【0066】

先ず、ボンディングステージ(図示せず)上に載置・固定された配線基板11と、吸着用治具21に吸着・保持された半導体素子12とを対向せしめる。(図6(a)参照)

配線基板11は、前述の如く、ガラスエポキシ樹脂、ガラス−BT(ビスマレイミドトリアジン)、或いはポリイミド等の有機材絶縁性樹脂、又はセラミック、ガラス等の無機材料を基材とし、その表面及び/或いは内部に、銅(Cu)等からなる配線層が選択的に配設されている。

【0067】

かかる配線基板11の一方の主面(上面)には、前記配線層に接続された導電層13が配設されている。当該導電層13は、ソルダーレジスト層(絶縁樹脂膜)15により選択的に被覆され、当該ソルダーレジスト層15の開口部に於いて、複数の電極端子16が露出している。

【0068】

当該電極端子16は、所謂フォトエッチング法、選択メッキ法等により形成され、前記図2に示すところの、本発明思想に従ったパターン形状に形成される。即ち、当該電極端子16は、第1の直線状部16−1と第2の直線状部16−2により構成され、当該第1の直線状部16−1と第2の直線状部16−2は、所定の角度を有する屈曲部16−3を介して連続している。

【0069】

一方、半導体素子12は、シリコン(Si)半導体基板16の主面上に配設された外部接続用端子パッド18上に、凸状外部接続端子14が配設されている。

【0070】

外部接続用端子パッド18は、通常アルミニウム(Al)、銅(Cu)或いはこれらの合金から形成され、また凸状外部接続端子14は、外部接続用端子パッド17の表面に、例えば所謂ボールボンディング法によって金(Au)ボールが固着・接続されて台座部が形成され、更に当該台座部上に突出する部位からなる凸状部をもって一体に形成されている。

【0071】

尚、当該凸状外部接続端子14の頂部に対しては、平坦化処理が施されてもよい。

【0072】

また、当該外部接続用端子パッド18表面への凸状外部接続端子14の形成法として、電解めっき法又は無電解めっき法により、金(Au)、銅(Cu)、ニッケル(Ni)等を被着させる方法を適用してもよい。

【0073】

更に、当該外部接続用端子パッド18の露出表面(最上層)には、電解めっき法又は蒸着法等により、金(Au)層を形成してもよい。

【0074】

一方、前記配線基板11の電極端子16には、予め例えば錫(Sn)を主体とする半田からなる導電部材19が、印刷法、メッキ法或いは蒸着・リフロー法等により、被覆・形成されている。

【0075】

このとき、電極端子16の屈曲部16−3に配設された導電部材19の厚さ(鉛直方向の高さ)は、前述の如く、第1の直線状部16−1並びに第2の直線状部16−2上に配設された導電部材19の厚さよりも厚い。

【0076】

この様な電極構造を有する半導体素子12の外部接続端子14を、配線基板11の電極端子16の屈曲部16−3に位置合わせし、対向させる。

【0077】

尚、前記吸着用治具21は、加熱樹段(図示せず)により、前記導電部材19の融点以上の温度(例えば180℃乃至260℃)に予め加熱しておく。

【0078】

かかる状態に於いて、半導体素子12を吸着保持する吸着用治具21を降下させ、半導体素子12の凸状外部接続端子14を配線基板11の電極端子16の表面を覆う導電部材19に接触させ、更に吸着用治具21により加重を付加して導電部材19を溶融せしめる。

【0079】

この結果、半導体素子12の凸状外部接続端子14は、少なくともその突出部が導電部材19により被覆され、半導体素子12の凸状外部接続端子14と配線基板11の電極端子16は導電部材19を介して接続される。(図6(b)参照)

尚、前記ボンディングステージを、予め50℃乃至100℃程の温度に加熱して、配線基板11を余熱しておき、導電部材19をより短時間で昇温させることもできる。

【0080】

このようにして、配線基板11上の電極端子16の屈曲部16−3に、半導体素子12の凸状外部接続端子14が接続・固着され、当該配線基板11に半導体素子12を搭載した後、当該配線基板11と半導体素子12との間に、エポキシ系樹脂、ポリイミド系樹脂、又はアクリル系樹脂等からなる熱硬化性接着剤等のアンダーフィル材20を充填する。(図7(c)参照)

当該アンダーフィル材20は、ノズル22を介して供給される。

【0081】

このようにして、配線基板11の一方の主面上に、半導体素子12がフリップチップ(フェイスダウン)方式をもって搭載・固着され、当該半導体素子12の凸状外部接続端子14と、これに対応する前記配線基板11上の電極端子16とが、導電部材19を介して機械的・電気的に接続される。(図7(d)参照)

しかる後、配線基板11の他方の主面(下面)に、半田を主体とする球状電極端子等の外部接続端子を配設(図示せず)し、半導体装置10を形成する。

【0082】

尚、本発明思想によれば、配線基板上の電極端子の形状、並びに半導体素子の外部接続端子の配設構造は、前記図2に示す形態に限られず、以下に示す変形例の如き形態を採ることもできる。

【0083】

[変形例1]

本発明の実施の形態の変形例1に係る、配線基板の電極端子形状を、図8に示す。同図に於いて、配線基板81上に搭載される半導体素子の外周端部を破線Bにて示し、当該配線基板上の電極端子に半導体素子の凸状外部接続端子が接続される部位を破線円Cにて示す。

即ち、破線Bより右側に半導体素子が位置する。

【0084】

本変形例1にあっても、配線基板81に配設される複数の電極端子85は、一定の幅を有し互いに繋がっている第1の直線状部85−1と第2の直線状部85−2とを具備する。当該第1の直線状部85−1と第2の直線状部85−2は、鈍角をなす屈曲部85−3を介して連続し、且つ互いに異なる方向に延在している。

【0085】

かかる構成にあって、当該電極端子85の第1の直線状部85−1は、比較的短い直線状(短冊状)を有し、前記半導体素子の外周端部に沿う方向に複数個、且つ互いに並行に並べられて配設されている。

【0086】

一方、第2の直線状部85−2は、第1の直線状部85−1の一方の端部に屈曲部85−3を介して連続して配設されるが、その屈曲部85−3は複数の第1の直線状部85−1に於いて交互に選択・配置され、結果として、第2の直線状部85−2は、第1の直線状部85−1の一つ置きに、異なる方向(図示される形態では左下方、右上方)に延在される。

【0087】

即ち、前記半導体素子の外周端部に沿う方向に並ぶ複数の第1の直線状部85−1に対し、その両端の一方が交互に選択されて、第2の直線状部85−2が導出されている。

【0088】

従って、屈曲部85−3、即ち半導体素子の外部接続端子が接続される部位は、半導体素子の外周端部から異なる距離をもって交互に設定されている。これにより、近接する屈曲部85−3相互の距離を実質的に大きくすることができ、当該屈曲部85−3に接続される半導体素子に於ける外部接続端子の、当該半導体素子の外周端部に沿う方向に於ける相互の間隔を、実質的に大きくすることができる。そして、同一方向に延在する第2の直線状部85−2は、相互に平行となるよう配設されている。

【0089】

[変形例2]

本発明の実施の形態の変形例2に係る配線基板の電極端子形状を、図9に示す。同図に於いて、配線基板91上に搭載される半導体素子の外周端部を、破線Bにて示す。即ち、破線Bより右側に半導体素子が位置する。また、当該配線基板上の電極端子に半導体素子の凸状外部接続端子が接続される部位を破線円にて示す。

【0090】

本変形例2にあっても、配線基板91に配設される複数の電極端子95は、一定の幅を有し互いに繋がっている第1の直線状部95−1と第2の直線状部95−2とを具備する。当該第1の直線状部95−1と第2の直線状部95−2は、鈍角をなす屈曲部95−3を介して連続し、且つ互いに異なる方向に延在している。

【0091】

かかる構成にあって、電極端子95の第1の直線状部95−1は、前記変形例1と同様に比較的短い直線状(短冊状)を有する。そして半導体素子の外周端部に沿う方向に、傾斜して2列に配設され、且つ一つの列にあっては、互いに並行に並べられて配設されている。

【0092】

そして、2列に並ぶ電極端子95の第1の直線状部95−1間にあっては、その傾斜方向が異なり、一方の列を構成する電極端子95の第1の直線状部95−1の端部が、当該他方の列を構成する電極端子95の第1の直線状部95−1の端部に近接して配設されている。

【0093】

一方、第2の直線状部95−2は、第1の直線状部95−1の他方の端部、即ち他方の列から遠い側の端部に、屈曲部95−3を介して連続して配設される。そして、当該第2の直線状部95−2は、前記列から遠ざかる方向に延在される。

【0094】

即ち、前記半導体素子の外周端部に沿う方向に、傾斜して2列に並ぶ複数の第1の直線状部95−1に対し、その一方の端部(他方の列からは遠い端部)に於いて第2の直線状部95−2が導出されている。

【0095】

従って、屈曲部95−3、即ち半導体素子の凸状外部接続端子が接続される部位は、半導体素子の外周端部から異なる寸法(距離)をもって交互に設定されている。

【0096】

このため、近接する屈曲部95−3相互の距離を実質的に大きくすることができ、当該屈曲部95−3に接続される半導体素子に於ける外部接続端子の、当該半導体素子の外周端部に沿う方向に於ける相互の間隔を、実質的に大きくすることができる。

【0097】

一方、同一方向に延在する第2の直線状部95−2は、相互に平行となるよう配設されている。

【0098】

この様な電極端子の配置構造を有する配線基板(変形例1、変形例2)に対して実装される半導体素子の外部接続用端子パッド及び凸状外部接続端子の配設構造を、図10(a)及び図10(b)に示す。当該図10(a)、図10(b)にあっては、それぞれ半導体素子の一つの隅部(コーナー部)を例示している。

【0099】

図10(a)に示す例にあっては、複数個の外部接続用端子パッド117が、半導体素子110の直線状外周縁部に沿って、且つ当該外周縁部からの距離が異なる状態をもって2列に配設されている。

【0100】

そして、外部接続用端子パッド117のそれぞれには、凸状外部接続端子114が配設されている。即ち、当該半導体素子100に於いては、その外周縁部に沿って、互いに平行な凸状外部接続端子114の列が二つ形成されている。

【0101】

一方、図10(b)に示す例にあっては、半導体素子110の外周縁部から内側に向かって延びる長方形の外部接続用端子パッド117が、当該半導体素子の直線状外周縁部に沿って、列状に配設されている。

【0102】

そして、隣接する長方形状の外部接続用端子パッド117間に於いては、長方形の長さ方向の異なる端部、即ち前記半導体素子の直線状外周縁部に近い端部、或いは遠い側の端部に、交互に、凸状外部接続端子124が配設される。即ち、当該半導体素子110にあっても、その外周縁部に沿って、互いに平行な凸状外部接続端子124の列が二つ形成されている。

【0103】

この様な凸状外部接続端子の配設形態を有する半導体素子を、前記図8或いは図9に示される配線基板(81、91)上にフリップチップ実装する際には、当該半導体素子の直線状外周縁部に沿って2列に配設された凸状外部接続端子が、配線基板上に於いて2列に配設された電極端子の屈曲部(85−3、95−3)に接続される。

【0104】

この時、2列の屈曲部のそれぞれに於いて、凸状外部接続端子は、厚く被着された(多量の)導電部材をもって、屈曲部に対して強固に接続・固着される。また、同時に当該凸状外部接続端子の高さのバラツキ、或いは配線基板の反りが吸収される。これにより、半導体素子と配線基板上の電極端子は、高い接続安定性(歩留り)及び高い接続信頼性をもって接続される。

【0105】

尚、前述の如く、配線基板上に列状に配設される電極端子の屈曲部、即ち半導体素子の外部接続端子が接続される部位は、近接する相互間に於いて、半導体素子の外周端部から異なる寸法(距離)をもって交互に設定されている。

【0106】

従って、近接する屈曲部相互の距離は実質的に大きく、当該屈曲部に接続される半導体素子に於ける外部接続端子の間隔を実質的に大きくすることができる。これにより、外部接続端子間の絶縁耐圧が確保され、もって、外部接続端子を高密度に備えた半導体素子のフリップチップ実装を行うことができる。

【0107】

[変形例3]

本発明の実施の形態の変形例3に係る配線基板の電極端子形状を、図11に示す。同図に於いて、配線基板131上に搭載される半導体素子の外周端部を破線Bにて示す。即ち、破線Bより右側に半導体素子が位置する。また、当該配線基板上の電極端子に半導体素子の凸状外部接続端子が接続される部位を破線円にて示す。

【0108】

本変形例3にあっては、配線基板131上に配設される複数の電極端子135は、一定の幅を有する第1の直線状部135−1と、当該第1の直線状部135−1の両端部から延在される第2の直線状部135−2A,135−2Bとを具備する。

【0109】

そして、第1の直線状部135−1は、半導体素子の外周端部に沿う方向に複数個配設され、二つの第2の直線状部135−2A,135−2Bは、当該第1の直線状部135−1の両端部に於いて、鈍角をなす屈曲部135−3A,135−3Bを介して連続し、且つ互いに異なる方向に延在している。かかる構成によれば、一つの電極配線135に於いて、2つの屈曲部、即ち半導体素子の凸状外部接続端子の接続部が設定される。

【0110】

この時、半導体素子の外周端部に沿って並ぶ第1の直線状部135−1は、その長さが互いに等しいことから、2つの屈曲部135−3A,135−3Bはそれぞれ半導体素子の外周端部に沿って並行に位置して配設され、列状を呈する。

【0111】

尚、図において、15はソルダーレジスト層を指す。

【0112】

この様な電極端子の配設構造を有する配線基板131に対してフリップチップ実装される半導体素子の外部接続用丹治パッド及び凸状外部接続端子の配設構造を、図12に示す。当該図12に於いても、半導体素子の一つの隅部(コーナー部)を例示している。即ち、半導体素子132の一つの直線状外周縁部に沿って、当該外周縁部から内側に延びる長方形状の外部接続用端子パッド137が複数個、列状に且つ互いに並行に配設されている。

【0113】

そして、一つの長方形状の外部接続用端子パッド137に於いては、長方形の長手方向に並んで二つの凸状外部接続端子134A,134Bが配設される。即ち、当該半導体素子132にあっても、その一つの直線状外周縁部に沿って、互いに平行な凸状外部接続端子134が、2列に配設される。

【0114】

この様な凸状外部接続端子の配設構造を有する半導体素子132を、前記配線基板131上にフリップチップ実装した状態を、図13に示す。

【0115】

即ち、配線基板131の一方の主面上に、半導体素子132がフリップチップ(フェイスダウン)方式をもって搭載され、当該半導体素子132の凸状外部接続端子134と、これに対応する前記配線基板131上の電極端子135とが、導電部材19を介して機械的・電気的に接続される。

【0116】

ここで、半導体素子132の電極端子パッド137に配設された二つの凸状外部接続端子134A、134Bは、配線基板131上の電極端子135−1の両端屈曲部135−3A,135−3Bに対して導電部材19を介して接続される。

【0117】

即ち、半導体素子132の凸状外部接続端子134は、一つの電極端子135に対して、2箇所に於いて接続され、且つ二つの凸状外部接続端子134A,134Bはそれぞれ、厚く被着された(多量の)導電部材19をもって、対応する屈曲部に接続・固着される。

【0118】

また、この時、当該凸状外部接続端子134の高さのバラツキ、或いは配線基板131の反りが吸収され、半導体素子132と配線基板上の電極端子134は、高い接続安定性(歩留り)及び高い接続信頼性をもって接続される。

【0119】

尚、図において、20はアンダーフィル材を指す。

【0120】

[変形例4]

本発明の実施の形態の変形例4に係る配線基板の電極端子形状を、図14に示す。同図に於いて、配線基板151上に搭載される半導体素子の外周端部を破線Bにて示す。即ち、破線Bより右側に半導体素子が位置する。また、当該配線基板上の電極端子に半導体素子の凸状外部接続端子が接続される部位を破線円にて示す。

【0121】

本変形例4にあっては、配線基板151上に配設される複数の電極端子155は、一定の幅を有する第1の直線状部155−1と、当該第1の直線状部155−1の両端部から延在される第2の直線状部155−2A,155−2Bとを具備する。

【0122】

そして、当該第1の直線状部155−1は、搭載される半導体素子の外周端部に沿う方向に対して傾斜し、且つ当該半導体素子の外周端部に沿う方向に、複数個互いに並行に配設される。

【0123】

一方、第2の直線状部155−2A及び155−2Bは、前記第1の直線状部155−1の両端部に於いて、ほぼ直角をなす屈曲部155−3A,155−3Bを介して連続し、且つ互いに反対方向に延在している。そして、当該第2の直線状部155−2A、第2の直線状部155−2Bもそれぞれ、半導体素子の外周端部に沿う方向に、複数個互いに並行に配設される。

【0124】

かかる構成に於いても、一つの電極端子155に於いて、2つの屈曲部、即ち半導体素子の凸状外部接続端子の接続部が設定される。この時、半導体素子の外周端部に沿って隣接する第1の直線状部155−1は、その長さが互いに等しいことから、2つの屈曲部155−3A,155−3Bはそれぞれ半導体素子の外周端部に沿って並行に位置して配設され、列状を呈する。

【0125】

尚、図において、15はソルダーレジスト層を指す。

【0126】

この様な電極端子の配設構造を有する配線基板151にフリップチップ実装される半導体素子152の外部接続用丹治パッド及び凸状外部接続端子の配設構造を、図15に示す。当該図15に於いても、半導体素子の一つの隅部(コーナー部)を例示している。

【0127】

即ち、半導体素子152の直線状外周縁部に沿って、矩形形状を有する外部接続用端子パッド157が、列状に配設されている。そして、当該外部接続用端子パッド157に於いては、矩形形状の対角線にほぼ沿って、凸状外部接続端子154A,154Bが並び配設されている。即ち、当該半導体素子152にあっても、その一つの外周縁部に沿って、凸状外部接続端子154が2列に、ほぼ平行に配設される。

【0128】

この様な凸状外部接続端子の配設形態を有する半導体素子152を、前記配線基板131上にフリップチップ実装した状態を、図16に示す。

【0129】

即ち、配線基板151の一方の主面上に、半導体素子152がフリップチップ(フェイスダウン)方式をもって搭載され、当該半導体素子152の凸状外部接続端子154と、これに対応する前記配線基板151上の電極端子154とが、導電部材19を介して機械的・電気的に接続される。ここで、半導体素子152の凸状外部接続端子154A、154Bは、対応する電極端子155−1の屈曲部155−3A,155−3Bに於いて、導電部材19を介して接続される。

【0130】

即ち、半導体素子152の一つの凸状外部接続用端子パッド157は、配線基板上の一つの電極端子155に対して、2箇所に於いて接続され、且つ二つの凸状外部接続端子154A,154Bはそれぞれ、厚く被着された(多量の)導電部材19をもって、対応する屈曲部位に於いて電極端子155に接続・固着される。

【0131】

また、この時、当該凸状外部接続端子154の高さのバラツキ、或いは配線基板151の反りが吸収され、半導体素子152と配線基板上の電極端子155は、高い接続安定性(歩留り)及び高い接続信頼性をもって接続される。

【0132】

尚、図において、20はアンダーフィル材を指す。

【0133】

以上、本発明の実施の形態及びその変形例について詳述したが、本発明は特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形及び変更が可能である。

【0134】

以上の説明に関し、更に以下の項を開示する。

(付記1)

一方の主面に、電子部品の外部接続端子が接続される電極端子が複数個、列状に配設された配線基板であって、

前記電極端子は、それぞれ、

第1の直線状部と、

当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、

前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部と

を有することを特徴とする配線基板。

(付記2)

付記1記載の配線基板であって、

前記複数個の電極端子は、前記第1の直線状部が互いに並行となる様配設されてなることを特徴とする配線基板。

(付記3)

付記1又は2記載の配線基板であって、

前記複数個の電極端子は、前記第2の直線状部が互いに並行となるよう配設されてなることを特徴とする配線基板。

(付記4)

付記1乃至3記載の配線基板であって、

前記複数個の電極端子は、前記屈曲部が列状に配設されてなることを特徴とする配線基板。

(付記5)

付記4記載の配線基板であって、

前記主面において、複数の前記電極端子から構成される列が、互いに平行に複数形成されており、

一の列を構成する電極端子の屈曲部と、他の列を構成する電極端子の屈曲部とは、前記列の形成方向においてずれて位置していることを特徴とする配線基板。

(付記6)

付記1記載の配線基板であって、

前記複数個の電極端子は、前記屈曲部が複数の列状に配設され、当該複数の列は互いに並行であることを特徴とする配線基板。

(付記7)

付記1記載の配線基板であって、

前記複数個の電極端子は、それぞれ前記第1の直線状部の両端部に前記屈曲部が配設されてなること特徴とする配線基板。

(付記8)

付記7記載の配線基板であって、

前記第1の直線状部の一の端部に配設された屈曲部と、前記第1の直線状部の他の端部に配設された屈曲部は、前記電極端子の配列方向と略垂直の方向に並んで配設されてなることを特徴とする配線基板。

(付記9)

付記7記載の配線基板であって、

前記第1の直線状部の一の端部に配設された屈曲部と、前記第1の直線状部の他の端部に配設された屈曲部は、前記電極端子の配列方向においてずれて配設されてなることを特徴とする配線基板。

(付記10)

付記1乃至9いずれか一項記載の配線基板であって、

前記第2の直線状部は、前記第1の直線状部の端部に於いて前記第1の直線状部に対して鋭角を為して延びていることを特徴とする配線基板。

(付記11)

電子部品が、導電部材を介して配線基板上の電極端子に実装される電子部品の実装構造であって、

一方の主面に、それぞれ、第1の直線状部と、当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部とを具備してなる前記電極端子が、複数個、列状に配設された前記配線基板の、前記電極端子の前記屈曲部に、導電部材を介して、前記電子部品の外部接続端子が接続されてなることを特徴とする電子部品の実装構造。

(付記12)

付記11記載の電子部品の実装構造であって、

前記電子部品の前記外部接続端子は、凸状を有することを特徴とする電子部品の実装構造。

(付記13)

付記11記載の電子部品の実装構造であって、

前記電子部品の前記外部接続端子は、互いに並行する複数の列状をもって、前記配線基板上の前記電極端子に接続されてなることを特徴とする電子部品の実装構造。

(付記14)

付記11記載の電子部品の実装構造であって、

前記電子部品の電極パッドに於ける前記外部接続端子の形態に対応して、前記配線基板上の前記電極端子の前記屈曲部が配設され、前記電子部品の前記外部接続端子と前記電極端子の前記屈曲部は、前記導電部材を介して接続されてなることを特徴とする電子部品の実装構造。

(付記15)

付記11乃至14いずれか一項記載の電子部品の実装構造であって、

前記導電部材は、半田を含む材料から構成されることを特徴とする電子部品の実装構造。

【図面の簡単な説明】

【0135】

【図1】本発明の実施の形態に係る配線基板上への半導体素子の実装構造の要部を示す図である。

【図2】図1に示す配線基板に於いて、点線Aで囲んだ部分の平面形状を示す平面図である。

【図3】図2に示す配線基板に於ける線X−X断面を示す図である。

【図4】図3に示す配線基板に於いて電極端子上に導電部材を被覆した状態を示す断面図である。

【図5】配線基板上の電極端子の屈曲部に設けられた導電部材の厚みと、第1の直線状部と第2の直線状部に設けられた導電部材の厚みとを説明するための図である。

【図6】図1に示す配線基板への半導体素子の実装工程を説明するための断面図(その1)である。

【図7】図1に示す配線基板への半導体素子の実装工程を説明するための断面図(その2)である。

【図8】本発明の実施の形態の変形例1に係る配線基板の電極端子を示す部分平面図である。

【図9】本発明の実施の形態の変形例2に係る配線基板の電極端子を示す部分平面図である。

【図10】図8又は図9に示す配線基板に実装される半導体素子の外部接続用端子パッド及び凸状外部接続端子の配設構造を示す部分平面図である。

【図11】本発明の実施の形態の変形例3に係る配線基板の電極端子を示す部分平面図である。

【図12】図11に示す配線基板に実装される半導体素子の、外部接続用端子パッド及び凸状外部接続端子の配設構造を示す部分平面図である。

【図13】図11に示す配線基板上に図12に示す半導体素子を実装した構造を示す断面図である。

【図14】本発明の実施の形態の変形例4に係る配線基板の電極端子を示す部分平面図である。

【図15】図14に示す配線基板に実装される半導体素子の、外部接続用端子パッド及び凸状外部接続端子の配設構造を示す部分平面図である。

【図16】図14に示す配線基板上に図15に示す半導体素子を実装した構造を示す断面図である。

【符号の説明】

【0136】

10、130、150 半導体装置

11、81、91、131、151 配線基板

12、100、110、132、152 半導体素子

14、114、124、134、154 凸状外部接続端子

16、85、95、135、155 電極端子

16−1、85−1、95−1、135−1、155−1 第1の直線状部

16−2、85−2、95−2、135−2、155−2 第2の直線状部

16−3、85−3、95−3、135−3、155−3 屈曲部

18、117、127、137、157 外部接続用端子パッド

19 導電部材

【特許請求の範囲】

【請求項1】

一方の主面に、電子部品の外部接続端子が接続される電極端子が複数個、列状に配設された配線基板であって、

前記電極端子は、それぞれ、

第1の直線状部と、

当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、

前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部と

を有することを特徴とする配線基板。

【請求項2】

請求項1記載の配線基板であって、

前記複数個の電極端子は、前記第1の直線状部が互いに並行となる様配設されてなることを特徴とする配線基板。

【請求項3】

請求項1又は2記載の配線基板であって、

前記複数個の電極端子は、前記第2の直線状部が互いに並行となるよう配設されてなることを特徴とする配線基板。

【請求項4】

請求項1乃至3記載の配線基板であって、

前記複数個の電極端子は、前記屈曲部が列状に配設されてなることを特徴とする配線基板。

【請求項5】

請求項1記載の配線基板であって、

前記複数個の電極端子は、前記屈曲部が複数の列状に配設され、当該複数の列は互いに並行であることを特徴とする配線基板。

【請求項6】

請求項1記載の配線基板であって、

前記複数個の電極端子は、それぞれ前記第1の直線状部の両端部に前記屈曲部が配設されてなること特徴とする配線基板。

【請求項7】

電子部品が、導電部材を介して配線基板上の電極端子に実装される電子部品の実装構造であって、

一方の主面に、それぞれ、第1の直線状部と、当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部とを具備してなる前記電極端子が、複数個、列状に配設された前記配線基板の、前記電極端子の前記屈曲部に、導電部材を介して、前記電子部品の外部接続端子が接続されてなることを特徴とする電子部品の実装構造。

【請求項8】

請求項7記載の電子部品の実装構造であって、

前記電子部品の前記外部接続端子は、凸状を有することを特徴とする電子部品の実装構造。

【請求項9】

請求項7記載の電子部品の実装構造であって、

前記電子部品の前記外部接続端子は、互いに並行する複数の列状をもって、前記配線基板上の前記電極端子に接続されてなることを特徴とする電子部品の実装構造。

【請求項10】

請求項7記載の電子部品の実装構造であって、

前記電子部品の電極パッドに於ける前記外部接続端子の形態に対応して、前記配線基板上の前記電極端子の前記屈曲部が配設され、前記電子部品の前記外部接続端子と前記電極端子の前記屈曲部は、前記導電部材を介して接続されてなることを特徴とする電子部品の実装構造。

【請求項1】

一方の主面に、電子部品の外部接続端子が接続される電極端子が複数個、列状に配設された配線基板であって、

前記電極端子は、それぞれ、

第1の直線状部と、

当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、

前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部と

を有することを特徴とする配線基板。

【請求項2】

請求項1記載の配線基板であって、

前記複数個の電極端子は、前記第1の直線状部が互いに並行となる様配設されてなることを特徴とする配線基板。

【請求項3】

請求項1又は2記載の配線基板であって、

前記複数個の電極端子は、前記第2の直線状部が互いに並行となるよう配設されてなることを特徴とする配線基板。

【請求項4】

請求項1乃至3記載の配線基板であって、

前記複数個の電極端子は、前記屈曲部が列状に配設されてなることを特徴とする配線基板。

【請求項5】

請求項1記載の配線基板であって、

前記複数個の電極端子は、前記屈曲部が複数の列状に配設され、当該複数の列は互いに並行であることを特徴とする配線基板。

【請求項6】

請求項1記載の配線基板であって、

前記複数個の電極端子は、それぞれ前記第1の直線状部の両端部に前記屈曲部が配設されてなること特徴とする配線基板。

【請求項7】

電子部品が、導電部材を介して配線基板上の電極端子に実装される電子部品の実装構造であって、

一方の主面に、それぞれ、第1の直線状部と、当該第1の直線状部の端部に於いて当該第1の直線状部とは異なる方向に延びる第2の直線状部と、前記第1の直線状部と前記第2の直線状部とが連続する部位に於ける屈曲部とを具備してなる前記電極端子が、複数個、列状に配設された前記配線基板の、前記電極端子の前記屈曲部に、導電部材を介して、前記電子部品の外部接続端子が接続されてなることを特徴とする電子部品の実装構造。

【請求項8】

請求項7記載の電子部品の実装構造であって、

前記電子部品の前記外部接続端子は、凸状を有することを特徴とする電子部品の実装構造。

【請求項9】

請求項7記載の電子部品の実装構造であって、

前記電子部品の前記外部接続端子は、互いに並行する複数の列状をもって、前記配線基板上の前記電極端子に接続されてなることを特徴とする電子部品の実装構造。

【請求項10】

請求項7記載の電子部品の実装構造であって、

前記電子部品の電極パッドに於ける前記外部接続端子の形態に対応して、前記配線基板上の前記電極端子の前記屈曲部が配設され、前記電子部品の前記外部接続端子と前記電極端子の前記屈曲部は、前記導電部材を介して接続されてなることを特徴とする電子部品の実装構造。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2008−227050(P2008−227050A)

【公開日】平成20年9月25日(2008.9.25)

【国際特許分類】

【出願番号】特願2007−61531(P2007−61531)

【出願日】平成19年3月12日(2007.3.12)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成20年9月25日(2008.9.25)

【国際特許分類】

【出願日】平成19年3月12日(2007.3.12)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]