配線基板

【課題】ダンピング抵抗に破断が発生することがなく、搭載する半導体素子を常に正常に作動させることが可能な配線基板を提供すること。

【解決手段】絶縁層1bの表面に、半導体素子の電極または電気回路基板が接続される接続面3dを有する複数の接続パッド3を具備して成る配線基板であって、接続パッド3の一部は、絶縁層1bの側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層3aと接続面3dの側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層3bとが積層されて成り、抵抗体層3bが接続面3dと主導体層3aとの間に電気的に直列に接続されている。

【解決手段】絶縁層1bの表面に、半導体素子の電極または電気回路基板が接続される接続面3dを有する複数の接続パッド3を具備して成る配線基板であって、接続パッド3の一部は、絶縁層1bの側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層3aと接続面3dの側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層3bとが積層されて成り、抵抗体層3bが接続面3dと主導体層3aとの間に電気的に直列に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路素子等の半導体素子を搭載するために用いられる配線基板に関するものである。

【背景技術】

【0002】

半導体集積回路素子等の半導体素子を搭載するために用いられる配線基板には、ガラス基材および熱硬化性樹脂から成る絶縁板と銅箔等から成る配線導体とを交互に複数積層して成るプリント配線基板や、ガラス基材および熱硬化性樹脂から成る絶縁板上に熱硬化性樹脂およびフィラーから成る絶縁層と銅めっき層から成る配線導体とを複数積層して成るビルドアップ配線基板が用いられている。

【0003】

このような配線基板の上面には半導体素子の電極と接続するための半導体素子接続パッドが格子状の並びに配列されている。また、配線基板の下面には外部の電気回路基板に接続するための外部接続パッドが格子状の並びに配列されている。これらの半導体素子接続パッドと外部接続パッドとの間は、帯状やベタ状の配線導体を介して接続されている。なお帯状の配線導体は信号用に利用され、ベタ状の配線導体は接地用や電源用に用いられる。さらに半導体素子接続パッド上には半導体素子の電極と半導体素子接続パッドとを接合するための半田バンプが溶着されている。

【0004】

そして、このような配線基板においては、半導体素子をその各電極がそれぞれ対応する半田バンプに当接するようにして配線基板の上面に載置するとともに、これらを加熱して半田バンプを溶融させて半田バンプと半導体素子の電極とを接合させることによって、半導体素子が配線基板上に搭載される。

【0005】

ところで、このような配線基板においては、信号が伝播する信号用の配線導体の特性インピーダンスは、信号の減衰を極小とするためにシングルエンド信号では50Ω前後、ディファレンス信号では100Ω前後に設定されている。他方、半導体素子の入力インピーダンスは数百MΩ以上であり、出力インピーダンスは数Ω〜数十Ωであることから配線導体の特性インピーダンスとは大きく相違する。そのため信号用の配線導体を通して半導体素子に高速の信号の出し入れを行った場合、信号用の配線導体を伝わる信号に入出力端における反射波が重なりあうノイズが発生し、そのノイズにより半導体素子を正常に作動させることができない問題があった。

【0006】

そこで、上記問題を解消するために、図3に示すように、絶縁層21上の信号用の帯状の配線導体22を、薄膜抵抗体層22aとその上の主導体層22bとから形成し、主導体層22bの一部を除去することにより配線導体22に薄膜抵抗体層22aから成るダンピング抵抗を接続させることが提案されている。このように信号用の配線導体22に薄膜抵抗体層22aから成るダンピング抵抗を接続させることにより、配線導体22の特性インピーダンスと半導体素子の特性インピーダンスの相違に起因して発生するノイズをダンピング抵抗で減衰させ、それにより半導体素子を正常に作動させることが可能となる。

【0007】

しかしながら、信号用の帯状の配線導体を、薄膜抵抗体層とその上の主導体層とから形成し、主導体層の一部を除去することにより配線導体の一部に薄膜抵抗体層から成るダンピング抵抗を接続した場合、配線基板に半導体素子を搭載する際の熱や半導体素子の作動時に発生する熱が繰り返し印加されると、その熱により発生する熱応力が主導体層から露出する薄膜抵抗層の両端部に集中して作用し、それによりダンピング抵抗を破断させてしまうというという問題があった。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2005−5354号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明は、かかる従来の問題に鑑み案出されたものであり、その目的は、ダンピング抵抗に破断が発生することがなく、搭載する半導体素子を常に正常に作動させることが可能な配線基板を提供することにある。

【課題を解決するための手段】

【0010】

本発明の配線基板は、絶縁層の表面に、半導体素子の電極または電気回路基板が接続される接続面を有する複数の接続パッドを具備して成る配線基板であって、前記接続パッドの一部は、前記絶縁層の側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層と前記接続面の側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層とが積層されて成り、該抵抗体層が前記接続面と前記主導体層との間に電気的に直列に接続されていることを特徴とするものである。

【発明の効果】

【0011】

本発明の配線基板によれば、前記接続パッドは、前記絶縁層の側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層と前記接続面の側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層とが積層されて成り、該抵抗体層が前記接続面と前記主導体層との間に電気的に直列に接続されていることから、配線基板に半導体素子を搭載する際の熱や半導体素子の作動時に発生する熱が繰り返し印加されても、その熱により発生する熱応力が抵抗体層に集中して印加されることはなく、抵抗体層が破断するようなことがない。したがって、搭載する半導体素子を常に正常に作動させることが可能な配線基板を提供することができる。

【図面の簡単な説明】

【0012】

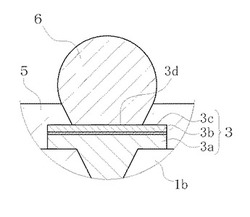

【図1】図1は、本発明の配線基板の実施形態の一例を示す概略断面図である。

【図2】図2は、図1に示す配線基板の要部拡大断面図である。

【図3】図3は、従来の配線基板を示す要部拡大断面図である。

【発明を実施するための形態】

【0013】

次に、本発明の配線基板の実施形態の一例を図1および図2を基にして詳細に説明する。図1は本発明の配線基板10の実施形態の一例を示す概略断面図であり、図2は図1に示す配線基板10の要部拡大断面図である。これらの図中、1は絶縁基板、2は配線導体、3は半導体素子接続パッド、4は外部接続パッド、5はソルダーレジスト層、6は半田バンプであり、主としてこれらにより本発明の配線基板10が構成される。

【0014】

なお、本例の配線基板10では、ガラス織物に熱硬化性樹脂を含浸させて成る絶縁板1aの上下面に熱硬化性樹脂から成る絶縁層1bを2層ずつ積層して絶縁基板1を形成しており、最表層の絶縁層1b上にソルダーレジスト層5が積層されている。また絶縁基板1の上面中央部には半導体素子Sが搭載される搭載部Aが形成されており、この搭載部Aにはそれぞれ半導体素子Sの電極Tが電気的に接続される半導体素子接続パッド3が形成されている。また、絶縁基板1の下面には外部電気回路基板に電気的に接続される外部接続パッド4が形成されており、絶縁基板1の上面から下面にかけてはそれぞれ対応する半導体素子パッド3と外部接続パッド4とを互いに電気的に接続する帯状やベタ状の配線導体2が配設されている。なお帯状の配線導体2は信号用に利用され、ベタ状の配線導体2は接地用や電源用に用いられる。さらに、半導体素子接続パッド3には半田バンプ6が溶着されている。

【0015】

そして、この配線基板10においては、半導体素子Sをその各電極Tがそれぞれ対応する半田バンプ6に当接するようにして配線基板10の上面に載置するとともに、これらを例えば電気炉等の加熱装置で約260℃程度に加熱して半田バンプ6を溶融させて半田バンプ6と半導体素子Sの電極Tとを接合させることによって、半導体素子Sが配線基板10上に搭載される。

【0016】

絶縁板1aは、本例の配線基板10におけるコア部材であり、例えばガラス繊維束を縦横に織り込んだガラス織物にエポキシ樹脂やビスマレイミドトリアジン樹脂等の熱硬化性樹脂を含浸させて成る。この絶縁板1aは、例えば厚みが0.3〜1.5mm程度であり、その上面から下面にかけて直径が0.1〜1mm程度の複数のスルーホール8を有している。そして、その上下面および各スルーホール8の内面には配線導体2の一部が被着されており、上下面の配線導体2がスルーホール8を介して電気的に接続されている。

【0017】

このような絶縁板1aは、ガラス織物に未硬化の熱硬化性樹脂を含浸させた絶縁シートを熱硬化させた後、これに上面から下面にかけてドリル加工を施すことにより製作される。なお、絶縁板1a上下面の配線導体2は、絶縁板1a用の絶縁シートの上下全面に厚みが3〜50μm程度の銅箔を貼着しておくとともにこの銅箔をシートの硬化後にエッチング加工することにより所定のパターンに形成される。また、スルーホール8内面の配線導体2は、絶縁板1aにスルーホール8を設けた後に、このスルーホール8内面に無電解めっき法および電解めっき法により厚みが3〜50μm程度の銅めっき膜を析出させることにより形成される。

【0018】

さらに、絶縁板1aは、そのスルーホール8の内部にエポキシ樹脂やビスマレイミドトリアジン樹脂等の熱硬化性樹脂から成る孔埋め樹脂9が充填されている。孔埋め樹脂9は、スルーホール8を塞ぐことによりスルーホール8の直上および直下に配線導体2および各絶縁層1bを形成可能とするためのものであり、未硬化のペースト状の熱硬化性樹脂をスルーホール8内にスクリーン印刷法により充填し、それを熱硬化させた後、その上下面を略平坦に研磨することにより形成される。そして、この孔埋め樹脂9を含む絶縁板1aの上下面に絶縁層1bがそれぞれ2層ずつ積層されている。

【0019】

絶縁板1aの上下面に積層された各絶縁層1bは、エポキシ樹脂やビスマレイミドトリアジン樹脂等の熱硬化性樹脂から成り、それぞれの厚みが10〜60μm程度であり、各層の上面から下面にかけて直径が20〜100μm程度の複数のビアホール11を有している。これらの各絶縁層1bは、配線導体2を高密度に配線するための絶縁間隔を提供するためのものである。そして、上層の配線導体2と下層の配線導体2とをビアホール11を介して電気的に接続することにより高密度配線が立体的に形成可能となっている。このような各絶縁層1bは、厚みが10〜60μm程度の未硬化の熱硬化性樹脂から成る絶縁フィルムを絶縁板1aの上下面に貼着し、これを熱硬化させるとともにレーザ加工によりビアホール11を穿孔し、さらにその上に同様にして次の絶縁層1bを順次積み重ねることによって形成される。なお、各絶縁層1bの表面およびビアホール11内に被着された配線導体2は、各絶縁層1bを形成する毎に各絶縁層1bの表面およびビアホール11内に5〜25μm程度の厚みの銅めっき膜を周知のセミアディティブ法等のパターン形成法により所定のパターンに被着させることによって形成される。

【0020】

絶縁基板1の上面の搭載部Aに形成された半導体素子接続パッド3は、ソルダーレジスト層5から露出する直径が50〜150μm程度の円形であり、搭載部A内の領域にピッチが100〜250μm程度の格子状の並びに多数配列形成されている。このような半導体素子接続パッド3は、半導体素子Sの電極Tを配線導体2に電気的に接続するための端子部として機能し、最上層の絶縁層1b上に形成された配線導体2の一部を、ソルダーレジスト層5に設けた直径が50〜150μm程度の円形の開口部5a内に露出させることにより形成されている。

【0021】

また、絶縁基板1の下面に形成された外部接続パッド4は、ソルダーレジスト層5から露出する直径が200〜700μm程度の円形であり、絶縁基板1下面の略全領域にピッチが500〜1000μm程度の格子状の並びに多数配列形成されている。外部接続パッド4は、配線導体2を外部電気回路基板に電気的に接続するための端子部として機能し、最下層の絶縁層1b上に形成された配線導体2の一部を、ソルダーレジスト層5に設けた直径が200〜700μmの円形の開口部5b内に露出させることにより形成されている。

【0022】

ソルダーレジスト層5は、アクリル変性エポキシ樹脂等の感光性を有する熱硬化性の樹脂から成り、その厚みが10〜30μm程度であり、上述したように半導体素子接続パッド3を露出させる開口部5aや外部接続パッド4を露出させる開口部5bを有している。それにより最表層における配線導体2を保護するとともに、開口部5aや5bを介して半導体素子接続パッド3や外部接続パッド4と半導体素子Sや外部電気回路基板との接続を可能としている。このようなソルダーレジスト層5は、感光性を有する樹脂ペーストまたは樹脂フィルムを最上層および最下層の絶縁層1bの表面に塗布または貼着するとともにフォトリソグラフィー技術を採用して開口部5aや5bを有するパターンに露光および現像した後、紫外線硬化および熱硬化させることにより形成される。

【0023】

半導体素子接続パッド3に溶着された半田バンプ6は、例えば錫−銀合金や錫−銀−銅合金等の鉛フリー半田から成り、半導体素子接続パッド3と半導体素子Sの電極Tとを電気的に接続するための接続部材として機能する。そして、半導体素子Sの電極Tを半田バンプ6に接触させた状態で半田バンプ6を加熱溶融させることにより半導体素子接続パッド3と半導体素子Sの電極Tとが半田バンプ6を介して電気的に接続されることとなる。このように半田バンプ6を半導体素子接続パッド3に予め溶着させておくことにより半導体素子接続パッド3への電極Tの接続の作業性が極めて良好なものとなる。なお、半導体素子Sの電極Tを半田バンプ6に接触させるのに先立って、半田バンプ6の上端部をプレスして平坦にしておくと、半導体素子Sの電極Tと半田バンプ6とを接触させることが容易かつ確実なものとなる。したがって、半導体素子Sの電極Tを半田バンプ6に接触させるのに先立って、半田バンプ6の上端部をプレスして平坦にしておくことが好ましい。

【0024】

さらに本発明においては、図2に示すように、半導体素子接続パッド3のうち、特に高速信号用の半導体素子接続パッド3は、主導体層3aと抵抗体層3bと被覆層3cとの積層体により形成されている。そして被覆層3cの表面が半導体素子Sの電極Tが半田バンプ6を介して接続される接続面3dを形成している。

【0025】

主導体層3aは、配線導体2と同じ材料であり、体積抵抗率が100μΩ・cm以下の低抵抗材料から成り、5〜25μm程度の厚みである。主導体層3aは、その体積抵抗率が100μΩ・cmを超えると、配線導体2の電気抵抗が高くなり、信号用の配線導体2においては信号の減衰が大きくなったり、接地や電源用の配線導体2においては、半導体素子Sに供給する電源電位の低下をもたらしたりする。したがって、主導体層3aの体積抵抗率は、100μΩ・cm以下であることが好ましい。このような低抵抗材料としては、例えば銅や銀、金、ニッケル、アルミニウム等が例示できるが、加工性や経済性等の観点から銅が好ましい。なお、主導体層3aを形成するには、主導体層3aが例えば銅から成る場合、配線導体2の形成と同じセミアディティブ法を採用することができる。

【0026】

抵抗体層3bは、体積抵抗率が10Ω・cm以上の高抵抗材料の薄膜から成り、100〜1000nm程度の厚みである。この抵抗体層3bは、ダンピング抵抗として機能するものであり、配線導体2の特性インピーダンスと半導体素子Sの特性インピーダンスの相違に起因して発生するノイズを減衰させ、それにより半導体素子Sを正常に作動させることを可能とするものである。抵抗体層3bの体積抵抗率が10Ω・cm未満であると、ダンピング抵抗としての抵抗値を抵抗体層3bにより付与することが困難となる。したがって、抵抗体層3bの体積抵抗率は10Ω・cm以上であることが好ましい。このような高抵抗材料としては、例えば、ゲルマニウムやフェライト等が例示できるが、加工性や透磁率の観点からゲルマニウムが好ましい。また、抵抗体層3bの厚みが100nm未満であるか1000nmを超えると、抵抗体層3bにダンピング抵抗として必要な抵抗値を付与することが困難となる。したがって、抵抗体層3bの厚みは、100〜1000nmの範囲が好ましい。なお、抵抗体層3bを形成するには、抵抗体層3bが例えばゲルマニウムから成る場合、周知のスパッタリング法により主導体層3aの表面にゲルマニウムの薄膜を100〜1000nm厚みに被着させる方法を採用することができる。

【0027】

被覆層3cは、半田との濡れ性に優れる低抵抗材料から成り、1〜10μm程度の厚みである。この被覆層3cは、半田バンプ6との接続を良好とするためのものである。被覆層3cの厚みが1μm未満では、半田バンプ6との接続を十分に良好とすることが困難となり、10μmを超えると、この被覆層3cを備えた半導体素子接続パッド3の高さが他の半導体素子接続パッド3の高さよりも高くなりすぎて半導体素子Sの電極Tを全ての半導体素子接続パッド3に半田バンプ6を介して良好に接続することが困難となる。したがって、被覆層3cの厚みは、1〜10μmの範囲が好ましい。被覆層3cを形成する低抵抗材料としては、例えば銅やニッケル、金、パラジウム、錫等が例示できるが、加工性や経済性等の観点から銅が好ましい。なお、被覆層3cを形成するには、被覆層3cが例えば銅から成る場合、周知のスパッタリング法により抵抗体層3bの上に厚みが0.05〜0.5μm程度の銅の薄膜を形成した後、その薄膜の上に電解銅めっき層を析出させる方法を採用することができる。

【0028】

このような構成により、本発明の配線基板10おいては、高速信号用の半導体素子接続パッド3は、絶縁層1bの側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層3aと接続面3dの側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層3bとが積層されて成り、抵抗体層3bが接続面3dと主導体層3aとの間に電気的に直列に接続されている状態となる。そして、主導体層3aと接続面3dとの間に電気的に直列に接続された抵抗体層3bによりダンピング抵抗が形成され、このダンピング抵抗により配線導体2の特性インピーダンスと半導体素子Sの特性インピーダンスの相違に起因して発生するノイズが減衰されて半導体素子Sを正常に作動させることが可能となる。そして本発明の配線基板10によれば、半導体素子Sを搭載する際の熱や半導体素子Sの作動時に発生する熱が繰り返し印加されても、その熱により発生する熱応力が抵抗体層3bに応力が集中して印加されることはなく、したがって抵抗体層3bが破断するようなこともない。その結果、搭載する半導体素子Sを常に正常に作動させることが可能な配線基板10を提供することができる。

【0029】

なお、本発明は上述の実施形態の一例に限定されるものではなく、本発明の要旨を逸脱しない範囲であれば種々の変更は可能であり、例えば上述した一例では、半導体素子Sの電極Tが接続される半導体素子接続パッド3にダンピング抵抗を設けた場合を示したが、外部の電気回路基板に接続される外部接続パッド4に上述の半導体素子接続パッド3と同様の層構成によるダンピング抵抗を設けてもよい。

【符号の説明】

【0030】

1b 絶縁層

3 接続パッド

3a 主導体層

3b 抵抗体層

3d 接続面

10 配線基板

【技術分野】

【0001】

本発明は、半導体集積回路素子等の半導体素子を搭載するために用いられる配線基板に関するものである。

【背景技術】

【0002】

半導体集積回路素子等の半導体素子を搭載するために用いられる配線基板には、ガラス基材および熱硬化性樹脂から成る絶縁板と銅箔等から成る配線導体とを交互に複数積層して成るプリント配線基板や、ガラス基材および熱硬化性樹脂から成る絶縁板上に熱硬化性樹脂およびフィラーから成る絶縁層と銅めっき層から成る配線導体とを複数積層して成るビルドアップ配線基板が用いられている。

【0003】

このような配線基板の上面には半導体素子の電極と接続するための半導体素子接続パッドが格子状の並びに配列されている。また、配線基板の下面には外部の電気回路基板に接続するための外部接続パッドが格子状の並びに配列されている。これらの半導体素子接続パッドと外部接続パッドとの間は、帯状やベタ状の配線導体を介して接続されている。なお帯状の配線導体は信号用に利用され、ベタ状の配線導体は接地用や電源用に用いられる。さらに半導体素子接続パッド上には半導体素子の電極と半導体素子接続パッドとを接合するための半田バンプが溶着されている。

【0004】

そして、このような配線基板においては、半導体素子をその各電極がそれぞれ対応する半田バンプに当接するようにして配線基板の上面に載置するとともに、これらを加熱して半田バンプを溶融させて半田バンプと半導体素子の電極とを接合させることによって、半導体素子が配線基板上に搭載される。

【0005】

ところで、このような配線基板においては、信号が伝播する信号用の配線導体の特性インピーダンスは、信号の減衰を極小とするためにシングルエンド信号では50Ω前後、ディファレンス信号では100Ω前後に設定されている。他方、半導体素子の入力インピーダンスは数百MΩ以上であり、出力インピーダンスは数Ω〜数十Ωであることから配線導体の特性インピーダンスとは大きく相違する。そのため信号用の配線導体を通して半導体素子に高速の信号の出し入れを行った場合、信号用の配線導体を伝わる信号に入出力端における反射波が重なりあうノイズが発生し、そのノイズにより半導体素子を正常に作動させることができない問題があった。

【0006】

そこで、上記問題を解消するために、図3に示すように、絶縁層21上の信号用の帯状の配線導体22を、薄膜抵抗体層22aとその上の主導体層22bとから形成し、主導体層22bの一部を除去することにより配線導体22に薄膜抵抗体層22aから成るダンピング抵抗を接続させることが提案されている。このように信号用の配線導体22に薄膜抵抗体層22aから成るダンピング抵抗を接続させることにより、配線導体22の特性インピーダンスと半導体素子の特性インピーダンスの相違に起因して発生するノイズをダンピング抵抗で減衰させ、それにより半導体素子を正常に作動させることが可能となる。

【0007】

しかしながら、信号用の帯状の配線導体を、薄膜抵抗体層とその上の主導体層とから形成し、主導体層の一部を除去することにより配線導体の一部に薄膜抵抗体層から成るダンピング抵抗を接続した場合、配線基板に半導体素子を搭載する際の熱や半導体素子の作動時に発生する熱が繰り返し印加されると、その熱により発生する熱応力が主導体層から露出する薄膜抵抗層の両端部に集中して作用し、それによりダンピング抵抗を破断させてしまうというという問題があった。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2005−5354号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明は、かかる従来の問題に鑑み案出されたものであり、その目的は、ダンピング抵抗に破断が発生することがなく、搭載する半導体素子を常に正常に作動させることが可能な配線基板を提供することにある。

【課題を解決するための手段】

【0010】

本発明の配線基板は、絶縁層の表面に、半導体素子の電極または電気回路基板が接続される接続面を有する複数の接続パッドを具備して成る配線基板であって、前記接続パッドの一部は、前記絶縁層の側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層と前記接続面の側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層とが積層されて成り、該抵抗体層が前記接続面と前記主導体層との間に電気的に直列に接続されていることを特徴とするものである。

【発明の効果】

【0011】

本発明の配線基板によれば、前記接続パッドは、前記絶縁層の側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層と前記接続面の側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層とが積層されて成り、該抵抗体層が前記接続面と前記主導体層との間に電気的に直列に接続されていることから、配線基板に半導体素子を搭載する際の熱や半導体素子の作動時に発生する熱が繰り返し印加されても、その熱により発生する熱応力が抵抗体層に集中して印加されることはなく、抵抗体層が破断するようなことがない。したがって、搭載する半導体素子を常に正常に作動させることが可能な配線基板を提供することができる。

【図面の簡単な説明】

【0012】

【図1】図1は、本発明の配線基板の実施形態の一例を示す概略断面図である。

【図2】図2は、図1に示す配線基板の要部拡大断面図である。

【図3】図3は、従来の配線基板を示す要部拡大断面図である。

【発明を実施するための形態】

【0013】

次に、本発明の配線基板の実施形態の一例を図1および図2を基にして詳細に説明する。図1は本発明の配線基板10の実施形態の一例を示す概略断面図であり、図2は図1に示す配線基板10の要部拡大断面図である。これらの図中、1は絶縁基板、2は配線導体、3は半導体素子接続パッド、4は外部接続パッド、5はソルダーレジスト層、6は半田バンプであり、主としてこれらにより本発明の配線基板10が構成される。

【0014】

なお、本例の配線基板10では、ガラス織物に熱硬化性樹脂を含浸させて成る絶縁板1aの上下面に熱硬化性樹脂から成る絶縁層1bを2層ずつ積層して絶縁基板1を形成しており、最表層の絶縁層1b上にソルダーレジスト層5が積層されている。また絶縁基板1の上面中央部には半導体素子Sが搭載される搭載部Aが形成されており、この搭載部Aにはそれぞれ半導体素子Sの電極Tが電気的に接続される半導体素子接続パッド3が形成されている。また、絶縁基板1の下面には外部電気回路基板に電気的に接続される外部接続パッド4が形成されており、絶縁基板1の上面から下面にかけてはそれぞれ対応する半導体素子パッド3と外部接続パッド4とを互いに電気的に接続する帯状やベタ状の配線導体2が配設されている。なお帯状の配線導体2は信号用に利用され、ベタ状の配線導体2は接地用や電源用に用いられる。さらに、半導体素子接続パッド3には半田バンプ6が溶着されている。

【0015】

そして、この配線基板10においては、半導体素子Sをその各電極Tがそれぞれ対応する半田バンプ6に当接するようにして配線基板10の上面に載置するとともに、これらを例えば電気炉等の加熱装置で約260℃程度に加熱して半田バンプ6を溶融させて半田バンプ6と半導体素子Sの電極Tとを接合させることによって、半導体素子Sが配線基板10上に搭載される。

【0016】

絶縁板1aは、本例の配線基板10におけるコア部材であり、例えばガラス繊維束を縦横に織り込んだガラス織物にエポキシ樹脂やビスマレイミドトリアジン樹脂等の熱硬化性樹脂を含浸させて成る。この絶縁板1aは、例えば厚みが0.3〜1.5mm程度であり、その上面から下面にかけて直径が0.1〜1mm程度の複数のスルーホール8を有している。そして、その上下面および各スルーホール8の内面には配線導体2の一部が被着されており、上下面の配線導体2がスルーホール8を介して電気的に接続されている。

【0017】

このような絶縁板1aは、ガラス織物に未硬化の熱硬化性樹脂を含浸させた絶縁シートを熱硬化させた後、これに上面から下面にかけてドリル加工を施すことにより製作される。なお、絶縁板1a上下面の配線導体2は、絶縁板1a用の絶縁シートの上下全面に厚みが3〜50μm程度の銅箔を貼着しておくとともにこの銅箔をシートの硬化後にエッチング加工することにより所定のパターンに形成される。また、スルーホール8内面の配線導体2は、絶縁板1aにスルーホール8を設けた後に、このスルーホール8内面に無電解めっき法および電解めっき法により厚みが3〜50μm程度の銅めっき膜を析出させることにより形成される。

【0018】

さらに、絶縁板1aは、そのスルーホール8の内部にエポキシ樹脂やビスマレイミドトリアジン樹脂等の熱硬化性樹脂から成る孔埋め樹脂9が充填されている。孔埋め樹脂9は、スルーホール8を塞ぐことによりスルーホール8の直上および直下に配線導体2および各絶縁層1bを形成可能とするためのものであり、未硬化のペースト状の熱硬化性樹脂をスルーホール8内にスクリーン印刷法により充填し、それを熱硬化させた後、その上下面を略平坦に研磨することにより形成される。そして、この孔埋め樹脂9を含む絶縁板1aの上下面に絶縁層1bがそれぞれ2層ずつ積層されている。

【0019】

絶縁板1aの上下面に積層された各絶縁層1bは、エポキシ樹脂やビスマレイミドトリアジン樹脂等の熱硬化性樹脂から成り、それぞれの厚みが10〜60μm程度であり、各層の上面から下面にかけて直径が20〜100μm程度の複数のビアホール11を有している。これらの各絶縁層1bは、配線導体2を高密度に配線するための絶縁間隔を提供するためのものである。そして、上層の配線導体2と下層の配線導体2とをビアホール11を介して電気的に接続することにより高密度配線が立体的に形成可能となっている。このような各絶縁層1bは、厚みが10〜60μm程度の未硬化の熱硬化性樹脂から成る絶縁フィルムを絶縁板1aの上下面に貼着し、これを熱硬化させるとともにレーザ加工によりビアホール11を穿孔し、さらにその上に同様にして次の絶縁層1bを順次積み重ねることによって形成される。なお、各絶縁層1bの表面およびビアホール11内に被着された配線導体2は、各絶縁層1bを形成する毎に各絶縁層1bの表面およびビアホール11内に5〜25μm程度の厚みの銅めっき膜を周知のセミアディティブ法等のパターン形成法により所定のパターンに被着させることによって形成される。

【0020】

絶縁基板1の上面の搭載部Aに形成された半導体素子接続パッド3は、ソルダーレジスト層5から露出する直径が50〜150μm程度の円形であり、搭載部A内の領域にピッチが100〜250μm程度の格子状の並びに多数配列形成されている。このような半導体素子接続パッド3は、半導体素子Sの電極Tを配線導体2に電気的に接続するための端子部として機能し、最上層の絶縁層1b上に形成された配線導体2の一部を、ソルダーレジスト層5に設けた直径が50〜150μm程度の円形の開口部5a内に露出させることにより形成されている。

【0021】

また、絶縁基板1の下面に形成された外部接続パッド4は、ソルダーレジスト層5から露出する直径が200〜700μm程度の円形であり、絶縁基板1下面の略全領域にピッチが500〜1000μm程度の格子状の並びに多数配列形成されている。外部接続パッド4は、配線導体2を外部電気回路基板に電気的に接続するための端子部として機能し、最下層の絶縁層1b上に形成された配線導体2の一部を、ソルダーレジスト層5に設けた直径が200〜700μmの円形の開口部5b内に露出させることにより形成されている。

【0022】

ソルダーレジスト層5は、アクリル変性エポキシ樹脂等の感光性を有する熱硬化性の樹脂から成り、その厚みが10〜30μm程度であり、上述したように半導体素子接続パッド3を露出させる開口部5aや外部接続パッド4を露出させる開口部5bを有している。それにより最表層における配線導体2を保護するとともに、開口部5aや5bを介して半導体素子接続パッド3や外部接続パッド4と半導体素子Sや外部電気回路基板との接続を可能としている。このようなソルダーレジスト層5は、感光性を有する樹脂ペーストまたは樹脂フィルムを最上層および最下層の絶縁層1bの表面に塗布または貼着するとともにフォトリソグラフィー技術を採用して開口部5aや5bを有するパターンに露光および現像した後、紫外線硬化および熱硬化させることにより形成される。

【0023】

半導体素子接続パッド3に溶着された半田バンプ6は、例えば錫−銀合金や錫−銀−銅合金等の鉛フリー半田から成り、半導体素子接続パッド3と半導体素子Sの電極Tとを電気的に接続するための接続部材として機能する。そして、半導体素子Sの電極Tを半田バンプ6に接触させた状態で半田バンプ6を加熱溶融させることにより半導体素子接続パッド3と半導体素子Sの電極Tとが半田バンプ6を介して電気的に接続されることとなる。このように半田バンプ6を半導体素子接続パッド3に予め溶着させておくことにより半導体素子接続パッド3への電極Tの接続の作業性が極めて良好なものとなる。なお、半導体素子Sの電極Tを半田バンプ6に接触させるのに先立って、半田バンプ6の上端部をプレスして平坦にしておくと、半導体素子Sの電極Tと半田バンプ6とを接触させることが容易かつ確実なものとなる。したがって、半導体素子Sの電極Tを半田バンプ6に接触させるのに先立って、半田バンプ6の上端部をプレスして平坦にしておくことが好ましい。

【0024】

さらに本発明においては、図2に示すように、半導体素子接続パッド3のうち、特に高速信号用の半導体素子接続パッド3は、主導体層3aと抵抗体層3bと被覆層3cとの積層体により形成されている。そして被覆層3cの表面が半導体素子Sの電極Tが半田バンプ6を介して接続される接続面3dを形成している。

【0025】

主導体層3aは、配線導体2と同じ材料であり、体積抵抗率が100μΩ・cm以下の低抵抗材料から成り、5〜25μm程度の厚みである。主導体層3aは、その体積抵抗率が100μΩ・cmを超えると、配線導体2の電気抵抗が高くなり、信号用の配線導体2においては信号の減衰が大きくなったり、接地や電源用の配線導体2においては、半導体素子Sに供給する電源電位の低下をもたらしたりする。したがって、主導体層3aの体積抵抗率は、100μΩ・cm以下であることが好ましい。このような低抵抗材料としては、例えば銅や銀、金、ニッケル、アルミニウム等が例示できるが、加工性や経済性等の観点から銅が好ましい。なお、主導体層3aを形成するには、主導体層3aが例えば銅から成る場合、配線導体2の形成と同じセミアディティブ法を採用することができる。

【0026】

抵抗体層3bは、体積抵抗率が10Ω・cm以上の高抵抗材料の薄膜から成り、100〜1000nm程度の厚みである。この抵抗体層3bは、ダンピング抵抗として機能するものであり、配線導体2の特性インピーダンスと半導体素子Sの特性インピーダンスの相違に起因して発生するノイズを減衰させ、それにより半導体素子Sを正常に作動させることを可能とするものである。抵抗体層3bの体積抵抗率が10Ω・cm未満であると、ダンピング抵抗としての抵抗値を抵抗体層3bにより付与することが困難となる。したがって、抵抗体層3bの体積抵抗率は10Ω・cm以上であることが好ましい。このような高抵抗材料としては、例えば、ゲルマニウムやフェライト等が例示できるが、加工性や透磁率の観点からゲルマニウムが好ましい。また、抵抗体層3bの厚みが100nm未満であるか1000nmを超えると、抵抗体層3bにダンピング抵抗として必要な抵抗値を付与することが困難となる。したがって、抵抗体層3bの厚みは、100〜1000nmの範囲が好ましい。なお、抵抗体層3bを形成するには、抵抗体層3bが例えばゲルマニウムから成る場合、周知のスパッタリング法により主導体層3aの表面にゲルマニウムの薄膜を100〜1000nm厚みに被着させる方法を採用することができる。

【0027】

被覆層3cは、半田との濡れ性に優れる低抵抗材料から成り、1〜10μm程度の厚みである。この被覆層3cは、半田バンプ6との接続を良好とするためのものである。被覆層3cの厚みが1μm未満では、半田バンプ6との接続を十分に良好とすることが困難となり、10μmを超えると、この被覆層3cを備えた半導体素子接続パッド3の高さが他の半導体素子接続パッド3の高さよりも高くなりすぎて半導体素子Sの電極Tを全ての半導体素子接続パッド3に半田バンプ6を介して良好に接続することが困難となる。したがって、被覆層3cの厚みは、1〜10μmの範囲が好ましい。被覆層3cを形成する低抵抗材料としては、例えば銅やニッケル、金、パラジウム、錫等が例示できるが、加工性や経済性等の観点から銅が好ましい。なお、被覆層3cを形成するには、被覆層3cが例えば銅から成る場合、周知のスパッタリング法により抵抗体層3bの上に厚みが0.05〜0.5μm程度の銅の薄膜を形成した後、その薄膜の上に電解銅めっき層を析出させる方法を採用することができる。

【0028】

このような構成により、本発明の配線基板10おいては、高速信号用の半導体素子接続パッド3は、絶縁層1bの側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層3aと接続面3dの側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層3bとが積層されて成り、抵抗体層3bが接続面3dと主導体層3aとの間に電気的に直列に接続されている状態となる。そして、主導体層3aと接続面3dとの間に電気的に直列に接続された抵抗体層3bによりダンピング抵抗が形成され、このダンピング抵抗により配線導体2の特性インピーダンスと半導体素子Sの特性インピーダンスの相違に起因して発生するノイズが減衰されて半導体素子Sを正常に作動させることが可能となる。そして本発明の配線基板10によれば、半導体素子Sを搭載する際の熱や半導体素子Sの作動時に発生する熱が繰り返し印加されても、その熱により発生する熱応力が抵抗体層3bに応力が集中して印加されることはなく、したがって抵抗体層3bが破断するようなこともない。その結果、搭載する半導体素子Sを常に正常に作動させることが可能な配線基板10を提供することができる。

【0029】

なお、本発明は上述の実施形態の一例に限定されるものではなく、本発明の要旨を逸脱しない範囲であれば種々の変更は可能であり、例えば上述した一例では、半導体素子Sの電極Tが接続される半導体素子接続パッド3にダンピング抵抗を設けた場合を示したが、外部の電気回路基板に接続される外部接続パッド4に上述の半導体素子接続パッド3と同様の層構成によるダンピング抵抗を設けてもよい。

【符号の説明】

【0030】

1b 絶縁層

3 接続パッド

3a 主導体層

3b 抵抗体層

3d 接続面

10 配線基板

【特許請求の範囲】

【請求項1】

絶縁層の表面に、半導体素子の電極または電気回路基板が接続される接続面を有する接続パッドを具備して成る配線基板であって、前記接続パッドは、前記絶縁層の側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層と前記接続面の側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層とが積層されて成り、該抵抗体層が前記接続面と前記主導体層との間に電気的に直列に接続されていることを特徴とする配線基板。

【請求項2】

前記主導体層が銅から成り、前記抵抗体層がゲルマニウムから成ることを特徴とする請求項1記載の配線基板。

【請求項1】

絶縁層の表面に、半導体素子の電極または電気回路基板が接続される接続面を有する接続パッドを具備して成る配線基板であって、前記接続パッドは、前記絶縁層の側に配置された体積抵抗率が100μΩ・cm以下の低抵抗材料から成る主導体層と前記接続面の側に配置された体積抵抗率が10Ω・cm以上の高抵抗材料から成る抵抗体層とが積層されて成り、該抵抗体層が前記接続面と前記主導体層との間に電気的に直列に接続されていることを特徴とする配線基板。

【請求項2】

前記主導体層が銅から成り、前記抵抗体層がゲルマニウムから成ることを特徴とする請求項1記載の配線基板。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−45938(P2013−45938A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2011−183560(P2011−183560)

【出願日】平成23年8月25日(2011.8.25)

【出願人】(304024898)京セラSLCテクノロジー株式会社 (213)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成23年8月25日(2011.8.25)

【出願人】(304024898)京セラSLCテクノロジー株式会社 (213)

【Fターム(参考)】

[ Back to top ]