配線構造及びそのバイヤホール形成方法

【目的】 FET の配設密度を高める。

【構成】 GaAs基板10の基板面10a 上に順次に、n+-AlGaAs 導電層121 及びアンドープGaAs絶縁層122 設け、絶縁層122 上に複数のGaAsFET14 を設ける。各FET14を酸素イオン注入領域20により、電気的に絶縁分離する。そしてイオン注入領域20にFET14 のソース電極28の配設面から導電層121 に至る深さのバイヤホール32を設け、このバイヤホール32に設けた配線電極32を介して、ソース電極28と導電層121 とを接続する。また他方の基板面10b から導電層121 に至る深さのバイヤホール16を、基板10に設け、この基板面10b 全面にわたって設けた裏面電極36をバイヤホール16を介し導電層121 と接続する。バイヤホール32の深さを浅くできるのでバイヤホール径を小さくでき、従って絶縁層122 上に設けた複数のFET14 の集積密度を高めることができる。

【構成】 GaAs基板10の基板面10a 上に順次に、n+-AlGaAs 導電層121 及びアンドープGaAs絶縁層122 設け、絶縁層122 上に複数のGaAsFET14 を設ける。各FET14を酸素イオン注入領域20により、電気的に絶縁分離する。そしてイオン注入領域20にFET14 のソース電極28の配設面から導電層121 に至る深さのバイヤホール32を設け、このバイヤホール32に設けた配線電極32を介して、ソース電極28と導電層121 とを接続する。また他方の基板面10b から導電層121 に至る深さのバイヤホール16を、基板10に設け、この基板面10b 全面にわたって設けた裏面電極36をバイヤホール16を介し導電層121 と接続する。バイヤホール32の深さを浅くできるのでバイヤホール径を小さくでき、従って絶縁層122 上に設けた複数のFET14 の集積密度を高めることができる。

【発明の詳細な説明】

【0001】

【産業上の利用分野】この発明は配線構造特に半導体装置の配線に適した配線構造と、この配線構造にバイヤホールを形成するためのバイヤホール形成方法とに関する。

【0002】

【従来の技術】従来より、GaAsICにおいてFETのソース接地を行なう場合にあっては、FETを表側の基板面上に設け、FETのソース電極直下に、基板を貫通するバイヤホールを形成する。そして裏側の基板面にアース電極を設け、バイヤホールを介しFETのソース電極とアース電極とを電気接続する。

【0003】

【発明が解決しようとする課題】しかしながら上述した従来の配線構造では、裏側の基板面からソース電極に至る深さのバイヤホールを、FETの活性層と並列させてソース電極直下に設けないと、ソース電極とアース電極とを電気接続することができない。このように深さの深いバイヤホールを、活性層と並列させて設けなければならないので、集積密度を上げることが難しい。通常、ウエットエッチングによりバイヤホールを形成するので、バイヤホールの深さが深くなる分だけ、バイヤホール径は広くなるからである。

【0004】また基板をICチップ毎に分割する際にICチップが損傷しないように分割を行なうためには、基板厚さを厚くすることが望まれる。しかし基板を厚くする分だけバイヤホールの深さが深くなり、従ってバイヤホール径が広くなるので集積密度が上がらなくなる。

【0005】さらにFETの放熱効率を高めるためには、バイヤホールを活性層直下に設けるのが好ましいが、従来の配線構造では、バイヤホールを活性層直下に設けると、アース電極を活性層と電気接続することとなるので、FETを正常動作させることができなくなる。

【0006】またFETにおいては、サイドゲート効果或はバックゲート効果により活性層の電位が変動し、その結果、FETの電気的特性が変動するという問題があった。これと類似した問題は、FET以外の電気回路素子例えばバイポーラトランジスタ、ダイオード、インダクタ、キャパシタ或は抵抗においても生じる。このような電気的特性の変動を防止するためには、電気回路素子の周辺電位を安定化することが有効である。

【0007】この発明は、上述した従来の問題点を解決するため、より集積密度を高めることのできる配線構造を提供することを第一の目的とし、さらにこの配線構造にバイヤホールを形成するのに適したバイヤホール形成方法を提供することを第二の目的とする。

【0008】またこの発明は、集積密度を高めることができ、しかも電気回路素子の周辺電位を安定化することもできる配線構造を提供することを第三の目的とする。

【0009】

【課題を解決するための手段及び作用】第一の目的を達成するため、請求項1記載の配線構造は、半導体基板と基板面上に積み重ねて設けられたn個(nは自然数)の配線ユニット層とにより配線のための積層体を構成し、配線ユニット層を、基板面側から順次に設けられた導電層及び絶縁層により構成し、この配線ユニット層を、基板面に沿う方向に平面状に延在させて成ることを特徴とする。

【0010】このような配線構造によれば、配線のための積層体の任意好適箇所に電気回路素子及びバイヤホールを設け、所望の電気回路素子と当該素子に対応する配線ユニット層の導電層とを、これら素子及び導電層の間に設けたバイヤホールを介し電気接続することができる。例えば、基板面側から数えて第n個目の配線ユニット層上に電気回路素子を設けることができる。或は、基板面又はその表層に電気回路素子を設け、この電気回路素子上に絶縁層を介し配線ユニット層を設けることができる。或は、配線ユニット層を設けた基板面とは反対側の基板面或はその表層に電気回路素子を設けることができる。或は、複数個の配線ユニット層を設けた場合には、配線ユニット層の絶縁層上に電気回路素子を設け、この電気回路素子上に絶縁層を介し他の配線ユニット層を設けることができる。

【0011】しかも配線ユニット層を、基板面に沿って平面状に延在させているので、平面的に見て、バイヤホールと配線ユニット層の導電層とが重なり合う範囲内であれば、バイヤホールの配設位置を自由に変更しても、相対応する電気回路素子と配線ユニット層の導電層とを互いに電気接続できる。従って配線の自由度が増す。また配線ユニット層の導電層を介し各電気回路素子相互の電気接続を行なうことにより、配線密度を低減することもできる。

【0012】また第三の目的を達成するため、請求項4記載の配線構造は、請求項1記載の配線構造において、基板面側から数えて第n個目の配線ユニット層上に設けられた電気回路素子を備え、第n個目の配線ユニット層の導電層を、電気回路素子の周辺電位を安定化し或は制御するための電極とすることを特徴とする。

【0013】このような配線構造によれば、配線ユニット層を、基板面に沿って平面状に延在させているので、第n個目の配線ユニット層の導電層を一定電位に保つことにより、この第n個目の配線ユニット層上に設けた電気回路素子の周辺電位を安定化することができる。また第n個目の配線ユニット層の導電層の電位を任意好適に変更することにより電気回路素子の周辺電位を可変制御することもできる。

【0014】また第二の目的を達成するため、請求項5記載のバイヤホール形成方法は、請求項1記載の配線構造の配線ユニット層にバイヤホールを形成するに当り、バイヤホールの最終到達深さに位置する配線ユニット層の絶縁層をエッチングする時は、当該配線ユニット層の導電層をエッチングせずに当該配線ユニット層の絶縁層を選択的にエッチングするエッチャント又はエッチングガスを用いることを特徴とする。

【0015】このようなバイヤホール形成方法によれば、配線ユニット層の導電層でエッチングを確実にストップさせることができるので、バイヤホールの深さを精度良く制御できる。

【0016】また第二の目的を達成するため、請求項6記載のバイヤホール形成方法は、請求項1記載の配線構造の半導体基板にバイヤホールを形成するに当り、バイヤホール形成のため半導体基板をエッチングする時は、配線ユニット層の導電層をエッチングせずに半導体基板を選択的にエッチングするエッチャント又はエッチングガスを用いることを特徴とする。

【0017】このようなバイヤホール形成方法によれば、配線ユニット層の導電層でエッチングを確実にストップさせることができるので、バイヤホールの深さを精度良く制御できる。

【0018】

【実施例】以下、図面を参照し、発明の実施例につき説明する。尚、図面は発明が理解できる程度に概略的に示してあるにすぎず、従って発明を図示例に限定するものではない。

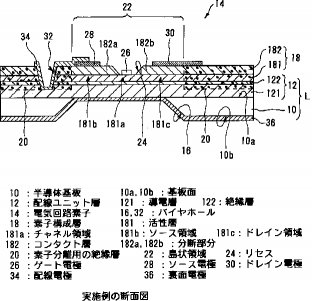

【0019】図1及び図2は請求項1の発明の実施例の構成を概略的に示す断面図及び平面図である。図1にあっては、図2のI−I線に沿って取った断面に対応する断面を示す。また図2にあっては、図面の理解を助けるため、ソース電極、ドレイン電極、ゲート電極及び配線電極を省略して示してある。

【0020】これら図にも示すように、この実施例の配線構造は、半導体基板10と基板面10a上に積み重ねて設けられたn個(nは自然数)の配線ユニット層12とにより配線のための積層体Lを構成し、配線ユニット層12を、基板面10a側から順次に設けられた導電層121及び絶縁層122により構成し、そして配線ユニット層12を基板面10aに沿う方向に平面状に延在させて成る。

【0021】この実施例では、n=1とするものであって、GaAs半導体基板10の表側の基板面10a上に、n(n=1)個の配線ユニット層12を積み重ねる。配線ユニット層12は、基板面10a側から順次に設けられたn+ −AlGaAs導電層121及びアンドープGaAs絶縁層122から成る。この配線ユニット層12の導電層121及び絶縁層122を、基板面10a全面にわたる領域に延在させる。

【0022】さらにこの実施例の配線構造は、基板面10a側から数えて第n(n=1)個目の配線ユニット層12上に設けられた電気回路素子14と、半導体基板10に設けられたバイヤホール16とを備え、このバイヤホール16を電気回路素子14直下に配置する。

【0023】ここでは、第n(n=1)個目の配線ユニット層12上に設けられた素子構成層18を用いて、電気回路素子14としてFET(Field Effect Transistor )例えばリセス構造のGaAsFETを構成する。このため、素子構成層18は、配線ユニット層12の絶縁層122上に順次に設けられたn−GaAs活性層181及びn+ −GaAsコンタクト層182から成る。そしてこの素子構成層18に、素子分離用の絶縁層20例えば不純物イオン注入領域を設ける。図にあっては、絶縁層20の形成のための不純物イオンが注入された領域を点を付して示すと共に、絶縁層20の形成のための不純物イオンが注入された領域及び注入されていない領域の境界を点線で示す。

【0024】絶縁層20は、素子構成層18の上面から第n(n=1)個目の配線ユニット層12の導電層121に至る深さを有し、この絶縁層20により、電気回路素子14が配設される島状領域22の周囲を、閉ループ状に取り囲む。この絶縁層20を、図2において、斜めのハッチングを付して示す。

【0025】この結果、島状領域22の素子構成層18と島状領域22以外の領域の素子構成層18とは、第n(n=1)個目の配線ユニット層12の絶縁層122及び素子分離用の絶縁層20により、電気的に絶縁分離される。

【0026】さらに島状領域22の素子構成層18に、コンタクト層182上面から活性層181に至る深さのリセス24を設ける。リセス24を介し、活性層181のチャネル領域181aを露出させ、このチャネル領域181a上にゲート電極26を設ける。またリセス24により、島状領域22のコンタクト層182を、活性層181の第一主電極領域ここではソース領域181bに対応する部分182aと第二主電極領域ここではドレイン領域181cに対応する部分182bとに分断し、一方の分断部分182a上に第一主電極ここではソース電極28及び他方の分断部分182b上に第二主電極ここではドレイン電極30を設ける。

【0027】従って電気回路素子14は、活性層181のチャネル領域181a、ソース領域181b及びドレイン領域181cと、チャネル領域181a上に設けられたゲート電極26と、ソース領域181b上にコンタクト層分断部分182aを介して設けられたソース電極28と、ドレイン領域181c上にコンタクト層分断部分182bを介して設けられたドレイン電極30とから成る。

【0028】またソース電極28に隣接する領域の絶縁層20をバイヤホール形成用の絶縁層として利用し、この領域の絶縁層20にバイヤホール32を設ける。バイヤホール32を、ソース電極28の配設面から最下層の配線ユニット層12の導電層121に至る深さまで形成し、バイヤホール32を介し最下層の導電層121を露出させる。そしてこの露出させた導電層121からソース電極28まで配線電極34を設け、これら導電層121及びソース電極28を、バイヤホール32を介し配線電極34により接続する。

【0029】また電気回路素子14直下の基板10に、バイヤホール16を設ける。バイヤホール16を裏側の基板面10bから最下層の配線ユニット層12の導電層121に至る深さまで形成し、バイヤホール16を介し最下層の導電層121を露出させる。そして裏面電極36を裏側の基板面10b全面にわたる領域に設け、バイヤホール16を介して最下層の導電層121と裏面電極36とを接続する。

【0030】図にあっては、1個の電気回路素子14を図示するのみであるが、配線ユニット層12上には複数の電気回路素子14を設け、各電気回路素子14毎にそれぞれ絶縁層20、バイヤホール32、配線電極34、バイヤホール16を設け、各電気回路素子14のソース電極28をそれぞれ、バイヤホール32、16を介して裏面電極36と接続している。

【0031】この実施例によれば、ソース電極28は、配線電極34と電気的に接続し、さらに配線電極34はバイヤホール32を介して高濃度不純物添加層であるn+ −AlGaAs導電層121と電気的に接続している。n+ −AlGaAs導電層121は高濃度に不純物が添加されているため金属層と同程度に抵抗値が小さい。そしてn+ −AlGaAs導電層121はバイヤホール16を介して裏面電極36と電気的に接続しているので、ソース電極28を裏面電極36と同電位とすることができる。

【0032】配線ユニット層12は平面状に延在しているので、基板裏側のバイヤホール16を、平面的に見て、配線ユニット層12と重なり合う領域に設けてあれば、裏面電極36を配線ユニット層12の導電層121と接続できる。従って基板裏側のバイヤホール16の配設位置(或は形成位置)が、バイヤホール形成のためのフォトリソ及びエッチング工程におけるマスクずれ等により、設計位置からずれたとしても、裏面電極36と配線ユニット層12の導電層121との接続不良が発生するおそれは非常に少ない。接続不良の発生を防止するためには、配線ユニット層12を基板面全面にわたって平面状に延在させるのが、効果的である。

【0033】また従来にあってはソース電極28から裏側の基板面10bに至る深さのバイヤホールを形成し、このバイヤホールを介しソース電極28と裏面電極36とを接続していた。これに対しこの実施例では、バイヤホール32の深さはソース電極28の配設面から配線ユニット層12の導電層121に至る深さであり、バイヤホール16の深さは裏側の基板面10bから配線ユニット層12の導電層121に至る深さであるので、従来形成していたバイヤホールに比べ深さの浅いバイヤホール32、16を用いてソース電極28と裏面電極36とを接続することができる。深さを浅くできる分だけ、バイヤホール径を小さくできる。特に配線ユニット層12上に複数の電気回路素子14を設ける場合には、基板表側のバイヤホール32の径を小さくすることにより、基板表側の電気回路素子14の集積密度を高めることができるという利点がある。

【0034】また基板裏側のバイヤホール16を電気回路素子14直下に設けるので、このバイヤホール16により電気回路素子14の放熱効率を高めることができる。しかも裏側の基板面10b全面にわたって裏面電極36を設けるようにした場合には、裏側の基板面10b上に設ける電気回路素子は裏面電極36のみであるので、基板裏側の電気回路素子の集積密度を高めるという配慮は不要であり、基板裏側のバイヤホール16の径を大きくできる。径の大きなバイヤホール16を設けることにより、一層、電気回路素子14の放熱効率を高めることができる。基板表側に複数の電気回路素子14を設ける場合には、各電気回路素子14の直下にそれぞれバイヤホール16を設け、個々の電気回路素子14の放熱効率を高めるようにするのが好ましい。

【0035】また配線ユニット層12上に電気回路素子14を設けているので、電気回路素子14直下に基板裏側のバイヤホール16を設けても、電気回路素子14はバイヤホール16を介し露出されることはない。従ってバイヤホール16を電気回路素子14直下に設けても、裏面電極36と電気回路素子14とが直接に接触することはないので、電気回路素子14の動作が損なわれることはない。

【0036】次に図3〜図6は図1に示す配線構造の主要な製造工程を段階的に示す断面図である。

【0037】以下、図3〜図6を参照し、図1に示す配線構造の製造方法の一例を説明すると共に、請求項5記載の発明の実施例及び請求項6記載の発明の実施例につき説明する。請求項5記載の発明の実施例は、図1の配線構造において、配線ユニット層12にバイヤホール32を形成するに当り、バイヤホール32の最終到達深さすなわち設計深さに位置する配線ユニット層12の絶縁層122をエッチングする時は、当該配線ユニット層12の導電層121をエッチングせずに当該配線ユニット層12の絶縁層122を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。また請求項6記載の発明の実施例は、図1の配線構造において、半導体基板10にバイヤホール16を形成するに当り、バイヤホール16形成のため半導体基板10をエッチングする時は、配線ユニット層12の導電層121をエッチングせずに半導体基板10を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0038】まず、MBE法等により、GaAs基板10の基板面10a上に順次に、n+−AlGaAs導電層121、アンドープGaAs絶縁層122、n−GaAs活性層181及びn+ −GaAsコンタクト層182を形成する(図3(A))。

【0039】次に、イオン注入法により、不純物イオンここでは酸素イオンを、コンタクト層182から導電層121に至る深さまで注入し、不活性領域である絶縁層20を形成し、電気回路素子14の形成領域となる島状領域22の周囲を絶縁層20で囲む(図3(B))。

【0040】次にリフトオフ法により、ソース電極28及びドレイン電極30を、島状領域22のコンタクト層182上であって活性層18のソース領域181b及びドレイン領域181cに対応する位置に形成する(図3(C))。

【0041】次にソース電極28及びドレイン電極30の間のコンタクト層182に、リセス24を形成し、リセス24を介し活性層181のチャネル領域181aを露出させる。然る後、露出させたチャネル領域181a上にゲート電極26を形成する(図4(A))。

【0042】次にバイヤホール形成用のレジストマスク38を、ゲート電極26上に形成する(図4(B))。レジストマスク38は、基板表側バイヤホール32の形成領域を露出する開口部38aを有する。

【0043】次にレジストマスク38を介し絶縁層20をエッチングして、絶縁層20にバイヤホール32を形成し、このバイヤホール32を介し導電層121を露出させる(図4(C))。この際、絶縁層20はエッチングするが導電層121はエッチングしないエッチャント例えばクエン酸溶液を用いる。クエン酸溶液は、絶縁層20すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122及び導電層121はエッチングするが、酸素イオンの注入されていない導電層121はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0044】エッチングが停止したらレジストマスク38を除去し、然る後、配線電極形成用のレジストマスク40をゲート電極26上に形成する(図5(A))。レジストマスク40は配線電極34の形成領域を露出する開口部40aを有する。

【0045】次に、真空蒸着法によりレジストマスク40を介し配線電極材料42を堆積させる(図5(B))。然る後、レジストマスク40を除去し、配線電極34の形成領域に残存する配線電極材料42から成る配線電極34を得る。

【0046】次に、バイヤホール形成用のレジストマスク44を、裏側の基板面10b上に形成する(図5(C))。レジストマスク44は基板裏側バイヤホール16の形成領域を露出する開口部44aを有する。従来と比較して、レジストマスク44の開口部44aの幅を10倍以上とし、またレジストマスク44形成のために用いる露光マスクの位置合わせ精度を±5μm程度にまで緩やかにすることができる。

【0047】次にレジストマスク44を介し基板10をエッチングして、基板裏側のバイヤホール16を形成する(図6(A))。このエッチングの際、基板10はエッチングするが酸素イオンが注入されていない導電層121はエッチングしないエッチャント例えばクエン酸溶液を用いる。クエン酸溶液を用いることにより、エッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0048】エッチングが停止した後エッチングマスク44を除去する。然る後、真空蒸着法により、裏側の基板面10b全面にわたって裏面電極36を形成し(図6(B))、図1の配線構造を完成する。

【0049】このようにバイヤホール32、16を形成するためのエッチングにおいて、酸素イオンが注入されていない導電層121で自動的にエッチングが停止するので、オーバーエッチングが生じず、従って配線不良の発生や電気回路素子14の損傷の発生を防止できる。

【0050】図7及び図8は請求項1の発明の他の実施例の構成を概略的に示す断面図及び平面図である。図7にあっては、図8のVII−VII線に沿って取った断面に対応する断面を示す。また図8にあっては、図面の理解を助けるため、ソース電極、ドレイン電極、ゲート電極及び配線電極を省略して示してある。

【0051】以下、図1の実施例と相違する点につき説明し、図1の実施例と同様の点についてはその詳細な説明を省略する。

【0052】この実施例では、n=2としn(=2)個の配線ユニット層46、12を、表側の基板面10a上に、積み重ねて設け、これら配線ユニット層46、12及び基板10により配線のための積層体Lを構成する。

【0053】基板面10a上に順次に、基板面10a全面にわたって平面状に延在させて、配線ユニット層46及び12を設け、配線ユニット層46を、基板面10a側から順次に設けられたn+ −AlGaAs導電層461及びアンドープGaAs絶縁層462により構成する。そして第n(n=2)個目の配線ユニット層12上に電気回路素子14を設ける。

【0054】またソース電極28に隣接する領域に、バイヤホール形成用の絶縁層48例えばイオン注入領域を設ける。絶縁層48を例えば酸素イオンの注入領域とする。平面的に見て、絶縁層48の一部又は全部を絶縁層20と重ね合わせるように設け、絶縁層48を、ソース電極28の配設面から最下層の配線ユニット層46の導電層461に至る深さに形成する。図にあっては、絶縁層20、48の形成のための不純物イオンが注入された領域を点を付して示すと共に、絶縁層20、48の形成のための不純物イオンが注入された領域及び注入されていない領域の境界を点線で示す。

【0055】そして絶縁層48に、バイヤホール32を設ける。バイヤホール32をソース電極28の配設面から最下層の配線ユニット層46の導電層461に至る深さに形成し、バイヤホール32を介し、最下層の導電層461を露出させる。そして露出させた最下層の導電層461からソース電極28まで配線電極34を設け、これら導電層461及びソース電極28を、バイヤホール32を介して配線電極34により接続する。

【0056】またバイヤホール16を、裏側の基板面10bから最下層の導電層461に至る深さに形成し、このバイヤホール16を介し裏面電極36と最下層の導電層461とを接続する。

【0057】さらにドレイン電極30に隣接する領域の絶縁層20をバイヤホール形成用の絶縁層に利用し、この領域の絶縁層20にバイヤホール50を設ける。バイヤホール50を、ドレイン電極20の配設面から残りの配線ユニット層12の導電層121に至る深さに形成し、バイヤホール50を介し残りの導電層121を露出させる。そして露出させた導電層121からドレイン電極30まで配線電極52を設け、これら導電層121及びドレイン電極30を、バイヤホール50を介して配線電極52により接続する。

【0058】図にあっては、1個の電気回路素子14を図示するのみであるが、配線ユニット層12上には複数の電気回路素子14を設け、各電気回路素子14毎にそれぞれ絶縁層20、バイヤホール32、配線電極34、バイヤホール16、バイヤホール50及び配線電極52を設け、各電気回路素子14のソース電極28をそれぞれ、バイヤホール32、16を介して裏面電極36と接続すると共に、各電気回路素子14のドレイン電極30をそれぞれ、これらに共通の導電層121とバイヤホール50を介して接続している。

【0059】この実施例によれば、ソース電極28は、配線電極34と電気的に接続し、さらに配線電極34はバイヤホール32を介して高濃度不純物添加層であるn+ −AlGaAs導電層461と電気的に接続している。n+ −AlGaAs導電層461は高濃度に不純物が添加されているため金属層と同程度に抵抗値が小さい。そしてn+ −AlGaAs導電層461はバイヤホール16を介して裏面電極36と電気的に接続しているので、ソース電極28と裏面電極36とは同電位となることができる。

【0060】またドレイン電極30は配線電極52と接続し、さらに配線電極52はバイヤホール50を介してn+ −AlGaAs導電層121と接続しているので、ドレイン電極30をn+ −AlGaAs層121と同電位とすることができる。

【0061】この実施例においても、図1の実施例と同様に、基板裏側のバイヤホール16の配設位置(或は形成位置)が設計位置からずれたとしても、裏面電極36と最下層の導電層461との接続不良が発生するおそれは非常に少ない。接続不良の発生を防止するためには、最下層の配線ユニット層46を基板面全面にわたって延在させるのが、効果的である。

【0062】またバイヤホール32の深さはソース電極28の配設面から最下層の導電層461に至る深さであり、バイヤホール16の深さは裏側の基板面10bから最下層の導電層461に至る深さであるので、従来形成していたバイヤホールに比べ深さの浅いバイヤホール32、16を用いてソース電極28と裏面電極36とを接続することができる。深さを浅くできる分だけ、バイヤホール径を小さくできる。特に最上層の配線ユニット層12上に複数の電気回路素子14を設ける場合には、基板表側のバイヤホール32の径を小さくすることにより、基板表側の電気回路素子14の集積密度を高めることができるという利点がある。

【0063】また基板裏側のバイヤホール16を電気回路素子14直下に設けるので、このバイヤホール16により電気回路素子14の放熱効率を高めることができる。しかも裏側の基板面10b全面にわたって裏面電極36を設けるようにした場合には、裏側の基板面10b上に設ける電気回路素子は裏面電極36のみであるので、基板裏側の電気回路素子の集積密度を高めるという配慮は不要であり、基板裏側のバイヤホール16の径を大きくできる。径の大きなバイヤホール16を設けることにより、一層、電気回路素子14の放熱効率を高めることができる。基板表側に複数の電気回路素子14を設ける場合には、各電気回路素子14の直下にそれぞれバイヤホール16を設け、個々の電気回路素子14の放熱効率を高めるようにするのが好ましい。

【0064】また配線ユニット層12上に電気回路素子14を設けているので、電気回路素子14直下に基板裏側のバイヤホール16を設けても、電気回路素子14はバイヤホール16を介し露出されることはない。従ってバイヤホール16を電気回路素子14直下に設けても、裏面電極36と電気回路素子14とが直接に接触することはないので、電気回路素子14の動作が損なわれることはない。

【0065】さらにこの実施例では、次のような効果も望める。すなわち、配線ユニット層12の導電層121により複数の電気回路素子14のドレイン電極30を共通接続することができるので、配線密度特にドレイン電極30の配設面上における配線密度を低減できる。従って配線取り回し特にドレイン電極30の配線面上における配線取り回しの自由度を増すことができると共に、電気回路素子14の集積密度を高めることが可能となる。配線取り回しの自由度を増し或は電気回路素子14の集積密度を高めるためには、配線ユニット層12の導電層121を、基板面10a全面にわたって平面状に延在させるのが効果的である。

【0066】次に請求項5記載の発明の他の2つの実施例について説明する。そのひとつの実施例は、図7の配線構造において、配線ユニット層12、46にバイヤホール32を形成するに当り、バイヤホール32の最終到達深さすなわち設計深さに位置する配線ユニット層46の絶縁層461をエッチングする時は、当該配線ユニット層46の導電層461をエッチングせずに当該配線ユニット層46の絶縁層462を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0067】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層48すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122、導電層121、絶縁層461及び導電層462はエッチングするが、酸素イオンの注入されていない導電層461はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層461に達した所で停止する。

【0068】他のひとつの実施例は、図7の配線構造において、配線ユニット層12にバイヤホール50を形成するに当り、バイヤホール50の最終到達深さすなわち設計深さに位置する配線ユニット層12の絶縁層121をエッチングする時は、当該配線ユニット層12の導電層121をエッチングせずに当該配線ユニット層12の絶縁層122を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0069】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層20すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122及び導電層121はエッチングするが、酸素イオンの注入されていない導電層121はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0070】また請求項6記載の発明の他の実施例について説明する。この実施例は、図7の配線構造において、半導体基板10にバイヤホール16を形成するに当り、バイヤホール16形成のため半導体基板10をエッチングする時は、配線ユニット層46の導電層461をエッチングせずに半導体基板10を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0071】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、基板10はエッチングするが、酸素イオンの注入されていない導電層121はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0072】図9及び図10は請求項4の発明の実施例の構成を概略的に示す断面図及び平面図である。図9にあっては、図10のIX−IX線に沿って取った断面に対応する断面を示す。また図10にあっては、図面の理解を助けるため、ソース電極、ドレイン電極、ゲート電極及び配線電極を省略して示してある。

【0073】この実施例は請求項1の発明の実施例でもあり、以下、図1の実施例と相違する点につき説明し、図1の実施例と同様の点についてはその詳細な説明を省略する。

【0074】この実施例では、n=3としn(=3)個の配線ユニット層54、46、12を、表側の基板面10a上に、積み重ねて設け、これら配線ユニット層54、46、12及び基板10により配線のための積層体Lを構成する。

【0075】基板面10a上に順次に、基板面10a全面にわたって平面状に延在させて、配線ユニット層54、46及び12を設け、配線ユニット層54を、基板面10a側から順次に設けられたn+ −AlGaAs導電層541及びアンドープGaAs絶縁層542により構成する。そして第n(n=3)個目の配線ユニット層12上に電気回路素子14を設ける。

【0076】またソース電極28に隣接する領域に、バイヤホール形成用の絶縁層48例えばイオン注入領域を設ける。絶縁層48を例えば酸素イオンの注入領域とする。平面的に見て、絶縁層48の一部又は全部を絶縁層20と重ね合わせるように設け、絶縁層48を、ソース電極28の配設面から最下層の配線ユニット層54の導電層541に至る深さに形成する。

【0077】そして絶縁層48に、バイヤホール32を設ける。バイヤホール32をソース電極28の配設面から最下層の配線ユニット層54の導電層541に至る深さに形成し、バイヤホール32を介し、最下層の導電層541を露出させる。そして露出させた最下層の導電層541からソース電極28まで配線電極34を設け、これら導電層541及びソース電極28を、バイヤホール32を介して配線電極34により接続する。

【0078】またバイヤホール16を、裏側の基板面10bから最下層の導電層541に至る深さに形成し、このバイヤホール16を介し裏面電極36と最下層の導電層541とを接続する。

【0079】さらに第n(n=3)個目の配線ユニット層12の導電層121を、電気回路素子14の周辺電位を安定化し或は制御するための電極とする。

【0080】ここでは、絶縁層20をバイヤホール形成用の絶縁層に利用する。絶縁層20は、ソース電極28或はドレイン電極30の配設面から第n(n=3)個目すなわち最上層の配線ユニット層12の導電層121に至る深さを有する。そしてこの絶縁層20の任意好適箇所にバイヤホール58を設ける。バイヤホール58を、ソース電極28或はドレイン電極30の配設面から最上層の導電層121に至る深さに形成し、このバイヤホール58を介し最上層の導電層121を露出させる。そして最上層の導電層121から、ソース電極28或はドレイン電極30の配線面まで電極端子60を設ける。

【0081】さらにドレイン電極30に隣接する領域に、バイヤホール形成用の絶縁層62例えばイオン注入領域を設ける。絶縁層62を例えば酸素イオンの注入領域とする。平面的に見て、絶縁層62の一部又は全部を絶縁層20と重ね合わせるように設け、絶縁層62を、ドレイン電極30の配設面から、残りの配線ユニット層46(中間の配線ユニット層46)の導電層461に至る深さに形成する。

【0082】そして絶縁層62に、バイヤホール50を設ける。バイヤホール50をドレイン電極30の配設面から中間の配線ユニット層46の導電層461に至る深さに形成し、バイヤホール50を介し、中間の導電層461を露出させる。そして露出させた中間の導電層461からドレイン電極30まで配線電極52を設け、これら導電層461及びドレイン電極30を、バイヤホール62を介して配線電極52により接続する。

【0083】図にあっては、絶縁層48、20、62の形成のための不純物イオンが注入された領域を点を付して示すと共に、絶縁層48、20、62の形成のための不純物イオンが注入された領域及び注入されていない領域の境界を点線で示す。また図にあっては、1個の電気回路素子14を図示するのみであるが、配線ユニット層12上には複数の電気回路素子14を設け、各電気回路素子14毎にそれぞれ絶縁層20、バイヤホール32、配線電極34、バイヤホール16、バイヤホール50及び配線電極52を設け、各電気回路素子14のソース電極28をそれぞれ、バイヤホール32、16を介して裏面電極36と接続すると共に、各電気回路素子14のドレイン電極30をそれぞれ、これらに共通の導電層461とバイヤホール50を介して接続している。また電気回路素子14の周辺電位を安定化するための導電層121及びその電極端子60は、これら各電気回路素子14に共通の導電層及び電極端子である。

【0084】この実施例によれば、ソース電極28は、配線電極34と電気的に接続し、さらに配線電極34はバイヤホール32を介して高濃度不純物添加層であるn+ −AlGaAs導電層541と電気的に接続している。n+ −AlGaAs導電層541は高濃度に不純物が添加されているため金属層と同程度に抵抗値が小さい。そしてn+ −AlGaAs導電層541はバイヤホール16を介して裏面電極36と電気的に接続しているので、ソース電極28を裏面電極36と同電位とすることができる。

【0085】またドレイン電極30は配線電極52と接続し、さらに配線電極52はバイヤホール50を介してn+ −AlGaAs導電層461と接続しているので、ドレイン電極30をn+ −AlGaAs層461と同電位とすることができる。

【0086】また電極端子60はバイヤホール58を介しn+ −AlGaAs導電層121と接続しているので、電極端子60を介し導電層121に一定電位を供給することにより、導電層121の電位を安定化することができる。

【0087】この実施例においても、図1の実施例と同様に、基板裏側のバイヤホール16の配設位置(或は形成位置)が設計位置からずれたとしても、裏面電極36と最下層の導電層541との接続不良が発生するおそれは非常に少ない。接続不良の発生を防止するためには、最下層の配線ユニット層54を基板面全面にわたって延在させるのが、効果的である。

【0088】またバイヤホール32の深さはソース電極28の配設面から最下層の導電層541に至る深さであり、バイヤホール16の深さは裏側の基板面10bから最下層の導電層541に至る深さであるので、従来形成していたバイヤホールに比べ深さの浅いバイヤホール32、16を用いてソース電極28と裏面電極36とを接続することができる。深さを浅くできる分だけ、バイヤホール径を小さくできる。特に最上層の配線ユニット層12上に複数の電気回路素子14を設ける場合には、基板表側のバイヤホール32の径を小さくすることにより、基板表側の電気回路素子14の集積密度を高めることができるという利点がある。

【0089】また基板裏側のバイヤホール16を電気回路素子14直下に設けるので、このバイヤホール16により電気回路素子14の放熱効率を高めることができる。しかも裏側の基板面10b全面にわたって裏面電極36を設けるようにした場合には、裏側の基板面10b上に設ける電気回路素子は裏面電極36のみであるので、基板裏側の電気回路素子の集積密度を高めるという配慮は不要であり、基板裏側のバイヤホール16の径を大きくできる。径の大きなバイヤホール16を設けることにより、一層、電気回路素子14の放熱効率を高めることができる。基板表側に複数の電気回路素子14を設ける場合には、各電気回路素子14の直下にそれぞれバイヤホール16を設け、個々の電気回路素子14の放熱効率を高めるようにするのが好ましい。

【0090】また配線ユニット層12上に電気回路素子14を設けているので、電気回路素子14直下に基板裏側のバイヤホール16を設けても、電気回路素子14はバイヤホール16を介し露出されることはない。従ってバイヤホール16を電気回路素子14直下に設けても、裏面電極36と電気回路素子14とが直接に接触することはないので、電気回路素子14の動作が損なわれることはない。

【0091】さらにこの実施例では、次のような効果も望める。第一に、中間の配線ユニット層46の導電層461により複数の電気回路素子14のドレイン電極30を共通接続することができるので、配線密度特にドレイン電極30の配設面上における配線密度を低減できる。従って配線取り回し特にドレイン電極30の配線面上における配線取り回しの自由度を増すことができると共に、電気回路素子14の集積密度を高めることが可能となる。配線取り回しの自由度を増し或は電気回路素子14の集積密度を高めるためには、配線ユニット層46の導電層461を、基板面10a全面にわたって平面状に延在させるのが効果的である。さらに最上層の配線ユニット層12の導電層121の電位を、電極端子60を介し一定に保持し安定化することができるので、電気回路素子14の動作特性を安定化することができる。特に電気回路素子14をFETとした場合には、FETのサイドゲート効果或はバックゲート効果を防止できる。また最上層の配線ユニット層12の導電層121の電位を、電極端子60を介し任意好適に変更できるので、回路設計の自由度を増すこともできる。さらに3個の配線ユニット層12、46、54を配線に供することにより、配線密度特にソース電極28或はドレイン電極30の配設面における配線密度を効果的に低減でき、従って電気回路素子14の集積度を高めることができる。

【0092】次に請求項5記載の発明の他の3つの実施例について説明する。そのひとつの実施例は、図9の配線構造において、配線ユニット層12、46、54にバイヤホール32を形成するに当り、バイヤホール32の最終到達深さすなわち設計深さに位置する配線ユニット層54の絶縁層541をエッチングする時は、当該配線ユニット層54の導電層541をエッチングせずに当該配線ユニット層54の絶縁層542を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0093】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層48すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122、導電層121、絶縁層461、導電層462、絶縁層541及び導電層541はエッチングするが、酸素イオンの注入されていない導電層541はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層541に達した所で停止する。

【0094】他のひとつの実施例は、図9の配線構造において、配線ユニット層12、46にバイヤホール50を形成するに当り、バイヤホール50の最終到達深さすなわち設計深さに位置する配線ユニット層46の絶縁層461をエッチングする時は、当該配線ユニット層46の導電層461をエッチングせずに当該配線ユニット層46の絶縁層462を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0095】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層62すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122、導電層121、絶縁層462及び導電層461はエッチングするが、酸素イオンの注入されていない導電層461はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層461に達した所で停止する。

【0096】他のひとつの実施例は、図9の配線構造において、配線ユニット層12にバイヤホール58を形成するに当り、バイヤホール58の最終到達深さすなわち設計深さに位置する配線ユニット層12の絶縁層121をエッチングする時は、当該配線ユニット層12の導電層121をエッチングせずに当該配線ユニット層12の絶縁層122を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0097】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層20すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122及び導電層121はエッチングするが、酸素イオンの注入されていない導電層121はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0098】また請求項6記載の発明の他の実施例について説明する。この実施例は、図9の配線構造において、半導体基板10にバイヤホール16を形成するに当り、バイヤホール16形成のため半導体基板10をエッチングする時は、配線ユニット層54の導電層541をエッチングせずに半導体基板10を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0099】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、基板10はエッチングするが、酸素イオンの注入されていない導電層541はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層541に達した所で停止する。

【0100】発明は上述した実施例にのみ限定されるものではなく、従って各構成成分の配設位置、配設個数、寸法、形状、構成、形成材料、導電型及びそのほかを、発明の趣旨の範囲内で任意好適に変更できる。

【0101】例えば、上述した実施例では電気回路素子14としてリセス構造のGaAsFETを設ける例につき説明したが、このほか、HEMT、InPFET等の化合物半導体素子、或は、Si等の元素半導体素子などGaAs以外の形成材料を用いた電気回路素子14を用いることもできる。また電気回路素子14の機能の観点からは、FETのほか例えばユニポーラトランジスタ、バイポーラトランジスタ、ダイオード、インダクタ、キャパシタ、抵抗、或は電極を電気回路素子14とすることができる。また1種類の電気回路素子14を設けるのみならず、ここで例示したユニポーラトランジスタ、バイポーラトランジスタ、ダイオード等の種々の電気回路素子を混合して設けるようにしても良い。回路設計特に接続関係は、図示例に限定されず、設計に応じて任意好適に変更できる。

【0102】また裏面電極36上に、めっき法等により表面平坦な金属層を形成し、この金属層をPHS(プレーテッドヒートシンク)として用いるようにしても良い。PHSは裏面電極としても機能させることができる。PHSを設けることにより、放熱効率を高めることができる。

【0103】また配線ユニット層の導電層として、n+ −AlGaAs層以外の半導体層例えばn+ −InP層を用いても良いし、或は、Al、Ge、In等の金属層を用いても良い。

【0104】また上述した実施例では、第一主電極28をソース電極、第一主電極領域181bをソース領域、第二主電極30をドレイン電極、第二主電極領域181cをドレイン領域としたが、第一主電極28をドレイン電極、第一主電極領域181bをドレイン領域、第二主電極30をソース電極、第二主電極領域181cをソース領域とすることもできる。

【0105】この発明の配線構造は、GaAsICそのほかの半導体集積回路或は半導体装置を構成するのに用いて好適である。

【0106】

【発明の効果】上述した説明からも明らかなように、請求項1記載の発明の配線構造によれば、配線ユニット層を、基板面に沿って平面状に延在させているので、平面的に見て、バイヤホールと配線ユニット層の導電層とが重なり合う範囲内であれば、バイヤホールの配設位置を自由に変更しても、相対応する電気回路素子と配線ユニット層の導電層とを互いに電気接続できる。従って配線の自由度が増す。また配線ユニット層の導電層を介し各電気回路素子相互の電気接続を行なうことにより、配線密度を低減することもできる。配線ユニット層の配設個数を増加させることにより、一層、配線密度を低減することができる。

【0107】これがため、請求項1記載の発明により、この配線構造に設ける電気回路素子の集積密度を高めることができる。

【0108】また請求項4記載の配線構造によれば、請求項1記載の配線構造において、第n個目の配線ユニット層(すなわち電気回路素子直下の最上層の配線ユニット層)の導電層を、電気回路素子の周辺電位を一定に保ち或は制御するための電極とする。従ってこの第n個目の配線ユニット層の電位を一定に保つことにより、電気回路素子の周辺電位を安定化することができる。周辺電位が安定化することにより、電気回路素子の動作特性或は電気的特性を安定化することができる。或は、第n個目の配線ユニット層の導電層を介し電気回路素子の周辺電位を任意好適に可変制御できる。周辺電位を可変制御することにより、回路設計の自由度を増すことができる。

【0109】これがため、請求項4記載の配線構造によれば、電気回路素子の集積密度を高めることができ、さらにこれと共に、電気回路素子の動作特性或は電気的特性を安定化し或は回路設計の自由度を増すことができる。

【0110】また請求項5記載のバイヤホール形成方法によれば、請求項1記載の配線構造の配線ユニット層にバイヤホールを形成するに当り、当該バイヤホールの最終到達深さ(すなわち設計深さ)に位置する配線ユニット層の導電層でエッチングを確実にストップさせることができるので、バイヤホールの深さを精度良く制御できる。

【0111】これがため、請求項5記載のバイヤホール形成方法によれば、請求項1記載の発明の配線構造にバイヤホールを形成するのに適した、バイヤホール形成方法を提供できる。

【0112】また請求項6記載のバイヤホール形成方法は、請求項1記載の配線構造の半導体基板にバイヤホールを形成するに当り、配線ユニット層の導電層でエッチングを確実にストップさせることができるので、バイヤホールの深さを精度良く制御できる。

【0113】これがため、請求項6記載のバイヤホール形成方法によれば、請求項1記載の発明の配線構造にバイヤホールを形成するのに適した、バイヤホール形成方法を提供できる。

【図面の簡単な説明】

【図1】実施例の構成を概略的に示す断面図である。

【図2】実施例の構成を概略的に示す平面図である。

【図3】(A)〜(C)は実施例の製造工程を概略的に示す断面図である。

【図4】(A)〜(C)は実施例の製造工程を概略的に示す断面図である。

【図5】(A)〜(C)は実施例の製造工程を概略的に示す断面図である。

【図6】(A)〜(B)は実施例の製造工程を概略的に示す断面図である。

【図7】実施例の構成を概略的に示す断面図である。

【図8】実施例の構成を概略的に示す平面図である。

【図9】実施例の構成を概略的に示す断面図である。

【図10】実施例の構成を概略的に示す平面図である。

【符号の説明】

10:半導体基板

12、46、54:配線ユニット層

121、461、541:導電層

122、462、542:絶縁層

14:電気回路素子

16、32、50、58:バイヤホール

【0001】

【産業上の利用分野】この発明は配線構造特に半導体装置の配線に適した配線構造と、この配線構造にバイヤホールを形成するためのバイヤホール形成方法とに関する。

【0002】

【従来の技術】従来より、GaAsICにおいてFETのソース接地を行なう場合にあっては、FETを表側の基板面上に設け、FETのソース電極直下に、基板を貫通するバイヤホールを形成する。そして裏側の基板面にアース電極を設け、バイヤホールを介しFETのソース電極とアース電極とを電気接続する。

【0003】

【発明が解決しようとする課題】しかしながら上述した従来の配線構造では、裏側の基板面からソース電極に至る深さのバイヤホールを、FETの活性層と並列させてソース電極直下に設けないと、ソース電極とアース電極とを電気接続することができない。このように深さの深いバイヤホールを、活性層と並列させて設けなければならないので、集積密度を上げることが難しい。通常、ウエットエッチングによりバイヤホールを形成するので、バイヤホールの深さが深くなる分だけ、バイヤホール径は広くなるからである。

【0004】また基板をICチップ毎に分割する際にICチップが損傷しないように分割を行なうためには、基板厚さを厚くすることが望まれる。しかし基板を厚くする分だけバイヤホールの深さが深くなり、従ってバイヤホール径が広くなるので集積密度が上がらなくなる。

【0005】さらにFETの放熱効率を高めるためには、バイヤホールを活性層直下に設けるのが好ましいが、従来の配線構造では、バイヤホールを活性層直下に設けると、アース電極を活性層と電気接続することとなるので、FETを正常動作させることができなくなる。

【0006】またFETにおいては、サイドゲート効果或はバックゲート効果により活性層の電位が変動し、その結果、FETの電気的特性が変動するという問題があった。これと類似した問題は、FET以外の電気回路素子例えばバイポーラトランジスタ、ダイオード、インダクタ、キャパシタ或は抵抗においても生じる。このような電気的特性の変動を防止するためには、電気回路素子の周辺電位を安定化することが有効である。

【0007】この発明は、上述した従来の問題点を解決するため、より集積密度を高めることのできる配線構造を提供することを第一の目的とし、さらにこの配線構造にバイヤホールを形成するのに適したバイヤホール形成方法を提供することを第二の目的とする。

【0008】またこの発明は、集積密度を高めることができ、しかも電気回路素子の周辺電位を安定化することもできる配線構造を提供することを第三の目的とする。

【0009】

【課題を解決するための手段及び作用】第一の目的を達成するため、請求項1記載の配線構造は、半導体基板と基板面上に積み重ねて設けられたn個(nは自然数)の配線ユニット層とにより配線のための積層体を構成し、配線ユニット層を、基板面側から順次に設けられた導電層及び絶縁層により構成し、この配線ユニット層を、基板面に沿う方向に平面状に延在させて成ることを特徴とする。

【0010】このような配線構造によれば、配線のための積層体の任意好適箇所に電気回路素子及びバイヤホールを設け、所望の電気回路素子と当該素子に対応する配線ユニット層の導電層とを、これら素子及び導電層の間に設けたバイヤホールを介し電気接続することができる。例えば、基板面側から数えて第n個目の配線ユニット層上に電気回路素子を設けることができる。或は、基板面又はその表層に電気回路素子を設け、この電気回路素子上に絶縁層を介し配線ユニット層を設けることができる。或は、配線ユニット層を設けた基板面とは反対側の基板面或はその表層に電気回路素子を設けることができる。或は、複数個の配線ユニット層を設けた場合には、配線ユニット層の絶縁層上に電気回路素子を設け、この電気回路素子上に絶縁層を介し他の配線ユニット層を設けることができる。

【0011】しかも配線ユニット層を、基板面に沿って平面状に延在させているので、平面的に見て、バイヤホールと配線ユニット層の導電層とが重なり合う範囲内であれば、バイヤホールの配設位置を自由に変更しても、相対応する電気回路素子と配線ユニット層の導電層とを互いに電気接続できる。従って配線の自由度が増す。また配線ユニット層の導電層を介し各電気回路素子相互の電気接続を行なうことにより、配線密度を低減することもできる。

【0012】また第三の目的を達成するため、請求項4記載の配線構造は、請求項1記載の配線構造において、基板面側から数えて第n個目の配線ユニット層上に設けられた電気回路素子を備え、第n個目の配線ユニット層の導電層を、電気回路素子の周辺電位を安定化し或は制御するための電極とすることを特徴とする。

【0013】このような配線構造によれば、配線ユニット層を、基板面に沿って平面状に延在させているので、第n個目の配線ユニット層の導電層を一定電位に保つことにより、この第n個目の配線ユニット層上に設けた電気回路素子の周辺電位を安定化することができる。また第n個目の配線ユニット層の導電層の電位を任意好適に変更することにより電気回路素子の周辺電位を可変制御することもできる。

【0014】また第二の目的を達成するため、請求項5記載のバイヤホール形成方法は、請求項1記載の配線構造の配線ユニット層にバイヤホールを形成するに当り、バイヤホールの最終到達深さに位置する配線ユニット層の絶縁層をエッチングする時は、当該配線ユニット層の導電層をエッチングせずに当該配線ユニット層の絶縁層を選択的にエッチングするエッチャント又はエッチングガスを用いることを特徴とする。

【0015】このようなバイヤホール形成方法によれば、配線ユニット層の導電層でエッチングを確実にストップさせることができるので、バイヤホールの深さを精度良く制御できる。

【0016】また第二の目的を達成するため、請求項6記載のバイヤホール形成方法は、請求項1記載の配線構造の半導体基板にバイヤホールを形成するに当り、バイヤホール形成のため半導体基板をエッチングする時は、配線ユニット層の導電層をエッチングせずに半導体基板を選択的にエッチングするエッチャント又はエッチングガスを用いることを特徴とする。

【0017】このようなバイヤホール形成方法によれば、配線ユニット層の導電層でエッチングを確実にストップさせることができるので、バイヤホールの深さを精度良く制御できる。

【0018】

【実施例】以下、図面を参照し、発明の実施例につき説明する。尚、図面は発明が理解できる程度に概略的に示してあるにすぎず、従って発明を図示例に限定するものではない。

【0019】図1及び図2は請求項1の発明の実施例の構成を概略的に示す断面図及び平面図である。図1にあっては、図2のI−I線に沿って取った断面に対応する断面を示す。また図2にあっては、図面の理解を助けるため、ソース電極、ドレイン電極、ゲート電極及び配線電極を省略して示してある。

【0020】これら図にも示すように、この実施例の配線構造は、半導体基板10と基板面10a上に積み重ねて設けられたn個(nは自然数)の配線ユニット層12とにより配線のための積層体Lを構成し、配線ユニット層12を、基板面10a側から順次に設けられた導電層121及び絶縁層122により構成し、そして配線ユニット層12を基板面10aに沿う方向に平面状に延在させて成る。

【0021】この実施例では、n=1とするものであって、GaAs半導体基板10の表側の基板面10a上に、n(n=1)個の配線ユニット層12を積み重ねる。配線ユニット層12は、基板面10a側から順次に設けられたn+ −AlGaAs導電層121及びアンドープGaAs絶縁層122から成る。この配線ユニット層12の導電層121及び絶縁層122を、基板面10a全面にわたる領域に延在させる。

【0022】さらにこの実施例の配線構造は、基板面10a側から数えて第n(n=1)個目の配線ユニット層12上に設けられた電気回路素子14と、半導体基板10に設けられたバイヤホール16とを備え、このバイヤホール16を電気回路素子14直下に配置する。

【0023】ここでは、第n(n=1)個目の配線ユニット層12上に設けられた素子構成層18を用いて、電気回路素子14としてFET(Field Effect Transistor )例えばリセス構造のGaAsFETを構成する。このため、素子構成層18は、配線ユニット層12の絶縁層122上に順次に設けられたn−GaAs活性層181及びn+ −GaAsコンタクト層182から成る。そしてこの素子構成層18に、素子分離用の絶縁層20例えば不純物イオン注入領域を設ける。図にあっては、絶縁層20の形成のための不純物イオンが注入された領域を点を付して示すと共に、絶縁層20の形成のための不純物イオンが注入された領域及び注入されていない領域の境界を点線で示す。

【0024】絶縁層20は、素子構成層18の上面から第n(n=1)個目の配線ユニット層12の導電層121に至る深さを有し、この絶縁層20により、電気回路素子14が配設される島状領域22の周囲を、閉ループ状に取り囲む。この絶縁層20を、図2において、斜めのハッチングを付して示す。

【0025】この結果、島状領域22の素子構成層18と島状領域22以外の領域の素子構成層18とは、第n(n=1)個目の配線ユニット層12の絶縁層122及び素子分離用の絶縁層20により、電気的に絶縁分離される。

【0026】さらに島状領域22の素子構成層18に、コンタクト層182上面から活性層181に至る深さのリセス24を設ける。リセス24を介し、活性層181のチャネル領域181aを露出させ、このチャネル領域181a上にゲート電極26を設ける。またリセス24により、島状領域22のコンタクト層182を、活性層181の第一主電極領域ここではソース領域181bに対応する部分182aと第二主電極領域ここではドレイン領域181cに対応する部分182bとに分断し、一方の分断部分182a上に第一主電極ここではソース電極28及び他方の分断部分182b上に第二主電極ここではドレイン電極30を設ける。

【0027】従って電気回路素子14は、活性層181のチャネル領域181a、ソース領域181b及びドレイン領域181cと、チャネル領域181a上に設けられたゲート電極26と、ソース領域181b上にコンタクト層分断部分182aを介して設けられたソース電極28と、ドレイン領域181c上にコンタクト層分断部分182bを介して設けられたドレイン電極30とから成る。

【0028】またソース電極28に隣接する領域の絶縁層20をバイヤホール形成用の絶縁層として利用し、この領域の絶縁層20にバイヤホール32を設ける。バイヤホール32を、ソース電極28の配設面から最下層の配線ユニット層12の導電層121に至る深さまで形成し、バイヤホール32を介し最下層の導電層121を露出させる。そしてこの露出させた導電層121からソース電極28まで配線電極34を設け、これら導電層121及びソース電極28を、バイヤホール32を介し配線電極34により接続する。

【0029】また電気回路素子14直下の基板10に、バイヤホール16を設ける。バイヤホール16を裏側の基板面10bから最下層の配線ユニット層12の導電層121に至る深さまで形成し、バイヤホール16を介し最下層の導電層121を露出させる。そして裏面電極36を裏側の基板面10b全面にわたる領域に設け、バイヤホール16を介して最下層の導電層121と裏面電極36とを接続する。

【0030】図にあっては、1個の電気回路素子14を図示するのみであるが、配線ユニット層12上には複数の電気回路素子14を設け、各電気回路素子14毎にそれぞれ絶縁層20、バイヤホール32、配線電極34、バイヤホール16を設け、各電気回路素子14のソース電極28をそれぞれ、バイヤホール32、16を介して裏面電極36と接続している。

【0031】この実施例によれば、ソース電極28は、配線電極34と電気的に接続し、さらに配線電極34はバイヤホール32を介して高濃度不純物添加層であるn+ −AlGaAs導電層121と電気的に接続している。n+ −AlGaAs導電層121は高濃度に不純物が添加されているため金属層と同程度に抵抗値が小さい。そしてn+ −AlGaAs導電層121はバイヤホール16を介して裏面電極36と電気的に接続しているので、ソース電極28を裏面電極36と同電位とすることができる。

【0032】配線ユニット層12は平面状に延在しているので、基板裏側のバイヤホール16を、平面的に見て、配線ユニット層12と重なり合う領域に設けてあれば、裏面電極36を配線ユニット層12の導電層121と接続できる。従って基板裏側のバイヤホール16の配設位置(或は形成位置)が、バイヤホール形成のためのフォトリソ及びエッチング工程におけるマスクずれ等により、設計位置からずれたとしても、裏面電極36と配線ユニット層12の導電層121との接続不良が発生するおそれは非常に少ない。接続不良の発生を防止するためには、配線ユニット層12を基板面全面にわたって平面状に延在させるのが、効果的である。

【0033】また従来にあってはソース電極28から裏側の基板面10bに至る深さのバイヤホールを形成し、このバイヤホールを介しソース電極28と裏面電極36とを接続していた。これに対しこの実施例では、バイヤホール32の深さはソース電極28の配設面から配線ユニット層12の導電層121に至る深さであり、バイヤホール16の深さは裏側の基板面10bから配線ユニット層12の導電層121に至る深さであるので、従来形成していたバイヤホールに比べ深さの浅いバイヤホール32、16を用いてソース電極28と裏面電極36とを接続することができる。深さを浅くできる分だけ、バイヤホール径を小さくできる。特に配線ユニット層12上に複数の電気回路素子14を設ける場合には、基板表側のバイヤホール32の径を小さくすることにより、基板表側の電気回路素子14の集積密度を高めることができるという利点がある。

【0034】また基板裏側のバイヤホール16を電気回路素子14直下に設けるので、このバイヤホール16により電気回路素子14の放熱効率を高めることができる。しかも裏側の基板面10b全面にわたって裏面電極36を設けるようにした場合には、裏側の基板面10b上に設ける電気回路素子は裏面電極36のみであるので、基板裏側の電気回路素子の集積密度を高めるという配慮は不要であり、基板裏側のバイヤホール16の径を大きくできる。径の大きなバイヤホール16を設けることにより、一層、電気回路素子14の放熱効率を高めることができる。基板表側に複数の電気回路素子14を設ける場合には、各電気回路素子14の直下にそれぞれバイヤホール16を設け、個々の電気回路素子14の放熱効率を高めるようにするのが好ましい。

【0035】また配線ユニット層12上に電気回路素子14を設けているので、電気回路素子14直下に基板裏側のバイヤホール16を設けても、電気回路素子14はバイヤホール16を介し露出されることはない。従ってバイヤホール16を電気回路素子14直下に設けても、裏面電極36と電気回路素子14とが直接に接触することはないので、電気回路素子14の動作が損なわれることはない。

【0036】次に図3〜図6は図1に示す配線構造の主要な製造工程を段階的に示す断面図である。

【0037】以下、図3〜図6を参照し、図1に示す配線構造の製造方法の一例を説明すると共に、請求項5記載の発明の実施例及び請求項6記載の発明の実施例につき説明する。請求項5記載の発明の実施例は、図1の配線構造において、配線ユニット層12にバイヤホール32を形成するに当り、バイヤホール32の最終到達深さすなわち設計深さに位置する配線ユニット層12の絶縁層122をエッチングする時は、当該配線ユニット層12の導電層121をエッチングせずに当該配線ユニット層12の絶縁層122を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。また請求項6記載の発明の実施例は、図1の配線構造において、半導体基板10にバイヤホール16を形成するに当り、バイヤホール16形成のため半導体基板10をエッチングする時は、配線ユニット層12の導電層121をエッチングせずに半導体基板10を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0038】まず、MBE法等により、GaAs基板10の基板面10a上に順次に、n+−AlGaAs導電層121、アンドープGaAs絶縁層122、n−GaAs活性層181及びn+ −GaAsコンタクト層182を形成する(図3(A))。

【0039】次に、イオン注入法により、不純物イオンここでは酸素イオンを、コンタクト層182から導電層121に至る深さまで注入し、不活性領域である絶縁層20を形成し、電気回路素子14の形成領域となる島状領域22の周囲を絶縁層20で囲む(図3(B))。

【0040】次にリフトオフ法により、ソース電極28及びドレイン電極30を、島状領域22のコンタクト層182上であって活性層18のソース領域181b及びドレイン領域181cに対応する位置に形成する(図3(C))。

【0041】次にソース電極28及びドレイン電極30の間のコンタクト層182に、リセス24を形成し、リセス24を介し活性層181のチャネル領域181aを露出させる。然る後、露出させたチャネル領域181a上にゲート電極26を形成する(図4(A))。

【0042】次にバイヤホール形成用のレジストマスク38を、ゲート電極26上に形成する(図4(B))。レジストマスク38は、基板表側バイヤホール32の形成領域を露出する開口部38aを有する。

【0043】次にレジストマスク38を介し絶縁層20をエッチングして、絶縁層20にバイヤホール32を形成し、このバイヤホール32を介し導電層121を露出させる(図4(C))。この際、絶縁層20はエッチングするが導電層121はエッチングしないエッチャント例えばクエン酸溶液を用いる。クエン酸溶液は、絶縁層20すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122及び導電層121はエッチングするが、酸素イオンの注入されていない導電層121はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0044】エッチングが停止したらレジストマスク38を除去し、然る後、配線電極形成用のレジストマスク40をゲート電極26上に形成する(図5(A))。レジストマスク40は配線電極34の形成領域を露出する開口部40aを有する。

【0045】次に、真空蒸着法によりレジストマスク40を介し配線電極材料42を堆積させる(図5(B))。然る後、レジストマスク40を除去し、配線電極34の形成領域に残存する配線電極材料42から成る配線電極34を得る。

【0046】次に、バイヤホール形成用のレジストマスク44を、裏側の基板面10b上に形成する(図5(C))。レジストマスク44は基板裏側バイヤホール16の形成領域を露出する開口部44aを有する。従来と比較して、レジストマスク44の開口部44aの幅を10倍以上とし、またレジストマスク44形成のために用いる露光マスクの位置合わせ精度を±5μm程度にまで緩やかにすることができる。

【0047】次にレジストマスク44を介し基板10をエッチングして、基板裏側のバイヤホール16を形成する(図6(A))。このエッチングの際、基板10はエッチングするが酸素イオンが注入されていない導電層121はエッチングしないエッチャント例えばクエン酸溶液を用いる。クエン酸溶液を用いることにより、エッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0048】エッチングが停止した後エッチングマスク44を除去する。然る後、真空蒸着法により、裏側の基板面10b全面にわたって裏面電極36を形成し(図6(B))、図1の配線構造を完成する。

【0049】このようにバイヤホール32、16を形成するためのエッチングにおいて、酸素イオンが注入されていない導電層121で自動的にエッチングが停止するので、オーバーエッチングが生じず、従って配線不良の発生や電気回路素子14の損傷の発生を防止できる。

【0050】図7及び図8は請求項1の発明の他の実施例の構成を概略的に示す断面図及び平面図である。図7にあっては、図8のVII−VII線に沿って取った断面に対応する断面を示す。また図8にあっては、図面の理解を助けるため、ソース電極、ドレイン電極、ゲート電極及び配線電極を省略して示してある。

【0051】以下、図1の実施例と相違する点につき説明し、図1の実施例と同様の点についてはその詳細な説明を省略する。

【0052】この実施例では、n=2としn(=2)個の配線ユニット層46、12を、表側の基板面10a上に、積み重ねて設け、これら配線ユニット層46、12及び基板10により配線のための積層体Lを構成する。

【0053】基板面10a上に順次に、基板面10a全面にわたって平面状に延在させて、配線ユニット層46及び12を設け、配線ユニット層46を、基板面10a側から順次に設けられたn+ −AlGaAs導電層461及びアンドープGaAs絶縁層462により構成する。そして第n(n=2)個目の配線ユニット層12上に電気回路素子14を設ける。

【0054】またソース電極28に隣接する領域に、バイヤホール形成用の絶縁層48例えばイオン注入領域を設ける。絶縁層48を例えば酸素イオンの注入領域とする。平面的に見て、絶縁層48の一部又は全部を絶縁層20と重ね合わせるように設け、絶縁層48を、ソース電極28の配設面から最下層の配線ユニット層46の導電層461に至る深さに形成する。図にあっては、絶縁層20、48の形成のための不純物イオンが注入された領域を点を付して示すと共に、絶縁層20、48の形成のための不純物イオンが注入された領域及び注入されていない領域の境界を点線で示す。

【0055】そして絶縁層48に、バイヤホール32を設ける。バイヤホール32をソース電極28の配設面から最下層の配線ユニット層46の導電層461に至る深さに形成し、バイヤホール32を介し、最下層の導電層461を露出させる。そして露出させた最下層の導電層461からソース電極28まで配線電極34を設け、これら導電層461及びソース電極28を、バイヤホール32を介して配線電極34により接続する。

【0056】またバイヤホール16を、裏側の基板面10bから最下層の導電層461に至る深さに形成し、このバイヤホール16を介し裏面電極36と最下層の導電層461とを接続する。

【0057】さらにドレイン電極30に隣接する領域の絶縁層20をバイヤホール形成用の絶縁層に利用し、この領域の絶縁層20にバイヤホール50を設ける。バイヤホール50を、ドレイン電極20の配設面から残りの配線ユニット層12の導電層121に至る深さに形成し、バイヤホール50を介し残りの導電層121を露出させる。そして露出させた導電層121からドレイン電極30まで配線電極52を設け、これら導電層121及びドレイン電極30を、バイヤホール50を介して配線電極52により接続する。

【0058】図にあっては、1個の電気回路素子14を図示するのみであるが、配線ユニット層12上には複数の電気回路素子14を設け、各電気回路素子14毎にそれぞれ絶縁層20、バイヤホール32、配線電極34、バイヤホール16、バイヤホール50及び配線電極52を設け、各電気回路素子14のソース電極28をそれぞれ、バイヤホール32、16を介して裏面電極36と接続すると共に、各電気回路素子14のドレイン電極30をそれぞれ、これらに共通の導電層121とバイヤホール50を介して接続している。

【0059】この実施例によれば、ソース電極28は、配線電極34と電気的に接続し、さらに配線電極34はバイヤホール32を介して高濃度不純物添加層であるn+ −AlGaAs導電層461と電気的に接続している。n+ −AlGaAs導電層461は高濃度に不純物が添加されているため金属層と同程度に抵抗値が小さい。そしてn+ −AlGaAs導電層461はバイヤホール16を介して裏面電極36と電気的に接続しているので、ソース電極28と裏面電極36とは同電位となることができる。

【0060】またドレイン電極30は配線電極52と接続し、さらに配線電極52はバイヤホール50を介してn+ −AlGaAs導電層121と接続しているので、ドレイン電極30をn+ −AlGaAs層121と同電位とすることができる。

【0061】この実施例においても、図1の実施例と同様に、基板裏側のバイヤホール16の配設位置(或は形成位置)が設計位置からずれたとしても、裏面電極36と最下層の導電層461との接続不良が発生するおそれは非常に少ない。接続不良の発生を防止するためには、最下層の配線ユニット層46を基板面全面にわたって延在させるのが、効果的である。

【0062】またバイヤホール32の深さはソース電極28の配設面から最下層の導電層461に至る深さであり、バイヤホール16の深さは裏側の基板面10bから最下層の導電層461に至る深さであるので、従来形成していたバイヤホールに比べ深さの浅いバイヤホール32、16を用いてソース電極28と裏面電極36とを接続することができる。深さを浅くできる分だけ、バイヤホール径を小さくできる。特に最上層の配線ユニット層12上に複数の電気回路素子14を設ける場合には、基板表側のバイヤホール32の径を小さくすることにより、基板表側の電気回路素子14の集積密度を高めることができるという利点がある。

【0063】また基板裏側のバイヤホール16を電気回路素子14直下に設けるので、このバイヤホール16により電気回路素子14の放熱効率を高めることができる。しかも裏側の基板面10b全面にわたって裏面電極36を設けるようにした場合には、裏側の基板面10b上に設ける電気回路素子は裏面電極36のみであるので、基板裏側の電気回路素子の集積密度を高めるという配慮は不要であり、基板裏側のバイヤホール16の径を大きくできる。径の大きなバイヤホール16を設けることにより、一層、電気回路素子14の放熱効率を高めることができる。基板表側に複数の電気回路素子14を設ける場合には、各電気回路素子14の直下にそれぞれバイヤホール16を設け、個々の電気回路素子14の放熱効率を高めるようにするのが好ましい。

【0064】また配線ユニット層12上に電気回路素子14を設けているので、電気回路素子14直下に基板裏側のバイヤホール16を設けても、電気回路素子14はバイヤホール16を介し露出されることはない。従ってバイヤホール16を電気回路素子14直下に設けても、裏面電極36と電気回路素子14とが直接に接触することはないので、電気回路素子14の動作が損なわれることはない。

【0065】さらにこの実施例では、次のような効果も望める。すなわち、配線ユニット層12の導電層121により複数の電気回路素子14のドレイン電極30を共通接続することができるので、配線密度特にドレイン電極30の配設面上における配線密度を低減できる。従って配線取り回し特にドレイン電極30の配線面上における配線取り回しの自由度を増すことができると共に、電気回路素子14の集積密度を高めることが可能となる。配線取り回しの自由度を増し或は電気回路素子14の集積密度を高めるためには、配線ユニット層12の導電層121を、基板面10a全面にわたって平面状に延在させるのが効果的である。

【0066】次に請求項5記載の発明の他の2つの実施例について説明する。そのひとつの実施例は、図7の配線構造において、配線ユニット層12、46にバイヤホール32を形成するに当り、バイヤホール32の最終到達深さすなわち設計深さに位置する配線ユニット層46の絶縁層461をエッチングする時は、当該配線ユニット層46の導電層461をエッチングせずに当該配線ユニット層46の絶縁層462を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0067】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層48すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122、導電層121、絶縁層461及び導電層462はエッチングするが、酸素イオンの注入されていない導電層461はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層461に達した所で停止する。

【0068】他のひとつの実施例は、図7の配線構造において、配線ユニット層12にバイヤホール50を形成するに当り、バイヤホール50の最終到達深さすなわち設計深さに位置する配線ユニット層12の絶縁層121をエッチングする時は、当該配線ユニット層12の導電層121をエッチングせずに当該配線ユニット層12の絶縁層122を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0069】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層20すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122及び導電層121はエッチングするが、酸素イオンの注入されていない導電層121はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0070】また請求項6記載の発明の他の実施例について説明する。この実施例は、図7の配線構造において、半導体基板10にバイヤホール16を形成するに当り、バイヤホール16形成のため半導体基板10をエッチングする時は、配線ユニット層46の導電層461をエッチングせずに半導体基板10を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0071】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、基板10はエッチングするが、酸素イオンの注入されていない導電層121はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0072】図9及び図10は請求項4の発明の実施例の構成を概略的に示す断面図及び平面図である。図9にあっては、図10のIX−IX線に沿って取った断面に対応する断面を示す。また図10にあっては、図面の理解を助けるため、ソース電極、ドレイン電極、ゲート電極及び配線電極を省略して示してある。

【0073】この実施例は請求項1の発明の実施例でもあり、以下、図1の実施例と相違する点につき説明し、図1の実施例と同様の点についてはその詳細な説明を省略する。

【0074】この実施例では、n=3としn(=3)個の配線ユニット層54、46、12を、表側の基板面10a上に、積み重ねて設け、これら配線ユニット層54、46、12及び基板10により配線のための積層体Lを構成する。

【0075】基板面10a上に順次に、基板面10a全面にわたって平面状に延在させて、配線ユニット層54、46及び12を設け、配線ユニット層54を、基板面10a側から順次に設けられたn+ −AlGaAs導電層541及びアンドープGaAs絶縁層542により構成する。そして第n(n=3)個目の配線ユニット層12上に電気回路素子14を設ける。

【0076】またソース電極28に隣接する領域に、バイヤホール形成用の絶縁層48例えばイオン注入領域を設ける。絶縁層48を例えば酸素イオンの注入領域とする。平面的に見て、絶縁層48の一部又は全部を絶縁層20と重ね合わせるように設け、絶縁層48を、ソース電極28の配設面から最下層の配線ユニット層54の導電層541に至る深さに形成する。

【0077】そして絶縁層48に、バイヤホール32を設ける。バイヤホール32をソース電極28の配設面から最下層の配線ユニット層54の導電層541に至る深さに形成し、バイヤホール32を介し、最下層の導電層541を露出させる。そして露出させた最下層の導電層541からソース電極28まで配線電極34を設け、これら導電層541及びソース電極28を、バイヤホール32を介して配線電極34により接続する。

【0078】またバイヤホール16を、裏側の基板面10bから最下層の導電層541に至る深さに形成し、このバイヤホール16を介し裏面電極36と最下層の導電層541とを接続する。

【0079】さらに第n(n=3)個目の配線ユニット層12の導電層121を、電気回路素子14の周辺電位を安定化し或は制御するための電極とする。

【0080】ここでは、絶縁層20をバイヤホール形成用の絶縁層に利用する。絶縁層20は、ソース電極28或はドレイン電極30の配設面から第n(n=3)個目すなわち最上層の配線ユニット層12の導電層121に至る深さを有する。そしてこの絶縁層20の任意好適箇所にバイヤホール58を設ける。バイヤホール58を、ソース電極28或はドレイン電極30の配設面から最上層の導電層121に至る深さに形成し、このバイヤホール58を介し最上層の導電層121を露出させる。そして最上層の導電層121から、ソース電極28或はドレイン電極30の配線面まで電極端子60を設ける。

【0081】さらにドレイン電極30に隣接する領域に、バイヤホール形成用の絶縁層62例えばイオン注入領域を設ける。絶縁層62を例えば酸素イオンの注入領域とする。平面的に見て、絶縁層62の一部又は全部を絶縁層20と重ね合わせるように設け、絶縁層62を、ドレイン電極30の配設面から、残りの配線ユニット層46(中間の配線ユニット層46)の導電層461に至る深さに形成する。

【0082】そして絶縁層62に、バイヤホール50を設ける。バイヤホール50をドレイン電極30の配設面から中間の配線ユニット層46の導電層461に至る深さに形成し、バイヤホール50を介し、中間の導電層461を露出させる。そして露出させた中間の導電層461からドレイン電極30まで配線電極52を設け、これら導電層461及びドレイン電極30を、バイヤホール62を介して配線電極52により接続する。

【0083】図にあっては、絶縁層48、20、62の形成のための不純物イオンが注入された領域を点を付して示すと共に、絶縁層48、20、62の形成のための不純物イオンが注入された領域及び注入されていない領域の境界を点線で示す。また図にあっては、1個の電気回路素子14を図示するのみであるが、配線ユニット層12上には複数の電気回路素子14を設け、各電気回路素子14毎にそれぞれ絶縁層20、バイヤホール32、配線電極34、バイヤホール16、バイヤホール50及び配線電極52を設け、各電気回路素子14のソース電極28をそれぞれ、バイヤホール32、16を介して裏面電極36と接続すると共に、各電気回路素子14のドレイン電極30をそれぞれ、これらに共通の導電層461とバイヤホール50を介して接続している。また電気回路素子14の周辺電位を安定化するための導電層121及びその電極端子60は、これら各電気回路素子14に共通の導電層及び電極端子である。

【0084】この実施例によれば、ソース電極28は、配線電極34と電気的に接続し、さらに配線電極34はバイヤホール32を介して高濃度不純物添加層であるn+ −AlGaAs導電層541と電気的に接続している。n+ −AlGaAs導電層541は高濃度に不純物が添加されているため金属層と同程度に抵抗値が小さい。そしてn+ −AlGaAs導電層541はバイヤホール16を介して裏面電極36と電気的に接続しているので、ソース電極28を裏面電極36と同電位とすることができる。

【0085】またドレイン電極30は配線電極52と接続し、さらに配線電極52はバイヤホール50を介してn+ −AlGaAs導電層461と接続しているので、ドレイン電極30をn+ −AlGaAs層461と同電位とすることができる。

【0086】また電極端子60はバイヤホール58を介しn+ −AlGaAs導電層121と接続しているので、電極端子60を介し導電層121に一定電位を供給することにより、導電層121の電位を安定化することができる。

【0087】この実施例においても、図1の実施例と同様に、基板裏側のバイヤホール16の配設位置(或は形成位置)が設計位置からずれたとしても、裏面電極36と最下層の導電層541との接続不良が発生するおそれは非常に少ない。接続不良の発生を防止するためには、最下層の配線ユニット層54を基板面全面にわたって延在させるのが、効果的である。

【0088】またバイヤホール32の深さはソース電極28の配設面から最下層の導電層541に至る深さであり、バイヤホール16の深さは裏側の基板面10bから最下層の導電層541に至る深さであるので、従来形成していたバイヤホールに比べ深さの浅いバイヤホール32、16を用いてソース電極28と裏面電極36とを接続することができる。深さを浅くできる分だけ、バイヤホール径を小さくできる。特に最上層の配線ユニット層12上に複数の電気回路素子14を設ける場合には、基板表側のバイヤホール32の径を小さくすることにより、基板表側の電気回路素子14の集積密度を高めることができるという利点がある。

【0089】また基板裏側のバイヤホール16を電気回路素子14直下に設けるので、このバイヤホール16により電気回路素子14の放熱効率を高めることができる。しかも裏側の基板面10b全面にわたって裏面電極36を設けるようにした場合には、裏側の基板面10b上に設ける電気回路素子は裏面電極36のみであるので、基板裏側の電気回路素子の集積密度を高めるという配慮は不要であり、基板裏側のバイヤホール16の径を大きくできる。径の大きなバイヤホール16を設けることにより、一層、電気回路素子14の放熱効率を高めることができる。基板表側に複数の電気回路素子14を設ける場合には、各電気回路素子14の直下にそれぞれバイヤホール16を設け、個々の電気回路素子14の放熱効率を高めるようにするのが好ましい。

【0090】また配線ユニット層12上に電気回路素子14を設けているので、電気回路素子14直下に基板裏側のバイヤホール16を設けても、電気回路素子14はバイヤホール16を介し露出されることはない。従ってバイヤホール16を電気回路素子14直下に設けても、裏面電極36と電気回路素子14とが直接に接触することはないので、電気回路素子14の動作が損なわれることはない。

【0091】さらにこの実施例では、次のような効果も望める。第一に、中間の配線ユニット層46の導電層461により複数の電気回路素子14のドレイン電極30を共通接続することができるので、配線密度特にドレイン電極30の配設面上における配線密度を低減できる。従って配線取り回し特にドレイン電極30の配線面上における配線取り回しの自由度を増すことができると共に、電気回路素子14の集積密度を高めることが可能となる。配線取り回しの自由度を増し或は電気回路素子14の集積密度を高めるためには、配線ユニット層46の導電層461を、基板面10a全面にわたって平面状に延在させるのが効果的である。さらに最上層の配線ユニット層12の導電層121の電位を、電極端子60を介し一定に保持し安定化することができるので、電気回路素子14の動作特性を安定化することができる。特に電気回路素子14をFETとした場合には、FETのサイドゲート効果或はバックゲート効果を防止できる。また最上層の配線ユニット層12の導電層121の電位を、電極端子60を介し任意好適に変更できるので、回路設計の自由度を増すこともできる。さらに3個の配線ユニット層12、46、54を配線に供することにより、配線密度特にソース電極28或はドレイン電極30の配設面における配線密度を効果的に低減でき、従って電気回路素子14の集積度を高めることができる。

【0092】次に請求項5記載の発明の他の3つの実施例について説明する。そのひとつの実施例は、図9の配線構造において、配線ユニット層12、46、54にバイヤホール32を形成するに当り、バイヤホール32の最終到達深さすなわち設計深さに位置する配線ユニット層54の絶縁層541をエッチングする時は、当該配線ユニット層54の導電層541をエッチングせずに当該配線ユニット層54の絶縁層542を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0093】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層48すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122、導電層121、絶縁層461、導電層462、絶縁層541及び導電層541はエッチングするが、酸素イオンの注入されていない導電層541はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層541に達した所で停止する。

【0094】他のひとつの実施例は、図9の配線構造において、配線ユニット層12、46にバイヤホール50を形成するに当り、バイヤホール50の最終到達深さすなわち設計深さに位置する配線ユニット層46の絶縁層461をエッチングする時は、当該配線ユニット層46の導電層461をエッチングせずに当該配線ユニット層46の絶縁層462を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0095】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層62すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122、導電層121、絶縁層462及び導電層461はエッチングするが、酸素イオンの注入されていない導電層461はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層461に達した所で停止する。

【0096】他のひとつの実施例は、図9の配線構造において、配線ユニット層12にバイヤホール58を形成するに当り、バイヤホール58の最終到達深さすなわち設計深さに位置する配線ユニット層12の絶縁層121をエッチングする時は、当該配線ユニット層12の導電層121をエッチングせずに当該配線ユニット層12の絶縁層122を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0097】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、絶縁層20すなわち酸素イオンがそれぞれ注入されたコンタクト層182、活性層181、絶縁層122及び導電層121はエッチングするが、酸素イオンの注入されていない導電層121はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層121に達した所で停止する。

【0098】また請求項6記載の発明の他の実施例について説明する。この実施例は、図9の配線構造において、半導体基板10にバイヤホール16を形成するに当り、バイヤホール16形成のため半導体基板10をエッチングする時は、配線ユニット層54の導電層541をエッチングせずに半導体基板10を選択的にエッチングするエッチャント又はエッチングガスを用いるというものである。

【0099】例えば、エッチャントとしてクエン酸溶液を用いれば良い。クエン酸溶液は、基板10はエッチングするが、酸素イオンの注入されていない導電層541はエッチングしない。従ってエッチングは酸素イオンが注入されていない導電層541に達した所で停止する。

【0100】発明は上述した実施例にのみ限定されるものではなく、従って各構成成分の配設位置、配設個数、寸法、形状、構成、形成材料、導電型及びそのほかを、発明の趣旨の範囲内で任意好適に変更できる。

【0101】例えば、上述した実施例では電気回路素子14としてリセス構造のGaAsFETを設ける例につき説明したが、このほか、HEMT、InPFET等の化合物半導体素子、或は、Si等の元素半導体素子などGaAs以外の形成材料を用いた電気回路素子14を用いることもできる。また電気回路素子14の機能の観点からは、FETのほか例えばユニポーラトランジスタ、バイポーラトランジスタ、ダイオード、インダクタ、キャパシタ、抵抗、或は電極を電気回路素子14とすることができる。また1種類の電気回路素子14を設けるのみならず、ここで例示したユニポーラトランジスタ、バイポーラトランジスタ、ダイオード等の種々の電気回路素子を混合して設けるようにしても良い。回路設計特に接続関係は、図示例に限定されず、設計に応じて任意好適に変更できる。

【0102】また裏面電極36上に、めっき法等により表面平坦な金属層を形成し、この金属層をPHS(プレーテッドヒートシンク)として用いるようにしても良い。PHSは裏面電極としても機能させることができる。PHSを設けることにより、放熱効率を高めることができる。

【0103】また配線ユニット層の導電層として、n+ −AlGaAs層以外の半導体層例えばn+ −InP層を用いても良いし、或は、Al、Ge、In等の金属層を用いても良い。

【0104】また上述した実施例では、第一主電極28をソース電極、第一主電極領域181bをソース領域、第二主電極30をドレイン電極、第二主電極領域181cをドレイン領域としたが、第一主電極28をドレイン電極、第一主電極領域181bをドレイン領域、第二主電極30をソース電極、第二主電極領域181cをソース領域とすることもできる。

【0105】この発明の配線構造は、GaAsICそのほかの半導体集積回路或は半導体装置を構成するのに用いて好適である。

【0106】

【発明の効果】上述した説明からも明らかなように、請求項1記載の発明の配線構造によれば、配線ユニット層を、基板面に沿って平面状に延在させているので、平面的に見て、バイヤホールと配線ユニット層の導電層とが重なり合う範囲内であれば、バイヤホールの配設位置を自由に変更しても、相対応する電気回路素子と配線ユニット層の導電層とを互いに電気接続できる。従って配線の自由度が増す。また配線ユニット層の導電層を介し各電気回路素子相互の電気接続を行なうことにより、配線密度を低減することもできる。配線ユニット層の配設個数を増加させることにより、一層、配線密度を低減することができる。

【0107】これがため、請求項1記載の発明により、この配線構造に設ける電気回路素子の集積密度を高めることができる。

【0108】また請求項4記載の配線構造によれば、請求項1記載の配線構造において、第n個目の配線ユニット層(すなわち電気回路素子直下の最上層の配線ユニット層)の導電層を、電気回路素子の周辺電位を一定に保ち或は制御するための電極とする。従ってこの第n個目の配線ユニット層の電位を一定に保つことにより、電気回路素子の周辺電位を安定化することができる。周辺電位が安定化することにより、電気回路素子の動作特性或は電気的特性を安定化することができる。或は、第n個目の配線ユニット層の導電層を介し電気回路素子の周辺電位を任意好適に可変制御できる。周辺電位を可変制御することにより、回路設計の自由度を増すことができる。

【0109】これがため、請求項4記載の配線構造によれば、電気回路素子の集積密度を高めることができ、さらにこれと共に、電気回路素子の動作特性或は電気的特性を安定化し或は回路設計の自由度を増すことができる。

【0110】また請求項5記載のバイヤホール形成方法によれば、請求項1記載の配線構造の配線ユニット層にバイヤホールを形成するに当り、当該バイヤホールの最終到達深さ(すなわち設計深さ)に位置する配線ユニット層の導電層でエッチングを確実にストップさせることができるので、バイヤホールの深さを精度良く制御できる。

【0111】これがため、請求項5記載のバイヤホール形成方法によれば、請求項1記載の発明の配線構造にバイヤホールを形成するのに適した、バイヤホール形成方法を提供できる。

【0112】また請求項6記載のバイヤホール形成方法は、請求項1記載の配線構造の半導体基板にバイヤホールを形成するに当り、配線ユニット層の導電層でエッチングを確実にストップさせることができるので、バイヤホールの深さを精度良く制御できる。

【0113】これがため、請求項6記載のバイヤホール形成方法によれば、請求項1記載の発明の配線構造にバイヤホールを形成するのに適した、バイヤホール形成方法を提供できる。

【図面の簡単な説明】

【図1】実施例の構成を概略的に示す断面図である。

【図2】実施例の構成を概略的に示す平面図である。

【図3】(A)〜(C)は実施例の製造工程を概略的に示す断面図である。

【図4】(A)〜(C)は実施例の製造工程を概略的に示す断面図である。

【図5】(A)〜(C)は実施例の製造工程を概略的に示す断面図である。

【図6】(A)〜(B)は実施例の製造工程を概略的に示す断面図である。

【図7】実施例の構成を概略的に示す断面図である。

【図8】実施例の構成を概略的に示す平面図である。

【図9】実施例の構成を概略的に示す断面図である。

【図10】実施例の構成を概略的に示す平面図である。

【符号の説明】

10:半導体基板

12、46、54:配線ユニット層

121、461、541:導電層

122、462、542:絶縁層

14:電気回路素子

16、32、50、58:バイヤホール

【特許請求の範囲】

【請求項1】 半導体基板と、基板面上に積み重ねて設けられたn個(nは自然数)の配線ユニット層とにより配線のための積層体を構成し、前記配線ユニット層を、基板面側から順次に設けられた導電層及び絶縁層により構成し、該配線ユニット層を、基板面に沿う方向に平面状に延在させて成ることを特徴とする配線構造。

【請求項2】 請求項1記載の配線構造において、配線ユニット層を、基板面全面にわたる領域に延在させて成ることを特徴とする配線構造。

【請求項3】 請求項1記載の配線構造において、基板面側から数えて第n個目の配線ユニット層上に設けられた電気回路素子と、半導体基板に設けられたバイヤホールとを備え、該バイヤホールを前記電気回路素子直下に配置して成ることを特徴とする配線構造。

【請求項4】 請求項1記載の配線構造において、基板面側から数えて第n個目の配線ユニット層上に設けられた電気回路素子を備え、該第n個目の配線ユニット層の導電層を、前記電気回路素子の周辺電位を安定化し或は制御するための電極とすることを特徴とする配線構造。

【請求項5】 請求項1記載の配線構造の配線ユニット層にバイヤホールを形成するに当り、バイヤホールの最終到達深さに位置する配線ユニット層の絶縁層をエッチングする時は、当該配線ユニット層の導電層をエッチングせずに当該配線ユニット層の絶縁層を選択的にエッチングするエッチャント又はエッチングガスを用いることを特徴とするバイヤホール形成方法。

【請求項6】 請求項1記載の配線構造の半導体基板にバイヤホールを形成するに当り、バイヤホール形成のため半導体基板をエッチングする時は、配線ユニット層の導電層をエッチングせずに半導体基板を選択的にエッチングするエッチャント又はエッチングガスを用いることを特徴とするバイヤホール形成方法。

【請求項1】 半導体基板と、基板面上に積み重ねて設けられたn個(nは自然数)の配線ユニット層とにより配線のための積層体を構成し、前記配線ユニット層を、基板面側から順次に設けられた導電層及び絶縁層により構成し、該配線ユニット層を、基板面に沿う方向に平面状に延在させて成ることを特徴とする配線構造。

【請求項2】 請求項1記載の配線構造において、配線ユニット層を、基板面全面にわたる領域に延在させて成ることを特徴とする配線構造。

【請求項3】 請求項1記載の配線構造において、基板面側から数えて第n個目の配線ユニット層上に設けられた電気回路素子と、半導体基板に設けられたバイヤホールとを備え、該バイヤホールを前記電気回路素子直下に配置して成ることを特徴とする配線構造。

【請求項4】 請求項1記載の配線構造において、基板面側から数えて第n個目の配線ユニット層上に設けられた電気回路素子を備え、該第n個目の配線ユニット層の導電層を、前記電気回路素子の周辺電位を安定化し或は制御するための電極とすることを特徴とする配線構造。

【請求項5】 請求項1記載の配線構造の配線ユニット層にバイヤホールを形成するに当り、バイヤホールの最終到達深さに位置する配線ユニット層の絶縁層をエッチングする時は、当該配線ユニット層の導電層をエッチングせずに当該配線ユニット層の絶縁層を選択的にエッチングするエッチャント又はエッチングガスを用いることを特徴とするバイヤホール形成方法。

【請求項6】 請求項1記載の配線構造の半導体基板にバイヤホールを形成するに当り、バイヤホール形成のため半導体基板をエッチングする時は、配線ユニット層の導電層をエッチングせずに半導体基板を選択的にエッチングするエッチャント又はエッチングガスを用いることを特徴とするバイヤホール形成方法。

【図1】

【図2】

【図3】

【図4】

【図6】

【図7】

【図5】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図6】

【図7】

【図5】

【図8】

【図9】

【図10】

【公開番号】特開平8−167620

【公開日】平成8年(1996)6月25日

【国際特許分類】

【出願番号】特願平6−306512

【出願日】平成6年(1994)12月9日

【出願人】(000000295)沖電気工業株式会社 (6,645)

【公開日】平成8年(1996)6月25日

【国際特許分類】

【出願日】平成6年(1994)12月9日

【出願人】(000000295)沖電気工業株式会社 (6,645)

[ Back to top ]