配線構造及びそれを用いた表示装置

【課題】 薄膜トランジスタを備えたアクティブマトリックス型の液晶表示装置において、ゲート電極を含む走査ラインをAl−Nd合金によって形成した際に、ピンホール(ボイド)が発生しても別に問題はなく、しかも抵抗率を10μΩcm程度以下とする。

【解決手段】 ゲート電極2を含む走査ラインは、ガラス基板1上に形成されたAl−Nd合金からなる第1配線層2aと、この第1配線層2a上に形成されたAl−Ti合金からなる第2配線層2bとによって構成されている。この場合、Al−Nd合金からなる第1配線層2aにピンホールが発生しても、その上に形成されたAl−Ti合金からなる第2配線層2bによって断線を防止することができ、したがってピンホールが発生しても別に問題はなく、しかも抵抗率を10μΩcm程度以下とすることができる。

【解決手段】 ゲート電極2を含む走査ラインは、ガラス基板1上に形成されたAl−Nd合金からなる第1配線層2aと、この第1配線層2a上に形成されたAl−Ti合金からなる第2配線層2bとによって構成されている。この場合、Al−Nd合金からなる第1配線層2aにピンホールが発生しても、その上に形成されたAl−Ti合金からなる第2配線層2bによって断線を防止することができ、したがってピンホールが発生しても別に問題はなく、しかも抵抗率を10μΩcm程度以下とすることができる。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】この発明は配線構造及びそれを用いた表示装置に関する。

【0002】

【従来の技術】例えば、アクティブマトリックス型の液晶表示装置には、走査ライン及び信号ライン等からなる配線を備えているとともに、走査ラインと信号ラインの各交点近傍に画素電極及び該画素電極に接続されたスイッチング素子としての薄膜トランジスタを備えたものがある。

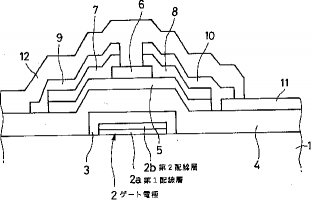

【0003】図3は従来のこのような液晶表示装置の一部の断面図を示したものである。この液晶表示装置はガラス基板1を備えている。ガラス基板1の上面の所定の箇所にはゲート電極2を含む走査ライン(図示せず)が形成され、その表面には陽極酸化膜3が形成され、その上面全体にはゲート絶縁膜4が形成されている。ゲート絶縁膜4の上面の所定の箇所でゲート電極2に対応する部分にはアモルファスシリコンからなる半導体薄膜5が形成されている。半導体薄膜5の上面の中央部にはブロッキング層6が形成されている。半導体薄膜5及びブロッキング層6の上面の両側にはn+シリコンからなるオーミックコンタクト層7、8が形成されている。オーミックコンタクト層7、8の各上面にはドレイン電極9及びソース電極10が形成されている。また、これら電極9、10の形成と同時に信号ライン(図示せず)が形成されている。ゲート絶縁膜4の上面の所定の箇所にはITOからなる画素電極11がソース電極10に接続されて形成されている。画素電極11の所定の部分を除く上面全体にはパッシベーション膜12が形成されている。

【0004】ところで、ゲート電極2を含む走査ラインからなる配線の材料としては、一般に、Ti、Ta、Mo、Cr等の高融点金属を含有するAl合金が用いられている。この場合、AlにTi等の高融点金属を含有させるのは、Alの耐熱性が十分でなく、後工程の加熱工程においてヒロックが発生するのを抑制するためである。このように、耐ヒロック特性を考慮するのは、例えば、ゲート電極2を含む走査ライン上に形成されるゲート絶縁膜4の絶縁耐圧が低下しないようにするためである。

【0005】しかるに、このような耐ヒロック特性を考慮した場合、Ti等の含有量を3at%程度以下とすることができず、ひいては配線(ゲート電極2を含む走査ライン)の抵抗率を20μΩcm程度以下とすることができない。一方、最近では、液晶表示装置の高精細化や高開口率化等に伴って、配線のより一層の低抵抗化が要求されている。このため、最近では、耐ヒロック特性が良く、しかも抵抗率を10μΩcm程度以下とすることのできるAl−Nd合金が注目されている。

【0006】

【発明が解決しようとする課題】しかしながら、Al−Nd合金からなる配線の場合には、ピンホール(ボイド)の発生が問題となっている。すなわち、走査ラインにピンホールが発生した場合には、走査ラインの断線により線欠陥となり、ゲート電極2にピンホールが発生した場合には、薄膜トランジスタの欠陥により点欠陥となり、歩留及び信頼性が低下することになる。この発明の課題は、配線にピンホールに起因する断線が生じないようにすることができ、しかも配線の抵抗率を10μΩcm程度以下とすることができるようにすることである。

【0007】

【課題を解決するための手段】請求項1記載の発明は、希土類元素の1種または2種以上を含有するAl合金からなる第1配線層とTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層とを含む複数の配線層で構成したものである。請求項5記載の発明は、主としてAlからなる第1配線層と、希土類元素の1種または2種以上を含有するAl合金からなる第2配線層と、Ti、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第3配線層とによって配線を構成したものである。

【0008】この発明によれば、Nd等の希土類元素を含有するAl合金からなる配線層にピンホールが発生しても、一体的に形成されたTi等の高融点金属を含有するAl合金からなる配線層によって断線を防止することができ、したがって配線にピンホールに起因する断線が生じないようにすることができ、しかも配線の抵抗率を10μΩcm程度以下とすることができる。

【0009】

【発明の実施の形態】図1はこの発明の第1実施形態における液晶表示装置の要部の断面図を示したものである。この図において、図3と同一名称部分には同一の符号を付し、その説明を適宜省略する。この第1実施形態では、ゲート電極2を含む走査ラインは、ガラス基板1上に形成されたNd等の希土類元素の1種または2種以上を含有するAl合金からなる第1配線層2aと、この第1配線層2a上に形成されたTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層2bとによって構成されている。そして、両配線層2a、2bからなるゲート電極2を含む走査ラインの表面には陽極酸化膜3が形成されている。

【0010】このようなゲート電極2を含む走査ラインでは、Nd等の希土類元素を含有するAl合金からなる第1配線層2aにピンホールが発生しても、その上に形成されたTi等の高融点金属を含有するAl合金からなる第2配線層2bによって断線を防止することができ、したがってピンホールに起因する断線が生じないようにすることができ、しかも抵抗率を10μΩcm程度以下とすることができる。この結果、低抵抗化を図ることができるとともに、歩留及び信頼性の向上を図ることができる。

【0011】次に、両配線層2a、2bの具体的材料及び具体的数値の一例について説明する。第1配線層2aはNdが0.5〜1.5at%含有されたAl−Nd合金であり、例えば、Al−1at%Nd合金によって形成すると、その抵抗率ρ1は約7.5μΩcmとなる。第2配線層2bはTiが2.5〜5at%含有されたAl−Ti合金であり、例えば、Al−2.9at%Ti合金によって形成すると、その抵抗率ρ2は約20μΩcmとなる。そして、第1配線層2aと第2配線層2bとの膜厚の比を6:4とする。この場合、計算の都合上、両配線層2a、2bの合計膜厚を1000Åとすると、第1配線層2aの膜厚t1は600Åとなり、第2配線層2bの膜厚t2は400Åとなる。

【0012】ところで、抵抗率ρとシート抵抗Rs(Ω/□)と膜厚t(cm)との間には、ρ=Rs×tの関係がある。したがって、第1配線層2aのシート抵抗Rs1は、ρ1/t1=7.5μΩcm/600Å=1.25Ω/□となる。第2配線層2bのシート抵抗Rs2は、ρ2/t2=20μΩcm/400Å=5Ω/□となる。そして、両配線層2a、2bの合成シート抵抗Rsは、両配線層2a、2bが抵抗として並列になっているので、1/{(1/Rs1)+(1/Rs2)}=1Ω/□となる。この結果、両配線層2a、2bの合成抵抗率ρは、Rs×t=1Ω/□×1000Å=10μΩcmとなり、低抵抗化を図ることができる。

【0013】次に、図2はこの発明の第2実施形態における液晶表示装置の要部の断面図を示したものである。この図において、図3と同一名称部分には同一の符号を付し、その説明を適宜省略する。この第2実施形態では、ゲート電極2を含む走査ラインは、ガラス基板1上に形成された主としてAlからなる第1配線層2cと、この第1配線層2c上に形成されたNd等の希土類元素の1種または2種以上を含有するAl合金からなる第2配線層2dと、この第2配線層2d上に形成されたTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第3配線層2eとによって構成されている。この場合も、第1〜第3配線層2c〜2eからなるゲート電極2を含む走査ラインの表面には陽極酸化膜3が形成されている。

【0014】そして、このようなゲート電極2を含む走査ラインの場合も、Al−Nd合金からなる第2配線層2dにピンホールが発生しても、その上に形成されたAl−Ti合金からなる第3配線層2eによって断線を防止することができ、したがってピンホールに起因する断線が生じないようにすることができ、しかも抵抗率を10μΩcm程度以下とすることができる。この結果、低抵抗化を図ることができるとともに、歩留及び信頼性の向上を図ることができる。

【0015】次に、第1〜第3配線層2c〜2eの具体的材料及び具体的数値の一例について説明する。第1配線層2cを主としてAlからなる材料によって形成すると、その抵抗率ρ3は約3μΩcmとなる。第2配線層2dをAl−1at%Nd合金によって形成すると、その抵抗率ρ4は約7.5μΩcmとなる。第3配線層2eをAl−2.9at%Ti合金によって形成すると、その抵抗率ρ5は約20μΩcmとなる。そして、第1〜第3配線層c〜2eの膜厚の比を5:2:3とする。この場合も、計算の都合上、第1〜第3配線層2c〜2eの合計膜厚を1000Åとすると、第1配線層2cの膜厚t3は500Åとなり、第2配線層2dの膜厚t4は200Åとなり、第3配線層2eの膜厚t5は300Åとなる。

【0016】そして、第1配線層2cのシート抵抗Rs3は、ρ3/t3=3μΩcm/500Å=0.6Ω/□となる。第2配線層2dのシート抵抗Rs4は、ρ4/t4=7.5μΩcm/200Å=3.75Ω/□となる。第3配線層2eのシート抵抗Rs5は、ρ5/t5=20μΩcm/300Å=6.67Ω/□となる。そして、第1〜第3配線層2c〜2eの合成シート抵抗Rsは、第1〜第3配線層2c〜2eが抵抗として並列になっているので、1/{(1/Rs3)+(1/Rs4)+(1/Rs5)}=0.48Ω/□となる。この結果、第1〜第3配線層2c〜2eの合成抵抗率ρは、Rs×t=0.48Ω/□×1000Å=4.8μΩcmとなり、より一層の低抵抗化を図ることができる。

【0017】なお、上記実施形態では、表示装置に適用した場合で示したが、本発明の配線構造は、表示装置以外の配線として幅広く適用できるものである。また、薄膜トランジスタのゲート電極を含む走査ラインに限らず、ソース電極、ドレイン電極またはこれらの電極を含む信号ラインの配線としても使用することができる。

【0018】

【発明の効果】以上説明したように、この発明によれば、Nd等の希土類元素を含有するAl合金からなる配線層にピンホールが発生しても、一体的に形成されたTi等の高融点金属を含有するAl合金からなる配線層によって断線を防止することができるので、配線にピンホールに起因する断線が生じないようにすることができ、しかも配線の抵抗率を10μΩcm程度以下とすることができ、ひいては低抵抗化を図ることができるとともに、歩留及び信頼性の向上を図ることができる。

【図面の簡単な説明】

【図1】この発明の第1実施形態における液晶表示装置の要部の断面図。

【図2】この発明の第2実施形態における液晶表示装置の要部の断面図。

【図3】従来の液晶表示装置の一部の断面図。

【符号の説明】

2 ゲート電極

2a 第1配線層

2b 第2配線層

2c 第1配線層

2d 第2配線層

2e 第3配線層

【0001】

【発明の属する技術分野】この発明は配線構造及びそれを用いた表示装置に関する。

【0002】

【従来の技術】例えば、アクティブマトリックス型の液晶表示装置には、走査ライン及び信号ライン等からなる配線を備えているとともに、走査ラインと信号ラインの各交点近傍に画素電極及び該画素電極に接続されたスイッチング素子としての薄膜トランジスタを備えたものがある。

【0003】図3は従来のこのような液晶表示装置の一部の断面図を示したものである。この液晶表示装置はガラス基板1を備えている。ガラス基板1の上面の所定の箇所にはゲート電極2を含む走査ライン(図示せず)が形成され、その表面には陽極酸化膜3が形成され、その上面全体にはゲート絶縁膜4が形成されている。ゲート絶縁膜4の上面の所定の箇所でゲート電極2に対応する部分にはアモルファスシリコンからなる半導体薄膜5が形成されている。半導体薄膜5の上面の中央部にはブロッキング層6が形成されている。半導体薄膜5及びブロッキング層6の上面の両側にはn+シリコンからなるオーミックコンタクト層7、8が形成されている。オーミックコンタクト層7、8の各上面にはドレイン電極9及びソース電極10が形成されている。また、これら電極9、10の形成と同時に信号ライン(図示せず)が形成されている。ゲート絶縁膜4の上面の所定の箇所にはITOからなる画素電極11がソース電極10に接続されて形成されている。画素電極11の所定の部分を除く上面全体にはパッシベーション膜12が形成されている。

【0004】ところで、ゲート電極2を含む走査ラインからなる配線の材料としては、一般に、Ti、Ta、Mo、Cr等の高融点金属を含有するAl合金が用いられている。この場合、AlにTi等の高融点金属を含有させるのは、Alの耐熱性が十分でなく、後工程の加熱工程においてヒロックが発生するのを抑制するためである。このように、耐ヒロック特性を考慮するのは、例えば、ゲート電極2を含む走査ライン上に形成されるゲート絶縁膜4の絶縁耐圧が低下しないようにするためである。

【0005】しかるに、このような耐ヒロック特性を考慮した場合、Ti等の含有量を3at%程度以下とすることができず、ひいては配線(ゲート電極2を含む走査ライン)の抵抗率を20μΩcm程度以下とすることができない。一方、最近では、液晶表示装置の高精細化や高開口率化等に伴って、配線のより一層の低抵抗化が要求されている。このため、最近では、耐ヒロック特性が良く、しかも抵抗率を10μΩcm程度以下とすることのできるAl−Nd合金が注目されている。

【0006】

【発明が解決しようとする課題】しかしながら、Al−Nd合金からなる配線の場合には、ピンホール(ボイド)の発生が問題となっている。すなわち、走査ラインにピンホールが発生した場合には、走査ラインの断線により線欠陥となり、ゲート電極2にピンホールが発生した場合には、薄膜トランジスタの欠陥により点欠陥となり、歩留及び信頼性が低下することになる。この発明の課題は、配線にピンホールに起因する断線が生じないようにすることができ、しかも配線の抵抗率を10μΩcm程度以下とすることができるようにすることである。

【0007】

【課題を解決するための手段】請求項1記載の発明は、希土類元素の1種または2種以上を含有するAl合金からなる第1配線層とTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層とを含む複数の配線層で構成したものである。請求項5記載の発明は、主としてAlからなる第1配線層と、希土類元素の1種または2種以上を含有するAl合金からなる第2配線層と、Ti、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第3配線層とによって配線を構成したものである。

【0008】この発明によれば、Nd等の希土類元素を含有するAl合金からなる配線層にピンホールが発生しても、一体的に形成されたTi等の高融点金属を含有するAl合金からなる配線層によって断線を防止することができ、したがって配線にピンホールに起因する断線が生じないようにすることができ、しかも配線の抵抗率を10μΩcm程度以下とすることができる。

【0009】

【発明の実施の形態】図1はこの発明の第1実施形態における液晶表示装置の要部の断面図を示したものである。この図において、図3と同一名称部分には同一の符号を付し、その説明を適宜省略する。この第1実施形態では、ゲート電極2を含む走査ラインは、ガラス基板1上に形成されたNd等の希土類元素の1種または2種以上を含有するAl合金からなる第1配線層2aと、この第1配線層2a上に形成されたTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層2bとによって構成されている。そして、両配線層2a、2bからなるゲート電極2を含む走査ラインの表面には陽極酸化膜3が形成されている。

【0010】このようなゲート電極2を含む走査ラインでは、Nd等の希土類元素を含有するAl合金からなる第1配線層2aにピンホールが発生しても、その上に形成されたTi等の高融点金属を含有するAl合金からなる第2配線層2bによって断線を防止することができ、したがってピンホールに起因する断線が生じないようにすることができ、しかも抵抗率を10μΩcm程度以下とすることができる。この結果、低抵抗化を図ることができるとともに、歩留及び信頼性の向上を図ることができる。

【0011】次に、両配線層2a、2bの具体的材料及び具体的数値の一例について説明する。第1配線層2aはNdが0.5〜1.5at%含有されたAl−Nd合金であり、例えば、Al−1at%Nd合金によって形成すると、その抵抗率ρ1は約7.5μΩcmとなる。第2配線層2bはTiが2.5〜5at%含有されたAl−Ti合金であり、例えば、Al−2.9at%Ti合金によって形成すると、その抵抗率ρ2は約20μΩcmとなる。そして、第1配線層2aと第2配線層2bとの膜厚の比を6:4とする。この場合、計算の都合上、両配線層2a、2bの合計膜厚を1000Åとすると、第1配線層2aの膜厚t1は600Åとなり、第2配線層2bの膜厚t2は400Åとなる。

【0012】ところで、抵抗率ρとシート抵抗Rs(Ω/□)と膜厚t(cm)との間には、ρ=Rs×tの関係がある。したがって、第1配線層2aのシート抵抗Rs1は、ρ1/t1=7.5μΩcm/600Å=1.25Ω/□となる。第2配線層2bのシート抵抗Rs2は、ρ2/t2=20μΩcm/400Å=5Ω/□となる。そして、両配線層2a、2bの合成シート抵抗Rsは、両配線層2a、2bが抵抗として並列になっているので、1/{(1/Rs1)+(1/Rs2)}=1Ω/□となる。この結果、両配線層2a、2bの合成抵抗率ρは、Rs×t=1Ω/□×1000Å=10μΩcmとなり、低抵抗化を図ることができる。

【0013】次に、図2はこの発明の第2実施形態における液晶表示装置の要部の断面図を示したものである。この図において、図3と同一名称部分には同一の符号を付し、その説明を適宜省略する。この第2実施形態では、ゲート電極2を含む走査ラインは、ガラス基板1上に形成された主としてAlからなる第1配線層2cと、この第1配線層2c上に形成されたNd等の希土類元素の1種または2種以上を含有するAl合金からなる第2配線層2dと、この第2配線層2d上に形成されたTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第3配線層2eとによって構成されている。この場合も、第1〜第3配線層2c〜2eからなるゲート電極2を含む走査ラインの表面には陽極酸化膜3が形成されている。

【0014】そして、このようなゲート電極2を含む走査ラインの場合も、Al−Nd合金からなる第2配線層2dにピンホールが発生しても、その上に形成されたAl−Ti合金からなる第3配線層2eによって断線を防止することができ、したがってピンホールに起因する断線が生じないようにすることができ、しかも抵抗率を10μΩcm程度以下とすることができる。この結果、低抵抗化を図ることができるとともに、歩留及び信頼性の向上を図ることができる。

【0015】次に、第1〜第3配線層2c〜2eの具体的材料及び具体的数値の一例について説明する。第1配線層2cを主としてAlからなる材料によって形成すると、その抵抗率ρ3は約3μΩcmとなる。第2配線層2dをAl−1at%Nd合金によって形成すると、その抵抗率ρ4は約7.5μΩcmとなる。第3配線層2eをAl−2.9at%Ti合金によって形成すると、その抵抗率ρ5は約20μΩcmとなる。そして、第1〜第3配線層c〜2eの膜厚の比を5:2:3とする。この場合も、計算の都合上、第1〜第3配線層2c〜2eの合計膜厚を1000Åとすると、第1配線層2cの膜厚t3は500Åとなり、第2配線層2dの膜厚t4は200Åとなり、第3配線層2eの膜厚t5は300Åとなる。

【0016】そして、第1配線層2cのシート抵抗Rs3は、ρ3/t3=3μΩcm/500Å=0.6Ω/□となる。第2配線層2dのシート抵抗Rs4は、ρ4/t4=7.5μΩcm/200Å=3.75Ω/□となる。第3配線層2eのシート抵抗Rs5は、ρ5/t5=20μΩcm/300Å=6.67Ω/□となる。そして、第1〜第3配線層2c〜2eの合成シート抵抗Rsは、第1〜第3配線層2c〜2eが抵抗として並列になっているので、1/{(1/Rs3)+(1/Rs4)+(1/Rs5)}=0.48Ω/□となる。この結果、第1〜第3配線層2c〜2eの合成抵抗率ρは、Rs×t=0.48Ω/□×1000Å=4.8μΩcmとなり、より一層の低抵抗化を図ることができる。

【0017】なお、上記実施形態では、表示装置に適用した場合で示したが、本発明の配線構造は、表示装置以外の配線として幅広く適用できるものである。また、薄膜トランジスタのゲート電極を含む走査ラインに限らず、ソース電極、ドレイン電極またはこれらの電極を含む信号ラインの配線としても使用することができる。

【0018】

【発明の効果】以上説明したように、この発明によれば、Nd等の希土類元素を含有するAl合金からなる配線層にピンホールが発生しても、一体的に形成されたTi等の高融点金属を含有するAl合金からなる配線層によって断線を防止することができるので、配線にピンホールに起因する断線が生じないようにすることができ、しかも配線の抵抗率を10μΩcm程度以下とすることができ、ひいては低抵抗化を図ることができるとともに、歩留及び信頼性の向上を図ることができる。

【図面の簡単な説明】

【図1】この発明の第1実施形態における液晶表示装置の要部の断面図。

【図2】この発明の第2実施形態における液晶表示装置の要部の断面図。

【図3】従来の液晶表示装置の一部の断面図。

【符号の説明】

2 ゲート電極

2a 第1配線層

2b 第2配線層

2c 第1配線層

2d 第2配線層

2e 第3配線層

【特許請求の範囲】

【請求項1】 希土類元素の1種または2種以上を含有するAl合金からなる第1配線層とTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層とを含む複数の配線層で構成したことを特徴とする配線構造。

【請求項2】 Al−Nd合金からなる第1配線層とAl−Ti合金からなる第2配線層とを含む複数の配線層で構成したことを特徴とする配線構造。

【請求項3】 請求項1または2記載の発明において、前記第1配線層が下層で、前記第2配線層が上層であることを特徴とする配線構造。

【請求項4】 請求項1〜3のいずれかに記載の発明において、前記第1配線層及び前記第2配線層の少なくとも一方は表面に酸化膜を有することを特徴とする配線構造。

【請求項5】 主としてAlからなる第1配線層と、希土類元素の1種または2種以上を含有するAl合金からなる第2配線層と、Ti、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第3配線層とによって配線を構成したことを特徴とする配線構造。

【請求項6】 主としてAlからなる第1配線層と、Al−Nd合金からなる第2配線層と、Al−Ti合金からなる第3配線層とによって配線を構成したことを特徴とする配線構造。

【請求項7】 請求項5または6記載の発明において、前記第1〜第3配線層はこの順番で順次積層されていることを特徴とする配線構造。

【請求項8】 請求項7記載の発明において、前記第1〜第3配線層の少なくとも一層は表面に酸化膜を有することを特徴とする配線構造。

【請求項9】 透明絶縁基板と、希土類元素の1種または2種以上を含有するAl合金からなる第1配線層とTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層とを含む複数の配線層で構成した配線と、を具備することを特徴とする表示装置。

【請求項10】 薄膜トランジスタをスイッチング素子として画素電極に接続したアクティブ型の表示装置において、前記薄膜トランジスタのゲート、ソース、ドレイン電極の少なくとも1つを、希土類元素の1種または2種以上を含有するAl合金からなる第1配線層とTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層とを含む複数の配線層で構成したことを特徴とする表示装置。

【請求項1】 希土類元素の1種または2種以上を含有するAl合金からなる第1配線層とTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層とを含む複数の配線層で構成したことを特徴とする配線構造。

【請求項2】 Al−Nd合金からなる第1配線層とAl−Ti合金からなる第2配線層とを含む複数の配線層で構成したことを特徴とする配線構造。

【請求項3】 請求項1または2記載の発明において、前記第1配線層が下層で、前記第2配線層が上層であることを特徴とする配線構造。

【請求項4】 請求項1〜3のいずれかに記載の発明において、前記第1配線層及び前記第2配線層の少なくとも一方は表面に酸化膜を有することを特徴とする配線構造。

【請求項5】 主としてAlからなる第1配線層と、希土類元素の1種または2種以上を含有するAl合金からなる第2配線層と、Ti、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第3配線層とによって配線を構成したことを特徴とする配線構造。

【請求項6】 主としてAlからなる第1配線層と、Al−Nd合金からなる第2配線層と、Al−Ti合金からなる第3配線層とによって配線を構成したことを特徴とする配線構造。

【請求項7】 請求項5または6記載の発明において、前記第1〜第3配線層はこの順番で順次積層されていることを特徴とする配線構造。

【請求項8】 請求項7記載の発明において、前記第1〜第3配線層の少なくとも一層は表面に酸化膜を有することを特徴とする配線構造。

【請求項9】 透明絶縁基板と、希土類元素の1種または2種以上を含有するAl合金からなる第1配線層とTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層とを含む複数の配線層で構成した配線と、を具備することを特徴とする表示装置。

【請求項10】 薄膜トランジスタをスイッチング素子として画素電極に接続したアクティブ型の表示装置において、前記薄膜トランジスタのゲート、ソース、ドレイン電極の少なくとも1つを、希土類元素の1種または2種以上を含有するAl合金からなる第1配線層とTi、Ta、Mo、Cr等の高融点金属の1種または2種以上を含有するAl合金からなる第2配線層とを含む複数の配線層で構成したことを特徴とする表示装置。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開平10−199827

【公開日】平成10年(1998)7月31日

【国際特許分類】

【出願番号】特願平8−358424

【出願日】平成8年(1996)12月28日

【出願人】(000001443)カシオ計算機株式会社 (8,748)

【公開日】平成10年(1998)7月31日

【国際特許分類】

【出願日】平成8年(1996)12月28日

【出願人】(000001443)カシオ計算機株式会社 (8,748)

[ Back to top ]