配線構造

【課題】電源・信号間の干渉および結合の抑制と、電源ノイズの抑制と、信号間の干渉・クロストークの抑制と、インピーダンス不連続による信号反射の抑制とを、全てバランスよく満たす低コストな高速デバイスを提供する。

【解決手段】信号用ボンディングワイヤ31d、31eと、グランド用ボンディングワイヤ31b、31gと、電源用ボンディングワイヤ32a、32c、32f]とを、次のように配置する。すなわち、グランド用ボンディングワイヤまたは電源用ボンディングワイヤの一方が、信号用ボンディングワイヤと同じ第1の包絡面に含まれ、他方は別の第2の包絡面に含まれる。ここで、第2の包絡面に含まれるボンディングワイヤおよび信号用ボンディングワイヤの間の電磁結合が、第1の包絡面に含まれる2本のボンディングワイヤの間の電磁結合よりも小さくなるようにする配線構造。

【解決手段】信号用ボンディングワイヤ31d、31eと、グランド用ボンディングワイヤ31b、31gと、電源用ボンディングワイヤ32a、32c、32f]とを、次のように配置する。すなわち、グランド用ボンディングワイヤまたは電源用ボンディングワイヤの一方が、信号用ボンディングワイヤと同じ第1の包絡面に含まれ、他方は別の第2の包絡面に含まれる。ここで、第2の包絡面に含まれるボンディングワイヤおよび信号用ボンディングワイヤの間の電磁結合が、第1の包絡面に含まれる2本のボンディングワイヤの間の電磁結合よりも小さくなるようにする配線構造。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線構造と、配線構造の設計方法とに係り、特に、半導体装置内部のボンディングワイヤにおける配線構造と、配線構造の設計方法とに係る。

【背景技術】

【0002】

近年、半導体デバイスの高速化に伴い、電源ノイズや、信号反射や、信号間干渉(クロストーク)や、さらにこれらに起因するEMI(ElectroMagnetic Interference:電磁放射干渉)などの問題が顕在化している。従来は、電源系の問題と、信号系の問題とは、別個に議論され、解析され、設計されていた。例として、電源ノイズとEMI、信号反射やskewによる信号品質の低下とEMI、信号間干渉による信号波形劣化とEMI、などの組み合わせが挙げられる。

【0003】

しかし、ここ数年になって、信号密度および信号速度の増大に伴って、信号伝送媒体内部における信号系と電源系との直接干渉が問題視されつつある。このような問題は、非特許文献1(Myoung Joon Choi, Vishram S. Pandit, and Woong Hwan Ryu, “Controllable Parameters Identification for High Speed Channel through Signal−Power Integrity Combined Analysis”, Proceedings of 58th Electronic Components and Technology Conference, 658 (2008))や、非特許文献2(Ryuichi Oikawa, “A Low−cost Wire−bonding Package Design with Package Built−in Three−dimensional Distributed Matching Circuit for over 5Gbps SerDes Applications”, Proceedings of 59th Electronic Components and Technology Conference, 1098 (2009))などでも論じられている。

【0004】

ここで、新たな問題として挙がって来たのは、電源ラインから信号ラインへのcommon modeノイズ伝播や、伝播信号による電源ラインへの直接ノイズ干渉などである。これらは、EMIの原因となったり、信号から電源へ、電源からさらに信号へ、と作用する正帰還系を構成することによってGbpsクラスの高速デバイスの動作不安定の原因となったりする。

【0005】

一般的に、ノイズを含め、信号間の干渉を防ぐには、GND(GrouND:グランド)シールドを設けると良いとされている。しかし、ボンディングワイヤを有する半導体装置において、ボンディングワイヤの周りにシールド構造を設けると、複数の欠点が生じる。これらの欠点としては、例えば、製造が難しくなる、半導体装置が大型化する、製造コストが上昇する、などが挙げられる。そこで、特別な製造工程を経ずに所望の電気的性能を達成できることが望ましい。

【0006】

図1は、2つの異なるインターポーザ上に実装された2つの同じLSIの出力信号を比較したグラフ群である。図1(a)は、インターポーザがボンディングワイヤを有する場合を示すグラフである。図1(b)は、インターポーザがフリップチップ実装型である場合を示すグラフである。ここで、フリップチップ実装型のインターポーザでは、電源ラインと信号ラインは別のレイヤに配線されており、GNDプレーンによってよく遮断されている。

【0007】

これら2つのLSIは、6.4Gbpsの信号速度で動作する。これらの出力信号は、観測されたcommon mode信号波形をFourier変換して得られたものである。これらのグラフにおいて、横軸は周波数を示し、縦軸はノイズの強度を示す。実線は電源ノイズがなく信号だけがインターポーザに入力された場合を、破線は電源ノイズがある状態でインターポーザに信号が入力された場合を示している。

【0008】

図1から、以下のことが読み取れる。すなわち、フリップチップ実装型のインターポーザの場合は、信号−電源間がよく遮断されているので、電源ノイズの有無に係らず、common modeノイズスペクトルがよく一致している。その一方で、ボンディングワイヤを有するインターポーザの場合は、電源ノイズの有無によるcommon modeノイズの差が、特にMHz帯において、極めて大きい。なお、MHz帯において差が大きいのは、この例では電源ノイズの主たる周波数成分がMHz帯にあるからである。ここで、ボンディングワイヤを有するインターポーザよりも、フリップ実装型のインターポーザの方が高価であることは言うまでもない。

【0009】

このように、ボンディングワイヤを有する半導体装置では、インターポーザの内部における電源系から信号系への直接的なノイズ遷移が大きく、これを低減する手段が必要とされている。すなわち、次世代の低コスト高速デバイスでは、電源―信号間の干渉および結合を低減するとともに、電源ノイズ自体をも低減する手段が必要である。加えて、旧来から指摘されている信号間干渉(クロストーク)や、インピーダンスの不連続による信号反射が抑制されていることも、Gbpsクラスの高速デバイスの安定動作要件である。インターポーザ上のレイアウトリソースは限られているので、これら全ての要件をバランスよく満たす手段が理想的である。

【0010】

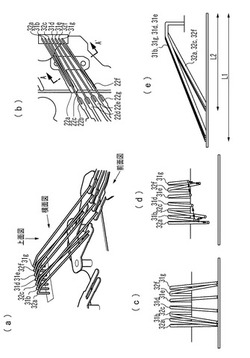

図2は、特許文献1(米国特許6538336号明細書)に記載の、LSIチップおよびインターポーザ基板を接続するボンディングワイヤの配置の例を示す図群である。図2(a)は、ボンディングワイヤの配置を全体的に示す俯瞰図である。図2(b)は、ボンディングワイヤの配置を示す側面図である。図2(c)は、図2(b)のA−A’によるボンディングワイヤの断面図である。

【0011】

図2(a)、図2(b)から読み取れるように、この例では、インターポーザ基板上にLSIチップがマウントされている。LSIチップの表面と、インターポーザ基板の表面とのそれぞれには、2列に縦横に配置されたボンディングパッドがある。LSIチップ側のボンディングパッドと、インターポーザ基板側のボンディングパッドとには、ボンディングワイヤの両端がそれぞれ接続されている。

【0012】

図2(c)に示す「S」、「G」および「P」は、ボンディングワイヤが、それぞれ信号(Signal)用、グランド(Ground)用および電源(Power)用であることを意味する。図2(c)から読み取れるように、信号用ボンディングワイヤの縦横方向の隣には、グランド用または電源用のボンディングワイヤが配置されている。ここで、グランド用ボンディングワイヤおよび電源用ボンディングワイヤは、固定電圧を印加されても良いし、信号用パッドが伝播する高速信号より周波数の非常に低い信号を伝播しても良い。以降、グランド用または電源用、もしくは極低周波信号用のボンディングワイヤを、固定電圧用ボンディングワイヤと記す。

【0013】

図2(b)から読み取れるように、LSIチップ上の2列のパッドのうち、実装基板に近い側に配置された一方の列に一端が接続されたボンディングワイヤは、他方の列に一端が接続されたボンディングワイヤの内側を通っている。言い換えれば、第1の列に接続されたボンディングワイヤは、第1の包絡面に含まれており、第2の列に接続されたボンディングワイヤは、第1の包絡面の内側に位置する第2の包絡面に含まれている。

【0014】

このように、図2の例では、高速信号用ボンディングワイヤと、固定電圧用ボンディングワイヤとを、2列の行列状に、交互に配置している。こうすることによって、高速信号用ボンディングワイヤ間を固定電圧用ボンディングワイヤがシールドする効果が得られる。この結果、高速信号間のクロストークが抑制される。

【0015】

ボンディングワイヤを上記のように配置するためには、基本的に、LSIチップ上またはインターポーザ基板上において、高速信号用ボンディングパッドと、電源用ボンディングパッドまたはグランド用ボンディングパッドとが、交互に並んでいる必要がある。

【0016】

図3は、特許文献1に記載の、LSIチップおよびインターポーザ基板を接続するボンディングワイヤの配置の別の例を示す平面図である。図3の例では、LSIチップ上のボンディングパッドが2列の千鳥状に配置されている。

【0017】

高速信号と、電源、グランドおよび極低周波信号とを同列に扱い、かつ、2列に配置されたボンディングパッドを用いることで、高速信号用ボンディングワイヤ間のクロストークを減殺することが出来る。この技術によれば、I/O(In/Out:入出力)回路のボンディングパッドが多くなりがちである。その一方で、高速信号用ボンディングパッドと、固定電圧用ボンディングパッドとの比率によっては、十分に良いクロストーク抑制効果が得られる。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】米国特許6538336号明細書

【非特許文献】

【0019】

【非特許文献1】Myoung Joon Choi, Vishram S. Pandit, and Woong Hwan Ryu, “Controllable Parameters Identification for High Speed Channel through Signal−Power Integrity Combined Analysis”, Proceedings of 58th Electronic Components and Technology Conference, 658 (2008)

【非特許文献2】Ryuichi Oikawa, “A Low−cost Wire−bonding Package Design with Package Built−in Three−dimensional Distributed Matching Circuit for over 5Gbps SerDes Applications”, Proceedings of 59th Electronic Components and Technology Conference, 1098 (2009)

【発明の概要】

【発明が解決しようとする課題】

【0020】

特許文献1での問題は、先に述べた次世代低コスト高速デバイスに対する要件を、全てバランス良く満たしていない点にある。上記要件とは、

(a)電源・信号間の干渉および結合の抑制(common modeノイズ伝播の抑制)

(b)電源ノイズの抑制

(c)信号間の干渉・クロストークの抑制

(d)インピーダンス不連続による信号反射の抑制

である。

【0021】

特許文献1で要件(c)が満たされていることは、その目的から見ても明らかである。要件(b)については、特許文献1には特に記載は無いものの、図3の配置を用いれば、電源用ボンディングワイヤおよびグランド用ボンディングワイヤが隣り合うので、相互インダクタンスにより実効インピーダンスが低下する。その結果、電源ノイズに対する抑制効果が働く。ただし、同じ特許文献1にある、図2の場合は、こうならない。

【0022】

次に、要件(d)について考える。特許文献1では、確かに、高速信号のリターンパスとして作用する電源またはグランドのボンディングワイヤが、信号ワイヤの近傍に配置されている。しかし、インターポーザ上のボンディングパッドが、高速信号用パッドと同じ列に並べられていない。そのため、もともと高いボンディングワイヤのインピーダンスを十分に低くできない。したがって、インピーダンスの連続性という点ではやや不利である。

【0023】

最後に、要件(a)について考える。これは、従来の考慮から抜けていた効果である。また、要件(a)は、特許文献1のように電源とGNDとを等価に扱っていては解決できない課題である。特許文献1においても解決方法は示されていない。

【課題を解決するための手段】

【0024】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0025】

本発明の配線構造は、半導体チップと、この半導体チップを実装する実装基板とを接続するボンディングワイヤ群を具備する。ボンディングワイヤ群は、第1の信号用ボンディングワイヤ(31d、31e)と、第1の電源用ボンディングワイヤ(31b、31g)と、第2の電源用ボンディングワイヤ(32a、32c、32f)とを具備する。ここで、第1の信号用ボンディングワイヤ(31d、31e)は、第1の包絡面に含まれて、信号を伝播する。第1の電源用ボンディングワイヤ(31b、31g)は、第1の包絡面に含まれて、第1の電源電圧を印加される。第2の電源用ボンディングワイヤ(32a、32c、32f)は、第2の包絡面に含まれて、第2の電源電圧を印加される。第1または第2の包絡面の一方は、第1または第2の包絡面の他方と、実装基板との間に配置されている。第2の電源用ボンディングワイヤ(32a、32c、32f)は、第1の信号用ボンディングワイヤ(31d、31e)との電磁結合が、第1の電源用ボンディングワイヤ(31b、31g)との電磁結合よりも小さい位置に配置されている。

【0026】

本発明の配線構造の設計方法は、半導体チップと、この半導体チップを実装する実装基板とを接続するボンディングワイヤ群を具備する配線構造の設計方法である。ここで、ボンディングワイヤ群は、第1の信号用ボンディングワイヤ(31d、31e)と、第1の電源用ボンディングワイヤ(31b、31g)と、第2の電源用ボンディングワイヤ(32a、32c、32f)とを具備する。第1の信号用ボンディングワイヤ(31d、31e)は、第1の包絡面に含まれて、信号を伝播する。第1の電源用ボンディングワイヤ(31b、31g)は、第1の包絡面に含まれて、第1の電源電圧を印加される。第2の電源用ボンディングワイヤ(32a、32c、32f)は、第1の包絡面および実装基板の間に配置された第2の包絡面に含まれて、第2の電源電圧を印加される。本発明の配線構造の設計方法は、(a)第1の信号用ボンディングワイヤならびに第1および第2の電源用ボンディングワイヤの長さに初期値を設定するステップと、(b)第1の信号用ボンディングワイヤならびに第1および第2の電源用ボンディングワイヤの長さに設定された値に基づいて、電磁界解析を用いた回路モデルを生成するステップと、(c)回路モデルに基づいて、回路シミュレーションを用いてcommon modeノイズを算出するステップと、(d)ステップ(c)で算出されたcommon modeノイズが所望の値以下ではないない場合に、第2の電源用ボンディングワイヤの長さを変更するステップと、(e)common modeノイズが所望の値以下になるまで、ステップ(b)〜(d)を繰り返すステップとを具備する。ここで、ステップ(a)は、(a−1)第2の電源用ボンディングワイヤの長さの初期値として、第1の電源用ボンディングワイヤの長さの半分の値を設定するステップを具備する。

【発明の効果】

【0027】

本発明の配線構造では、信号用ボンディングワイヤと、グランド用ボンディングワイヤと、電源用ボンディングワイヤとを、次のように配置する。すなわち、グランド用ボンディングワイヤまたは電源用ボンディングワイヤの一方が、信号用ボンディングワイヤと同じ第1の包絡面に含まれ、他方は別の第2の包絡面に含まれる。ここで、第2の包絡面に含まれるボンディングワイヤおよび信号用ボンディングワイヤの間の電磁結合が、第1の包絡面に含まれる2本のボンディングワイヤの間の電磁結合よりも小さくなるようにする。

【図面の簡単な説明】

【0028】

【図1】図1は、2つの異なるインターポーザ上に実装された2つの同じLSIの出力信号を比較したグラフ群である。図1(a)は、インターポーザがボンディングワイヤを有する場合を示すグラフである。図1(b)は、インターポーザがフリップチップ実装型である場合を示すグラフである。

【図2】図2は、特許文献1に記載の、LSIチップおよびインターポーザ基板を接続するボンディングワイヤの配置の例を示す図群である。図2(a)は、ボンディングワイヤの配置を全体的に示す俯瞰図である。図2(b)は、ボンディングワイヤの配置を示す側面図である。図2(c)は、図2(b)のA−A’によるボンディングワイヤの断面図である。

【図3】図3は、特許文献1に記載の、LSIチップおよびインターポーザ基板を接続するボンディングワイヤの配置の別の例を示す平面図である。

【図4】図4は、本発明の第1の実施形態による配線構造を示す図である。

【図5】図5は、本発明の第1の実施形態による配線構造の構成を示す図群である。図5(a)は、本発明の第1の実施形態による配線構造の構成を示す俯瞰図である。図5(b)は、図5(a)の配線構造を上から見た上面図である。図5(c)は、図5(a)の配線構造を前から見た前面図である。図5(d)は、図5(b)の配線構造のA−A’による断面図である。図5(e)は、図5(a)の配線構造を側面から見た側面図である。

【図6】図6は、ボンディングワイヤ群と、ボンディングワイヤ間の結合フィールドとの関係を示す断面図群である。図6(a)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が最小となる場合を示す断面図である。図6(b)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が最大となる場合を示す断面図である。図6(c)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が中間的となる場合を示す断面図である。図6(d)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が中間的となる別の場合を示す断面図である。

【図7A】図7Aは、本発明の第1の実施形態による配線構造の設計方法の各ステップを示すフローチャートである。

【図7B】図7Bは、本発明の第1の実施形態による配線構造の設計方法で用いる回路モデルの構成を示す回路図である。

【図8】図8は、本発明の第2の実施形態による配線構造の構成を示す図群である。図8(a)は、本発明の第1の実施形態による配線構造の構成を示す俯瞰図である。図8(b)は、図8(a)の配線構造を上から見た上面図である。図8(c)は、図8(a)の配線構造を前から見た前面図である。図8(d)は、図8(b)の配線構造のA−A’による断面図である。図8(e)は、図8(a)の配線構造を側面から見た側面図である。

【図9】図9は、本発明の第2の実施形態による配線構造と従来技術との比較結果を示すグラフ群である。図9(a)は、従来技術による配線構造における相互インダクタンス(Mutual inductance)、すなわち信号用ボンディングワイヤおよび電源用ボンディングワイヤの間の結合を示すグラフである。図9(b)は、従来技術による配線構造におけるcommon mode出力のスペクトルを示すグラフである。図9(c)は、本発明の第2の実施形態による配線構造における相互インダクタンスを示すグラフである。図9(d)は、本発明の第2の実施形態による配線構造におけるcommon mode出力のスペクトルを示すグラフである。

【図10】図10は、本発明の第3の実施形態による配線構造の構成を示す図群である。図10(a)は、本発明の第3の実施形態による配線構造の構成を示す俯瞰図である。図10(b)は、図10(a)の配線構造を上から見た上面図である。図10(c)は、図10(a)の配線構造を前から見た前面図である。図10(d)は、図10(b)の配線構造のA−A’による断面図である。図10(e)は、図10(a)の配線構造を側面から見た側面図である。

【図11】図11は、本発明の第4の実施形態による配線構造の構成を示す図群である。図11(a)は、本発明の第4の実施形態による配線構造の構成を示す俯瞰図である。図11(b)は、図11(a)の配線構造を上から見た上面図である。図11(c)は、図11(a)の配線構造を前から見た前面図である。図11(d)は、図11(b)の配線構造のA−A’による断面図である。図11(e)は、図11(a)の配線構造を側面から見た側面図である。

【図12】図12は、本発明の第5の実施形態による配線構造の構成を示す平面図である。

【発明を実施するための形態】

【0029】

添付図面を参照して、本発明による配線構造および配線構造の設計方法を実施するための形態を以下に説明する。

【0030】

(第1の実施形態)

図4は、本発明の第1の実施形態による配線構造を用いた半導体装置の全体的な構成を概略的に示す図群である。図4(a)は、本発明の第1の実施形態による配線構造を用いた半導体装置の全体的な構成を概略的に示す平面図である。図4(b)は、図4(a)のA−A’による断面図である。

【0031】

図4の半導体装置は、LSIチップ10と、実装基板20と、ボンディングワイヤ30とを具備している。LSIチップ10は、ボンディングパッド11を具備している。実装基板20は、ボンディングパッド21と、リード22とを具備している。

【0032】

LSIチップ10は、実装基板20上に実装されている。ボンディングワイヤ30の両端は、LSIチップ10のボンディングパッド11と、実装基板のボンディングパッド21とに、それぞれ接続されている。実装基板20のボンディングパッド21は、リード22に接続されている。リード22は、図示しない任意の回路に接続されている。

【0033】

一部のボンディングワイヤ31は、同一の包絡面に含まれている。以降、これらのボンディングワイヤをまとめて、第1群のボンディングワイヤ31と呼び、この包絡面を第1の包絡面と呼ぶ。また、別の一部のボンディングワイヤ32は、別の同一の包絡面に含まれている。以降、これらのボンディングワイヤをまとめて、第2群のボンディングワイヤ32と呼び、この包絡面を第2の包絡面と呼ぶ。なお、第2の包絡面は、第1の包絡面と、実装基板20の表面との間に位置している。言い換えれば、第2の包絡面は、第1の包絡面の内側に位置している。

【0034】

図5は、本発明の第1の実施形態による配線構造の構成を示す図群である。図5(a)は、本発明の第1の実施形態による配線構造の構成を示す俯瞰図である。図5(b)は、図5(a)の配線構造を上から見た上面図である。図5(c)は、図5(a)の配線構造を前から見た前面図である。図5(d)は、図5(b)の配線構造のA−A’による断面図である。図5(e)は、図5(a)の配線構造を側面から見た側面図である。

【0035】

本実施形態の配線構造は、LSIチップ10と、実装基板20と、複数のボンディングワイヤとを具備している。ただし、図5では、本発明の第1の実施形態の配線構造のうち、第1〜第7の、合計7本のボンディングワイヤ32a、31b、32c、31d、31e、32f、31gが示されており、他のボンディングワイヤは省略されている。

【0036】

LSIチップ10は、複数のボンディングパッド11を具備している。実装基板20は、複数のボンディングパッド21を具備している。なお、本実施形態では、実装基板20としてインターポーザ基板が用いられているが、これに限定するものでは決してない。

【0037】

第1〜第7のボンディングワイヤ32a、31b、32c、31d、31e、32f、31gは、一方の端部で、第1〜第7のボンディングパッド11a〜gを介してLSIチップ10にそれぞれ接続されている。また、第1〜第7のボンディングワイヤ32a、31b、32c、31d、31e、32f、31gは、他方の端部で、第1〜第7のボンディングパッド21a〜gを介して実装基板20にそれぞれ接続されている。

【0038】

図5(e)からは、第1〜第7のボンディングワイヤ32a、31b、32c、31d、31e、32f、31gを含む第1および第2の包絡面が読み取れる。すなわち、第2のボンディングワイヤ31b、第4のボンディングワイヤ31d、第5のボンディングワイヤ31e、第7のボンディングワイヤ31gは、第1の包絡面に含まれている。また、第1のボンディングワイヤ32a、第3のボンディングワイヤ32c、第6のボンディングワイヤ32fは、第2の包絡面に含まれている。

【0039】

言い換えれば、第2、第4、第5、第7のボンディングワイヤ31b、31d、31e、31gは、互いにほぼ平行に配置されている。このことを、第2、第4、第5、第7のボンディングワイヤ31b、31d、31e、31gのプロファイルは同じである、と表現しても良い。同様に、第1、第3、第6のボンディングワイヤ32a、32c、32fは、互いにほぼ平行に配置されている。したがって、第1、第3、第6のボンディングワイヤ32a、32c、32fのプロファイルは同じだが、第2、第4、第5、第7のボンディングワイヤのプロファイルとは異なる。

【0040】

上記2つのプロファイルが異なることは、図5(b)からも読み取れる。特に、第1、第3のボンディングワイヤ32a、32cは、第2のボンディングワイヤ31bの下に潜り込むように配置されている。同様に、第6のボンディングワイヤ32fは、第7のボンディングワイヤ31gの下に潜り込むように配置されている。

【0041】

さらに、プロファイルの違いにより、実装基板20上のボンディングパッド21a〜21gの配置にも違いが生じていることが、図5(b)からも読み取れる。すなわち、第1、第3、第6のボンディングワイヤ32a、32c、32fに接続される第1、第3、第6のボンディングパッド21a、21c、21fは、他のボンディングパッド21b、21d、21e、21gよりも、LSIチップ10に近い位置に配置されている。

【0042】

第2、第7のボンディングパッド22b、22gは、図示しないグランドに接地されている。第1、第3、第6のボンディングパッド22a、22c、22fは、図示しない電源電圧供給源に接続されている。

【0043】

本実施形態では、第4、第5のボンディングワイヤ31d、31eは対となって、LSIチップ10および実装基板20の間で差動信号を伝達する信号用ボンディングワイヤとして動作する。第2、第7のボンディングワイヤ31b、31gは、グランド用ボンディングワイヤとして動作する。第1、第3、第6のボンディングワイヤ32a、32c、32fは、電源用ボンディングワイヤとして動作する。

【0044】

なお、信号用ボンディングワイヤ31d、31eが差動信号を伝達することは、本発明の本質とは直接関係しない。したがって、本発明の配線構造では、必ずしも2本の信号用ボンディングワイヤが隣接していなくても良いし、信号用ボンディングワイヤに隣接するグランド用ボンディングワイヤの本数は1本であっても良い。

【0045】

本実施形態の配線構造では、信号用ボンディングワイヤ31d、31eと、グランド用ボンディングワイヤ31b、31gとが、LSIチップ10から実装基板20まで並走している。このことにより、元来高すぎるボンディングワイヤのインピーダンスが低下する。この結果、ボンディングワイヤのインピーダンスは、実装基板20の伝送路インピーダンスとも、本発明による半導体装置1が搭載されるシステムボードの伝送路インピーダンスとも、近い値になる。さらに、信号31d−31e間のスキューもほぼ0となる。

【0046】

また、図5の構成では、電源用ボンディングワイヤ32a、32c、32fおよび信号用ボンディングワイヤ31d、31eを介する、すなわち電源系回路から信号系回路への、ノイズ干渉が最小化される。この原理を、図6を用いて説明する。

【0047】

図6は、ボンディングワイヤ群と、ボンディングワイヤ間の結合フィールドとの関係を示す断面図群である。図6(a)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が最小となる場合を示す断面図である。図6(b)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が最大となる場合を示す断面図である。図6(c)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が中間的となる場合を示す断面図である。図6(d)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が中間的となる別の場合を示す断面図である。

【0048】

図6のボンディングワイヤ群は、第1〜第6のボンディングワイヤ33a〜33fを具備している。ここで、第1、第6のボンディングワイヤ33a、33fは、電源用ボンディングワイヤである。第2、第5のボンディングワイヤ33b、33eは、グランド用ボンディングワイヤである。第3、第4のボンディングワイヤ33c、33dは、信号用ボンディングワイヤである。

【0049】

図6において、隣接するボンディングワイヤの間に、第1〜第4の結合フィールド34a〜34dが発生している。第1の結合フィールド33aは、第1、第2のボンディングワイヤ33a、33bの間に発生している。第2の結合フィールド33aは、第2、第3のボンディングワイヤ33a、33bの間に発生している。第3の結合フィールド33aは、第4、第5のボンディングワイヤ33a、33bの間に発生している。第4の結合フィールド33aは、第5、第6のボンディングワイヤ33a、33bの間に発生している。なお、第3、第4のボンディングワイヤ33c、33dも互いに隣接しているので、当然両者の間に第5の結合フィールドが発生するはずである。しかし、信号−電源間の干渉を説明するのに信号間結合効果は必要ないので、その表示を省略してある。

【0050】

図6において、第2、第3の結合フィールド34b、34cが発生するのは、グランド用ボンディングワイヤ33b、33eが、隣接する信号用ボンディングワイヤ33c、33dにそれぞれに対応するリターンパスとして動作するからである。同様に、第1、第4の結合フィールド34a、34dが発生するのは、電源用ボンディングワイヤ33aとグランド用ボンディング33bが互いにリターンパスとして動作し、グランド用ボンディング33eと電源用ボンディングワイヤ33fもまた互いにリターンパスとして動作するからである。

【0051】

なお、これらの結合フィールド34a〜34dは、磁力線と捉えてもよいし、電気力線の包絡線と捉えてもよい。

【0052】

図6(b)では、グランド・電源間の結合フィールド34aと、信号・グランド間の結合フィールド34bとが、互いに平行になっている。この場合、2つの結合フィールド34a、34bは、同じ向きであるか、180度逆の正反対の向きであるかのどちらかである。すなわち、2つの結合フィールド34a、34bは、互いに最大限に強め合うか、互いに最大限に弱め合うかのどちらかである。さらに、信号・グランド間の結合フィールド34cと、グランド・電源間の結合フィールド34dとも、互いに平行になっている。したがって、電源系回路から信号系回路への、common modeノイズの伝播は、図6(b)の構成において最大になる。

【0053】

この観点から、電源系回路から信号系回路への、common modeノイズの伝播が最小になるのは、図6(a)のように、グランド・電源間の結合フィールド34aおよび34dと、信号・グランド間の結合フィールド34bおよび34cとが、それぞれ直角に交わる場合である。なぜなら、このとき互いのフィールドベクトルのスカラー積(内積)が0に近い値をとり、したがってエネルギー伝播が最小となるからである。

【0054】

また、図6(c)や図6(d)のように、グランド・電源間の結合フィールド34aおよび34dと、信号・グランド間の結合フィールド34bおよび34cとが、それぞれ交わる角度が90度より大きく、かつ、180度より小さい場合は、電源系回路から信号系回路への、common modeノイズの伝播が中間的な強さになる。

【0055】

したがって、図6(a)のように、信号用ボンディングワイヤおよびグランド用ボンディングワイヤが張る平面と、電源用ボンディングワイヤおよびグランド用ボンディングワイヤが張る平面とが、直交する構成を実現するのが理想的である。図5(d)から読み取れるように、本実施形態では、この原理に基づいて、ボンディングワイヤの位置関係を立体的に設定している。

【0056】

なお、厳密には2本のボンディングワイヤが張る面は、実際には曲面である場合が多い。この場合に、2つの面の直交を定義することは難しい。そこで、例えば、電源用ボンディングワイヤにおけるいずれかの点を規準にして、この基準点と、この基準点に最も近い信号用ボンディングワイヤ上の点とを結ぶ第1の直線を考える。同様に、この基準点と、この基準点に最も近いグランド用ボンディングワイヤ上の点とを結ぶ第2の直線を考える。これら第1、第2の直線が、この基準点において直交することが望ましい。さらには、このような基準点が、電源用ボンディングワイヤ上に複数あることが好ましい。

【0057】

本発明の原理は、ボンディングワイヤ間の第1および第2の結合フィールドの位置関係を、直交に近づけることにある。ここで、第1の結合フィールドは、信号を伝播する第1のボンディングワイヤと、この信号のリターンパスとして動作する第2のボンディングワイヤとの間に発生する結合フィールドである。また、第2の結合フィールドは、電源電圧を印加される第3のボンディングワイヤと、この電源電圧のリターンパスとして動作する第2のボンディングワイヤとの間に発生する結合フィールドである。

【0058】

なお、従来技術の説明で述べたとおり、電源用ボンディングワイヤは信号用ボンディングワイヤのリターンパスとして動作可能である。また、電源用ボンディングワイヤと、グランド用ボンディングワイヤとは、互いにリターンパスの関係となり得る。したがって、電源用ボンディングワイヤと、グランド用ボンディングワイヤとの関係をそっくり入れ替えても、本発明では同じ効果が得られる。少し詳しく説明すると次のとおりである。グラウンドを信号のリターンパスとするとき、信号に対するノイズ源はグラウンドと異なる電位変動をするもう一方の電圧源、つまり電源ワイヤである。反対に、電源を信号のリターンパスとするときは、電源と異なる電位変動をするもう一方の電圧源であるグラウンドのほうが信号に対するノイズ源となる。

【0059】

また、本発明では、主に2つの結合フィールドが交わる相対角度が問題となる。したがって、ボンディングワイヤの複数のプロファイルに対応する包絡面の上下関係、すなわちボンディングワイヤの断面の上下関係は、どちらであっても構わない。例えば、電源用ボンディングワイヤを、グランド用ボンディングワイヤより、その断面図構造における上方に配置しても、なんら支障はない。なお、この場合、実装基板上では、電源用ボンディングパッドは、LSIチップから見てより遠い側に、信号用またはグランド用ボンディングパッドは、LSIチップから見てより近い側に、それぞれ配置されることになる。

【0060】

次に、各ボンディングワイヤの長さの比率について説明する。図5(e)に示したとおり、信号用ボンディングワイヤと同じ包絡面に含まれて、すなわち信号用ボンディングワイヤと同じプロファイルを有する、グランド用ボンディングワイヤ31b、31gの長さをL1とする。同様に、信号用ボンディングワイヤとは異なる包絡面に含まれて、すなわち信号用ボンディングワイヤとは異なるプロファイルを有する、電源用ボンディングワイヤ32a、32c、32fの長さをL2とする。本発明では、これらのワイヤ長L1、L2には、最適な比率が存在する。

【0061】

この最適比率は、半導体装置側および実装基板側のボンディングパッドの高さの違いなどにも依存するが、様々な例における計算機実験によれば、概ね、

L1:L2=1:0.6

が最適値として得られた。

【0062】

この最適比率は、次のように理論的に説明できる。電源系回路から信号系回路へのノイズ伝播を小さくするには、電源ノイズ自体を小さくするか、信号系回路と電源系回路との間の干渉を小さくするか、いずれかを行えばよい。

【0063】

信号用ボンディングワイヤおよびグランド用ボンディングワイヤが通る第1の平面と、グランド用ボンディングワイヤおよび電源用ボンディングワイヤが通る第2の平面とが直交するとき、電源用ボンディングワイヤの長さを長くすれば、いいかえれば電源用ボンディングワイヤとグラウンド用ボンディングワイヤの並走距離を長くすれば、前記結合フィールドの直交関係が保たれる範囲が大きくなるので、信号系回路および電源系回路の間の干渉は小さくなる。しかし、電源用ボンディングワイヤが長くなれば長くなるだけ電源インピーダンスも増加するので、同時に電源ノイズが増加する。

【0064】

反対に、電源用ボンディングワイヤの長さを短くすれば、電源ノイズは小さくなるが、反対に、信号形回路および電源系回路の間の干渉は大きくなる。LSI上のデカップリング容量や、この半導体装置が実装されるボードの設計にもよるが、原理的に、極荒い近似では、これらのワイヤ長は1:2、つまり短いボンディングワイヤが長いボンディングワイヤの半分の長さにするのが、最適比率となる。上記の計算で得られた1:0.6は、本発明の第1の実施形態の構成の場合にそうなった、ということであり、十分に納得できる値である。

【0065】

近年よく行われる、いわゆるシリコン・パッケージ・ボードco−designの初期においては、パッケージ設計に使用するシリコンおよびボードの情報が未知であったり、精度が悪かったりするのは、よくあることである。そのような場合に、ボンディングワイヤプロファイルの設計を行うには、長さ比率50%を初期値として行うことで、パッケージの設計を効率よく行うことが出来る。また、長さ比率50%を初期値とすることは、未知要素の変動に対して、確率的に最大の安定度が得られる。

【0066】

ここで、図7Aおよび図7Bを用いて、本発明の第1の実施形態による配線構造の設計方法について説明する。

【0067】

図7Aは、本発明の第1の実施形態による配線構造の設計方法の各ステップを示すフローチャートである。図7Bは、本発明の第1の実施形態による配線構造の設計方法で用いる回路モデルの構成を示す回路図である。

【0068】

図7Bの回路モデルの構成要素について説明する。図7Bの回路モデルは、LSIチップモデル(LSI model)部100と、パッケージモデル(Package model)部200と、ボードモデル(Board model)部300と、直流電源モデル(DC Supply)部400と、終端モデル(Termination)部500と、計測点600とを具備している。

【0069】

LSIチップモデル部100は、入出力回路モデル(I/O Driver model)部110と、チップ上電流源モデル部と、チップ上電力供給回路モデル部とを具備している。

【0070】

パッケージモデル部200は、信号用ボンディングワイヤ、グランド用ボンディングワイヤ、電源用ボンディングワイヤ、などのモデルを含む。

【0071】

ボードモデル部300は、電源回路モデル部(Power supply model)310と、信号回路モデル部(Sgnal model)320とを具備している。

【0072】

図7Bの回路モデルの構成要素の接続関係について説明する。入出力回路モデル部110は、パッケージモデル部200に接続されている。チップ上電流源モデル部120は、チップ上電力供給回路モデル部130を介してパッケージモデル部200に接続されている。パッケージモデル部200は、電源回路モデル部310と、信号回路モデル部320とに接続されている。電源回路モデル310部は、直流電源モデル部400に接続されている。信号回路モデル部320は、終端モデル部500に接続されている。

【0073】

なお、計測点(Observation point)600は、信号回路モデル部320および終端モデル部500の接続点に設定されている。

【0074】

図7Aのフローチャートについて説明する。図7Aのフローチャートは、第1〜第9のステップS1〜S9を具備している。

【0075】

第1のステップS1において、本発明の配線構造の設計方法を開始する。第1のステップS1の次に、第2のステップS2へ進む。

【0076】

第2のステップS2において、電源用ボンディングワイヤの長さの初期値を、グランド用ボンディングワイヤの半分の長さに設定する。第2のステップS2の次は、第3のステップS3へ進む。

【0077】

第3のステップS3において、電磁界解析によって実装基板モデル200を生成する。第3のステップS3の次は、第6のステップS6へ進む。

【0078】

なお、第6のステップS6を行う前に、第4、第5のステップS4、S5において、LSIチップモデル100と、ボードの回路モデル300とを、それぞれあらかじめ用意しておくことが望ましい。第4、第5のステップS4、S5は、第6のステップS6を行う前であればいつ生成してもよいし、既存のデータを用いても構わない。

【0079】

第6のステップS6において、回路シミュレーションによってcommon modeノイズを、計測点600で計測する。この回路シミュレーションには、第3〜第5のステップS3〜S5で得られた各モデルを用いる。第6のステップS6の次は、第7のステップS7へ進む。

【0080】

第7のステップS7において、第6のステップS6で得られたcommon modeノイズが、所望の値以下であるかどうかを確認する。common modeノイズが所望の値以下であれば、第9のステップS9へ進み、その他の場合は第8のステップS8へ進む。

【0081】

第8のステップS8において、電源用ボンディングワイヤの長さを延長または短縮する。このとき、common modeノイズが減る方向に、電源用ボンディングワイヤの長さに変化を与えるべきなので、事前に調べておくことが望ましい。第8のステップS8の次は、第3のステップに戻る。

【0082】

第9のステップS9において、本発明の配線構造の設計方法を終了する。

【0083】

(第2の実施形態)

図8は、本発明の第2の実施形態による配線構造の構成を示す図群である。図8(a)は、本発明の第1の実施形態による配線構造の構成を示す俯瞰図である。図8(b)は、図8(a)の配線構造を上から見た上面図である。図8(c)は、図8(a)の配線構造を前から見た前面図である。図8(d)は、図8(b)の配線構造のA−A’による断面図である。図8(e)は、図8(a)の配線構造を側面から見た側面図である。

【0084】

本実施形態は、本発明の第1の実施形態から、実装基板上の電源用ボンディングパッド21a、21c、21fの位置を変更したものである。その結果、図8(a)、図8(b)、図8(c)、図8(d)から読み取れるように、電源用ボンディングワイヤ32a、32c、32fの方向も変更されている。ただし、図8(e)から読み取れるように、電源用ボンディングワイヤ32a、32c、32fのプロファイルは、本発明の第1の実施形態と同じである。言い換えれば、電源用ボンディングワイヤ32a、32c、32fを含む包絡面も、本発明の第1の実施形態同じである。その他の構成要素、接続関係、動作などは、本発明の第1の実施形態と全て同じであるので、さらなる説明を省略する。

【0085】

本発明の第1の実施形態では、信号用ボンディングワイヤおよびグランド用ボンディングワイヤの平面と、グランド用ボンディングワイヤおよび電源用ボンディングワイヤの平面とが交わる角度が、ほぼ90度であった。しかし、本実施形態では、この角度がほぼ60度〜ほぼ120度の範囲に含まれている。実験によれば、信号用ボンディングワイヤ、グランド用ボンディングワイヤ、電源用ボンディングワイヤのなかで最も短い最短のボンディングワイヤの、全長の半分に相当する領域において、この角度が60度よりおおきく、かつ、120度よりも小さければ、common modeノイズが半減し、十分な効果が得られることが確認された。ただし、いずれの場合も、電源用ボンディングワイヤまたはグランド用ボンディングワイヤのうち、信号用ボンディングワイヤに対するリターンパスとして用いる方のボンディングワイヤは、信号ボンディングワイヤと同じプロファイルにする必要がある。

【0086】

なお、60度〜120度の範囲の規準となる平面は、実際には曲面である場合が多い。したがって、本発明の第1の実施形態と同様に、1本のボンディングワイヤ上の基準点において、この範囲の角度を得られることが望ましい。さらには、信号用、グランド用、電源用の3本のボンディングワイヤのうち、最も短い最短のボンディングワイヤの、全長の半分に相当する領域における任意の点が、このような基準点の条件を満たすことが好ましい。

【0087】

ここで、本実施形態による配線構造の構成例を用いて、従来技術の場合との比較を行う。本発明との比較対象となる従来技術による配線構造の構成は、図8の電源用ボンディングワイヤ32a、32c、32fの長さを伸ばして、信号用およびグランド用のボンディングワイヤ31b、31d、31e、31gと同じプロファイルとしたものとする。

【0088】

図9は、本発明の第2の実施形態による配線構造と従来技術との比較結果を示すグラフ群である。図9(a)は、従来技術による配線構造における相互インダクタンス(Mutual inductance)、すなわち信号用ボンディングワイヤおよび電源用ボンディングワイヤの間の結合を示すグラフである。図9(b)は、従来技術による配線構造におけるcommon mode出力のスペクトルを示すグラフである。図9(c)は、本発明の第2の実施形態による配線構造における相互インダクタンスを示すグラフである。図9(d)は、本発明の第2の実施形態による配線構造におけるcommon mode出力のスペクトルを示すグラフである。

【0089】

図9から、本発明により、信号用ボンディングワイヤおよび電源用ボンディングワイヤの間の相互インダクタンスが、従来技術の半分以下、ほぼ1/3程度にまで減少することが読み取れる。また、その結果として電源系回路から信号系回路に伝播する電源ノイズに起因する低周波成分が減少していることが確認できる。

【0090】

(第3の実施形態)

図10は、本発明の第3の実施形態による配線構造の構成を示す図群である。図10(a)は、本発明の第3の実施形態による配線構造の構成を示す俯瞰図である。図10(b)は、図10(a)の配線構造を上から見た上面図である。図10(c)は、図10(a)の配線構造を前から見た前面図である。図10(d)は、図10(b)の配線構造のA−A’による断面図である。図10(e)は、図10(a)の配線構造を側面から見た側面図である。

【0091】

本実施形態は、本発明の第1の実施形態から、電源用ボンディングワイヤとして動作する第1のボンディングワイヤ32aを取り除き、さらに、LSIチップ10のボンディングパッド11の位置を変更したものである。その結果、図10(e)から読み取れるように、電源用ボンディングワイヤ32c、32fを含む第2の包絡面は、グランド用ボンディングワイヤ31b、31gおよび信号用ボンディングワイヤ31d、31eを含む第1の包絡面から完全に離れて、その内側に配置されている。言い換えると、電源用ボンディングワイヤ32c、32fのプロファイルは、グランド用ボンディングワイヤ31b、31gおよび信号用ボンディングワイヤ31d、31eのプロファイルにほぼ平行となっている。さらに、図10(b)から読み取れるように、グランド用ボンディングワイヤ31b、31gおよび信号用ボンディングワイヤ31d、31eがほぼ平行に配置されている。また、電源用ボンディングワイヤ32c、32fがグランド用ボンディングワイヤ31b、31gのほぼ真下を通っている。その他の構成要素、接続関係、動作などは、本発明の第1の実施形態と全て同じであるので、さらなる説明を省略する。

【0092】

このように、本実施形態によれば、LSIチップ10上のボンディングパッド11に必要な面積が増えるものの、本発明の理想とする配線の構造を、本発明の第1または第2の実施形態よりも、さらに忠実に適用できる。

【0093】

(第4の実施形態)

図11は、本発明の第4の実施形態による配線構造の構成を示す図群である。図11(a)は、本発明の第4の実施形態による配線構造の構成を示す俯瞰図である。図11(b)は、図11(a)の配線構造を上から見た上面図である。図11(c)は、図11(a)の配線構造を前から見た前面図である。図11(d)は、図11(b)の配線構造のA−A’による断面図である。図11(e)は、図11(a)の配線構造を側面から見た側面図である。

【0094】

LSIチップ10を実装する実装基板20として、本発明の第1〜第3の実施形態ではインターポーザ基板を用いたが、本実施形態ではリードフレームを用いる。本実施形態の実装基板20は、LSIチップを実装するダイパッド24と、ボンディングワイヤに接続されるリードピン23b、23d、23e、23gとを具備している。図11の例では、ダイパッド24が露出するタイプのQFP(Quad Flat Package)用のリードフレームが用いられている。

【0095】

本実施形態では、実装基板20上の、LSIチップ10に近い方のボンディングパッドとして、LSIチップ10を実装するダイパッド24を用いている。また、LSIチップ10から遠い方のボンディングパッドとして、リードピン23b、23d、23e、23gを用いている。そこで、本実施形態では、グランド用ボンディングワイヤおよび電源用ボンディングワイヤの役割を、本発明の第1〜第3の実施形態とは逆にしている。すなわち、実装基板20上の、LSIチップ10に近い方のボンディングパッドに接続される第1、第3、第6のボンディングワイヤ32a、32c、32fは、本実施形態ではグランド用ボンディングワイヤとして動作する。また、実装基板20上の、LSIチップ10から遠い方のボンディングパッドに接続される第2、第7のボンディングワイヤ31b、31gは、電源用ボンディングワイヤとして動作する。本発明において、グランド用ボンディングワイヤおよび電源用ボンディングワイヤの役割、すなわち印加される電圧を交換しても構わないことは、すでに説明したとおりである。その他の構成要素、接続関係、動作などは、本発明の第1の実施形態と全て同じであるので、さらなる説明を省略する。

【0096】

このように、本発明による配線構造は、実装基板として、本発明の第1〜第3の実施形態で用いたインターポーザ基板のみならず、リードフレームを用いた場合でも適用可能である。

【0097】

(第5の実施形態)

図12は、本発明の第5の実施形態による配線構造の構成を示す平面図である。本実施形態は、本発明の第4の実施形態に、第8〜第10のボンディングワイヤ31h〜31jと、3つのリードピン23h〜23jとを追加したものに等しい。

【0098】

3本のボンディングワイヤ31h、31i、31jは、この順番に、信号用ボンディングワイヤとして動作する第4のボンディングワイヤ31eと、グランド用ボンディングワイヤとして動作する第6のボンディングワイヤ31fとの間に配置されている。同様に、3つの3つのリードピン23h〜23jは、この順番に、第5、第6のリードピン23e、23fの間に配置されている。3本のボンディングワイヤ31h、31i、31jは、電源用ボンディングワイヤまたは信号用ボンディングワイヤとして動作する第2、第4、第5、第7のボンディングワイヤ31b、31d、31e、31gと同様に、第1のプロファイルを有しており、すなわち、第1の包絡面に含まれている。

【0099】

第8〜第10のボンディングワイヤ31h、31i、31jの一方の端部は、LSIチップ10のボンディングパッドに接続されている。第8〜第10のボンディングワイヤ31h、31i、31jの他方の端部は、3つのリードピン23h〜23jにそれぞれ接続されている。

【0100】

その他の構成要素、接続関係、動作などは、本発明の第1の実施形態と全て同じであるので、さらなる説明を省略する。

【0101】

第8のボンディングワイヤ31hは、電源用ボンディングワイヤとして動作する。また第9、第19の、ボンディングワイヤ31i、31jは、差動信号を伝播する1対の信号用ボンディングワイヤとして動作する。すなわち、本実施形態では、2対の信号用ボンディングワイヤを用いて、2つの差動信号を伝播する。一般的に、2対の信号用ボンディングワイヤの間には、信号間干渉、すなわちクロストークが発生する可能性がある。

【0102】

図12に示した構成例を用いて、本発明の配線構造が有する、信号間干渉すなわちクロストークを抑制する効果について説明する。電源用ボンディングワイヤとして動作する第2、第7、第8のボンディングワイヤ31b、31g、31hは、信号用ボンディングワイヤとして動作する第4、第5、第9、第10のボンディングワイヤ31d、31e、31i、13jと同じプロファイルで、かつ、ほぼ平行に配置されている。したがって、第1の差動信号を伝播する第1の信号用ボンディングワイヤ対31d、31eと、第2の差動信号を伝播する第2の信号用ボンディングワイヤ対31i、31jとは、間に挟まれた第8のボンディングワイヤ31hによって、その全長にわたってシールドされている。したがって、第1および第2の信号用ボンディングワイヤ対31d、31eおよび31i、31jの間では、クロストークが効率よく抑制される。

【0103】

これまで、本発明の配線構造における複数の実施形態について説明した。いずれの構成の場合も、信号用ボンディングワイヤおよび信号用のリターンパスとして動作するボンディングワイヤは、互いに強い相互インピーダンスを持つように配置される。また、電源用ボンディングワイヤおよび電源用リターンパスとして動作するボンディングワイヤの組み合わせにおいても、やはり互いに強い相互インピーダンスを持つように配置される。なぜなら信号―電源間の干渉が抑制されるためには、信号とそのリターンパス同士、および電源とそのリターンパス同士が強い結合をもつことが必須条件だからである。電源用ボンディングワイヤとそのリターンパス用ボンディングワイヤ、すなわちグラウンドワイヤが互いに強い結合をもつことから、本発明による配線構造を用いることは、クロストークのみならず、電源インピーダンスの低減にも効果的である。

【0104】

以上、本発明による配線構造が、課題として挙げた4つの要件、すなわち

(a)電源・信号間の干渉および結合の抑制(common modeノイズ伝播の抑制)

(b)電源ノイズの抑制

(c)信号間の干渉・クロストークの抑制

(d)インピーダンス不連続による信号反射の抑制

の全てを満たすことを説明した。

【0105】

なお、これら複数の実施形態におけるそれぞれの特徴は、技術的に矛盾しない範囲において、自由に組み合わせ可能であることは言うまでもない。

【符号の説明】

【0106】

1 半導体装置

10 LSIチップ

11、11a〜11g ボンディングパッド

20 実装基板

21、21a〜21g ボンディングパッド

22 リード

23b、23d、23e、23g〜23j リードピン

24 ダイパッド

30 ボンディングワイヤ

31 ボンディングワイヤ(第1群)

31b、31g (グランド用)ボンディングワイヤ

31d、31e (信号用)ボンディングワイヤ

32 ボンディングワイヤ(第2群)

32a、32c、32f (電源用)ボンディングワイヤ

33a〜33f ボンディングワイヤ

34a〜34d 結合フィールド

100 LSIチップモデル部

110 入出力回路モデル部

120 チップ上電流源モデル部

130 チップ上電力供給回路モデル部

200 パッケージモデル部

300 ボードモデル部

310 電源回路モデル部

320 信号回路モデル部

400 直流電源モデル部

500 終端モデル部

600 計測点

【技術分野】

【0001】

本発明は、配線構造と、配線構造の設計方法とに係り、特に、半導体装置内部のボンディングワイヤにおける配線構造と、配線構造の設計方法とに係る。

【背景技術】

【0002】

近年、半導体デバイスの高速化に伴い、電源ノイズや、信号反射や、信号間干渉(クロストーク)や、さらにこれらに起因するEMI(ElectroMagnetic Interference:電磁放射干渉)などの問題が顕在化している。従来は、電源系の問題と、信号系の問題とは、別個に議論され、解析され、設計されていた。例として、電源ノイズとEMI、信号反射やskewによる信号品質の低下とEMI、信号間干渉による信号波形劣化とEMI、などの組み合わせが挙げられる。

【0003】

しかし、ここ数年になって、信号密度および信号速度の増大に伴って、信号伝送媒体内部における信号系と電源系との直接干渉が問題視されつつある。このような問題は、非特許文献1(Myoung Joon Choi, Vishram S. Pandit, and Woong Hwan Ryu, “Controllable Parameters Identification for High Speed Channel through Signal−Power Integrity Combined Analysis”, Proceedings of 58th Electronic Components and Technology Conference, 658 (2008))や、非特許文献2(Ryuichi Oikawa, “A Low−cost Wire−bonding Package Design with Package Built−in Three−dimensional Distributed Matching Circuit for over 5Gbps SerDes Applications”, Proceedings of 59th Electronic Components and Technology Conference, 1098 (2009))などでも論じられている。

【0004】

ここで、新たな問題として挙がって来たのは、電源ラインから信号ラインへのcommon modeノイズ伝播や、伝播信号による電源ラインへの直接ノイズ干渉などである。これらは、EMIの原因となったり、信号から電源へ、電源からさらに信号へ、と作用する正帰還系を構成することによってGbpsクラスの高速デバイスの動作不安定の原因となったりする。

【0005】

一般的に、ノイズを含め、信号間の干渉を防ぐには、GND(GrouND:グランド)シールドを設けると良いとされている。しかし、ボンディングワイヤを有する半導体装置において、ボンディングワイヤの周りにシールド構造を設けると、複数の欠点が生じる。これらの欠点としては、例えば、製造が難しくなる、半導体装置が大型化する、製造コストが上昇する、などが挙げられる。そこで、特別な製造工程を経ずに所望の電気的性能を達成できることが望ましい。

【0006】

図1は、2つの異なるインターポーザ上に実装された2つの同じLSIの出力信号を比較したグラフ群である。図1(a)は、インターポーザがボンディングワイヤを有する場合を示すグラフである。図1(b)は、インターポーザがフリップチップ実装型である場合を示すグラフである。ここで、フリップチップ実装型のインターポーザでは、電源ラインと信号ラインは別のレイヤに配線されており、GNDプレーンによってよく遮断されている。

【0007】

これら2つのLSIは、6.4Gbpsの信号速度で動作する。これらの出力信号は、観測されたcommon mode信号波形をFourier変換して得られたものである。これらのグラフにおいて、横軸は周波数を示し、縦軸はノイズの強度を示す。実線は電源ノイズがなく信号だけがインターポーザに入力された場合を、破線は電源ノイズがある状態でインターポーザに信号が入力された場合を示している。

【0008】

図1から、以下のことが読み取れる。すなわち、フリップチップ実装型のインターポーザの場合は、信号−電源間がよく遮断されているので、電源ノイズの有無に係らず、common modeノイズスペクトルがよく一致している。その一方で、ボンディングワイヤを有するインターポーザの場合は、電源ノイズの有無によるcommon modeノイズの差が、特にMHz帯において、極めて大きい。なお、MHz帯において差が大きいのは、この例では電源ノイズの主たる周波数成分がMHz帯にあるからである。ここで、ボンディングワイヤを有するインターポーザよりも、フリップ実装型のインターポーザの方が高価であることは言うまでもない。

【0009】

このように、ボンディングワイヤを有する半導体装置では、インターポーザの内部における電源系から信号系への直接的なノイズ遷移が大きく、これを低減する手段が必要とされている。すなわち、次世代の低コスト高速デバイスでは、電源―信号間の干渉および結合を低減するとともに、電源ノイズ自体をも低減する手段が必要である。加えて、旧来から指摘されている信号間干渉(クロストーク)や、インピーダンスの不連続による信号反射が抑制されていることも、Gbpsクラスの高速デバイスの安定動作要件である。インターポーザ上のレイアウトリソースは限られているので、これら全ての要件をバランスよく満たす手段が理想的である。

【0010】

図2は、特許文献1(米国特許6538336号明細書)に記載の、LSIチップおよびインターポーザ基板を接続するボンディングワイヤの配置の例を示す図群である。図2(a)は、ボンディングワイヤの配置を全体的に示す俯瞰図である。図2(b)は、ボンディングワイヤの配置を示す側面図である。図2(c)は、図2(b)のA−A’によるボンディングワイヤの断面図である。

【0011】

図2(a)、図2(b)から読み取れるように、この例では、インターポーザ基板上にLSIチップがマウントされている。LSIチップの表面と、インターポーザ基板の表面とのそれぞれには、2列に縦横に配置されたボンディングパッドがある。LSIチップ側のボンディングパッドと、インターポーザ基板側のボンディングパッドとには、ボンディングワイヤの両端がそれぞれ接続されている。

【0012】

図2(c)に示す「S」、「G」および「P」は、ボンディングワイヤが、それぞれ信号(Signal)用、グランド(Ground)用および電源(Power)用であることを意味する。図2(c)から読み取れるように、信号用ボンディングワイヤの縦横方向の隣には、グランド用または電源用のボンディングワイヤが配置されている。ここで、グランド用ボンディングワイヤおよび電源用ボンディングワイヤは、固定電圧を印加されても良いし、信号用パッドが伝播する高速信号より周波数の非常に低い信号を伝播しても良い。以降、グランド用または電源用、もしくは極低周波信号用のボンディングワイヤを、固定電圧用ボンディングワイヤと記す。

【0013】

図2(b)から読み取れるように、LSIチップ上の2列のパッドのうち、実装基板に近い側に配置された一方の列に一端が接続されたボンディングワイヤは、他方の列に一端が接続されたボンディングワイヤの内側を通っている。言い換えれば、第1の列に接続されたボンディングワイヤは、第1の包絡面に含まれており、第2の列に接続されたボンディングワイヤは、第1の包絡面の内側に位置する第2の包絡面に含まれている。

【0014】

このように、図2の例では、高速信号用ボンディングワイヤと、固定電圧用ボンディングワイヤとを、2列の行列状に、交互に配置している。こうすることによって、高速信号用ボンディングワイヤ間を固定電圧用ボンディングワイヤがシールドする効果が得られる。この結果、高速信号間のクロストークが抑制される。

【0015】

ボンディングワイヤを上記のように配置するためには、基本的に、LSIチップ上またはインターポーザ基板上において、高速信号用ボンディングパッドと、電源用ボンディングパッドまたはグランド用ボンディングパッドとが、交互に並んでいる必要がある。

【0016】

図3は、特許文献1に記載の、LSIチップおよびインターポーザ基板を接続するボンディングワイヤの配置の別の例を示す平面図である。図3の例では、LSIチップ上のボンディングパッドが2列の千鳥状に配置されている。

【0017】

高速信号と、電源、グランドおよび極低周波信号とを同列に扱い、かつ、2列に配置されたボンディングパッドを用いることで、高速信号用ボンディングワイヤ間のクロストークを減殺することが出来る。この技術によれば、I/O(In/Out:入出力)回路のボンディングパッドが多くなりがちである。その一方で、高速信号用ボンディングパッドと、固定電圧用ボンディングパッドとの比率によっては、十分に良いクロストーク抑制効果が得られる。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】米国特許6538336号明細書

【非特許文献】

【0019】

【非特許文献1】Myoung Joon Choi, Vishram S. Pandit, and Woong Hwan Ryu, “Controllable Parameters Identification for High Speed Channel through Signal−Power Integrity Combined Analysis”, Proceedings of 58th Electronic Components and Technology Conference, 658 (2008)

【非特許文献2】Ryuichi Oikawa, “A Low−cost Wire−bonding Package Design with Package Built−in Three−dimensional Distributed Matching Circuit for over 5Gbps SerDes Applications”, Proceedings of 59th Electronic Components and Technology Conference, 1098 (2009)

【発明の概要】

【発明が解決しようとする課題】

【0020】

特許文献1での問題は、先に述べた次世代低コスト高速デバイスに対する要件を、全てバランス良く満たしていない点にある。上記要件とは、

(a)電源・信号間の干渉および結合の抑制(common modeノイズ伝播の抑制)

(b)電源ノイズの抑制

(c)信号間の干渉・クロストークの抑制

(d)インピーダンス不連続による信号反射の抑制

である。

【0021】

特許文献1で要件(c)が満たされていることは、その目的から見ても明らかである。要件(b)については、特許文献1には特に記載は無いものの、図3の配置を用いれば、電源用ボンディングワイヤおよびグランド用ボンディングワイヤが隣り合うので、相互インダクタンスにより実効インピーダンスが低下する。その結果、電源ノイズに対する抑制効果が働く。ただし、同じ特許文献1にある、図2の場合は、こうならない。

【0022】

次に、要件(d)について考える。特許文献1では、確かに、高速信号のリターンパスとして作用する電源またはグランドのボンディングワイヤが、信号ワイヤの近傍に配置されている。しかし、インターポーザ上のボンディングパッドが、高速信号用パッドと同じ列に並べられていない。そのため、もともと高いボンディングワイヤのインピーダンスを十分に低くできない。したがって、インピーダンスの連続性という点ではやや不利である。

【0023】

最後に、要件(a)について考える。これは、従来の考慮から抜けていた効果である。また、要件(a)は、特許文献1のように電源とGNDとを等価に扱っていては解決できない課題である。特許文献1においても解決方法は示されていない。

【課題を解決するための手段】

【0024】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0025】

本発明の配線構造は、半導体チップと、この半導体チップを実装する実装基板とを接続するボンディングワイヤ群を具備する。ボンディングワイヤ群は、第1の信号用ボンディングワイヤ(31d、31e)と、第1の電源用ボンディングワイヤ(31b、31g)と、第2の電源用ボンディングワイヤ(32a、32c、32f)とを具備する。ここで、第1の信号用ボンディングワイヤ(31d、31e)は、第1の包絡面に含まれて、信号を伝播する。第1の電源用ボンディングワイヤ(31b、31g)は、第1の包絡面に含まれて、第1の電源電圧を印加される。第2の電源用ボンディングワイヤ(32a、32c、32f)は、第2の包絡面に含まれて、第2の電源電圧を印加される。第1または第2の包絡面の一方は、第1または第2の包絡面の他方と、実装基板との間に配置されている。第2の電源用ボンディングワイヤ(32a、32c、32f)は、第1の信号用ボンディングワイヤ(31d、31e)との電磁結合が、第1の電源用ボンディングワイヤ(31b、31g)との電磁結合よりも小さい位置に配置されている。

【0026】

本発明の配線構造の設計方法は、半導体チップと、この半導体チップを実装する実装基板とを接続するボンディングワイヤ群を具備する配線構造の設計方法である。ここで、ボンディングワイヤ群は、第1の信号用ボンディングワイヤ(31d、31e)と、第1の電源用ボンディングワイヤ(31b、31g)と、第2の電源用ボンディングワイヤ(32a、32c、32f)とを具備する。第1の信号用ボンディングワイヤ(31d、31e)は、第1の包絡面に含まれて、信号を伝播する。第1の電源用ボンディングワイヤ(31b、31g)は、第1の包絡面に含まれて、第1の電源電圧を印加される。第2の電源用ボンディングワイヤ(32a、32c、32f)は、第1の包絡面および実装基板の間に配置された第2の包絡面に含まれて、第2の電源電圧を印加される。本発明の配線構造の設計方法は、(a)第1の信号用ボンディングワイヤならびに第1および第2の電源用ボンディングワイヤの長さに初期値を設定するステップと、(b)第1の信号用ボンディングワイヤならびに第1および第2の電源用ボンディングワイヤの長さに設定された値に基づいて、電磁界解析を用いた回路モデルを生成するステップと、(c)回路モデルに基づいて、回路シミュレーションを用いてcommon modeノイズを算出するステップと、(d)ステップ(c)で算出されたcommon modeノイズが所望の値以下ではないない場合に、第2の電源用ボンディングワイヤの長さを変更するステップと、(e)common modeノイズが所望の値以下になるまで、ステップ(b)〜(d)を繰り返すステップとを具備する。ここで、ステップ(a)は、(a−1)第2の電源用ボンディングワイヤの長さの初期値として、第1の電源用ボンディングワイヤの長さの半分の値を設定するステップを具備する。

【発明の効果】

【0027】

本発明の配線構造では、信号用ボンディングワイヤと、グランド用ボンディングワイヤと、電源用ボンディングワイヤとを、次のように配置する。すなわち、グランド用ボンディングワイヤまたは電源用ボンディングワイヤの一方が、信号用ボンディングワイヤと同じ第1の包絡面に含まれ、他方は別の第2の包絡面に含まれる。ここで、第2の包絡面に含まれるボンディングワイヤおよび信号用ボンディングワイヤの間の電磁結合が、第1の包絡面に含まれる2本のボンディングワイヤの間の電磁結合よりも小さくなるようにする。

【図面の簡単な説明】

【0028】

【図1】図1は、2つの異なるインターポーザ上に実装された2つの同じLSIの出力信号を比較したグラフ群である。図1(a)は、インターポーザがボンディングワイヤを有する場合を示すグラフである。図1(b)は、インターポーザがフリップチップ実装型である場合を示すグラフである。

【図2】図2は、特許文献1に記載の、LSIチップおよびインターポーザ基板を接続するボンディングワイヤの配置の例を示す図群である。図2(a)は、ボンディングワイヤの配置を全体的に示す俯瞰図である。図2(b)は、ボンディングワイヤの配置を示す側面図である。図2(c)は、図2(b)のA−A’によるボンディングワイヤの断面図である。

【図3】図3は、特許文献1に記載の、LSIチップおよびインターポーザ基板を接続するボンディングワイヤの配置の別の例を示す平面図である。

【図4】図4は、本発明の第1の実施形態による配線構造を示す図である。

【図5】図5は、本発明の第1の実施形態による配線構造の構成を示す図群である。図5(a)は、本発明の第1の実施形態による配線構造の構成を示す俯瞰図である。図5(b)は、図5(a)の配線構造を上から見た上面図である。図5(c)は、図5(a)の配線構造を前から見た前面図である。図5(d)は、図5(b)の配線構造のA−A’による断面図である。図5(e)は、図5(a)の配線構造を側面から見た側面図である。

【図6】図6は、ボンディングワイヤ群と、ボンディングワイヤ間の結合フィールドとの関係を示す断面図群である。図6(a)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が最小となる場合を示す断面図である。図6(b)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が最大となる場合を示す断面図である。図6(c)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が中間的となる場合を示す断面図である。図6(d)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が中間的となる別の場合を示す断面図である。

【図7A】図7Aは、本発明の第1の実施形態による配線構造の設計方法の各ステップを示すフローチャートである。

【図7B】図7Bは、本発明の第1の実施形態による配線構造の設計方法で用いる回路モデルの構成を示す回路図である。

【図8】図8は、本発明の第2の実施形態による配線構造の構成を示す図群である。図8(a)は、本発明の第1の実施形態による配線構造の構成を示す俯瞰図である。図8(b)は、図8(a)の配線構造を上から見た上面図である。図8(c)は、図8(a)の配線構造を前から見た前面図である。図8(d)は、図8(b)の配線構造のA−A’による断面図である。図8(e)は、図8(a)の配線構造を側面から見た側面図である。

【図9】図9は、本発明の第2の実施形態による配線構造と従来技術との比較結果を示すグラフ群である。図9(a)は、従来技術による配線構造における相互インダクタンス(Mutual inductance)、すなわち信号用ボンディングワイヤおよび電源用ボンディングワイヤの間の結合を示すグラフである。図9(b)は、従来技術による配線構造におけるcommon mode出力のスペクトルを示すグラフである。図9(c)は、本発明の第2の実施形態による配線構造における相互インダクタンスを示すグラフである。図9(d)は、本発明の第2の実施形態による配線構造におけるcommon mode出力のスペクトルを示すグラフである。

【図10】図10は、本発明の第3の実施形態による配線構造の構成を示す図群である。図10(a)は、本発明の第3の実施形態による配線構造の構成を示す俯瞰図である。図10(b)は、図10(a)の配線構造を上から見た上面図である。図10(c)は、図10(a)の配線構造を前から見た前面図である。図10(d)は、図10(b)の配線構造のA−A’による断面図である。図10(e)は、図10(a)の配線構造を側面から見た側面図である。

【図11】図11は、本発明の第4の実施形態による配線構造の構成を示す図群である。図11(a)は、本発明の第4の実施形態による配線構造の構成を示す俯瞰図である。図11(b)は、図11(a)の配線構造を上から見た上面図である。図11(c)は、図11(a)の配線構造を前から見た前面図である。図11(d)は、図11(b)の配線構造のA−A’による断面図である。図11(e)は、図11(a)の配線構造を側面から見た側面図である。

【図12】図12は、本発明の第5の実施形態による配線構造の構成を示す平面図である。

【発明を実施するための形態】

【0029】

添付図面を参照して、本発明による配線構造および配線構造の設計方法を実施するための形態を以下に説明する。

【0030】

(第1の実施形態)

図4は、本発明の第1の実施形態による配線構造を用いた半導体装置の全体的な構成を概略的に示す図群である。図4(a)は、本発明の第1の実施形態による配線構造を用いた半導体装置の全体的な構成を概略的に示す平面図である。図4(b)は、図4(a)のA−A’による断面図である。

【0031】

図4の半導体装置は、LSIチップ10と、実装基板20と、ボンディングワイヤ30とを具備している。LSIチップ10は、ボンディングパッド11を具備している。実装基板20は、ボンディングパッド21と、リード22とを具備している。

【0032】

LSIチップ10は、実装基板20上に実装されている。ボンディングワイヤ30の両端は、LSIチップ10のボンディングパッド11と、実装基板のボンディングパッド21とに、それぞれ接続されている。実装基板20のボンディングパッド21は、リード22に接続されている。リード22は、図示しない任意の回路に接続されている。

【0033】

一部のボンディングワイヤ31は、同一の包絡面に含まれている。以降、これらのボンディングワイヤをまとめて、第1群のボンディングワイヤ31と呼び、この包絡面を第1の包絡面と呼ぶ。また、別の一部のボンディングワイヤ32は、別の同一の包絡面に含まれている。以降、これらのボンディングワイヤをまとめて、第2群のボンディングワイヤ32と呼び、この包絡面を第2の包絡面と呼ぶ。なお、第2の包絡面は、第1の包絡面と、実装基板20の表面との間に位置している。言い換えれば、第2の包絡面は、第1の包絡面の内側に位置している。

【0034】

図5は、本発明の第1の実施形態による配線構造の構成を示す図群である。図5(a)は、本発明の第1の実施形態による配線構造の構成を示す俯瞰図である。図5(b)は、図5(a)の配線構造を上から見た上面図である。図5(c)は、図5(a)の配線構造を前から見た前面図である。図5(d)は、図5(b)の配線構造のA−A’による断面図である。図5(e)は、図5(a)の配線構造を側面から見た側面図である。

【0035】

本実施形態の配線構造は、LSIチップ10と、実装基板20と、複数のボンディングワイヤとを具備している。ただし、図5では、本発明の第1の実施形態の配線構造のうち、第1〜第7の、合計7本のボンディングワイヤ32a、31b、32c、31d、31e、32f、31gが示されており、他のボンディングワイヤは省略されている。

【0036】

LSIチップ10は、複数のボンディングパッド11を具備している。実装基板20は、複数のボンディングパッド21を具備している。なお、本実施形態では、実装基板20としてインターポーザ基板が用いられているが、これに限定するものでは決してない。

【0037】

第1〜第7のボンディングワイヤ32a、31b、32c、31d、31e、32f、31gは、一方の端部で、第1〜第7のボンディングパッド11a〜gを介してLSIチップ10にそれぞれ接続されている。また、第1〜第7のボンディングワイヤ32a、31b、32c、31d、31e、32f、31gは、他方の端部で、第1〜第7のボンディングパッド21a〜gを介して実装基板20にそれぞれ接続されている。

【0038】

図5(e)からは、第1〜第7のボンディングワイヤ32a、31b、32c、31d、31e、32f、31gを含む第1および第2の包絡面が読み取れる。すなわち、第2のボンディングワイヤ31b、第4のボンディングワイヤ31d、第5のボンディングワイヤ31e、第7のボンディングワイヤ31gは、第1の包絡面に含まれている。また、第1のボンディングワイヤ32a、第3のボンディングワイヤ32c、第6のボンディングワイヤ32fは、第2の包絡面に含まれている。

【0039】

言い換えれば、第2、第4、第5、第7のボンディングワイヤ31b、31d、31e、31gは、互いにほぼ平行に配置されている。このことを、第2、第4、第5、第7のボンディングワイヤ31b、31d、31e、31gのプロファイルは同じである、と表現しても良い。同様に、第1、第3、第6のボンディングワイヤ32a、32c、32fは、互いにほぼ平行に配置されている。したがって、第1、第3、第6のボンディングワイヤ32a、32c、32fのプロファイルは同じだが、第2、第4、第5、第7のボンディングワイヤのプロファイルとは異なる。

【0040】

上記2つのプロファイルが異なることは、図5(b)からも読み取れる。特に、第1、第3のボンディングワイヤ32a、32cは、第2のボンディングワイヤ31bの下に潜り込むように配置されている。同様に、第6のボンディングワイヤ32fは、第7のボンディングワイヤ31gの下に潜り込むように配置されている。

【0041】

さらに、プロファイルの違いにより、実装基板20上のボンディングパッド21a〜21gの配置にも違いが生じていることが、図5(b)からも読み取れる。すなわち、第1、第3、第6のボンディングワイヤ32a、32c、32fに接続される第1、第3、第6のボンディングパッド21a、21c、21fは、他のボンディングパッド21b、21d、21e、21gよりも、LSIチップ10に近い位置に配置されている。

【0042】

第2、第7のボンディングパッド22b、22gは、図示しないグランドに接地されている。第1、第3、第6のボンディングパッド22a、22c、22fは、図示しない電源電圧供給源に接続されている。

【0043】

本実施形態では、第4、第5のボンディングワイヤ31d、31eは対となって、LSIチップ10および実装基板20の間で差動信号を伝達する信号用ボンディングワイヤとして動作する。第2、第7のボンディングワイヤ31b、31gは、グランド用ボンディングワイヤとして動作する。第1、第3、第6のボンディングワイヤ32a、32c、32fは、電源用ボンディングワイヤとして動作する。

【0044】

なお、信号用ボンディングワイヤ31d、31eが差動信号を伝達することは、本発明の本質とは直接関係しない。したがって、本発明の配線構造では、必ずしも2本の信号用ボンディングワイヤが隣接していなくても良いし、信号用ボンディングワイヤに隣接するグランド用ボンディングワイヤの本数は1本であっても良い。

【0045】

本実施形態の配線構造では、信号用ボンディングワイヤ31d、31eと、グランド用ボンディングワイヤ31b、31gとが、LSIチップ10から実装基板20まで並走している。このことにより、元来高すぎるボンディングワイヤのインピーダンスが低下する。この結果、ボンディングワイヤのインピーダンスは、実装基板20の伝送路インピーダンスとも、本発明による半導体装置1が搭載されるシステムボードの伝送路インピーダンスとも、近い値になる。さらに、信号31d−31e間のスキューもほぼ0となる。

【0046】

また、図5の構成では、電源用ボンディングワイヤ32a、32c、32fおよび信号用ボンディングワイヤ31d、31eを介する、すなわち電源系回路から信号系回路への、ノイズ干渉が最小化される。この原理を、図6を用いて説明する。

【0047】

図6は、ボンディングワイヤ群と、ボンディングワイヤ間の結合フィールドとの関係を示す断面図群である。図6(a)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が最小となる場合を示す断面図である。図6(b)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が最大となる場合を示す断面図である。図6(c)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が中間的となる場合を示す断面図である。図6(d)は、信号・グランド間の結合フィールドと、グランド・電源間の結合フィールドとの干渉が中間的となる別の場合を示す断面図である。

【0048】

図6のボンディングワイヤ群は、第1〜第6のボンディングワイヤ33a〜33fを具備している。ここで、第1、第6のボンディングワイヤ33a、33fは、電源用ボンディングワイヤである。第2、第5のボンディングワイヤ33b、33eは、グランド用ボンディングワイヤである。第3、第4のボンディングワイヤ33c、33dは、信号用ボンディングワイヤである。

【0049】

図6において、隣接するボンディングワイヤの間に、第1〜第4の結合フィールド34a〜34dが発生している。第1の結合フィールド33aは、第1、第2のボンディングワイヤ33a、33bの間に発生している。第2の結合フィールド33aは、第2、第3のボンディングワイヤ33a、33bの間に発生している。第3の結合フィールド33aは、第4、第5のボンディングワイヤ33a、33bの間に発生している。第4の結合フィールド33aは、第5、第6のボンディングワイヤ33a、33bの間に発生している。なお、第3、第4のボンディングワイヤ33c、33dも互いに隣接しているので、当然両者の間に第5の結合フィールドが発生するはずである。しかし、信号−電源間の干渉を説明するのに信号間結合効果は必要ないので、その表示を省略してある。

【0050】

図6において、第2、第3の結合フィールド34b、34cが発生するのは、グランド用ボンディングワイヤ33b、33eが、隣接する信号用ボンディングワイヤ33c、33dにそれぞれに対応するリターンパスとして動作するからである。同様に、第1、第4の結合フィールド34a、34dが発生するのは、電源用ボンディングワイヤ33aとグランド用ボンディング33bが互いにリターンパスとして動作し、グランド用ボンディング33eと電源用ボンディングワイヤ33fもまた互いにリターンパスとして動作するからである。

【0051】

なお、これらの結合フィールド34a〜34dは、磁力線と捉えてもよいし、電気力線の包絡線と捉えてもよい。

【0052】

図6(b)では、グランド・電源間の結合フィールド34aと、信号・グランド間の結合フィールド34bとが、互いに平行になっている。この場合、2つの結合フィールド34a、34bは、同じ向きであるか、180度逆の正反対の向きであるかのどちらかである。すなわち、2つの結合フィールド34a、34bは、互いに最大限に強め合うか、互いに最大限に弱め合うかのどちらかである。さらに、信号・グランド間の結合フィールド34cと、グランド・電源間の結合フィールド34dとも、互いに平行になっている。したがって、電源系回路から信号系回路への、common modeノイズの伝播は、図6(b)の構成において最大になる。

【0053】

この観点から、電源系回路から信号系回路への、common modeノイズの伝播が最小になるのは、図6(a)のように、グランド・電源間の結合フィールド34aおよび34dと、信号・グランド間の結合フィールド34bおよび34cとが、それぞれ直角に交わる場合である。なぜなら、このとき互いのフィールドベクトルのスカラー積(内積)が0に近い値をとり、したがってエネルギー伝播が最小となるからである。

【0054】

また、図6(c)や図6(d)のように、グランド・電源間の結合フィールド34aおよび34dと、信号・グランド間の結合フィールド34bおよび34cとが、それぞれ交わる角度が90度より大きく、かつ、180度より小さい場合は、電源系回路から信号系回路への、common modeノイズの伝播が中間的な強さになる。

【0055】

したがって、図6(a)のように、信号用ボンディングワイヤおよびグランド用ボンディングワイヤが張る平面と、電源用ボンディングワイヤおよびグランド用ボンディングワイヤが張る平面とが、直交する構成を実現するのが理想的である。図5(d)から読み取れるように、本実施形態では、この原理に基づいて、ボンディングワイヤの位置関係を立体的に設定している。

【0056】

なお、厳密には2本のボンディングワイヤが張る面は、実際には曲面である場合が多い。この場合に、2つの面の直交を定義することは難しい。そこで、例えば、電源用ボンディングワイヤにおけるいずれかの点を規準にして、この基準点と、この基準点に最も近い信号用ボンディングワイヤ上の点とを結ぶ第1の直線を考える。同様に、この基準点と、この基準点に最も近いグランド用ボンディングワイヤ上の点とを結ぶ第2の直線を考える。これら第1、第2の直線が、この基準点において直交することが望ましい。さらには、このような基準点が、電源用ボンディングワイヤ上に複数あることが好ましい。

【0057】

本発明の原理は、ボンディングワイヤ間の第1および第2の結合フィールドの位置関係を、直交に近づけることにある。ここで、第1の結合フィールドは、信号を伝播する第1のボンディングワイヤと、この信号のリターンパスとして動作する第2のボンディングワイヤとの間に発生する結合フィールドである。また、第2の結合フィールドは、電源電圧を印加される第3のボンディングワイヤと、この電源電圧のリターンパスとして動作する第2のボンディングワイヤとの間に発生する結合フィールドである。

【0058】

なお、従来技術の説明で述べたとおり、電源用ボンディングワイヤは信号用ボンディングワイヤのリターンパスとして動作可能である。また、電源用ボンディングワイヤと、グランド用ボンディングワイヤとは、互いにリターンパスの関係となり得る。したがって、電源用ボンディングワイヤと、グランド用ボンディングワイヤとの関係をそっくり入れ替えても、本発明では同じ効果が得られる。少し詳しく説明すると次のとおりである。グラウンドを信号のリターンパスとするとき、信号に対するノイズ源はグラウンドと異なる電位変動をするもう一方の電圧源、つまり電源ワイヤである。反対に、電源を信号のリターンパスとするときは、電源と異なる電位変動をするもう一方の電圧源であるグラウンドのほうが信号に対するノイズ源となる。

【0059】

また、本発明では、主に2つの結合フィールドが交わる相対角度が問題となる。したがって、ボンディングワイヤの複数のプロファイルに対応する包絡面の上下関係、すなわちボンディングワイヤの断面の上下関係は、どちらであっても構わない。例えば、電源用ボンディングワイヤを、グランド用ボンディングワイヤより、その断面図構造における上方に配置しても、なんら支障はない。なお、この場合、実装基板上では、電源用ボンディングパッドは、LSIチップから見てより遠い側に、信号用またはグランド用ボンディングパッドは、LSIチップから見てより近い側に、それぞれ配置されることになる。

【0060】

次に、各ボンディングワイヤの長さの比率について説明する。図5(e)に示したとおり、信号用ボンディングワイヤと同じ包絡面に含まれて、すなわち信号用ボンディングワイヤと同じプロファイルを有する、グランド用ボンディングワイヤ31b、31gの長さをL1とする。同様に、信号用ボンディングワイヤとは異なる包絡面に含まれて、すなわち信号用ボンディングワイヤとは異なるプロファイルを有する、電源用ボンディングワイヤ32a、32c、32fの長さをL2とする。本発明では、これらのワイヤ長L1、L2には、最適な比率が存在する。

【0061】

この最適比率は、半導体装置側および実装基板側のボンディングパッドの高さの違いなどにも依存するが、様々な例における計算機実験によれば、概ね、

L1:L2=1:0.6

が最適値として得られた。

【0062】

この最適比率は、次のように理論的に説明できる。電源系回路から信号系回路へのノイズ伝播を小さくするには、電源ノイズ自体を小さくするか、信号系回路と電源系回路との間の干渉を小さくするか、いずれかを行えばよい。

【0063】

信号用ボンディングワイヤおよびグランド用ボンディングワイヤが通る第1の平面と、グランド用ボンディングワイヤおよび電源用ボンディングワイヤが通る第2の平面とが直交するとき、電源用ボンディングワイヤの長さを長くすれば、いいかえれば電源用ボンディングワイヤとグラウンド用ボンディングワイヤの並走距離を長くすれば、前記結合フィールドの直交関係が保たれる範囲が大きくなるので、信号系回路および電源系回路の間の干渉は小さくなる。しかし、電源用ボンディングワイヤが長くなれば長くなるだけ電源インピーダンスも増加するので、同時に電源ノイズが増加する。

【0064】

反対に、電源用ボンディングワイヤの長さを短くすれば、電源ノイズは小さくなるが、反対に、信号形回路および電源系回路の間の干渉は大きくなる。LSI上のデカップリング容量や、この半導体装置が実装されるボードの設計にもよるが、原理的に、極荒い近似では、これらのワイヤ長は1:2、つまり短いボンディングワイヤが長いボンディングワイヤの半分の長さにするのが、最適比率となる。上記の計算で得られた1:0.6は、本発明の第1の実施形態の構成の場合にそうなった、ということであり、十分に納得できる値である。

【0065】

近年よく行われる、いわゆるシリコン・パッケージ・ボードco−designの初期においては、パッケージ設計に使用するシリコンおよびボードの情報が未知であったり、精度が悪かったりするのは、よくあることである。そのような場合に、ボンディングワイヤプロファイルの設計を行うには、長さ比率50%を初期値として行うことで、パッケージの設計を効率よく行うことが出来る。また、長さ比率50%を初期値とすることは、未知要素の変動に対して、確率的に最大の安定度が得られる。

【0066】

ここで、図7Aおよび図7Bを用いて、本発明の第1の実施形態による配線構造の設計方法について説明する。

【0067】

図7Aは、本発明の第1の実施形態による配線構造の設計方法の各ステップを示すフローチャートである。図7Bは、本発明の第1の実施形態による配線構造の設計方法で用いる回路モデルの構成を示す回路図である。

【0068】

図7Bの回路モデルの構成要素について説明する。図7Bの回路モデルは、LSIチップモデル(LSI model)部100と、パッケージモデル(Package model)部200と、ボードモデル(Board model)部300と、直流電源モデル(DC Supply)部400と、終端モデル(Termination)部500と、計測点600とを具備している。

【0069】

LSIチップモデル部100は、入出力回路モデル(I/O Driver model)部110と、チップ上電流源モデル部と、チップ上電力供給回路モデル部とを具備している。

【0070】

パッケージモデル部200は、信号用ボンディングワイヤ、グランド用ボンディングワイヤ、電源用ボンディングワイヤ、などのモデルを含む。

【0071】

ボードモデル部300は、電源回路モデル部(Power supply model)310と、信号回路モデル部(Sgnal model)320とを具備している。

【0072】

図7Bの回路モデルの構成要素の接続関係について説明する。入出力回路モデル部110は、パッケージモデル部200に接続されている。チップ上電流源モデル部120は、チップ上電力供給回路モデル部130を介してパッケージモデル部200に接続されている。パッケージモデル部200は、電源回路モデル部310と、信号回路モデル部320とに接続されている。電源回路モデル310部は、直流電源モデル部400に接続されている。信号回路モデル部320は、終端モデル部500に接続されている。

【0073】

なお、計測点(Observation point)600は、信号回路モデル部320および終端モデル部500の接続点に設定されている。

【0074】

図7Aのフローチャートについて説明する。図7Aのフローチャートは、第1〜第9のステップS1〜S9を具備している。

【0075】

第1のステップS1において、本発明の配線構造の設計方法を開始する。第1のステップS1の次に、第2のステップS2へ進む。

【0076】

第2のステップS2において、電源用ボンディングワイヤの長さの初期値を、グランド用ボンディングワイヤの半分の長さに設定する。第2のステップS2の次は、第3のステップS3へ進む。

【0077】

第3のステップS3において、電磁界解析によって実装基板モデル200を生成する。第3のステップS3の次は、第6のステップS6へ進む。

【0078】

なお、第6のステップS6を行う前に、第4、第5のステップS4、S5において、LSIチップモデル100と、ボードの回路モデル300とを、それぞれあらかじめ用意しておくことが望ましい。第4、第5のステップS4、S5は、第6のステップS6を行う前であればいつ生成してもよいし、既存のデータを用いても構わない。

【0079】

第6のステップS6において、回路シミュレーションによってcommon modeノイズを、計測点600で計測する。この回路シミュレーションには、第3〜第5のステップS3〜S5で得られた各モデルを用いる。第6のステップS6の次は、第7のステップS7へ進む。

【0080】

第7のステップS7において、第6のステップS6で得られたcommon modeノイズが、所望の値以下であるかどうかを確認する。common modeノイズが所望の値以下であれば、第9のステップS9へ進み、その他の場合は第8のステップS8へ進む。

【0081】

第8のステップS8において、電源用ボンディングワイヤの長さを延長または短縮する。このとき、common modeノイズが減る方向に、電源用ボンディングワイヤの長さに変化を与えるべきなので、事前に調べておくことが望ましい。第8のステップS8の次は、第3のステップに戻る。

【0082】

第9のステップS9において、本発明の配線構造の設計方法を終了する。

【0083】

(第2の実施形態)

図8は、本発明の第2の実施形態による配線構造の構成を示す図群である。図8(a)は、本発明の第1の実施形態による配線構造の構成を示す俯瞰図である。図8(b)は、図8(a)の配線構造を上から見た上面図である。図8(c)は、図8(a)の配線構造を前から見た前面図である。図8(d)は、図8(b)の配線構造のA−A’による断面図である。図8(e)は、図8(a)の配線構造を側面から見た側面図である。

【0084】

本実施形態は、本発明の第1の実施形態から、実装基板上の電源用ボンディングパッド21a、21c、21fの位置を変更したものである。その結果、図8(a)、図8(b)、図8(c)、図8(d)から読み取れるように、電源用ボンディングワイヤ32a、32c、32fの方向も変更されている。ただし、図8(e)から読み取れるように、電源用ボンディングワイヤ32a、32c、32fのプロファイルは、本発明の第1の実施形態と同じである。言い換えれば、電源用ボンディングワイヤ32a、32c、32fを含む包絡面も、本発明の第1の実施形態同じである。その他の構成要素、接続関係、動作などは、本発明の第1の実施形態と全て同じであるので、さらなる説明を省略する。

【0085】

本発明の第1の実施形態では、信号用ボンディングワイヤおよびグランド用ボンディングワイヤの平面と、グランド用ボンディングワイヤおよび電源用ボンディングワイヤの平面とが交わる角度が、ほぼ90度であった。しかし、本実施形態では、この角度がほぼ60度〜ほぼ120度の範囲に含まれている。実験によれば、信号用ボンディングワイヤ、グランド用ボンディングワイヤ、電源用ボンディングワイヤのなかで最も短い最短のボンディングワイヤの、全長の半分に相当する領域において、この角度が60度よりおおきく、かつ、120度よりも小さければ、common modeノイズが半減し、十分な効果が得られることが確認された。ただし、いずれの場合も、電源用ボンディングワイヤまたはグランド用ボンディングワイヤのうち、信号用ボンディングワイヤに対するリターンパスとして用いる方のボンディングワイヤは、信号ボンディングワイヤと同じプロファイルにする必要がある。

【0086】

なお、60度〜120度の範囲の規準となる平面は、実際には曲面である場合が多い。したがって、本発明の第1の実施形態と同様に、1本のボンディングワイヤ上の基準点において、この範囲の角度を得られることが望ましい。さらには、信号用、グランド用、電源用の3本のボンディングワイヤのうち、最も短い最短のボンディングワイヤの、全長の半分に相当する領域における任意の点が、このような基準点の条件を満たすことが好ましい。

【0087】

ここで、本実施形態による配線構造の構成例を用いて、従来技術の場合との比較を行う。本発明との比較対象となる従来技術による配線構造の構成は、図8の電源用ボンディングワイヤ32a、32c、32fの長さを伸ばして、信号用およびグランド用のボンディングワイヤ31b、31d、31e、31gと同じプロファイルとしたものとする。

【0088】

図9は、本発明の第2の実施形態による配線構造と従来技術との比較結果を示すグラフ群である。図9(a)は、従来技術による配線構造における相互インダクタンス(Mutual inductance)、すなわち信号用ボンディングワイヤおよび電源用ボンディングワイヤの間の結合を示すグラフである。図9(b)は、従来技術による配線構造におけるcommon mode出力のスペクトルを示すグラフである。図9(c)は、本発明の第2の実施形態による配線構造における相互インダクタンスを示すグラフである。図9(d)は、本発明の第2の実施形態による配線構造におけるcommon mode出力のスペクトルを示すグラフである。

【0089】

図9から、本発明により、信号用ボンディングワイヤおよび電源用ボンディングワイヤの間の相互インダクタンスが、従来技術の半分以下、ほぼ1/3程度にまで減少することが読み取れる。また、その結果として電源系回路から信号系回路に伝播する電源ノイズに起因する低周波成分が減少していることが確認できる。

【0090】

(第3の実施形態)

図10は、本発明の第3の実施形態による配線構造の構成を示す図群である。図10(a)は、本発明の第3の実施形態による配線構造の構成を示す俯瞰図である。図10(b)は、図10(a)の配線構造を上から見た上面図である。図10(c)は、図10(a)の配線構造を前から見た前面図である。図10(d)は、図10(b)の配線構造のA−A’による断面図である。図10(e)は、図10(a)の配線構造を側面から見た側面図である。

【0091】

本実施形態は、本発明の第1の実施形態から、電源用ボンディングワイヤとして動作する第1のボンディングワイヤ32aを取り除き、さらに、LSIチップ10のボンディングパッド11の位置を変更したものである。その結果、図10(e)から読み取れるように、電源用ボンディングワイヤ32c、32fを含む第2の包絡面は、グランド用ボンディングワイヤ31b、31gおよび信号用ボンディングワイヤ31d、31eを含む第1の包絡面から完全に離れて、その内側に配置されている。言い換えると、電源用ボンディングワイヤ32c、32fのプロファイルは、グランド用ボンディングワイヤ31b、31gおよび信号用ボンディングワイヤ31d、31eのプロファイルにほぼ平行となっている。さらに、図10(b)から読み取れるように、グランド用ボンディングワイヤ31b、31gおよび信号用ボンディングワイヤ31d、31eがほぼ平行に配置されている。また、電源用ボンディングワイヤ32c、32fがグランド用ボンディングワイヤ31b、31gのほぼ真下を通っている。その他の構成要素、接続関係、動作などは、本発明の第1の実施形態と全て同じであるので、さらなる説明を省略する。

【0092】

このように、本実施形態によれば、LSIチップ10上のボンディングパッド11に必要な面積が増えるものの、本発明の理想とする配線の構造を、本発明の第1または第2の実施形態よりも、さらに忠実に適用できる。

【0093】

(第4の実施形態)

図11は、本発明の第4の実施形態による配線構造の構成を示す図群である。図11(a)は、本発明の第4の実施形態による配線構造の構成を示す俯瞰図である。図11(b)は、図11(a)の配線構造を上から見た上面図である。図11(c)は、図11(a)の配線構造を前から見た前面図である。図11(d)は、図11(b)の配線構造のA−A’による断面図である。図11(e)は、図11(a)の配線構造を側面から見た側面図である。

【0094】

LSIチップ10を実装する実装基板20として、本発明の第1〜第3の実施形態ではインターポーザ基板を用いたが、本実施形態ではリードフレームを用いる。本実施形態の実装基板20は、LSIチップを実装するダイパッド24と、ボンディングワイヤに接続されるリードピン23b、23d、23e、23gとを具備している。図11の例では、ダイパッド24が露出するタイプのQFP(Quad Flat Package)用のリードフレームが用いられている。

【0095】

本実施形態では、実装基板20上の、LSIチップ10に近い方のボンディングパッドとして、LSIチップ10を実装するダイパッド24を用いている。また、LSIチップ10から遠い方のボンディングパッドとして、リードピン23b、23d、23e、23gを用いている。そこで、本実施形態では、グランド用ボンディングワイヤおよび電源用ボンディングワイヤの役割を、本発明の第1〜第3の実施形態とは逆にしている。すなわち、実装基板20上の、LSIチップ10に近い方のボンディングパッドに接続される第1、第3、第6のボンディングワイヤ32a、32c、32fは、本実施形態ではグランド用ボンディングワイヤとして動作する。また、実装基板20上の、LSIチップ10から遠い方のボンディングパッドに接続される第2、第7のボンディングワイヤ31b、31gは、電源用ボンディングワイヤとして動作する。本発明において、グランド用ボンディングワイヤおよび電源用ボンディングワイヤの役割、すなわち印加される電圧を交換しても構わないことは、すでに説明したとおりである。その他の構成要素、接続関係、動作などは、本発明の第1の実施形態と全て同じであるので、さらなる説明を省略する。

【0096】

このように、本発明による配線構造は、実装基板として、本発明の第1〜第3の実施形態で用いたインターポーザ基板のみならず、リードフレームを用いた場合でも適用可能である。

【0097】

(第5の実施形態)

図12は、本発明の第5の実施形態による配線構造の構成を示す平面図である。本実施形態は、本発明の第4の実施形態に、第8〜第10のボンディングワイヤ31h〜31jと、3つのリードピン23h〜23jとを追加したものに等しい。

【0098】

3本のボンディングワイヤ31h、31i、31jは、この順番に、信号用ボンディングワイヤとして動作する第4のボンディングワイヤ31eと、グランド用ボンディングワイヤとして動作する第6のボンディングワイヤ31fとの間に配置されている。同様に、3つの3つのリードピン23h〜23jは、この順番に、第5、第6のリードピン23e、23fの間に配置されている。3本のボンディングワイヤ31h、31i、31jは、電源用ボンディングワイヤまたは信号用ボンディングワイヤとして動作する第2、第4、第5、第7のボンディングワイヤ31b、31d、31e、31gと同様に、第1のプロファイルを有しており、すなわち、第1の包絡面に含まれている。

【0099】

第8〜第10のボンディングワイヤ31h、31i、31jの一方の端部は、LSIチップ10のボンディングパッドに接続されている。第8〜第10のボンディングワイヤ31h、31i、31jの他方の端部は、3つのリードピン23h〜23jにそれぞれ接続されている。

【0100】

その他の構成要素、接続関係、動作などは、本発明の第1の実施形態と全て同じであるので、さらなる説明を省略する。

【0101】

第8のボンディングワイヤ31hは、電源用ボンディングワイヤとして動作する。また第9、第19の、ボンディングワイヤ31i、31jは、差動信号を伝播する1対の信号用ボンディングワイヤとして動作する。すなわち、本実施形態では、2対の信号用ボンディングワイヤを用いて、2つの差動信号を伝播する。一般的に、2対の信号用ボンディングワイヤの間には、信号間干渉、すなわちクロストークが発生する可能性がある。

【0102】

図12に示した構成例を用いて、本発明の配線構造が有する、信号間干渉すなわちクロストークを抑制する効果について説明する。電源用ボンディングワイヤとして動作する第2、第7、第8のボンディングワイヤ31b、31g、31hは、信号用ボンディングワイヤとして動作する第4、第5、第9、第10のボンディングワイヤ31d、31e、31i、13jと同じプロファイルで、かつ、ほぼ平行に配置されている。したがって、第1の差動信号を伝播する第1の信号用ボンディングワイヤ対31d、31eと、第2の差動信号を伝播する第2の信号用ボンディングワイヤ対31i、31jとは、間に挟まれた第8のボンディングワイヤ31hによって、その全長にわたってシールドされている。したがって、第1および第2の信号用ボンディングワイヤ対31d、31eおよび31i、31jの間では、クロストークが効率よく抑制される。

【0103】

これまで、本発明の配線構造における複数の実施形態について説明した。いずれの構成の場合も、信号用ボンディングワイヤおよび信号用のリターンパスとして動作するボンディングワイヤは、互いに強い相互インピーダンスを持つように配置される。また、電源用ボンディングワイヤおよび電源用リターンパスとして動作するボンディングワイヤの組み合わせにおいても、やはり互いに強い相互インピーダンスを持つように配置される。なぜなら信号―電源間の干渉が抑制されるためには、信号とそのリターンパス同士、および電源とそのリターンパス同士が強い結合をもつことが必須条件だからである。電源用ボンディングワイヤとそのリターンパス用ボンディングワイヤ、すなわちグラウンドワイヤが互いに強い結合をもつことから、本発明による配線構造を用いることは、クロストークのみならず、電源インピーダンスの低減にも効果的である。

【0104】

以上、本発明による配線構造が、課題として挙げた4つの要件、すなわち

(a)電源・信号間の干渉および結合の抑制(common modeノイズ伝播の抑制)

(b)電源ノイズの抑制

(c)信号間の干渉・クロストークの抑制

(d)インピーダンス不連続による信号反射の抑制

の全てを満たすことを説明した。

【0105】

なお、これら複数の実施形態におけるそれぞれの特徴は、技術的に矛盾しない範囲において、自由に組み合わせ可能であることは言うまでもない。

【符号の説明】

【0106】

1 半導体装置

10 LSIチップ

11、11a〜11g ボンディングパッド

20 実装基板

21、21a〜21g ボンディングパッド

22 リード

23b、23d、23e、23g〜23j リードピン

24 ダイパッド

30 ボンディングワイヤ

31 ボンディングワイヤ(第1群)

31b、31g (グランド用)ボンディングワイヤ

31d、31e (信号用)ボンディングワイヤ

32 ボンディングワイヤ(第2群)

32a、32c、32f (電源用)ボンディングワイヤ

33a〜33f ボンディングワイヤ

34a〜34d 結合フィールド

100 LSIチップモデル部

110 入出力回路モデル部

120 チップ上電流源モデル部

130 チップ上電力供給回路モデル部

200 パッケージモデル部

300 ボードモデル部

310 電源回路モデル部

320 信号回路モデル部

400 直流電源モデル部

500 終端モデル部

600 計測点

【特許請求の範囲】

【請求項1】

半導体チップと、前記半導体チップを実装する実装基板とを接続するボンディングワイヤ群

を具備し、

前記ボンディングワイヤ群は、

第1の包絡面に含まれて、信号を伝播する第1の信号用ボンディングワイヤと、

前記第1の包絡面に含まれて、第1の電源電圧を印加される第1の電源用ボンディングワイヤと、

第2の包絡面に含まれて、第2の電源電圧を印加される第2の電源用ボンディングワイヤと

を具備し、

前記第1または前記第2の包絡面の一方は、前記第1または前記第2の包絡面の他方と、前記実装基板との間に配置されており、

前記第2の電源用ボンディングワイヤは、前記第1の信号用ボンディングワイヤとの電磁結合が、前記第1の電源用ボンディングワイヤとの電磁結合よりも小さい位置に配置されている

配線構造。

【請求項2】

請求項1に記載の配線構造において、

前記第1の信号用ボンディングワイヤならびに前記第1および前記第2の電源用ボンディングワイヤからなる3本のボンディングワイヤの中で、

全長が最も短い最短ボンディングワイヤの半分の長さに相当する領域における任意の点および前記最短ボンディングワイヤ以外の一方のボンディングワイヤ上で最も近い第1の点を通る第1の直線と、前記任意の点および前記最短ボンディングワイヤ以外の他方のボンディングワイヤ上で最も近い第2の点を通る第2の直線とが交わる角度が、60度より大きく、かつ、120度より小さい

配線構造。

【請求項3】

請求項1〜2のいずれかに記載の配線構造において、

前記第1の電源用ボンディングワイヤ上の所定の点および前記第1の信号用ボンディングワイヤ上で前記所定の点から最も近い第1の点を通る第1の直線と、前記第1の電源用ボンディングワイヤ上の所定の点および前記第2の電源用ボンディングワイヤ上で前記所定の点から最も近い第2の点とを通る第2の直線とが、直角に交わる

配線構造。

【請求項4】

請求項1〜3のいずれかに記載の配線構造において、

前記ボンディングワイヤ群は、

前記第1の包絡面に含まれて、かつ、前記第1の信号用ボンディングワイヤに隣接して配置されて、前記第1の信号用ボンディングワイヤとともに差動信号を伝達する第2の信号用ボンディングワイヤ

をさらに具備する

配線構造。

【請求項5】

請求項1〜4のいずれかに記載の配線構造において、

前記第1の電源用ボンディングワイヤは、接地されている

配線構造。

【請求項6】

請求項1〜4のいずれかに記載の配線構造において、

前記第2の電源用ボンディングワイヤは、接地されている

配線構造。

【請求項7】

請求項1〜6のいずれかに記載の配線構造において、

前記半導体装置と、

前記実装基板と、

前記ボンディングワイヤ群と

を具備する

半導体装置。

【請求項8】

半導体チップと、前記半導体チップを実装する実装基板とを接続するボンディングワイヤ群を具備する配線構造の設計方法であって、

前記ボンディングワイヤ群は、

第1の包絡面に含まれて、信号を伝播する第1の信号用ボンディングワイヤと、

前記第1の包絡面に含まれて、第1の電源電圧を印加される第1の電源用ボンディングワイヤと、

前記第1の包絡面および前記実装基板の間に配置された第2の包絡面に含まれて、第2の電源電圧を印加される第2の電源用ボンディングワイヤと

を具備し、

(a)前記第1の信号用ボンディングワイヤならびに前記第1および前記第2の電源用ボンディングワイヤの長さに初期値を設定するステップと、

(b)前記第1の信号用ボンディングワイヤならびに前記第1および前記第2の電源用ボンディングワイヤの長さに設定された値に基づいて、電磁界解析を用いた回路モデルを生成するステップと、

(c)前記回路モデルに基づいて、回路シミュレーションを用いてcommon modeノイズを算出するステップと、

(d)前記ステップ(c)で算出されたcommon modeノイズが所望の値以下ではないない場合に、前記第2の電源用ボンディングワイヤの長さを変更するステップと、

(e)前記common modeノイズが前記所望の値以下になるまで、前記ステップ(b)〜(d)を繰り返すステップと

を具備し、

前記ステップ(a)は、

(a−1)前記第2の電源用ボンディングワイヤの長さの初期値として、前記第1の電源用ボンディングワイヤの長さの半分の値を設定するステップ

を具備する

配線構造の設計方法。

【請求項9】

請求項8に記載の配線構造の設計方法において、

前記ステップ(b)は、

(b−1)前記LSIチップのモデルを生成するステップと、

(b−2)前記実装基板のモデルを生成するステップと

を具備する

配線構造の設計方法。

【請求項1】

半導体チップと、前記半導体チップを実装する実装基板とを接続するボンディングワイヤ群

を具備し、

前記ボンディングワイヤ群は、

第1の包絡面に含まれて、信号を伝播する第1の信号用ボンディングワイヤと、

前記第1の包絡面に含まれて、第1の電源電圧を印加される第1の電源用ボンディングワイヤと、

第2の包絡面に含まれて、第2の電源電圧を印加される第2の電源用ボンディングワイヤと

を具備し、

前記第1または前記第2の包絡面の一方は、前記第1または前記第2の包絡面の他方と、前記実装基板との間に配置されており、

前記第2の電源用ボンディングワイヤは、前記第1の信号用ボンディングワイヤとの電磁結合が、前記第1の電源用ボンディングワイヤとの電磁結合よりも小さい位置に配置されている

配線構造。

【請求項2】

請求項1に記載の配線構造において、

前記第1の信号用ボンディングワイヤならびに前記第1および前記第2の電源用ボンディングワイヤからなる3本のボンディングワイヤの中で、

全長が最も短い最短ボンディングワイヤの半分の長さに相当する領域における任意の点および前記最短ボンディングワイヤ以外の一方のボンディングワイヤ上で最も近い第1の点を通る第1の直線と、前記任意の点および前記最短ボンディングワイヤ以外の他方のボンディングワイヤ上で最も近い第2の点を通る第2の直線とが交わる角度が、60度より大きく、かつ、120度より小さい

配線構造。

【請求項3】

請求項1〜2のいずれかに記載の配線構造において、

前記第1の電源用ボンディングワイヤ上の所定の点および前記第1の信号用ボンディングワイヤ上で前記所定の点から最も近い第1の点を通る第1の直線と、前記第1の電源用ボンディングワイヤ上の所定の点および前記第2の電源用ボンディングワイヤ上で前記所定の点から最も近い第2の点とを通る第2の直線とが、直角に交わる

配線構造。

【請求項4】

請求項1〜3のいずれかに記載の配線構造において、

前記ボンディングワイヤ群は、

前記第1の包絡面に含まれて、かつ、前記第1の信号用ボンディングワイヤに隣接して配置されて、前記第1の信号用ボンディングワイヤとともに差動信号を伝達する第2の信号用ボンディングワイヤ

をさらに具備する

配線構造。

【請求項5】

請求項1〜4のいずれかに記載の配線構造において、

前記第1の電源用ボンディングワイヤは、接地されている

配線構造。

【請求項6】

請求項1〜4のいずれかに記載の配線構造において、

前記第2の電源用ボンディングワイヤは、接地されている

配線構造。

【請求項7】

請求項1〜6のいずれかに記載の配線構造において、

前記半導体装置と、

前記実装基板と、

前記ボンディングワイヤ群と

を具備する

半導体装置。

【請求項8】

半導体チップと、前記半導体チップを実装する実装基板とを接続するボンディングワイヤ群を具備する配線構造の設計方法であって、

前記ボンディングワイヤ群は、

第1の包絡面に含まれて、信号を伝播する第1の信号用ボンディングワイヤと、

前記第1の包絡面に含まれて、第1の電源電圧を印加される第1の電源用ボンディングワイヤと、

前記第1の包絡面および前記実装基板の間に配置された第2の包絡面に含まれて、第2の電源電圧を印加される第2の電源用ボンディングワイヤと

を具備し、

(a)前記第1の信号用ボンディングワイヤならびに前記第1および前記第2の電源用ボンディングワイヤの長さに初期値を設定するステップと、

(b)前記第1の信号用ボンディングワイヤならびに前記第1および前記第2の電源用ボンディングワイヤの長さに設定された値に基づいて、電磁界解析を用いた回路モデルを生成するステップと、

(c)前記回路モデルに基づいて、回路シミュレーションを用いてcommon modeノイズを算出するステップと、

(d)前記ステップ(c)で算出されたcommon modeノイズが所望の値以下ではないない場合に、前記第2の電源用ボンディングワイヤの長さを変更するステップと、

(e)前記common modeノイズが前記所望の値以下になるまで、前記ステップ(b)〜(d)を繰り返すステップと

を具備し、

前記ステップ(a)は、

(a−1)前記第2の電源用ボンディングワイヤの長さの初期値として、前記第1の電源用ボンディングワイヤの長さの半分の値を設定するステップ

を具備する

配線構造の設計方法。

【請求項9】

請求項8に記載の配線構造の設計方法において、

前記ステップ(b)は、

(b−1)前記LSIチップのモデルを生成するステップと、

(b−2)前記実装基板のモデルを生成するステップと

を具備する

配線構造の設計方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−155184(P2011−155184A)

【公開日】平成23年8月11日(2011.8.11)

【国際特許分類】

【出願番号】特願2010−16576(P2010−16576)

【出願日】平成22年1月28日(2010.1.28)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年8月11日(2011.8.11)

【国際特許分類】

【出願日】平成22年1月28日(2010.1.28)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]