酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。

【発明の詳細な説明】

【技術分野】

【0001】

(関連出願の相互参照)

本出願は、2003年9月26日に申請された米国仮出願第60/506,713号に対する優先権を主張する。

【背景技術】

【0002】

最新の集積回路は、半導体基板内及びその上に形成された、トランジスタ及びキャパシタなどの最大数百万個の能動素子で構成される。能動素子間の相互接続は、多結晶シリコン及び金属などの複数の導電性相互接続層を設けることによって生成され、これらはエッチングされて信号を伝達する導体を形成する。この導電性層及び層間誘電体は、シリコン基板ウェーハ上に連続して堆積され、各層は例えば1ミクロン程度の厚みがある。

【0003】

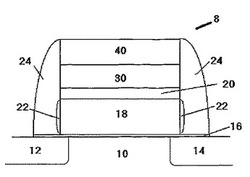

ゲート構造体は、トランジスタの一要素である。図1は、ゲートスタック8の1つの実施例を示す。半導体基板10は、基板内のドープ領域(ソース/ドレイン領域)(12及び14)に重なり合うゲート絶縁層16を支持し、そのゲート絶縁層は通常多結晶シリコンであるゲート18を支持する。ゲート上には金属層30が存在する。金属層は、集合的にバリア層20として示された、窒化物、酸化物、又はケイ化物といった1つ又はそれ以上の他の層によってゲートから分離することができる。次に金属層は、窒化物、酸化物、又はケイ化物といった1つ又はそれ以上の他の層(集合的に40)を支持することができる。酸化物22が、ゲートスタックの下部でゲート酸化物を保護するためにゲートの側部に形成することができ、絶縁スペーサ24はゲートスタックのいずれかの側部に形成することができる。更にまた、基板内のソース/ドレイン領域へのコンタクト、及びゲート構造体へのコンタクトを形成することができる。

【0004】

VLSI技術の継続的なスケーリングでは、必要な漏洩性能を維持しながら厚みが縮小されたゲート誘電体が求められている。二酸化ケイ素は、約25オングストロームの厚みまではこれらの要求を満足していた。この厚みを下回ると、二酸化ケイ素はまず漏洩に関して限界となり、次いで、より優れた性能を求めてPMOSFET用のP+ポリゲートに技術が移行するにつれて厚み制御自体が問題となり、最終的には、ゲート酸化物上のポリシリコンから基板内へのボロン突き抜けの問題が極めて重要な課題となっている。ゲート酸化物をN2O又はNO中でアニールすることによって窒素を導入した(2から3%)窒化SiO2が提案されている。この誘電体は、窒化SiO2の誘電率がやや高いため漏洩に関してより良好であることに起因して、ボロン突き抜けに対し堅牢である。この誘電体は、約22から24オングストローム(物理厚み)にまで縮小することができるが、これを下回ると、漏洩及びボロン突き抜けによりこの誘電体が機能しなくなる。NOアニール処理はまた酸化物厚みを増大させるので、要求厚みで導入することができる窒素量には限界がある。70nm以下のCD(限界寸法、ゲートの幅に対応する)を用いる技術では、ゲート誘電体の厚みは14から16オングストロームETO(等価酸化膜厚)の範囲内でなければならず、これは窒化SiO2では適合することができない。全ての要求に適合する新規な材料が必要とされる。

【0005】

現在の技術では、最初に乾式又は湿式酸化によってSiO2を成長させ、その酸化物を通常NO中において約850℃から900℃で少なくとも15分間アニールし十分な窒素を導入することによって形成された窒化SiO2を用いる。酸化が過度に早く、NO中のアニールがかなりの量の酸化物を成長させるので、厚みを約18オングストローム未満に小さくすることは極めて難しい。また、15から16オングストロームのEOTでは、誘電体は物理的に薄すぎる。この厚みでは、誘電体を通過するトンネル電流が多過ぎて、高い漏洩が生じることになる。薄い誘電体はまた、許容できないボロン突き抜けを生じさせる。より多くの窒素を導入すると、アニールの増大が必要となり、これは要求限界を越えて酸化物の厚みを増大させることになる。

【発明の開示】

【0006】

第1の態様において、本発明は、半導体を製造する方法であって、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大で25オングストロームである。

【0007】

第2の態様において、本発明は、ゲート誘電体を形成する方法であって、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層の厚みが、6−10オングストロームであり、窒化ケイ素層の厚みは、10−30オングストロームである。

【0008】

第3の態様において、本発明は、基板と、基板上の酸化物層と、酸化物層上の窒化ケイ素層とを備える半導体構造体である。酸化物層の厚みは、6−10オングストロームであり、窒化ケイ素層の厚みは、10−30オングストロームである。

【0009】

第4の態様において、本発明は、基板と、基板上の酸化物層と、酸化物層上の窒化ケイ素層とを備える半導体構造体である。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚が、12−25オングストロームである。

【発明を実施するための最良の形態】

【0010】

本発明は、下側層が酸化ケイ素、上側層が窒化ケイ素の二層ゲート誘電体が、13−15オングストローム、14オングストローム、及び20−25オングストロームを含む、好ましくは12−25オングストロームのEOTを有するように製造することができる開示事項を利用するものである。

【0011】

この二重ゲート誘電体は、図11に示される。ゲート絶縁層又は誘電層102は、2つの部分、すなわち酸化ケイ素層104及び窒化ケイ素層103から構成される。ゲート絶縁層102は、基板100上にある。酸化ケイ素層は、7、8及び9オングストロームを含む、6−10オングストロームの厚みを有するのが好ましい。窒化ケイ素層は、11、12、13、14、15、16、17、18、19、20、21、22、23及び24オングストロームを含む、10−30オングストロームの厚みを有するのが好ましい。

【0012】

酸化物層は、フッ化水素酸を用いて基板からどのような自然酸化物をも除去した後、様々な方法で形成することができる。1つの方法は、RCA洗浄を使用すること、また別の方法は、基板をオゾン(O3)を含有する脱イオン水で洗い、約8オングストロームの厚みの酸化物層を形成するものであり、この処理は自然酸化物の除去に続く洗浄処理として行うことができる。別の方法では、任意選択的に窒素又は別の不活性ガスで希釈された低圧(100−200mTorr)酸素を用いて、酸化物層を熱成長させる。更に別の方法では、酸化物層は水蒸気酸化によって形成することができる。

【0013】

酸化物が形成されると、窒化ケイ素層を形成することができる。これは、ジクロロシラン及びアンモニアを好ましくは1:1000から1:3、より好ましくは1:100から1:33、最も好ましくは1:33の比率で用いて、LPCVDにより窒素リッチな窒化ケイ素を形成することで行うことができる。或いは、窒化ケイ素層は、原子層堆積法によってジクロロシラン及びアンモニアから形成することができる。形成されると、該層はNO中800−900℃で15−30分間アニールすることができ、アンモニア中でラピッドサーマルアニール(RTA)により30秒から1分間、又は加熱炉内で5−10分間アニールすることができる。任意選択的に、窒素を用いて、NO及びアンモニアをいずれかのアニール工程で希釈することができる。

【0014】

半導体構造体の他の部分は以下のように形成することができる。

【0015】

図2を参照すると、ゲート絶縁層102は、半導体基板100上に存在する。この半導体基板は、従来から知られている半導体材料とすることができる。半導体材料の実施例としては、シリコン、ヒ化ガリウム、ゲルマニウム、窒化ガリウム、リン化アルミニウム、及びSi1-XGeX及びAlXGa1-XAs(式中0≦x≦1)などの合金が挙げられる。好ましくは、半導体基板はシリコンであり、ドープ又は非ドープとすることができる。

【0016】

図3を参照すると、ゲート層105は、ゲート絶縁層上に形成することができる。ゲート層は、種々の半導体材料を含むことができる。通常、ゲート層は、多結晶シリコン(ポリ)又はアモルファス・シリコンを含む。ゲート層は、1つのタイプのドーパント(P+又はN+)でドープすることができ、又は両方のタイプのドーパントを離散的領域に含むことができる。スプリットゲートは、P+及びN+ドープ領域の両方を含むゲート層である。

【0017】

スプリットゲートの場合、P+ドープされた(B又はBF2+などで)ゲートの領域は、基板のN-ドープ・チャンネル領域の上にあり、PMOSデバイスを形成し、N+ドープされた(As+又はリン+などで)ゲートの領域は、基板のP-ドープ・チャンネル領域の上にあり、NMOSデバイスを形成する。ゲートのP+及びN+ドープ領域は、基板の絶縁領域上にある領域によって分離される。ゲート領域のドープは、好ましくはゲートを形成した後、各領域を別個にマスキング及びドープすることにより、又は1つのドーパントタイプでゲート全体をドープした後マスキングして他のドーパントタイプで1つの領域のみをドープする(カウンタードープ)ことにより行われる。

【0018】

図4を参照すると、バリア層115は、任意選択的にゲート層上に形成することができる。任意選択的なバリア層は、窒化物、ケイ化物、及び酸化物を含む種々の材料を含むことができ、好ましくは導電性材料である。例えば、バリア層は耐火性のケイ化物又は窒化物を含むことができる。好ましくは、バリア層は窒化タングステン又はケイ化タングステンを含む。

【0019】

更に図4を参照すると、金属層125が、ゲート層上、或いは存在する場合にはバリア層115上に形成することができる。好ましくは、金属層は、200−600オングストローム、より好ましくは300−500オングストローム、最も好ましくは325−450オングストロームの厚みを有する。金属層125は、種々の金属含有材料を含むことができる。例えば、金属層は、アルミニウム、銅、タンタル、チタン、タングステン、及びこれらの合金又は化合物を含むことができる。好ましくは、金属層は、タングステン又はチタンを含む。金属層は、例えば、金属の物理蒸着(PVD)、或いは金属ハロゲン化物と水素との混合物の低圧化学蒸着(LPCVD)によって形成することができる。

【0020】

図5を参照すると、化学蒸着(CVD)を含む種々の方法によってエッチング停止層145を金属層の上に形成することができる。好ましくは、エッチング停止層は窒化物層である。より好ましくは、エッチング停止層は、PECVDによって形成された窒化ケイ素である。エッチング停止層は、例えばエッチング停止層の表面がシリコンリッチの窒化ケイ素又は酸窒化ケイ素である、エッチング停止層の表面が反射防止性であるように組成を変化させることができ、この層はまた後続のエッチングの間エッチング停止層を保護するハードマスクとしても機能することができる。或いは、別個の反射防止層(ARC)を形成してもよい。

【0021】

好ましくは、エッチング停止層は、比較的低温で急速に形成される。例えば、ゲート層がP+及びN+ドープ領域の両方を含む場合、ウェーハが長時間にわたって十分高温に維持されるとドーパントの拡散を生じる可能性がある。従って、どのような高温加工も比較的短期間でのみ実施されるのが望ましい。同様に、どのような長期にわたる加工も比較的低温で実施されることが好ましい。実質的に酸素が存在しない雰囲気、或いは還元環境(水素リッチ)であるときには、好ましくは、エッチング停止層は最大750℃の温度で形成される。通常の条件では、最大600℃の温度が好ましく、最大450℃の温度がより好ましい。400℃などの最低でも350℃の温度が好ましい。エッチング停止層の堆積は、スプリットゲートのP+領域とN+領域との間で実質的に拡散が生じない温度及び時間で行われるのが好ましい。

【0022】

図6−9を参照すると、ゲートスタックを形成するよう各層をパターン形成することができる。パターン形成は、例えば、通常のフォトリソグラフィ及びエッチング技法によって行うことができる。図6及び図7を参照すると、例えば、エッチング停止層145上にパターン化されたフォトレジスト210を形成させ(図6)、次いで層の露出部分をエッチングすることにより、エッチング停止層をエッチングしてパターン化されたエッチング停止層150を形成することができる。フッ化水素酸浸漬を用いて、側壁パッシベーションを除去することができる。

【0023】

エッチング停止のエッチングは、ガスの混合物により形成されたプラズマに曝露することで実施できる。好ましくは、ガス及びプラズマは、炭素、フッ素、及び水素を含む。好ましくは、フッ素:水素の原子比率が43:1から13.3、より好ましくは35:1から5:1、最も好ましくは27:1から7:1である。好ましくは、ガスの混合物は、CF4及びCHF3を含み、CF4:CHF3の容積比率は好ましくは10:1から1:3、より好ましくは8:1から1:2、最も好ましくは6:1から1:1である。ガス混合物及びプラズマはまた、He、Ne又はArなどの他のガスを含むことができる。エッチング中の圧力は4mTorrより高く、好ましくは10−80mTorrなどの少なくとも10mTorrであり、より好ましくは15−45mTorrなどの少なくとも15mTorrであり、最も好ましくは25−35mTorrである。

【0024】

パターン化エッチング停止層は、金属層125(図7)をエッチングしてパターン化金属層130(図8)を形成するためのハードマスクとして使用することができる。パターン化エッチング停止層及びパターン化金属層は、ゲート層105(図8)をエッチングしてパターン化ゲート層110(図9)を形成するためのハードマスクとして使用することができる。ゲート層のエッチングは、例えば、塩素、臭化水素酸、及び/又は酸素により形成されるプラズマに曝露することによるなどの、通常のゲートエッチング技法によって実施することができる。

【0025】

パターン化フォトレジスト210(図6)は、エッチング停止層のエッチングに続くゲートスタック形成のどの段階でも除去することができる。例えば、パターン化フォトレジストは、エッチング停止層のエッチング(図6及び図7に示した)の直後に除去することができ、或いは、金属層のエッチング又はゲート層エッチング後に除去することができる。フォトレジストの除去の後に洗浄処理が続き、フォトレジスト又はフォトレジスト除去のどのような残留副生成物を確実に除去することができる。例えば、パターン化フォトレジストを灰化することによりフォトレジストを除去し、パターン化エッチング停止層を含むゲートスタック(図7)を提供することができる。次にフォトレジストの無いこのゲートスタックを洗浄液で処理し、除去及び洗浄処理を完了することができる。最も好ましい洗浄剤は、水、2−(2アミノエトキシ)エタノール、ヒドロキシルアミン、及びカテコールを含有する。洗浄液の実施例はEKC265(登録商標)(EKC、カリフォルニア州ヘイワード)である。

【0026】

図9は、半導体ウェーハ上に形成することができるゲートスタック200を示す。半導体基板100は、ゲート絶縁層102を支持し、該層はゲート層110を支持する。ゲート層は、金属層130を支持し、該層は任意選択的にバリア層120によってゲート層から分離することができる。エッチング停止層150は、金属層130の上に存在する。

【0027】

ゲート構造体の更なる加工は、ゲート層110への側壁酸化物領域170の形成と、スタックの側部へのスペーサ160(好ましくは窒化物を含有する)の形成とを含む。更にまた、図10に示されるように、誘電層180はエッチング停止層上に形成することができ、コンタクト又はバイア190は誘電層から基板まで形成することができる。このバイアは、例えばTiN及びタングステンでそれぞれライニング及び充填し、バイア−コンタクトを形成することができる。他の加工は、ゲート自体へのコンタクト形成を含むことができる。

【0028】

他の加工方法を用いて本半導体構造体による半導体デバイスの形成を完成させることができる。例えば、ソース/ドレイン領域12、14を基板内に形成でき、追加の誘電層を基板上に形成でき、コンタクト及びメタライゼーション層をこれらの構造体上に形成することができる。これらの追加要素は、ゲートスタックの形成の前、形成中、又は形成後に形成することができる。

【0029】

本発明で使用するためのゲートスタック層のエッチングを含む関連加工段階、並びに研磨、洗浄、及び堆積段階などの他の段階は、当業者には周知であり、また、Encyclopedia of Chemical Technology、Kirk−Othmer、Volume14,pp.677−709(1995);Semiconductor Device Fundamentals,Robert F.Pierret,Addison−Wesley,1996;Wolf,Silicon Processing for the VLSI Era,Lattice Press,1986,1990,1995(それぞれvol.1−vol.3)、及びMicrochip Fabrication,4rd edition,Peter Van Zant,McGraw−Hill,2000においても記載されている。

【0030】

本発明の半導体構造体は、例えば、SCRAM、DRAM、EPROM,EEPROM等といったメモリーセル;プログラマブル・ロジック・デバイス;データ通信デバイス;クロック発生デバイスといった集積回路のような半導体デバイス内に組み込むことができる。更にまた、これらの半導体デバイスの何れもが、例えばコンピュータ、航空機、又は自動車の電子デバイスに組み込むことができる。

【0031】

本発明の二重ゲート誘電体を使用することで、SiONよりもやや高い(−0.54対−0.46)PMOSFET用のVt(閾値電圧)を示し、ボロン突き抜けを示さない。図12は、縦軸に漏洩(A/cm2)を示し、横軸にEOT(オングストローム単位)を示すグラフである。このグラフにおいて、「サーマル−NO」は、熱成長させ続いてNO中でアニールした酸化物を有するデバイスを表し、「VTR−NO」は、垂直加熱炉内で熱成長させ続いてNO中でアニールした酸化物であり、O/Nスタックは本発明の二重ゲート誘電体である。

【図面の簡単な説明】

【0032】

【図1】ゲートスタック構造体を示す図である。

【図2】図9の構造体を形成する方法を示す図である。

【図3】図9の構造体を形成する方法を示す図である。

【図4】図9の構造体を形成する方法を示す図である。

【図5】図9の構造体を形成する方法を示す図である。

【図6】図9の構造体を形成する方法を示す図である。

【図7】図9の構造体を形成する方法を示す図である。

【図8】図9の構造体を形成する方法を示す図である。

【図9】本発明のゲートスタックを示す図である。

【図10】追加加工後の図9のゲートスタックを示す図である。

【図11】ゲートスタック誘電体の詳細を示す図である。

【図12】漏洩を示すグラフである。

【符号の説明】

【0033】

8 ゲートスタック

10 半導体基板

12 ソース領域

14 ドレイン領域

16 ゲート絶縁層

18 ゲート

20 バリア層

22 酸化物

24 絶縁スペーサ

30 金属層

40 他の層

【技術分野】

【0001】

(関連出願の相互参照)

本出願は、2003年9月26日に申請された米国仮出願第60/506,713号に対する優先権を主張する。

【背景技術】

【0002】

最新の集積回路は、半導体基板内及びその上に形成された、トランジスタ及びキャパシタなどの最大数百万個の能動素子で構成される。能動素子間の相互接続は、多結晶シリコン及び金属などの複数の導電性相互接続層を設けることによって生成され、これらはエッチングされて信号を伝達する導体を形成する。この導電性層及び層間誘電体は、シリコン基板ウェーハ上に連続して堆積され、各層は例えば1ミクロン程度の厚みがある。

【0003】

ゲート構造体は、トランジスタの一要素である。図1は、ゲートスタック8の1つの実施例を示す。半導体基板10は、基板内のドープ領域(ソース/ドレイン領域)(12及び14)に重なり合うゲート絶縁層16を支持し、そのゲート絶縁層は通常多結晶シリコンであるゲート18を支持する。ゲート上には金属層30が存在する。金属層は、集合的にバリア層20として示された、窒化物、酸化物、又はケイ化物といった1つ又はそれ以上の他の層によってゲートから分離することができる。次に金属層は、窒化物、酸化物、又はケイ化物といった1つ又はそれ以上の他の層(集合的に40)を支持することができる。酸化物22が、ゲートスタックの下部でゲート酸化物を保護するためにゲートの側部に形成することができ、絶縁スペーサ24はゲートスタックのいずれかの側部に形成することができる。更にまた、基板内のソース/ドレイン領域へのコンタクト、及びゲート構造体へのコンタクトを形成することができる。

【0004】

VLSI技術の継続的なスケーリングでは、必要な漏洩性能を維持しながら厚みが縮小されたゲート誘電体が求められている。二酸化ケイ素は、約25オングストロームの厚みまではこれらの要求を満足していた。この厚みを下回ると、二酸化ケイ素はまず漏洩に関して限界となり、次いで、より優れた性能を求めてPMOSFET用のP+ポリゲートに技術が移行するにつれて厚み制御自体が問題となり、最終的には、ゲート酸化物上のポリシリコンから基板内へのボロン突き抜けの問題が極めて重要な課題となっている。ゲート酸化物をN2O又はNO中でアニールすることによって窒素を導入した(2から3%)窒化SiO2が提案されている。この誘電体は、窒化SiO2の誘電率がやや高いため漏洩に関してより良好であることに起因して、ボロン突き抜けに対し堅牢である。この誘電体は、約22から24オングストローム(物理厚み)にまで縮小することができるが、これを下回ると、漏洩及びボロン突き抜けによりこの誘電体が機能しなくなる。NOアニール処理はまた酸化物厚みを増大させるので、要求厚みで導入することができる窒素量には限界がある。70nm以下のCD(限界寸法、ゲートの幅に対応する)を用いる技術では、ゲート誘電体の厚みは14から16オングストロームETO(等価酸化膜厚)の範囲内でなければならず、これは窒化SiO2では適合することができない。全ての要求に適合する新規な材料が必要とされる。

【0005】

現在の技術では、最初に乾式又は湿式酸化によってSiO2を成長させ、その酸化物を通常NO中において約850℃から900℃で少なくとも15分間アニールし十分な窒素を導入することによって形成された窒化SiO2を用いる。酸化が過度に早く、NO中のアニールがかなりの量の酸化物を成長させるので、厚みを約18オングストローム未満に小さくすることは極めて難しい。また、15から16オングストロームのEOTでは、誘電体は物理的に薄すぎる。この厚みでは、誘電体を通過するトンネル電流が多過ぎて、高い漏洩が生じることになる。薄い誘電体はまた、許容できないボロン突き抜けを生じさせる。より多くの窒素を導入すると、アニールの増大が必要となり、これは要求限界を越えて酸化物の厚みを増大させることになる。

【発明の開示】

【0006】

第1の態様において、本発明は、半導体を製造する方法であって、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大で25オングストロームである。

【0007】

第2の態様において、本発明は、ゲート誘電体を形成する方法であって、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層の厚みが、6−10オングストロームであり、窒化ケイ素層の厚みは、10−30オングストロームである。

【0008】

第3の態様において、本発明は、基板と、基板上の酸化物層と、酸化物層上の窒化ケイ素層とを備える半導体構造体である。酸化物層の厚みは、6−10オングストロームであり、窒化ケイ素層の厚みは、10−30オングストロームである。

【0009】

第4の態様において、本発明は、基板と、基板上の酸化物層と、酸化物層上の窒化ケイ素層とを備える半導体構造体である。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚が、12−25オングストロームである。

【発明を実施するための最良の形態】

【0010】

本発明は、下側層が酸化ケイ素、上側層が窒化ケイ素の二層ゲート誘電体が、13−15オングストローム、14オングストローム、及び20−25オングストロームを含む、好ましくは12−25オングストロームのEOTを有するように製造することができる開示事項を利用するものである。

【0011】

この二重ゲート誘電体は、図11に示される。ゲート絶縁層又は誘電層102は、2つの部分、すなわち酸化ケイ素層104及び窒化ケイ素層103から構成される。ゲート絶縁層102は、基板100上にある。酸化ケイ素層は、7、8及び9オングストロームを含む、6−10オングストロームの厚みを有するのが好ましい。窒化ケイ素層は、11、12、13、14、15、16、17、18、19、20、21、22、23及び24オングストロームを含む、10−30オングストロームの厚みを有するのが好ましい。

【0012】

酸化物層は、フッ化水素酸を用いて基板からどのような自然酸化物をも除去した後、様々な方法で形成することができる。1つの方法は、RCA洗浄を使用すること、また別の方法は、基板をオゾン(O3)を含有する脱イオン水で洗い、約8オングストロームの厚みの酸化物層を形成するものであり、この処理は自然酸化物の除去に続く洗浄処理として行うことができる。別の方法では、任意選択的に窒素又は別の不活性ガスで希釈された低圧(100−200mTorr)酸素を用いて、酸化物層を熱成長させる。更に別の方法では、酸化物層は水蒸気酸化によって形成することができる。

【0013】

酸化物が形成されると、窒化ケイ素層を形成することができる。これは、ジクロロシラン及びアンモニアを好ましくは1:1000から1:3、より好ましくは1:100から1:33、最も好ましくは1:33の比率で用いて、LPCVDにより窒素リッチな窒化ケイ素を形成することで行うことができる。或いは、窒化ケイ素層は、原子層堆積法によってジクロロシラン及びアンモニアから形成することができる。形成されると、該層はNO中800−900℃で15−30分間アニールすることができ、アンモニア中でラピッドサーマルアニール(RTA)により30秒から1分間、又は加熱炉内で5−10分間アニールすることができる。任意選択的に、窒素を用いて、NO及びアンモニアをいずれかのアニール工程で希釈することができる。

【0014】

半導体構造体の他の部分は以下のように形成することができる。

【0015】

図2を参照すると、ゲート絶縁層102は、半導体基板100上に存在する。この半導体基板は、従来から知られている半導体材料とすることができる。半導体材料の実施例としては、シリコン、ヒ化ガリウム、ゲルマニウム、窒化ガリウム、リン化アルミニウム、及びSi1-XGeX及びAlXGa1-XAs(式中0≦x≦1)などの合金が挙げられる。好ましくは、半導体基板はシリコンであり、ドープ又は非ドープとすることができる。

【0016】

図3を参照すると、ゲート層105は、ゲート絶縁層上に形成することができる。ゲート層は、種々の半導体材料を含むことができる。通常、ゲート層は、多結晶シリコン(ポリ)又はアモルファス・シリコンを含む。ゲート層は、1つのタイプのドーパント(P+又はN+)でドープすることができ、又は両方のタイプのドーパントを離散的領域に含むことができる。スプリットゲートは、P+及びN+ドープ領域の両方を含むゲート層である。

【0017】

スプリットゲートの場合、P+ドープされた(B又はBF2+などで)ゲートの領域は、基板のN-ドープ・チャンネル領域の上にあり、PMOSデバイスを形成し、N+ドープされた(As+又はリン+などで)ゲートの領域は、基板のP-ドープ・チャンネル領域の上にあり、NMOSデバイスを形成する。ゲートのP+及びN+ドープ領域は、基板の絶縁領域上にある領域によって分離される。ゲート領域のドープは、好ましくはゲートを形成した後、各領域を別個にマスキング及びドープすることにより、又は1つのドーパントタイプでゲート全体をドープした後マスキングして他のドーパントタイプで1つの領域のみをドープする(カウンタードープ)ことにより行われる。

【0018】

図4を参照すると、バリア層115は、任意選択的にゲート層上に形成することができる。任意選択的なバリア層は、窒化物、ケイ化物、及び酸化物を含む種々の材料を含むことができ、好ましくは導電性材料である。例えば、バリア層は耐火性のケイ化物又は窒化物を含むことができる。好ましくは、バリア層は窒化タングステン又はケイ化タングステンを含む。

【0019】

更に図4を参照すると、金属層125が、ゲート層上、或いは存在する場合にはバリア層115上に形成することができる。好ましくは、金属層は、200−600オングストローム、より好ましくは300−500オングストローム、最も好ましくは325−450オングストロームの厚みを有する。金属層125は、種々の金属含有材料を含むことができる。例えば、金属層は、アルミニウム、銅、タンタル、チタン、タングステン、及びこれらの合金又は化合物を含むことができる。好ましくは、金属層は、タングステン又はチタンを含む。金属層は、例えば、金属の物理蒸着(PVD)、或いは金属ハロゲン化物と水素との混合物の低圧化学蒸着(LPCVD)によって形成することができる。

【0020】

図5を参照すると、化学蒸着(CVD)を含む種々の方法によってエッチング停止層145を金属層の上に形成することができる。好ましくは、エッチング停止層は窒化物層である。より好ましくは、エッチング停止層は、PECVDによって形成された窒化ケイ素である。エッチング停止層は、例えばエッチング停止層の表面がシリコンリッチの窒化ケイ素又は酸窒化ケイ素である、エッチング停止層の表面が反射防止性であるように組成を変化させることができ、この層はまた後続のエッチングの間エッチング停止層を保護するハードマスクとしても機能することができる。或いは、別個の反射防止層(ARC)を形成してもよい。

【0021】

好ましくは、エッチング停止層は、比較的低温で急速に形成される。例えば、ゲート層がP+及びN+ドープ領域の両方を含む場合、ウェーハが長時間にわたって十分高温に維持されるとドーパントの拡散を生じる可能性がある。従って、どのような高温加工も比較的短期間でのみ実施されるのが望ましい。同様に、どのような長期にわたる加工も比較的低温で実施されることが好ましい。実質的に酸素が存在しない雰囲気、或いは還元環境(水素リッチ)であるときには、好ましくは、エッチング停止層は最大750℃の温度で形成される。通常の条件では、最大600℃の温度が好ましく、最大450℃の温度がより好ましい。400℃などの最低でも350℃の温度が好ましい。エッチング停止層の堆積は、スプリットゲートのP+領域とN+領域との間で実質的に拡散が生じない温度及び時間で行われるのが好ましい。

【0022】

図6−9を参照すると、ゲートスタックを形成するよう各層をパターン形成することができる。パターン形成は、例えば、通常のフォトリソグラフィ及びエッチング技法によって行うことができる。図6及び図7を参照すると、例えば、エッチング停止層145上にパターン化されたフォトレジスト210を形成させ(図6)、次いで層の露出部分をエッチングすることにより、エッチング停止層をエッチングしてパターン化されたエッチング停止層150を形成することができる。フッ化水素酸浸漬を用いて、側壁パッシベーションを除去することができる。

【0023】

エッチング停止のエッチングは、ガスの混合物により形成されたプラズマに曝露することで実施できる。好ましくは、ガス及びプラズマは、炭素、フッ素、及び水素を含む。好ましくは、フッ素:水素の原子比率が43:1から13.3、より好ましくは35:1から5:1、最も好ましくは27:1から7:1である。好ましくは、ガスの混合物は、CF4及びCHF3を含み、CF4:CHF3の容積比率は好ましくは10:1から1:3、より好ましくは8:1から1:2、最も好ましくは6:1から1:1である。ガス混合物及びプラズマはまた、He、Ne又はArなどの他のガスを含むことができる。エッチング中の圧力は4mTorrより高く、好ましくは10−80mTorrなどの少なくとも10mTorrであり、より好ましくは15−45mTorrなどの少なくとも15mTorrであり、最も好ましくは25−35mTorrである。

【0024】

パターン化エッチング停止層は、金属層125(図7)をエッチングしてパターン化金属層130(図8)を形成するためのハードマスクとして使用することができる。パターン化エッチング停止層及びパターン化金属層は、ゲート層105(図8)をエッチングしてパターン化ゲート層110(図9)を形成するためのハードマスクとして使用することができる。ゲート層のエッチングは、例えば、塩素、臭化水素酸、及び/又は酸素により形成されるプラズマに曝露することによるなどの、通常のゲートエッチング技法によって実施することができる。

【0025】

パターン化フォトレジスト210(図6)は、エッチング停止層のエッチングに続くゲートスタック形成のどの段階でも除去することができる。例えば、パターン化フォトレジストは、エッチング停止層のエッチング(図6及び図7に示した)の直後に除去することができ、或いは、金属層のエッチング又はゲート層エッチング後に除去することができる。フォトレジストの除去の後に洗浄処理が続き、フォトレジスト又はフォトレジスト除去のどのような残留副生成物を確実に除去することができる。例えば、パターン化フォトレジストを灰化することによりフォトレジストを除去し、パターン化エッチング停止層を含むゲートスタック(図7)を提供することができる。次にフォトレジストの無いこのゲートスタックを洗浄液で処理し、除去及び洗浄処理を完了することができる。最も好ましい洗浄剤は、水、2−(2アミノエトキシ)エタノール、ヒドロキシルアミン、及びカテコールを含有する。洗浄液の実施例はEKC265(登録商標)(EKC、カリフォルニア州ヘイワード)である。

【0026】

図9は、半導体ウェーハ上に形成することができるゲートスタック200を示す。半導体基板100は、ゲート絶縁層102を支持し、該層はゲート層110を支持する。ゲート層は、金属層130を支持し、該層は任意選択的にバリア層120によってゲート層から分離することができる。エッチング停止層150は、金属層130の上に存在する。

【0027】

ゲート構造体の更なる加工は、ゲート層110への側壁酸化物領域170の形成と、スタックの側部へのスペーサ160(好ましくは窒化物を含有する)の形成とを含む。更にまた、図10に示されるように、誘電層180はエッチング停止層上に形成することができ、コンタクト又はバイア190は誘電層から基板まで形成することができる。このバイアは、例えばTiN及びタングステンでそれぞれライニング及び充填し、バイア−コンタクトを形成することができる。他の加工は、ゲート自体へのコンタクト形成を含むことができる。

【0028】

他の加工方法を用いて本半導体構造体による半導体デバイスの形成を完成させることができる。例えば、ソース/ドレイン領域12、14を基板内に形成でき、追加の誘電層を基板上に形成でき、コンタクト及びメタライゼーション層をこれらの構造体上に形成することができる。これらの追加要素は、ゲートスタックの形成の前、形成中、又は形成後に形成することができる。

【0029】

本発明で使用するためのゲートスタック層のエッチングを含む関連加工段階、並びに研磨、洗浄、及び堆積段階などの他の段階は、当業者には周知であり、また、Encyclopedia of Chemical Technology、Kirk−Othmer、Volume14,pp.677−709(1995);Semiconductor Device Fundamentals,Robert F.Pierret,Addison−Wesley,1996;Wolf,Silicon Processing for the VLSI Era,Lattice Press,1986,1990,1995(それぞれvol.1−vol.3)、及びMicrochip Fabrication,4rd edition,Peter Van Zant,McGraw−Hill,2000においても記載されている。

【0030】

本発明の半導体構造体は、例えば、SCRAM、DRAM、EPROM,EEPROM等といったメモリーセル;プログラマブル・ロジック・デバイス;データ通信デバイス;クロック発生デバイスといった集積回路のような半導体デバイス内に組み込むことができる。更にまた、これらの半導体デバイスの何れもが、例えばコンピュータ、航空機、又は自動車の電子デバイスに組み込むことができる。

【0031】

本発明の二重ゲート誘電体を使用することで、SiONよりもやや高い(−0.54対−0.46)PMOSFET用のVt(閾値電圧)を示し、ボロン突き抜けを示さない。図12は、縦軸に漏洩(A/cm2)を示し、横軸にEOT(オングストローム単位)を示すグラフである。このグラフにおいて、「サーマル−NO」は、熱成長させ続いてNO中でアニールした酸化物を有するデバイスを表し、「VTR−NO」は、垂直加熱炉内で熱成長させ続いてNO中でアニールした酸化物であり、O/Nスタックは本発明の二重ゲート誘電体である。

【図面の簡単な説明】

【0032】

【図1】ゲートスタック構造体を示す図である。

【図2】図9の構造体を形成する方法を示す図である。

【図3】図9の構造体を形成する方法を示す図である。

【図4】図9の構造体を形成する方法を示す図である。

【図5】図9の構造体を形成する方法を示す図である。

【図6】図9の構造体を形成する方法を示す図である。

【図7】図9の構造体を形成する方法を示す図である。

【図8】図9の構造体を形成する方法を示す図である。

【図9】本発明のゲートスタックを示す図である。

【図10】追加加工後の図9のゲートスタックを示す図である。

【図11】ゲートスタック誘電体の詳細を示す図である。

【図12】漏洩を示すグラフである。

【符号の説明】

【0033】

8 ゲートスタック

10 半導体基板

12 ソース領域

14 ドレイン領域

16 ゲート絶縁層

18 ゲート

20 バリア層

22 酸化物

24 絶縁スペーサ

30 金属層

40 他の層

【特許請求の範囲】

【請求項1】

半導体構造体を製造する方法であって、

基板上に酸化物層を形成する段階と、

前記酸化物層上に窒化ケイ素層を形成する段階と、

前記各層をNO中でアニールする段階と、

前記各層をアンモニア中でアニールする段階と、

を含み、

前記酸化物層と前記窒化ケイ素層とを併せた等価酸化膜厚が最大で25オングストロームであることを特徴とする方法。

【請求項2】

前記酸化物層の厚みが、6−10オングストロームであることを特徴とする請求項1に記載の方法。

【請求項3】

前記窒化ケイ素層の厚みが、10−30オングストロームであることを特徴とする請求項1に記載の方法。

【請求項4】

前記酸化物層を形成する段階が、前記基板をオゾンを含有する脱イオン水で洗う段階を含む請求項1に記載の方法。

【請求項5】

前記酸化物層を形成する段階が、水蒸気酸化する段階を含む請求項1に記載の方法。

【請求項6】

前記酸化物層を形成する段階が、酸素を用いて前記酸化物層を熱成長させる段階を含む請求項1に記載の方法。

【請求項7】

前記窒化ケイ素層を形成する段階が、LPCVDによって前記窒化ケイ素層を堆積させる段階を含む請求項1に記載の方法。

【請求項8】

前記NO中のアニールが、800−900℃の温度で15−30分間行われることを特徴とする請求項1に記載の方法。

【請求項9】

前記アンモニア中のアニールが、900℃の温度で0.5−1.0分間ラピッドサーマルアニールによって行われることを特徴とする請求項1に記載の方法。

【請求項10】

前記アンモニア中のアニールが、900℃の温度で5−10分間加熱炉内で行われることを特徴とする請求項1に記載の方法。

【請求項11】

前記半導体構造体が、ゲート誘電体であることを特徴とする請求項1に記載の方法。

【請求項12】

電子デバイスを製造する方法であって、

請求項1に記載の方法によって半導体デバイスを形成する段階と、

前記半導体デバイスを備える電子デバイスを形成する段階と、

を含む方法。

【請求項13】

電子デバイスを作製する方法であって、

請求項12に記載の方法によって半導体デバイスを形成する段階と、

前記半導体デバイスを備える電子デバイスを形成する段階と、

を含む方法。

【請求項14】

ゲート誘電体を形成する方法であって、

基板上に酸化物層を形成する段階と、

前記酸化物層上に窒化ケイ素層を形成する段階と、

前記各層をNO及びアンモニア中でアニールする段階と、

を含み、

前記酸化物層の厚みが6−10オングストロームであり、前記窒化ケイ素層の厚みが10−30オングストロームであることを特徴とする方法。

【請求項15】

半導体構造体であって、

基板と、

前記基板上にある酸化物層と、

前記酸化物層上にある窒化ケイ素層と、

を備え、

前記酸化物層の厚みが6−10オングストロームであり、前記窒化ケイ素層の厚みが10−30オングストロームであることを特徴とする半導体構造体。

【請求項16】

前記酸化物層と前記窒化ケイ素層とを併せた等価酸化膜厚が、12−25オングストロームであることを特徴とする請求項15に記載の半導体構造体。

【請求項17】

前記窒化ケイ素層の上にポリシリコン層を更に備えることを特徴とする請求項15に記載の半導体構造体。

【請求項18】

前記ポリシリコン層上にある金属層と、

前記金属層上にあるエッチング停止層と、

更に備えることを特徴とする請求項17に記載の半導体構造体。

【請求項19】

半導体構造体であって、

基板と、

前記基板上にある酸化物層と、

前記酸化物層上にある窒化ケイ素層と、

を備え、

前記酸化物層と前記窒化ケイ素層とを併せた等価酸化膜厚が、12−25オングストロームであることを特徴とする半導体構造体。

【請求項20】

前記酸化物層の厚みが、6−10オングストロームであることを特徴とする請求項19に記載の半導体構造体。

【請求項21】

前記窒化ケイ素層の厚みが、10−30オングストロームであることを特徴とする請求項19に記載の半導体構造体。

【請求項22】

前記窒化ケイ素層上にあるポリシリコン層を更に備えることを特徴とする請求項19に記載の半導体構造体。

【請求項23】

前記ポリシリコン層上にある金属層と、

前記金属層上にあるエッチング停止層と、

を更に備えることを特徴とする請求項22に記載の半導体構造体。

【請求項24】

前記ポリシリコン層が、45−110nmの幅を有するゲートであることを特徴とする請求項22に記載の半導体構造体。

【請求項25】

前記ポリシリコン層が、最大70nmまでの幅を有するゲートであることを特徴とする請求項22に記載の半導体構造体。

【請求項1】

半導体構造体を製造する方法であって、

基板上に酸化物層を形成する段階と、

前記酸化物層上に窒化ケイ素層を形成する段階と、

前記各層をNO中でアニールする段階と、

前記各層をアンモニア中でアニールする段階と、

を含み、

前記酸化物層と前記窒化ケイ素層とを併せた等価酸化膜厚が最大で25オングストロームであることを特徴とする方法。

【請求項2】

前記酸化物層の厚みが、6−10オングストロームであることを特徴とする請求項1に記載の方法。

【請求項3】

前記窒化ケイ素層の厚みが、10−30オングストロームであることを特徴とする請求項1に記載の方法。

【請求項4】

前記酸化物層を形成する段階が、前記基板をオゾンを含有する脱イオン水で洗う段階を含む請求項1に記載の方法。

【請求項5】

前記酸化物層を形成する段階が、水蒸気酸化する段階を含む請求項1に記載の方法。

【請求項6】

前記酸化物層を形成する段階が、酸素を用いて前記酸化物層を熱成長させる段階を含む請求項1に記載の方法。

【請求項7】

前記窒化ケイ素層を形成する段階が、LPCVDによって前記窒化ケイ素層を堆積させる段階を含む請求項1に記載の方法。

【請求項8】

前記NO中のアニールが、800−900℃の温度で15−30分間行われることを特徴とする請求項1に記載の方法。

【請求項9】

前記アンモニア中のアニールが、900℃の温度で0.5−1.0分間ラピッドサーマルアニールによって行われることを特徴とする請求項1に記載の方法。

【請求項10】

前記アンモニア中のアニールが、900℃の温度で5−10分間加熱炉内で行われることを特徴とする請求項1に記載の方法。

【請求項11】

前記半導体構造体が、ゲート誘電体であることを特徴とする請求項1に記載の方法。

【請求項12】

電子デバイスを製造する方法であって、

請求項1に記載の方法によって半導体デバイスを形成する段階と、

前記半導体デバイスを備える電子デバイスを形成する段階と、

を含む方法。

【請求項13】

電子デバイスを作製する方法であって、

請求項12に記載の方法によって半導体デバイスを形成する段階と、

前記半導体デバイスを備える電子デバイスを形成する段階と、

を含む方法。

【請求項14】

ゲート誘電体を形成する方法であって、

基板上に酸化物層を形成する段階と、

前記酸化物層上に窒化ケイ素層を形成する段階と、

前記各層をNO及びアンモニア中でアニールする段階と、

を含み、

前記酸化物層の厚みが6−10オングストロームであり、前記窒化ケイ素層の厚みが10−30オングストロームであることを特徴とする方法。

【請求項15】

半導体構造体であって、

基板と、

前記基板上にある酸化物層と、

前記酸化物層上にある窒化ケイ素層と、

を備え、

前記酸化物層の厚みが6−10オングストロームであり、前記窒化ケイ素層の厚みが10−30オングストロームであることを特徴とする半導体構造体。

【請求項16】

前記酸化物層と前記窒化ケイ素層とを併せた等価酸化膜厚が、12−25オングストロームであることを特徴とする請求項15に記載の半導体構造体。

【請求項17】

前記窒化ケイ素層の上にポリシリコン層を更に備えることを特徴とする請求項15に記載の半導体構造体。

【請求項18】

前記ポリシリコン層上にある金属層と、

前記金属層上にあるエッチング停止層と、

更に備えることを特徴とする請求項17に記載の半導体構造体。

【請求項19】

半導体構造体であって、

基板と、

前記基板上にある酸化物層と、

前記酸化物層上にある窒化ケイ素層と、

を備え、

前記酸化物層と前記窒化ケイ素層とを併せた等価酸化膜厚が、12−25オングストロームであることを特徴とする半導体構造体。

【請求項20】

前記酸化物層の厚みが、6−10オングストロームであることを特徴とする請求項19に記載の半導体構造体。

【請求項21】

前記窒化ケイ素層の厚みが、10−30オングストロームであることを特徴とする請求項19に記載の半導体構造体。

【請求項22】

前記窒化ケイ素層上にあるポリシリコン層を更に備えることを特徴とする請求項19に記載の半導体構造体。

【請求項23】

前記ポリシリコン層上にある金属層と、

前記金属層上にあるエッチング停止層と、

を更に備えることを特徴とする請求項22に記載の半導体構造体。

【請求項24】

前記ポリシリコン層が、45−110nmの幅を有するゲートであることを特徴とする請求項22に記載の半導体構造体。

【請求項25】

前記ポリシリコン層が、最大70nmまでの幅を有するゲートであることを特徴とする請求項22に記載の半導体構造体。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公表番号】特表2007−507112(P2007−507112A)

【公表日】平成19年3月22日(2007.3.22)

【国際特許分類】

【出願番号】特願2006−528273(P2006−528273)

【出願日】平成16年9月24日(2004.9.24)

【国際出願番号】PCT/US2004/031541

【国際公開番号】WO2005/031833

【国際公開日】平成17年4月7日(2005.4.7)

【出願人】(301020237)サイプレス セミコンダクター コーポレイション (18)

【Fターム(参考)】

【公表日】平成19年3月22日(2007.3.22)

【国際特許分類】

【出願日】平成16年9月24日(2004.9.24)

【国際出願番号】PCT/US2004/031541

【国際公開番号】WO2005/031833

【国際公開日】平成17年4月7日(2005.4.7)

【出願人】(301020237)サイプレス セミコンダクター コーポレイション (18)

【Fターム(参考)】

[ Back to top ]