酸化物半導体電界効果型トランジスタ及びその製造方法

【課題】移動度が高く、S値の低い電界効果型トランジスタの提供を目的とする。また、低温又は短時間の熱履歴でも高い特性の得られる電界効果型トランジスタの製造方法の提供を目的とする。

【解決手段】In元素及びZn元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【解決手段】In元素及びZn元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、酸化物半導体膜をチャンネル層に用いた電界効果型トランジスタ、及びその製造方法に関する。

【背景技術】

【0002】

薄膜トランジスタ(TFT)等の電界効果型トランジスタは、半導体メモリ集積回路の単位電子素子、高周波信号増幅素子、液晶駆動用素子等として広く用いられており、現在、最も多く実用されている電子デバイスである。

なかでも、近年における表示装置のめざましい発展に伴い、液晶表示装置(LCD)、エレクトロルミネッセンス表示装置(EL)、フィールドエミッションディスプレイ(FED)等の各種の表示装置において、表示素子に駆動電圧を印加して表示装置を駆動させるスイッチング素子として、TFTが多用されている。

【0003】

電界効果型トランジスタの主要部材である半導体層(チャンネル層)の材料としては、シリコン半導体化合物が最も広く用いられている。一般に、高速動作が必要な高周波増幅素子や集積回路用素子等には、シリコン単結晶が用いられている。一方、液晶駆動用素子等には、大面積化の要求から非晶性シリコン半導体(アモルファスシリコン)が用いられている。

【0004】

例えば、TFTとして、ガラス等の基板上にゲ−ト電極、ゲ−ト絶縁層、水素化アモルファスシリコン(a−Si:H)等の半導体層、ソ−ス及びドレイン電極を積層した逆スタガ構造のものがある。このTFTは、イメ−ジセンサを始め、大面積デバイスの分野において、アクティブマトリスク型の液晶ディスプレイに代表されるフラットパネルディスプレイ等の駆動素子として用いられている。これらの用途では、従来アモルファスシリコンを用いたものでも高機能化に伴い作動の高速化が求められている。

【0005】

現在、表示装置を駆動させるスイッチング素子としては、シリコン系の半導体膜を用いた素子が主流を占めているが、それは、シリコン薄膜の安定性、加工性の良さの他、スイッチング速度が速い等、種々の性能が良好なためである。そして、このようなシリコン系薄膜は、一般に化学蒸気析出法(CVD)法により製造されている。

【0006】

ところで、結晶性のシリコン系薄膜は、結晶化を図る際に、例えば、800℃以上の高温が必要となり、ガラス基板上や有機物基板上への構成が困難である。このため、シリコンウェハーや石英等の耐熱性の高い高価な基板上にしか形成できず、また、製造に際して多大なエネルギーと工程数を要する等の問題があった。

また、結晶性のシリコン系薄膜は、通常TFTの素子構成がトップゲート構成に限定されるためマスク枚数の削減等コストダウンが困難であった。

【0007】

一方、アモルファスシリコンの薄膜は、比較的低温で形成できるものの、結晶性のものに比べてスイッチング速度が遅いため、表示装置を駆動するスイッチング素子として使用したときに、高速な動画の表示に追従できない場合がある。

また、半導体活性層に可視光が照射されると導電性を示し、漏れ電流が発生して誤動作のおそれがある等、スイッチング素子としての特性が劣化するという問題もある。そのため、可視光を遮断する遮光層を設ける方法が知られている。例えば、遮光層としては金属薄膜が用いられている。

しかしながら、金属薄膜からなる遮光層を設けると工程が増えるだけでなく、浮遊電位を持つこととなるので、遮光層をグランドレベルにする必要があり、その場合にも寄生容量が発生するという問題がある。

【0008】

具体的に、解像度がVGAである液晶テレビでは、移動度が0.5〜1cm2/Vsのアモルファスシリコンが使用可能であったが、解像度がSXGA、UXGA、QXGAあるいはそれ以上になると2cm2/Vs以上の移動度が要求される。また、画質を向上させるため駆動周波数を上げるとさらに高い移動度が必要となる。

また、有機ELディスプレイでは電流駆動となるため、DCストレスにより特性が変化するアモルファスシリコンを使用すると長時間の使用により画質が低下するという問題があった。

その他、これらの用途に結晶シリコンを使用すると、大面積に対応できなかったり、高温の熱処理が必要なため製造コストが高くなるという問題があった。

【0009】

このような状況下、近年にあっては、シリコン系半導体薄膜よりも安定性が優れるものとして、酸化物を用いた酸化物半導体薄膜が注目されている。

例えば、特許文献1には半導体層として酸化亜鉛を使用したTFTが記載されている。

しかしながら、この半導体層では電界効果移動度が1cm2/V・sec程度と低く、on−off比も小さかった。その上、漏れ電流が発生しやすいため、工業的には実用化が困難であった。また、酸化亜鉛を用いた結晶質を含む酸化物半導体については、多数の検討がなされているが、工業的に一般に行われているスパッタリング法で成膜した場合には、次のような問題があった。

【0010】

即ち、移動度が低い、on−off比が低い、漏れ電流が大きい、ピンチオフが不明瞭、ノーマリーオンになりやすい等、TFTの性能が低くなるおそれがあった。また、耐薬品性が劣るため、ウェットエッチングが難しい等製造プロセスや使用環境の制限があった。さらに、性能を上げるためには高い圧力で成膜する必要があり成膜速度が遅かったり、700℃以上の高温処理が必要である等工業化に問題もあった。また、ボトムゲート構成での電解移動度等のTFT性能が低く、性能を上げるにはトップゲート構成で膜厚を50nm以上にする必要がある等TFT素子構成上の制限もあった。

【0011】

このような問題を解決するために酸化インジウム、酸化亜鉛からなる非晶質の酸化物半導体膜を作製し、薄膜トランジスタを駆動させる方法が検討されている(特許文献2)。しかしながら、このトランジスタでは、性能が不十分であった。また、この酸化物半導体膜を用いた薄膜トランジスタでは、S値を小さく押さえたり、ストレスによる閾値シフトを小さくために、相応の熱履歴(例えば、300℃以上の高温で1時間以上熱処理する等)をかけることが必要であった(非特許文献1)。そのため、移動度が低く、S値が大きいという問題の他に、液晶ディスプレイや有機ELディスプレイ等のTFTとして用いる場合には、耐熱性の高い基板を用いる必要があった。従って、安価なガラス基板によるコストダウンや、基板の樹脂化によるフレキシブルディスプレイの工業化が困難であった。

【0012】

また、酸化インジウム、酸化亜鉛、酸化ガリウムからなる非晶質の酸化物半導体膜を作製し、薄膜トランジスタを駆動させる方法が検討されている(特許文献3、4)。しかしながら、ターゲットの抵抗を下げることやターゲットの密度を上げることが難しく、ターゲットが破損しやすかったり、DCスパッタリング法を用いることが難しかった。また、具体的な検討はガリウムを多量に含まれたものでなされており、アルミニウムを含むものについて検討はされていなかった。従来のガリウムを多量に含んだ半導体層では、S値が大きく、耐熱性が低く、ストレスによる閾値シフトが大きいという問題があった。

【0013】

一方、インジウム及び亜鉛と、アルミニウム等の元素を含む複合酸化物が、透明導電膜として検討されている(特許文献5、非特許文献2参照)。しかしながら、キャリア密度が高くトランジスタとして利用可能なものではなかった。

【特許文献1】特開2003−86808号公報

【特許文献2】US2005/0199959

【特許文献3】特開2007−73701号公報

【特許文献4】特開2007−73312号公報

【特許文献5】特開2000−44236号公報

【非特許文献1】Kim, Chang Jung et al. Highly Stable Ga2O3−In2O3−ZnO TFT for Active−Matrix Organic Light−Emitting Diode Display Application, Electron Devices Meeting, 2006. IEDM ’06. International(ISBN:1−4244−0439−8)

【非特許文献2】K.Tomonaga etal.,J.Vac.Sci.Technol.A23(3),2005,401

【発明の概要】

【発明が解決しようとする課題】

【0014】

本発明は、上記の事情に鑑みなされたものであり、移動度が高く、S値の低い電界効果型トランジスタの提供を目的とする。

また、低温又は短時間の熱履歴でも高い特性の得られる電界効果型トランジスタの製造方法の提供を目的とする。

【課題を解決するための手段】

【0015】

本発明によれば、以下の電界効果型トランジスタ等が提供される。

In元素及びZn元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【0016】

本発明は元素Xの種類により、以下の2つの態様に分けられる。

・本発明の第一の態様

1.In(インジウム)元素及びZn(亜鉛)元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr及びNbからなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

2.前記元素XがZrである1に記載の電界効果型トランジスタ。

3.前記半導体層が非晶質膜であり、その電子キャリア濃度が1013〜1018/cm3であり、バンドギャップが2.0〜6.0eVである1又は2に記載の電界効果型トランジスタ。

4.前記半導体層が非縮退半導体である1〜3のいずれかに記載の電界効果型トランジスタ。

5.In(インジウム)元素及びZn(亜鉛)元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr及びNbからなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層用ターゲット。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

6.上記5に記載のターゲットを用いて、DC又はACスパッタリングにより半導体層を成膜する工程と、前記半導体層を70〜350℃で熱処理する工程を含む、電界効果型トランジスタの製造方法。

【0017】

・本発明の第二の態様

1.In(インジウム)元素及びZn(亜鉛)元素と、Al(アルミニウム)、B(ホウ素)、Sc(スカンジウム)、Y(イットリウム)及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

2.複合酸化物からなる半導体層が元素Xを下記(2)’の原子比で含むことを特徴とする1の電界効果型トランジスタ。

In/(In+X)=0.59〜0.99 (2)’

3.前記元素Xが、Al又はBである1又は2に記載の電界効果型トランジスタ。

4.前記元素Xが、Sc又はYである1又は2に記載の電界効果型トランジスタ。

5.前記元素Xが、ランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)である1又は2に記載の電界効果型トランジスタ。

6.前記半導体層が非晶質膜であり、その電子キャリア濃度が1013〜1018/cm3であり、バンドギャップが2.0〜6.0eVである1〜5のいずれかに記載の電界効果型トランジスタ。

7.前記半導体層が、非縮退半導体である1〜6のいずれかに記載の電界効果型トランジスタ。

8.In(インジウム)元素及びZn(亜鉛)元素と、Al(アルミニウム)、B(ホウ素)、Sc(スカンジウム)、Y(イットリウム)及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群から選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層用ターゲット。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

9.さらに、Sn(錫)、Ge(ゲルマニウム)、Si(シリコン)、Ti(チタン)、Zr(ジルコニウム)及びHf(ハフニウム)からなる群より選択される1以上の元素を100〜10000原子ppm含む8に記載の半導体層用ターゲット。

10.上記8又は9に記載のターゲットを用いて、DC又はACスパッタリングにより半導体層を成膜する工程と、前記半導体層を70〜350℃で熱処理する工程を含む、電界効果型トランジスタの製造方法。

【発明の効果】

【0018】

本発明によれば、移動度が高く、S値の低い電界効果型トランジスタが得られる。また、低温又は短時間の熱履歴で電界効果型トランジスタを製造することができる。

【図面の簡単な説明】

【0019】

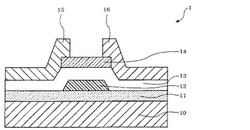

【図1】本発明の一実施形態の電界効果型トランジスタの概略断面図である。

【図2】電界効果型トランジスタ1の概略上面図である。

【図3】本発明の他の実施形態の電界効果型トランジスタの概略断面図である。

【図4】本発明の他の実施形態の電界効果型トランジスタの概略断面図である。

【図5】本発明の他の実施形態の電界効果型トランジスタの概略断面図である。

【図6】半導体層の熱処理温度と移動度の関係を示すグラフである。

【図7】半導体層の熱処理温度と移動度の関係を示すグラフである。

【発明を実施するための形態】

【0020】

[本発明の第一の態様]

本発明の電界効果型トランジスタは、In(インジウム)元素及びZn(亜鉛)元素と、下記の群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する。

群:Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr及びNb

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【0021】

半導体層を上記の複合酸化物から形成することによって、移動度が高く、S値の低い電界効果型トランジスタが得られる。また、低温又は短時間の熱履歴(熱処理)でも、高い特性の得られる電界効果型トランジスタとなる。

【0022】

上記(1)においてInの比率が0.2より小さいと、移動度が低くなったり、S値が大きくなったり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下するおそれがある。一方、0.8より大きいと、オフ電流やゲートリーク電流が大きくなったり、S値が大きくなったり、耐プラズマ性が低下したり、閾値が負になりノーマリーオンとなるおそれがある。

In/(In+Zn)は、好ましくは0.3〜0.75であり、より好ましくは0.35〜0.7である。

【0023】

上記(2)においてInの比率が0.29より小さいと、移動度が低くなったり、S値が大きくなったり、閾値電圧が高くなるおそれがある。一方、0.99より大きいと、オフ電流やゲートリーク電流が大きくなったり、閾値が負になりノーマリーオンとなったり、光電流が大きくなったり、耐プラズマ性が低下したり、閾値電圧のシフトが大きくなるおそれがある。

In/(In+X)は、好ましくは0.45〜0.98であり、より好ましくは0.65〜0.98であり、特に好ましくは0.7〜0.97である。

【0024】

上記(3)においてZnの比率が0.29より小さいと、移動度が低くなったり、S値が大きくなったり、安定化させるのに高温あるいは長時間の熱処理が必要となったり、ウェットエッチングレートが遅くなるおそれがある。一方、0.99より大きいと移動度が低くなったり、S値が大きくなったり、熱安定性や耐熱性が低下したり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下したり、閾値電圧のシフトが大きくなるおそれがある。

Zn/(X+Zn)は、好ましくは0.45〜0.98であり、より好ましくは0.6〜0.98であり、さらに好ましくは0.7〜0.97である。

【0025】

本発明においては、半導体層が、さらに、下記(4)の比率(原子比)を満たすことが好ましい。

X/(In+Zn+X)=0.01〜0.2 (4)

Xの比率が0.2より大きいと、S値が大きくなったり、移動度が低下したり、閾値電圧が大きくなったりするおそれがある。一方、0.01より小さいと、熱安定性や耐熱性が低下したり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下したり、閾値電圧のシフトが大きくなるおそれがある。

X/(In+Zn+X)は、0.02〜0.15がより好ましく、特に、0.03〜0.1が好ましい。

【0026】

さらに、用途によって半導体層が、下記(5)あるいは(6)の比率(原子比)を満たすことが特に好ましい。

In/(In+Zn+X)=0.3〜0.5 (5)

In/(In+Zn+X)=0.5〜0.7(0.5を含まない) (6)

上記(5)の比率は、オフ電流を低減しやすくオンオフ比を高くすることができる。また、成膜条件や後処理条件のマージンも広い。上記(6)の比率だと移動度を高く、閾値電圧を小さくすることができる。

【0027】

本発明では、熱安定性、耐熱性、耐薬品性が向上し、S値やオフ電流を低減できることから、元素XはZr又はHfであることが好ましく、Zrであることが特に好ましい。

また、光電流を低減したい場合は、元素XはZr、Hf、Ge、Si、Tiが好ましい。また、プラズマ耐性を高くして後工程で特性が変化しにくくしたい場合は、元素XはCu、Ni、Co、Fe、Cr、Mn、W、Mo、V及びNbが好ましい。

【0028】

[本発明の第二の態様]

本発明の電界効果型トランジスタは、In(インジウム)元素及びZn(亜鉛)元素と、下記のA群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する。

A群:Al(アルミニウム)、B(ホウ素)、Sc(スカンジウム)、Y(イットリウム)及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【0029】

半導体層を上記の複合酸化物から形成することによって、移動度が高く、S値の低い電界効果型トランジスタが得られる。また、低温又は短時間の熱履歴(熱処理)でも、高い特性の得られる電界効果型トランジスタとなる。

【0030】

上記(1)においてInの比率が0.2より小さいと、移動度が低くなったり、S値が大きくなったり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下するおそれがある。一方、0.8より大きいと、オフ電流やゲートリーク電流が大きくなったり、S値が大きくなったり、耐プラズマ性が低下したり、閾値が負になりノーマリーオンとなるおそれがある。

In/(In+Zn)は、好ましくは0.3〜0.75であり、より好ましくは0.35〜0.7である。

【0031】

上記(2)においてInの比率が0.29より小さいと、移動度が低くなったり、S値が大きくなったり、閾値電圧が高くなるおそれがある。一方、0.99より大きいと、オフ電流やゲートリーク電流が大きくなったり、閾値が負になりノーマリーオンとなったり、光電流が大きくなったり、耐プラズマ性が低下したり、閾値電圧のシフトが大きくなるおそれがある。

In/(In+X)は、通常は0.29〜0.99、好ましくは0.59〜0.98、より好ましくは0.6〜0.97であり、さらに好ましくは0.65〜0.96であり、特に好ましくは0.7〜0.95である。

【0032】

上記(3)においてZnの比率が0.29より小さいと、移動度が低くなったり、S値が大きくなったり、安定化させるのに高温あるいは長時間の熱処理が必要となったり、ウェットエッチングレートが遅くなるおそれがある。一方、0.99より大きいと移動度が低くなったり、S値が大きくなったり、熱安定性や耐熱性が低下したり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下したり、閾値電圧のシフトが大きくなるおそれがある

Zn/(X+Zn)は、好ましくは0.45〜0.98であり、より好ましくは0.6〜0.98であり、さらに好ましくは0.7〜0.97であり、特に好ましくは0.75〜0.90である。

【0033】

本発明においては、半導体層が、さらに、下記(4)の比率(原子比)を満たすことが好ましい。

X/(In+Zn+X)=0.02〜0.3 (4)

Xの比率が0.3より大きいと、S値が大きくなったり、移動度が低下したり、閾値電圧が大きくなったりするおそれがある。一方、0.02より小さいと熱安定性や耐熱性が低下したり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下したり、オフ電流が大きくなったり、閾値電圧のシフトが大きくなるおそれがある。

X/(In+Zn+X)は、0.04〜0.25がより好ましく、0.055〜0.2がさらに好ましく、0.06〜0.15が特に好ましい。

【0034】

さらに、半導体層が、下記(5)又は(6)の比率(原子比)を満たすことが、用途により使い分けることができ特に好ましい。

In/(In+Zn+X)=0.3〜0.5 (5)

In/(In+Zn+X)=0.5〜0.7(0.5は含まない) (6)

上記(5)の比率では、オフ電流を低減しやすく、オンオフ比を高くすることができる。また、成膜条件や後処理条件のマージンも広い。上記(6)の比率だと移動度を高く、閾値電圧を小さくすることができる。

【0035】

本発明において元素Xは、Al又はBであることが好ましい。また、Sc又はYである場合も好ましい。さらに、ランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)である場合も好ましい。

【0036】

本発明の電界効果型トランジスタは、上述した第一の態様又は第二の態様で示した半導体層を有していれば、他の構成については特に限定はない。トップゲート型やボトムゲート型等、公知の構造を利用することができる。以下、電界効果型トランジスタの構成例について図面を参照して説明する。

【0037】

図1は、本発明の一実施形態の電界効果型トランジスタの概略断面図である。

電界効果型トランジスタ1はボトムゲート型であり、熱酸化膜11を有するシリコン基板10上に、ゲート電極12がストライプ状に形成されている。このゲート電極12を覆うようにゲート絶縁膜13を有し、このゲート絶縁膜13上であって、かつ、ゲート電極12上に半導体層14(活性層)が形成されている。

半導体層14の一端14aに、ゲート電極12と直交する方向にソース電極15が接続されている。また、半導体層14の一端14aに対向する他端14bにドレイン電極16が接続されている。

【0038】

図2は、ゲート電極12、半導体層14、ソース電極15及びドレイン電極16の位置関係を示す概略上面図である。位置関係の可視化のため一部の部材を省略してある。

【0039】

ボトムゲート型の電界効果型トランジスタの場合、半導体層は保護層で保護していることが好ましい。ボトムゲート型のトランジスタでは保護層が無いと半導体層の主要部分が露出するため保護層の効果が大きい。

図3及び図4は、本発明の他の実施形態の電界効果型トランジスタの概略断面図である。

電界効果型トランジスタ2及び3は、保護層17を形成している他は、上述した電界効果型トランジスタ1と同じ構成をしている。

【0040】

図5は、トップゲート型の電界効果型トランジスタの例を示す概略断面図である。

電界効果型トランジスタ4では、基板30上にソース電極35及びドレイン電極36が形成され、その間隙及びこれら電極の一部を覆うように半導体層34が設けられている。そして、半導体層34にゲート絶縁膜33を介してゲート電極32が形成されている。

トランジスタ3では、基板30が保護層37の役割をしている。

【0041】

以下、本発明の電界効果型トランジスタを構成部材について説明する。

1.基板

特に制限はなく、本技術分野で公知のものを使用できる。例えば、ケイ酸アルカリ系ガラス、無アルカリガラス、石英ガラス等のガラス基板、シリコン基板、アクリル、ポリカーボネート、ポリエチレンナフタレート(PEN)等の樹脂基板、ポリエチレンテレフタレート(PET)、ポリアミド等の高分子フィルム基材等が使用できる。

基板や基材の厚さは0.1〜10mmが一般的であり、0.3〜5mmが好ましい。ガラス基板の場合は、化学的に、或いは熱的に強化させたものが好ましい。

透明性や平滑性が求められる場合は、ガラス基板、樹脂基板が好ましく、ガラス基板が特に好ましい。軽量化が求められる場合は樹脂基板や高分子機材が好ましい。

【0042】

2.半導体層

半導体層は、上述した第一の態様又は第二の態様で示したIn(インジウム)、Zn(亜鉛)及び元素Xを上記(1)〜(3)の比率、好ましくは(1)〜(4)の比率を満たすように含有する複合酸化物からなる。

このような半導体層は、例えば、本発明の複合酸化物ターゲット(半導体層用ターゲット)を使用して薄膜を形成することで作製できる。

【0043】

本発明の半導体層用ターゲットは、上述した第一の態様又は第二の態様で示した比率(1)〜(3)又は(1)〜(4)を満たす複合酸化物の焼結体からなる。このターゲットは、例えば、酸化インジウム、酸化亜鉛及び元素Xの酸化物を、上記の元素比率を満たすように含む混合粉体を原料とする。原料粉体をボールミル等で微粉体化した後、ターゲット状に成形し焼成することによって作製できる。

尚、使用する原料粉体の一部は、ターゲットの端材や使用済みターゲット等の高純度酸化インジウム含有スクラップから回収して作製したものであってもよい。特に、ITOターゲットから回収した酸化インジウムは不純物としてSn(錫)を適度に含んでおり好ましい。酸化インジウムの回収は特開2002−069544号に記載の方法等、公知の方法を用いることができる。

尚、上述した第一の態様で示した元素XがZr、Hf、Ge、Si、Ti、V及びNbであると、特に外観のよく抗折力の高いターゲットを製造しやすい。

【0044】

各原料粉の純度は、通常99.9%(3N)以上、好ましくは99.99%(4N)以上、さらに好ましくは99.995%以上、特に好ましくは99.999%(5N)以上である。各原料粉の純度が99.9%(3N)未満だと、不純物により半導体特性が低下したり、色むらや斑点などの外観上の不良が発生したり、信頼性が低下する等のおそれがある。

原料粉について、酸化インジウム粉の比表面積を8〜10m2/g、酸化亜鉛粉の比表面積を2〜4m2/g、元素Xの酸化物の比表面積を5〜10m2/g(より好ましくは8〜10m2/g)とすることが好ましい。又は、酸化インジウム粉のメジアン径を0.2〜2μm、酸化亜鉛粉のメジアン径を0.8〜1.6μmとすることが好ましい。

尚、酸化インジウム粉の比表面積と元素Xの酸化物粉の比表面積が、ほぼ同じである粉末を使用することが好ましい。これにより、より効率的に粉砕混合できる。具体的には、比表面積の差を5m2/g以下にすることが好ましい。比表面積が違いすぎると、効率的な粉砕混合が出来ず、焼結体中に元素Xの酸化物の粒子が残る場合がある。

【0045】

混合粉体を、例えば、湿式媒体撹拌ミルを使用して混合粉砕する。このとき、粉砕後の比表面積が原料混合粉体の比表面積より1.5〜2.5m2/g増加する程度か、又は粉砕後の平均メジアン径が0.6〜1μmとなる程度に粉砕することが好ましい。このように調整した原料粉を使用することにより、仮焼工程を全く必要とせずに、高密度の酸化物焼結体を得ることができる。また、還元工程も不要となる。

尚、原料混合粉体の比表面積の増加分が1.0m2/g未満又は粉砕後の原料混合粉の平均メジアン径が1μmを超えると、焼結密度が十分に大きくならない場合がある。一方、原料混合粉体の比表面積の増加分が3.0m2/gを超える場合又は粉砕後の平均メジアン径が0.6μm未満にすると、粉砕時の粉砕器機等からのコンタミ(不純物混入量)が増加する場合がある。

ここで、各粉体の比表面積はBET法で測定した値である。各粉体の粒度分布のメジアン径は、粒度分布計で測定した値である。これらの値は、粉体を乾式粉砕法、湿式粉砕法等により粉砕することにより調整できる。

粉砕工程後の原料をスプレードライヤー等で乾燥した後、成形する。成形は公知の方法、例えば、加圧成形、冷間静水圧加圧が採用できる。

【0046】

次いで、得られた成形物を焼結して焼結体を得る。焼結は、1350〜1600℃で2〜20時間焼結することが好ましい。1350℃未満では、密度が向上せず、また、1600℃を超えると亜鉛が蒸散し、焼結体の組成が変化したり、蒸散により焼結体中にボイド(空隙)が発生したりする場合がある。

また、焼結は酸素を流通することにより酸素雰囲気中で焼結するか、加圧下にて焼結するのがよい。これにより亜鉛の蒸散を抑えることができ、ボイド(空隙)のない焼結体が得られる。

このようにして製造した焼結体は、密度が高いため、使用時におけるノジュールやパーティクルの発生が少ないことから、膜特性に優れた酸化物半導体膜を作製することができる。

【0047】

酸化物焼結体は、研磨等の加工を施すことによりターゲットとなる。具体的には、焼結体を、例えば、平面研削盤で研削して表面粗さRaを5μm以下とする。さらに、ターゲットのスパッタ面に鏡面加工を施して、平均表面粗さRaが1000オングストローム以下としてもよい。この鏡面加工(研磨)は機械的な研磨、化学研磨、メカノケミカル研磨(機械的な研磨と化学研磨の併用)等の、すでに知られている研磨技術を用いることができる。例えば、固定砥粒ポリッシャー(ポリッシュ液:水)で#2000以上にポリッシングしたり、又は遊離砥粒ラップ(研磨材:SiCペースト等)にてラッピング後、研磨材をダイヤモンドペーストに換えてラッピングすることによって得ることができる。このような研磨方法には特に制限はない。

【0048】

得られたターゲットをバッキングプレートへボンディングすることにより、各種成膜装置に装着して使用できる。成膜法としては、例えば、スパッタリング法、PLD(パルスレーザーディポジション)法、真空蒸着法、イオンプレーティング法等が挙げられる。

【0049】

尚、ターゲットの清浄処理には、エアーブローや流水洗浄等を使用できる。エアーブローで異物を除去する際には、ノズルの向い側から集塵機で吸気を行なうとより有効に除去できる。

エアーブローや流水洗浄の他に、超音波洗浄等を行なうこともできる。超音波洗浄では、周波数25〜300KHzの間で多重発振させて行なう方法が有効である。例えば周波数25〜300KHzの間で、25KHz刻みに12種類の周波数を多重発振させて超音波洗浄を行なうのがよい。

【0050】

酸化物焼結体中における各化合物の粒径は、それぞれ20μm以下が好ましく、10μm以下がさらに好ましく、5μm以下が特に好ましい。尚、粒径は電子プローブマイクロアナライザ(EPMA)で測定した平均粒径である。結晶粒径は、例えば、原料である酸化インジウム、X元素の酸化物、酸化亜鉛の各粉体の配合比や原料粉体の粒径、純度、昇温時間、焼結温度、焼結時間、焼結雰囲気、降温時間を調製することにより得られる。化合物の粒径が20μmより大きいとスパッタ時にノジュールが発生するおそれがある。

【0051】

ターゲットの密度は、理論密度の95%以上が好ましく、98%以上がより好ましく、99%以上が特に好ましい。ターゲットの密度が95%より小さいと強度が不十分となり成膜時にターゲットが破損するおそれがある。また、トランジスタを作製した際に性能が不均一になるおそれがある。

ここで、ターゲットの理論相対密度は、各酸化物の比重(例えば、ZnOは5.66g/cm3、In2O3は7.12g/cm3、ZrO2は5.98g/cm3)とその量比から密度を計算し、アルキメデス法で測定した密度との比率を計算して理論相対密度とする。

【0052】

ターゲットのバルク抵抗は、20mΩ以下が好ましく、10mΩ以下がより好ましく、5mΩ以下がさらに好ましく、2mΩcm以下が特に好ましい。。20mΩより大きいとDCスパッタでの成膜時にターゲットが破損するおそれがある。また、異常放電によりスパークが発生し、ターゲットが割れたり、スパークにより飛び出した粒子が成膜基板に付着し、酸化物半導体膜としての性能を低下させたりする場合がある。また、放電時にターゲットが割れるおそれもある。

尚、バルク抵抗は抵抗率計を使用し、四探針法により測定した値である。

【0053】

本発明のターゲットの抗折力は、8kg/mm2以上であることが好ましく、10kg/mm2以上であることがより好ましく、12kg/mm2以上であることが特に好ましい。ターゲットの運搬、取り付け時に荷重がかかり、ターゲットが破損するおそれがあるという理由で、ターゲットには、一定以上の抗折力が要求され、8kg/mm2未満では、ターゲットとしての使用に耐えられないおそれがある。ターゲットの抗折力は、JIS R 1601に準じて測定することができる。

【0054】

尚、本発明の第二の態様に関するターゲットでは、さらに、Sn(錫)、Ge(ゲルマニウム)、Si(シリコン)、Ti(チタン)、Zr(ジルコニウム)及びHf(ハフニウム)からなる群より選択される1以上の元素を、100〜10000ppm含むことが好ましい。これらの元素を含むと、ターゲットの密度の向上、強度の向上、抵抗の低下、色むらの減少、均一性の向上、異常放電やイエローフレークの減少等の効果があり、半導体用ターゲットとして品質が向上することが期待できる。

上記元素は、これらの元素を含む焼結体(ターゲット)から回収した原料を用いて、不純物として含まれていてもよい。また、原料に金属粉体や酸化物として添加してもよい。

【0055】

本発明において、半導体層は非晶質膜であることが好ましい。

非晶質膜であることにより、絶縁膜や保護層との密着性が改善されたり、大面積でも均一なトランジスタ特性が容易に得られることとなる。

ここで、半導体層が非晶質膜であるかは、X線結晶構造解析により確認できる。明確なピークが観測されない場合が非晶質である。

【0056】

また、半導体層の電子キャリア濃度が1013〜1018/cm3であることが好ましく、特に1014〜1017/cm3であることが好ましい。

電子キャリア濃度が上記の範囲であれば、非縮退半導体となりやすく、トランジスタとして用いた際に移動度とオンオフ比のバランスが良好となり好ましい。

また、バンドギャップが2.0〜6.0eVであることが好ましく、特に、2.8〜5.0eVがより好ましい。バンドギャップは、2.0eVより小さいと可視光を吸収し電界効果型トランジスタが誤動作するおそれがある。一方、6.0eVより大きいとキャリアが供給されにくくなり電界効果型トランジスタが機能しなくなるおそれがある。

【0057】

半導体層は、熱活性型を示す非縮退半導体であることが好ましい。縮退半導体であるとキャリアが多すぎてオフ電流・ゲートリーク電流が増加したり、閾値が負になりノーマリーオンとなるおそれがある。

半導体層が非縮退半導体であるかは、ホール効果を用いた移動度とキャリア密度の温度変化の測定を行うことにより判断できる。

また、半導体層を非縮退半導体とするには、成膜時の酸素分圧を調整したり、後処理をすることで酸素欠陥量を制御しキャリア密度を最適化することで達成できる。

【0058】

半導体層の表面粗さ(RMS)は、1nm以下が好ましく、0.6nm以下がさらに好ましく、0.3nm以下が特に好ましい。1nmより大きいと、移動度が低下するおそれがある。

【0059】

半導体層は、酸化インジウムのビックスバイト構造の稜共有構造の少なくとも一部を維持している非晶質膜であることが好ましい。酸化インジウムを含む非晶質膜が酸化インジウムのビックスバイト構造の稜共有構造の少なくとも一部を維持しているかどうかは、高輝度のシンクロトロン放射等を用いた微小角入射X線散乱(GIXS)によって求めた動径分布関数(RDF)により、In−X(Xは,In,Zn)を表すピークが0.30から0.36nmの間にあることで確認できる。詳細については、下記の文献を参照すればよい。

F.Utsuno, et al.,Thin Solid Films,Volume 496, 2006, Pages 95−98

【0060】

さらに、原子間距離が0.30から0.36nmの間のRDFの最大値をA、原子間距離が0.36から0.42の間のRDFの最大値をBとした場合に、A/B>0.7の関係を満たすことが好ましく、A/B>0.85がより好ましく、A/B>1がさらに好ましく、A/B>1.2が特に好ましい。

A/Bが0.7以下だと、半導体層をトランジスタの活性層として用いた場合、移動度が低下したり、閾値やS値が大きくなりすぎるおそれがある。A/Bが小さいことは、非晶質膜の近距離秩序性が悪いことを反映しているものと考えられる。

【0061】

また、In−Inの平均結合距離が0.3〜0.322nmであることが好ましく、0.31〜0.32nmであることが特に好ましい。In−Inの平均結合距離はX線吸収分光法により求めることができる。X線吸収分光法による測定では、立ち上がりから数百eVも高いエネルギーのところまで広がったX線吸収広域微細構造(EXAFS)を示す。EXAFSは励起された原子の周囲の原子による電子の後方散乱によって引き起こされる。飛び出していく電子波と後方散乱された波との干渉効果が起こる。干渉は電子状態の波長と周囲の原子へ行き来する光路長に依存する。EXAFSをフーリエ変換することで動径分布関数(RDF)が得られる。RDFのピークから平均結合距離を見積もることができる。

【0062】

半導体層の膜厚は、通常0.5〜500nm、好ましくは1〜150nm、より好ましくは3〜80nm、特に好ましくは10〜60nmである。0.5nmより薄いと工業的に均一に成膜することが難しい。一方、500nmより厚いと成膜時間が長くなり工業的に採用できない。また、3〜80nmの範囲内にあると、移動度やオンオフ比等TFT特性が特に良好である。

【0063】

本発明では、半導体層が非晶質膜であり、非局在準位のエネルギー幅(E0)が14meV以下であることが好ましい。半導体層の非局在準位のエネルギー幅(E0)は10meV以下がより好ましく、8meV以下がさらに好ましく6meV以下が特に好ましい。

非局在準位のエネルギー幅(E0)が14meVより大きいと、半導体層をトランジスタの活性層として用いた場合、移動度が低下したり、閾値やS値が大きくなりすぎるおそれがある。半導体層の非局在準位のエネルギー幅(E0)が大きいことは、非晶質膜の近距離秩序性が悪いことを反映しているものと考えられる。

【0064】

3.半導体層の保護層

電界効果型トランジスタは、半導体の保護層があることが好ましい。半導体の保護層が無いと、真空中や低圧下で半導体の表面層の酸素が脱離し、オフ電流が高くなったり、閾値電圧が負になるおそれがある。また、大気下でも湿度等周囲の影響を受け、閾値電圧等のトランジスタ特性のばらつきが大きくなるおそれがある。

【0065】

半導体の保護層を形成する材料は特に制限はない。本発明の効果を失わない範囲で一般に用いられているものを任意に選択できる。例えば、SiO2,SiNx,Al2O3,Ta2O5,TiO2,MgO,ZrO2,CeO2,K2O,Li2O,Na2O,Rb2O,Sc2O3,Y2O3,Hf2O3,CaHfO3,PbTi3,BaTa2O6,SrTiO3,AlN等を用いることができる。これらのなかでも、SiO2,SiNx,Al2O3,Y2O3,Hf2O3,CaHfO3を用いるのが好ましく、より好ましくはSiO2,SiNx,Y2O3,Hf2O3,CaHfO3であり、特に好ましくはSiO2,Y2O3,Hf2O3,CaHfO3等の酸化物である。これらの酸化物の酸素数は、必ずしも化学量論比と一致していなくともよい(例えば、SiO2でもSiOxでもよい)。また、SiNxは水素元素を含んでいても良い。

【0066】

このような保護膜は、異なる2層以上の絶縁膜を積層した構造でもよい。

また、保護層は、結晶質、多結晶質、非晶質のいずれであってもよいが、工業的に製造しやすい多結晶質か、非晶質であるのが好ましい。しかし、保護層が非晶質であることが特に好ましい。非晶質膜でないと界面の平滑性が悪く移動度が低下したり、閾値電圧やS値が大きくなりすぎるおそれがある。

【0067】

半導体層の保護層は、非晶質酸化物あるいは非晶質窒化物であることが好ましく、非晶質酸化物であることが特に好ましい。また、保護層が酸化物でないと半導体中の酸素が保護層側に移動し、オフ電流が高くなったり、閾値電圧が負になりノーマリーオフを示すおそれがある。

また、半導体層の保護層は、ポリ(4−ビニルフェノール)(PVP)、パリレン等の有機絶縁膜を用いてもよい。さらに、半導体層の保護層は無機絶縁膜及び有機絶縁膜の2層以上積層構造を有してもよい。

【0068】

4.ゲート絶縁膜

ゲート絶縁膜を形成する材料にも特に制限はない。本実施形態の発明の効果を失わない範囲で一般に用いられているものを任意に選択できる。例えば、SiO2,SiNx,Al2O3,Ta2O5,TiO2,MgO,ZrO2,CeO2,K2O,Li2O,Na2O,Rb2O,Sc2O3,Y2O3,Hf2O3,CaHfO3,PbTi3,BaTa2O6,SrTiO3,AlN等を用いることができる。これらのなかでも、SiO2,SiNx,Al2O3,Y2O3,Hf2O3,CaHfO3を用いるのが好ましく、より好ましくはSiO2,SiNx,Y2O3,Hf2O3,CaHfO3である。これらの酸化物の酸素数は、必ずしも化学量論比と一致していなくともよい(例えば、SiO2でもSiOxでもよい)。また、SiNxは水素元素を含んでいても良い。

【0069】

このようなゲート絶縁膜は、異なる2層以上の絶縁膜を積層した構造でもよい。また、ゲート絶縁膜は、結晶質、多結晶質、非晶質のいずれであってもよいが、工業的に製造しやすい多結晶質か、非晶質であるのが好ましい。

また、ゲート絶縁膜は、ポリ(4−ビニルフェノール)(PVP)、パリレン等の有機絶縁膜を用いてもよい。さらに、ゲート絶縁膜は無機絶縁膜及び有機絶縁膜の2層以上積層構造を有してもよい。

【0070】

5.電極

ゲート電極、ソ−ス電極及びドレイン電極の各電極を形成する材料に特に制限はなく、本発明の効果を失わない範囲で一般に用いられているものを任意に選択することができる。

例えば、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物、ZnO、SnO2等の透明電極や、Al,Ag,Cr,Ni,Mo,Au,Ti,Ta、Cu等の金属電極、又はこれらを含む合金の金属電極を用いることができる。また、それらを2層以上積層して接触抵抗を低減したり、界面強度を向上させることが好ましい。また、ソ−ス電極、ドレイン電極の接触抵抗を低減させるため半導体の電極との界面をプラズマ処理、オゾン処理等で抵抗を調整してもよい。

【0071】

続いて、本発明の電界効果型トランジスタの製造方法について説明する。

本発明の製造方法では、上述した本発明のターゲットを用い、DCあるいはACスパッタリングにより半導体層を成膜する工程と、半導体層を形成した後に70〜350℃で熱処理する工程を含むことを特徴とする。

尚、上述した電界効果型トランジスタの各構成部材(層)は、本技術分野で公知の手法で形成できる。

具体的に、成膜方法としては、スプレー法、ディップ法、CVD法等の化学的成膜方法、又はスパッタ法、真空蒸着法、イオンプレーティング法、パルスレーザーディポジション法等の物理的成膜方法を用いることができる。キャリア密度が制御し易い、及び膜質向上が容易であることから、好ましくは物理的成膜方法を用い、より好ましくは生産性が高いことからスパッタ法を用いる。

【0072】

スパッタリングでは、複合酸化物の焼結ターゲットを用いる方法、複数の焼結ターゲットを用いコスパッタを用いる方法、合金ターゲットを用い反応性スパッタを用いる方法等が利用できる。但し、複数の焼結ターゲットを用いコスパッタを用いる方法や、合金ターゲットを用い反応性スパッタを用いる方法では、均一性や再現性が悪くなる場合や、非局在準位のエネルギー幅(E0)が大きくなる場合があり、移動度が低下したり、閾値電圧が大きくなる等、トランジスタ特性が低下するおそれがある。好ましくは、複合酸化物の焼結ターゲットを用いる。

形成した膜を各種エッチング法によりパターニングできる。

【0073】

本発明では半導体層を、本発明のターゲットを用い、DC又はACスパッタリングにより成膜する。DC又はACスパッタリングを用いることにより、RFスパッタリングの場合と比べて、成膜時のダメージを低減できる。このため、電界効果型トランジスタにおいて、閾値電圧シフトの低減、移動度の向上、閾値電圧の減少、S値の減少等の効果が期待できる。

【0074】

また、本発明では半導体層と半導体の保護層を形成した後に、70〜350℃で熱処理する。70℃より低いと得られるトランジスタの熱安定性や耐熱性が低下したり、移動度が低くなったり、S値が大きくなったり、閾値電圧が高くなるおそれがある。一方、350℃より高いと耐熱性のない基板が使用できないおそれや、熱処理用の設備費用がかかるおそれや、保護層、絶縁膜又は半導体層の界面が劣化するおそれや、水分圧を下げて成膜した際に結晶化し、非晶質膜が得られないおそれがある。

熱処理温度は80〜260℃が好ましく、90〜180℃がより好ましく、100〜150℃がさらに好ましい。特に、熱処理温度が180℃以下であれば、基板としてPEN等の耐熱性の低い樹脂基板を利用できるため好ましい。

【0075】

熱処理時間は、通常1秒〜24時間が好ましいが、処理温度により調整することが好ましい。例えば、70〜180℃では、10分から24時間がより好ましく、20分から6時間がさらに好ましく、30分〜3時間が特に好ましい。180〜260℃では、6分から4時間がより好ましく、15分から2時間がさらに好ましい。260〜300℃では、30秒から4時間がより好ましく、1分から2時間が特に好ましい。300〜350℃では、1秒から1時間がより好ましく、2秒から30分が特に好ましい。

【0076】

熱処理は、不活性ガス中で酸素分圧が10−3Pa以下の環境下で行うか、あるいは半導体層を保護層で覆った後に行うことが好ましい。上記条件下だと再現性が向上する。

不活性ガスとしては、N2、He、Ne、Ar、Kr、Xeが好ましい。

【0077】

本発明の電界効果トランジスタでは、移動度は1cm2/Vs以上が好ましく、3cm2/Vs以上がより好ましく、8cm2/Vs以上が特に好ましい。1cm2/Vsより小さいとスイッチング速度が遅くなり大画面高精細のディスプレイに用いることができないおそれがある。

オンオフ比は、106以上が好ましく、107以上がより好ましく、108以上が特に好ましい。

【0078】

オフ電流は、2pA以下が好ましく、1pA以下がより好ましく、0.5pA以下がさらに好ましく、0.2pA以下が特に好ましい。オフ電流が2pAより大きいとディスプレイのTFTとして用いた場合にコントラストが悪くなったり、画面の均一性が悪くなるおそれがある。

ゲートリーク電流は1pA以下が好ましい。1pAより大きいとディスプレイのTFTとして用いた場合にコントラストが悪くなるおそれがある。

【0079】

閾値電圧は、通常0〜10Vであるが、0〜4Vが好ましく、0〜3Vがより好ましく、0〜2Vが特に好ましい。0Vより小さいとノーマリーオンとなり、オフ時に電圧をかける必要になり消費電力が大きくなるおそれがある。10Vより大きいと駆動電圧が大きくなり消費電力が大きくなったり、高い移動度が必要となるおそれがある。

【0080】

また、S値は0.8V/dec以下が好ましく、0.3V/dec以下がより好ましく、0.25V/dec以下がさらに好ましく、0.2V/dec以下が特に好ましい。0.8V/decより大きいと駆動電圧が大きくなり消費電力が大きくなるおそれがある。特に、有機ELディスプレイで用いる場合は、直流駆動のためS値を0.3V/dec以下にすると消費電力を大幅に低減できるため好ましい。

【0081】

尚、S値(Swing Factor)とは、オフ状態からゲート電圧を増加させた際に、オフ状態からオン状態にかけてドレイン電流が急峻に立ち上がるが、この急峻さを示す値である。下記式で定義されるように、ドレイン電流が1桁(10倍)上昇するときのゲート電圧の増分をS値とする。

S値=dVg/dlog(Ids)

S値が小さいほど急峻な立ち上がりとなる(「薄膜トランジスタ技術のすべて」、鵜飼育弘著、2007年刊、工業調査会)。

S値が大きいと、オンからオフに切り替える際に高いゲート電圧をかける必要があり、消費電力が大きくなるおそれがある。

【0082】

また、10μAの直流電圧50℃で100時間加えた前後の閾値電圧のシフト量は、1.0V以下が好ましく、0.5V以下がより好ましい。1Vより大きいと有機ELディスプレイのトランジスタとして利用した場合、画質が変化してしまうおそれがある。

【0083】

また、伝達曲線でゲート電圧を昇降させた場合のヒステリシスが小さい方が好ましい。

【0084】

また、チャンネル幅Wとチャンネル長Lの比W/L(図2参照。)は、通常0.1〜100、好ましくは0.5〜20、特に好ましくは1〜8である。W/Lが100を越えると漏れ電流が増えたり、on−off比が低下したりするおそれがある。0.1より小さいと電界効果移動度が低下したり、ピンチオフが不明瞭になったりするおそれがある。

【0085】

また、チャンネル長Lは通常0.1〜1000μm、好ましくは1〜100μm、さらに好ましくは2〜10μmである。0.1μm以下は工業的に製造が難しくまた漏れ電流が大きくなるおそれがある、1000μm以上では素子が大きくなりすぎて好ましくない。

【0086】

本発明の電界効果型トランジスタは、半導体層を遮光する構造を持つことが好ましい。半導体層を遮光する構造(例えば、遮光層)を持っていないと、光が半導体層に入射した場合にキャリア電子が励起されオフ電流が高くなるおそれがある。遮光層は、300〜800nmに吸収を持つ薄膜が好ましい。遮光層は半導体層の上部、下部どちらかでも構わないが、上部及び下部の両方にあることが好ましい。また、遮光層はゲート絶縁膜やブラックマトリックス等と兼用されていても構わない。遮光層が片側だけにある場合、遮光層が無い側から光が半導体層に照射しないよう構造上工夫する必要がある。

【0087】

尚、本発明の電界効果型トランジスタでは、半導体層とソース電極あるいはドレイン電極との間にコンタクト層を設けることが好ましい。コンタクト層の形成材料は、上述した半導体層と同様な組成の複合酸化物が使用できる。即ち、コンタクト層はInやZn等、半導体層に含まれる元素を主成分とする酸化物であることが好ましい。これらの元素を含まないと、コンタクト層と半導体層の間で元素の移動が発生し、ストレス試験等を行った際に閾値電圧のシフトが大きくなるおそれがある。

コンタクト層の作製方法に特に制約はないが、成膜条件を変えて半導体層と同じ組成比のコンタクト層を成膜したり、半導体層と組成比の異なる層を成膜したり、半導体の電極とのコンタクト部分をプラズマ処理やオゾン処理により抵抗を高めることで構成したり、半導体層を成膜する際に酸素分圧等の成膜条件により抵抗を高くなる層を構成してもよい。

【0088】

また、本発明の電界効果型トランジスタでは、半導体層とゲート絶縁膜との間、及び/又は半導体層と保護層との間に、半導体層よりも抵抗の高い酸化物抵抗層を有することが好ましい。酸化物抵抗層が無いとオフ電流が発生したり、閾値電圧が負となりノーマリーオンとなるおそれがある。また、保護膜成膜やエッチング等の後処理工程時に半導体層が変質し特性が劣化するおそれがある。

【0089】

酸化物抵抗層としては、以下のものが例示できる。

・半導体膜の成膜時よりも高い酸素分圧で成膜した半導体層と同一組成の非晶質酸化物膜

・半導体層と同一組成であるが組成比を変えた非晶質酸化物膜

・In及びZnを含み半導体層と異なる元素Xを含む非晶質酸化物膜

・酸化インジウムを主成分とする多結晶酸化物膜

・酸化インジウムを主成分とし、Zn、Cu、Co、Ni、Mn、Mgなどの正二価元素を1種以上ドープした多結晶酸化物膜

・半導体層に含まれる組成にさらにCu、Co、Ni、Mn、Fe、Mg、Ca、Sr、Ba、Ag、Auから選ばれる1種以上の元素を加えた非晶質酸化物膜

【0090】

半導体層と同一組成であるが組成比を変えた非晶質酸化物膜や、In及びZnを含み半導体層と異なる元素Xを含む非晶質酸化物膜の場合は、In組成比が半導体層よりも少ないことが好ましい。また、元素Xの組成比が半導体層よりも多いことが好ましい。

【0091】

酸化物抵抗層は、In及びZnの各元素を含む酸化物であることが好ましい。これらを含まないと、酸化物抵抗層と半導体層の間で元素の移動が発生し、ストレス試験等を行った際に閾値電圧のシフトが大きくなるおそれがある。

半導体層に含まれる組成に、さらにCu、Co、Ni、Mn、Fe、Mg、Ca、Sr、Ba、Ag、Auから選ばれる1種以上の元素を加えた非晶質酸化物膜の場合は、In組成比が半導体層よりも少ないことが好ましい。また、Ga組成比が半導体層よりも多いことが好ましい。

【実施例】

【0092】

[第一の態様]

実施例1

(1)スパッタリングターゲットの製造

原料として、酸化インジウム、酸化亜鉛及び酸化ジルコニウムの粉末を、原子比〔In/(In+Zn+Zr)〕が0.48、原子比〔Zn/(In+Zn+Zr)〕が0.50、原子比〔Zr/(In+Zn+Zr)〕が0.02となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径10cm、厚さ5mmの寸法にプレス成形し、これを焼成炉に入れ、1500℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットのバルク抵抗は3mΩ、理論相対密度は0.99であった。また、色むらが無く外観の均一性の高いターゲットが得られた。

尚、理論相対密度は各酸化物の比重とその量比から計算した密度を、アルキメデス法で測定した密度との比率を計算して求めた。

【0093】

(2)トランジスタの作製

基板にガラス基板を使用した他は、図1に示す電界効果型トランジスタと同様のトランジスタを作製した。

ガラス基板上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極を作製した。

次に、ゲート電極を作製した基板にプラズマ化学気相成長装置(PECVD)にて、SiNxを300℃で成膜(厚さ200nm)し、ゲート絶縁膜とした。

次に、(1)で製造したターゲットを、DCスパッタ法の一つであるDCマグネトロンスパッタリング法の成膜装置に装着し、ゲート絶縁膜上に成膜し、その後パターニングして半導体層(膜厚50nm)を形成した。

スパッタ条件は、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar99.5%及び酸素0.5%、スパッタ圧力(全圧);2×10−1Pa、投入電力100W、成膜時間6分間、S−T距離110mmとした。

次に、リフトオフプロセス及びRFマグネトロンスパッタリング(室温、Ar100%)を用い、In2O3−ZnOからなるソース/ドレイン電極を形成した。

その後、窒素環境下、170℃で2時間熱処理して電界効果型トランジスタを製造した(図2のWが40μm、Lが4μmのボトムゲート型の電界効果型トランジスタ)。

【0094】

[半導体層の評価]

ガラス基板(コーニング1737)上に、上記実施例(1)で製造したターゲットを使用して半導体層を形成し評価した。

半導体層の形成は、DCマグネトロンスパッタリング法の成膜装置にて、実施例(2)と同じようにした。この結果、ガラス基板上に、膜厚が50nmの酸化物薄膜が形成された。

【0095】

得られた半導体膜をICP(Inductively Coupled Plasma)法で分析したところ、原子比〔In/(In+Zn+Zr)〕が0.49、原子比〔Zn/(In+Zn+Zr)〕が0.49、原子比〔Ga/(In+Zn+Zr)〕が0.02であった。

【0096】

上記半導体膜を窒素環境下で、170℃で2時間の熱処理を行った。

熱処理後の半導体膜のキャリア濃度及びホール移動度を、ホール測定装置により測定した。結果はn型を示し、キャリア濃度は4×1017cm−3、ホール移動度は2cm2/Vsであった。

尚、ホール測定装置、及びその測定条件は下記のとおりであった、

・ホール測定装置

東陽テクニカ製:Resi Test8310

・測定条件

測定温度:室温(25℃)

測定磁場:0.5T

測定電流:10−12〜10−4A

測定モード:AC磁場ホール測定

【0097】

また、X線結晶構造解析により非晶質であることが確認された。AMFにより測定した表面粗さはRMS0.2nmであった。また光学的に求めたバンドギャップは3.8eVであった。

さらに、77〜300Kの範囲で測定温度を変化させホール効果を測定すると熱活性型を示し、半導体膜は非縮退半導体であることが確認できた。

また、温度を変化させホール効果を用い測定したキャリア濃度と活性化エネルギーの関係から非局在準位のエネルギー幅(E0)は6meV以下であった。

さらに、X線散乱測定によって求めた動径分布関数(RDF)により、In−Inを表すピークが0.35nm付近に観測され、酸化インジウムのビックスバイト構造の稜共有構造が残っていることが確認できた。原子間距離が0.30から0.36nmの間のRDFの最大値をA、原子間距離が0.36から0.42の間のRDFの最大値をBとした場合のA/Bは、1.3であった。X線吸収分光法によって求めたIn−Inの平均結合距離が0.318nmであった。

【0098】

[トランジスタの評価]

電界効果型トランジスタについて、下記の評価を行った。

(1)電界効果移動度(μ)、オンオフ比、オフ電流、ゲートリーク電流、S値、閾値電圧(Vth)

半導体パラメーターアナライザー(ケースレー4200)を用い、室温、大気中、かつ遮光環境下で測定した。

(2)ヒステリシス

半導体パラメーターアナライザーを用い、昇電圧時の伝達曲線(I−V特性)と降電圧時の伝達曲線(I−V特性)を測定し、昇降時の電圧の差をΔVgとする。ΔVgの最大値が0.5V以下であるものを「少ない」、0.5〜3Vであるものを「ある」、3V以上であるものを「大きい」とした。

(3)ストレス試験

ストレス条件は、ゲート電圧15Vで10μAの直流電圧を50℃で100時間加えることとした。ストレスをかける前後のVthを比較し、閾値電圧のシフト量(ΔVth)を測定した。

【0099】

また、耐酸性及び耐湿性を以下のようにして評価した。

(1)耐酸性

実施例1(2)と同じ条件で、ガラス基板上に200nm厚の半導体膜を形成し、熱処理した。これを蓚酸系エッチング液(関東化学製、ITO−06)にてエッチングし、25℃でのエッチング速度を測定した。評価は下記のようにした。

◎:200nm/分未満

○:200〜500nm/分

△:500〜1000nm/分

×:1000nm/分以上

(2)耐湿性

作製したトランジスタを、85℃、85%RHにて、2000時間耐湿試験を実施した。試験前後の抵抗を測定し、下記のように分類した。試験前の抵抗値÷試験後の抵抗値、試験後の抵抗値÷試験前の抵抗値の大きい方を変化率とした。

◎:変化率2倍未満

○:変化率2〜5倍変化

△:変化率5〜100倍変化

×:変化率100倍以上変化

測定結果を表1に示す。

【0100】

実施例2〜29、比較例1〜7

原料である酸化インジウム、酸化亜鉛及びX元素の酸化物の混合比を、表1−4に示す組成となるように調製した他は、実施例1(1)と同様にしてスパッタリングターゲットを製造した。

上記のスパッタリングターゲットを使用し、成膜条件を表1−4に示すように変更した他は、実施例1(2)と同様にして電界効果型トランジスタを作製し、評価した。

尚、スパッタリングターゲットの製造時に、酸化ジルコニウムに代えて使用した原料は以下のとおりである。

実施例12:HfO2、株式会社高純度化学研究所社製、HFO01PB

実施例13:GeO2、株式会社高純度化学研究所社製、GEO06PB

実施例14:SiO2、株式会社高純度化学研究所社製、SIO12PB

実施例15:TiO2、株式会社高純度化学研究所社製、TIO14PB

実施例16:MnO2、株式会社高純度化学研究所社製、MNO03PB

実施例17:WO3、株式会社高純度化学研究所社製、WWO04PB

実施例18:MoO3、株式会社高純度化学研究所社製、MOO03PB

実施例19:V2O5、株式会社高純度化学研究所社製、VVO09PB

実施例20:Nb2O5、株式会社高純度化学研究所社製、NBO08PB

実施例25:CuO、株式会社高純度化学研究所社製、CUO08PB

実施例26:NiO、株式会社高純度化学研究所社製、NIO11PB

実施例27:CoO、株式会社高純度化学研究所社製、COO03PB

実施例28:FeO、株式会社高純度化学研究所社製、FEO01PB

実施例29:Cr2O3、株式会社高純度化学研究所社製、CRO01GB

【0101】

実施例21では、ソース/ドレイン電極を形成したあとに、RFマグネトロンスパッタリングでSiO2を300nm成膜して保護層を形成し、図4に示す電解効果型トランジスタを作製した。

【0102】

実施例22、及び比較例1〜7では、半導体層の形成をRFスパッタリングで行った。具体的に、ターゲットをRFマグネトロンスパッタリング成膜装置に装着し成膜した。

ここでのスパッタ条件は、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar99.5%及び酸素0.5%、スパッタ圧力(全圧);2×10−1Pa、投入電力100W、成膜時間8分間、S−T距離100mmとした。

【0103】

実施例23では、SiO2熱酸化膜付シリコン基板を使用した。SiO2熱酸化膜の厚みは100nmであった。このトランジスタでは、ゲート絶縁膜がSiO2熱酸化膜であり、シリコン基板がゲート電極と基板の役割を果たす。

SiO2熱酸化膜付シリコン基板上に、半導体層、ソース電極及びドレイン電極を実施例1と同様にして形成した。

【0104】

【表1】

【0105】

【表2】

【0106】

【表3】

【0107】

【表4】

【0108】

【表5】

【0109】

[スパッタリングターゲットの例]

実施例30

原料として、酸化インジウム、酸化亜鉛及び酸化ジルコニウムの粉末を、原子比〔In/(In+Zn+Zr)〕が0.4、原子比〔Zn/(In+Zn+Zr)〕が0.4、原子比〔Zr/(In+Zn+Zr)〕が0.2となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径20cm、厚さ5mmの寸法にプレス成形した後、これを焼成炉に入れ、1400℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットのバルク抵抗は5mΩ、理論相対密度は0.98であった。ターゲットの抗折力は、12kg/mm2であった。また、色むらが無く外観の均一性の高いターゲットが得られた。

【0110】

比較例8

原料として、酸化インジウム、酸化亜鉛及び酸化ガリウムの粉末を、原子比〔In/(In+Zn+Ga)〕が0.4、原子比〔Zn/(In+Zn+Ga)〕が0.4、原子比〔Ga/(In+Zn+Ga)〕が0.2となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径20cm、厚さ5mmの寸法にプレス成形した後、これを焼成炉に入れ、1400℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットのバルク抵抗は70mΩ、理論相対密度は0.82であった。ターゲットの抗折力は、7kg/mm2であった。また、ターゲットには若干色むらが確認された。

【0111】

図6に、実施例1及び5と同じ組成の半導体層について、熱処理温度と移動度との関係を示した。尚、処理時間は2時間である。

実施例1の組成では150℃の処理で移動度が安定するのに対して、実施例5の組成では移動度を安定させるのに300℃以上の処理温度が必要であった。

【0112】

[第二の態様]

[スパッタリングターゲットの作製]

実施例31(ターゲットI)

原料として、5N(純度99.999%)の酸化インジウム(株式会社高純度化学研究所社製INO04PB)、5Nの酸化亜鉛(株式会社高純度化学研究所社製ZNO04PB)及び5Nの酸化アルミニウム(株式会社高純度化学研究所社製)の粉末を、原子比〔In/(In+Zn+Al)〕が0.48、原子比〔Zn/(In+Zn+Al)〕が0.50、原子比〔Al/(In+Zn+Al)〕が0.02となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径10cm、厚さ5mmの寸法にプレス成形して、これを焼成炉に入れ、1500℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットを粉砕しICPで分析したところ、Sn(錫)、Ge(ゲルマニウム)、Si(シリコン)、Ti(チタン)、Zr(ジルコニウム)、Hf(ハフニウム)等の不純物は含まれていなかった。また、ターゲットのバルク抵抗は20mΩ、理論相対密度は0.95であった。

【0113】

実施例32(ターゲットII)

原料として、使用済みのITOターゲット等から回収した酸化インジウム、5Nの酸化亜鉛(株式会社高純度化学研究所社製ZNO04PB)及び4Nの酸化アルミニウム(株式会社高純度化学研究所社製ALO12PB)の粉末を、原子比〔In/(In+Zn+Al)〕が0.48、原子比〔Zn/(In+Zn+Al)〕が0.50、原子比〔Al/(In+Zn+Al)〕が0.02となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径10cm、厚さ5mmの寸法にプレス成形して、これを焼成炉に入れ、1500℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットを粉砕しICPで分析したところ、不純物としてSn(錫)500ppmが含まれていた。また、ターゲットのバルク抵抗は3mΩ、理論相対密度は0.99であった。また、色むらが無く外観の均一性の高いターゲットが得られた。

【0114】

実施例33−37(ターゲットIII−VII)

Ge,Si,Ti,Zr又はHf元素を、原料中の金属元素全体に対して500原子ppmとなるように酸化物として添加した他はターゲットIと同じ工程で作製した。ターゲットはターゲットIIとほぼ同じ品質のものが得られたが、外観はさらに均質で綺麗なものが得られた。

【0115】

[スパッタリングターゲットの評価]

・ターゲットI

上記実施例31で作製したターゲットIを、RFスパッタ法の一つであるRFマグネトロンスパッタリング法の成膜装置に装着し、ガラス基板(コーニング1737)上に半導体膜を成膜した。

ここでのスパッタ条件としては、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar99.5%及び酸素0.5%、スパッタ圧力(全圧);2×10−1Pa、投入電力100W、成膜時間8分間、S−T距離100mmとした。

【0116】

この結果、ガラス基板上に、膜厚が70nmの半導体膜が形成された。

尚、得られた膜組成をICP法で分析したところ、原子比〔In/(In+Zn+Al)〕が0.49、原子比〔Zn/(In+Zn+Al)〕が0.49、原子比〔Al/(In+Zn+Al)〕が0.02であった。

【0117】

このように、ターゲットIでは半導体膜を形成することができた。

【0118】

・ターゲットII〜VII

上記のターゲットIと同様にして半導体膜を成膜した。その結果、ターゲットII〜VIIを用いた場合も、ターゲットIの結果とほぼ同じように、半導体膜を形成することができた。

但し、長期間連続放電した際、ターゲットIを使用した場合に比べ、スパッタリング時の異常放電の頻度やイエローフレークの量の減少が確認できた。

【0119】

[半導体膜の評価]

ターゲットIを使用して形成した上記の半導体膜を、窒素環境下、150℃で2時間の熱処理を行った。

熱処理後の半導体膜について、ホール測定装置にてキャリア濃度及びホール移動度を測定した。その結果、半導体膜はn型を示し、キャリア濃度は4×1017cm−3、ホール移動度は3cm2/Vsであった。

【0120】

また、X線結晶構造解析により非晶質であることが確認された。原子間力顕微鏡(AMF)により測定した表面粗さはRMS0.2nmであった。また光学的に求めたバンドギャップは3.9eVであった。

【0121】

また、77〜300Kの範囲で測定温度を変化させホール効果を測定すると熱活性型を示し、半導体膜は非縮退半導体であることが確認できた。

また、温度を変化させホール効果を用い測定したキャリア濃度と活性化エネルギーの関係から非局在準位のエネルギー幅(E0)は6meV以下であった。

さらに、X線散乱測定によって求めた動径分布関数(RDF)により、In−Inを表すピークが0.35nm付近に観測され、酸化インジウムのビックスバイト構造の稜共有構造が残っていることが確認できた。原子間距離が0.30から0.36nmの間のRDFの最大値をA、原子間距離が0.36から0.42の間のRDFの最大値をBとした場合のA/Bは、1.5であった。X線吸収分光法によって求めたIn−Inの平均結合距離が0.317nmであった。

【0122】

[電解効果型トランジスタの作製]

実施例38

基板にガラス基板を使用した他は、図1に示す電界効果型トランジスタと同様のトランジスタを作製した。

ガラス基板上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極を作製した。

次に、ゲート電極を作製した基板にプラズマ化学気相成長装置(PECVD)にて、SiNxを300℃で成膜(厚さ200nm)し、ゲート絶縁膜とした。

次に、実施例31で製造したターゲットIを用い、上記ターゲットIの評価時に作製した半導体膜と同じ条件で成膜し、その後パターニングして半導体層を形成した。

次に、リフトオフプロセス及びRFマグネトロンスパッタリング(室温、Ar100%)を用い、In2O3−ZnOからなるソース/ドレイン電極を形成した。

その後、窒素環境下、150℃で2時間熱処理して、電界効果型トランジスタを製造した(図2のWが50μm、Lが4μmのボトムゲート型の電界効果型トランジスタ)。

【0123】

この電界効果型トランジスタについて、実施例1と同様に評価した。測定結果を表6に示す。

【0124】

実施例39〜61、比較例11〜18

原料である酸化インジウム、酸化亜鉛及びX元素の酸化物の混合比を、表6−9に示す組成となるように調製した他は、実施例31と同様にしてスパッタリングターゲットを製造した。

上記のスパッタリングターゲットを使用し、成膜条件を表6−9に示すように変更した他は、実施例38と同様にして電界効果型トランジスタを作製し、評価した。

尚、スパッタリングターゲットの製造時に、酸化アルミニウムに代えて使用した原料は以下のとおりである。

実施例49:B2O3、株式会社高純度化学研究所社製、BBO06PB

実施例50:Y2O3、株式会社高純度化学研究所社製、YYO03PB

実施例51:Sc2O3、株式会社高純度化学研究所社製、SCO01PB

実施例52:CeO2、株式会社高純度化学研究所社製、CEO05PB

実施例53:Nd2O3、株式会社高純度化学研究所社製、NDO01PB

実施例54:Sm2O3、株式会社高純度化学研究所社製、SMO01PB

実施例55:Gd2O3、株式会社高純度化学研究所社製、GDO01PB

実施例56:Tb2O3、株式会社高純度化学研究所社製、TBO02PB

実施例57:Yb2O3、株式会社高純度化学研究所社製、YBO02PB

【0125】

実施例58では、ソース/ドレイン電極を形成したあとに、RFマグネトロンスパッタリングでSiO2を300nm成膜して保護層を形成し、図4に示す電解効果型トランジスタを作製した。

【0126】

実施例59では、半導体層の形成をDCスパッタリングで行った。ターゲットをDCマグネトロンスパッタリング成膜装置(神港精機(株)製)に装着し、ガラス基板(コーニング1737)上に半導体層を成膜した。

ここでのスパッタ条件としては、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar99%及び酸素1.0%、スパッタ圧力(全圧);2×10−1Pa、投入電力100W、成膜時間8分間、S−T距離100mmとした。

成膜前に、チャンバーを十分にベーキングし、到達圧力を十分に下げ、ロードロックを用い基板を投入することで、成膜時の水分圧を低減した。四重極質量分析器(Q−mass)でスパッタチャンバー中のH2O(水)を分析し、成膜時の水分圧を測定したところ1×10−6Pa以下であった。

【0127】

実施例60では、SiO2熱酸化膜付シリコン基板を使用した。SiO2熱酸化膜の厚みは100nmであった。このトランジスタでは、ゲート絶縁膜がSiO2熱酸化膜であり、シリコン基板がゲート電極と基板の役割を果たす。

SiO2熱酸化膜付シリコン基板上に、半導体層、ソース電極及びドレイン電極を実施例38と同様にして形成した。

【0128】

【表6】

【0129】

【表7】

【0130】

【表8】

【0131】

【表9】

【0132】

尚、比較例17の薄膜は、X線吸収分光法によって求めたIn−Inの平均結合距離が0.325nmであった。さらに、ホール効果を用い測定したキャリア濃度と活性化エネルギーの関係から求めた非局在準位のエネルギー幅(E0)は22meVであった。

【0133】

[熱処理温度と効果]

図7に、実施例41、61及び比較例14と同じ組成の半導体層について、熱処理温度と移動度との関係を示した。尚、処理時間は2時間である。

実施例41の組成では150℃の処理で移動度が安定するのに対して、実施例61の組成では移動度を安定させるのに300℃以上の処理温度が必要であり、比較例14では400℃以上で熱処理しても効果がないことが確認された。

【産業上の利用可能性】

【0134】

本発明の電解効果型トランジスタは、論理回路、メモリ回路、差動増幅回路等の集積回路に適用できる。特に、液晶ディスプレイ又は有機ELディスプレイを駆動させるスイッチング素子として使用できる。

【技術分野】

【0001】

本発明は、酸化物半導体膜をチャンネル層に用いた電界効果型トランジスタ、及びその製造方法に関する。

【背景技術】

【0002】

薄膜トランジスタ(TFT)等の電界効果型トランジスタは、半導体メモリ集積回路の単位電子素子、高周波信号増幅素子、液晶駆動用素子等として広く用いられており、現在、最も多く実用されている電子デバイスである。

なかでも、近年における表示装置のめざましい発展に伴い、液晶表示装置(LCD)、エレクトロルミネッセンス表示装置(EL)、フィールドエミッションディスプレイ(FED)等の各種の表示装置において、表示素子に駆動電圧を印加して表示装置を駆動させるスイッチング素子として、TFTが多用されている。

【0003】

電界効果型トランジスタの主要部材である半導体層(チャンネル層)の材料としては、シリコン半導体化合物が最も広く用いられている。一般に、高速動作が必要な高周波増幅素子や集積回路用素子等には、シリコン単結晶が用いられている。一方、液晶駆動用素子等には、大面積化の要求から非晶性シリコン半導体(アモルファスシリコン)が用いられている。

【0004】

例えば、TFTとして、ガラス等の基板上にゲ−ト電極、ゲ−ト絶縁層、水素化アモルファスシリコン(a−Si:H)等の半導体層、ソ−ス及びドレイン電極を積層した逆スタガ構造のものがある。このTFTは、イメ−ジセンサを始め、大面積デバイスの分野において、アクティブマトリスク型の液晶ディスプレイに代表されるフラットパネルディスプレイ等の駆動素子として用いられている。これらの用途では、従来アモルファスシリコンを用いたものでも高機能化に伴い作動の高速化が求められている。

【0005】

現在、表示装置を駆動させるスイッチング素子としては、シリコン系の半導体膜を用いた素子が主流を占めているが、それは、シリコン薄膜の安定性、加工性の良さの他、スイッチング速度が速い等、種々の性能が良好なためである。そして、このようなシリコン系薄膜は、一般に化学蒸気析出法(CVD)法により製造されている。

【0006】

ところで、結晶性のシリコン系薄膜は、結晶化を図る際に、例えば、800℃以上の高温が必要となり、ガラス基板上や有機物基板上への構成が困難である。このため、シリコンウェハーや石英等の耐熱性の高い高価な基板上にしか形成できず、また、製造に際して多大なエネルギーと工程数を要する等の問題があった。

また、結晶性のシリコン系薄膜は、通常TFTの素子構成がトップゲート構成に限定されるためマスク枚数の削減等コストダウンが困難であった。

【0007】

一方、アモルファスシリコンの薄膜は、比較的低温で形成できるものの、結晶性のものに比べてスイッチング速度が遅いため、表示装置を駆動するスイッチング素子として使用したときに、高速な動画の表示に追従できない場合がある。

また、半導体活性層に可視光が照射されると導電性を示し、漏れ電流が発生して誤動作のおそれがある等、スイッチング素子としての特性が劣化するという問題もある。そのため、可視光を遮断する遮光層を設ける方法が知られている。例えば、遮光層としては金属薄膜が用いられている。

しかしながら、金属薄膜からなる遮光層を設けると工程が増えるだけでなく、浮遊電位を持つこととなるので、遮光層をグランドレベルにする必要があり、その場合にも寄生容量が発生するという問題がある。

【0008】

具体的に、解像度がVGAである液晶テレビでは、移動度が0.5〜1cm2/Vsのアモルファスシリコンが使用可能であったが、解像度がSXGA、UXGA、QXGAあるいはそれ以上になると2cm2/Vs以上の移動度が要求される。また、画質を向上させるため駆動周波数を上げるとさらに高い移動度が必要となる。

また、有機ELディスプレイでは電流駆動となるため、DCストレスにより特性が変化するアモルファスシリコンを使用すると長時間の使用により画質が低下するという問題があった。

その他、これらの用途に結晶シリコンを使用すると、大面積に対応できなかったり、高温の熱処理が必要なため製造コストが高くなるという問題があった。

【0009】

このような状況下、近年にあっては、シリコン系半導体薄膜よりも安定性が優れるものとして、酸化物を用いた酸化物半導体薄膜が注目されている。

例えば、特許文献1には半導体層として酸化亜鉛を使用したTFTが記載されている。

しかしながら、この半導体層では電界効果移動度が1cm2/V・sec程度と低く、on−off比も小さかった。その上、漏れ電流が発生しやすいため、工業的には実用化が困難であった。また、酸化亜鉛を用いた結晶質を含む酸化物半導体については、多数の検討がなされているが、工業的に一般に行われているスパッタリング法で成膜した場合には、次のような問題があった。

【0010】

即ち、移動度が低い、on−off比が低い、漏れ電流が大きい、ピンチオフが不明瞭、ノーマリーオンになりやすい等、TFTの性能が低くなるおそれがあった。また、耐薬品性が劣るため、ウェットエッチングが難しい等製造プロセスや使用環境の制限があった。さらに、性能を上げるためには高い圧力で成膜する必要があり成膜速度が遅かったり、700℃以上の高温処理が必要である等工業化に問題もあった。また、ボトムゲート構成での電解移動度等のTFT性能が低く、性能を上げるにはトップゲート構成で膜厚を50nm以上にする必要がある等TFT素子構成上の制限もあった。

【0011】

このような問題を解決するために酸化インジウム、酸化亜鉛からなる非晶質の酸化物半導体膜を作製し、薄膜トランジスタを駆動させる方法が検討されている(特許文献2)。しかしながら、このトランジスタでは、性能が不十分であった。また、この酸化物半導体膜を用いた薄膜トランジスタでは、S値を小さく押さえたり、ストレスによる閾値シフトを小さくために、相応の熱履歴(例えば、300℃以上の高温で1時間以上熱処理する等)をかけることが必要であった(非特許文献1)。そのため、移動度が低く、S値が大きいという問題の他に、液晶ディスプレイや有機ELディスプレイ等のTFTとして用いる場合には、耐熱性の高い基板を用いる必要があった。従って、安価なガラス基板によるコストダウンや、基板の樹脂化によるフレキシブルディスプレイの工業化が困難であった。

【0012】

また、酸化インジウム、酸化亜鉛、酸化ガリウムからなる非晶質の酸化物半導体膜を作製し、薄膜トランジスタを駆動させる方法が検討されている(特許文献3、4)。しかしながら、ターゲットの抵抗を下げることやターゲットの密度を上げることが難しく、ターゲットが破損しやすかったり、DCスパッタリング法を用いることが難しかった。また、具体的な検討はガリウムを多量に含まれたものでなされており、アルミニウムを含むものについて検討はされていなかった。従来のガリウムを多量に含んだ半導体層では、S値が大きく、耐熱性が低く、ストレスによる閾値シフトが大きいという問題があった。

【0013】

一方、インジウム及び亜鉛と、アルミニウム等の元素を含む複合酸化物が、透明導電膜として検討されている(特許文献5、非特許文献2参照)。しかしながら、キャリア密度が高くトランジスタとして利用可能なものではなかった。

【特許文献1】特開2003−86808号公報

【特許文献2】US2005/0199959

【特許文献3】特開2007−73701号公報

【特許文献4】特開2007−73312号公報

【特許文献5】特開2000−44236号公報

【非特許文献1】Kim, Chang Jung et al. Highly Stable Ga2O3−In2O3−ZnO TFT for Active−Matrix Organic Light−Emitting Diode Display Application, Electron Devices Meeting, 2006. IEDM ’06. International(ISBN:1−4244−0439−8)

【非特許文献2】K.Tomonaga etal.,J.Vac.Sci.Technol.A23(3),2005,401

【発明の概要】

【発明が解決しようとする課題】

【0014】

本発明は、上記の事情に鑑みなされたものであり、移動度が高く、S値の低い電界効果型トランジスタの提供を目的とする。

また、低温又は短時間の熱履歴でも高い特性の得られる電界効果型トランジスタの製造方法の提供を目的とする。

【課題を解決するための手段】

【0015】

本発明によれば、以下の電界効果型トランジスタ等が提供される。

In元素及びZn元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【0016】

本発明は元素Xの種類により、以下の2つの態様に分けられる。

・本発明の第一の態様

1.In(インジウム)元素及びZn(亜鉛)元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr及びNbからなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

2.前記元素XがZrである1に記載の電界効果型トランジスタ。

3.前記半導体層が非晶質膜であり、その電子キャリア濃度が1013〜1018/cm3であり、バンドギャップが2.0〜6.0eVである1又は2に記載の電界効果型トランジスタ。

4.前記半導体層が非縮退半導体である1〜3のいずれかに記載の電界効果型トランジスタ。

5.In(インジウム)元素及びZn(亜鉛)元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr及びNbからなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層用ターゲット。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

6.上記5に記載のターゲットを用いて、DC又はACスパッタリングにより半導体層を成膜する工程と、前記半導体層を70〜350℃で熱処理する工程を含む、電界効果型トランジスタの製造方法。

【0017】

・本発明の第二の態様

1.In(インジウム)元素及びZn(亜鉛)元素と、Al(アルミニウム)、B(ホウ素)、Sc(スカンジウム)、Y(イットリウム)及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

2.複合酸化物からなる半導体層が元素Xを下記(2)’の原子比で含むことを特徴とする1の電界効果型トランジスタ。

In/(In+X)=0.59〜0.99 (2)’

3.前記元素Xが、Al又はBである1又は2に記載の電界効果型トランジスタ。

4.前記元素Xが、Sc又はYである1又は2に記載の電界効果型トランジスタ。

5.前記元素Xが、ランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)である1又は2に記載の電界効果型トランジスタ。

6.前記半導体層が非晶質膜であり、その電子キャリア濃度が1013〜1018/cm3であり、バンドギャップが2.0〜6.0eVである1〜5のいずれかに記載の電界効果型トランジスタ。

7.前記半導体層が、非縮退半導体である1〜6のいずれかに記載の電界効果型トランジスタ。

8.In(インジウム)元素及びZn(亜鉛)元素と、Al(アルミニウム)、B(ホウ素)、Sc(スカンジウム)、Y(イットリウム)及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群から選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層用ターゲット。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

9.さらに、Sn(錫)、Ge(ゲルマニウム)、Si(シリコン)、Ti(チタン)、Zr(ジルコニウム)及びHf(ハフニウム)からなる群より選択される1以上の元素を100〜10000原子ppm含む8に記載の半導体層用ターゲット。

10.上記8又は9に記載のターゲットを用いて、DC又はACスパッタリングにより半導体層を成膜する工程と、前記半導体層を70〜350℃で熱処理する工程を含む、電界効果型トランジスタの製造方法。

【発明の効果】

【0018】

本発明によれば、移動度が高く、S値の低い電界効果型トランジスタが得られる。また、低温又は短時間の熱履歴で電界効果型トランジスタを製造することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の一実施形態の電界効果型トランジスタの概略断面図である。

【図2】電界効果型トランジスタ1の概略上面図である。

【図3】本発明の他の実施形態の電界効果型トランジスタの概略断面図である。

【図4】本発明の他の実施形態の電界効果型トランジスタの概略断面図である。

【図5】本発明の他の実施形態の電界効果型トランジスタの概略断面図である。

【図6】半導体層の熱処理温度と移動度の関係を示すグラフである。

【図7】半導体層の熱処理温度と移動度の関係を示すグラフである。

【発明を実施するための形態】

【0020】

[本発明の第一の態様]

本発明の電界効果型トランジスタは、In(インジウム)元素及びZn(亜鉛)元素と、下記の群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する。

群:Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr及びNb

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【0021】

半導体層を上記の複合酸化物から形成することによって、移動度が高く、S値の低い電界効果型トランジスタが得られる。また、低温又は短時間の熱履歴(熱処理)でも、高い特性の得られる電界効果型トランジスタとなる。

【0022】

上記(1)においてInの比率が0.2より小さいと、移動度が低くなったり、S値が大きくなったり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下するおそれがある。一方、0.8より大きいと、オフ電流やゲートリーク電流が大きくなったり、S値が大きくなったり、耐プラズマ性が低下したり、閾値が負になりノーマリーオンとなるおそれがある。

In/(In+Zn)は、好ましくは0.3〜0.75であり、より好ましくは0.35〜0.7である。

【0023】

上記(2)においてInの比率が0.29より小さいと、移動度が低くなったり、S値が大きくなったり、閾値電圧が高くなるおそれがある。一方、0.99より大きいと、オフ電流やゲートリーク電流が大きくなったり、閾値が負になりノーマリーオンとなったり、光電流が大きくなったり、耐プラズマ性が低下したり、閾値電圧のシフトが大きくなるおそれがある。

In/(In+X)は、好ましくは0.45〜0.98であり、より好ましくは0.65〜0.98であり、特に好ましくは0.7〜0.97である。

【0024】

上記(3)においてZnの比率が0.29より小さいと、移動度が低くなったり、S値が大きくなったり、安定化させるのに高温あるいは長時間の熱処理が必要となったり、ウェットエッチングレートが遅くなるおそれがある。一方、0.99より大きいと移動度が低くなったり、S値が大きくなったり、熱安定性や耐熱性が低下したり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下したり、閾値電圧のシフトが大きくなるおそれがある。

Zn/(X+Zn)は、好ましくは0.45〜0.98であり、より好ましくは0.6〜0.98であり、さらに好ましくは0.7〜0.97である。

【0025】

本発明においては、半導体層が、さらに、下記(4)の比率(原子比)を満たすことが好ましい。

X/(In+Zn+X)=0.01〜0.2 (4)

Xの比率が0.2より大きいと、S値が大きくなったり、移動度が低下したり、閾値電圧が大きくなったりするおそれがある。一方、0.01より小さいと、熱安定性や耐熱性が低下したり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下したり、閾値電圧のシフトが大きくなるおそれがある。

X/(In+Zn+X)は、0.02〜0.15がより好ましく、特に、0.03〜0.1が好ましい。

【0026】

さらに、用途によって半導体層が、下記(5)あるいは(6)の比率(原子比)を満たすことが特に好ましい。

In/(In+Zn+X)=0.3〜0.5 (5)

In/(In+Zn+X)=0.5〜0.7(0.5を含まない) (6)

上記(5)の比率は、オフ電流を低減しやすくオンオフ比を高くすることができる。また、成膜条件や後処理条件のマージンも広い。上記(6)の比率だと移動度を高く、閾値電圧を小さくすることができる。

【0027】

本発明では、熱安定性、耐熱性、耐薬品性が向上し、S値やオフ電流を低減できることから、元素XはZr又はHfであることが好ましく、Zrであることが特に好ましい。

また、光電流を低減したい場合は、元素XはZr、Hf、Ge、Si、Tiが好ましい。また、プラズマ耐性を高くして後工程で特性が変化しにくくしたい場合は、元素XはCu、Ni、Co、Fe、Cr、Mn、W、Mo、V及びNbが好ましい。

【0028】

[本発明の第二の態様]

本発明の電界効果型トランジスタは、In(インジウム)元素及びZn(亜鉛)元素と、下記のA群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する。

A群:Al(アルミニウム)、B(ホウ素)、Sc(スカンジウム)、Y(イットリウム)及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【0029】

半導体層を上記の複合酸化物から形成することによって、移動度が高く、S値の低い電界効果型トランジスタが得られる。また、低温又は短時間の熱履歴(熱処理)でも、高い特性の得られる電界効果型トランジスタとなる。

【0030】

上記(1)においてInの比率が0.2より小さいと、移動度が低くなったり、S値が大きくなったり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下するおそれがある。一方、0.8より大きいと、オフ電流やゲートリーク電流が大きくなったり、S値が大きくなったり、耐プラズマ性が低下したり、閾値が負になりノーマリーオンとなるおそれがある。

In/(In+Zn)は、好ましくは0.3〜0.75であり、より好ましくは0.35〜0.7である。

【0031】

上記(2)においてInの比率が0.29より小さいと、移動度が低くなったり、S値が大きくなったり、閾値電圧が高くなるおそれがある。一方、0.99より大きいと、オフ電流やゲートリーク電流が大きくなったり、閾値が負になりノーマリーオンとなったり、光電流が大きくなったり、耐プラズマ性が低下したり、閾値電圧のシフトが大きくなるおそれがある。

In/(In+X)は、通常は0.29〜0.99、好ましくは0.59〜0.98、より好ましくは0.6〜0.97であり、さらに好ましくは0.65〜0.96であり、特に好ましくは0.7〜0.95である。

【0032】

上記(3)においてZnの比率が0.29より小さいと、移動度が低くなったり、S値が大きくなったり、安定化させるのに高温あるいは長時間の熱処理が必要となったり、ウェットエッチングレートが遅くなるおそれがある。一方、0.99より大きいと移動度が低くなったり、S値が大きくなったり、熱安定性や耐熱性が低下したり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下したり、閾値電圧のシフトが大きくなるおそれがある

Zn/(X+Zn)は、好ましくは0.45〜0.98であり、より好ましくは0.6〜0.98であり、さらに好ましくは0.7〜0.97であり、特に好ましくは0.75〜0.90である。

【0033】

本発明においては、半導体層が、さらに、下記(4)の比率(原子比)を満たすことが好ましい。

X/(In+Zn+X)=0.02〜0.3 (4)

Xの比率が0.3より大きいと、S値が大きくなったり、移動度が低下したり、閾値電圧が大きくなったりするおそれがある。一方、0.02より小さいと熱安定性や耐熱性が低下したり、耐湿性が低下したり、酸・アルカリ等への耐薬品性が低下したり、オフ電流が大きくなったり、閾値電圧のシフトが大きくなるおそれがある。

X/(In+Zn+X)は、0.04〜0.25がより好ましく、0.055〜0.2がさらに好ましく、0.06〜0.15が特に好ましい。

【0034】

さらに、半導体層が、下記(5)又は(6)の比率(原子比)を満たすことが、用途により使い分けることができ特に好ましい。

In/(In+Zn+X)=0.3〜0.5 (5)

In/(In+Zn+X)=0.5〜0.7(0.5は含まない) (6)

上記(5)の比率では、オフ電流を低減しやすく、オンオフ比を高くすることができる。また、成膜条件や後処理条件のマージンも広い。上記(6)の比率だと移動度を高く、閾値電圧を小さくすることができる。

【0035】

本発明において元素Xは、Al又はBであることが好ましい。また、Sc又はYである場合も好ましい。さらに、ランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)である場合も好ましい。

【0036】

本発明の電界効果型トランジスタは、上述した第一の態様又は第二の態様で示した半導体層を有していれば、他の構成については特に限定はない。トップゲート型やボトムゲート型等、公知の構造を利用することができる。以下、電界効果型トランジスタの構成例について図面を参照して説明する。

【0037】

図1は、本発明の一実施形態の電界効果型トランジスタの概略断面図である。

電界効果型トランジスタ1はボトムゲート型であり、熱酸化膜11を有するシリコン基板10上に、ゲート電極12がストライプ状に形成されている。このゲート電極12を覆うようにゲート絶縁膜13を有し、このゲート絶縁膜13上であって、かつ、ゲート電極12上に半導体層14(活性層)が形成されている。

半導体層14の一端14aに、ゲート電極12と直交する方向にソース電極15が接続されている。また、半導体層14の一端14aに対向する他端14bにドレイン電極16が接続されている。

【0038】

図2は、ゲート電極12、半導体層14、ソース電極15及びドレイン電極16の位置関係を示す概略上面図である。位置関係の可視化のため一部の部材を省略してある。

【0039】

ボトムゲート型の電界効果型トランジスタの場合、半導体層は保護層で保護していることが好ましい。ボトムゲート型のトランジスタでは保護層が無いと半導体層の主要部分が露出するため保護層の効果が大きい。

図3及び図4は、本発明の他の実施形態の電界効果型トランジスタの概略断面図である。

電界効果型トランジスタ2及び3は、保護層17を形成している他は、上述した電界効果型トランジスタ1と同じ構成をしている。

【0040】

図5は、トップゲート型の電界効果型トランジスタの例を示す概略断面図である。

電界効果型トランジスタ4では、基板30上にソース電極35及びドレイン電極36が形成され、その間隙及びこれら電極の一部を覆うように半導体層34が設けられている。そして、半導体層34にゲート絶縁膜33を介してゲート電極32が形成されている。

トランジスタ3では、基板30が保護層37の役割をしている。

【0041】

以下、本発明の電界効果型トランジスタを構成部材について説明する。

1.基板

特に制限はなく、本技術分野で公知のものを使用できる。例えば、ケイ酸アルカリ系ガラス、無アルカリガラス、石英ガラス等のガラス基板、シリコン基板、アクリル、ポリカーボネート、ポリエチレンナフタレート(PEN)等の樹脂基板、ポリエチレンテレフタレート(PET)、ポリアミド等の高分子フィルム基材等が使用できる。

基板や基材の厚さは0.1〜10mmが一般的であり、0.3〜5mmが好ましい。ガラス基板の場合は、化学的に、或いは熱的に強化させたものが好ましい。

透明性や平滑性が求められる場合は、ガラス基板、樹脂基板が好ましく、ガラス基板が特に好ましい。軽量化が求められる場合は樹脂基板や高分子機材が好ましい。

【0042】

2.半導体層

半導体層は、上述した第一の態様又は第二の態様で示したIn(インジウム)、Zn(亜鉛)及び元素Xを上記(1)〜(3)の比率、好ましくは(1)〜(4)の比率を満たすように含有する複合酸化物からなる。

このような半導体層は、例えば、本発明の複合酸化物ターゲット(半導体層用ターゲット)を使用して薄膜を形成することで作製できる。

【0043】

本発明の半導体層用ターゲットは、上述した第一の態様又は第二の態様で示した比率(1)〜(3)又は(1)〜(4)を満たす複合酸化物の焼結体からなる。このターゲットは、例えば、酸化インジウム、酸化亜鉛及び元素Xの酸化物を、上記の元素比率を満たすように含む混合粉体を原料とする。原料粉体をボールミル等で微粉体化した後、ターゲット状に成形し焼成することによって作製できる。

尚、使用する原料粉体の一部は、ターゲットの端材や使用済みターゲット等の高純度酸化インジウム含有スクラップから回収して作製したものであってもよい。特に、ITOターゲットから回収した酸化インジウムは不純物としてSn(錫)を適度に含んでおり好ましい。酸化インジウムの回収は特開2002−069544号に記載の方法等、公知の方法を用いることができる。

尚、上述した第一の態様で示した元素XがZr、Hf、Ge、Si、Ti、V及びNbであると、特に外観のよく抗折力の高いターゲットを製造しやすい。

【0044】

各原料粉の純度は、通常99.9%(3N)以上、好ましくは99.99%(4N)以上、さらに好ましくは99.995%以上、特に好ましくは99.999%(5N)以上である。各原料粉の純度が99.9%(3N)未満だと、不純物により半導体特性が低下したり、色むらや斑点などの外観上の不良が発生したり、信頼性が低下する等のおそれがある。

原料粉について、酸化インジウム粉の比表面積を8〜10m2/g、酸化亜鉛粉の比表面積を2〜4m2/g、元素Xの酸化物の比表面積を5〜10m2/g(より好ましくは8〜10m2/g)とすることが好ましい。又は、酸化インジウム粉のメジアン径を0.2〜2μm、酸化亜鉛粉のメジアン径を0.8〜1.6μmとすることが好ましい。

尚、酸化インジウム粉の比表面積と元素Xの酸化物粉の比表面積が、ほぼ同じである粉末を使用することが好ましい。これにより、より効率的に粉砕混合できる。具体的には、比表面積の差を5m2/g以下にすることが好ましい。比表面積が違いすぎると、効率的な粉砕混合が出来ず、焼結体中に元素Xの酸化物の粒子が残る場合がある。

【0045】

混合粉体を、例えば、湿式媒体撹拌ミルを使用して混合粉砕する。このとき、粉砕後の比表面積が原料混合粉体の比表面積より1.5〜2.5m2/g増加する程度か、又は粉砕後の平均メジアン径が0.6〜1μmとなる程度に粉砕することが好ましい。このように調整した原料粉を使用することにより、仮焼工程を全く必要とせずに、高密度の酸化物焼結体を得ることができる。また、還元工程も不要となる。

尚、原料混合粉体の比表面積の増加分が1.0m2/g未満又は粉砕後の原料混合粉の平均メジアン径が1μmを超えると、焼結密度が十分に大きくならない場合がある。一方、原料混合粉体の比表面積の増加分が3.0m2/gを超える場合又は粉砕後の平均メジアン径が0.6μm未満にすると、粉砕時の粉砕器機等からのコンタミ(不純物混入量)が増加する場合がある。

ここで、各粉体の比表面積はBET法で測定した値である。各粉体の粒度分布のメジアン径は、粒度分布計で測定した値である。これらの値は、粉体を乾式粉砕法、湿式粉砕法等により粉砕することにより調整できる。

粉砕工程後の原料をスプレードライヤー等で乾燥した後、成形する。成形は公知の方法、例えば、加圧成形、冷間静水圧加圧が採用できる。

【0046】

次いで、得られた成形物を焼結して焼結体を得る。焼結は、1350〜1600℃で2〜20時間焼結することが好ましい。1350℃未満では、密度が向上せず、また、1600℃を超えると亜鉛が蒸散し、焼結体の組成が変化したり、蒸散により焼結体中にボイド(空隙)が発生したりする場合がある。

また、焼結は酸素を流通することにより酸素雰囲気中で焼結するか、加圧下にて焼結するのがよい。これにより亜鉛の蒸散を抑えることができ、ボイド(空隙)のない焼結体が得られる。

このようにして製造した焼結体は、密度が高いため、使用時におけるノジュールやパーティクルの発生が少ないことから、膜特性に優れた酸化物半導体膜を作製することができる。

【0047】

酸化物焼結体は、研磨等の加工を施すことによりターゲットとなる。具体的には、焼結体を、例えば、平面研削盤で研削して表面粗さRaを5μm以下とする。さらに、ターゲットのスパッタ面に鏡面加工を施して、平均表面粗さRaが1000オングストローム以下としてもよい。この鏡面加工(研磨)は機械的な研磨、化学研磨、メカノケミカル研磨(機械的な研磨と化学研磨の併用)等の、すでに知られている研磨技術を用いることができる。例えば、固定砥粒ポリッシャー(ポリッシュ液:水)で#2000以上にポリッシングしたり、又は遊離砥粒ラップ(研磨材:SiCペースト等)にてラッピング後、研磨材をダイヤモンドペーストに換えてラッピングすることによって得ることができる。このような研磨方法には特に制限はない。

【0048】

得られたターゲットをバッキングプレートへボンディングすることにより、各種成膜装置に装着して使用できる。成膜法としては、例えば、スパッタリング法、PLD(パルスレーザーディポジション)法、真空蒸着法、イオンプレーティング法等が挙げられる。

【0049】

尚、ターゲットの清浄処理には、エアーブローや流水洗浄等を使用できる。エアーブローで異物を除去する際には、ノズルの向い側から集塵機で吸気を行なうとより有効に除去できる。

エアーブローや流水洗浄の他に、超音波洗浄等を行なうこともできる。超音波洗浄では、周波数25〜300KHzの間で多重発振させて行なう方法が有効である。例えば周波数25〜300KHzの間で、25KHz刻みに12種類の周波数を多重発振させて超音波洗浄を行なうのがよい。

【0050】

酸化物焼結体中における各化合物の粒径は、それぞれ20μm以下が好ましく、10μm以下がさらに好ましく、5μm以下が特に好ましい。尚、粒径は電子プローブマイクロアナライザ(EPMA)で測定した平均粒径である。結晶粒径は、例えば、原料である酸化インジウム、X元素の酸化物、酸化亜鉛の各粉体の配合比や原料粉体の粒径、純度、昇温時間、焼結温度、焼結時間、焼結雰囲気、降温時間を調製することにより得られる。化合物の粒径が20μmより大きいとスパッタ時にノジュールが発生するおそれがある。

【0051】

ターゲットの密度は、理論密度の95%以上が好ましく、98%以上がより好ましく、99%以上が特に好ましい。ターゲットの密度が95%より小さいと強度が不十分となり成膜時にターゲットが破損するおそれがある。また、トランジスタを作製した際に性能が不均一になるおそれがある。

ここで、ターゲットの理論相対密度は、各酸化物の比重(例えば、ZnOは5.66g/cm3、In2O3は7.12g/cm3、ZrO2は5.98g/cm3)とその量比から密度を計算し、アルキメデス法で測定した密度との比率を計算して理論相対密度とする。

【0052】

ターゲットのバルク抵抗は、20mΩ以下が好ましく、10mΩ以下がより好ましく、5mΩ以下がさらに好ましく、2mΩcm以下が特に好ましい。。20mΩより大きいとDCスパッタでの成膜時にターゲットが破損するおそれがある。また、異常放電によりスパークが発生し、ターゲットが割れたり、スパークにより飛び出した粒子が成膜基板に付着し、酸化物半導体膜としての性能を低下させたりする場合がある。また、放電時にターゲットが割れるおそれもある。

尚、バルク抵抗は抵抗率計を使用し、四探針法により測定した値である。

【0053】

本発明のターゲットの抗折力は、8kg/mm2以上であることが好ましく、10kg/mm2以上であることがより好ましく、12kg/mm2以上であることが特に好ましい。ターゲットの運搬、取り付け時に荷重がかかり、ターゲットが破損するおそれがあるという理由で、ターゲットには、一定以上の抗折力が要求され、8kg/mm2未満では、ターゲットとしての使用に耐えられないおそれがある。ターゲットの抗折力は、JIS R 1601に準じて測定することができる。

【0054】

尚、本発明の第二の態様に関するターゲットでは、さらに、Sn(錫)、Ge(ゲルマニウム)、Si(シリコン)、Ti(チタン)、Zr(ジルコニウム)及びHf(ハフニウム)からなる群より選択される1以上の元素を、100〜10000ppm含むことが好ましい。これらの元素を含むと、ターゲットの密度の向上、強度の向上、抵抗の低下、色むらの減少、均一性の向上、異常放電やイエローフレークの減少等の効果があり、半導体用ターゲットとして品質が向上することが期待できる。

上記元素は、これらの元素を含む焼結体(ターゲット)から回収した原料を用いて、不純物として含まれていてもよい。また、原料に金属粉体や酸化物として添加してもよい。

【0055】

本発明において、半導体層は非晶質膜であることが好ましい。

非晶質膜であることにより、絶縁膜や保護層との密着性が改善されたり、大面積でも均一なトランジスタ特性が容易に得られることとなる。

ここで、半導体層が非晶質膜であるかは、X線結晶構造解析により確認できる。明確なピークが観測されない場合が非晶質である。

【0056】

また、半導体層の電子キャリア濃度が1013〜1018/cm3であることが好ましく、特に1014〜1017/cm3であることが好ましい。

電子キャリア濃度が上記の範囲であれば、非縮退半導体となりやすく、トランジスタとして用いた際に移動度とオンオフ比のバランスが良好となり好ましい。

また、バンドギャップが2.0〜6.0eVであることが好ましく、特に、2.8〜5.0eVがより好ましい。バンドギャップは、2.0eVより小さいと可視光を吸収し電界効果型トランジスタが誤動作するおそれがある。一方、6.0eVより大きいとキャリアが供給されにくくなり電界効果型トランジスタが機能しなくなるおそれがある。

【0057】

半導体層は、熱活性型を示す非縮退半導体であることが好ましい。縮退半導体であるとキャリアが多すぎてオフ電流・ゲートリーク電流が増加したり、閾値が負になりノーマリーオンとなるおそれがある。

半導体層が非縮退半導体であるかは、ホール効果を用いた移動度とキャリア密度の温度変化の測定を行うことにより判断できる。

また、半導体層を非縮退半導体とするには、成膜時の酸素分圧を調整したり、後処理をすることで酸素欠陥量を制御しキャリア密度を最適化することで達成できる。

【0058】

半導体層の表面粗さ(RMS)は、1nm以下が好ましく、0.6nm以下がさらに好ましく、0.3nm以下が特に好ましい。1nmより大きいと、移動度が低下するおそれがある。

【0059】

半導体層は、酸化インジウムのビックスバイト構造の稜共有構造の少なくとも一部を維持している非晶質膜であることが好ましい。酸化インジウムを含む非晶質膜が酸化インジウムのビックスバイト構造の稜共有構造の少なくとも一部を維持しているかどうかは、高輝度のシンクロトロン放射等を用いた微小角入射X線散乱(GIXS)によって求めた動径分布関数(RDF)により、In−X(Xは,In,Zn)を表すピークが0.30から0.36nmの間にあることで確認できる。詳細については、下記の文献を参照すればよい。

F.Utsuno, et al.,Thin Solid Films,Volume 496, 2006, Pages 95−98

【0060】

さらに、原子間距離が0.30から0.36nmの間のRDFの最大値をA、原子間距離が0.36から0.42の間のRDFの最大値をBとした場合に、A/B>0.7の関係を満たすことが好ましく、A/B>0.85がより好ましく、A/B>1がさらに好ましく、A/B>1.2が特に好ましい。

A/Bが0.7以下だと、半導体層をトランジスタの活性層として用いた場合、移動度が低下したり、閾値やS値が大きくなりすぎるおそれがある。A/Bが小さいことは、非晶質膜の近距離秩序性が悪いことを反映しているものと考えられる。

【0061】

また、In−Inの平均結合距離が0.3〜0.322nmであることが好ましく、0.31〜0.32nmであることが特に好ましい。In−Inの平均結合距離はX線吸収分光法により求めることができる。X線吸収分光法による測定では、立ち上がりから数百eVも高いエネルギーのところまで広がったX線吸収広域微細構造(EXAFS)を示す。EXAFSは励起された原子の周囲の原子による電子の後方散乱によって引き起こされる。飛び出していく電子波と後方散乱された波との干渉効果が起こる。干渉は電子状態の波長と周囲の原子へ行き来する光路長に依存する。EXAFSをフーリエ変換することで動径分布関数(RDF)が得られる。RDFのピークから平均結合距離を見積もることができる。

【0062】

半導体層の膜厚は、通常0.5〜500nm、好ましくは1〜150nm、より好ましくは3〜80nm、特に好ましくは10〜60nmである。0.5nmより薄いと工業的に均一に成膜することが難しい。一方、500nmより厚いと成膜時間が長くなり工業的に採用できない。また、3〜80nmの範囲内にあると、移動度やオンオフ比等TFT特性が特に良好である。

【0063】

本発明では、半導体層が非晶質膜であり、非局在準位のエネルギー幅(E0)が14meV以下であることが好ましい。半導体層の非局在準位のエネルギー幅(E0)は10meV以下がより好ましく、8meV以下がさらに好ましく6meV以下が特に好ましい。

非局在準位のエネルギー幅(E0)が14meVより大きいと、半導体層をトランジスタの活性層として用いた場合、移動度が低下したり、閾値やS値が大きくなりすぎるおそれがある。半導体層の非局在準位のエネルギー幅(E0)が大きいことは、非晶質膜の近距離秩序性が悪いことを反映しているものと考えられる。

【0064】

3.半導体層の保護層

電界効果型トランジスタは、半導体の保護層があることが好ましい。半導体の保護層が無いと、真空中や低圧下で半導体の表面層の酸素が脱離し、オフ電流が高くなったり、閾値電圧が負になるおそれがある。また、大気下でも湿度等周囲の影響を受け、閾値電圧等のトランジスタ特性のばらつきが大きくなるおそれがある。

【0065】

半導体の保護層を形成する材料は特に制限はない。本発明の効果を失わない範囲で一般に用いられているものを任意に選択できる。例えば、SiO2,SiNx,Al2O3,Ta2O5,TiO2,MgO,ZrO2,CeO2,K2O,Li2O,Na2O,Rb2O,Sc2O3,Y2O3,Hf2O3,CaHfO3,PbTi3,BaTa2O6,SrTiO3,AlN等を用いることができる。これらのなかでも、SiO2,SiNx,Al2O3,Y2O3,Hf2O3,CaHfO3を用いるのが好ましく、より好ましくはSiO2,SiNx,Y2O3,Hf2O3,CaHfO3であり、特に好ましくはSiO2,Y2O3,Hf2O3,CaHfO3等の酸化物である。これらの酸化物の酸素数は、必ずしも化学量論比と一致していなくともよい(例えば、SiO2でもSiOxでもよい)。また、SiNxは水素元素を含んでいても良い。

【0066】

このような保護膜は、異なる2層以上の絶縁膜を積層した構造でもよい。

また、保護層は、結晶質、多結晶質、非晶質のいずれであってもよいが、工業的に製造しやすい多結晶質か、非晶質であるのが好ましい。しかし、保護層が非晶質であることが特に好ましい。非晶質膜でないと界面の平滑性が悪く移動度が低下したり、閾値電圧やS値が大きくなりすぎるおそれがある。

【0067】

半導体層の保護層は、非晶質酸化物あるいは非晶質窒化物であることが好ましく、非晶質酸化物であることが特に好ましい。また、保護層が酸化物でないと半導体中の酸素が保護層側に移動し、オフ電流が高くなったり、閾値電圧が負になりノーマリーオフを示すおそれがある。

また、半導体層の保護層は、ポリ(4−ビニルフェノール)(PVP)、パリレン等の有機絶縁膜を用いてもよい。さらに、半導体層の保護層は無機絶縁膜及び有機絶縁膜の2層以上積層構造を有してもよい。

【0068】

4.ゲート絶縁膜

ゲート絶縁膜を形成する材料にも特に制限はない。本実施形態の発明の効果を失わない範囲で一般に用いられているものを任意に選択できる。例えば、SiO2,SiNx,Al2O3,Ta2O5,TiO2,MgO,ZrO2,CeO2,K2O,Li2O,Na2O,Rb2O,Sc2O3,Y2O3,Hf2O3,CaHfO3,PbTi3,BaTa2O6,SrTiO3,AlN等を用いることができる。これらのなかでも、SiO2,SiNx,Al2O3,Y2O3,Hf2O3,CaHfO3を用いるのが好ましく、より好ましくはSiO2,SiNx,Y2O3,Hf2O3,CaHfO3である。これらの酸化物の酸素数は、必ずしも化学量論比と一致していなくともよい(例えば、SiO2でもSiOxでもよい)。また、SiNxは水素元素を含んでいても良い。

【0069】

このようなゲート絶縁膜は、異なる2層以上の絶縁膜を積層した構造でもよい。また、ゲート絶縁膜は、結晶質、多結晶質、非晶質のいずれであってもよいが、工業的に製造しやすい多結晶質か、非晶質であるのが好ましい。

また、ゲート絶縁膜は、ポリ(4−ビニルフェノール)(PVP)、パリレン等の有機絶縁膜を用いてもよい。さらに、ゲート絶縁膜は無機絶縁膜及び有機絶縁膜の2層以上積層構造を有してもよい。

【0070】

5.電極

ゲート電極、ソ−ス電極及びドレイン電極の各電極を形成する材料に特に制限はなく、本発明の効果を失わない範囲で一般に用いられているものを任意に選択することができる。

例えば、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物、ZnO、SnO2等の透明電極や、Al,Ag,Cr,Ni,Mo,Au,Ti,Ta、Cu等の金属電極、又はこれらを含む合金の金属電極を用いることができる。また、それらを2層以上積層して接触抵抗を低減したり、界面強度を向上させることが好ましい。また、ソ−ス電極、ドレイン電極の接触抵抗を低減させるため半導体の電極との界面をプラズマ処理、オゾン処理等で抵抗を調整してもよい。

【0071】

続いて、本発明の電界効果型トランジスタの製造方法について説明する。

本発明の製造方法では、上述した本発明のターゲットを用い、DCあるいはACスパッタリングにより半導体層を成膜する工程と、半導体層を形成した後に70〜350℃で熱処理する工程を含むことを特徴とする。

尚、上述した電界効果型トランジスタの各構成部材(層)は、本技術分野で公知の手法で形成できる。

具体的に、成膜方法としては、スプレー法、ディップ法、CVD法等の化学的成膜方法、又はスパッタ法、真空蒸着法、イオンプレーティング法、パルスレーザーディポジション法等の物理的成膜方法を用いることができる。キャリア密度が制御し易い、及び膜質向上が容易であることから、好ましくは物理的成膜方法を用い、より好ましくは生産性が高いことからスパッタ法を用いる。

【0072】

スパッタリングでは、複合酸化物の焼結ターゲットを用いる方法、複数の焼結ターゲットを用いコスパッタを用いる方法、合金ターゲットを用い反応性スパッタを用いる方法等が利用できる。但し、複数の焼結ターゲットを用いコスパッタを用いる方法や、合金ターゲットを用い反応性スパッタを用いる方法では、均一性や再現性が悪くなる場合や、非局在準位のエネルギー幅(E0)が大きくなる場合があり、移動度が低下したり、閾値電圧が大きくなる等、トランジスタ特性が低下するおそれがある。好ましくは、複合酸化物の焼結ターゲットを用いる。

形成した膜を各種エッチング法によりパターニングできる。

【0073】

本発明では半導体層を、本発明のターゲットを用い、DC又はACスパッタリングにより成膜する。DC又はACスパッタリングを用いることにより、RFスパッタリングの場合と比べて、成膜時のダメージを低減できる。このため、電界効果型トランジスタにおいて、閾値電圧シフトの低減、移動度の向上、閾値電圧の減少、S値の減少等の効果が期待できる。

【0074】

また、本発明では半導体層と半導体の保護層を形成した後に、70〜350℃で熱処理する。70℃より低いと得られるトランジスタの熱安定性や耐熱性が低下したり、移動度が低くなったり、S値が大きくなったり、閾値電圧が高くなるおそれがある。一方、350℃より高いと耐熱性のない基板が使用できないおそれや、熱処理用の設備費用がかかるおそれや、保護層、絶縁膜又は半導体層の界面が劣化するおそれや、水分圧を下げて成膜した際に結晶化し、非晶質膜が得られないおそれがある。

熱処理温度は80〜260℃が好ましく、90〜180℃がより好ましく、100〜150℃がさらに好ましい。特に、熱処理温度が180℃以下であれば、基板としてPEN等の耐熱性の低い樹脂基板を利用できるため好ましい。

【0075】

熱処理時間は、通常1秒〜24時間が好ましいが、処理温度により調整することが好ましい。例えば、70〜180℃では、10分から24時間がより好ましく、20分から6時間がさらに好ましく、30分〜3時間が特に好ましい。180〜260℃では、6分から4時間がより好ましく、15分から2時間がさらに好ましい。260〜300℃では、30秒から4時間がより好ましく、1分から2時間が特に好ましい。300〜350℃では、1秒から1時間がより好ましく、2秒から30分が特に好ましい。

【0076】

熱処理は、不活性ガス中で酸素分圧が10−3Pa以下の環境下で行うか、あるいは半導体層を保護層で覆った後に行うことが好ましい。上記条件下だと再現性が向上する。

不活性ガスとしては、N2、He、Ne、Ar、Kr、Xeが好ましい。

【0077】

本発明の電界効果トランジスタでは、移動度は1cm2/Vs以上が好ましく、3cm2/Vs以上がより好ましく、8cm2/Vs以上が特に好ましい。1cm2/Vsより小さいとスイッチング速度が遅くなり大画面高精細のディスプレイに用いることができないおそれがある。

オンオフ比は、106以上が好ましく、107以上がより好ましく、108以上が特に好ましい。

【0078】

オフ電流は、2pA以下が好ましく、1pA以下がより好ましく、0.5pA以下がさらに好ましく、0.2pA以下が特に好ましい。オフ電流が2pAより大きいとディスプレイのTFTとして用いた場合にコントラストが悪くなったり、画面の均一性が悪くなるおそれがある。

ゲートリーク電流は1pA以下が好ましい。1pAより大きいとディスプレイのTFTとして用いた場合にコントラストが悪くなるおそれがある。

【0079】

閾値電圧は、通常0〜10Vであるが、0〜4Vが好ましく、0〜3Vがより好ましく、0〜2Vが特に好ましい。0Vより小さいとノーマリーオンとなり、オフ時に電圧をかける必要になり消費電力が大きくなるおそれがある。10Vより大きいと駆動電圧が大きくなり消費電力が大きくなったり、高い移動度が必要となるおそれがある。

【0080】

また、S値は0.8V/dec以下が好ましく、0.3V/dec以下がより好ましく、0.25V/dec以下がさらに好ましく、0.2V/dec以下が特に好ましい。0.8V/decより大きいと駆動電圧が大きくなり消費電力が大きくなるおそれがある。特に、有機ELディスプレイで用いる場合は、直流駆動のためS値を0.3V/dec以下にすると消費電力を大幅に低減できるため好ましい。

【0081】

尚、S値(Swing Factor)とは、オフ状態からゲート電圧を増加させた際に、オフ状態からオン状態にかけてドレイン電流が急峻に立ち上がるが、この急峻さを示す値である。下記式で定義されるように、ドレイン電流が1桁(10倍)上昇するときのゲート電圧の増分をS値とする。

S値=dVg/dlog(Ids)

S値が小さいほど急峻な立ち上がりとなる(「薄膜トランジスタ技術のすべて」、鵜飼育弘著、2007年刊、工業調査会)。

S値が大きいと、オンからオフに切り替える際に高いゲート電圧をかける必要があり、消費電力が大きくなるおそれがある。

【0082】

また、10μAの直流電圧50℃で100時間加えた前後の閾値電圧のシフト量は、1.0V以下が好ましく、0.5V以下がより好ましい。1Vより大きいと有機ELディスプレイのトランジスタとして利用した場合、画質が変化してしまうおそれがある。

【0083】

また、伝達曲線でゲート電圧を昇降させた場合のヒステリシスが小さい方が好ましい。

【0084】

また、チャンネル幅Wとチャンネル長Lの比W/L(図2参照。)は、通常0.1〜100、好ましくは0.5〜20、特に好ましくは1〜8である。W/Lが100を越えると漏れ電流が増えたり、on−off比が低下したりするおそれがある。0.1より小さいと電界効果移動度が低下したり、ピンチオフが不明瞭になったりするおそれがある。

【0085】

また、チャンネル長Lは通常0.1〜1000μm、好ましくは1〜100μm、さらに好ましくは2〜10μmである。0.1μm以下は工業的に製造が難しくまた漏れ電流が大きくなるおそれがある、1000μm以上では素子が大きくなりすぎて好ましくない。

【0086】

本発明の電界効果型トランジスタは、半導体層を遮光する構造を持つことが好ましい。半導体層を遮光する構造(例えば、遮光層)を持っていないと、光が半導体層に入射した場合にキャリア電子が励起されオフ電流が高くなるおそれがある。遮光層は、300〜800nmに吸収を持つ薄膜が好ましい。遮光層は半導体層の上部、下部どちらかでも構わないが、上部及び下部の両方にあることが好ましい。また、遮光層はゲート絶縁膜やブラックマトリックス等と兼用されていても構わない。遮光層が片側だけにある場合、遮光層が無い側から光が半導体層に照射しないよう構造上工夫する必要がある。

【0087】

尚、本発明の電界効果型トランジスタでは、半導体層とソース電極あるいはドレイン電極との間にコンタクト層を設けることが好ましい。コンタクト層の形成材料は、上述した半導体層と同様な組成の複合酸化物が使用できる。即ち、コンタクト層はInやZn等、半導体層に含まれる元素を主成分とする酸化物であることが好ましい。これらの元素を含まないと、コンタクト層と半導体層の間で元素の移動が発生し、ストレス試験等を行った際に閾値電圧のシフトが大きくなるおそれがある。

コンタクト層の作製方法に特に制約はないが、成膜条件を変えて半導体層と同じ組成比のコンタクト層を成膜したり、半導体層と組成比の異なる層を成膜したり、半導体の電極とのコンタクト部分をプラズマ処理やオゾン処理により抵抗を高めることで構成したり、半導体層を成膜する際に酸素分圧等の成膜条件により抵抗を高くなる層を構成してもよい。

【0088】

また、本発明の電界効果型トランジスタでは、半導体層とゲート絶縁膜との間、及び/又は半導体層と保護層との間に、半導体層よりも抵抗の高い酸化物抵抗層を有することが好ましい。酸化物抵抗層が無いとオフ電流が発生したり、閾値電圧が負となりノーマリーオンとなるおそれがある。また、保護膜成膜やエッチング等の後処理工程時に半導体層が変質し特性が劣化するおそれがある。

【0089】

酸化物抵抗層としては、以下のものが例示できる。

・半導体膜の成膜時よりも高い酸素分圧で成膜した半導体層と同一組成の非晶質酸化物膜

・半導体層と同一組成であるが組成比を変えた非晶質酸化物膜

・In及びZnを含み半導体層と異なる元素Xを含む非晶質酸化物膜

・酸化インジウムを主成分とする多結晶酸化物膜

・酸化インジウムを主成分とし、Zn、Cu、Co、Ni、Mn、Mgなどの正二価元素を1種以上ドープした多結晶酸化物膜

・半導体層に含まれる組成にさらにCu、Co、Ni、Mn、Fe、Mg、Ca、Sr、Ba、Ag、Auから選ばれる1種以上の元素を加えた非晶質酸化物膜

【0090】

半導体層と同一組成であるが組成比を変えた非晶質酸化物膜や、In及びZnを含み半導体層と異なる元素Xを含む非晶質酸化物膜の場合は、In組成比が半導体層よりも少ないことが好ましい。また、元素Xの組成比が半導体層よりも多いことが好ましい。

【0091】

酸化物抵抗層は、In及びZnの各元素を含む酸化物であることが好ましい。これらを含まないと、酸化物抵抗層と半導体層の間で元素の移動が発生し、ストレス試験等を行った際に閾値電圧のシフトが大きくなるおそれがある。

半導体層に含まれる組成に、さらにCu、Co、Ni、Mn、Fe、Mg、Ca、Sr、Ba、Ag、Auから選ばれる1種以上の元素を加えた非晶質酸化物膜の場合は、In組成比が半導体層よりも少ないことが好ましい。また、Ga組成比が半導体層よりも多いことが好ましい。

【実施例】

【0092】

[第一の態様]

実施例1

(1)スパッタリングターゲットの製造

原料として、酸化インジウム、酸化亜鉛及び酸化ジルコニウムの粉末を、原子比〔In/(In+Zn+Zr)〕が0.48、原子比〔Zn/(In+Zn+Zr)〕が0.50、原子比〔Zr/(In+Zn+Zr)〕が0.02となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径10cm、厚さ5mmの寸法にプレス成形し、これを焼成炉に入れ、1500℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットのバルク抵抗は3mΩ、理論相対密度は0.99であった。また、色むらが無く外観の均一性の高いターゲットが得られた。

尚、理論相対密度は各酸化物の比重とその量比から計算した密度を、アルキメデス法で測定した密度との比率を計算して求めた。

【0093】

(2)トランジスタの作製

基板にガラス基板を使用した他は、図1に示す電界効果型トランジスタと同様のトランジスタを作製した。

ガラス基板上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極を作製した。

次に、ゲート電極を作製した基板にプラズマ化学気相成長装置(PECVD)にて、SiNxを300℃で成膜(厚さ200nm)し、ゲート絶縁膜とした。

次に、(1)で製造したターゲットを、DCスパッタ法の一つであるDCマグネトロンスパッタリング法の成膜装置に装着し、ゲート絶縁膜上に成膜し、その後パターニングして半導体層(膜厚50nm)を形成した。

スパッタ条件は、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar99.5%及び酸素0.5%、スパッタ圧力(全圧);2×10−1Pa、投入電力100W、成膜時間6分間、S−T距離110mmとした。

次に、リフトオフプロセス及びRFマグネトロンスパッタリング(室温、Ar100%)を用い、In2O3−ZnOからなるソース/ドレイン電極を形成した。

その後、窒素環境下、170℃で2時間熱処理して電界効果型トランジスタを製造した(図2のWが40μm、Lが4μmのボトムゲート型の電界効果型トランジスタ)。

【0094】

[半導体層の評価]

ガラス基板(コーニング1737)上に、上記実施例(1)で製造したターゲットを使用して半導体層を形成し評価した。

半導体層の形成は、DCマグネトロンスパッタリング法の成膜装置にて、実施例(2)と同じようにした。この結果、ガラス基板上に、膜厚が50nmの酸化物薄膜が形成された。

【0095】

得られた半導体膜をICP(Inductively Coupled Plasma)法で分析したところ、原子比〔In/(In+Zn+Zr)〕が0.49、原子比〔Zn/(In+Zn+Zr)〕が0.49、原子比〔Ga/(In+Zn+Zr)〕が0.02であった。

【0096】

上記半導体膜を窒素環境下で、170℃で2時間の熱処理を行った。

熱処理後の半導体膜のキャリア濃度及びホール移動度を、ホール測定装置により測定した。結果はn型を示し、キャリア濃度は4×1017cm−3、ホール移動度は2cm2/Vsであった。

尚、ホール測定装置、及びその測定条件は下記のとおりであった、

・ホール測定装置

東陽テクニカ製:Resi Test8310

・測定条件

測定温度:室温(25℃)

測定磁場:0.5T

測定電流:10−12〜10−4A

測定モード:AC磁場ホール測定

【0097】

また、X線結晶構造解析により非晶質であることが確認された。AMFにより測定した表面粗さはRMS0.2nmであった。また光学的に求めたバンドギャップは3.8eVであった。

さらに、77〜300Kの範囲で測定温度を変化させホール効果を測定すると熱活性型を示し、半導体膜は非縮退半導体であることが確認できた。

また、温度を変化させホール効果を用い測定したキャリア濃度と活性化エネルギーの関係から非局在準位のエネルギー幅(E0)は6meV以下であった。

さらに、X線散乱測定によって求めた動径分布関数(RDF)により、In−Inを表すピークが0.35nm付近に観測され、酸化インジウムのビックスバイト構造の稜共有構造が残っていることが確認できた。原子間距離が0.30から0.36nmの間のRDFの最大値をA、原子間距離が0.36から0.42の間のRDFの最大値をBとした場合のA/Bは、1.3であった。X線吸収分光法によって求めたIn−Inの平均結合距離が0.318nmであった。

【0098】

[トランジスタの評価]

電界効果型トランジスタについて、下記の評価を行った。

(1)電界効果移動度(μ)、オンオフ比、オフ電流、ゲートリーク電流、S値、閾値電圧(Vth)

半導体パラメーターアナライザー(ケースレー4200)を用い、室温、大気中、かつ遮光環境下で測定した。

(2)ヒステリシス

半導体パラメーターアナライザーを用い、昇電圧時の伝達曲線(I−V特性)と降電圧時の伝達曲線(I−V特性)を測定し、昇降時の電圧の差をΔVgとする。ΔVgの最大値が0.5V以下であるものを「少ない」、0.5〜3Vであるものを「ある」、3V以上であるものを「大きい」とした。

(3)ストレス試験

ストレス条件は、ゲート電圧15Vで10μAの直流電圧を50℃で100時間加えることとした。ストレスをかける前後のVthを比較し、閾値電圧のシフト量(ΔVth)を測定した。

【0099】

また、耐酸性及び耐湿性を以下のようにして評価した。

(1)耐酸性

実施例1(2)と同じ条件で、ガラス基板上に200nm厚の半導体膜を形成し、熱処理した。これを蓚酸系エッチング液(関東化学製、ITO−06)にてエッチングし、25℃でのエッチング速度を測定した。評価は下記のようにした。

◎:200nm/分未満

○:200〜500nm/分

△:500〜1000nm/分

×:1000nm/分以上

(2)耐湿性

作製したトランジスタを、85℃、85%RHにて、2000時間耐湿試験を実施した。試験前後の抵抗を測定し、下記のように分類した。試験前の抵抗値÷試験後の抵抗値、試験後の抵抗値÷試験前の抵抗値の大きい方を変化率とした。

◎:変化率2倍未満

○:変化率2〜5倍変化

△:変化率5〜100倍変化

×:変化率100倍以上変化

測定結果を表1に示す。

【0100】

実施例2〜29、比較例1〜7

原料である酸化インジウム、酸化亜鉛及びX元素の酸化物の混合比を、表1−4に示す組成となるように調製した他は、実施例1(1)と同様にしてスパッタリングターゲットを製造した。

上記のスパッタリングターゲットを使用し、成膜条件を表1−4に示すように変更した他は、実施例1(2)と同様にして電界効果型トランジスタを作製し、評価した。

尚、スパッタリングターゲットの製造時に、酸化ジルコニウムに代えて使用した原料は以下のとおりである。

実施例12:HfO2、株式会社高純度化学研究所社製、HFO01PB

実施例13:GeO2、株式会社高純度化学研究所社製、GEO06PB

実施例14:SiO2、株式会社高純度化学研究所社製、SIO12PB

実施例15:TiO2、株式会社高純度化学研究所社製、TIO14PB

実施例16:MnO2、株式会社高純度化学研究所社製、MNO03PB

実施例17:WO3、株式会社高純度化学研究所社製、WWO04PB

実施例18:MoO3、株式会社高純度化学研究所社製、MOO03PB

実施例19:V2O5、株式会社高純度化学研究所社製、VVO09PB

実施例20:Nb2O5、株式会社高純度化学研究所社製、NBO08PB

実施例25:CuO、株式会社高純度化学研究所社製、CUO08PB

実施例26:NiO、株式会社高純度化学研究所社製、NIO11PB

実施例27:CoO、株式会社高純度化学研究所社製、COO03PB

実施例28:FeO、株式会社高純度化学研究所社製、FEO01PB

実施例29:Cr2O3、株式会社高純度化学研究所社製、CRO01GB

【0101】

実施例21では、ソース/ドレイン電極を形成したあとに、RFマグネトロンスパッタリングでSiO2を300nm成膜して保護層を形成し、図4に示す電解効果型トランジスタを作製した。

【0102】

実施例22、及び比較例1〜7では、半導体層の形成をRFスパッタリングで行った。具体的に、ターゲットをRFマグネトロンスパッタリング成膜装置に装着し成膜した。

ここでのスパッタ条件は、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar99.5%及び酸素0.5%、スパッタ圧力(全圧);2×10−1Pa、投入電力100W、成膜時間8分間、S−T距離100mmとした。

【0103】

実施例23では、SiO2熱酸化膜付シリコン基板を使用した。SiO2熱酸化膜の厚みは100nmであった。このトランジスタでは、ゲート絶縁膜がSiO2熱酸化膜であり、シリコン基板がゲート電極と基板の役割を果たす。

SiO2熱酸化膜付シリコン基板上に、半導体層、ソース電極及びドレイン電極を実施例1と同様にして形成した。

【0104】

【表1】

【0105】

【表2】

【0106】

【表3】

【0107】

【表4】

【0108】

【表5】

【0109】

[スパッタリングターゲットの例]

実施例30

原料として、酸化インジウム、酸化亜鉛及び酸化ジルコニウムの粉末を、原子比〔In/(In+Zn+Zr)〕が0.4、原子比〔Zn/(In+Zn+Zr)〕が0.4、原子比〔Zr/(In+Zn+Zr)〕が0.2となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径20cm、厚さ5mmの寸法にプレス成形した後、これを焼成炉に入れ、1400℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットのバルク抵抗は5mΩ、理論相対密度は0.98であった。ターゲットの抗折力は、12kg/mm2であった。また、色むらが無く外観の均一性の高いターゲットが得られた。

【0110】

比較例8

原料として、酸化インジウム、酸化亜鉛及び酸化ガリウムの粉末を、原子比〔In/(In+Zn+Ga)〕が0.4、原子比〔Zn/(In+Zn+Ga)〕が0.4、原子比〔Ga/(In+Zn+Ga)〕が0.2となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径20cm、厚さ5mmの寸法にプレス成形した後、これを焼成炉に入れ、1400℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットのバルク抵抗は70mΩ、理論相対密度は0.82であった。ターゲットの抗折力は、7kg/mm2であった。また、ターゲットには若干色むらが確認された。

【0111】

図6に、実施例1及び5と同じ組成の半導体層について、熱処理温度と移動度との関係を示した。尚、処理時間は2時間である。

実施例1の組成では150℃の処理で移動度が安定するのに対して、実施例5の組成では移動度を安定させるのに300℃以上の処理温度が必要であった。

【0112】

[第二の態様]

[スパッタリングターゲットの作製]

実施例31(ターゲットI)

原料として、5N(純度99.999%)の酸化インジウム(株式会社高純度化学研究所社製INO04PB)、5Nの酸化亜鉛(株式会社高純度化学研究所社製ZNO04PB)及び5Nの酸化アルミニウム(株式会社高純度化学研究所社製)の粉末を、原子比〔In/(In+Zn+Al)〕が0.48、原子比〔Zn/(In+Zn+Al)〕が0.50、原子比〔Al/(In+Zn+Al)〕が0.02となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径10cm、厚さ5mmの寸法にプレス成形して、これを焼成炉に入れ、1500℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットを粉砕しICPで分析したところ、Sn(錫)、Ge(ゲルマニウム)、Si(シリコン)、Ti(チタン)、Zr(ジルコニウム)、Hf(ハフニウム)等の不純物は含まれていなかった。また、ターゲットのバルク抵抗は20mΩ、理論相対密度は0.95であった。

【0113】

実施例32(ターゲットII)

原料として、使用済みのITOターゲット等から回収した酸化インジウム、5Nの酸化亜鉛(株式会社高純度化学研究所社製ZNO04PB)及び4Nの酸化アルミニウム(株式会社高純度化学研究所社製ALO12PB)の粉末を、原子比〔In/(In+Zn+Al)〕が0.48、原子比〔Zn/(In+Zn+Al)〕が0.50、原子比〔Al/(In+Zn+Al)〕が0.02となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。

得られた原料微粉末を造粒した後、直径10cm、厚さ5mmの寸法にプレス成形して、これを焼成炉に入れ、1500℃で12時間焼成して、焼結体(ターゲット)を得た。

ターゲットを粉砕しICPで分析したところ、不純物としてSn(錫)500ppmが含まれていた。また、ターゲットのバルク抵抗は3mΩ、理論相対密度は0.99であった。また、色むらが無く外観の均一性の高いターゲットが得られた。

【0114】

実施例33−37(ターゲットIII−VII)

Ge,Si,Ti,Zr又はHf元素を、原料中の金属元素全体に対して500原子ppmとなるように酸化物として添加した他はターゲットIと同じ工程で作製した。ターゲットはターゲットIIとほぼ同じ品質のものが得られたが、外観はさらに均質で綺麗なものが得られた。

【0115】

[スパッタリングターゲットの評価]

・ターゲットI

上記実施例31で作製したターゲットIを、RFスパッタ法の一つであるRFマグネトロンスパッタリング法の成膜装置に装着し、ガラス基板(コーニング1737)上に半導体膜を成膜した。

ここでのスパッタ条件としては、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar99.5%及び酸素0.5%、スパッタ圧力(全圧);2×10−1Pa、投入電力100W、成膜時間8分間、S−T距離100mmとした。

【0116】

この結果、ガラス基板上に、膜厚が70nmの半導体膜が形成された。

尚、得られた膜組成をICP法で分析したところ、原子比〔In/(In+Zn+Al)〕が0.49、原子比〔Zn/(In+Zn+Al)〕が0.49、原子比〔Al/(In+Zn+Al)〕が0.02であった。

【0117】

このように、ターゲットIでは半導体膜を形成することができた。

【0118】

・ターゲットII〜VII

上記のターゲットIと同様にして半導体膜を成膜した。その結果、ターゲットII〜VIIを用いた場合も、ターゲットIの結果とほぼ同じように、半導体膜を形成することができた。

但し、長期間連続放電した際、ターゲットIを使用した場合に比べ、スパッタリング時の異常放電の頻度やイエローフレークの量の減少が確認できた。

【0119】

[半導体膜の評価]

ターゲットIを使用して形成した上記の半導体膜を、窒素環境下、150℃で2時間の熱処理を行った。

熱処理後の半導体膜について、ホール測定装置にてキャリア濃度及びホール移動度を測定した。その結果、半導体膜はn型を示し、キャリア濃度は4×1017cm−3、ホール移動度は3cm2/Vsであった。

【0120】

また、X線結晶構造解析により非晶質であることが確認された。原子間力顕微鏡(AMF)により測定した表面粗さはRMS0.2nmであった。また光学的に求めたバンドギャップは3.9eVであった。

【0121】

また、77〜300Kの範囲で測定温度を変化させホール効果を測定すると熱活性型を示し、半導体膜は非縮退半導体であることが確認できた。

また、温度を変化させホール効果を用い測定したキャリア濃度と活性化エネルギーの関係から非局在準位のエネルギー幅(E0)は6meV以下であった。

さらに、X線散乱測定によって求めた動径分布関数(RDF)により、In−Inを表すピークが0.35nm付近に観測され、酸化インジウムのビックスバイト構造の稜共有構造が残っていることが確認できた。原子間距離が0.30から0.36nmの間のRDFの最大値をA、原子間距離が0.36から0.42の間のRDFの最大値をBとした場合のA/Bは、1.5であった。X線吸収分光法によって求めたIn−Inの平均結合距離が0.317nmであった。

【0122】

[電解効果型トランジスタの作製]

実施例38

基板にガラス基板を使用した他は、図1に示す電界効果型トランジスタと同様のトランジスタを作製した。

ガラス基板上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極を作製した。

次に、ゲート電極を作製した基板にプラズマ化学気相成長装置(PECVD)にて、SiNxを300℃で成膜(厚さ200nm)し、ゲート絶縁膜とした。

次に、実施例31で製造したターゲットIを用い、上記ターゲットIの評価時に作製した半導体膜と同じ条件で成膜し、その後パターニングして半導体層を形成した。

次に、リフトオフプロセス及びRFマグネトロンスパッタリング(室温、Ar100%)を用い、In2O3−ZnOからなるソース/ドレイン電極を形成した。

その後、窒素環境下、150℃で2時間熱処理して、電界効果型トランジスタを製造した(図2のWが50μm、Lが4μmのボトムゲート型の電界効果型トランジスタ)。

【0123】

この電界効果型トランジスタについて、実施例1と同様に評価した。測定結果を表6に示す。

【0124】

実施例39〜61、比較例11〜18

原料である酸化インジウム、酸化亜鉛及びX元素の酸化物の混合比を、表6−9に示す組成となるように調製した他は、実施例31と同様にしてスパッタリングターゲットを製造した。

上記のスパッタリングターゲットを使用し、成膜条件を表6−9に示すように変更した他は、実施例38と同様にして電界効果型トランジスタを作製し、評価した。

尚、スパッタリングターゲットの製造時に、酸化アルミニウムに代えて使用した原料は以下のとおりである。

実施例49:B2O3、株式会社高純度化学研究所社製、BBO06PB

実施例50:Y2O3、株式会社高純度化学研究所社製、YYO03PB

実施例51:Sc2O3、株式会社高純度化学研究所社製、SCO01PB

実施例52:CeO2、株式会社高純度化学研究所社製、CEO05PB

実施例53:Nd2O3、株式会社高純度化学研究所社製、NDO01PB

実施例54:Sm2O3、株式会社高純度化学研究所社製、SMO01PB

実施例55:Gd2O3、株式会社高純度化学研究所社製、GDO01PB

実施例56:Tb2O3、株式会社高純度化学研究所社製、TBO02PB

実施例57:Yb2O3、株式会社高純度化学研究所社製、YBO02PB

【0125】

実施例58では、ソース/ドレイン電極を形成したあとに、RFマグネトロンスパッタリングでSiO2を300nm成膜して保護層を形成し、図4に示す電解効果型トランジスタを作製した。

【0126】

実施例59では、半導体層の形成をDCスパッタリングで行った。ターゲットをDCマグネトロンスパッタリング成膜装置(神港精機(株)製)に装着し、ガラス基板(コーニング1737)上に半導体層を成膜した。

ここでのスパッタ条件としては、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar99%及び酸素1.0%、スパッタ圧力(全圧);2×10−1Pa、投入電力100W、成膜時間8分間、S−T距離100mmとした。

成膜前に、チャンバーを十分にベーキングし、到達圧力を十分に下げ、ロードロックを用い基板を投入することで、成膜時の水分圧を低減した。四重極質量分析器(Q−mass)でスパッタチャンバー中のH2O(水)を分析し、成膜時の水分圧を測定したところ1×10−6Pa以下であった。

【0127】

実施例60では、SiO2熱酸化膜付シリコン基板を使用した。SiO2熱酸化膜の厚みは100nmであった。このトランジスタでは、ゲート絶縁膜がSiO2熱酸化膜であり、シリコン基板がゲート電極と基板の役割を果たす。

SiO2熱酸化膜付シリコン基板上に、半導体層、ソース電極及びドレイン電極を実施例38と同様にして形成した。

【0128】

【表6】

【0129】

【表7】

【0130】

【表8】

【0131】

【表9】

【0132】

尚、比較例17の薄膜は、X線吸収分光法によって求めたIn−Inの平均結合距離が0.325nmであった。さらに、ホール効果を用い測定したキャリア濃度と活性化エネルギーの関係から求めた非局在準位のエネルギー幅(E0)は22meVであった。

【0133】

[熱処理温度と効果]

図7に、実施例41、61及び比較例14と同じ組成の半導体層について、熱処理温度と移動度との関係を示した。尚、処理時間は2時間である。

実施例41の組成では150℃の処理で移動度が安定するのに対して、実施例61の組成では移動度を安定させるのに300℃以上の処理温度が必要であり、比較例14では400℃以上で熱処理しても効果がないことが確認された。

【産業上の利用可能性】

【0134】

本発明の電解効果型トランジスタは、論理回路、メモリ回路、差動増幅回路等の集積回路に適用できる。特に、液晶ディスプレイ又は有機ELディスプレイを駆動させるスイッチング素子として使用できる。

【特許請求の範囲】

【請求項1】

In元素及びZn元素と、

Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【請求項2】

前記元素XがAl、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素であり、

複合酸化物からなる半導体層が元素Xを下記(2)’の原子比で含むことを特徴とする請求項1の電界効果型トランジスタ。

In/(In+X)=0.59〜0.99 (2)’

【請求項3】

前記元素Xが、Al又はBである請求項1又は2に記載の電界効果型トランジスタ。

【請求項4】

前記元素Xが、Sc又はYである請求項1又は2に記載の電界効果型トランジスタ。

【請求項5】

前記元素Xが、ランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)である請求項1又は2に記載の電界効果型トランジスタ。

【請求項6】

前記元素XがZrである請求項1に記載の電界効果型トランジスタ。

【請求項7】

前記半導体層が非晶質膜であり、その電子キャリア濃度が1013〜1018/cm3であり、バンドギャップが2.0〜6.0eVである請求項1〜6のいずれかに記載の電界効果型トランジスタ。

【請求項8】

前記半導体層が、非縮退半導体である請求項1〜7のいずれかに記載の電界効果型トランジスタ。

【請求項9】

In元素及びZn元素と、

Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層用ターゲット。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【請求項10】

前記元素XがAl、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素であり、

さらに、Sn、Ge、Si、Ti、Zr及びHfからなる群より選択される1以上の元素を100〜10000原子ppm含む請求項9に記載の半導体層用ターゲット。

【請求項11】

請求項9又は10に記載のターゲットを用いて、DC又はACスパッタリングにより半導体層を成膜する工程と、

前記半導体層を70〜350℃で熱処理する工程を含む、電界効果型トランジスタの製造方法。

【請求項1】

In元素及びZn元素と、

Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【請求項2】

前記元素XがAl、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素であり、

複合酸化物からなる半導体層が元素Xを下記(2)’の原子比で含むことを特徴とする請求項1の電界効果型トランジスタ。

In/(In+X)=0.59〜0.99 (2)’

【請求項3】

前記元素Xが、Al又はBである請求項1又は2に記載の電界効果型トランジスタ。

【請求項4】

前記元素Xが、Sc又はYである請求項1又は2に記載の電界効果型トランジスタ。

【請求項5】

前記元素Xが、ランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)である請求項1又は2に記載の電界効果型トランジスタ。

【請求項6】

前記元素XがZrである請求項1に記載の電界効果型トランジスタ。

【請求項7】

前記半導体層が非晶質膜であり、その電子キャリア濃度が1013〜1018/cm3であり、バンドギャップが2.0〜6.0eVである請求項1〜6のいずれかに記載の電界効果型トランジスタ。

【請求項8】

前記半導体層が、非縮退半導体である請求項1〜7のいずれかに記載の電界効果型トランジスタ。

【請求項9】

In元素及びZn元素と、

Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層用ターゲット。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

【請求項10】

前記元素XがAl、B、Sc、Y及びランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)からなる群より選択される1以上の元素であり、

さらに、Sn、Ge、Si、Ti、Zr及びHfからなる群より選択される1以上の元素を100〜10000原子ppm含む請求項9に記載の半導体層用ターゲット。

【請求項11】

請求項9又は10に記載のターゲットを用いて、DC又はACスパッタリングにより半導体層を成膜する工程と、

前記半導体層を70〜350℃で熱処理する工程を含む、電界効果型トランジスタの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−80929(P2013−80929A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2012−230042(P2012−230042)

【出願日】平成24年10月17日(2012.10.17)

【分割の表示】特願2009−547088(P2009−547088)の分割

【原出願日】平成20年12月19日(2008.12.19)

【出願人】(000183646)出光興産株式会社 (2,069)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成24年10月17日(2012.10.17)

【分割の表示】特願2009−547088(P2009−547088)の分割

【原出願日】平成20年12月19日(2008.12.19)

【出願人】(000183646)出光興産株式会社 (2,069)

【Fターム(参考)】

[ Back to top ]