量子ドットの形成方法

【課題】GaAs層上に形成されるInAs量子ドットのサイズを適切に制御する。

【解決手段】量子ドットの形成方法は、基板(110)上にGaAsを含んでなる第1半導体層(120)を形成する第1形成工程と、基板の基板温度を摂氏480度及び摂氏530度の間の温度にした後に、第1半導体層の上に、In及びAsを夫々照射して、InAsを含んでなる第2半導体層(130)を形成する第2形成工程とを備える。第2形成工程において、第2半導体層の成長速度を0.02ML/s及び0.1ML/sの間の成長速度とし、第2半導体層の成長量を1.2ML及び2.5MLの間の成長量とすることにより、第2半導体層の第1半導体層と対向しない側の面(130a)にInAsを含んでなる量子ドット(131)を形成する。

【解決手段】量子ドットの形成方法は、基板(110)上にGaAsを含んでなる第1半導体層(120)を形成する第1形成工程と、基板の基板温度を摂氏480度及び摂氏530度の間の温度にした後に、第1半導体層の上に、In及びAsを夫々照射して、InAsを含んでなる第2半導体層(130)を形成する第2形成工程とを備える。第2形成工程において、第2半導体層の成長速度を0.02ML/s及び0.1ML/sの間の成長速度とし、第2半導体層の成長量を1.2ML及び2.5MLの間の成長量とすることにより、第2半導体層の第1半導体層と対向しない側の面(130a)にInAsを含んでなる量子ドット(131)を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えばGaAs等のIII−V族化合物半導体上に、例えばInAs等のIII−V族化合物からなる量子ドットを形成する量子ドットの形成方法の技術分野に関する。

【背景技術】

【0002】

この種の形成方法として、例えば、InGaAs層上に、InAsからなる量子ドットを形成する際の成長温度を、摂氏470度〜540度の範囲を選択することによって、ドット密度を5倍以上調節する技術が提案されている(特許文献1参照)。或いは、AlGaSb化合物半導体上に、In分子線及びAs分子線を照射して、InAs量子ドットを成長させて形成する技術が提案されている。ここでは特に、基板の温度を約摂氏500度、As分子線の照射量を約5.5×10−7Torrとすることによって、波長約1.3μm(マイクロメートル)及び1.55μmの発光をする量子ドットを形成する技術が提案されている(特許文献2参照)。

【0003】

或いは、基板温度摂氏520度、圧力6.65×10−4Paにおいて、GaAsからなるクラッド層に、As及びInを照射し、InAs膜を1.9ML(モノレイヤー)まで結晶成長させグレインを形成する。その後、Inを間欠照射することによって、直径30〜65nm(ナノメートル)のInAsからなる量子ドットを形成する技術が提案されている(特許文献3参照)。

【0004】

或いは、GaAs層上にAs2を供給しながら成長中断を60秒入れた後、In及びAs2を供給して、InAs量子ドットを形成する技術が提案されている。ここでは特に、InAsの成長速度を0.1ML/s(モノレイヤー/秒)、成長温度を摂氏520度とすることによって、量子ドットの表面密度を1.1×1011cm−2とする技術が提案されている(特許文献4参照)。或いは、InGaAsP層上にInAsからなる量子ドットを形成する際の成長温度を、摂氏450度以下にすることによって、量子ドットの横方向のサイズを25nm以下まで縮小する技術が提案されている(特許文献5参照)。

【0005】

【特許文献1】特開2004−528705号公報

【特許文献2】特開2005−93553号公報

【特許文献3】特開2006−269886号公報

【特許文献4】特開2007−53322号公報

【特許文献5】特開2007−157975号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上述の背景技術によれば、量子ドットのサイズを適切に制御することが困難であるという技術的問題点がある。

【0007】

本発明は、例えば上記問題点に鑑みてなされたものであり、量子ドットのサイズを適切に制御することができる量子ドットの形成方法を提供することを課題とする。

【課題を解決するための手段】

【0008】

本発明の量子ドットの形成方法は、上記課題を解決するために、基板上にGaAsを含んでなる第1半導体層を形成する第1形成工程と、前記基板の基板温度を摂氏480度及び摂氏530度の間の温度にした後に、前記第1半導体層の上に、In及びAsを夫々照射して、InAsを含んでなる第2半導体層を形成する第2形成工程とを備え、前記第2形成工程において、前記第2半導体層の成長速度を0.02ML/s及び0.1ML/sの間の成長速度とし、前記第2半導体層の成長量を1.2ML及び2.5MLの間の成長量とすることにより、前記第2半導体層の前記第1半導体層と対向しない側の面にInAsを含んでなる量子ドットを形成する。

【0009】

本発明の量子ドットの形成方法によれば、例えば分子線エピタキシャル(Molecular Beam Epitaxy:MBE)成長装置内に、例えばGaAs等からなる基板を設置した後に、第1形成工程において、基板上にGa及びAsを夫々照射することによって、基板上にGaAsを含んでなる第1半導体層をエピタキシャル成長させて形成する。

【0010】

第2形成工程において、基板温度を摂氏480度及び摂氏530度の間の温度にした後に、第1半導体層の上に、In及びAsを夫々照射して、InAsを含んでなる第2半導体層を形成する。ここに、「摂氏480度及び摂氏530度の間の温度」とは、摂氏480度以上、摂氏530度以下の所定の温度を意味する。この所定の温度は、所望する量子ドットのサイズに応じて決定される。

【0011】

第2形成工程では、第2半導体層の成長速度が0.02ML/s及び0.1ML/sの間の成長速度となるように、例えばMBE成長装置における蒸発源内のInの温度等が設定されると共に、第2半導体層の成長量が1.2ML及び2.5MLの間の成長量となるように、In及びAsが夫々照射されることにより、第2半導体層の第1半導体層と対向しない側の面(即ち、第2半導体層の上面)に、InAsを含んでなる量子ドットが自己組織化成長によって形成される。尚、「0.02ML/s及び0.1ML/sの間の成長速度」とは、0.02ML/s以上、0.1ML/s以下の所定の成長速度を意味する。また、「1.2ML及び2.5MLの間の成長量」とは、1.2ML以上、2.5ML以下の所定の成長量を意味する。これらの所定の成長速度及び所定の成長量は、所望する量子ドットのサイズに応じて決定される。

【0012】

一般的に、量子ドットは、例えば半導体レーザの活性領域に用いられている(所謂、量子ドットレーザ)。量子ドットレーザに用いられる量子ドットの形成方法では、量子ドットの密度及びサイズの均一さに主眼が置かれている。他方で、近接した量子ドット間における近接場光を介したエネルギー移動を適用する、量子ドットを用いる光論理回路の実現が期待されている。光論理回路では、量子ドットのサイズ、及び近接する量子ドット各々のサイズの比が重要となる。従って、光論理回路の実現には、量子ドットのサイズを適切に制御可能な量子ドットの形成方法が求められるが、量子ドットレーザに用いられる量子ドットの形成方法では、量子ドットのサイズを適切に制御することが困難であることが判明している。

【0013】

しかるに本発明では、第2形成工程における基板温度及び成長量を決定すれば、所望するサイズの量子ドットが形成される。言い換えれば、第2形成工程における基板温度及び成長量を決定すれば、量子ドットのサイズを適切に制御することができる。

【0014】

本発明の量子ドットの形成方法の一態様では、前記形成される量子ドットの直径は、20nm乃至60nmであり、前記形成される量子ドットの高さは、15nm以下である。

【0015】

この態様によれば、形成される量子ドットの直径は20nm乃至60nmであり、高さは15nm以下であるので、該形成される量子ドット内に電子等がトラップされることにより量子理論的効果が発現される。従って、比較的容易にして、例えば光論理回路、量子ドットレーザ等に適用可能な量子ドットを形成することができる。

【0016】

本発明の作用及びその他の利得は次に説明する実施するための最良の形態から明らかにされよう。

【発明を実施するための最良の形態】

【0017】

以下、本発明に係る量子ドットの形成方法の実施形態を図1乃至図10を参照して説明する。尚、以下の図では、各層・各部材を図面上で認識可能な程度の大きさとするため、該各層・各部材毎に縮尺を異ならしめてある。

【0018】

図1に示すように、MBE成長装置200の成長室201内における基板回転加熱機構211上に、GaAs基板110が設置される。ここに、図1は、本実施形態に係る形成方法の工程の一部を示す工程図である。尚、図1では、MBE成長装置200の詳細な部材については適宜省略し、直接関連のある部材のみを示している。

【0019】

次に、成長室201内を、例えば1×10−9Torr以下にした後に、GaAs基板110に対し、蒸発源214からAsを、例えば約1×10−5Torrの照射量で照射する。As照射下において、基板回転加熱機構211によって、GaAs基板110の基板温度を、例えば摂氏600度程度に加熱して、GaAs基板110の表面を清浄にする。

【0020】

次に、基板温度を、例えば摂氏560度にした後に、GaAs基板110に対し、蒸発源214及び212から夫々As及びGaを、例えば約10分間照射して、図2に示すように、GaAs基板110の(001)面上に、本発明に係る「第1半導体層」の一例としてのGaAsバッファ層120を形成する。ここで、As及びGa各々の照射量は、例えばGaAsバッファ層120が1ML/s程度の成長速度で成長可能な照射量として設定される。形成されたGaAs層の厚さは、例えば約150nmである。尚、図2は、図1の工程に続く工程を示す工程図である。以降の図においては、MBE成長装置200に係る部材ついては図示を省略する。

【0021】

次に、基板温度を摂氏480度及び摂氏530度の間の温度にした後に、GaAsバッファ層120上に、蒸発源214及び213から夫々As及びInを照射して、図3に示すように、GaAsバッファ層120上に、本発明に係る「第2半導体層」の一例としてのInAs層130を形成する。ここで、As及びIn各々の照射量は、InAs層130が0.02ML/s及び0.1ML/sの間の成長速度で成長可能な照射量として設定される。尚、図3は、図2の工程に続く工程を示す工程図である。

【0022】

InAs層130の成長に伴い、InAs層130の上面130aに、InAsを含んでなる複数の量子ドット131が自己組織化成長により形成される。InAs層130の成長量を1.2ML及び2.5MLの間の成長量とすることによって、直径20nm乃至60nm、高さ15nm以下の量子ドット131を形成することができる。尚、本実施形態に係る「上面130a」は、本発明に係る「第2半導体層の第1半導体層と対向しない側の面」の一例である。

【0023】

ここで、InAs層130を形成する際の、成長速度、基板温度及びInAs層130の成長量について、図5乃至図10を参照して説明を加える。ここに、図5は、成長速度を0.04ML/sとした場合における基板温度及び量子ドットの直径の関係をInAs層130の成長量毎に示す実験値の一例であり、図6は、成長速度を0.04ML/sとした場合における基板温度及び量子ドットの高さの関係をInAs層130の成長量毎に示す実験値の一例である。尚、図5及び図6においては、便宜上、記号が相互に重ならないように、基板温度をずらして示している。また、以降の図において、図中の記号に付されている縦線は誤差を示している。

【0024】

成長速度が決定(又は固定)されることにより得られる図5及び図6に示すように、基板温度及びInAs層130の成長量が決定されれば、形成される量子ドット131の直径及び高さを適切に決定することができる。言い換えれば、所望する量子ドットの直径及び高さから、基板温度及びInAs層130の成長量を夫々決定することができる。

【0025】

図5及び図6を用いて、所望する量子ドットの直径及び高さから、基板温度及びInAs層130の成長量を夫々決定する場合、先ず、例えば所望する量子ドットの直径及び高さを形成可能な基板温度の範囲を特定する。次に、該特定された基板温度の範囲内において基板温度を決定する。

【0026】

ここで、例えば基板温度を摂氏520度と決定した場合、次に、図7及び図8に示すような、決定された基板温度における量子ドットの直径又は高さとInAs層130の成長量との関係から、所望する量子ドットの直径及び高さを形成可能な成長量を決定する。ここに、図7は、基板温度を摂氏520度とした場合のInAs層130の成長量及び量子ドットの直径の関係を示す実験値の一例であり、図8は、基板温度を摂氏520度とした場合のInAs層130の成長量及び量子ドットの高さの関係を示す実験値の一例である。尚、成長量は、例えば量子ドット131を含む半導体装置全体のサイズ、製造コスト等に応じて決定すればよい。

【0027】

或いは、上述の如く、最初に成長速度が決定(又は固定)されることに代えて、基板温度及びInAs層130の成長量が決定された後に、図9及び図10に示すような、量子ドットの直径又は高さと成長速度との関係から、所望する量子ドットの直径及び高さを形成可能な成長速度を決定してもよい。ここに、図9は、基板温度摂氏500度、成長量2.0MLとした場合における成長速度及び量子ドットの直径の関係を示す実験値の一例であり、図10は、基板温度摂氏500度、成長量2.0MLとした場合における成長速度及び量子ドットの高さの関係を示す実験値の一例である。

【0028】

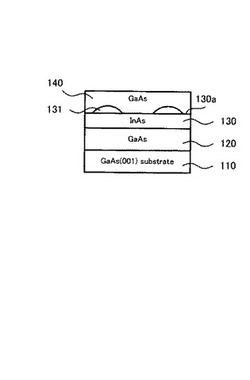

量子ドット131が形成された後に、InAs層130上に、蒸発源214及び213から夫々As及びGaを照射することにより、図4に示すように、GaAs被覆層140を形成する。ここに、図4は、図3の工程に続く工程を示す工程図である。尚、このGaAs被覆層140上に、InAsを含んでなる量子ドットを上述の方法で形成し、更に、該量子ドットを上述の如くGaAsにより被覆することを繰り返すことによって、InAsを含んでなる量子ドットを多層化してもよい。

【0029】

本発明は、上述した実施形態に限られるものではなく、請求の範囲及び明細書全体から読み取れる発明の要旨或いは思想に反しない範囲で適宜変更可能であり、そのような変更を伴う量子ドットの形成方法もまた本発明の技術的範囲に含まれるものである。

【図面の簡単な説明】

【0030】

【図1】本発明の実施形態に係る形成方法の工程の一部を示す工程図である。

【図2】図1の工程に続く工程を示す工程図である。

【図3】図2の工程に続く工程を示す工程図である。

【図4】図3の工程に続く工程を示す工程図である。

【図5】成長速度を0.04ML/sとした場合における基板温度及び量子ドットの直径の関係をInAs層の成長量毎に示す実験値の一例である。

【図6】成長速度を0.04ML/sとした場合における基板温度及び量子ドットの高さの関係をInAs層の成長量毎に示す実験値の一例である。

【図7】基板温度を摂氏520度とした場合のInAs層の成長量及び量子ドットの直径の関係を示す実験値の一例である。

【図8】基板温度を摂氏520度とした場合のInAs層の成長量及び量子ドットの高さの関係を示す実験値の一例である。

【図9】基板温度摂氏500度、成長量2.0MLとした場合における成長速度及び量子ドットの直径の関係を示す実験値の一例である。

【図10】基板温度摂氏500度、成長量2.0MLとした場合における成長速度及び量子ドットの高さの関係を示す実験値の一例である。

【符号の説明】

【0031】

110…GaAs基板、120…GaAsバッファ層、130…InAs層、131…量子ドット、140…GaAs被覆層、200…MBE成長装置、211…基板回転加熱機構、212、213、214…蒸発源

【技術分野】

【0001】

本発明は、例えばGaAs等のIII−V族化合物半導体上に、例えばInAs等のIII−V族化合物からなる量子ドットを形成する量子ドットの形成方法の技術分野に関する。

【背景技術】

【0002】

この種の形成方法として、例えば、InGaAs層上に、InAsからなる量子ドットを形成する際の成長温度を、摂氏470度〜540度の範囲を選択することによって、ドット密度を5倍以上調節する技術が提案されている(特許文献1参照)。或いは、AlGaSb化合物半導体上に、In分子線及びAs分子線を照射して、InAs量子ドットを成長させて形成する技術が提案されている。ここでは特に、基板の温度を約摂氏500度、As分子線の照射量を約5.5×10−7Torrとすることによって、波長約1.3μm(マイクロメートル)及び1.55μmの発光をする量子ドットを形成する技術が提案されている(特許文献2参照)。

【0003】

或いは、基板温度摂氏520度、圧力6.65×10−4Paにおいて、GaAsからなるクラッド層に、As及びInを照射し、InAs膜を1.9ML(モノレイヤー)まで結晶成長させグレインを形成する。その後、Inを間欠照射することによって、直径30〜65nm(ナノメートル)のInAsからなる量子ドットを形成する技術が提案されている(特許文献3参照)。

【0004】

或いは、GaAs層上にAs2を供給しながら成長中断を60秒入れた後、In及びAs2を供給して、InAs量子ドットを形成する技術が提案されている。ここでは特に、InAsの成長速度を0.1ML/s(モノレイヤー/秒)、成長温度を摂氏520度とすることによって、量子ドットの表面密度を1.1×1011cm−2とする技術が提案されている(特許文献4参照)。或いは、InGaAsP層上にInAsからなる量子ドットを形成する際の成長温度を、摂氏450度以下にすることによって、量子ドットの横方向のサイズを25nm以下まで縮小する技術が提案されている(特許文献5参照)。

【0005】

【特許文献1】特開2004−528705号公報

【特許文献2】特開2005−93553号公報

【特許文献3】特開2006−269886号公報

【特許文献4】特開2007−53322号公報

【特許文献5】特開2007−157975号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上述の背景技術によれば、量子ドットのサイズを適切に制御することが困難であるという技術的問題点がある。

【0007】

本発明は、例えば上記問題点に鑑みてなされたものであり、量子ドットのサイズを適切に制御することができる量子ドットの形成方法を提供することを課題とする。

【課題を解決するための手段】

【0008】

本発明の量子ドットの形成方法は、上記課題を解決するために、基板上にGaAsを含んでなる第1半導体層を形成する第1形成工程と、前記基板の基板温度を摂氏480度及び摂氏530度の間の温度にした後に、前記第1半導体層の上に、In及びAsを夫々照射して、InAsを含んでなる第2半導体層を形成する第2形成工程とを備え、前記第2形成工程において、前記第2半導体層の成長速度を0.02ML/s及び0.1ML/sの間の成長速度とし、前記第2半導体層の成長量を1.2ML及び2.5MLの間の成長量とすることにより、前記第2半導体層の前記第1半導体層と対向しない側の面にInAsを含んでなる量子ドットを形成する。

【0009】

本発明の量子ドットの形成方法によれば、例えば分子線エピタキシャル(Molecular Beam Epitaxy:MBE)成長装置内に、例えばGaAs等からなる基板を設置した後に、第1形成工程において、基板上にGa及びAsを夫々照射することによって、基板上にGaAsを含んでなる第1半導体層をエピタキシャル成長させて形成する。

【0010】

第2形成工程において、基板温度を摂氏480度及び摂氏530度の間の温度にした後に、第1半導体層の上に、In及びAsを夫々照射して、InAsを含んでなる第2半導体層を形成する。ここに、「摂氏480度及び摂氏530度の間の温度」とは、摂氏480度以上、摂氏530度以下の所定の温度を意味する。この所定の温度は、所望する量子ドットのサイズに応じて決定される。

【0011】

第2形成工程では、第2半導体層の成長速度が0.02ML/s及び0.1ML/sの間の成長速度となるように、例えばMBE成長装置における蒸発源内のInの温度等が設定されると共に、第2半導体層の成長量が1.2ML及び2.5MLの間の成長量となるように、In及びAsが夫々照射されることにより、第2半導体層の第1半導体層と対向しない側の面(即ち、第2半導体層の上面)に、InAsを含んでなる量子ドットが自己組織化成長によって形成される。尚、「0.02ML/s及び0.1ML/sの間の成長速度」とは、0.02ML/s以上、0.1ML/s以下の所定の成長速度を意味する。また、「1.2ML及び2.5MLの間の成長量」とは、1.2ML以上、2.5ML以下の所定の成長量を意味する。これらの所定の成長速度及び所定の成長量は、所望する量子ドットのサイズに応じて決定される。

【0012】

一般的に、量子ドットは、例えば半導体レーザの活性領域に用いられている(所謂、量子ドットレーザ)。量子ドットレーザに用いられる量子ドットの形成方法では、量子ドットの密度及びサイズの均一さに主眼が置かれている。他方で、近接した量子ドット間における近接場光を介したエネルギー移動を適用する、量子ドットを用いる光論理回路の実現が期待されている。光論理回路では、量子ドットのサイズ、及び近接する量子ドット各々のサイズの比が重要となる。従って、光論理回路の実現には、量子ドットのサイズを適切に制御可能な量子ドットの形成方法が求められるが、量子ドットレーザに用いられる量子ドットの形成方法では、量子ドットのサイズを適切に制御することが困難であることが判明している。

【0013】

しかるに本発明では、第2形成工程における基板温度及び成長量を決定すれば、所望するサイズの量子ドットが形成される。言い換えれば、第2形成工程における基板温度及び成長量を決定すれば、量子ドットのサイズを適切に制御することができる。

【0014】

本発明の量子ドットの形成方法の一態様では、前記形成される量子ドットの直径は、20nm乃至60nmであり、前記形成される量子ドットの高さは、15nm以下である。

【0015】

この態様によれば、形成される量子ドットの直径は20nm乃至60nmであり、高さは15nm以下であるので、該形成される量子ドット内に電子等がトラップされることにより量子理論的効果が発現される。従って、比較的容易にして、例えば光論理回路、量子ドットレーザ等に適用可能な量子ドットを形成することができる。

【0016】

本発明の作用及びその他の利得は次に説明する実施するための最良の形態から明らかにされよう。

【発明を実施するための最良の形態】

【0017】

以下、本発明に係る量子ドットの形成方法の実施形態を図1乃至図10を参照して説明する。尚、以下の図では、各層・各部材を図面上で認識可能な程度の大きさとするため、該各層・各部材毎に縮尺を異ならしめてある。

【0018】

図1に示すように、MBE成長装置200の成長室201内における基板回転加熱機構211上に、GaAs基板110が設置される。ここに、図1は、本実施形態に係る形成方法の工程の一部を示す工程図である。尚、図1では、MBE成長装置200の詳細な部材については適宜省略し、直接関連のある部材のみを示している。

【0019】

次に、成長室201内を、例えば1×10−9Torr以下にした後に、GaAs基板110に対し、蒸発源214からAsを、例えば約1×10−5Torrの照射量で照射する。As照射下において、基板回転加熱機構211によって、GaAs基板110の基板温度を、例えば摂氏600度程度に加熱して、GaAs基板110の表面を清浄にする。

【0020】

次に、基板温度を、例えば摂氏560度にした後に、GaAs基板110に対し、蒸発源214及び212から夫々As及びGaを、例えば約10分間照射して、図2に示すように、GaAs基板110の(001)面上に、本発明に係る「第1半導体層」の一例としてのGaAsバッファ層120を形成する。ここで、As及びGa各々の照射量は、例えばGaAsバッファ層120が1ML/s程度の成長速度で成長可能な照射量として設定される。形成されたGaAs層の厚さは、例えば約150nmである。尚、図2は、図1の工程に続く工程を示す工程図である。以降の図においては、MBE成長装置200に係る部材ついては図示を省略する。

【0021】

次に、基板温度を摂氏480度及び摂氏530度の間の温度にした後に、GaAsバッファ層120上に、蒸発源214及び213から夫々As及びInを照射して、図3に示すように、GaAsバッファ層120上に、本発明に係る「第2半導体層」の一例としてのInAs層130を形成する。ここで、As及びIn各々の照射量は、InAs層130が0.02ML/s及び0.1ML/sの間の成長速度で成長可能な照射量として設定される。尚、図3は、図2の工程に続く工程を示す工程図である。

【0022】

InAs層130の成長に伴い、InAs層130の上面130aに、InAsを含んでなる複数の量子ドット131が自己組織化成長により形成される。InAs層130の成長量を1.2ML及び2.5MLの間の成長量とすることによって、直径20nm乃至60nm、高さ15nm以下の量子ドット131を形成することができる。尚、本実施形態に係る「上面130a」は、本発明に係る「第2半導体層の第1半導体層と対向しない側の面」の一例である。

【0023】

ここで、InAs層130を形成する際の、成長速度、基板温度及びInAs層130の成長量について、図5乃至図10を参照して説明を加える。ここに、図5は、成長速度を0.04ML/sとした場合における基板温度及び量子ドットの直径の関係をInAs層130の成長量毎に示す実験値の一例であり、図6は、成長速度を0.04ML/sとした場合における基板温度及び量子ドットの高さの関係をInAs層130の成長量毎に示す実験値の一例である。尚、図5及び図6においては、便宜上、記号が相互に重ならないように、基板温度をずらして示している。また、以降の図において、図中の記号に付されている縦線は誤差を示している。

【0024】

成長速度が決定(又は固定)されることにより得られる図5及び図6に示すように、基板温度及びInAs層130の成長量が決定されれば、形成される量子ドット131の直径及び高さを適切に決定することができる。言い換えれば、所望する量子ドットの直径及び高さから、基板温度及びInAs層130の成長量を夫々決定することができる。

【0025】

図5及び図6を用いて、所望する量子ドットの直径及び高さから、基板温度及びInAs層130の成長量を夫々決定する場合、先ず、例えば所望する量子ドットの直径及び高さを形成可能な基板温度の範囲を特定する。次に、該特定された基板温度の範囲内において基板温度を決定する。

【0026】

ここで、例えば基板温度を摂氏520度と決定した場合、次に、図7及び図8に示すような、決定された基板温度における量子ドットの直径又は高さとInAs層130の成長量との関係から、所望する量子ドットの直径及び高さを形成可能な成長量を決定する。ここに、図7は、基板温度を摂氏520度とした場合のInAs層130の成長量及び量子ドットの直径の関係を示す実験値の一例であり、図8は、基板温度を摂氏520度とした場合のInAs層130の成長量及び量子ドットの高さの関係を示す実験値の一例である。尚、成長量は、例えば量子ドット131を含む半導体装置全体のサイズ、製造コスト等に応じて決定すればよい。

【0027】

或いは、上述の如く、最初に成長速度が決定(又は固定)されることに代えて、基板温度及びInAs層130の成長量が決定された後に、図9及び図10に示すような、量子ドットの直径又は高さと成長速度との関係から、所望する量子ドットの直径及び高さを形成可能な成長速度を決定してもよい。ここに、図9は、基板温度摂氏500度、成長量2.0MLとした場合における成長速度及び量子ドットの直径の関係を示す実験値の一例であり、図10は、基板温度摂氏500度、成長量2.0MLとした場合における成長速度及び量子ドットの高さの関係を示す実験値の一例である。

【0028】

量子ドット131が形成された後に、InAs層130上に、蒸発源214及び213から夫々As及びGaを照射することにより、図4に示すように、GaAs被覆層140を形成する。ここに、図4は、図3の工程に続く工程を示す工程図である。尚、このGaAs被覆層140上に、InAsを含んでなる量子ドットを上述の方法で形成し、更に、該量子ドットを上述の如くGaAsにより被覆することを繰り返すことによって、InAsを含んでなる量子ドットを多層化してもよい。

【0029】

本発明は、上述した実施形態に限られるものではなく、請求の範囲及び明細書全体から読み取れる発明の要旨或いは思想に反しない範囲で適宜変更可能であり、そのような変更を伴う量子ドットの形成方法もまた本発明の技術的範囲に含まれるものである。

【図面の簡単な説明】

【0030】

【図1】本発明の実施形態に係る形成方法の工程の一部を示す工程図である。

【図2】図1の工程に続く工程を示す工程図である。

【図3】図2の工程に続く工程を示す工程図である。

【図4】図3の工程に続く工程を示す工程図である。

【図5】成長速度を0.04ML/sとした場合における基板温度及び量子ドットの直径の関係をInAs層の成長量毎に示す実験値の一例である。

【図6】成長速度を0.04ML/sとした場合における基板温度及び量子ドットの高さの関係をInAs層の成長量毎に示す実験値の一例である。

【図7】基板温度を摂氏520度とした場合のInAs層の成長量及び量子ドットの直径の関係を示す実験値の一例である。

【図8】基板温度を摂氏520度とした場合のInAs層の成長量及び量子ドットの高さの関係を示す実験値の一例である。

【図9】基板温度摂氏500度、成長量2.0MLとした場合における成長速度及び量子ドットの直径の関係を示す実験値の一例である。

【図10】基板温度摂氏500度、成長量2.0MLとした場合における成長速度及び量子ドットの高さの関係を示す実験値の一例である。

【符号の説明】

【0031】

110…GaAs基板、120…GaAsバッファ層、130…InAs層、131…量子ドット、140…GaAs被覆層、200…MBE成長装置、211…基板回転加熱機構、212、213、214…蒸発源

【特許請求の範囲】

【請求項1】

基板上にGaAsを含んでなる第1半導体層を形成する第1形成工程と、

前記基板の基板温度を摂氏480度及び摂氏530度の間の温度にした後に、前記第1半導体層の上に、In及びAsを夫々照射して、InAsを含んでなる第2半導体層を形成する第2形成工程と

を備え、

前記第2形成工程において、前記第2半導体層の成長速度を0.02ML/s及び0.1ML/sの間の成長速度とし、前記第2半導体層の成長量を1.2ML及び2.5MLの間の成長量とすることにより、前記第2半導体層の前記第1半導体層と対向しない側の面にInAsを含んでなる量子ドットを形成する

ことを特徴とする量子ドットの形成方法。

【請求項2】

前記形成される量子ドットの直径は、20nm乃至60nmであり、前記形成される量子ドットの高さは、15nm以下であることを特徴とする請求項1に記載の量子ドットの形成方法。

【請求項1】

基板上にGaAsを含んでなる第1半導体層を形成する第1形成工程と、

前記基板の基板温度を摂氏480度及び摂氏530度の間の温度にした後に、前記第1半導体層の上に、In及びAsを夫々照射して、InAsを含んでなる第2半導体層を形成する第2形成工程と

を備え、

前記第2形成工程において、前記第2半導体層の成長速度を0.02ML/s及び0.1ML/sの間の成長速度とし、前記第2半導体層の成長量を1.2ML及び2.5MLの間の成長量とすることにより、前記第2半導体層の前記第1半導体層と対向しない側の面にInAsを含んでなる量子ドットを形成する

ことを特徴とする量子ドットの形成方法。

【請求項2】

前記形成される量子ドットの直径は、20nm乃至60nmであり、前記形成される量子ドットの高さは、15nm以下であることを特徴とする請求項1に記載の量子ドットの形成方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2009−231601(P2009−231601A)

【公開日】平成21年10月8日(2009.10.8)

【国際特許分類】

【出願番号】特願2008−76306(P2008−76306)

【出願日】平成20年3月24日(2008.3.24)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成18年度独立行政法人新エネルギー・産業技術総合開発機構低損失オプティカル新機能部材技術開発委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000005016)パイオニア株式会社 (3,620)

【出願人】(503213291)パイオニア・マイクロ・テクノロジー株式会社 (25)

【Fターム(参考)】

【公開日】平成21年10月8日(2009.10.8)

【国際特許分類】

【出願日】平成20年3月24日(2008.3.24)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成18年度独立行政法人新エネルギー・産業技術総合開発機構低損失オプティカル新機能部材技術開発委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000005016)パイオニア株式会社 (3,620)

【出願人】(503213291)パイオニア・マイクロ・テクノロジー株式会社 (25)

【Fターム(参考)】

[ Back to top ]